Programming FPGA through the GBTSCA REconfigure FPGA through

Programming FPGA through the GBT-SCA RE-configure FPGA through JTAG ◦ Heidelberg option, needs reprogramming of Altera devices (not in this talk) Needed for re-programming after loss of conf. due to radiation ◦ Nikhef option, re-programming would be a big advantage Re-configuration needed for debugging, bug fixes, and upgrades. Only during technical stops. (no time limitations) 432 FE-Boxes with each 4 Actel proasic 3 e’s Flash based FPGA’s ◦ Difficult to physically reach the devices 11 April 2013 Antonio Pellegrino, Tom Sluijk, Wilco Vink 1

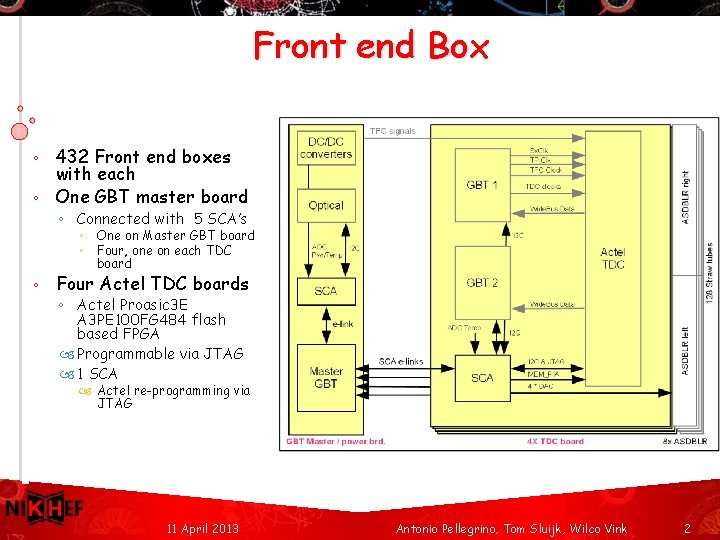

Front end Box 432 Front end boxes with each ◦ One GBT master board ◦ ◦ Connected with 5 SCA’s ◦ One on Master GBT board ◦ Four, one on each TDC board ◦ Four Actel TDC boards ◦ Actel Proasic 3 E A 3 PE 100 FG 484 flash based FPGA Programmable via JTAG 1 SCA Actel re-programming via JTAG 11 April 2013 Antonio Pellegrino, Tom Sluijk, Wilco Vink 2

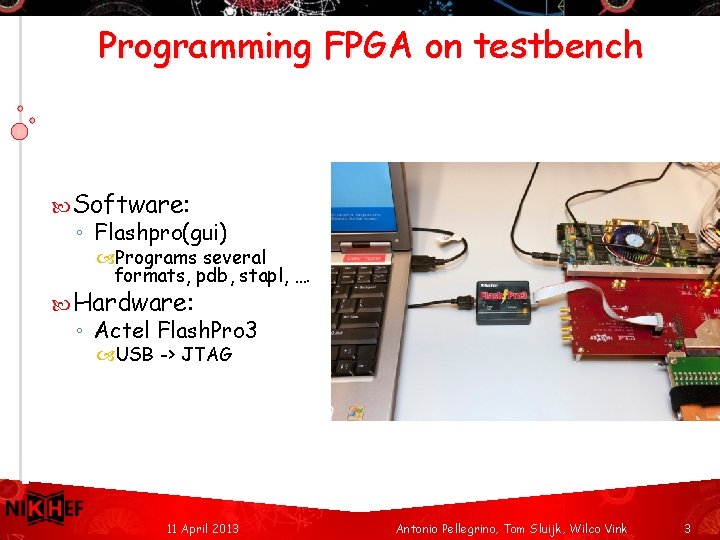

Programming FPGA on testbench Software: ◦ Flashpro(gui) Programs several formats, pdb, stapl, …. Hardware: ◦ Actel Flash. Pro 3 USB -> JTAG 11 April 2013 Antonio Pellegrino, Tom Sluijk, Wilco Vink 3

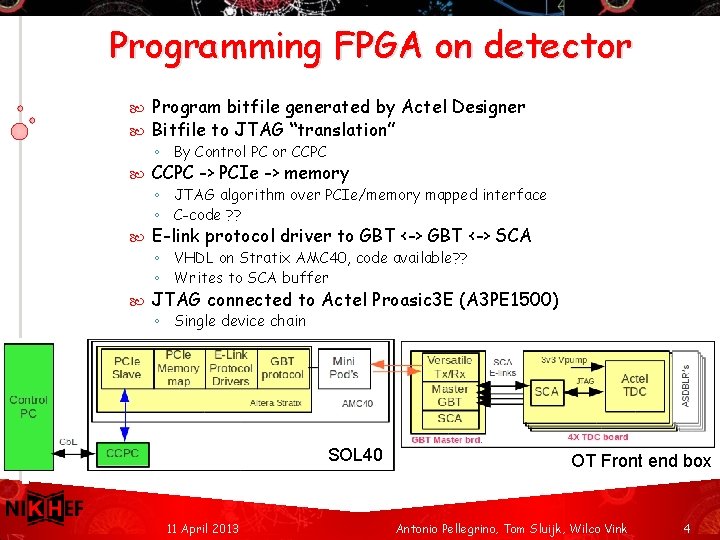

Programming FPGA on detector Program bitfile generated by Actel Designer Bitfile to JTAG “translation” ◦ By Control PC or CCPC -> PCIe -> memory ◦ JTAG algorithm over PCIe/memory mapped interface ◦ C-code ? ? E-link protocol driver to GBT <-> SCA ◦ VHDL on Stratix AMC 40, code available? ? ◦ Writes to SCA buffer JTAG connected to Actel Proasic 3 E (A 3 PE 1500) ◦ Single device chain SOL 40 11 April 2013 OT Front end box Antonio Pellegrino, Tom Sluijk, Wilco Vink 4

CCPC software Available software by FPGA suppliers ◦ Actel Stapl player, C-code available http: //www. actel. com/download/program_debug/stapl 11. aspx#sup CCPC compatible? ◦ Actel Bitfile -> JTAG register/pins (bitbangs JTAG pins/register) Ccode written for microprocessor(s), Uses Actel DAT format http: //www. actel. com/download/program_debug/directc/dc 27. aspx CCPC compatible? (Maybe in embedded Processor FPGA? ? ) ◦ Altera JAM stapl player (currently used in CCPC’s LHCb for Xilinx and Altera) Actel generated stapl files aren’t compatible (both mention JESD 71 standard) Translation (visa versa) to ◦ PCIe memory map ◦ E-link to SCA JTAG buffer ◦ Something available ? ? ? 11 April 2013 https: //indico. cern. ch/get. File. py/access? contrib. Id =7&session. Id=3&res. Id=1&material. Id=slides&conf. I d=242284 Antonio Pellegrino, Tom Sluijk, Wilco Vink 5

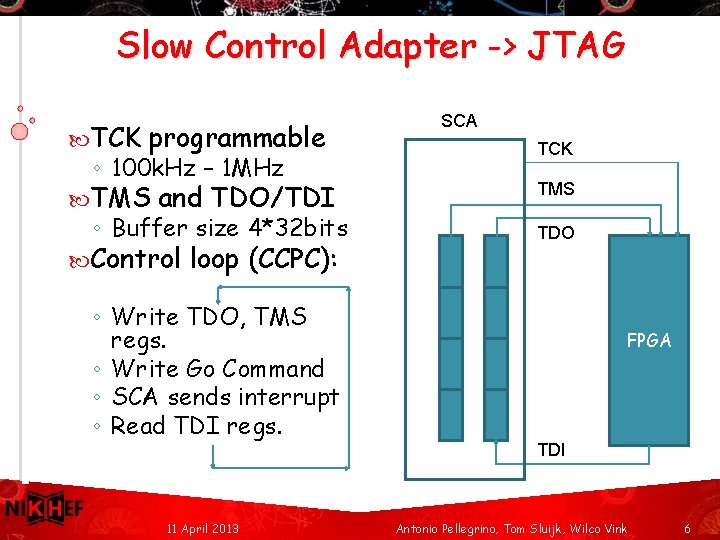

Slow Control Adapter -> JTAG TCK programmable ◦ 100 k. Hz – 1 MHz TMS and TDO/TDI ◦ Buffer size 4*32 bits Control loop (CCPC): ◦ Write TDO, TMS regs. ◦ Write Go Command ◦ SCA sends interrupt ◦ Read TDI regs. 11 April 2013 SCA TCK TMS TDO FPGA TDI Antonio Pellegrino, Tom Sluijk, Wilco Vink 6

Requirements and limitations JTAG “player” software ◦ No fixed timing relation between multiple bursts of SCA buffer size in JTAG cycles ◦ 128 bits + GBT latency, from TDO device to TDO(in) software on CCPC Stapl files reads ID codes before programming, -> input needed Otherwise customize Stapl files Actel timing requirements unknown SCA limitations ◦ Does the device require constant bursts / TCK, min/max frequency ? ? ? ◦ Asked Actel, waiting for answers… ◦ Pro. Asic 3 Not capable of partial re-programming (Actel information) ◦ JTAG Buffer size 128 bit ◦ Latency in read back from TDO 11 April 2013 Antonio Pellegrino, Tom Sluijk, Wilco Vink 7

- Slides: 7