FPGA DEVELOPMENT FLOW FOR FUTURE LARGE SPACE FPGA

- Slides: 24

FPGA DEVELOPMENT FLOW FOR FUTURE LARGE SPACE FPGA Florent Manni (CNES-DCT/TV/IN) 15 -17/03/2016 SEFUW - Estec 1 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

INTRODUCTION ZYNQ 7030 : DEVELOPMENT EXAMPLE KEY FEATURE FOR FUTURE DEVELOPMENT FLOW CONCLUSION SOMMAIRE 2 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

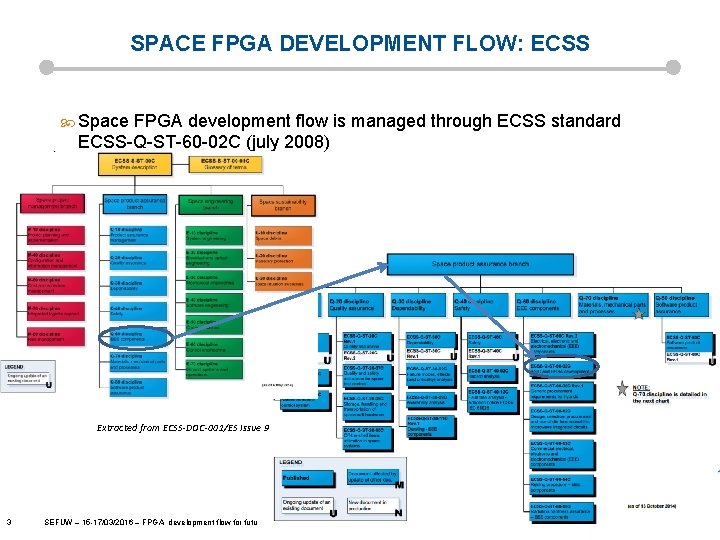

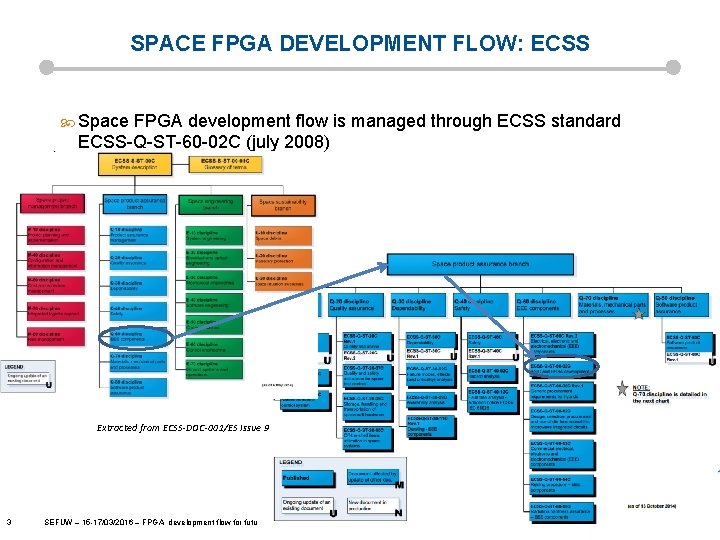

SPACE FPGA DEVELOPMENT FLOW: ECSS Space FPGA development flow is managed through ECSS standard ECSS-Q-ST-60 -02 C (july 2008) Extracted from ECSS-DOC-001/ES Issue 9 3 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

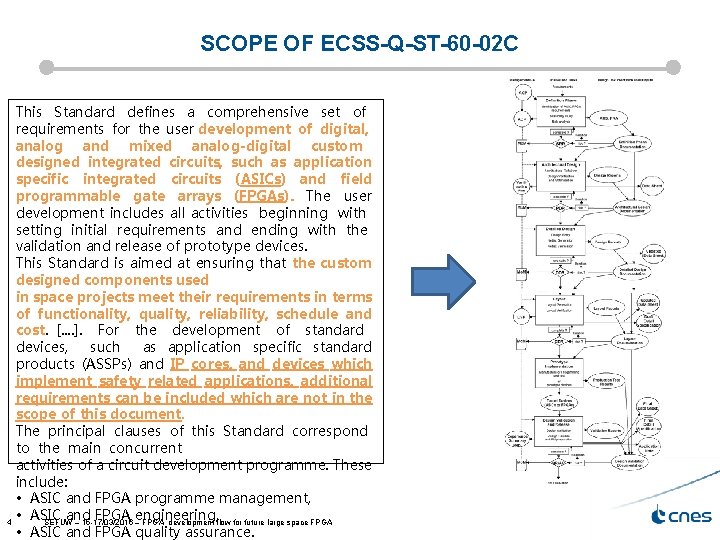

SCOPE OF ECSS-Q-ST-60 -02 C This Standard defines a comprehensive set of requirements for the user development of digital, analog and mixed analog‐digital custom designed integrated circuits, such as application specific integrated circuits (ASICs) and field programmable gate arrays (FPGAs). The user development includes all activities beginning with setting initial requirements and ending with the validation and release of prototype devices. This Standard is aimed at ensuring that the custom designed components used in space projects meet their requirements in terms of functionality, quality, reliability, schedule and cost. [. . ]. For the development of standard devices, such as application specific standard products (ASSPs) and IP cores, and devices which implement safety related applications, additional requirements can be included which are not in the scope of this document. The principal clauses of this Standard correspond to the main concurrent activities of a circuit development programme. These include: • ASIC and FPGA programme management, • ASIC and FPGA engineering, 4 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA • ASIC and FPGA quality assurance.

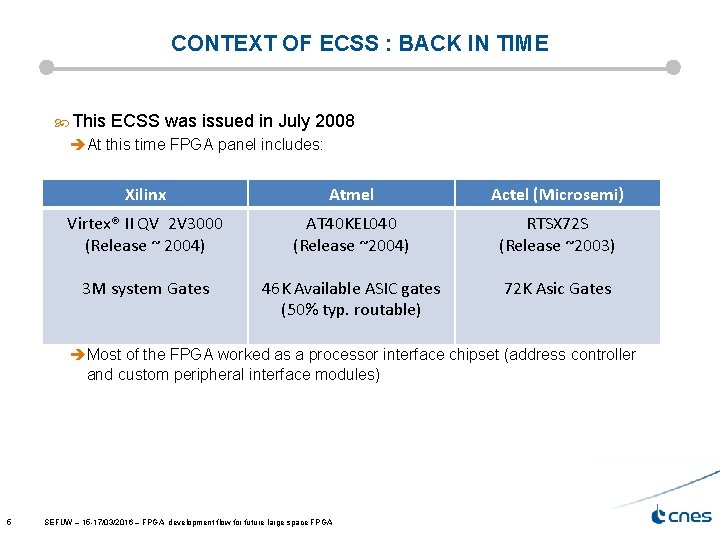

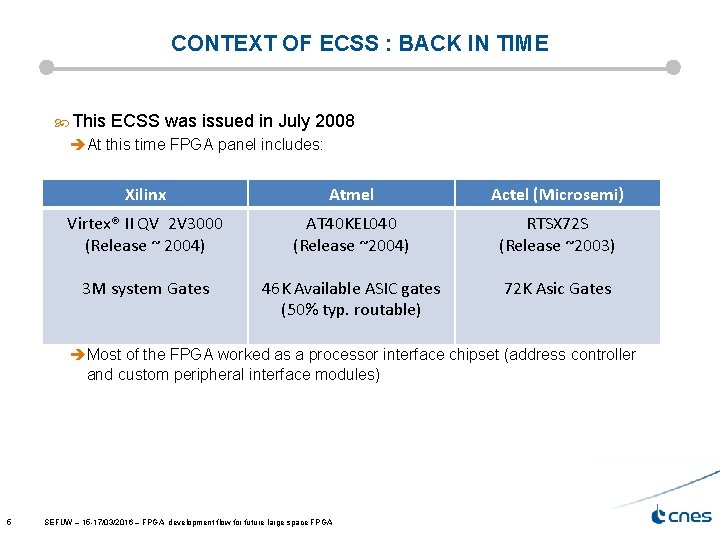

CONTEXT OF ECSS : BACK IN TIME This ECSS was issued in July 2008 èAt this time FPGA panel includes: Xilinx Atmel Actel (Microsemi) Virtex® II QV 2 V 3000 (Release ~ 2004) AT 40 KEL 040 (Release ~2004) RTSX 72 S (Release ~2003) 3 M system Gates 46 K Available ASIC gates (50% typ. routable) 72 K Asic Gates èMost of the FPGA worked as a processor interface chipset (address controller and custom peripheral interface modules) 5 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

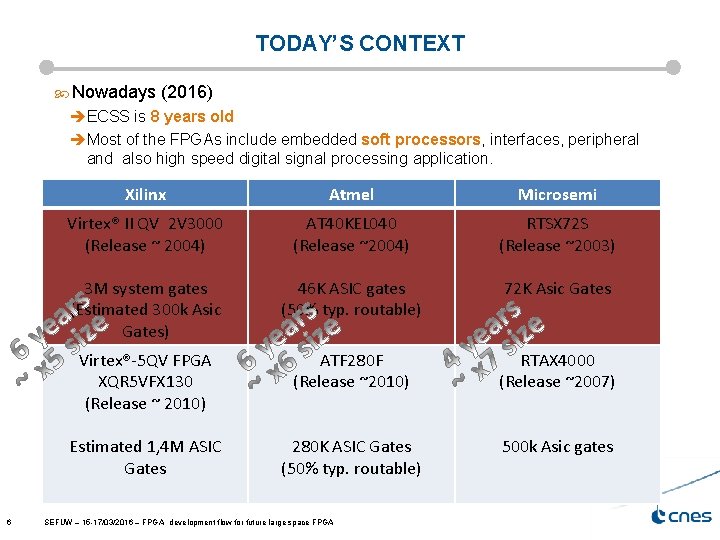

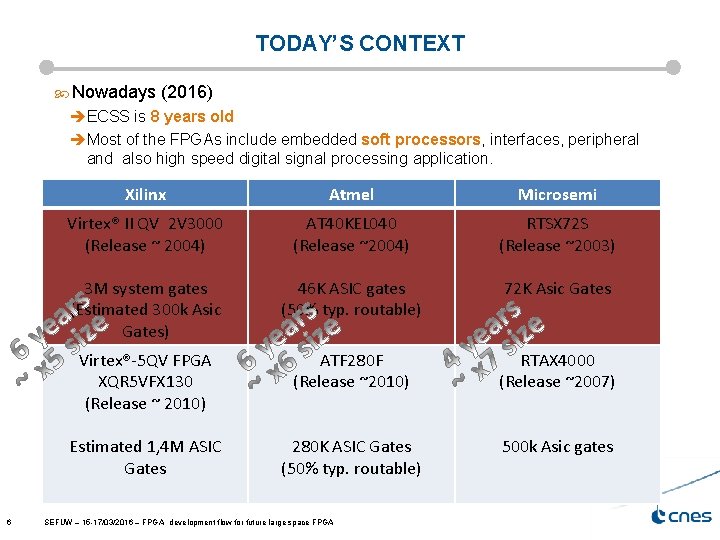

TODAY’S CONTEXT Nowadays (2016) èECSS is 8 years old èMost of the FPGAs include embedded soft processors, interfaces, peripheral and also high speed digital signal processing application. 6 Xilinx Atmel Microsemi Virtex® II QV 2 V 3000 (Release ~ 2004) AT 40 KEL 040 (Release ~2004) RTSX 72 S (Release ~2003) 3 M system gates (Estimated 300 k Asic Gates) 46 K ASIC gates (50% typ. routable) 72 K Asic Gates Virtex®-5 QV FPGA XQR 5 VFX 130 (Release ~ 2010) ATF 280 F (Release ~2010) RTAX 4000 (Release ~2007) Estimated 1, 4 M ASIC Gates 280 K ASIC Gates (50% typ. routable) 500 k Asic gates SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

INTRODUCTION ZYNQ 7030 : DEVELOPMENT EXAMPLE KEY FEATURE FOR FUTURE DEVELOPMENT FLOW CONCLUSION SOMMAIRE 7 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

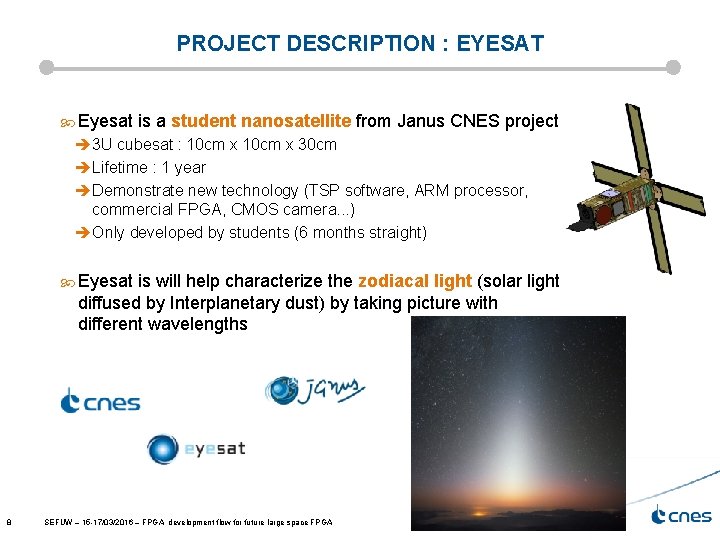

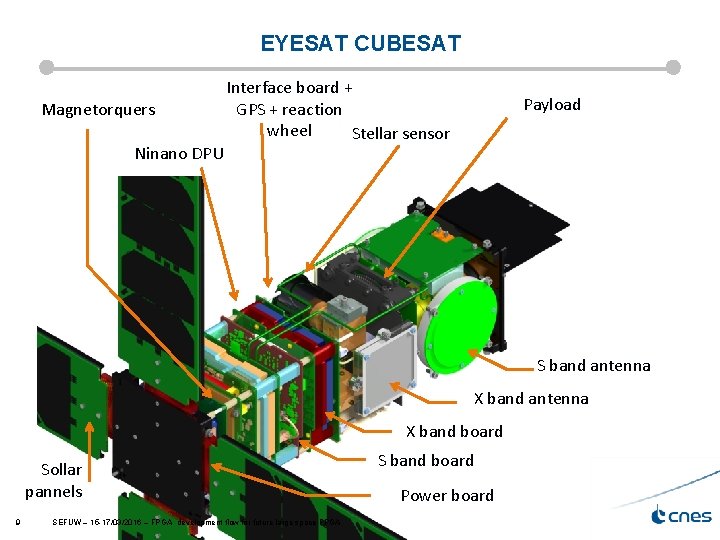

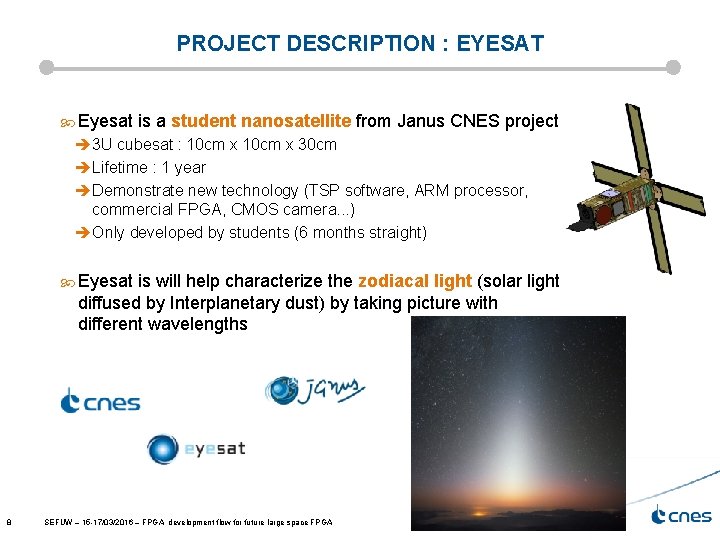

PROJECT DESCRIPTION : EYESAT Eyesat is a student nanosatellite from Janus CNES project è 3 U cubesat : 10 cm x 30 cm èLifetime : 1 year èDemonstrate new technology (TSP software, ARM processor, commercial FPGA, CMOS camera. . . ) èOnly developed by students (6 months straight) Eyesat is will help characterize the zodiacal light (solar light diffused by Interplanetary dust) by taking picture with different wavelengths 8 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

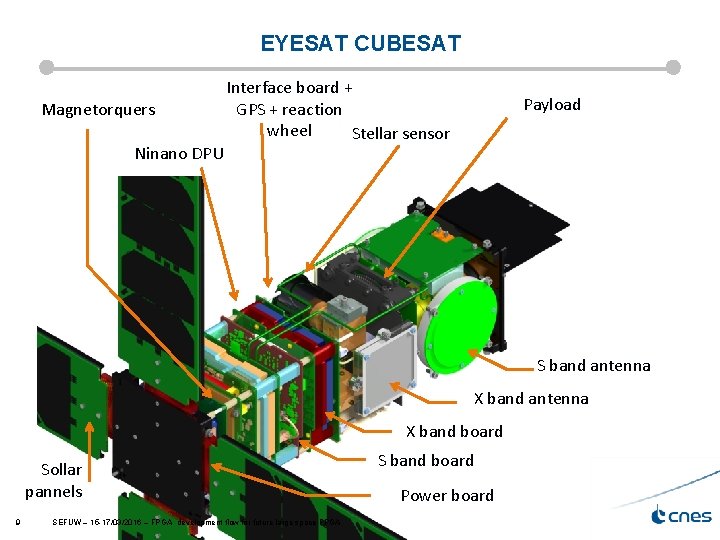

EYESAT CUBESAT Magnetorquers Ninano DPU Interface board + GPS + reaction wheel Stellar sensor Payload S band antenna X band board Sollar pannels 9 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA S band board Power board

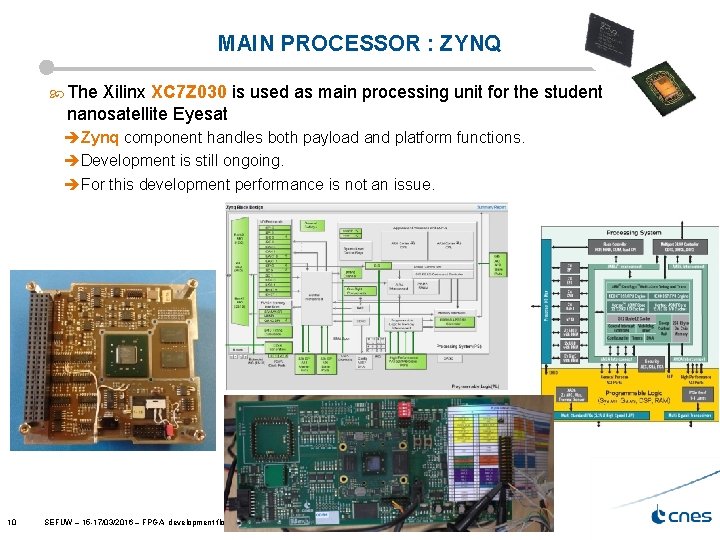

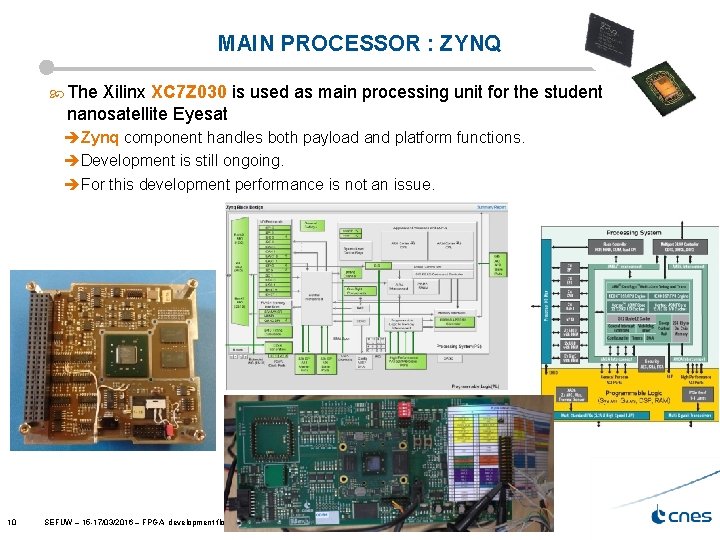

MAIN PROCESSOR : ZYNQ The Xilinx XC 7 Z 030 is used as main processing unit for the student nanosatellite Eyesat èZynq component handles both payload and platform functions. èDevelopment is still ongoing. èFor this development performance is not an issue. 10 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

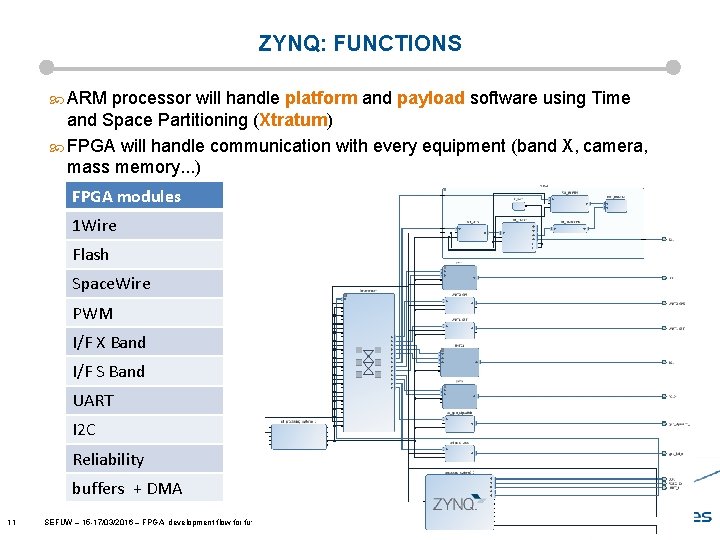

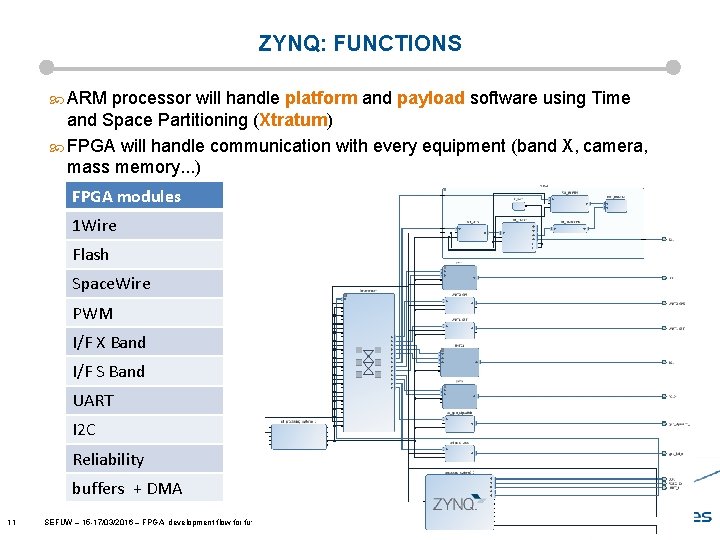

ZYNQ: FUNCTIONS ARM processor will handle platform and payload software using Time and Space Partitioning (Xtratum) FPGA will handle communication with every equipment (band X, camera, mass memory. . . ) FPGA modules 1 Wire Flash Space. Wire PWM I/F X Band I/F S Band UART I 2 C Reliability buffers + DMA 11 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

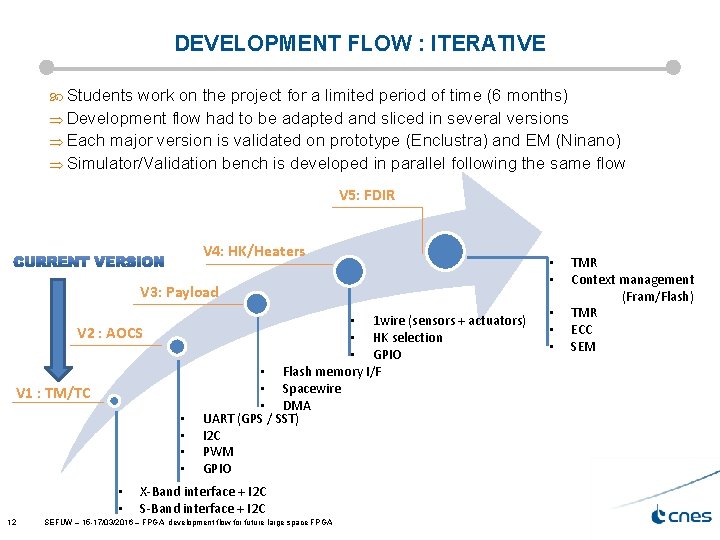

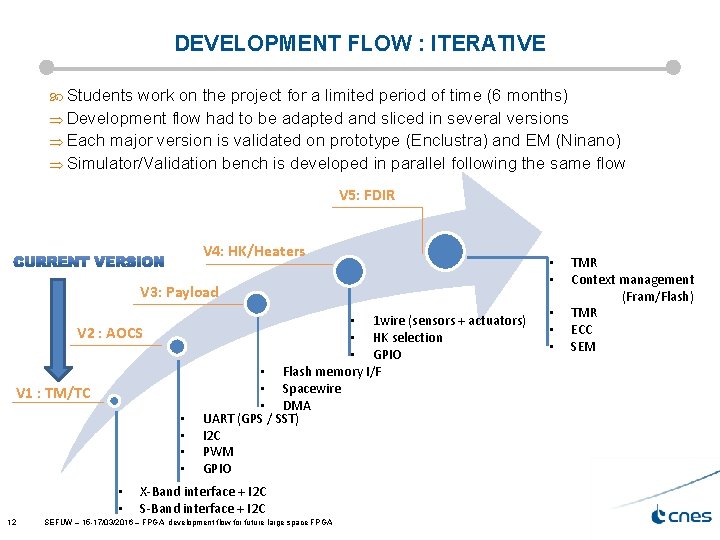

DEVELOPMENT FLOW : ITERATIVE Students work on the project for a limited period of time (6 months) Þ Development flow had to be adapted and sliced in several versions Þ Each major version is validated on prototype (Enclustra) and EM (Ninano) Þ Simulator/Validation bench is developed in parallel following the same flow V 5: FDIR V 4: HK/Heaters V 3: Payload V 2 : AOCS V 1 : TM/TC • • 12 • • 1 wire (sensors + actuators) • HK selection • GPIO • Flash memory I/F • Spacewire • DMA UART (GPS / SST) I 2 C PWM GPIO X-Band interface + I 2 C SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA • • • TMR Context management (Fram/Flash) TMR ECC SEM

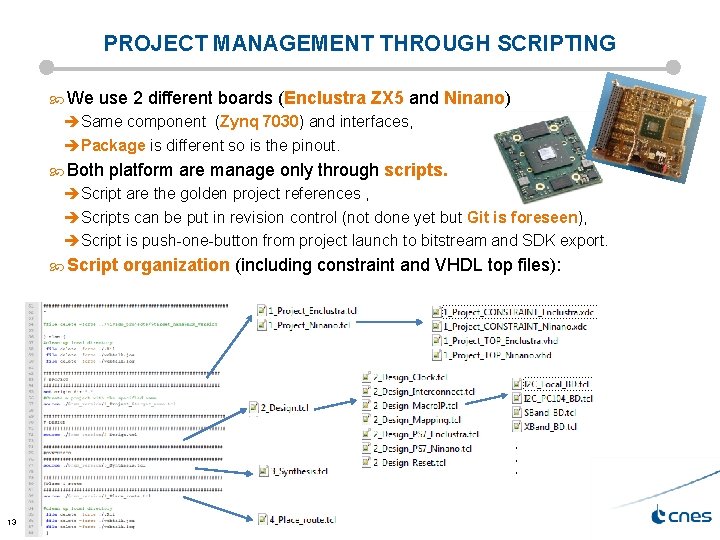

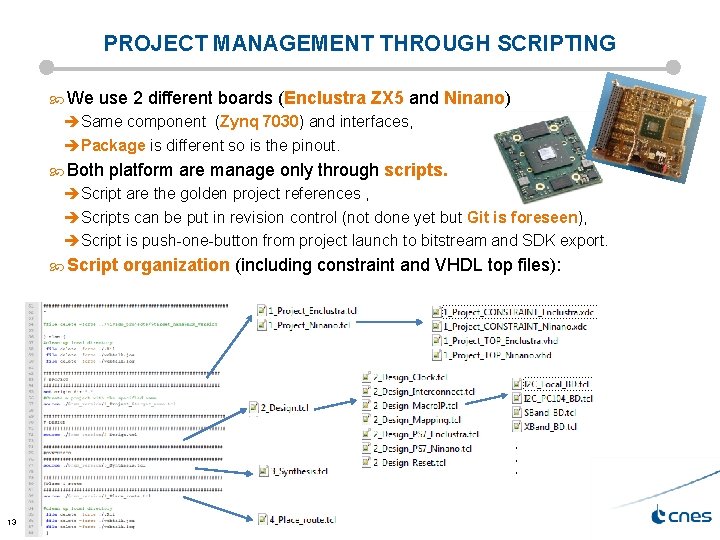

PROJECT MANAGEMENT THROUGH SCRIPTING We use 2 different boards (Enclustra ZX 5 and Ninano) èSame component (Zynq 7030) and interfaces, èPackage is different so is the pinout. Both platform are manage only through scripts. èScript are the golden project references , èScripts can be put in revision control (not done yet but Git is foreseen), èScript is push-one-button from project launch to bitstream and SDK export. Script organization (including constraint and VHDL top files): . . . 13

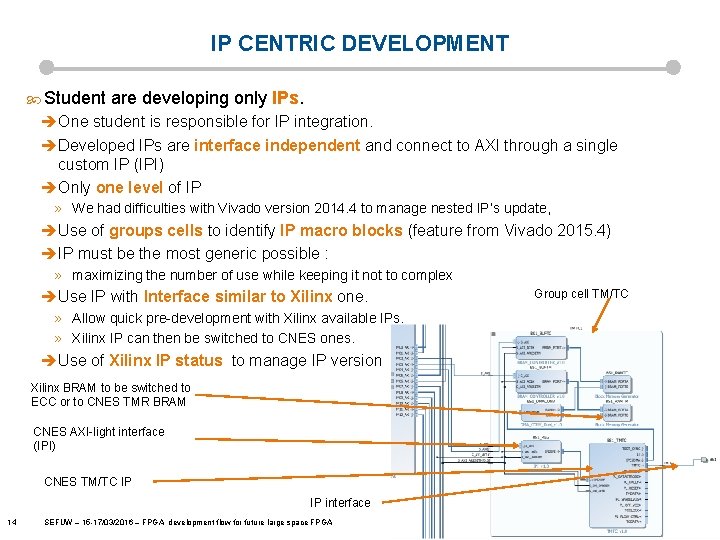

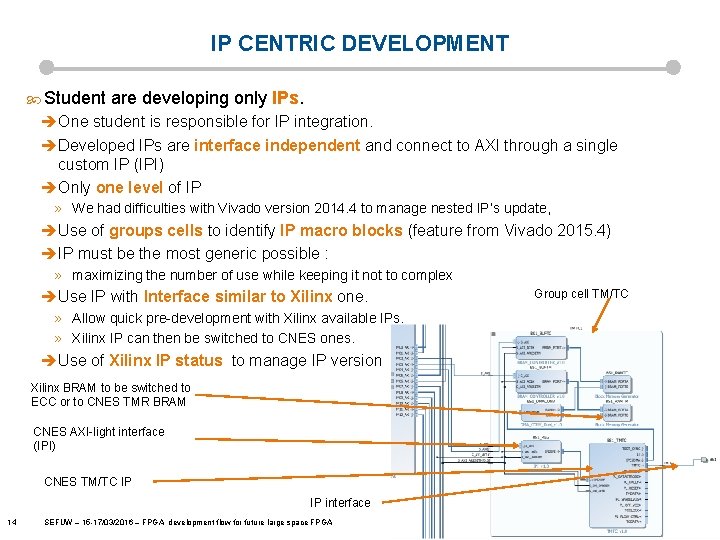

IP CENTRIC DEVELOPMENT Student are developing only IPs. èOne student is responsible for IP integration. èDeveloped IPs are interface independent and connect to AXI through a single custom IP (IPI) èOnly one level of IP » We had difficulties with Vivado version 2014. 4 to manage nested IP’s update, èUse of groups cells to identify IP macro blocks (feature from Vivado 2015. 4) èIP must be the most generic possible : » maximizing the number of use while keeping it not to complex èUse IP with Interface similar to Xilinx one. » Allow quick pre-development with Xilinx available IPs. » Xilinx IP can then be switched to CNES ones. èUse of Xilinx IP status to manage IP version Xilinx BRAM to be switched to ECC or to CNES TMR BRAM CNES AXI-light interface (IPI) CNES TM/TC IP IP interface 14 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA Group cell TM/TC

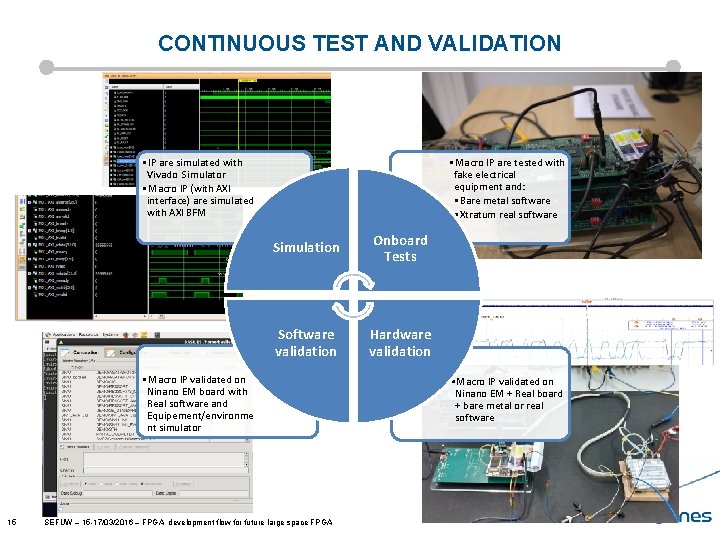

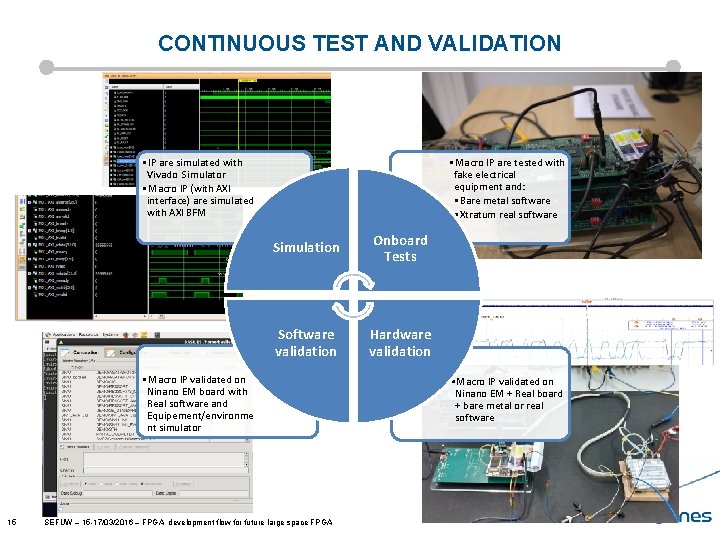

CONTINUOUS TEST AND VALIDATION • IP are simulated with Vivado Simulator • Macro IP (with AXI interface) are simulated with AXI BFM • Macro IP are tested with fake electrical equipment and: • Bare metal software • Xtratum real software Simulation Onboard Tests Software validation Hardware validation • Macro IP validated on Ninano EM board with Real software and Equipement/environme nt simulator 15 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA • Macro IP validated on Ninano EM + Real board + bare metal or real software

INTRODUCTION ZYNQ 7030 : DEVELOPMENT EXAMPLE KEY FEATURE FOR FUTURE DEVELOPMENT FLOW CONCLUSION SOMMAIRE 16 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

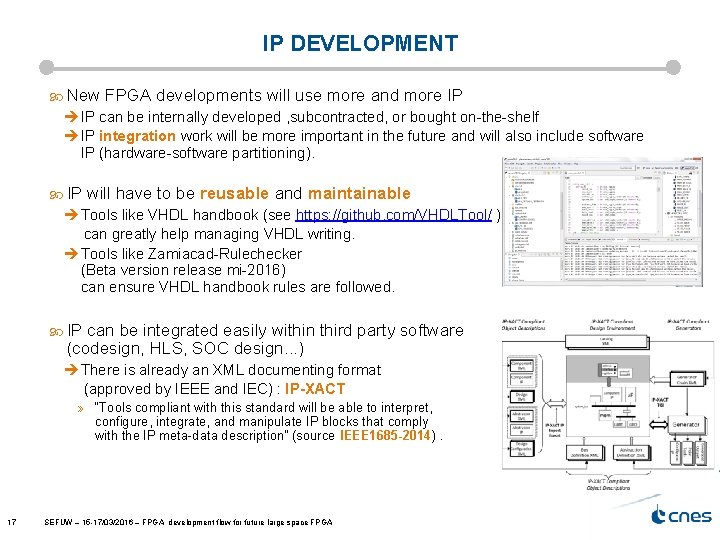

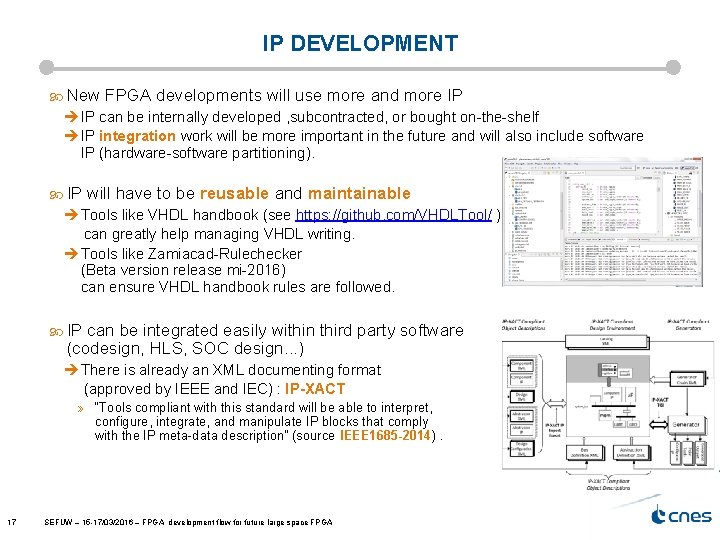

IP DEVELOPMENT New FPGA developments will use more and more IP è IP can be internally developed , subcontracted, or bought on-the-shelf è IP integration work will be more important in the future and will also include software IP (hardware-software partitioning). IP will have to be reusable and maintainable è Tools like VHDL handbook (see https: //github. com/VHDLTool/ ) can greatly help managing VHDL writing. è Tools like Zamiacad-Rulechecker (Beta version release mi-2016) can ensure VHDL handbook rules are followed. IP can be integrated easily within third party software (codesign, HLS, SOC design. . . ) è There is already an XML documenting format (approved by IEEE and IEC) : IP-XACT » “Tools compliant with this standard will be able to interpret, configure, integrate, and manipulate IP blocks that comply with the IP meta-data description” (source IEEE 1685 -2014). 17 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

AGILE DEVELOPMENT FPGA development IP oriented can get benefit from Agile Software development flow’s example: è Continuous improvement can more easily be managed with IP than with whole FPGA. » FPGA IP have boundaries well defined (like Amba bus or address/data/chipselect bus) è Requirements and solutions can change during the development. » For example : FFT IP that change algorithm, command dictionary that add TC. . è Early delivery of partially completed FPGA. » For example: Interface IP to one out of several equipment for interface tests. Continuous development needs many automated tests for: è IP Validation. è Non regression testing after IP upgrade. è IP Integration. Technology like OS-VVM (randomisation) and UVM (verification metodology) can help achieve full validation Continuous development needs version control mechanism è Git or SVN are good candidate 18 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

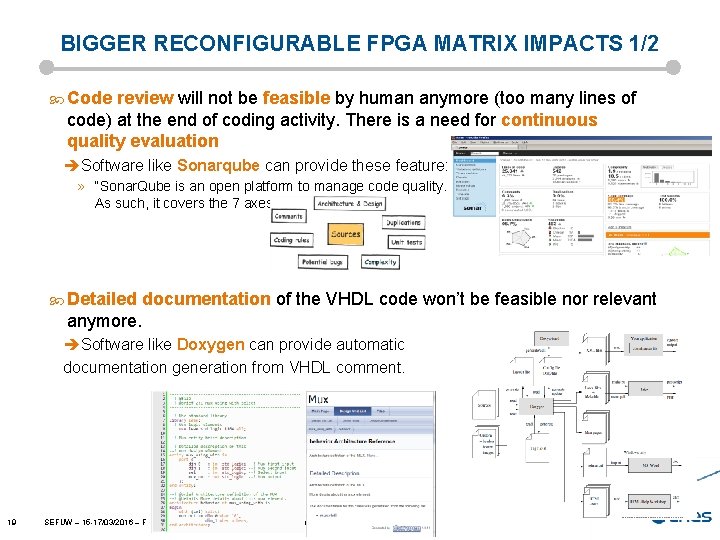

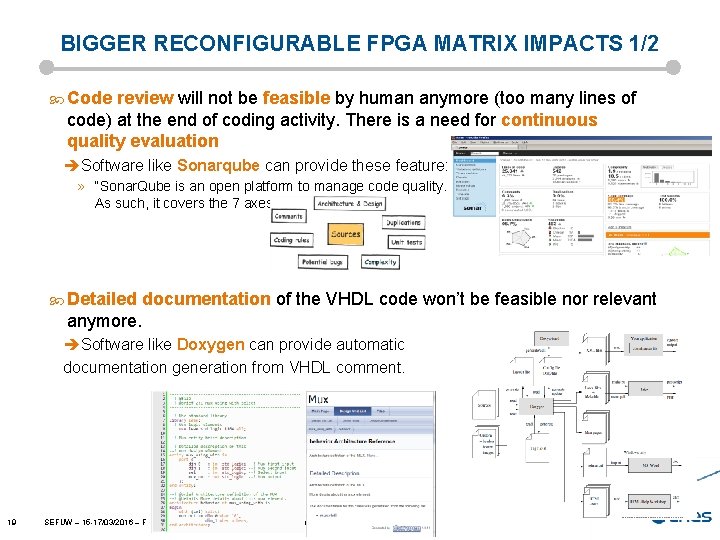

BIGGER RECONFIGURABLE FPGA MATRIX IMPACTS 1/2 Code review will not be feasible by human anymore (too many lines of code) at the end of coding activity. There is a need for continuous quality evaluation èSoftware like Sonarqube can provide these feature: » “Sonar. Qube is an open platform to manage code quality. As such, it covers the 7 axes of code quality”: Detailed documentation of the VHDL code won’t be feasible nor relevant anymore. èSoftware like Doxygen can provide automatic documentation generation from VHDL comment. 19 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

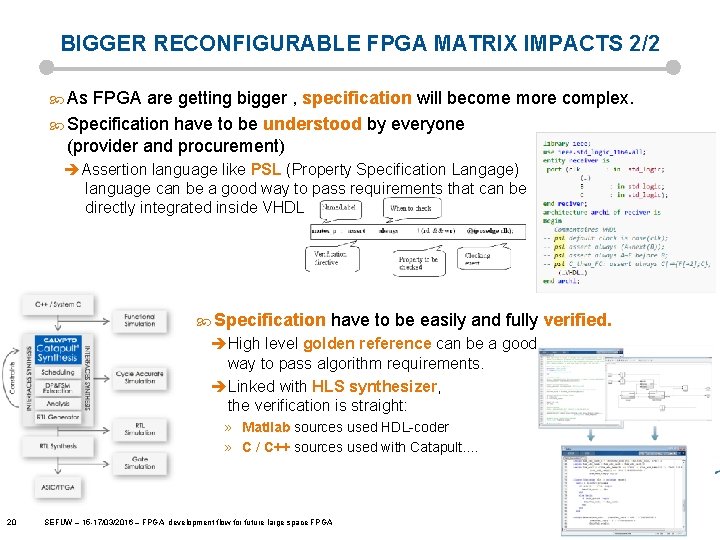

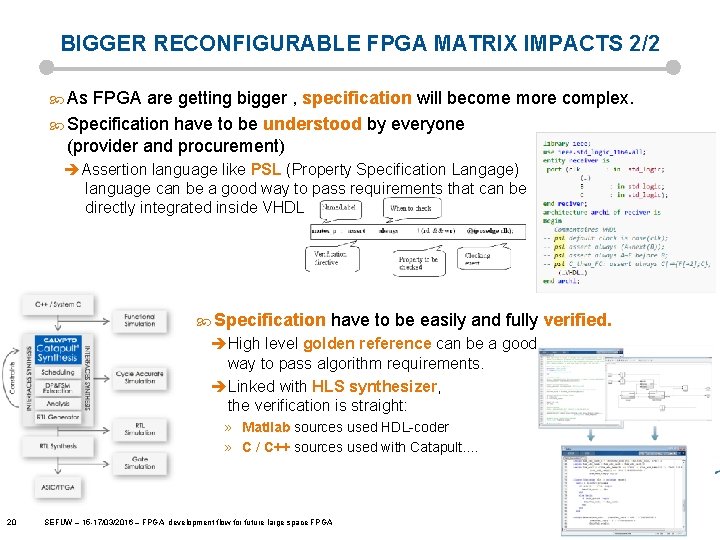

BIGGER RECONFIGURABLE FPGA MATRIX IMPACTS 2/2 As FPGA are getting bigger , specification will become more complex. Specification have to be understood by everyone (provider and procurement) èAssertion language like PSL (Property Specification Langage) language can be a good way to pass requirements that can be directly integrated inside VHDL. Specification have to be easily and fully verified. èHigh level golden reference can be a good way to pass algorithm requirements. èLinked with HLS synthesizer, the verification is straight: » Matllab sources used HDL-coder » C / C++ sources used with Catapult. . 20 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

INTRODUCTION ZYNQ 7030 : DEVELOPMENT EXAMPLE KEY FEATURE FOR FUTURE DEVELOPMENT FLOW CONCLUSION SOMMAIRE 21 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

CONCLUSION Space ones FPGA will move from smaller OTP device to bigger reprogrammable è Reprogrammability will change the design flow from a linear one to incremental one thus leading to more complex match with ECSS original FPGA flow. è Bigger devices will push to include more and more IPs (Interfaces, processors. . . ) or use automatic code generation tools. With bigger reprogrammable FPGA for space, a new activity will arise : FPGA integrator FPGA will include more and more functions in the future. è What was previously on a whole PCB will fit inside an unique FPGA. è FPGA reviews can no longer be grouped with equipment reviews Standards like ECSS-Q-ST-60 -02 C ensure that “space projects meet their requirements in terms of functionality, quality, reliability, schedule and cost” soon this standard will not be enough for next generation of FPGAs. 22 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA

Thanks for your attention Any question? ©CNES-mars 2002/Illus. D. Ducros – SPOT from 1, 2, 4 and 5 - 30 th birthday February 2016 03/11/2020 23

GETTING IN TOUCH CNES free software : https: //logiciels. cnes. fr/content/vhdltool? language=en VHDLTool Github: https: //github. com/VHDLTool/ Standard rules Github: https: //github. com/VHDLTool/VHDL_Handbook_STD CNES custom rules Github https: //github. com/VHDLTool/VHDL_Handbook_CNE Toolchain (handbook XML to PDF) Github: https: //github. com/VHDLTool/VHDL_Handbook_Toolchain Zamiacad eclipse plugin http: //zamiacad. sourceforge. net/web/ 24 SEFUW – 15 -17/03/2016 – FPGA development flow for future large space FPGA