CPLD FPGA CIRCUITS LOGIQUES PROGRAMMABLES PAL EPLD FPGA

CPLD FPGA CIRCUITS LOGIQUES PROGRAMMABLES PAL EPLD FPGA 28/09/2000 1

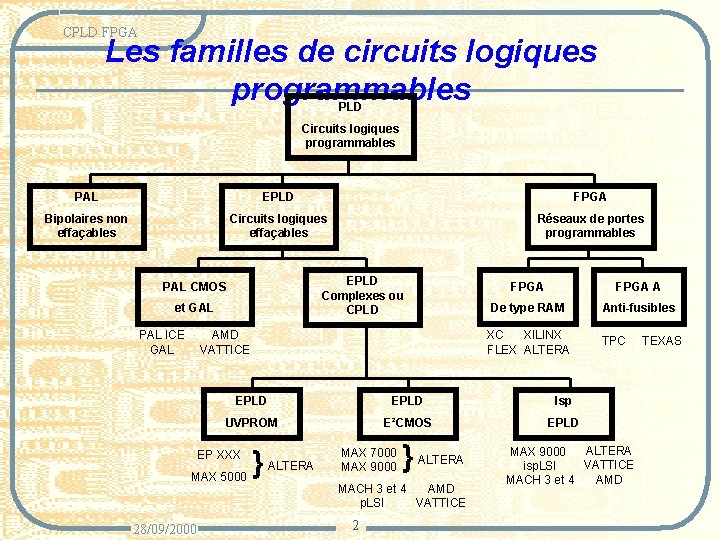

CPLD FPGA Les familles de circuits logiques programmables PLD Circuits logiques programmables PAL EPLD FPGA Bipolaires non effaçables Circuits logiques effaçables Réseaux de portes programmables EPLD Complexes ou CPLD PAL CMOS et GAL PAL ICE GAL AMD VATTICE FPGA A De type RAM Anti-fusibles XC XILINX FLEX ALTERA EPLD Isp UVPROM E²CMOS EPLD EP XXX MAX 5000 28/09/2000 FPGA } ALTERA MAX 7000 MAX 9000 } ALTERA AMD MACH 3 et 4 VATTICE p. LSI 2 TPC ALTERA MAX 9000 VATTICE isp. LSI AMD MACH 3 et 4 TEXAS

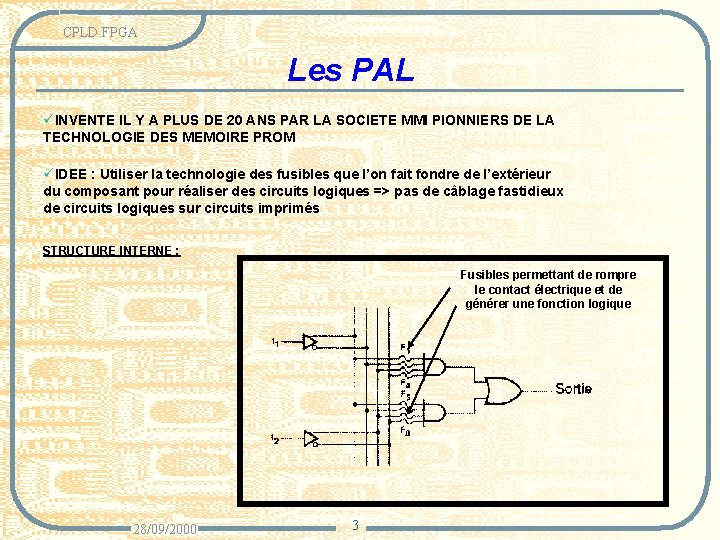

CPLD FPGA Les PAL üINVENTE IL Y A PLUS DE 20 ANS PAR LA SOCIETE MMI PIONNIERS DE LA TECHNOLOGIE DES MEMOIRE PROM üIDEE : Utiliser la technologie des fusibles que l’on fait fondre de l’extérieur du composant pour réaliser des circuits logiques => pas de câblage fastidieux de circuits logiques sur circuits imprimés STRUCTURE INTERNE : Fusibles permettant de rompre le contact électrique et de générer une fonction logique 28/09/2000 3

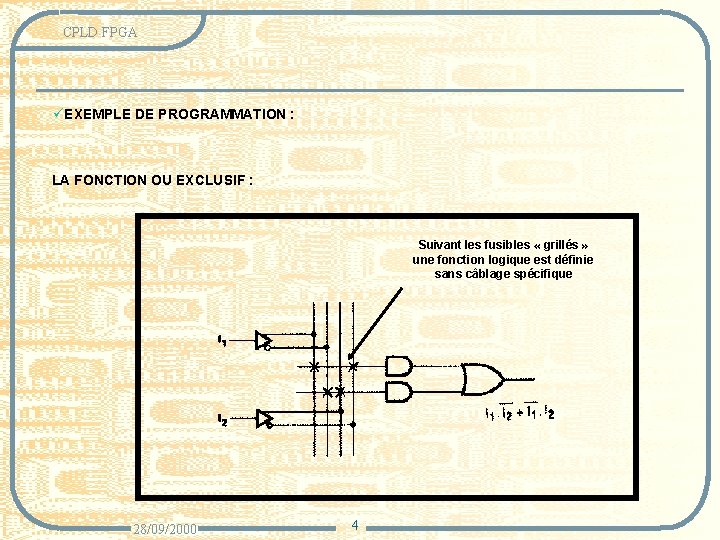

CPLD FPGA üEXEMPLE DE PROGRAMMATION : LA FONCTION OU EXCLUSIF : Suivant les fusibles « grillés » une fonction logique est définie sans câblage spécifique 28/09/2000 4

CPLD FPGA F LA LOGIQUE : SYSTEME ELECTRONIQUE (COMPLEXE) FONCTIONNEL BESOIN DEFINITION D’UNE STRUCTURE LOGIQUE GENERATION DE FONCTIONS LOGIQUES COMPLEXES PROGRAMMATEUR SPECIFIQUE (OU système à µP) COMPOSANT PROGRAMMABLE POSSEDANT UNE STRUCTURE DE BASE ü EST UTILISEE POUR PERMETTRE DE GENERER DES SYSTEMES ELECTRONIQUES COMPLEXES 28/09/2000 5

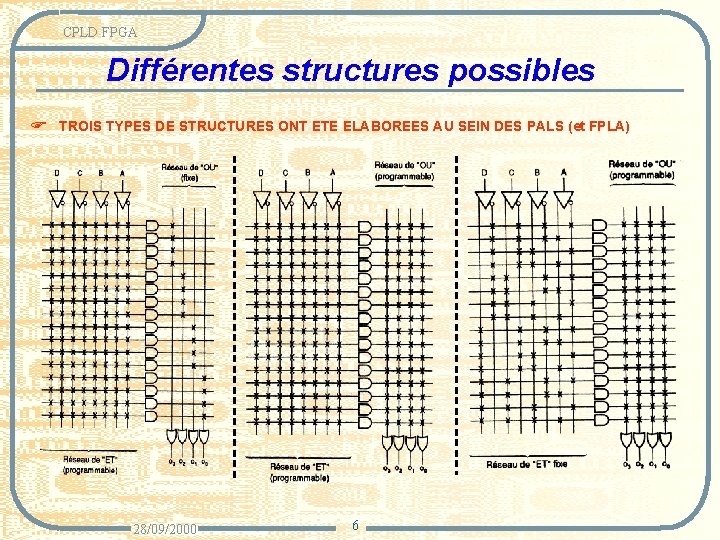

CPLD FPGA Différentes structures possibles F TROIS TYPES DE STRUCTURES ONT ETE ELABOREES AU SEIN DES PALS (et FPLA) 28/09/2000 6

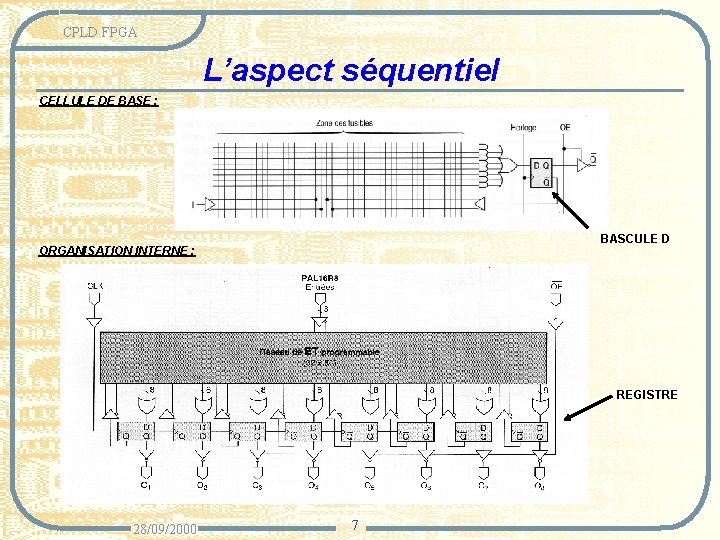

CPLD FPGA L’aspect séquentiel CELLULE DE BASE : BASCULE D ORGANISATION INTERNE : REGISTRE 28/09/2000 7

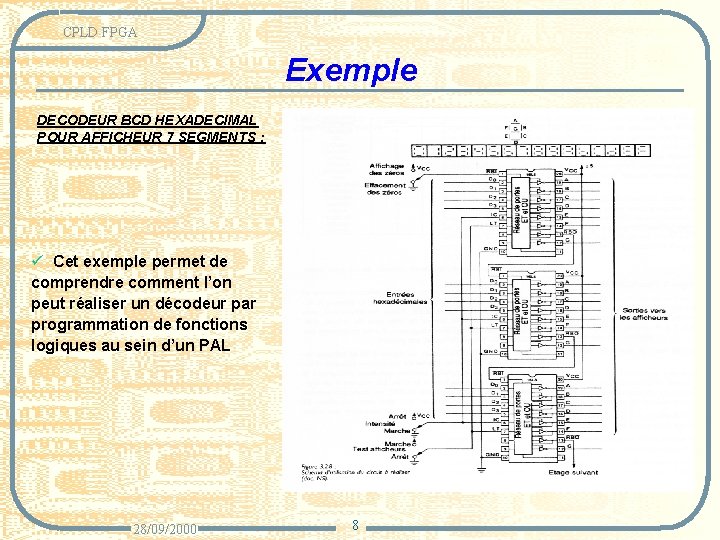

CPLD FPGA Exemple DECODEUR BCD HEXADECIMAL POUR AFFICHEUR 7 SEGMENTS : ü Cet exemple permet de comprendre comment l’on peut réaliser un décodeur par programmation de fonctions logiques au sein d’un PAL 28/09/2000 8

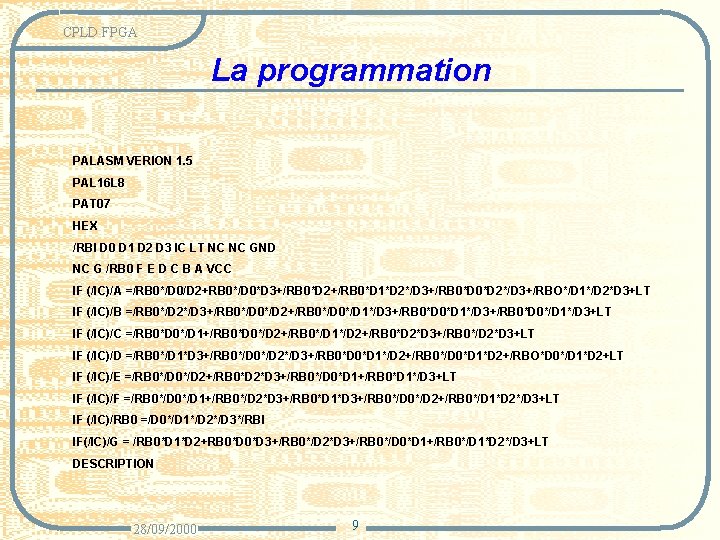

CPLD FPGA La programmation PALASM VERION 1. 5 PAL 16 L 8 PAT 07 HEX /RBI D 0 D 1 D 2 D 3 IC LT NC NC GND NC G /RB 0 F E D C B A VCC IF (/IC)/A =/RB 0*/D 0/D 2+RB 0*/D 0*D 3+/RB 0*D 2+/RB 0*D 1*D 2*/D 3+/RB 0*D 2*/D 3+/RBO*/D 1*/D 2*D 3+LT IF (/IC)/B =/RB 0*/D 2*/D 3+/RB 0*/D 2+/RB 0*/D 1*/D 3+/RB 0*D 0*/D 1*/D 3+LT IF (/IC)/C =/RB 0*D 0*/D 1+/RB 0*D 0*/D 2+/RB 0*/D 1*/D 2+/RB 0*D 2*D 3+/RB 0*/D 2*D 3+LT IF (/IC)/D =/RB 0*/D 1*D 3+/RB 0*/D 2*/D 3+/RB 0*D 1*/D 2+/RB 0*/D 0*D 1*D 2+/RBO*D 0*/D 1*D 2+LT IF (/IC)/E =/RB 0*/D 2+/RB 0*D 2*D 3+/RB 0*/D 0*D 1+/RB 0*D 1*/D 3+LT IF (/IC)/F =/RB 0*/D 1+/RB 0*/D 2*D 3+/RB 0*D 1*D 3+/RB 0*/D 2+/RB 0*/D 1*D 2*/D 3+LT IF (/IC)/RB 0 =/D 0*/D 1*/D 2*/D 3*/RBI IF(/IC)/G = /RB 0*D 1*D 2+RB 0*D 3+/RB 0*/D 2*D 3+/RB 0*/D 0*D 1+/RB 0*/D 1*D 2*/D 3+LT DESCRIPTION 28/09/2000 9

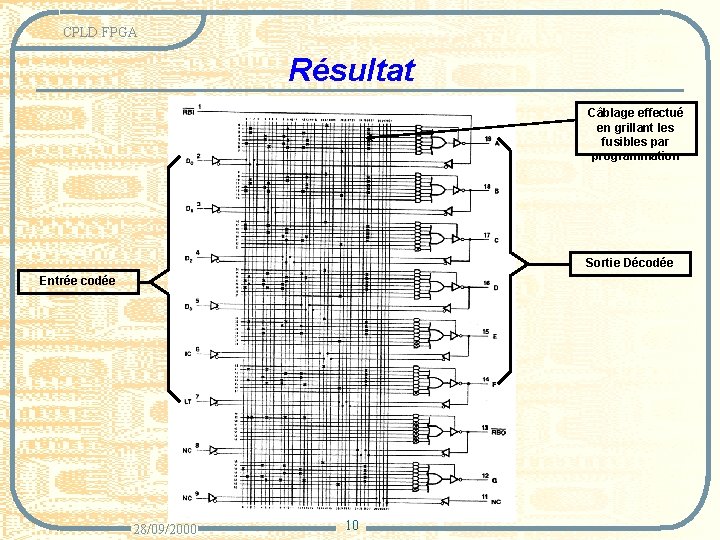

CPLD FPGA Résultat Câblage effectué en grillant les fusibles par programmation Sortie Décodée Entrée codée 28/09/2000 10

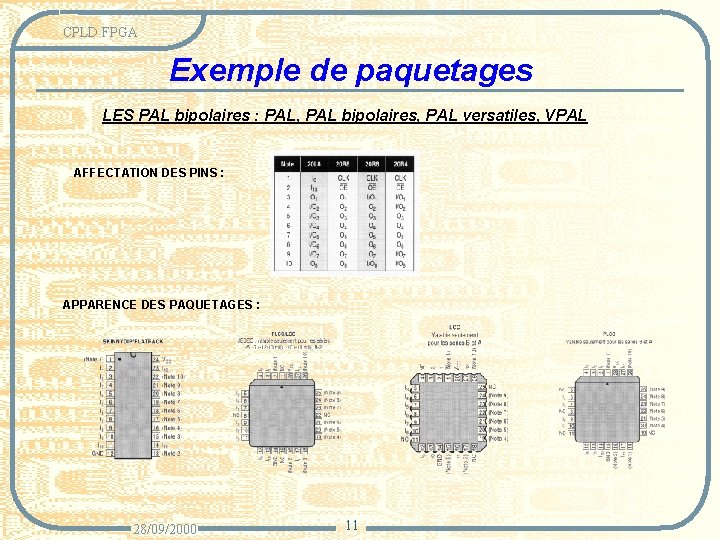

CPLD FPGA Exemple de paquetages LES PAL bipolaires : PAL, PAL bipolaires, PAL versatiles, VPAL AFFECTATION DES PINS : APPARENCE DES PAQUETAGES : 28/09/2000 11

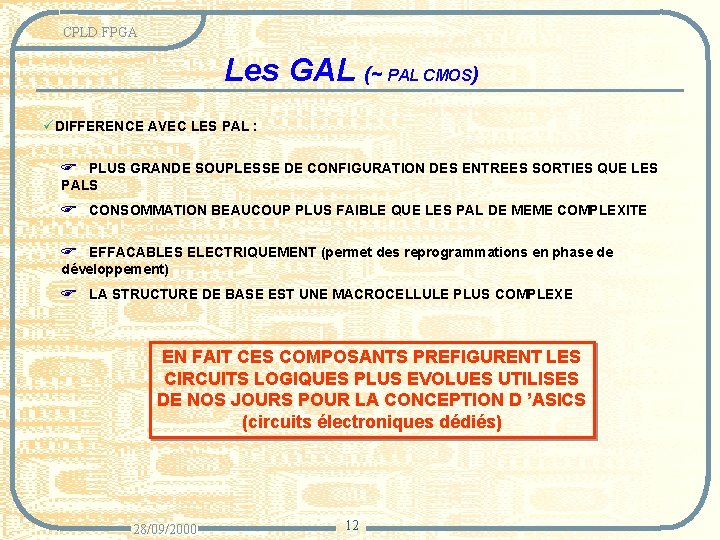

CPLD FPGA Les GAL (~ PAL CMOS) üDIFFERENCE AVEC LES PAL : F PLUS GRANDE SOUPLESSE DE CONFIGURATION DES ENTREES SORTIES QUE LES PALS F CONSOMMATION BEAUCOUP PLUS FAIBLE QUE LES PAL DE MEME COMPLEXITE F EFFACABLES ELECTRIQUEMENT (permet des reprogrammations en phase de développement) F LA STRUCTURE DE BASE EST UNE MACROCELLULE PLUS COMPLEXE EN FAIT CES COMPOSANTS PREFIGURENT LES CIRCUITS LOGIQUES PLUS EVOLUES UTILISES DE NOS JOURS POUR LA CONCEPTION D ’ASICS (circuits électroniques dédiés) 28/09/2000 12

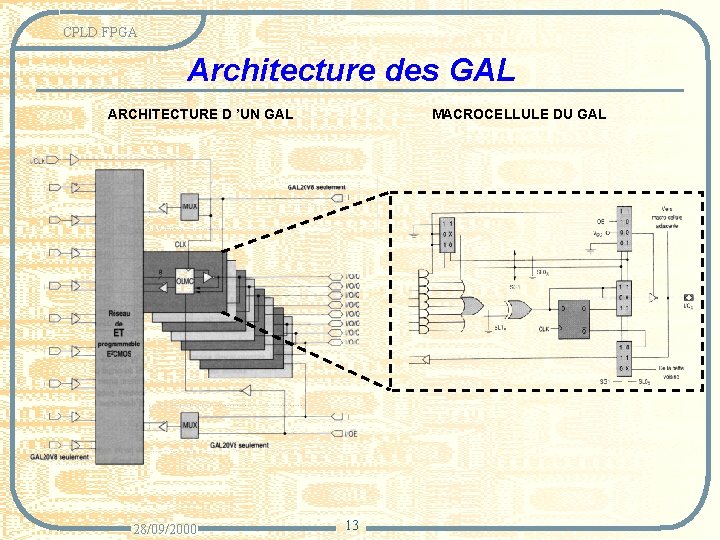

CPLD FPGA Architecture des GAL ARCHITECTURE D ’UN GAL 28/09/2000 MACROCELLULE DU GAL 13

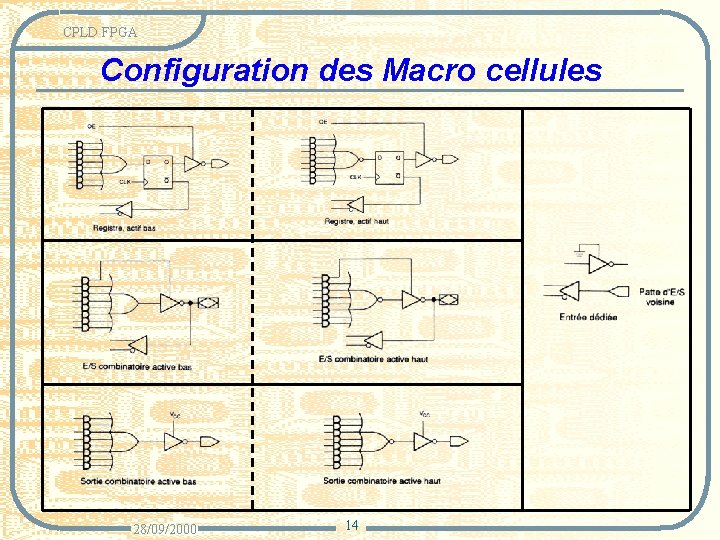

CPLD FPGA Configuration des Macro cellules 28/09/2000 14

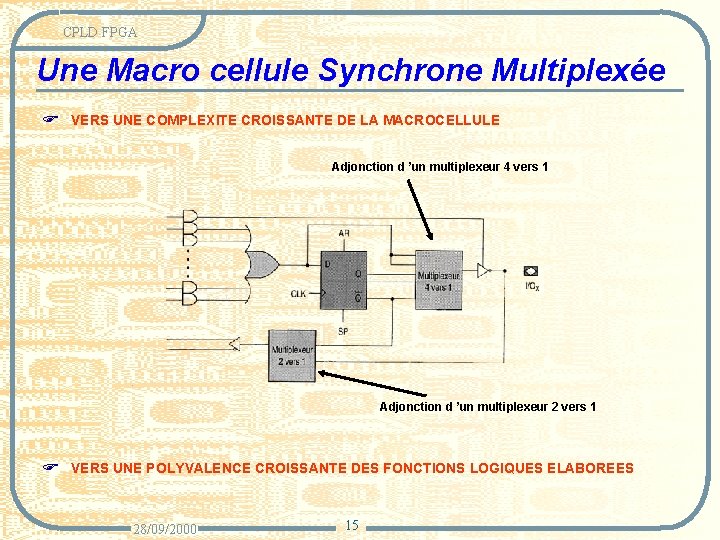

CPLD FPGA Une Macro cellule Synchrone Multiplexée F VERS UNE COMPLEXITE CROISSANTE DE LA MACROCELLULE Adjonction d ’un multiplexeur 4 vers 1 Adjonction d ’un multiplexeur 2 vers 1 F VERS UNE POLYVALENCE CROISSANTE DES FONCTIONS LOGIQUES ELABOREES 28/09/2000 15

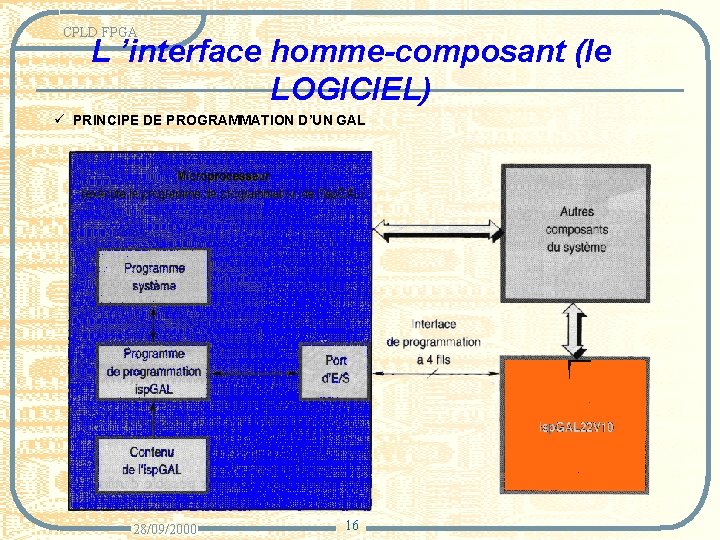

CPLD FPGA L ’interface homme-composant (le LOGICIEL) ü PRINCIPE DE PROGRAMMATION D’UN GAL 28/09/2000 16

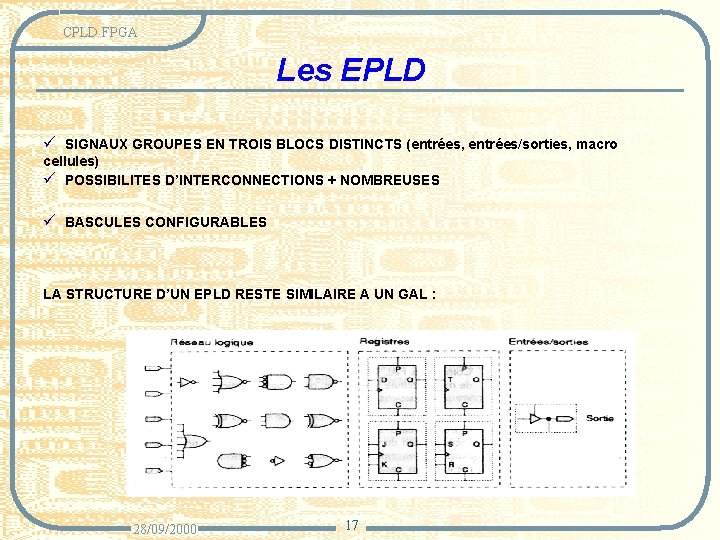

CPLD FPGA Les EPLD ü SIGNAUX GROUPES EN TROIS BLOCS DISTINCTS (entrées, entrées/sorties, macro cellules) ü POSSIBILITES D’INTERCONNECTIONS + NOMBREUSES ü BASCULES CONFIGURABLES LA STRUCTURE D’UN EPLD RESTE SIMILAIRE A UN GAL : 28/09/2000 17

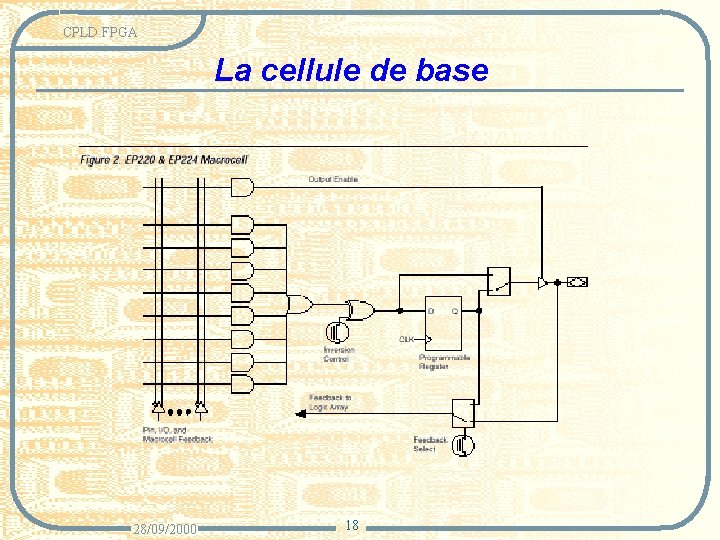

CPLD FPGA La cellule de base 28/09/2000 18

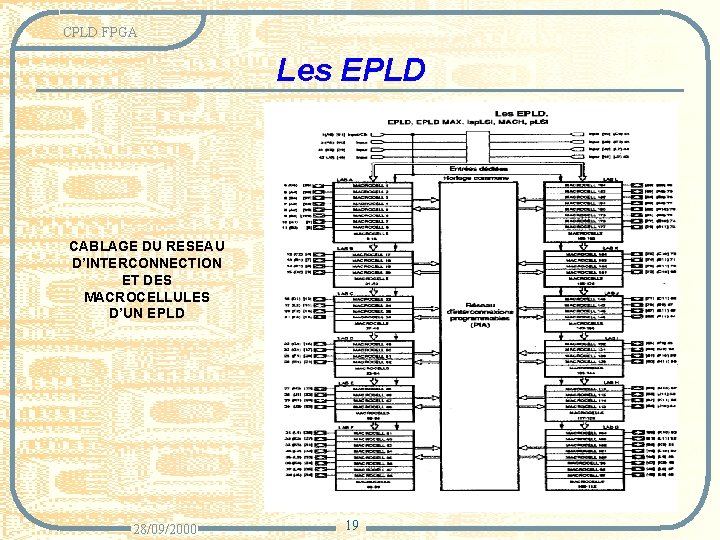

CPLD FPGA Les EPLD CABLAGE DU RESEAU D’INTERCONNECTION ET DES MACROCELLULES D’UN EPLD 28/09/2000 19

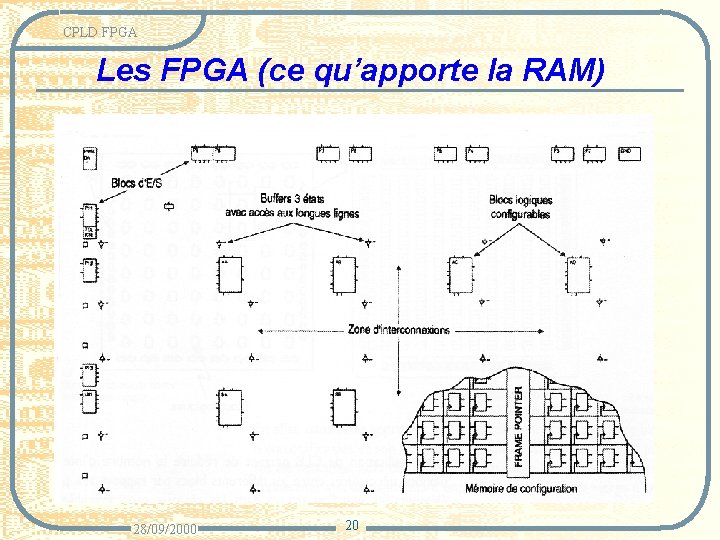

CPLD FPGA Les FPGA (ce qu’apporte la RAM) 28/09/2000 20

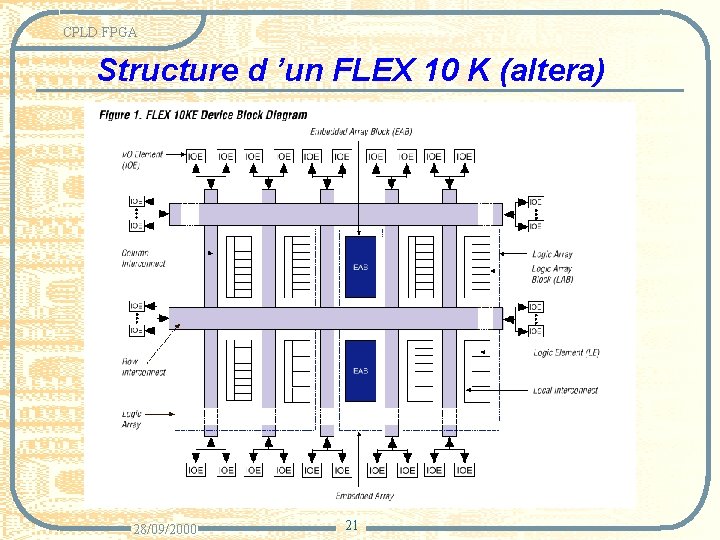

CPLD FPGA Structure d ’un FLEX 10 K (altera) 28/09/2000 21

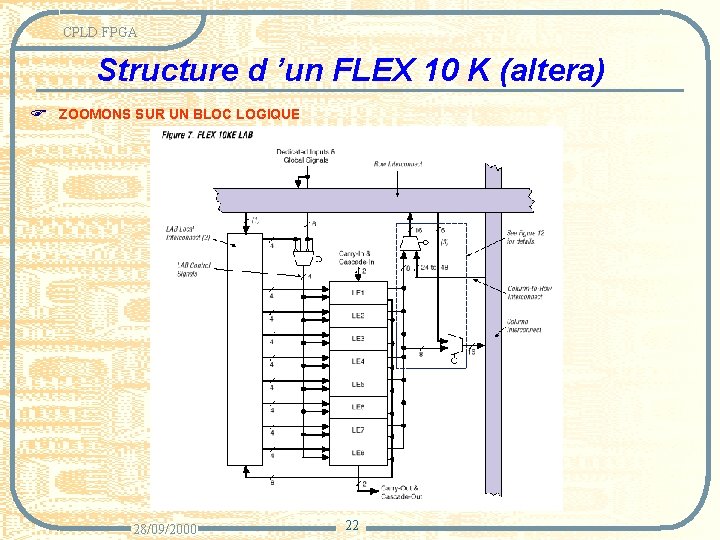

CPLD FPGA Structure d ’un FLEX 10 K (altera) F ZOOMONS SUR UN BLOC LOGIQUE 28/09/2000 22

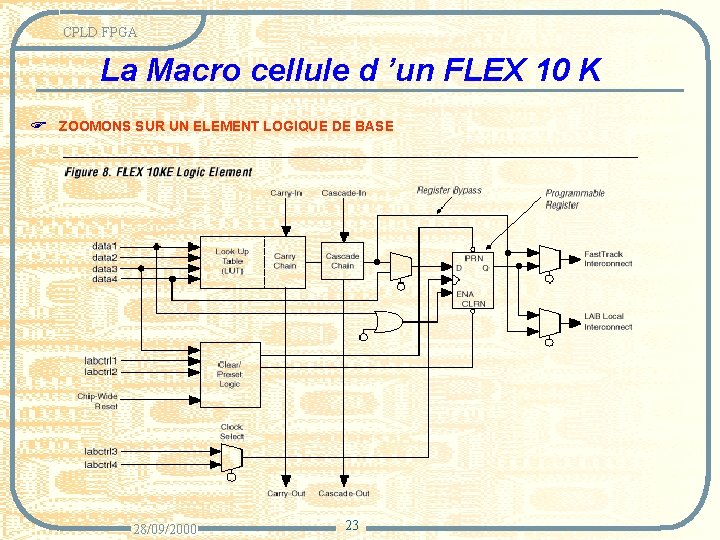

CPLD FPGA La Macro cellule d ’un FLEX 10 K F ZOOMONS SUR UN ELEMENT LOGIQUE DE BASE 28/09/2000 23

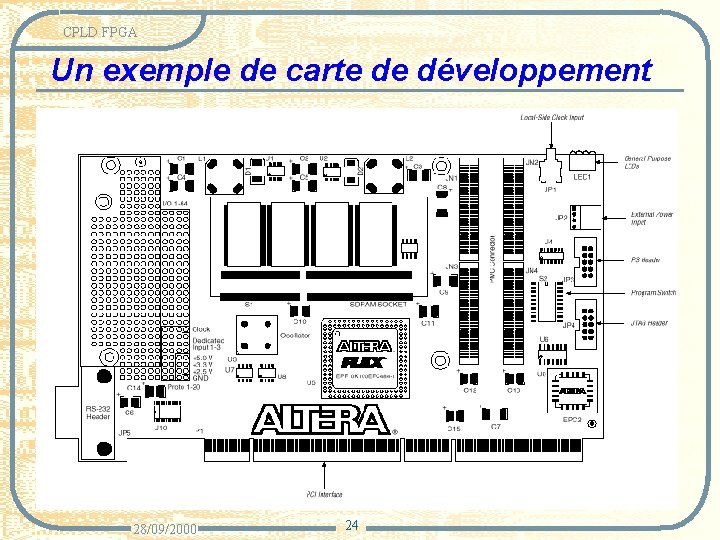

CPLD FPGA Un exemple de carte de développement 28/09/2000 24

CPLD FPGA Quelquestions légitimes ü QUEL EST L’INTERET DE CES COMPOSANTS PROGRAMMABLES EN ELECTRONIQUE ? ü QU ’APPORTENT-ILS DE PLUS QUE LES SYSTEMES DE PORTES LOGIQUES C BLES SUR CIRCUITS IMPRIMES? ü QU ’EST CE QUE LA SIMULATION LOGIQUE ET EN QUOI A-T-ELLLE UN RAPPORT AVEC CES COMPOSANTS? ü QU ’EST CE QUE LA SYNTHESE LOGIQUE ET EN QUOI CES COMPOSANTS NOUS PERMETTENT-ILS DE DEFINIR DE NOUVEAUX COMPOSANTS DEDIES? ü AVEZ-VOUS ENTENDU PARLER DE LANGUAGES DE MODELISATION (VHDL, VERILOG, TNSS) ? F NOUS ALLONS ESSAYER DE REPONDRE A CES QUESTIONS AU TRAVERS D ’UN EXEMPLE CONCRET ET LIBERATEUR …… LA MACHINE A LAVER ! 28/09/2000 25

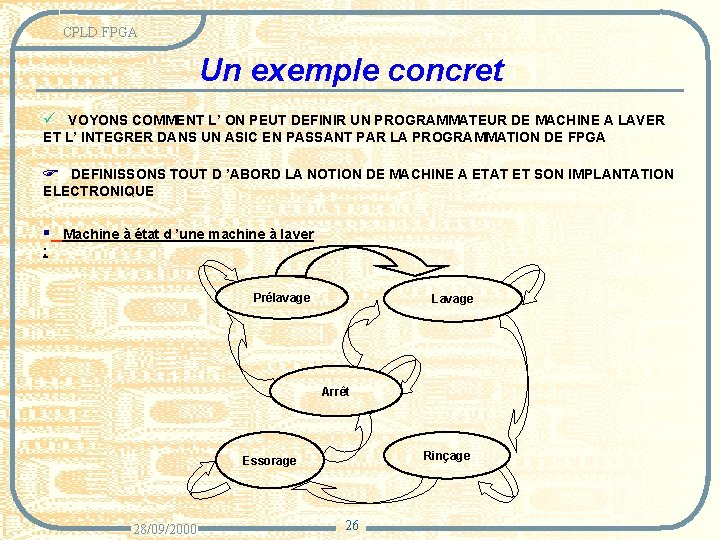

CPLD FPGA Un exemple concret ü VOYONS COMMENT L’ ON PEUT DEFINIR UN PROGRAMMATEUR DE MACHINE A LAVER ET L’ INTEGRER DANS UN ASIC EN PASSANT PAR LA PROGRAMMATION DE FPGA F DEFINISSONS TOUT D ’ABORD LA NOTION DE MACHINE A ETAT ET SON IMPLANTATION ELECTRONIQUE § Machine à état d ’une machine à laver : Prélavage Lavage Arrêt Rinçage Essorage 28/09/2000 26

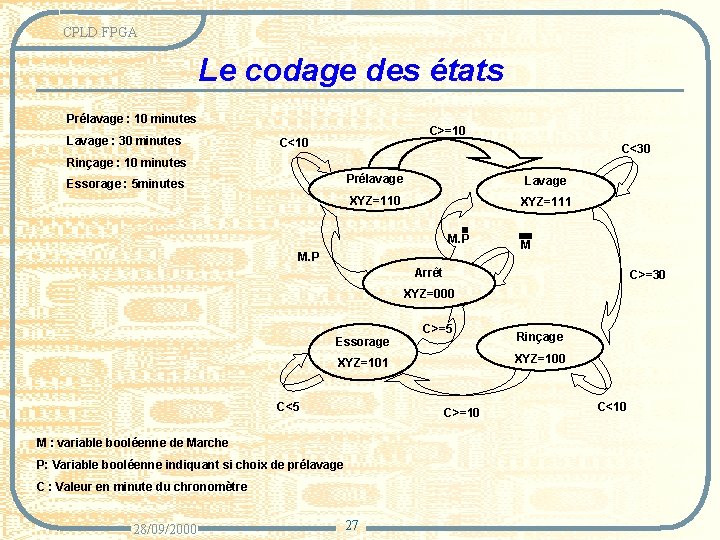

CPLD FPGA Le codage des états Prélavage : 10 minutes Lavage : 30 minutes C>=10 C<30 Rinçage : 10 minutes Essorage : 5 minutes Prélavage Lavage XYZ=110 XYZ=111 M. P M Arrêt C>=30 XYZ=000 Essorage C>=5 XYZ=100 XYZ=101 C<5 C>=10 M : variable booléenne de Marche P: Variable booléenne indiquant si choix de prélavage C : Valeur en minute du chronomètre 28/09/2000 27 Rinçage C<10

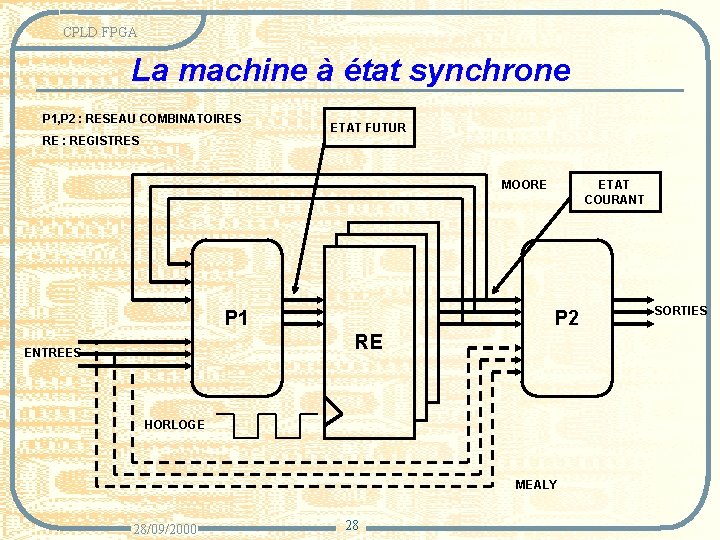

CPLD FPGA La machine à état synchrone P 1, P 2 : RESEAU COMBINATOIRES RE : REGISTRES ETAT FUTUR ETAT COURANT MOORE P 1 P 2 RE ENTREES HORLOGE MEALY 28/09/2000 28 SORTIES

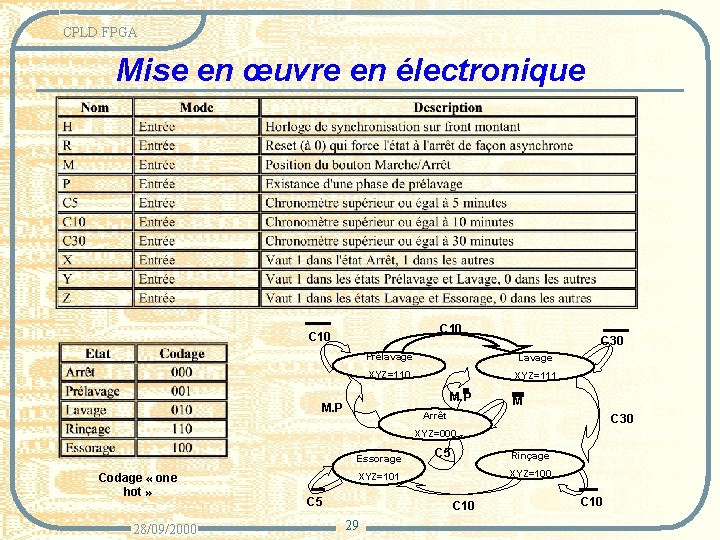

CPLD FPGA Mise en œuvre en électronique C 10 C 30 Prélavage Lavage XYZ=110 XYZ=111 M. P M Arrêt C 30 XYZ=000 Essorage Codage « one hot » 28/09/2000 C 5 Rinçage XYZ=100 XYZ=101 C 5 C 10 29 C 10

CPLD FPGA La définition des combinaisons logiques F DEFINITION DES TABLEAUX DE KARNAUGH F SIMPLIFICATION DE L’EXPRESSION LOGIQUE F DEFINITION DU CABLAGE DES PORTES LOGIQUES F RECHERCHE D’UNE SOLUTION ADAPTEE EN ELECTRONIQUE AU COURS DE CETTE DEMARCHE NOUS VERRONS COMMENT L’ON PEUT UTILISER LES PAL, GAL, EPLD, ET FPGA POUR MODELISER CETTE MACHINE A ETAT 28/09/2000 30

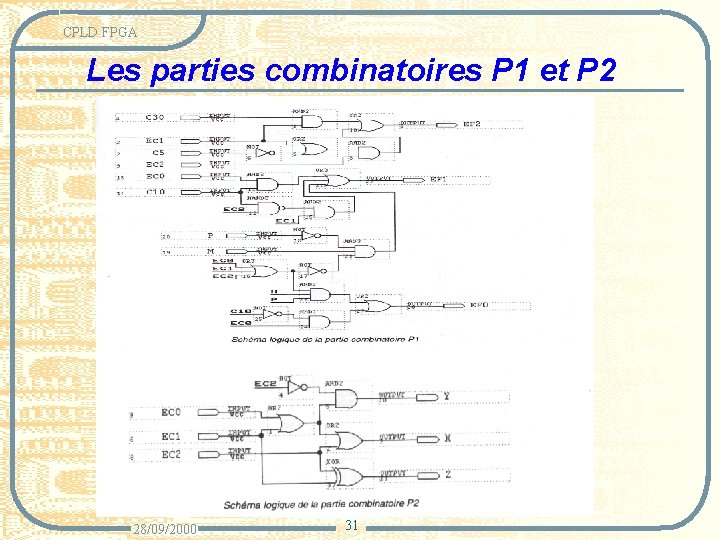

CPLD FPGA Les parties combinatoires P 1 et P 2 28/09/2000 31

CPLD FPGA FDEUX CHOIX S’IMPOSENT ALORS : üREALISER UN CIRCUIT IMPRIME SUR LEQUEL SERAIENT CABLES DES CIRCUITS CONTENANT DES FONCTIONS ELEMENTAIRES 74 LSXX (UN PEU DE SERIEUX) üUTILISER DES RESSOURCES DE L’ELECTRONIQUE NUMERIQUE MODERNE POUR ABOUTIR A UN COMPOSANT DE PETITE TAILLE GERANT PARFAITEMENT LE CYCLE DE LAVAGE D’UNE MACHINE A LAVER PROGRAMMATION D’EPLD et d’FPGA SYNTHETISER COMMERCIALISER UN ASIC DEDIE A CETTE APPLICATION 28/09/2000 32

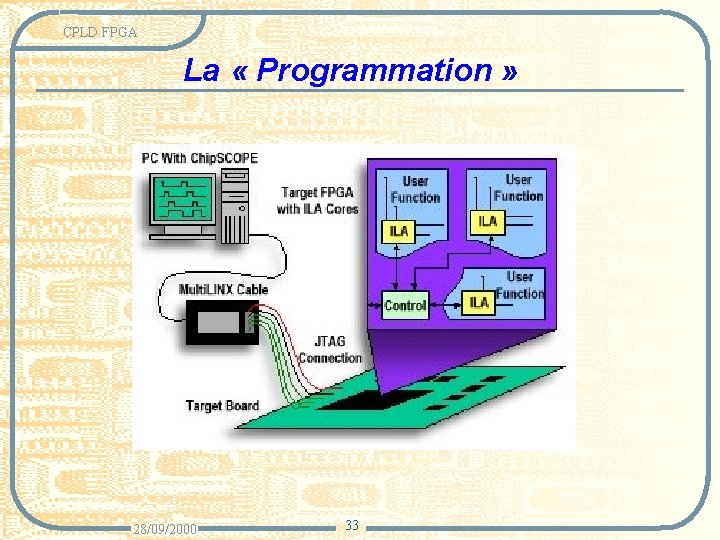

CPLD FPGA La « Programmation » 28/09/2000 33

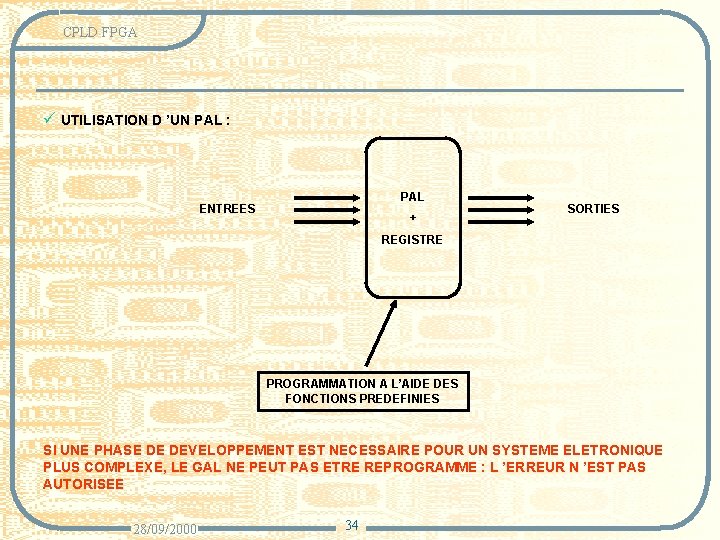

CPLD FPGA ü UTILISATION D ’UN PAL : PAL ENTREES + SORTIES REGISTRE PROGRAMMATION A L’AIDE DES FONCTIONS PREDEFINIES SI UNE PHASE DE DEVELOPPEMENT EST NECESSAIRE POUR UN SYSTEME ELETRONIQUE PLUS COMPLEXE, LE GAL NE PEUT PAS ETRE REPROGRAMME : L ’ERREUR N ’EST PAS AUTORISEE 28/09/2000 34

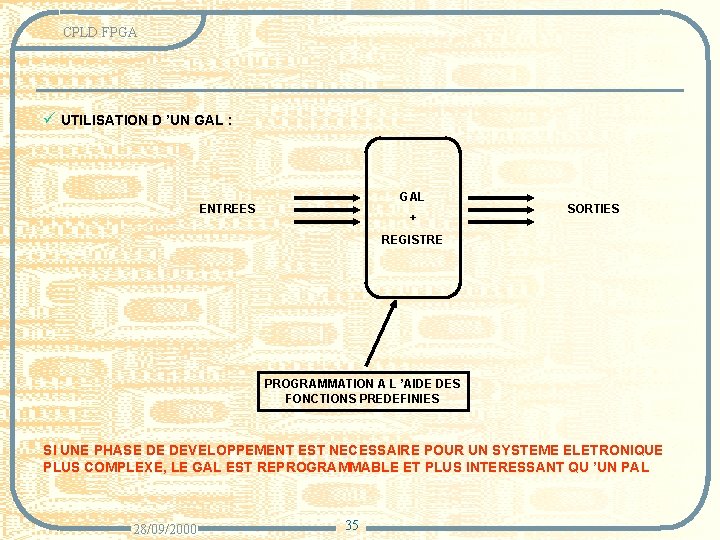

CPLD FPGA ü UTILISATION D ’UN GAL : GAL ENTREES + SORTIES REGISTRE PROGRAMMATION A L ’AIDE DES FONCTIONS PREDEFINIES SI UNE PHASE DE DEVELOPPEMENT EST NECESSAIRE POUR UN SYSTEME ELETRONIQUE PLUS COMPLEXE, LE GAL EST REPROGRAMMABLE ET PLUS INTERESSANT QU ’UN PAL 28/09/2000 35

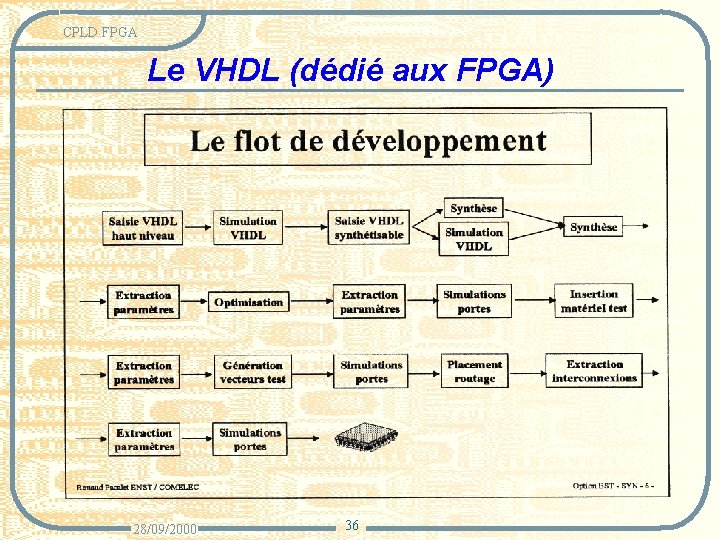

CPLD FPGA Le VHDL (dédié aux FPGA) 28/09/2000 36

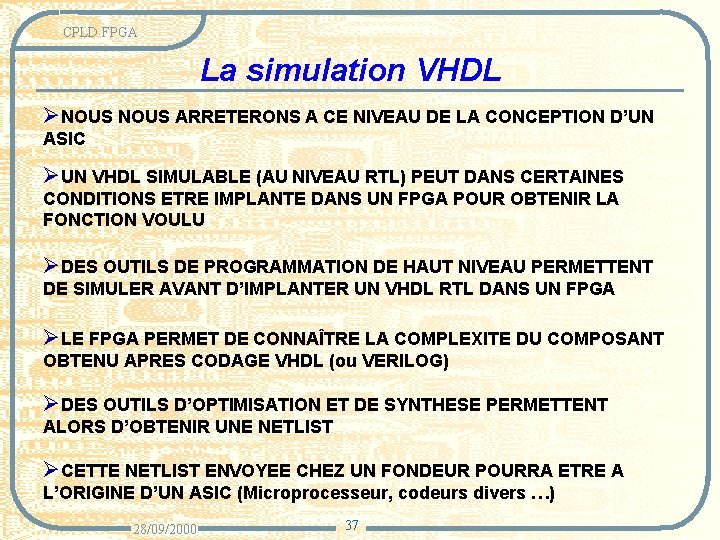

CPLD FPGA La simulation VHDL ØNOUS ARRETERONS A CE NIVEAU DE LA CONCEPTION D’UN ASIC ØUN VHDL SIMULABLE (AU NIVEAU RTL) PEUT DANS CERTAINES CONDITIONS ETRE IMPLANTE DANS UN FPGA POUR OBTENIR LA FONCTION VOULU ØDES OUTILS DE PROGRAMMATION DE HAUT NIVEAU PERMETTENT DE SIMULER AVANT D’IMPLANTER UN VHDL RTL DANS UN FPGA ØLE FPGA PERMET DE CONNAÎTRE LA COMPLEXITE DU COMPOSANT OBTENU APRES CODAGE VHDL (ou VERILOG) ØDES OUTILS D’OPTIMISATION ET DE SYNTHESE PERMETTENT ALORS D’OBTENIR UNE NETLIST ØCETTE NETLIST ENVOYEE CHEZ UN FONDEUR POURRA ETRE A L’ORIGINE D’UN ASIC (Microprocesseur, codeurs divers …) 28/09/2000 37

CPLD FPGA Conclusion §REGARDEZ BIEN CET ECRAN C’EST UN FLOT DE CONCEPTION SIMILLAIRE QUI A PERMIS DE CRÉER TOUS LES COMPOSANTS (ou presque) QUI VOUS PERMETTENT DE SUIVRE CET EXPOSE. §ET CECI GRACE A UNE MACHINE NUMERIQUE SI COMPLEXE QU’IL EST IMPOSSIBLE DE CONNAÎTRE SON NOMBRE D’ETAT POSSIBLE ET LE NOMBRE EXACTE DE TRANSISTORS QUI SE COMMUTTENT ACTUELLEMENT POUR VOUS AFFICHER DE BEAUX PIXELS. 28/09/2000 38

CPLD FPGA Bibliographie q. CIRCUITS LOGIQUES PROGRAMMABLES aux éditions DUNOD par CHRISTIAN TAVERNIER q. ELECTRONIQUE NUMERIQUE INTEGREE dominante COMELEC ENST q. TECHNOLOGIES ET PERFORMANCE DES SYSTEMES INTEGRES dominante COMELEC ENST q. VHDL INTRODUCTION A LA SYNTHESE LOGIQUE aux éditions EYROLLES par PHILIPPE LARCHER q. SYNTHESE, du VHDL au CIRCUIT option EST ENST 28/09/2000 39

CPLD FPGA QUESTIONS 28/09/2000 40

- Slides: 40