Computer Organization Design Peng Liu College of Information

![Signed & Unsigned Number • If given b[n-1: 0] in a register or in Signed & Unsigned Number • If given b[n-1: 0] in a register or in](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-17.jpg)

![Array Example • Consider the example a = b + pow 2[7] • Use Array Example • Consider the example a = b + pow 2[7] • Use](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-27.jpg)

![Complex Array Example • Consider line 7 from sum_pow 2() ret = pow 2[a]; Complex Array Example • Consider line 7 from sum_pow 2() ret = pow 2[a];](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-28.jpg)

![Storing to an Array • Consider the example a[3] = b + c; • Storing to an Array • Consider the example a[3] = b + c; •](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-31.jpg)

![Complex Array Storage • Consider the example a [i] = b + c; • Complex Array Storage • Consider the example a [i] = b + c; •](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-32.jpg)

![While Loop in C • Consider a while loop While (A[i] == k) i While Loop in C • Consider a while loop While (A[i] == k) i](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-51.jpg)

![J-Format Instructions (2/2) • Summary: – New PC = { PC[31. . 28], target J-Format Instructions (2/2) • Summary: – New PC = { PC[31. . 28], target](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-59.jpg)

- Slides: 82

Computer Organization & Design Peng Liu (刘鹏) College of Information Science & Electronic Engineering Zhejiang University, Hangzhou 310027, China liupeng@zju. edu. cn

Lecture 2 MIPS Instruction Set Architecture 2

MIPS ISA • Textbook reading – 2. 1 -2. 4 – Look at how instructions are defined and represented • What is an instruction set architecture (ISA)? • Interplay of C and MIPS ISA • Components of MIPS ISA – – Register operands Memory operands Arithmetic operations Control flow operations 3

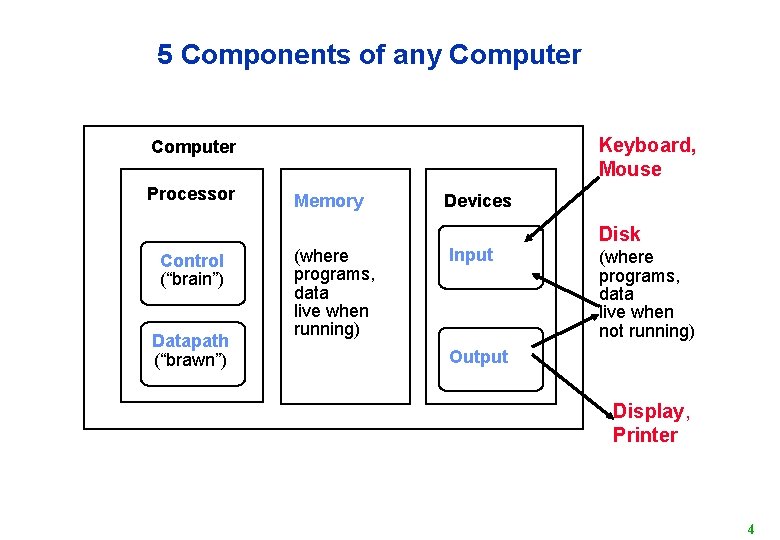

5 Components of any Computer Keyboard, Mouse Computer Processor Control (“brain”) Datapath (“brawn”) Memory (where programs, data live when running) Devices Input Disk (where programs, data live when not running) Output Display, Printer 4

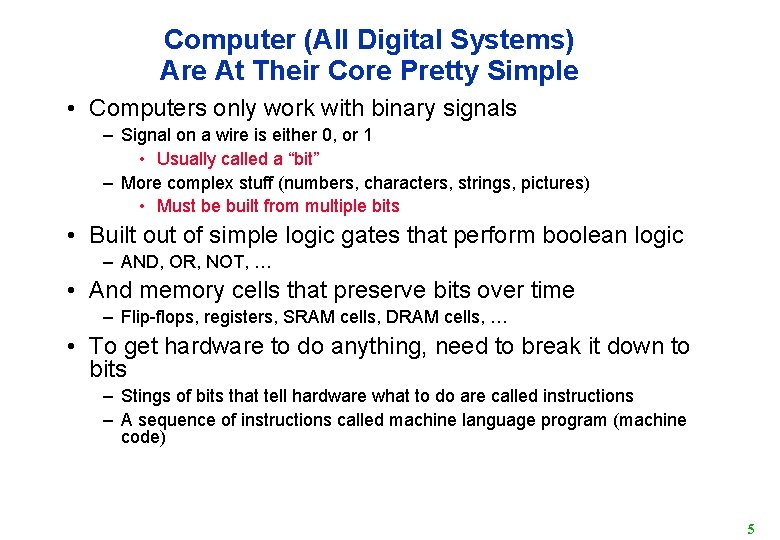

Computer (All Digital Systems) Are At Their Core Pretty Simple • Computers only work with binary signals – Signal on a wire is either 0, or 1 • Usually called a “bit” – More complex stuff (numbers, characters, strings, pictures) • Must be built from multiple bits • Built out of simple logic gates that perform boolean logic – AND, OR, NOT, … • And memory cells that preserve bits over time – Flip-flops, registers, SRAM cells, DRAM cells, … • To get hardware to do anything, need to break it down to bits – Stings of bits that tell hardware what to do are called instructions – A sequence of instructions called machine language program (machine code) 5

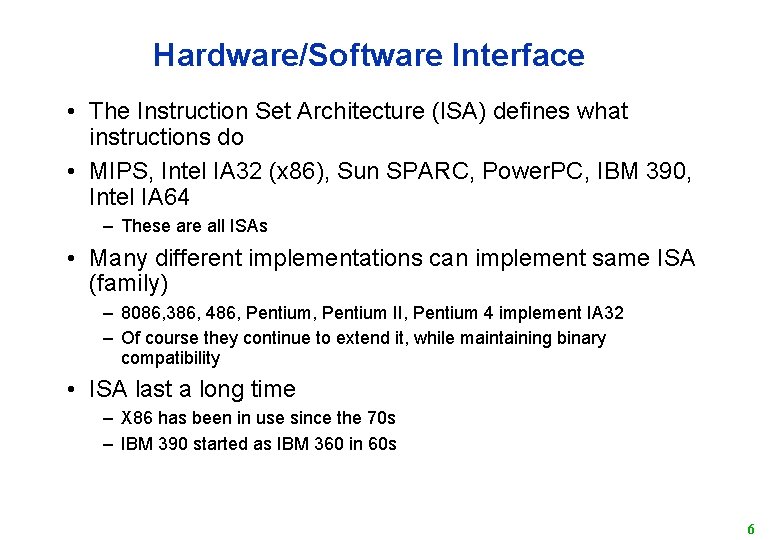

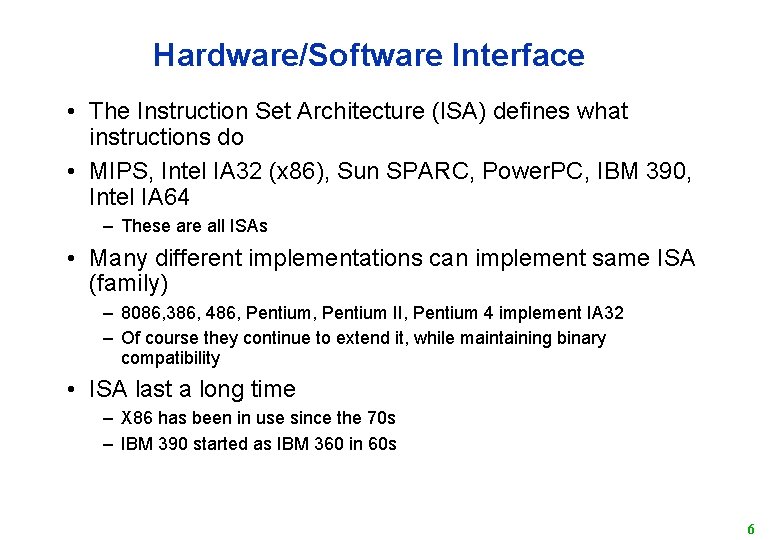

Hardware/Software Interface • The Instruction Set Architecture (ISA) defines what instructions do • MIPS, Intel IA 32 (x 86), Sun SPARC, Power. PC, IBM 390, Intel IA 64 – These are all ISAs • Many different implementations can implement same ISA (family) – 8086, 386, 486, Pentium II, Pentium 4 implement IA 32 – Of course they continue to extend it, while maintaining binary compatibility • ISA last a long time – X 86 has been in use since the 70 s – IBM 390 started as IBM 360 in 60 s 6

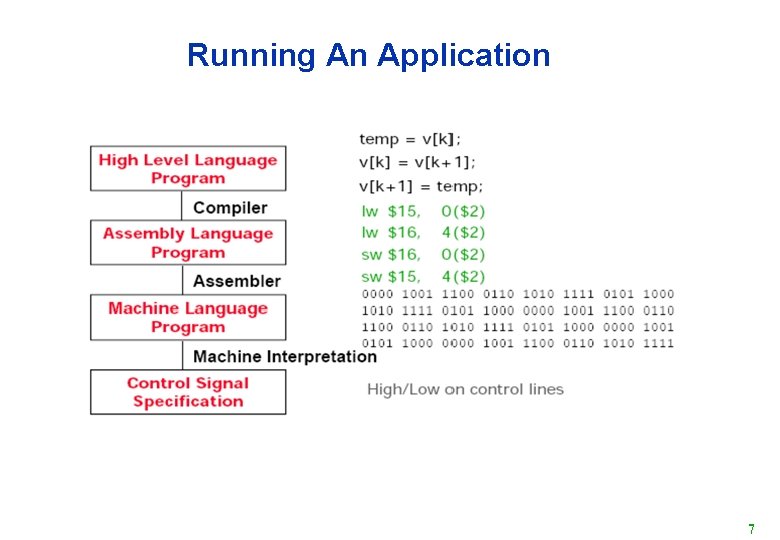

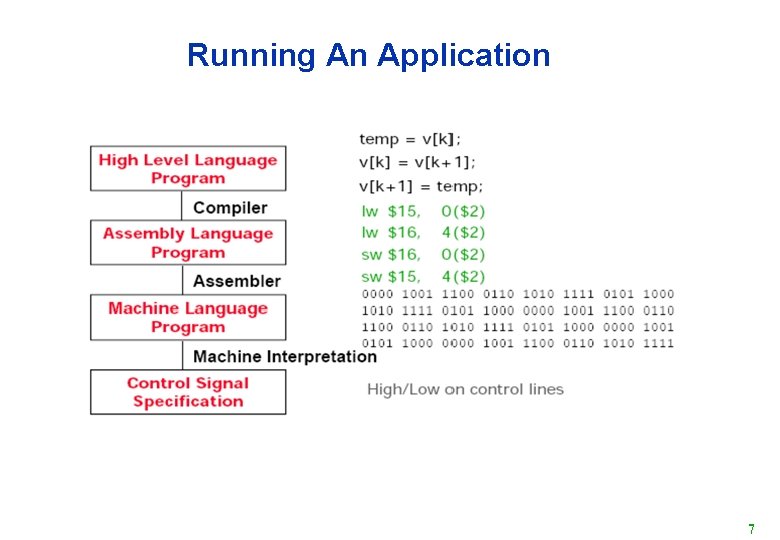

Running An Application 7

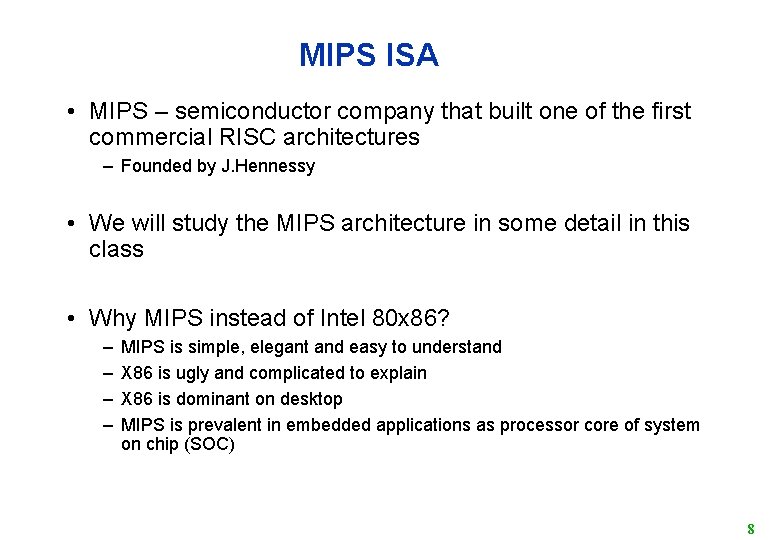

MIPS ISA • MIPS – semiconductor company that built one of the first commercial RISC architectures – Founded by J. Hennessy • We will study the MIPS architecture in some detail in this class • Why MIPS instead of Intel 80 x 86? – – MIPS is simple, elegant and easy to understand X 86 is ugly and complicated to explain X 86 is dominant on desktop MIPS is prevalent in embedded applications as processor core of system on chip (SOC) 8

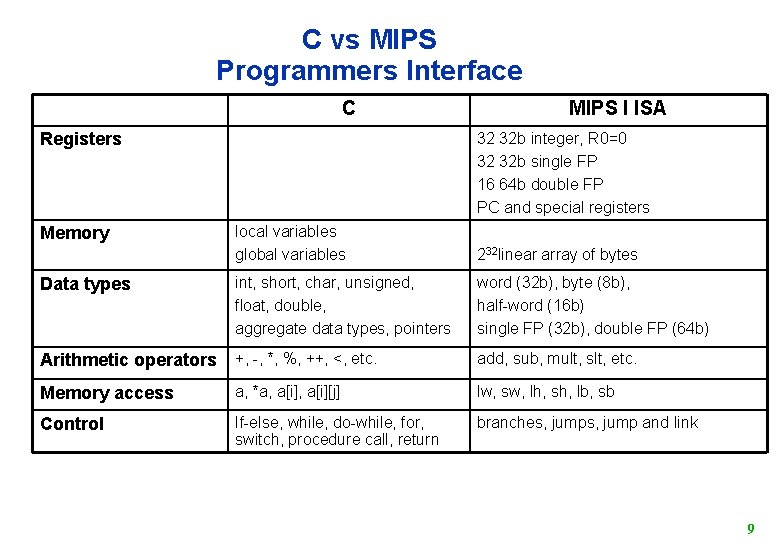

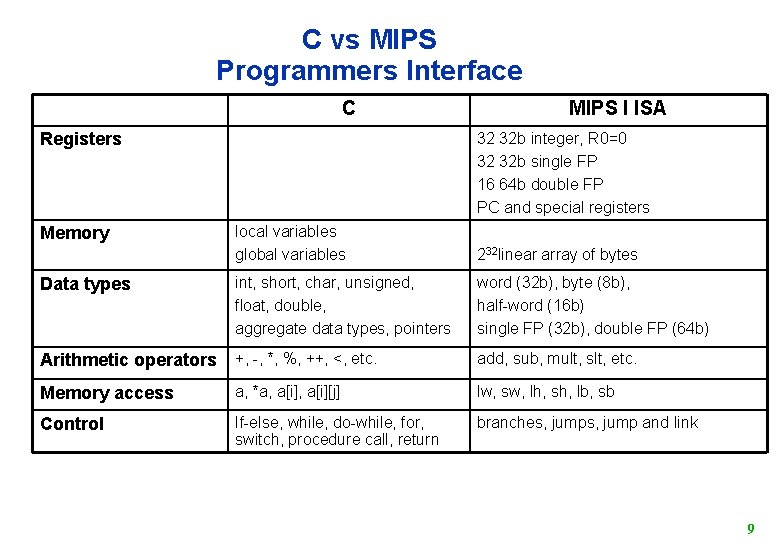

C vs MIPS Programmers Interface C Registers Memory MIPS I ISA 32 32 b integer, R 0=0 32 32 b single FP 16 64 b double FP PC and special registers local variables global variables 232 linear array of bytes Data types int, short, char, unsigned, float, double, aggregate data types, pointers word (32 b), byte (8 b), half-word (16 b) single FP (32 b), double FP (64 b) Arithmetic operators +, -, *, %, ++, <, etc. add, sub, mult, slt, etc. Memory access a, *a, a[i][j] lw, sw, lh, sh, lb, sb Control If-else, while, do-while, for, switch, procedure call, return branches, jump and link 9

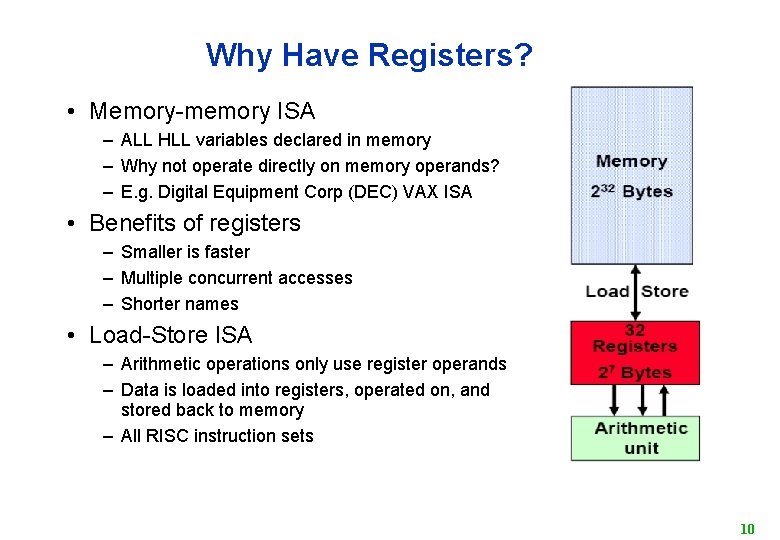

Why Have Registers? • Memory-memory ISA – ALL HLL variables declared in memory – Why not operate directly on memory operands? – E. g. Digital Equipment Corp (DEC) VAX ISA • Benefits of registers – Smaller is faster – Multiple concurrent accesses – Shorter names • Load-Store ISA – Arithmetic operations only use register operands – Data is loaded into registers, operated on, and stored back to memory – All RISC instruction sets 10

Using Registers • Registers are a finite resource that needs to be managed – Programmer – Compilers: register allocation • Goals – Keep data in registers as much as possible – Always use data still in registers if possible • Issues – Finite number of registers available • Spill register to memory when all register in use – Arrays • Data is too large to store in registers – What’s the impact of fewer or more registers? 11

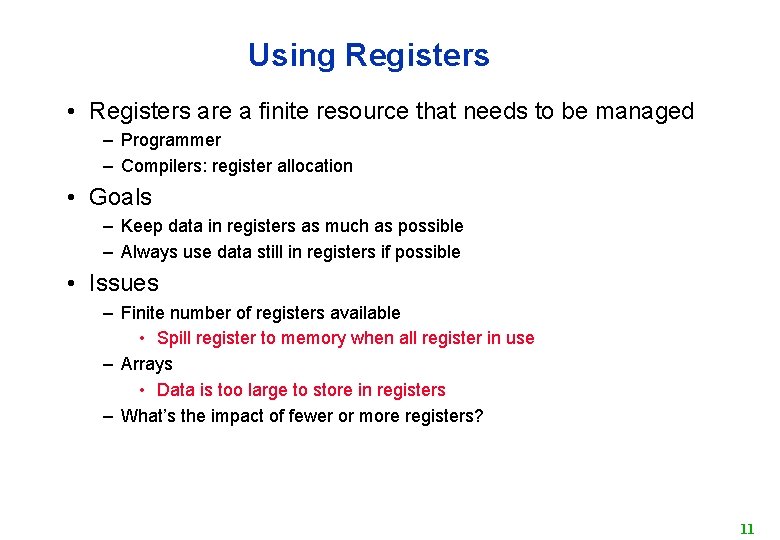

Register Naming • Registers are identified by a $<num> • By convention, we also give them names – – – $zero contains the hardwired value 0 $v 0, $v 1 are for results and expression evaluation $a 0 -$a 3 are for arguments $s 0, $s 1, … $s 7 are for save values $to, $t 1, …$t 9 are for temporary values The others will be introduced as appropriate • Compilers use these conventions to simplify linking 12

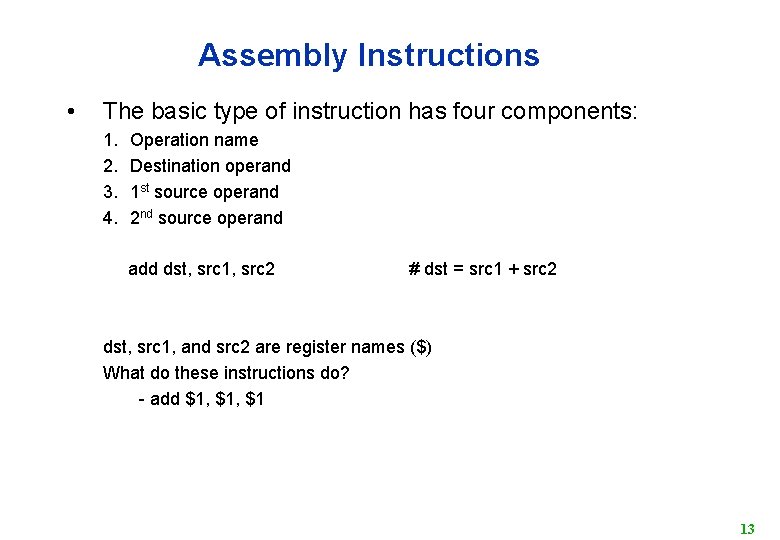

Assembly Instructions • The basic type of instruction has four components: 1. 2. 3. 4. Operation name Destination operand 1 st source operand 2 nd source operand add dst, src 1, src 2 # dst = src 1 + src 2 dst, src 1, and src 2 are register names ($) What do these instructions do? - add $1, $1 13

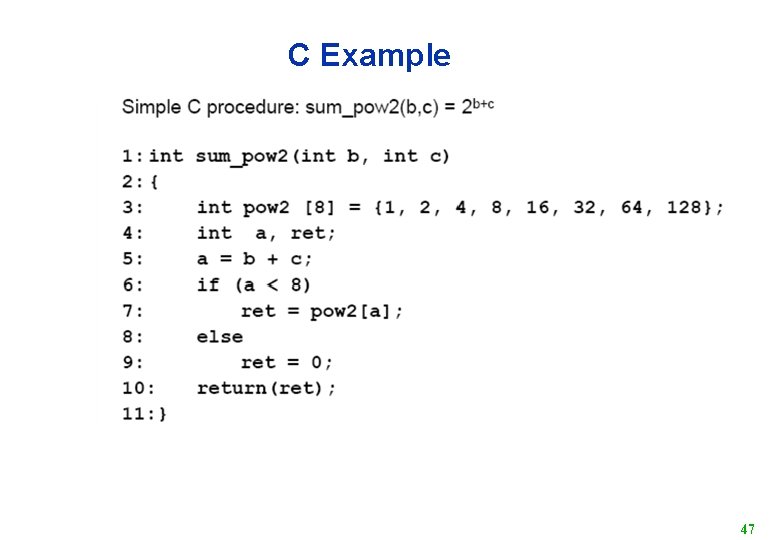

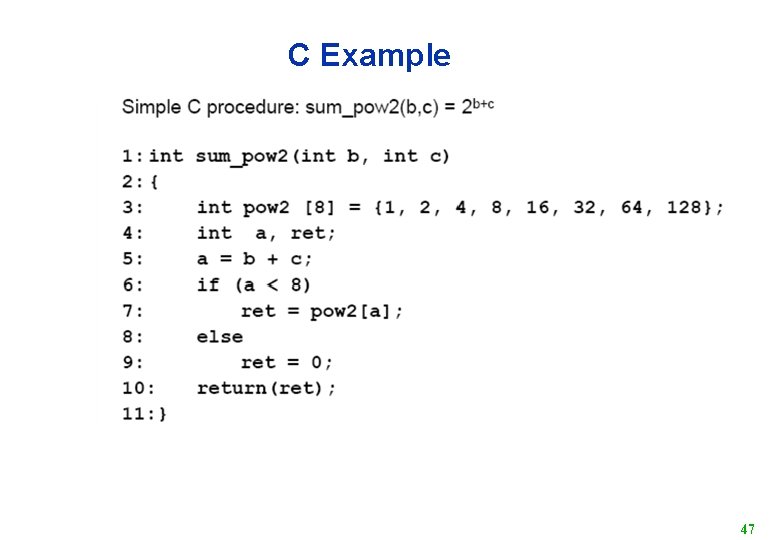

C Example Simple C procedure: sum_pow 2 = 2 b+c 1: int sum_pow 2 (int b, int c) 2: { 3: int pow 2[8] = {1, 2, 4, 8, 16, 32, 64, 128}; 4: int a , ret; 5: a = b + c; 6: if (a < 8) 7: ret = pow 2[a]; 8: else 9: ret = 0; 10: return (ret); 11: } 14

Arithmetic Operators • Consider line 5, C operation for addition a = b + c; • Assume the variables are in register $1 -$3 respectively. • The add operator using registers add $1, $2, $3 # a = b +c • Use the sub operator for a=b-c in MIPS sub $1, $2, $3 # a = b - c • But we know that variables a, b, and c really start in some memory location – Will add load & store instruction soon 15

Complex Operations • What about more complex statements? a = b + c + d – e; • Break into multiple instructions add $t 0, $s 1, $s 2 # $t 0 = b + c add $t 1, $t 0, $s 3 # $t 1 = $t 0 + d sub $s 0, $t 1, $s 4 # a = $t 1 - e 16

![Signed Unsigned Number If given bn1 0 in a register or in Signed & Unsigned Number • If given b[n-1: 0] in a register or in](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-17.jpg)

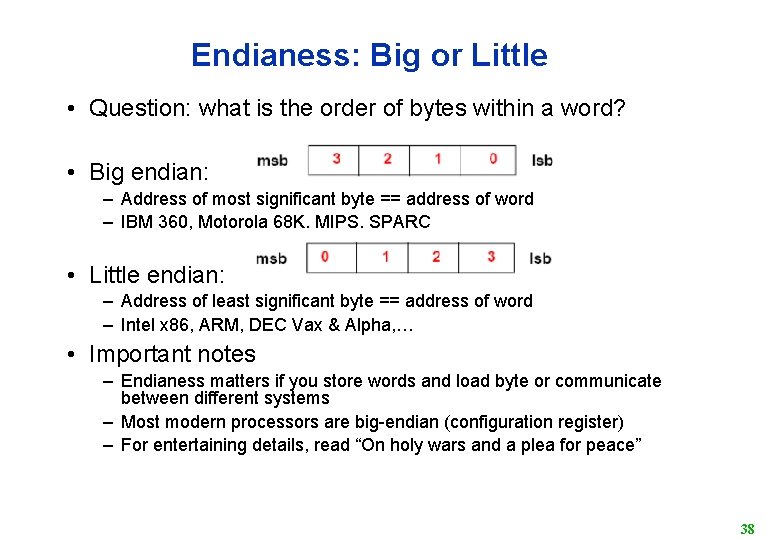

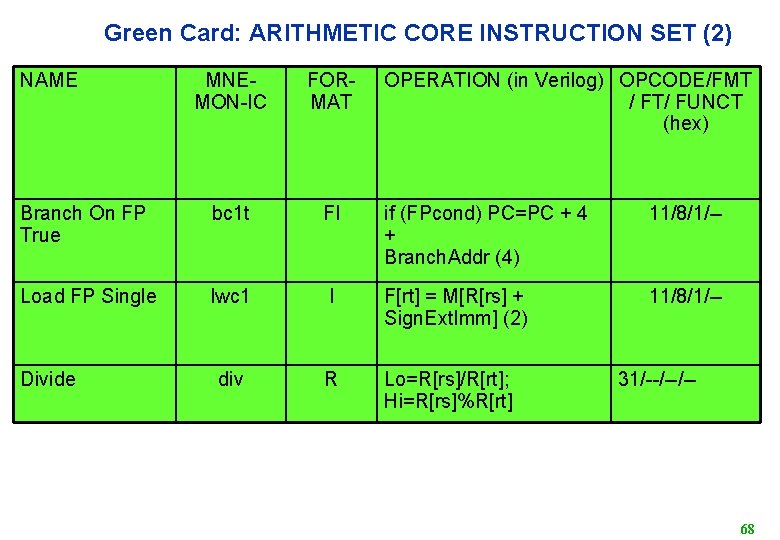

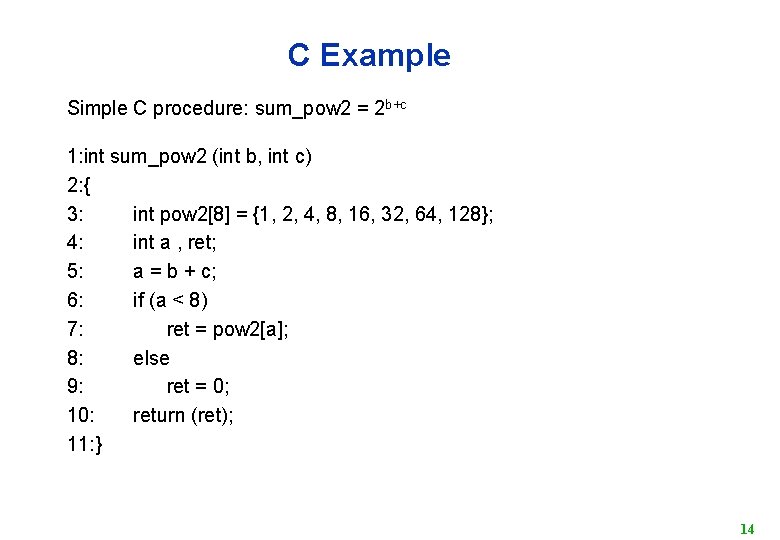

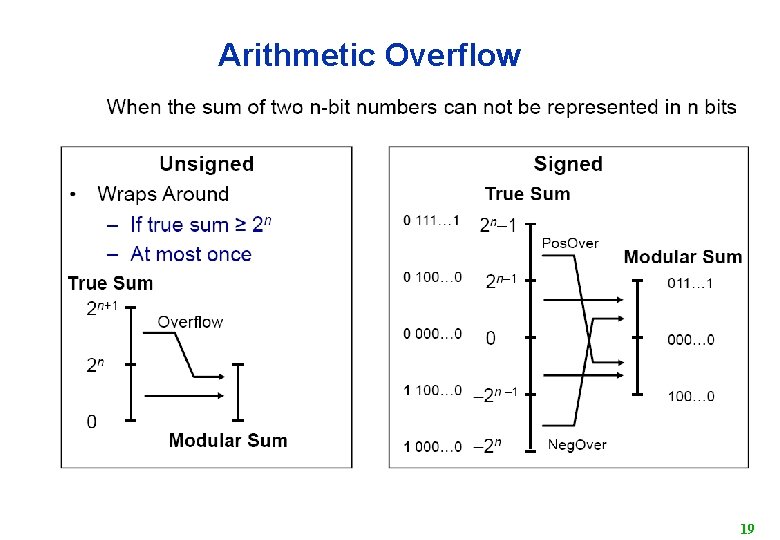

Signed & Unsigned Number • If given b[n-1: 0] in a register or in memory • Unsigned value • Signed value (2’s complement) 17

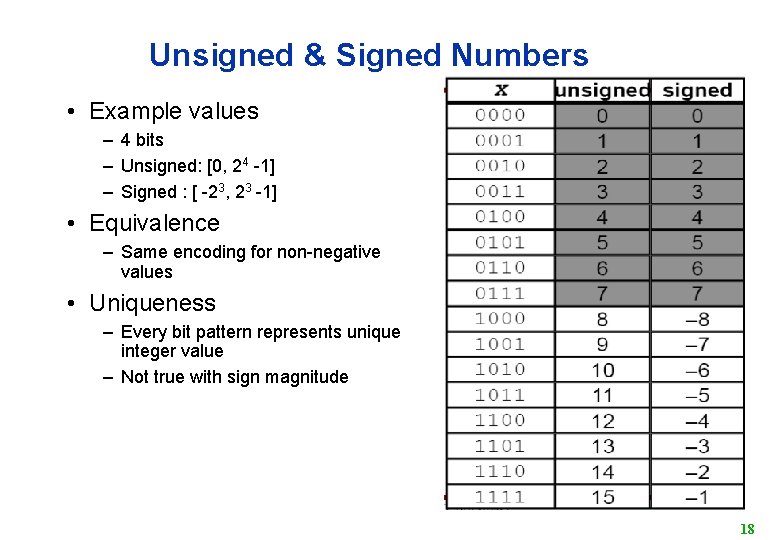

Unsigned & Signed Numbers • Example values – 4 bits – Unsigned: [0, 24 -1] – Signed : [ -23, 23 -1] • Equivalence – Same encoding for non-negative values • Uniqueness – Every bit pattern represents unique integer value – Not true with sign magnitude 18

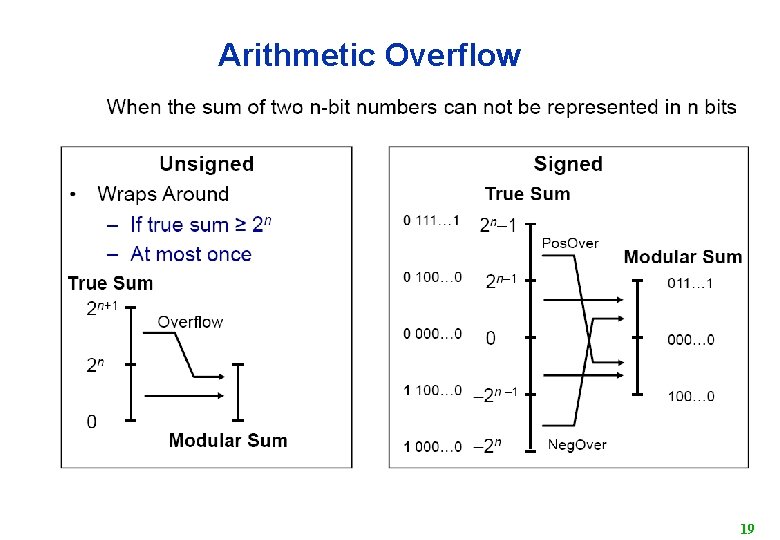

Arithmetic Overflow 19

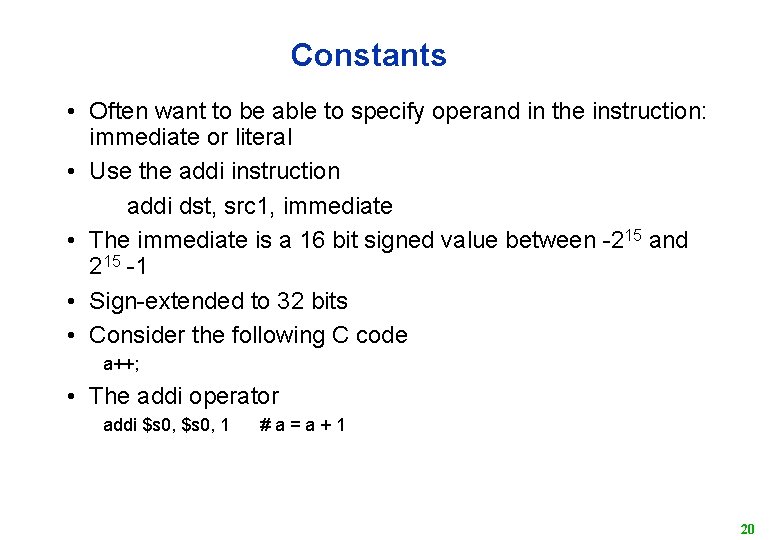

Constants • Often want to be able to specify operand in the instruction: immediate or literal • Use the addi instruction addi dst, src 1, immediate • The immediate is a 16 bit signed value between -215 and 215 -1 • Sign-extended to 32 bits • Consider the following C code a++; • The addi operator addi $s 0, 1 # a = a + 1 20

Memory Data Transfer • Data transfer instructions are used to move data to and from memory. • A load operation moves data from a memory location to a register and a store operation moves data from a register to a memory location. 21

Data Transfer Instructions: Loads • Data transfer instructions have three parts – Operator name (transfer size) – Destination register – Base register address and constant offset lw dst, offset (base) – Offset value is a singed constant 22

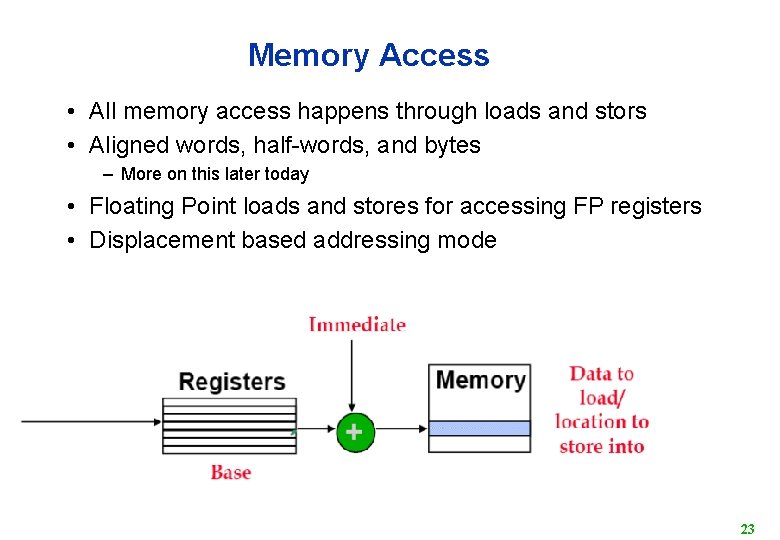

Memory Access • All memory access happens through loads and stors • Aligned words, half-words, and bytes – More on this later today • Floating Point loads and stores for accessing FP registers • Displacement based addressing mode 23

Loading Data Example • Consider the example a = b + *c; Use the lw instruction to load Assume a($s 0), b($s 1), c($s 2) lw $t 0, 0 ($s 2) # $t 0 = Memory[c] add $s 0, $s 1, $t 0 # a = b + *c 24

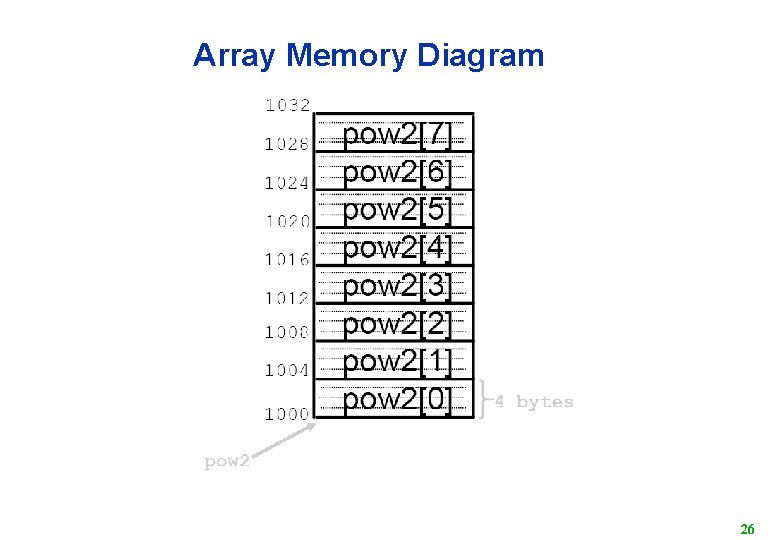

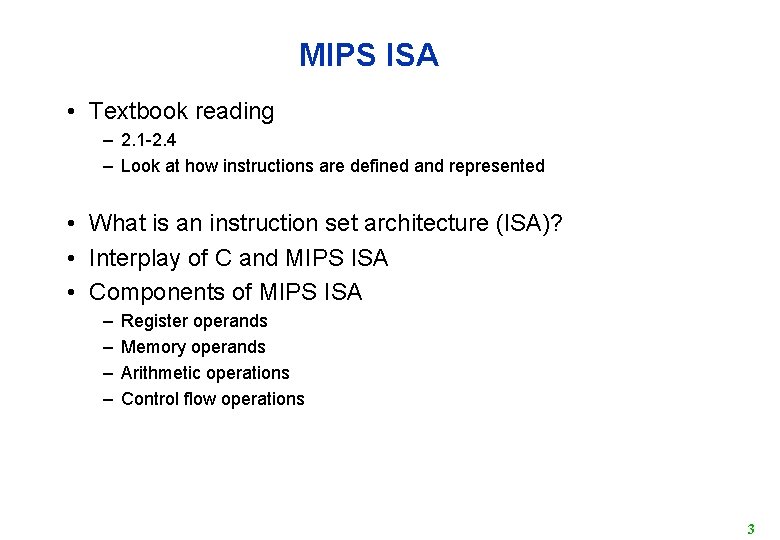

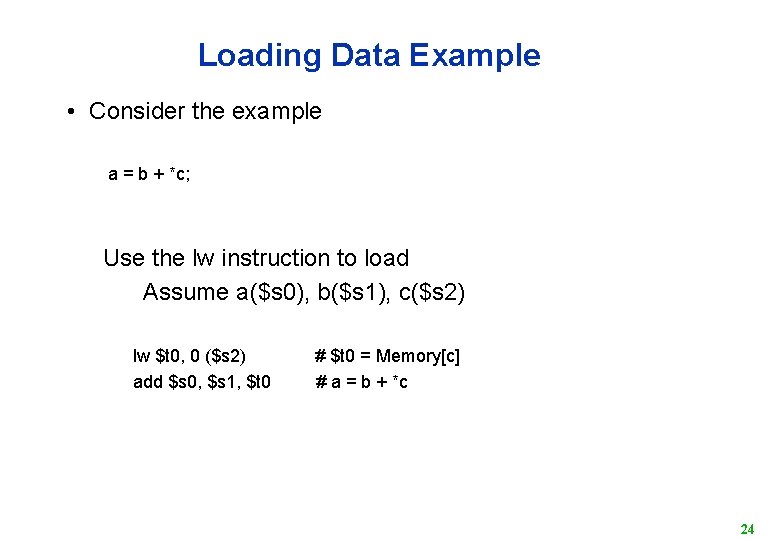

Accessing Arrays • Arrays are really pointers to the base address in memory – Address of element A[0] • Use offset value to indicate which index • Remember that addresses are in bytes, so multiply by the size of the element – – Consider the integer array where pow 2 is the base address With this compiler on this architecture, each int requires 4 bytes The data to be accessed is at index 5: pow 2[5] Then the address from memory is pow 2 + 5*4 • Unlike C, assembly does not handle pointer arithmetic for you! 25

Array Memory Diagram 26

![Array Example Consider the example a b pow 27 Use Array Example • Consider the example a = b + pow 2[7] • Use](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-27.jpg)

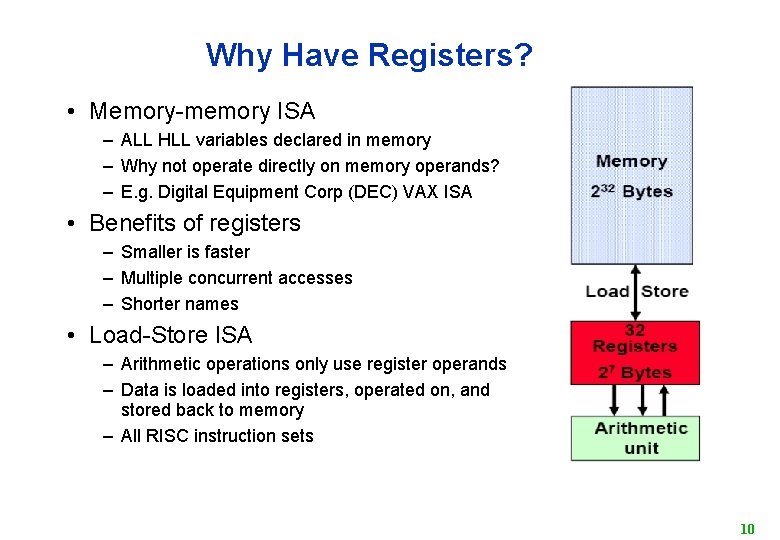

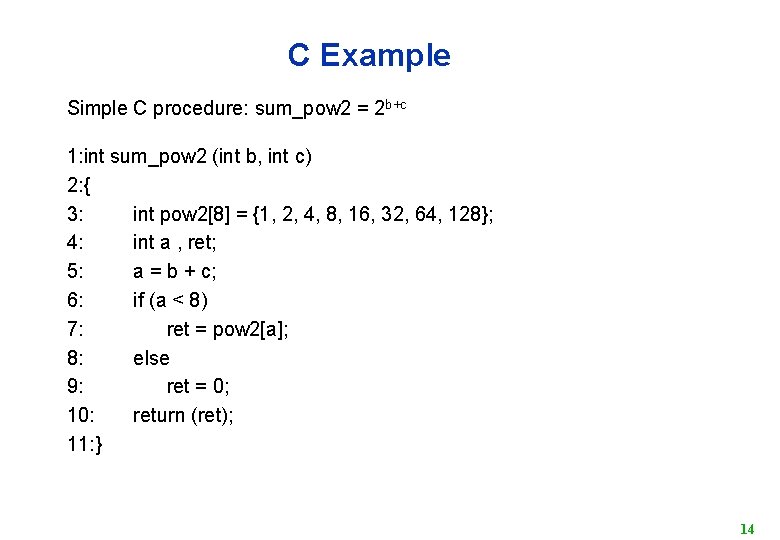

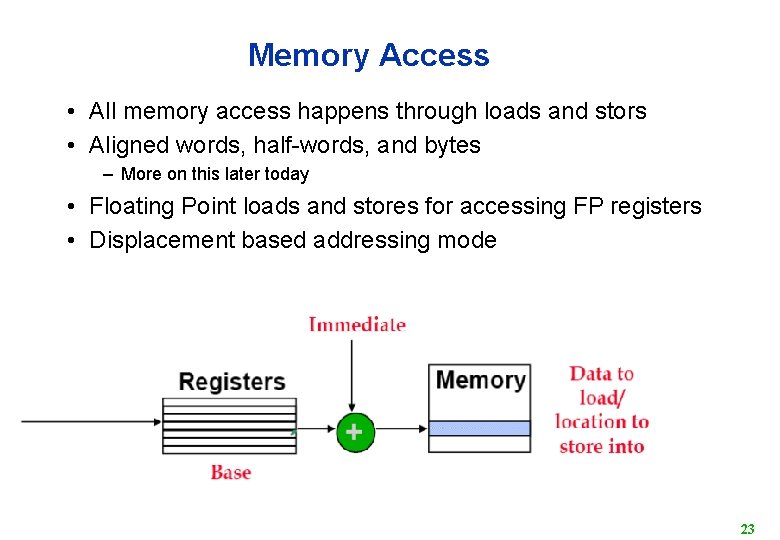

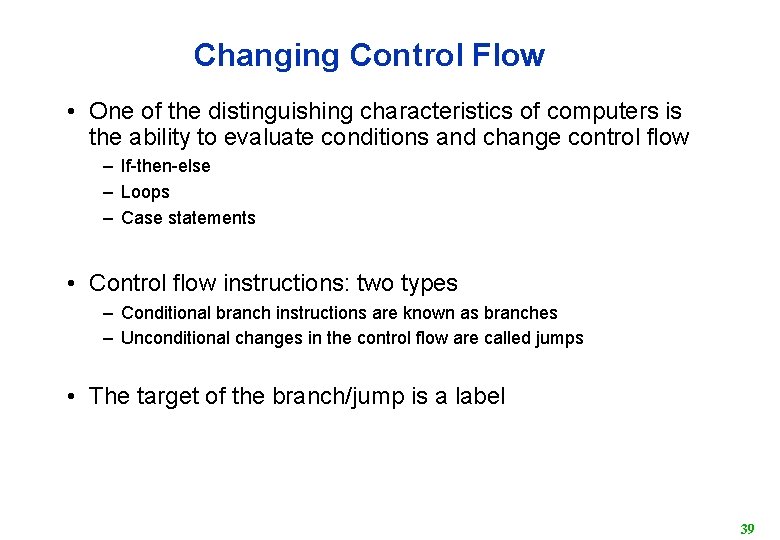

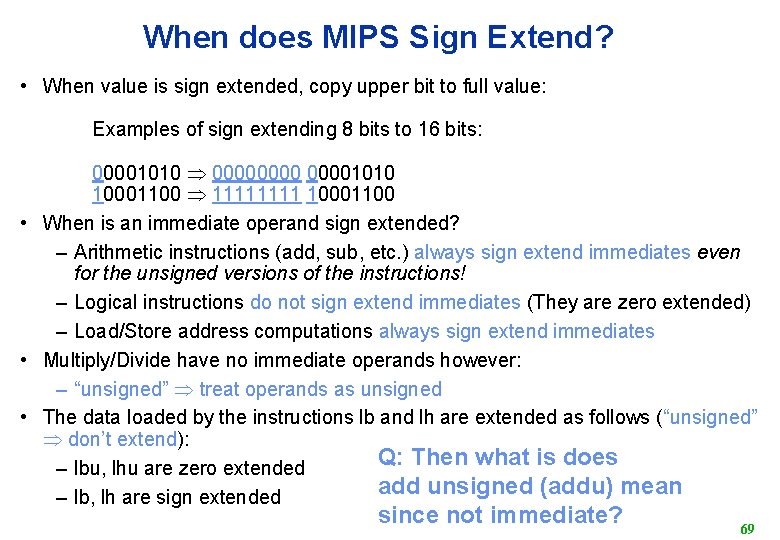

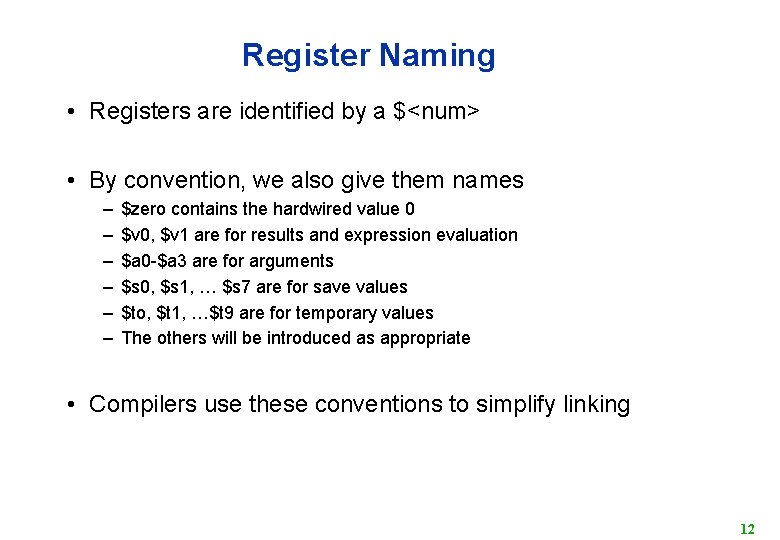

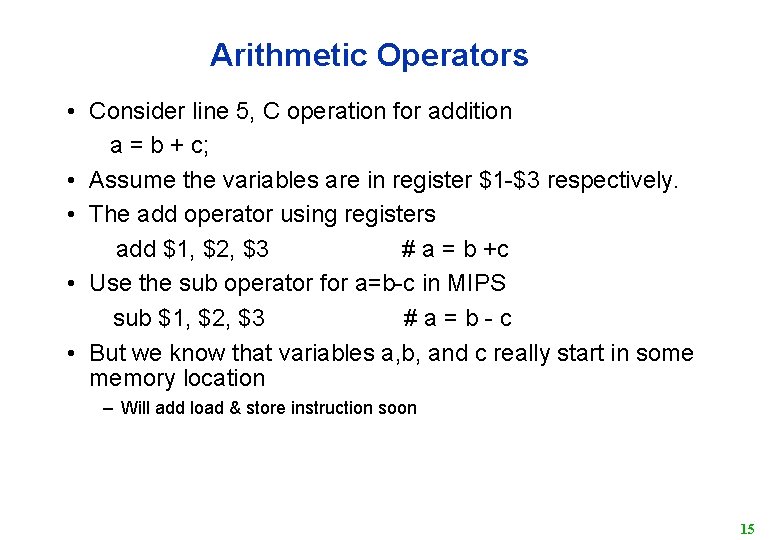

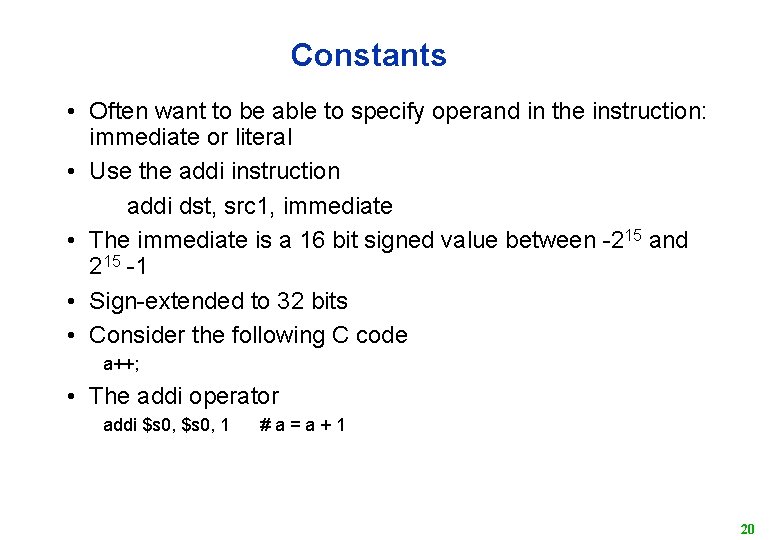

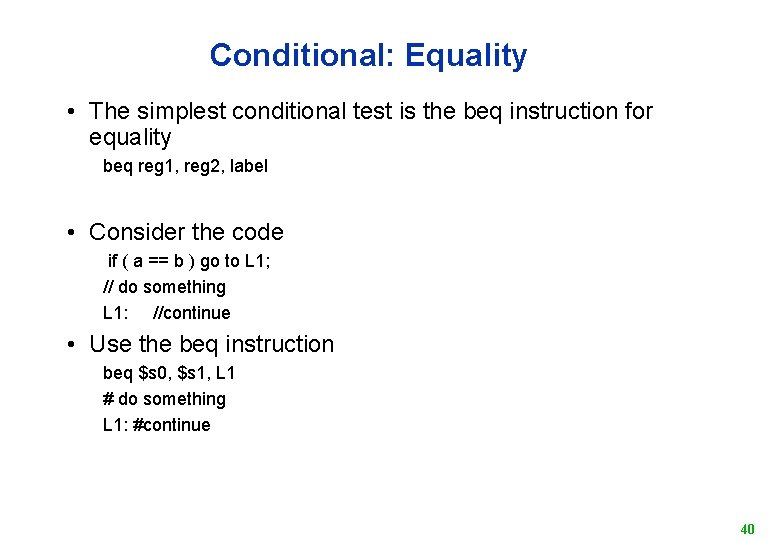

Array Example • Consider the example a = b + pow 2[7] • Use the lw instruction offset, assume $s 3 = 1000 lw $t 0, 28($s 3) # $t 0 = Memory[pow 2[7]] add $s 0, $s 1, $t 0 # a = b + pow 2[7]

![Complex Array Example Consider line 7 from sumpow 2 ret pow 2a Complex Array Example • Consider line 7 from sum_pow 2() ret = pow 2[a];](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-28.jpg)

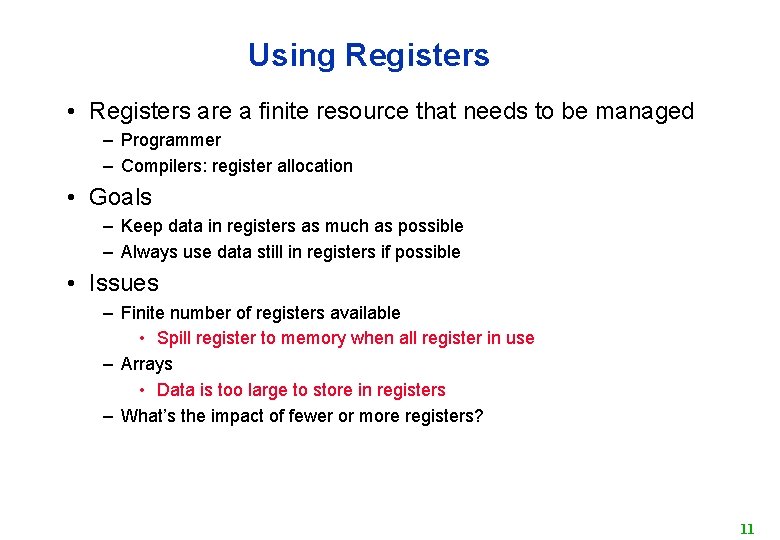

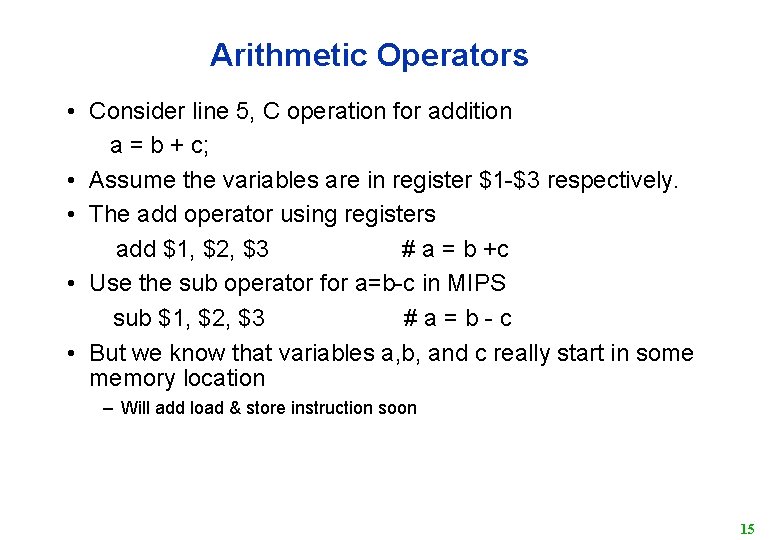

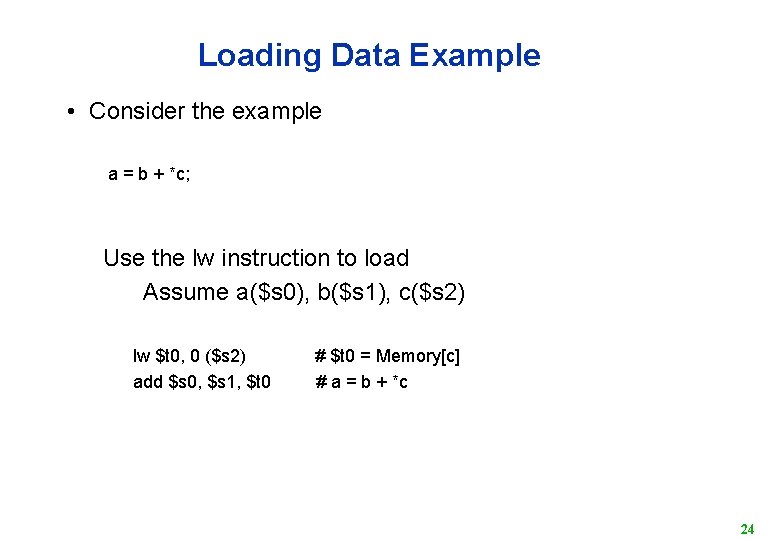

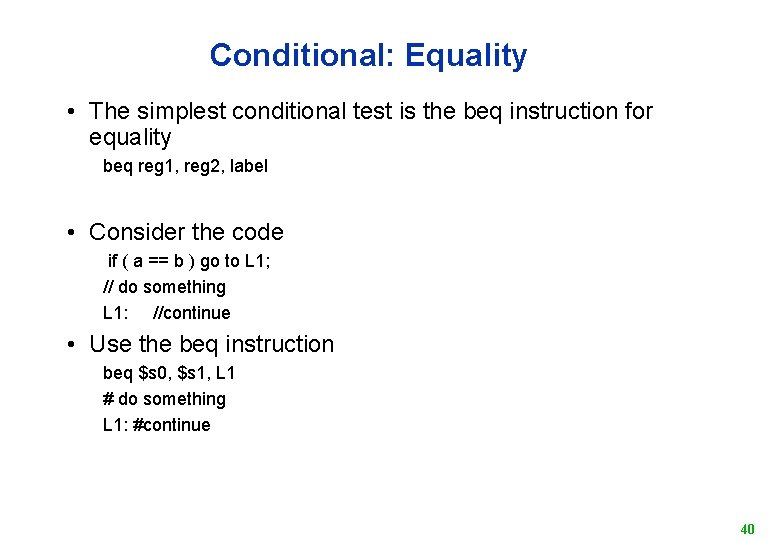

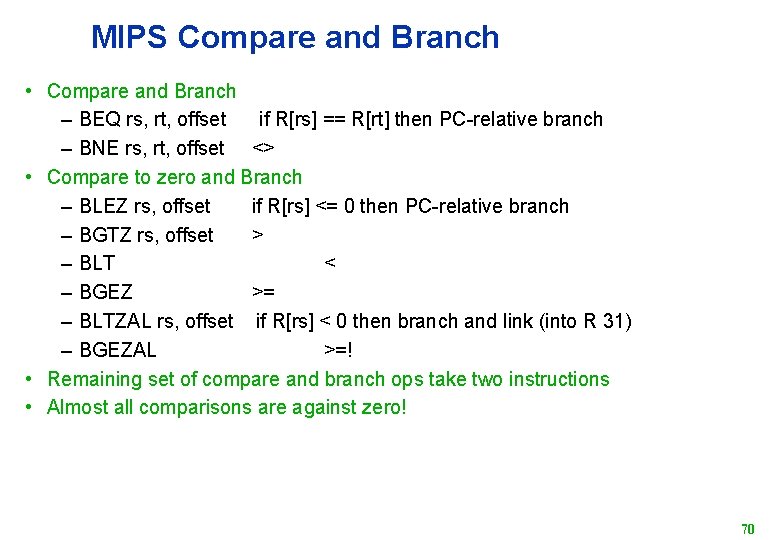

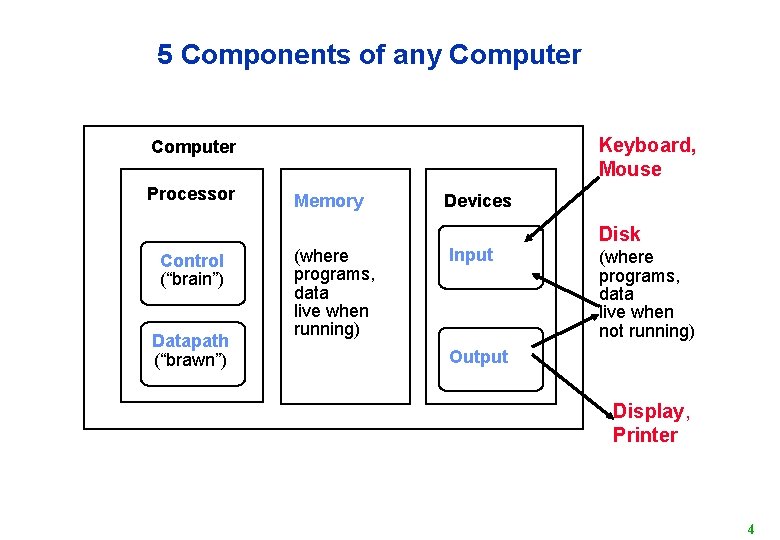

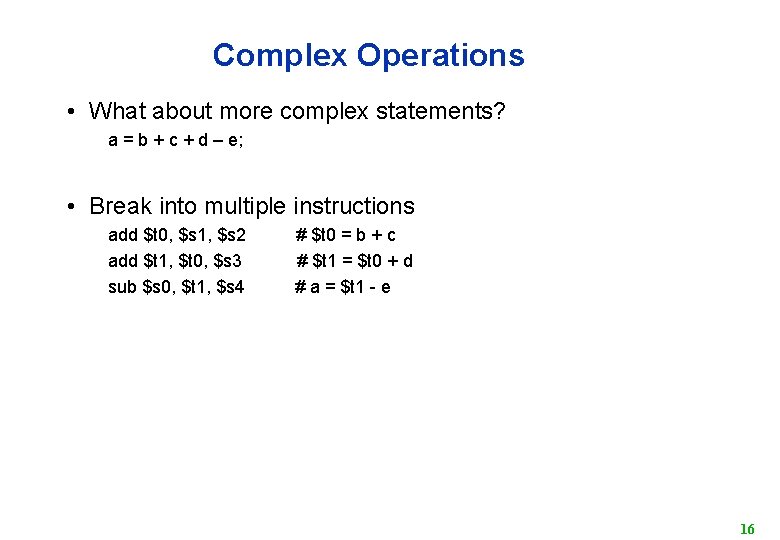

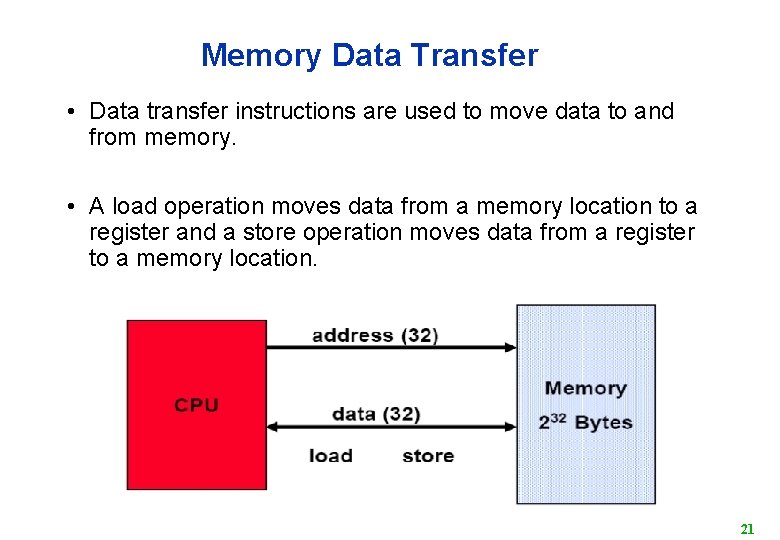

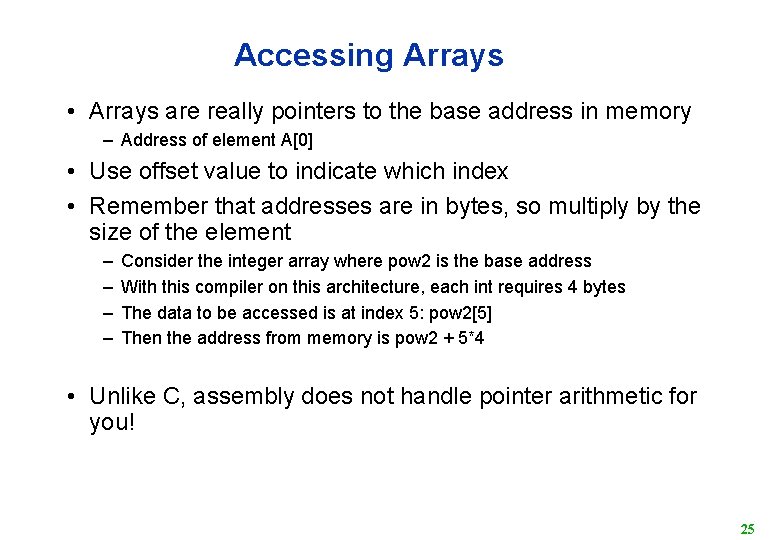

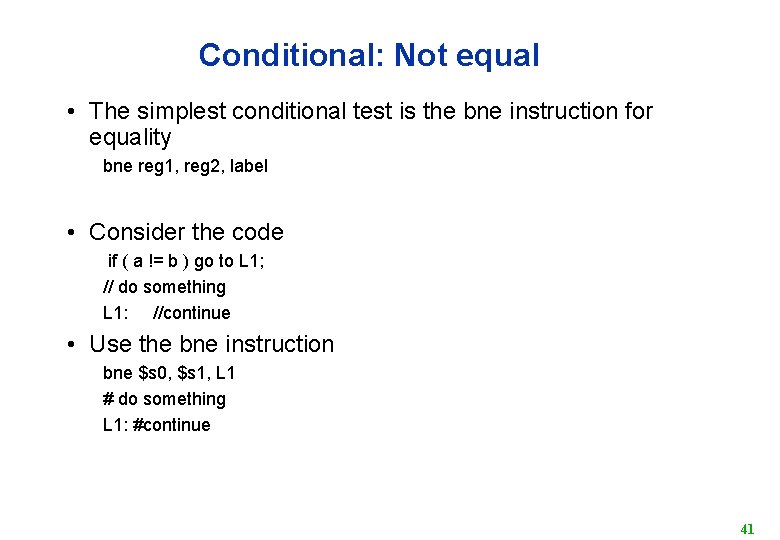

Complex Array Example • Consider line 7 from sum_pow 2() ret = pow 2[a]; • First find the correct offset, again assume $s 3 = 1000 sll $t 0, $s 0, 2 # $t 0 = 4 * a; shift left by 2 add $t 1, $s 3, $t 0 # $t 1 = pow 2 + 4*a lw $v 0, 0($t 1) # $v 0 = Memory[pow 2[a]]

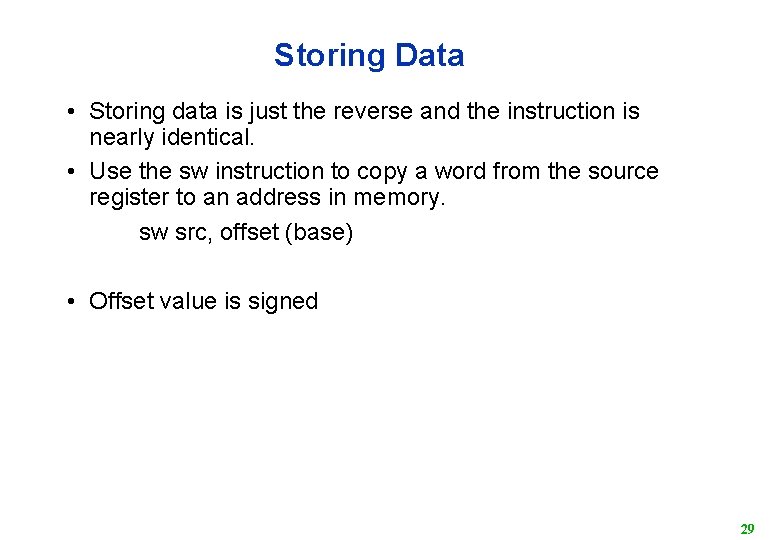

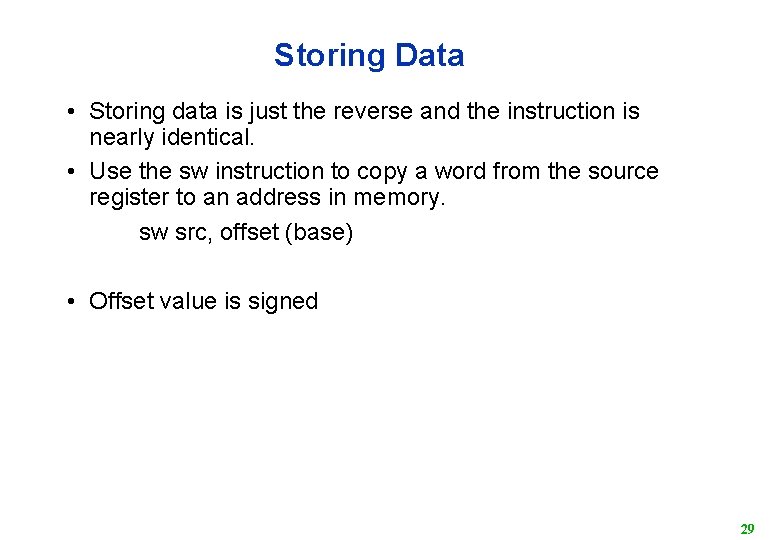

Storing Data • Storing data is just the reverse and the instruction is nearly identical. • Use the sw instruction to copy a word from the source register to an address in memory. sw src, offset (base) • Offset value is signed 29

Storing Data Example • Consider the example *a = b + c; • Use the sw instruction to store add $ t 0, $s 1, $s 2 # $t 0 = b + c sw $t 0, 0($s 0) # Memory[s 0] = b + c 30

![Storing to an Array Consider the example a3 b c Storing to an Array • Consider the example a[3] = b + c; •](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-31.jpg)

Storing to an Array • Consider the example a[3] = b + c; • Use the sw instruction offset add $t 0, $s 1, $s 2 # $t 0 = b + c sw $t 0, 12($s 0) # Memory[a[3]] = b + c 31

![Complex Array Storage Consider the example a i b c Complex Array Storage • Consider the example a [i] = b + c; •](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-32.jpg)

Complex Array Storage • Consider the example a [i] = b + c; • Use the sw instruction offset add $t 0, $s 1, $s 2 # $t 0 = b + c sll $t 1, $s 3, 2 # $t 1 = 4 * I add $t 2, $s 0, $t 1 #t 2 = a + 4*I sw $t 0, 0($t 2) # Memory[a[i]]= b + c 32

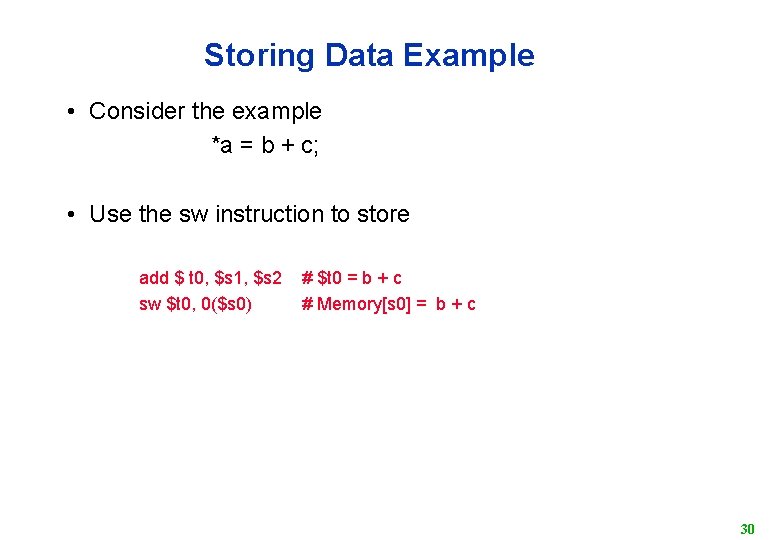

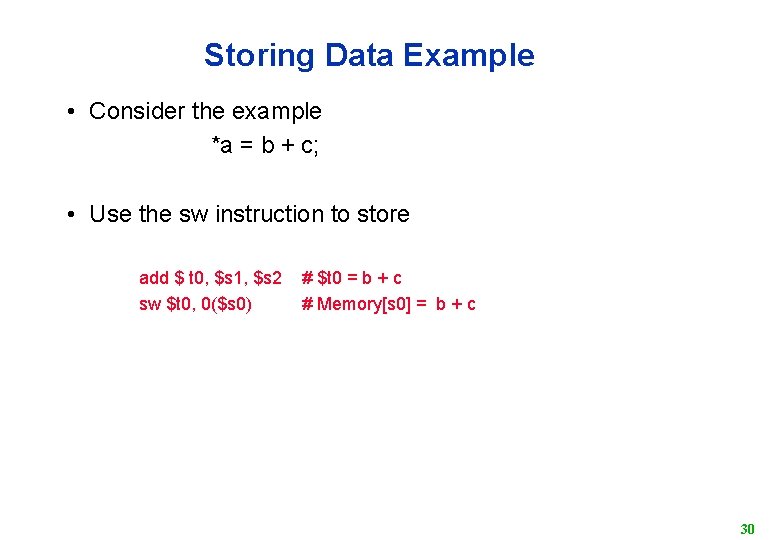

A “short” Array Example • ANSI C requires a short to be at least 16 bits and no longer than an int, but does not define the exact size • For our purposes, treat a short as 2 bytes • So, with a short array c[7] is at c + 7*2, shift left by 1 33

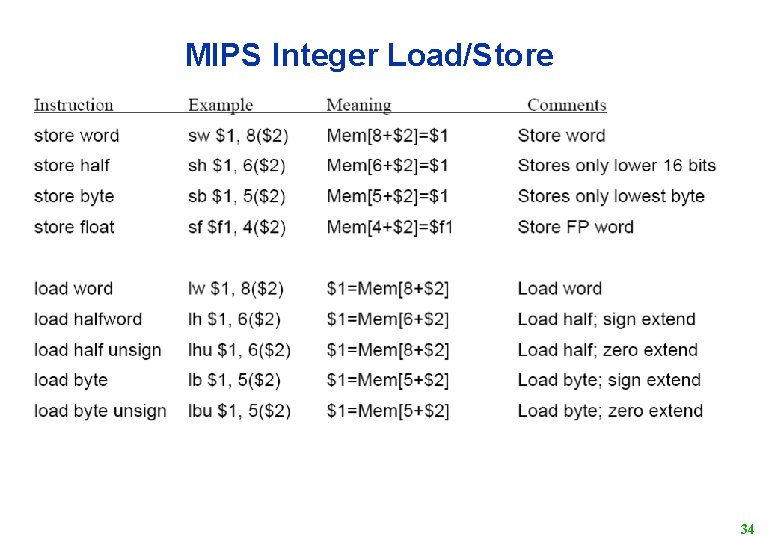

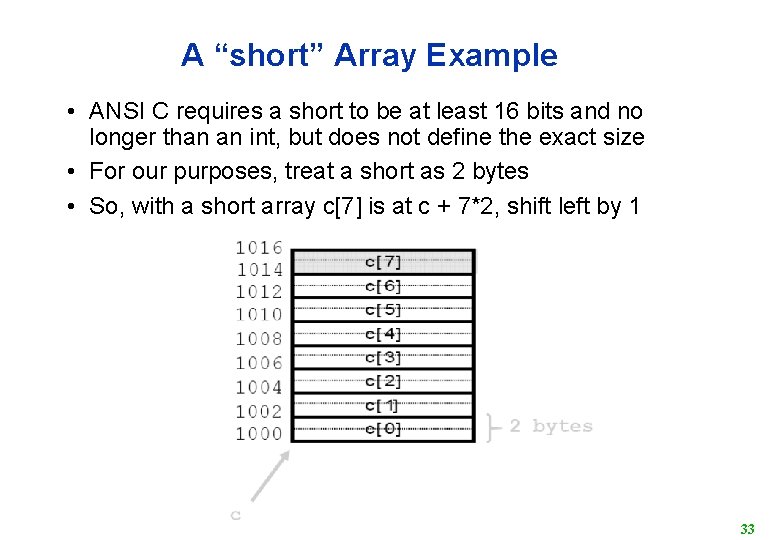

MIPS Integer Load/Store 34

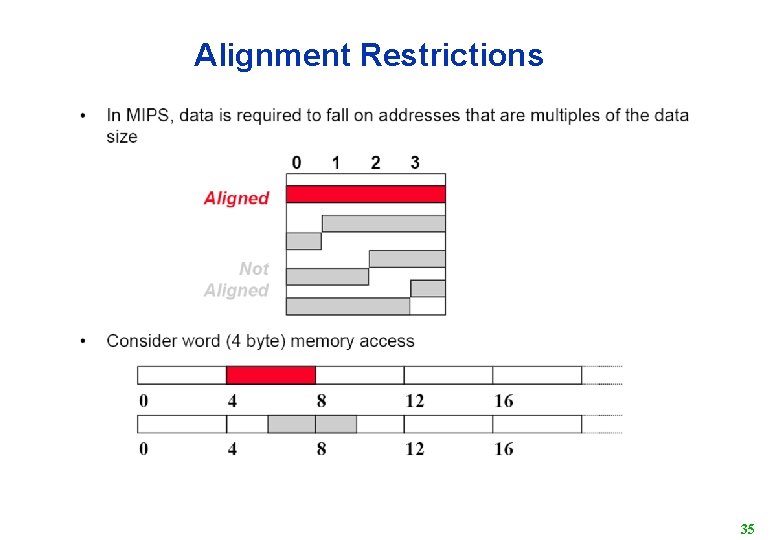

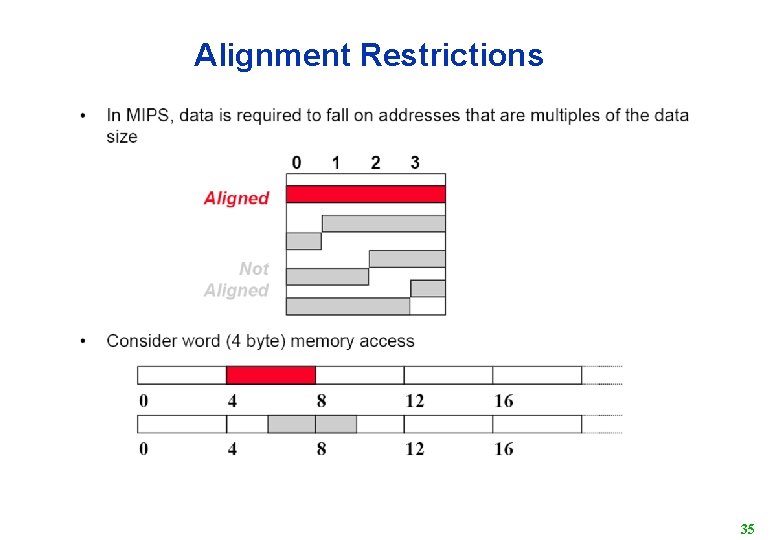

Alignment Restrictions 35

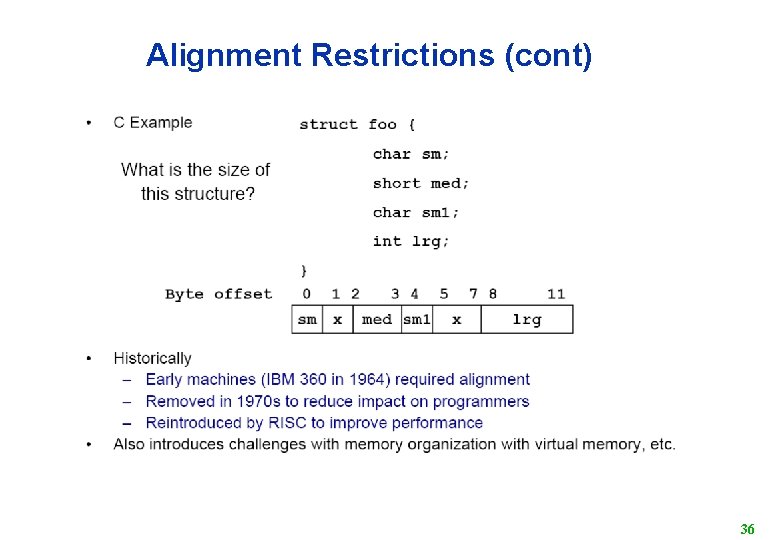

Alignment Restrictions (cont) 36

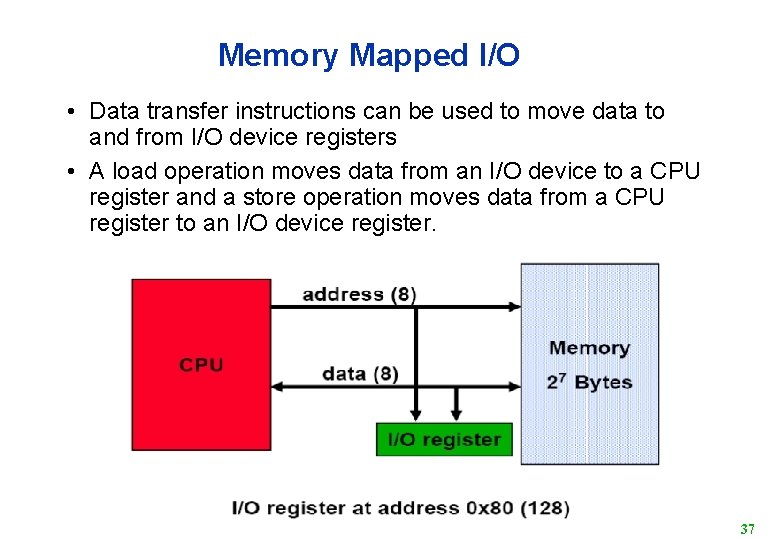

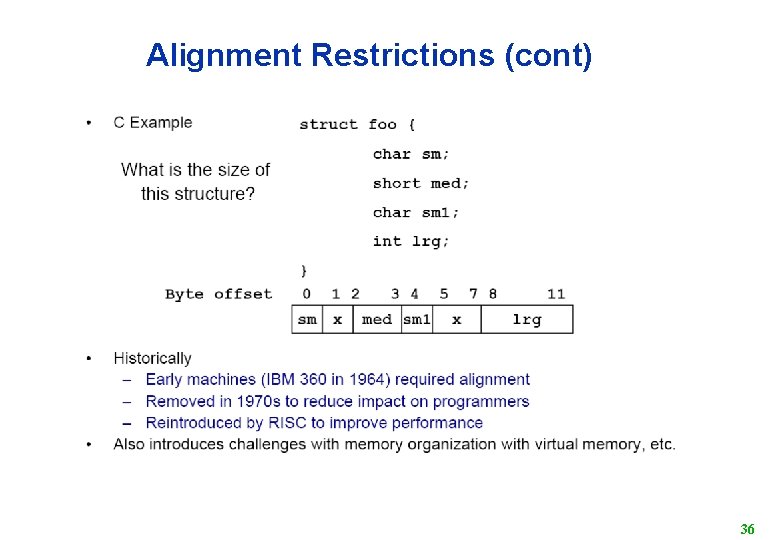

Memory Mapped I/O • Data transfer instructions can be used to move data to and from I/O device registers • A load operation moves data from an I/O device to a CPU register and a store operation moves data from a CPU register to an I/O device register. 37

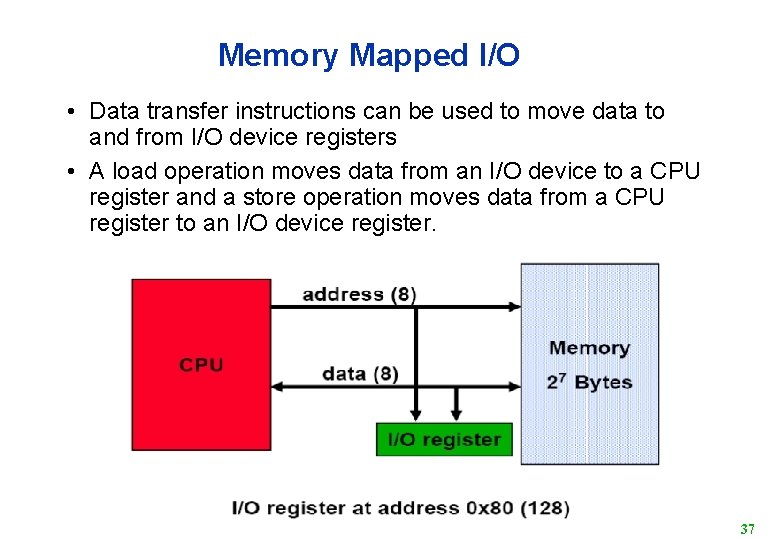

Endianess: Big or Little • Question: what is the order of bytes within a word? • Big endian: – Address of most significant byte == address of word – IBM 360, Motorola 68 K, MIPS, SPARC • Little endian: – Address of least significant byte == address of word – Intel x 86, ARM, DEC Vax & Alpha, … • Important notes – Endianess matters if you store words and load byte or communicate between different systems – Most modern processors are big-endian (configuration register) – For entertaining details, read “On holy wars and a plea for peace” 38

Changing Control Flow • One of the distinguishing characteristics of computers is the ability to evaluate conditions and change control flow – If-then-else – Loops – Case statements • Control flow instructions: two types – Conditional branch instructions are known as branches – Unconditional changes in the control flow are called jumps • The target of the branch/jump is a label 39

Conditional: Equality • The simplest conditional test is the beq instruction for equality beq reg 1, reg 2, label • Consider the code if ( a == b ) go to L 1; // do something L 1: //continue • Use the beq instruction beq $s 0, $s 1, L 1 # do something L 1: #continue 40

Conditional: Not equal • The simplest conditional test is the bne instruction for equality bne reg 1, reg 2, label • Consider the code if ( a != b ) go to L 1; // do something L 1: //continue • Use the bne instruction bne $s 0, $s 1, L 1 # do something L 1: #continue 41

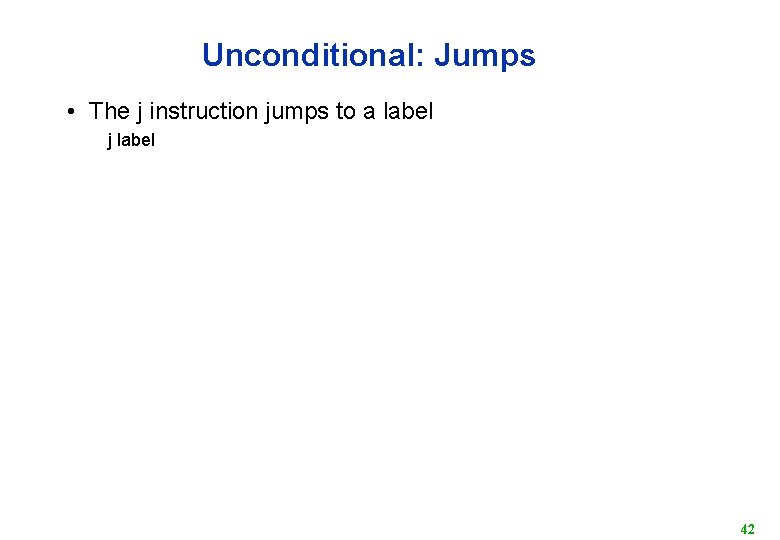

Unconditional: Jumps • The j instruction jumps to a label j label 42

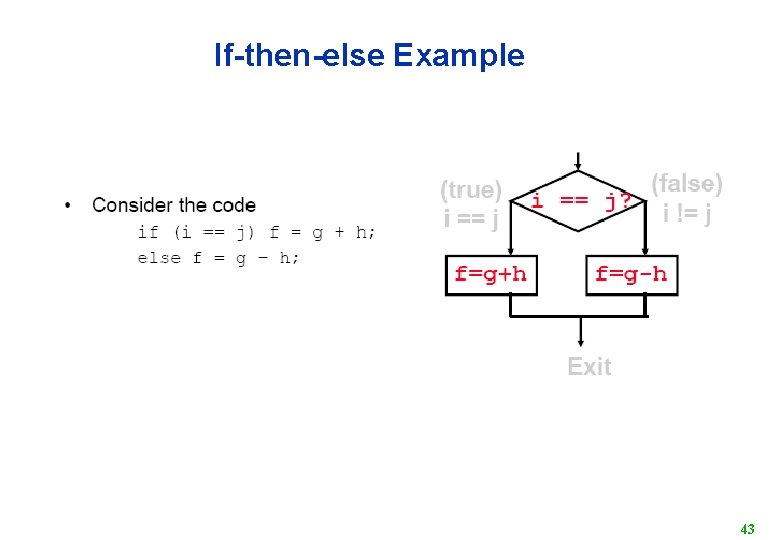

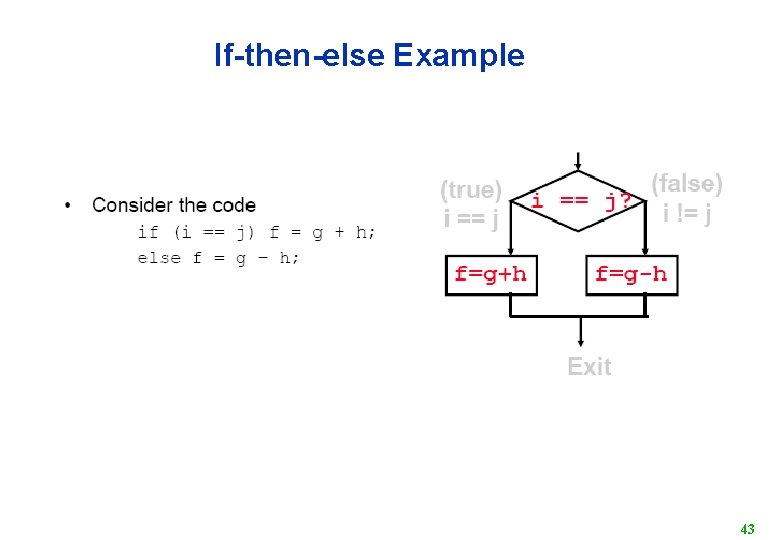

If-then-else Example 43

If-then-else Solution 44

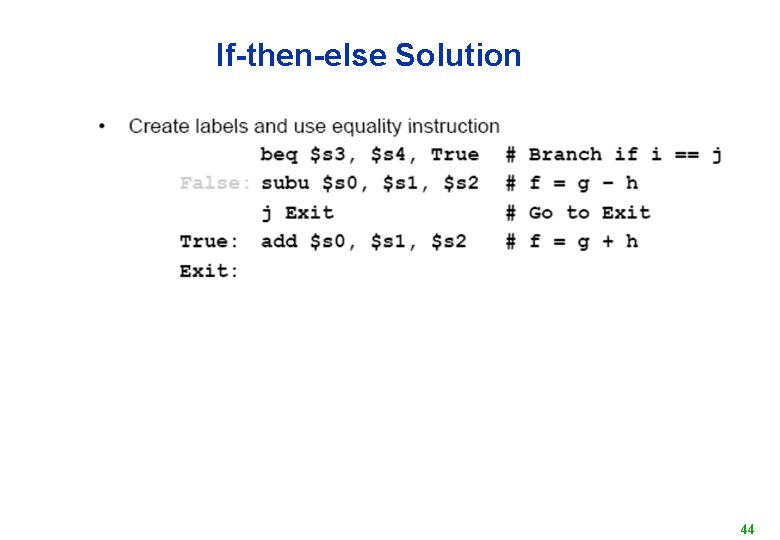

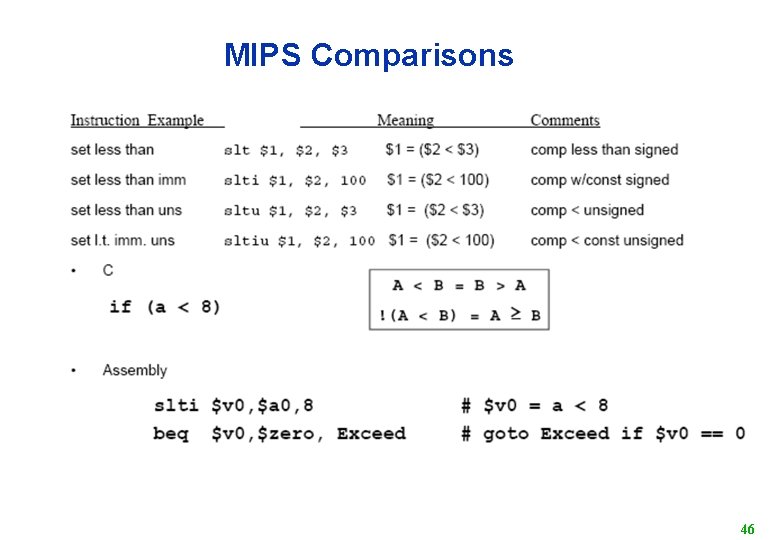

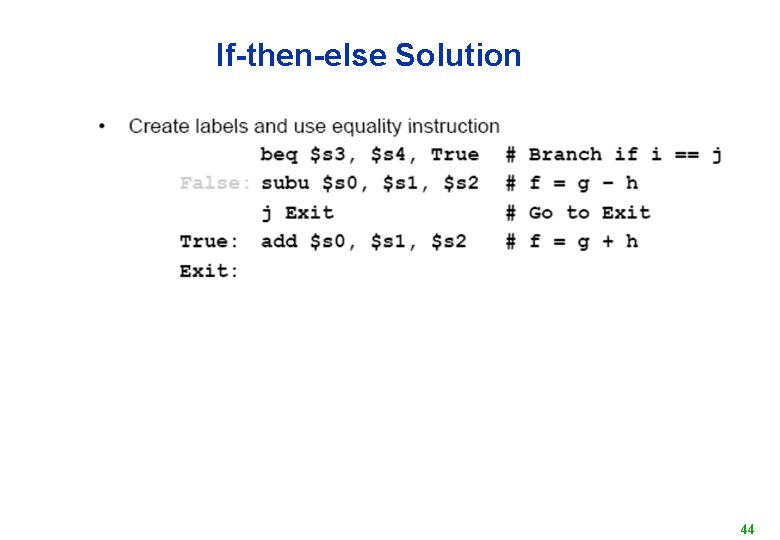

Other Comparisons • Other conditional arithmetic operators are useful in evaluating conditional < > <= expressions using <, >, <=, >= • Use compare instruction to “set” register to 1 when condition met • Consider the following C code if (f < g) goto Less; • Solution slt $t 0, $s 1 # $t 0 = 1 if $s 0 < $s 1 bne $t 0, $zero, Less # Goto Less if $t 0 != 0 45

MIPS Comparisons 46

C Example 47

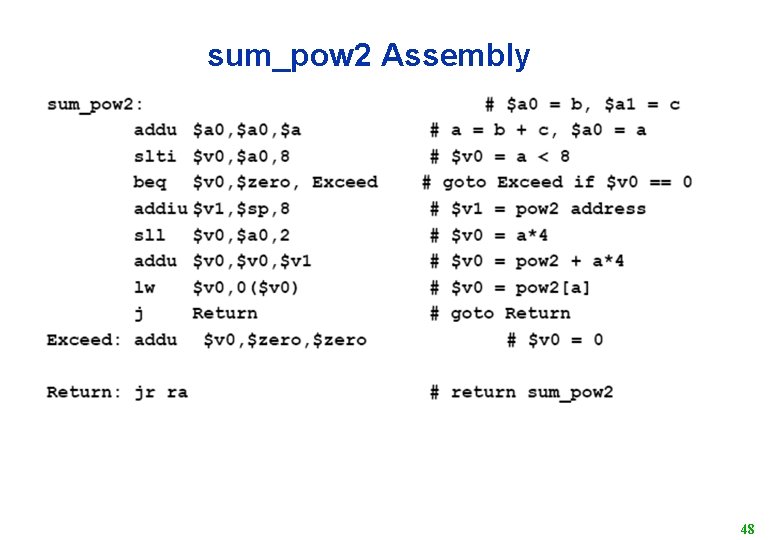

sum_pow 2 Assembly 48

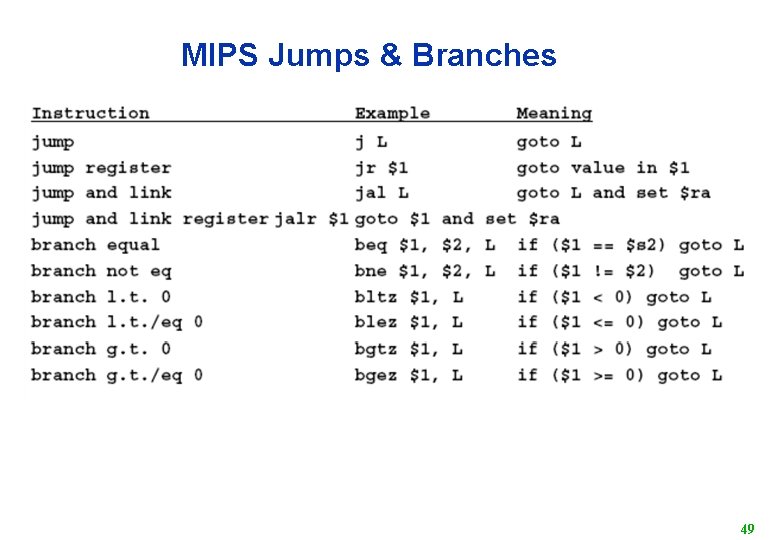

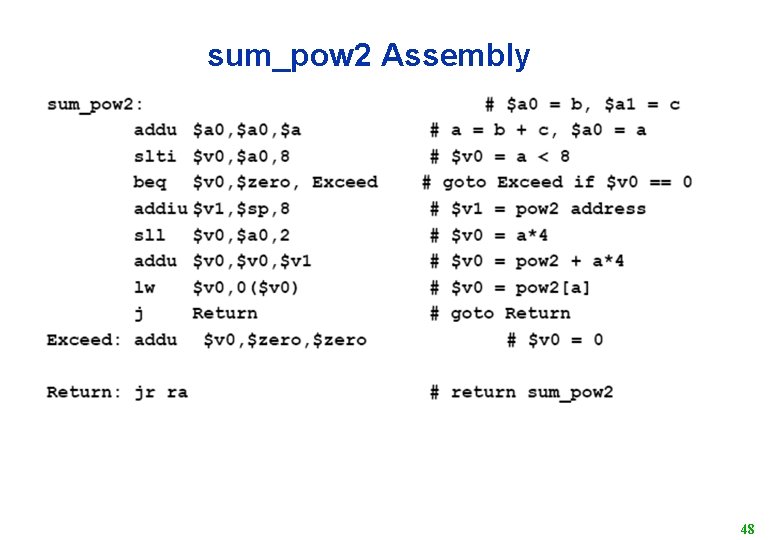

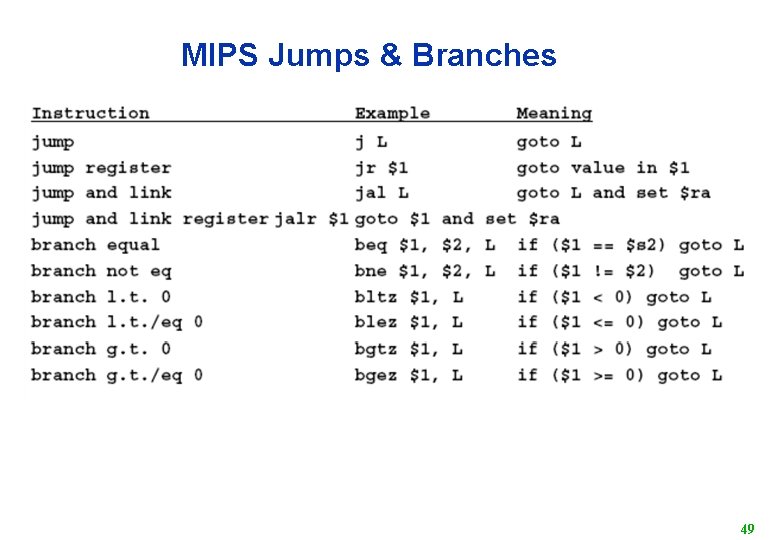

MIPS Jumps & Branches 49

Support for Simple Branches Only • Notice that there is no branch less than instruction for comparing two registers? – The reason is that such an instruction would be too complicated and might require a longer clock cycle time – Therefore, conditionals that do not compare against zero take at least two instructions where the first is a set and the second is a conditional branch • As we’ll see later, this is a design trade-off – Less time per instruction vs. fewer instructions • How do you decide what to do? – Other RISC ISAs made a different choice. 50

![While Loop in C Consider a while loop While Ai k i While Loop in C • Consider a while loop While (A[i] == k) i](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-51.jpg)

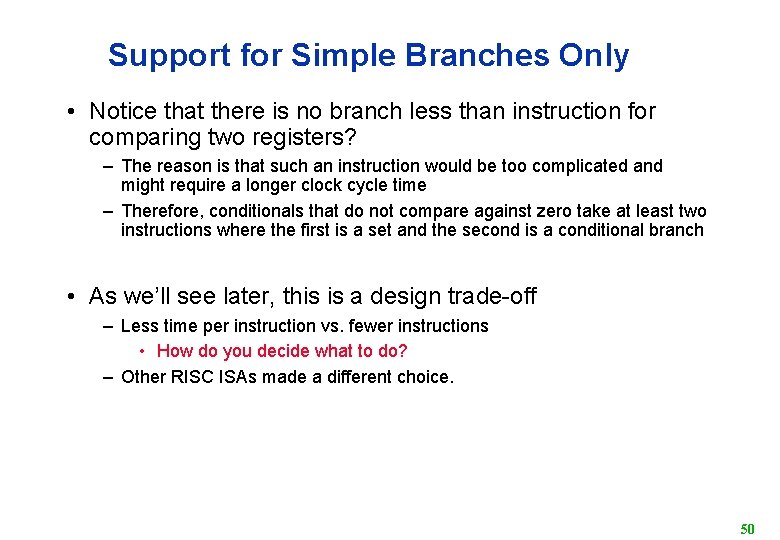

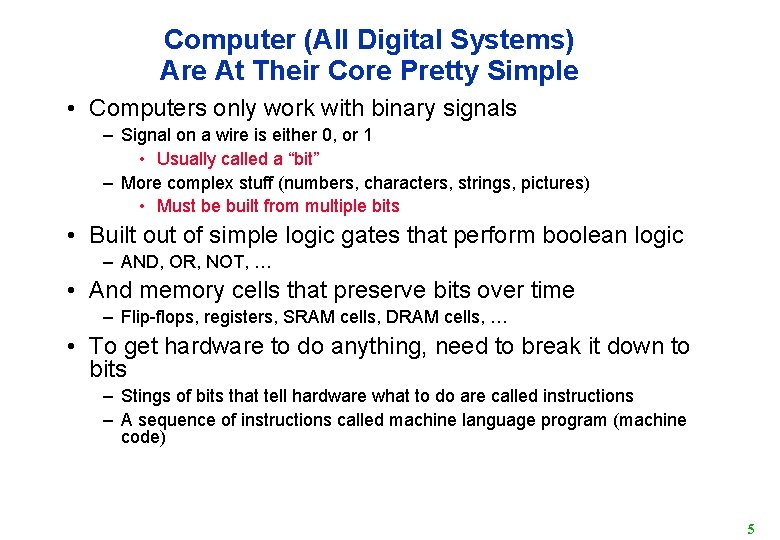

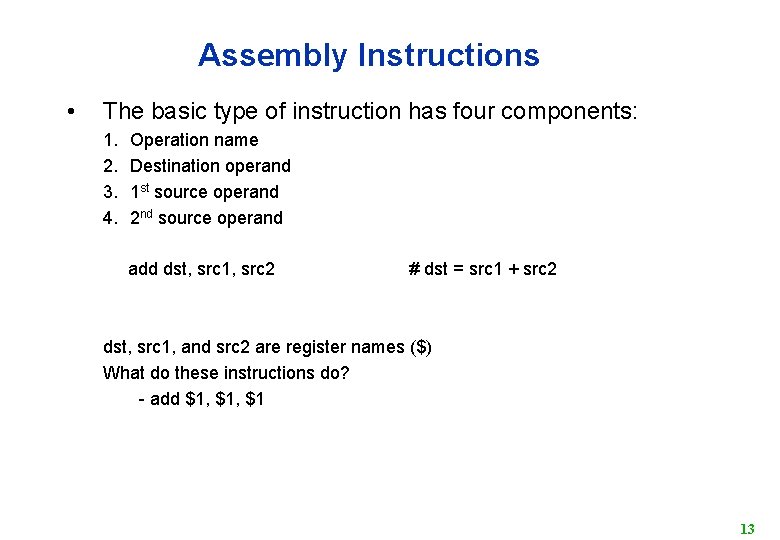

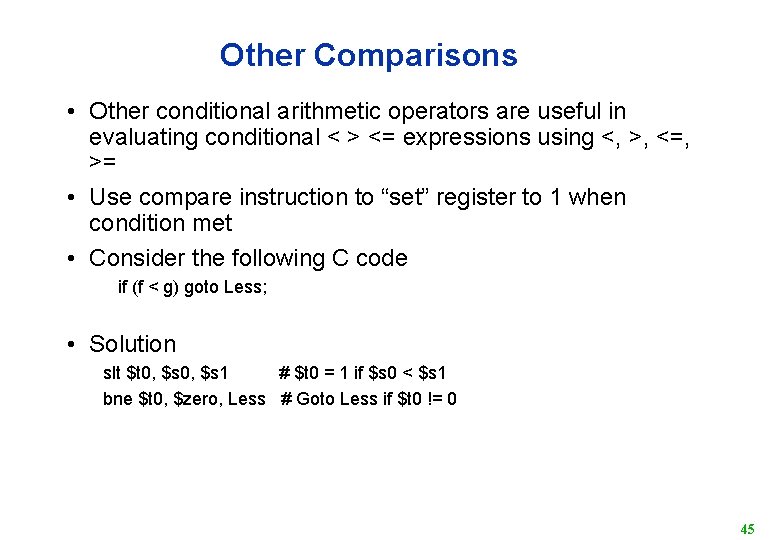

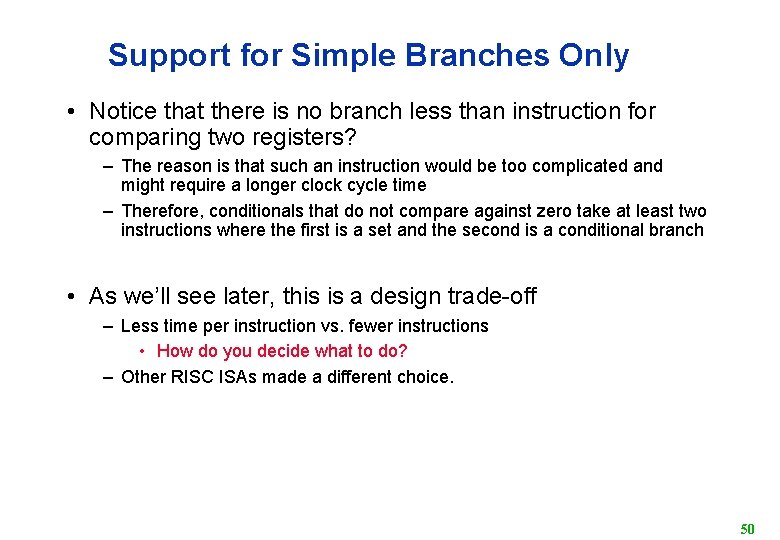

While Loop in C • Consider a while loop While (A[i] == k) i = i + j; Assembly loop Assume i = $s 0, j = $s 1, k = $s 2 Loop: sll $t 0, $s 0, 2 #$t 0 = 4 *i addu $t 1, $t 0, $s 3 # $t 1 = &(A[i]) lw $t 2, 0($t 1) # $t 2 = A[i] bne $t 2, $s 2, Exit # goto Exit if != addu $s 0, $s 1 # i = i + j j Loop # goto Loop Exit Basic Block Maximal sequence of instructions with out branches or branch targets 51

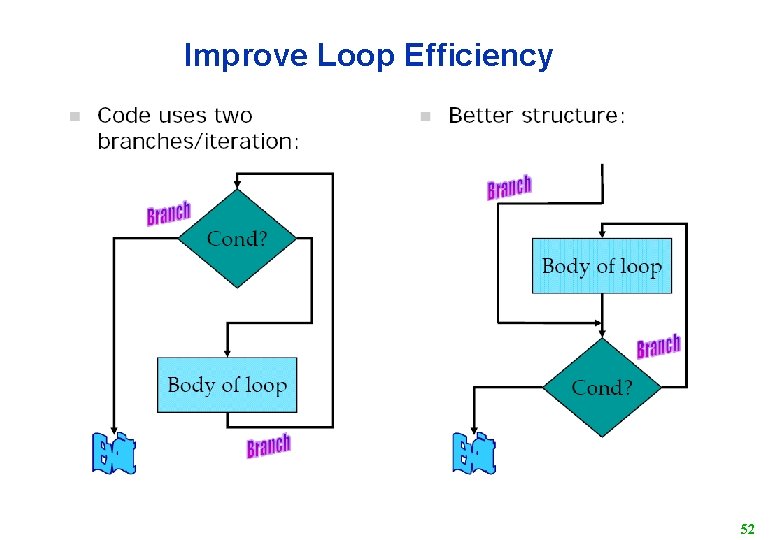

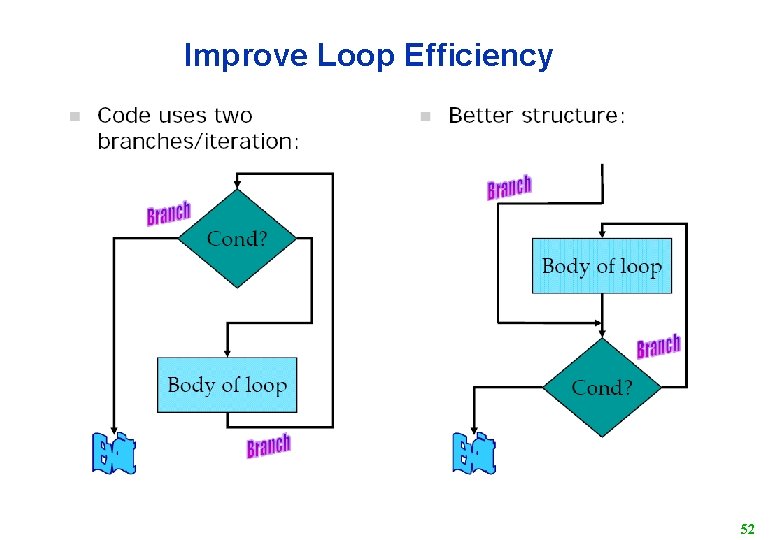

Improve Loop Efficiency 52

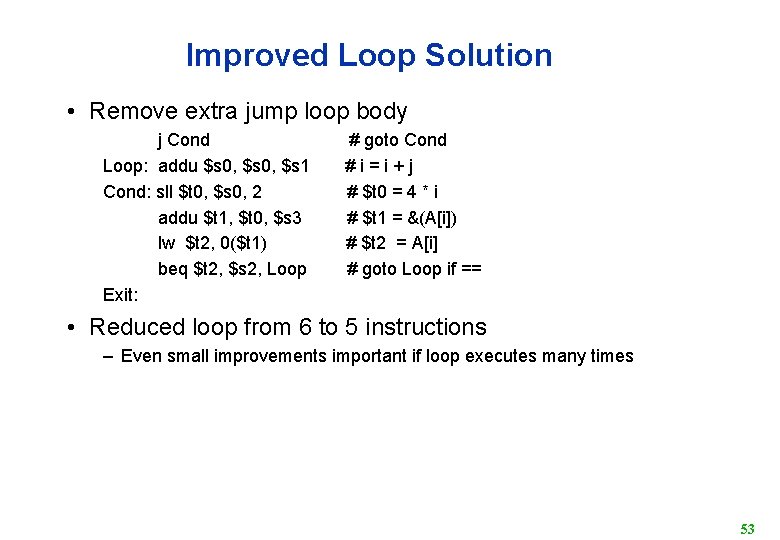

Improved Loop Solution • Remove extra jump loop body j Cond # goto Cond Loop: addu $s 0, $s 1 # i = i + j Cond: sll $t 0, $s 0, 2 # $t 0 = 4 * i addu $t 1, $t 0, $s 3 # $t 1 = &(A[i]) lw $t 2, 0($t 1) # $t 2 = A[i] beq $t 2, $s 2, Loop # goto Loop if == Exit: • Reduced loop from 6 to 5 instructions – Even small improvements important if loop executes many times 53

Machine Language Representation • Instructions are represented as binary data in memory – Stored program – Von Neumann • Simplicity • One memory system • Same addresses used for branches, procedures, data, etc. • The only difference is how bits are interpreted • What are the risks of this decision? • Binary compatibility (backwards) – Commercial software relies on ability to work on next generation hardware – This leads to very long life for an ISA 54

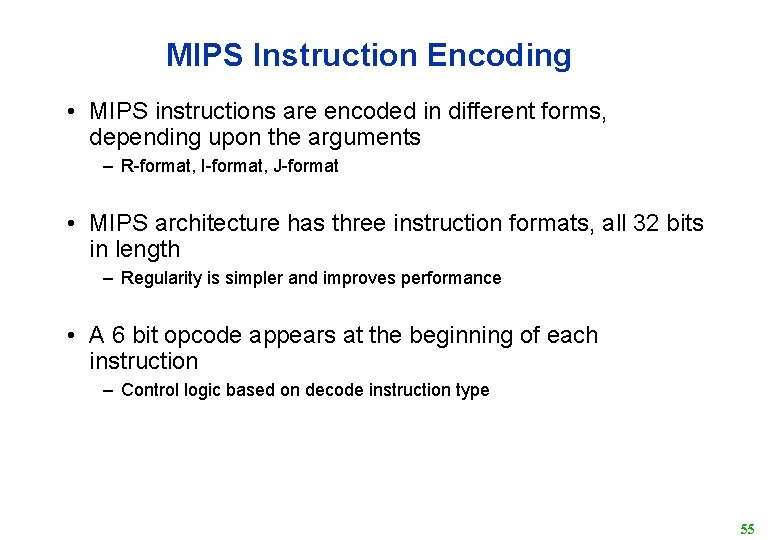

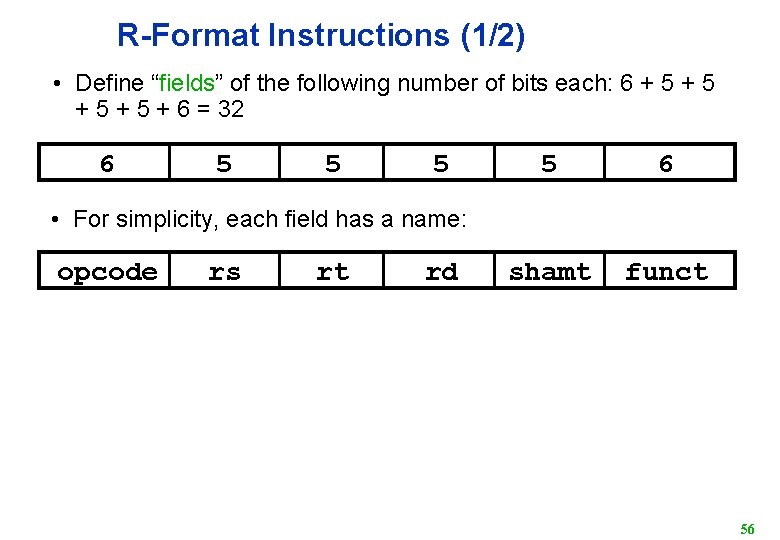

MIPS Instruction Encoding • MIPS instructions are encoded in different forms, depending upon the arguments – R-format, I-format, J-format • MIPS architecture has three instruction formats, all 32 bits in length – Regularity is simpler and improves performance • A 6 bit opcode appears at the beginning of each instruction – Control logic based on decode instruction type 55

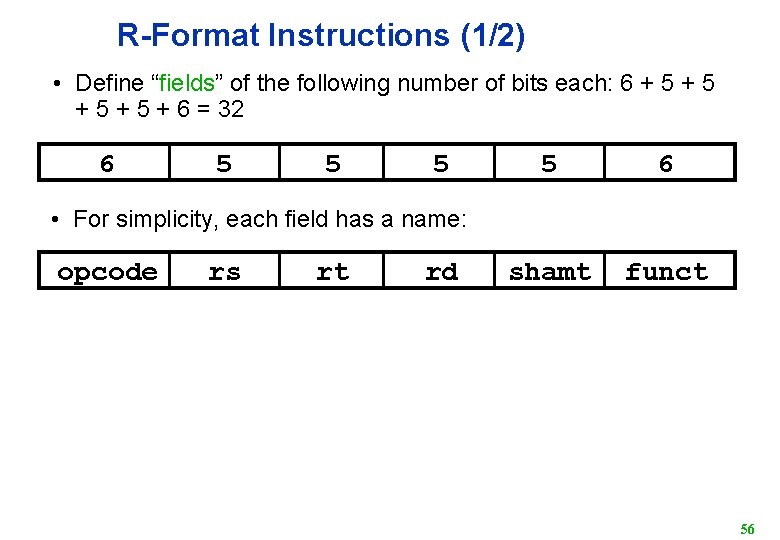

R-Format Instructions (1/2) • Define “fields” of the following number of bits each: 6 + 5 + 5 + 6 = 32 6 5 5 6 shamt funct • For simplicity, each field has a name: opcode rs rt rd 56

R-Format Instructions (2/2) • More fields: – rs (Source Register): generally used to specify register containing first operand – rt (Target Register): generally used to specify register containing second operand (note that name is misleading) – rd (Destination Register): generally used to specify register which will receive result of computation 57

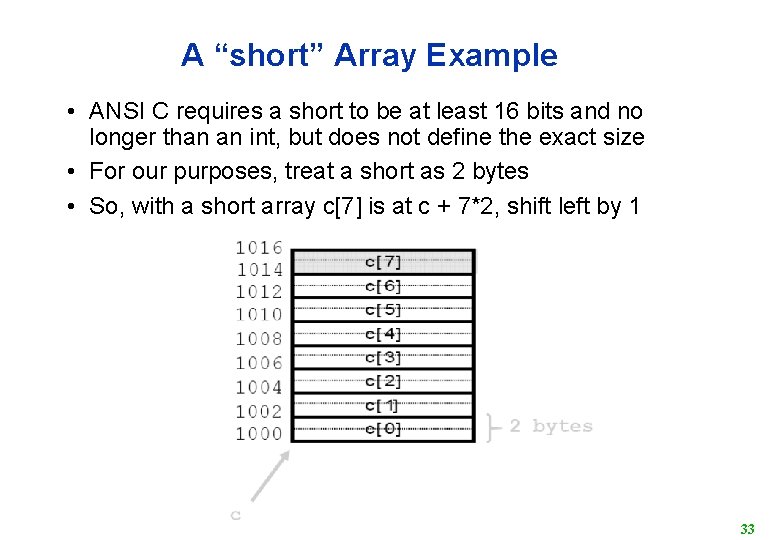

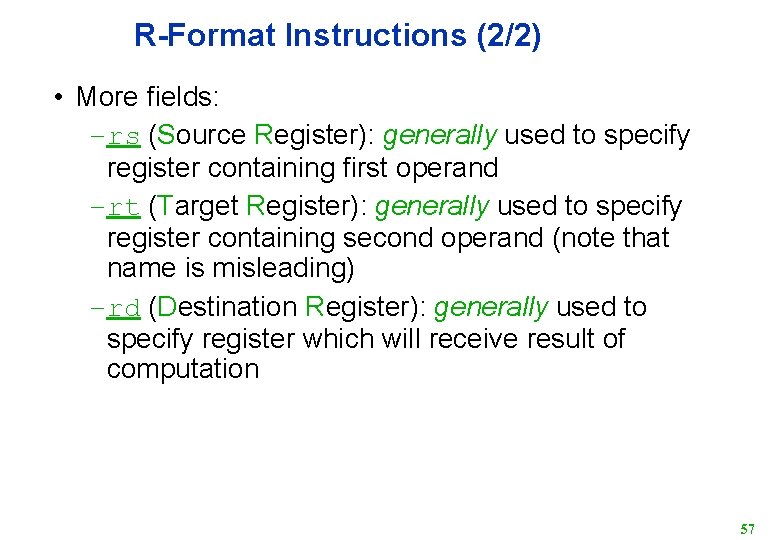

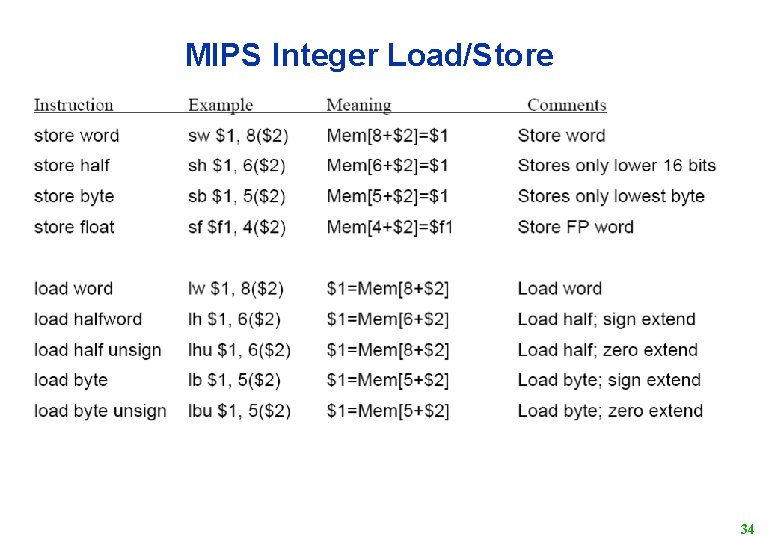

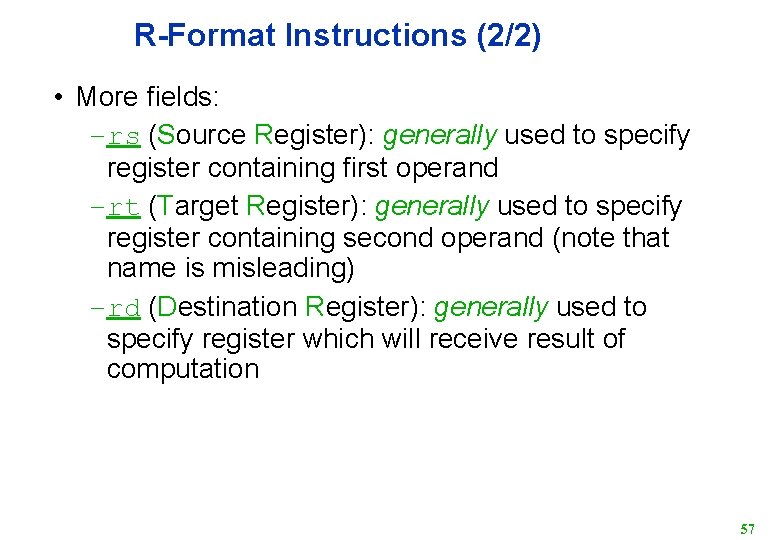

J-Format Instructions (1/2) • Define “fields” of the following number of bits each: 6 bits 26 bits • As usual, each field has a name: opcode target address • Key Concepts – Keep opcode field identical to R-format and I-format for consistency. – Combine all other fields to make room for large target address. 58

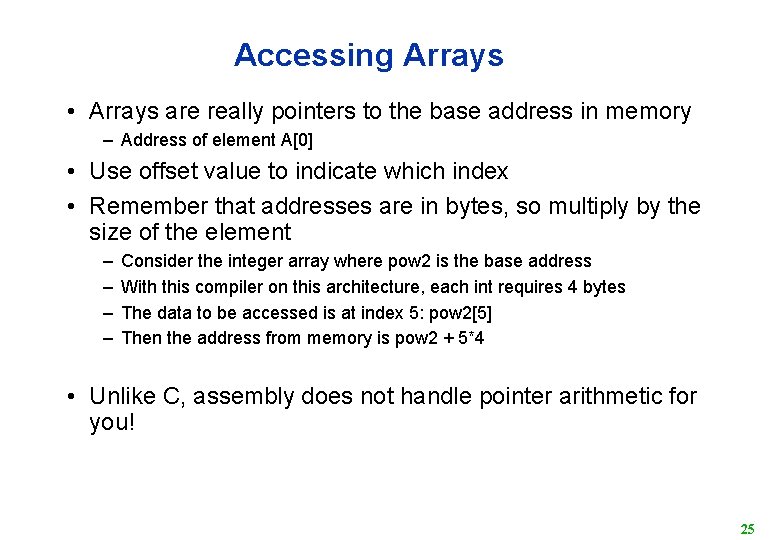

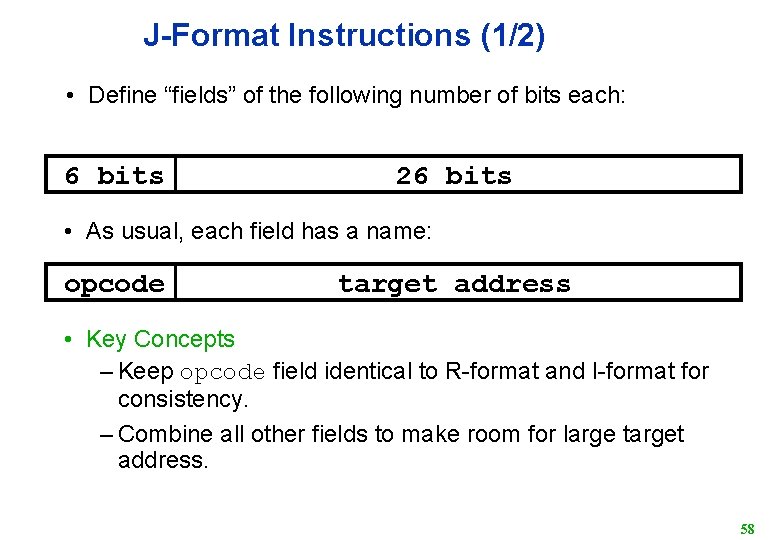

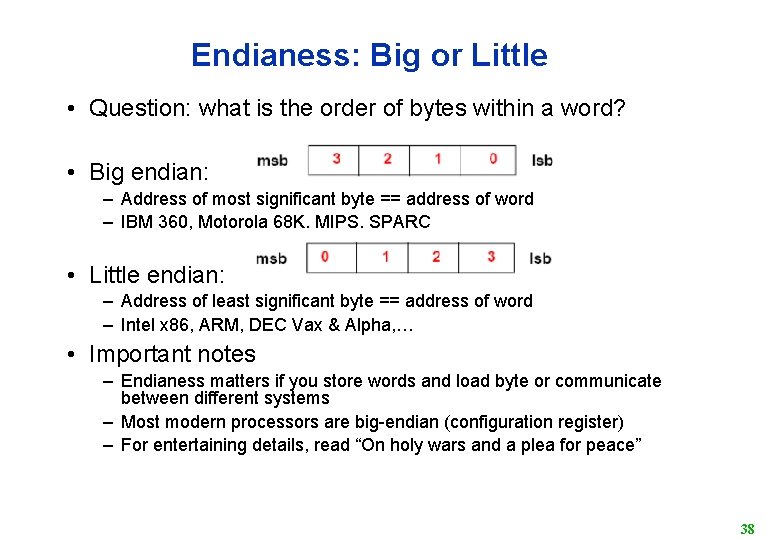

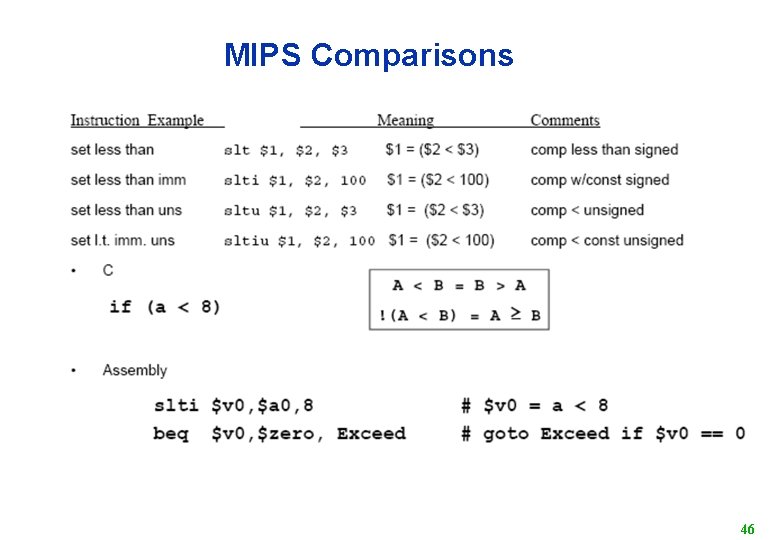

![JFormat Instructions 22 Summary New PC PC31 28 target J-Format Instructions (2/2) • Summary: – New PC = { PC[31. . 28], target](https://slidetodoc.com/presentation_image/111d82608a5dacd2c6467f9ba5474f91/image-59.jpg)

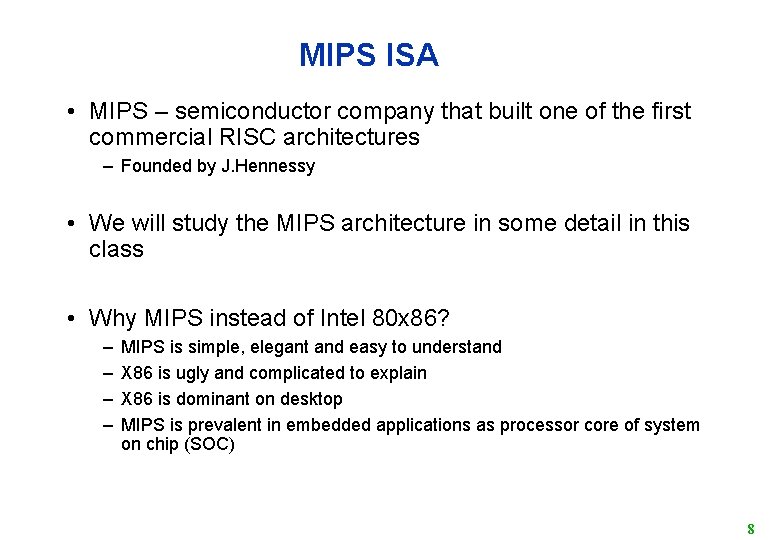

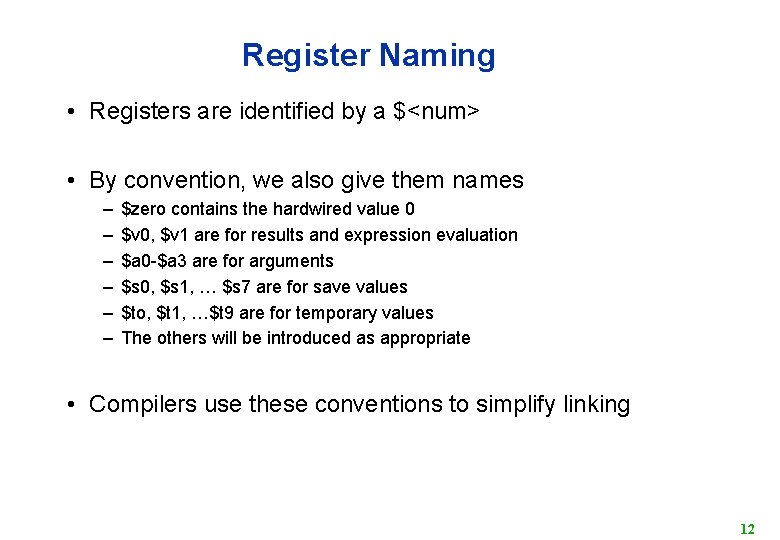

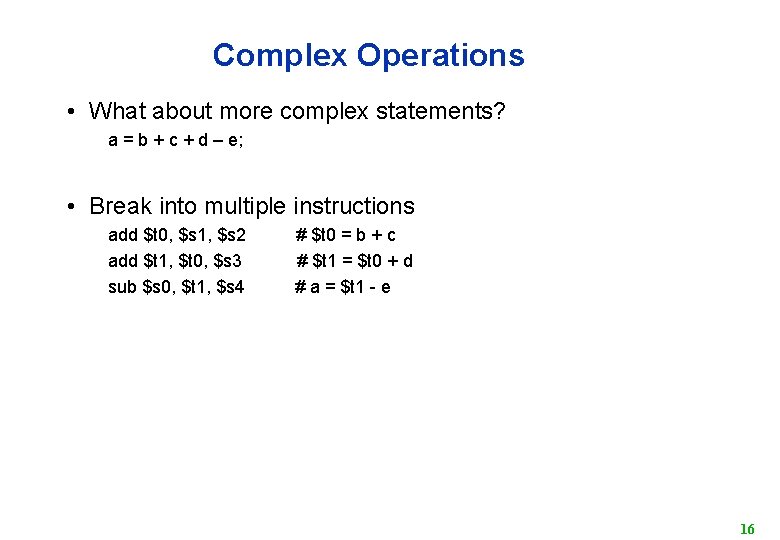

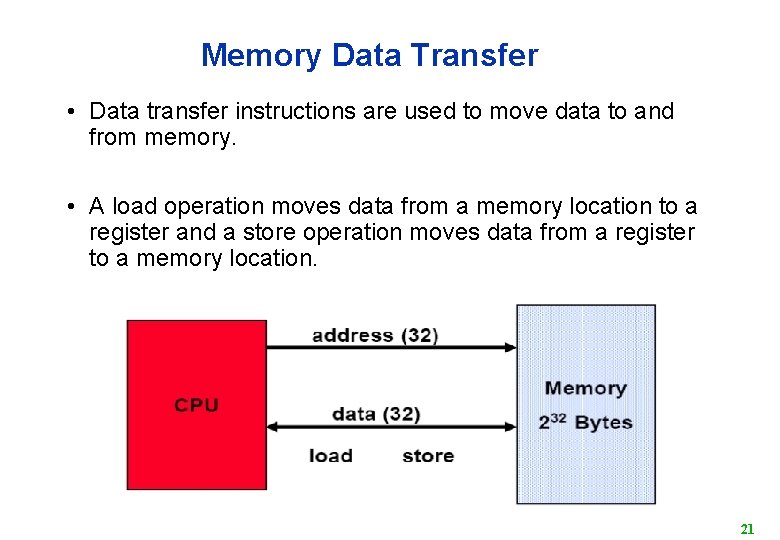

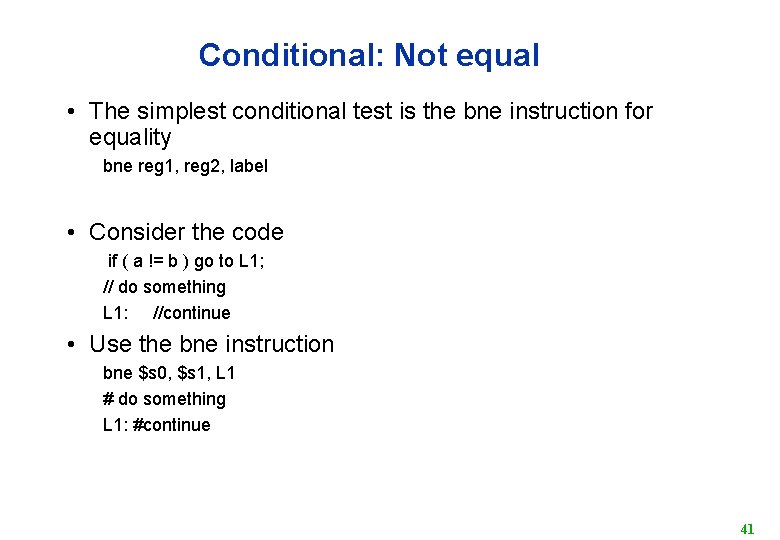

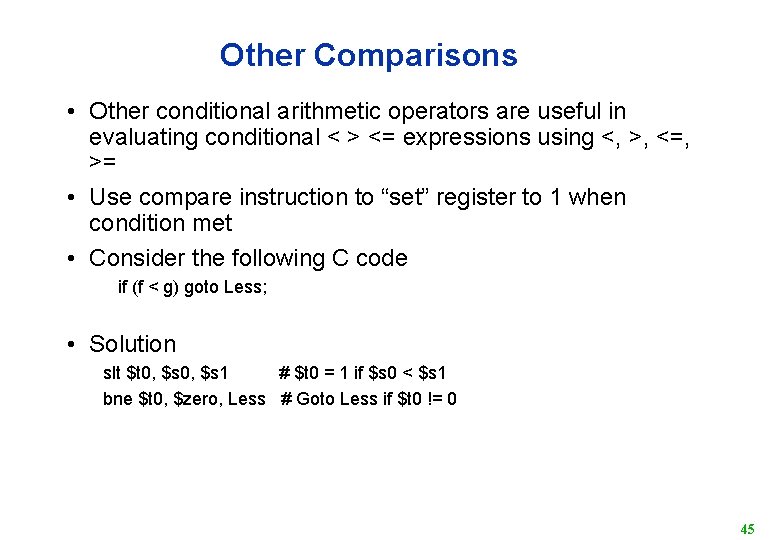

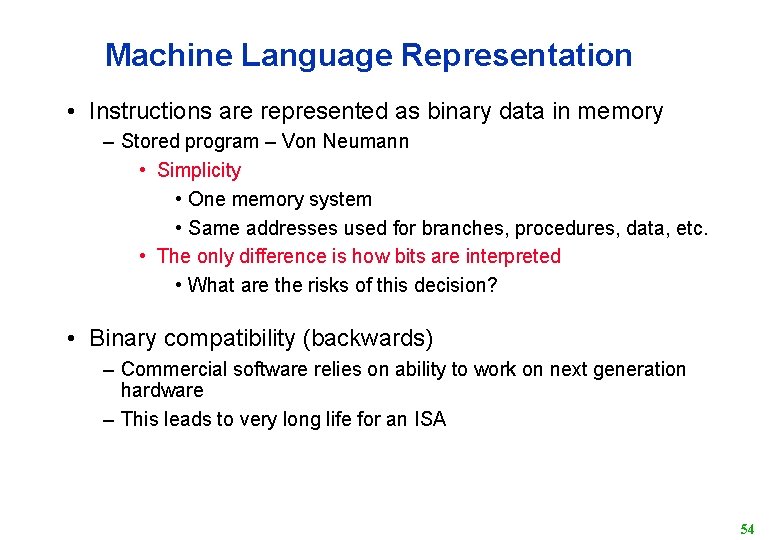

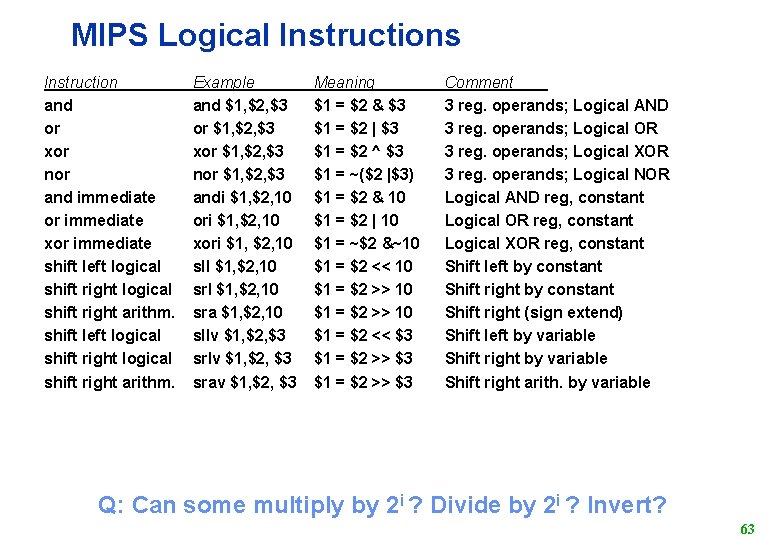

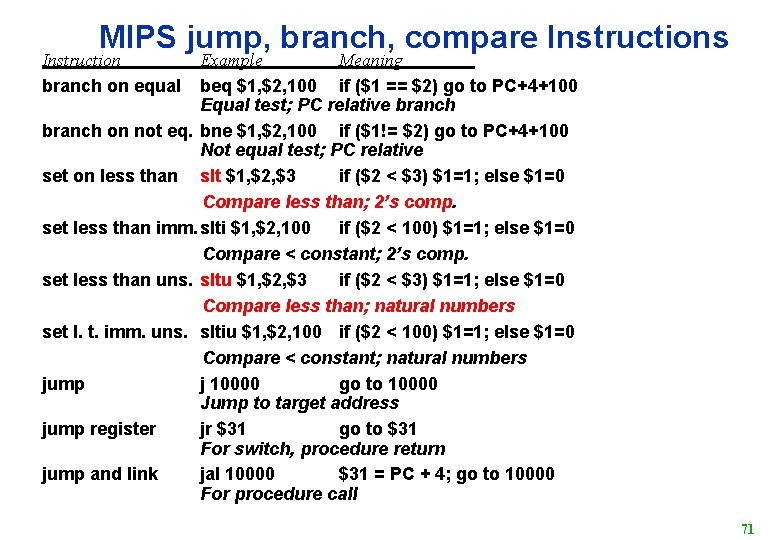

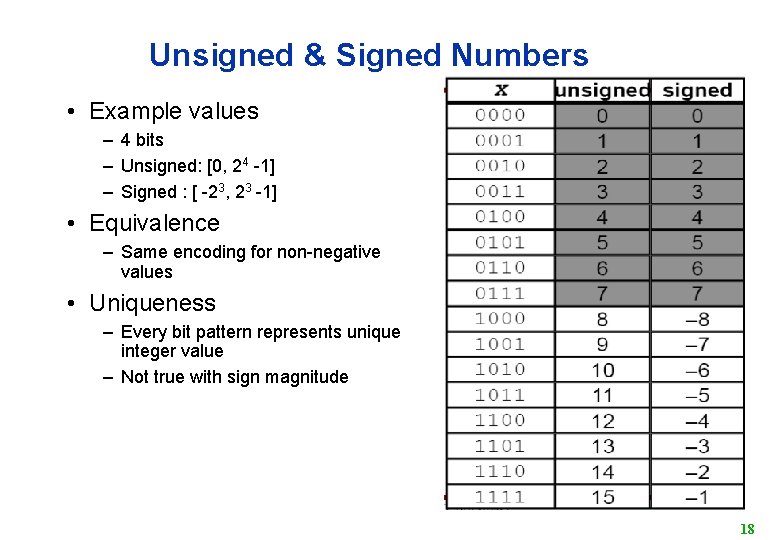

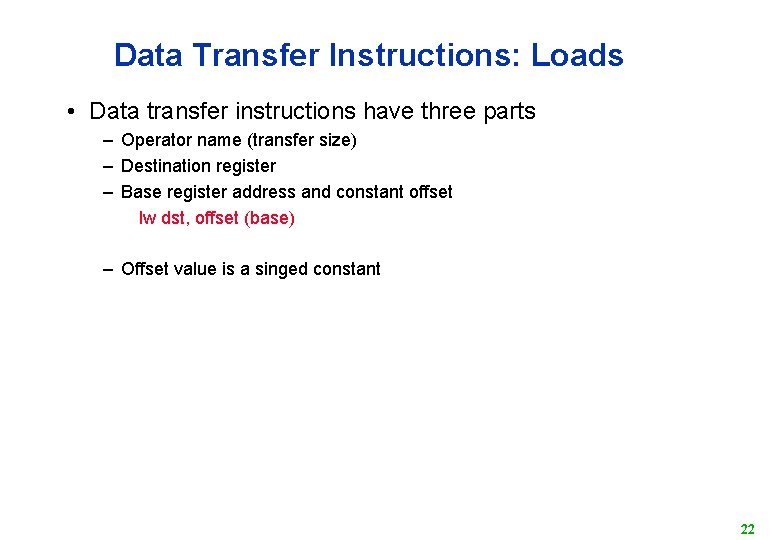

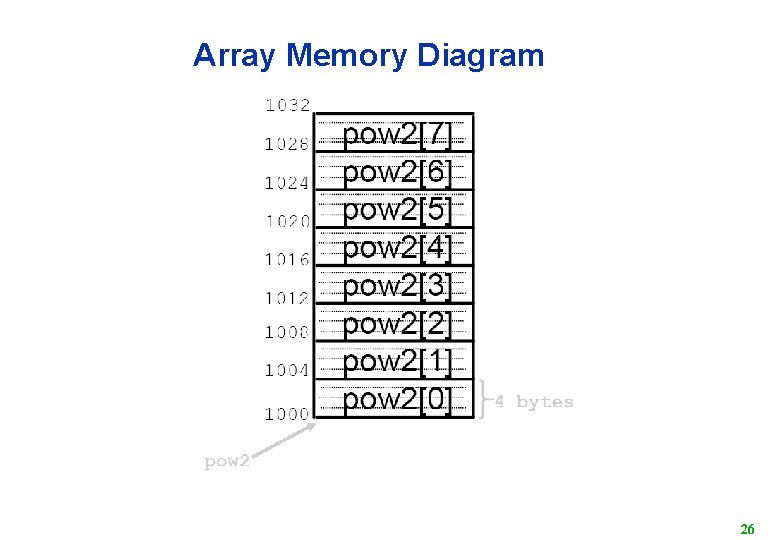

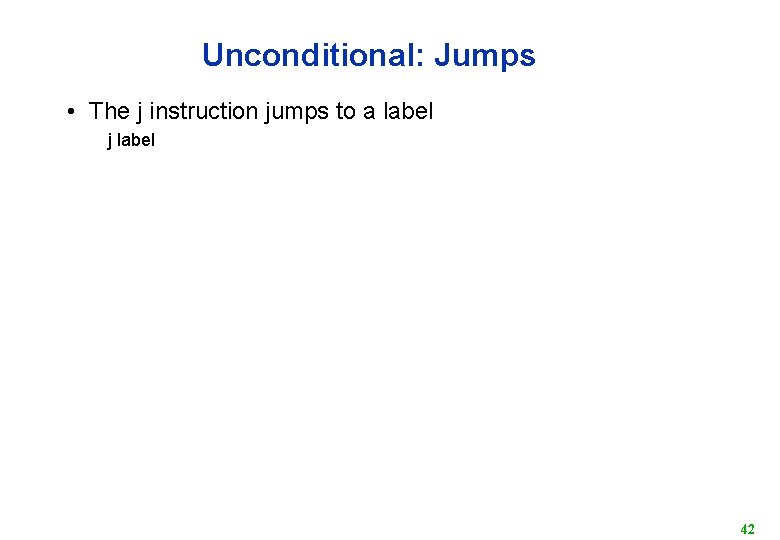

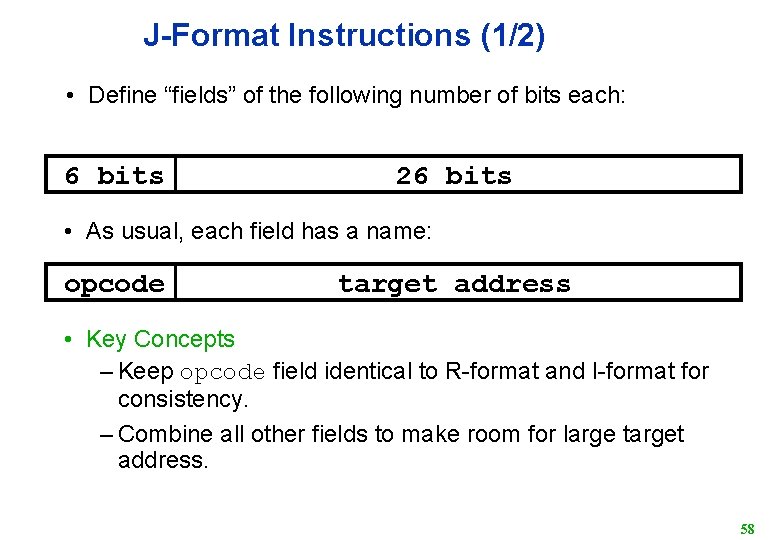

J-Format Instructions (2/2) • Summary: – New PC = { PC[31. . 28], target address, 00 } • Understand where each part came from! • Note: In Verilog, { , , } means concatenation { 4 bits , 26 bits , 2 bits } = 32 bit address – { 1010, 1111111111111, 00 } = 1010111111111111100 – We use Verilog in this class 59

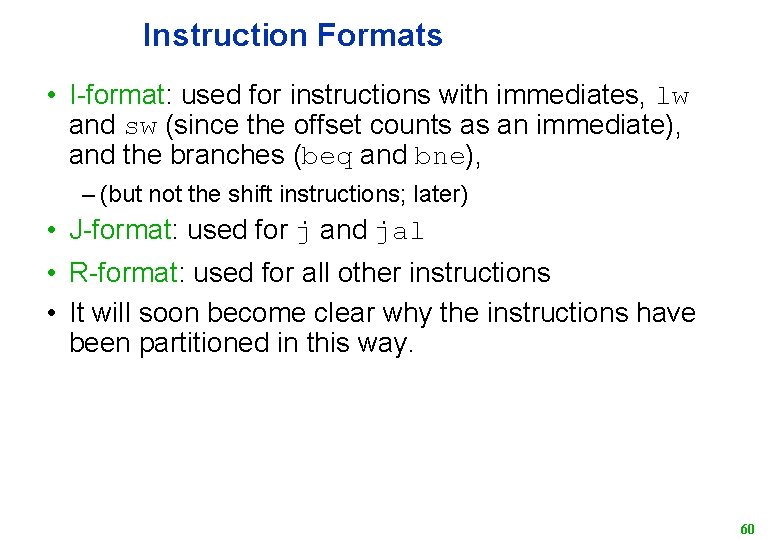

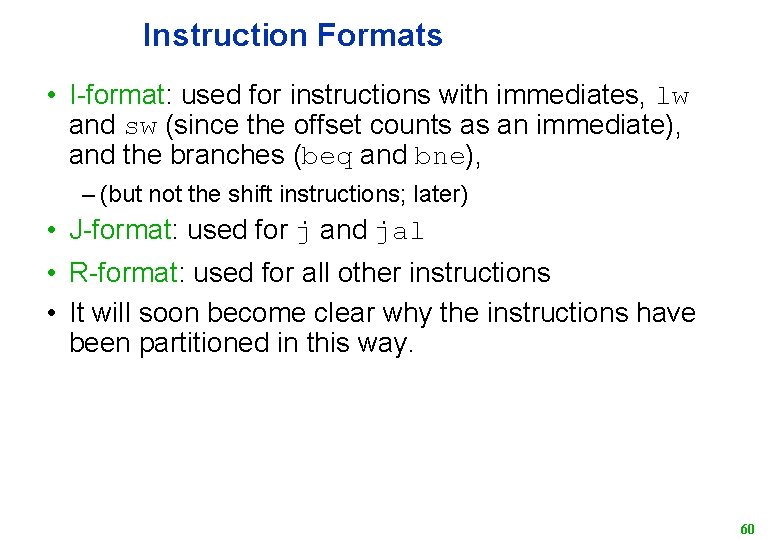

Instruction Formats • I-format: used for instructions with immediates, lw and sw (since the offset counts as an immediate), and the branches (beq and bne), – (but not the shift instructions; later) • J-format: used for j and jal • R-format: used for all other instructions • It will soon become clear why the instructions have been partitioned in this way. 60

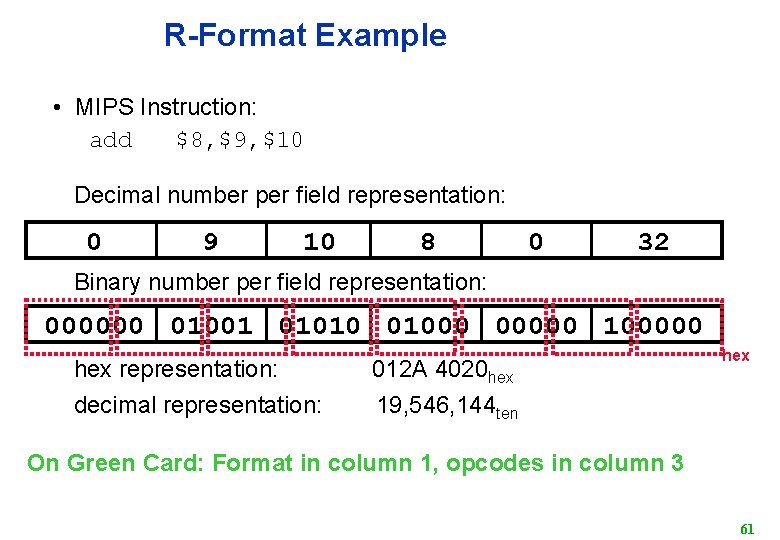

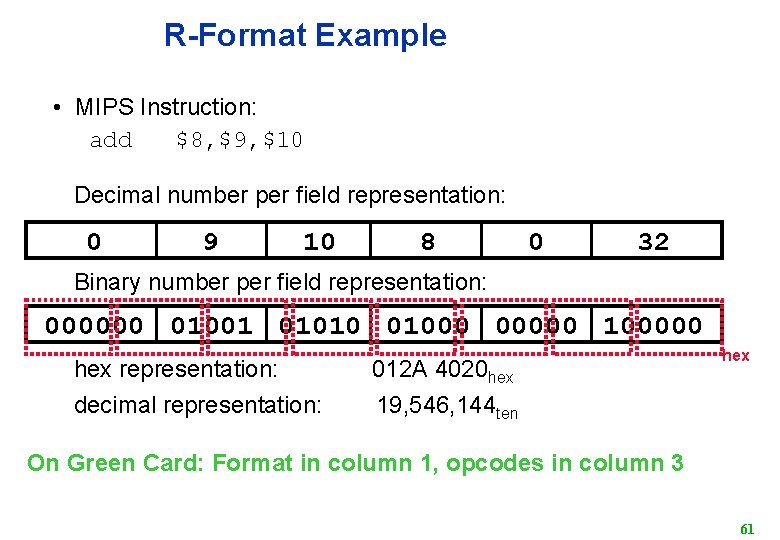

R-Format Example • MIPS Instruction: add $8, $9, $10 Decimal number per field representation: 0 9 10 8 0 32 Binary number per field representation: 000000 01001 01010 01000 00000 100000 hex representation: 012 A 4020 hex decimal representation: 19, 546, 144 ten hex On Green Card: Format in column 1, opcodes in column 3 61

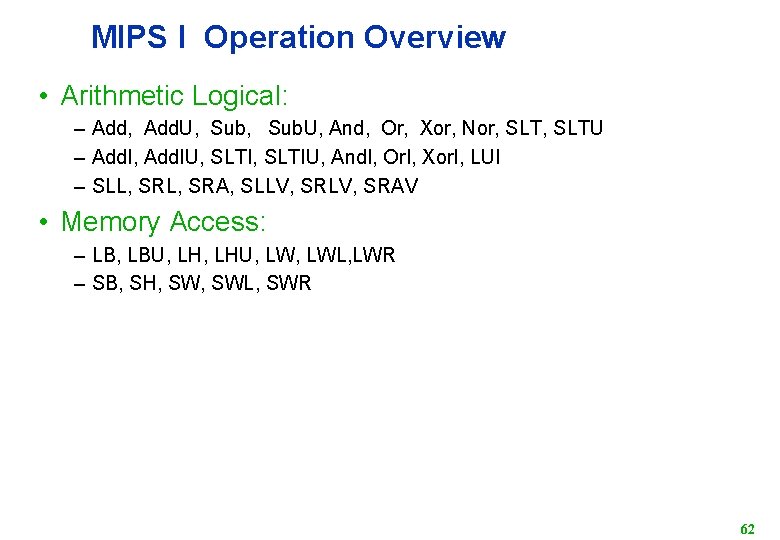

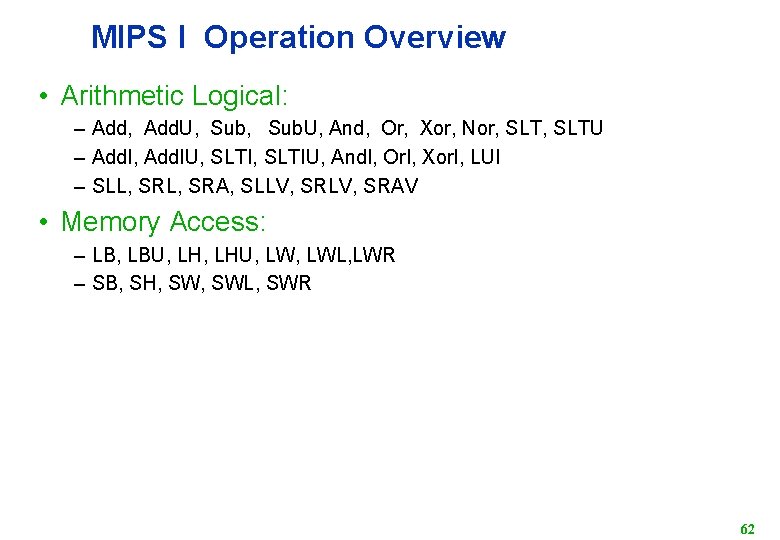

MIPS I Operation Overview • Arithmetic Logical: – Add, Add. U, Sub. U, And, Or, Xor, Nor, SLTU – Add. I, Add. IU, SLTIU, And. I, Or. I, Xor. I, LUI – SLL, SRA, SLLV, SRAV • Memory Access: – LB, LBU, LHU, LWL, LWR – SB, SH, SWL, SWR 62

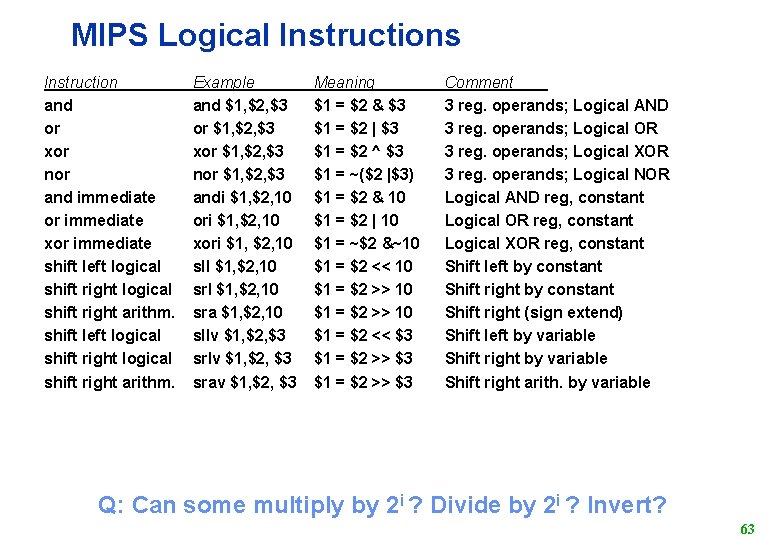

MIPS Logical Instructions Instruction and or xor nor and immediate or immediate xor immediate shift left logical shift right arithm. Example and $1, $2, $3 or $1, $2, $3 xor $1, $2, $3 nor $1, $2, $3 andi $1, $2, 10 ori $1, $2, 10 xori $1, $2, 10 sll $1, $2, 10 sra $1, $2, 10 sllv $1, $2, $3 srav $1, $2, $3 Meaning $1 = $2 & $3 $1 = $2 | $3 $1 = $2 ^ $3 $1 = ~($2 |$3) $1 = $2 & 10 $1 = $2 | 10 $1 = ~$2 &~10 $1 = $2 << 10 $1 = $2 >> 10 $1 = $2 << $3 $1 = $2 >> $3 Comment 3 reg. operands; Logical AND 3 reg. operands; Logical OR 3 reg. operands; Logical XOR 3 reg. operands; Logical NOR Logical AND reg, constant Logical OR reg, constant Logical XOR reg, constant Shift left by constant Shift right (sign extend) Shift left by variable Shift right arith. by variable Q: Can some multiply by 2 i ? Divide by 2 i ? Invert? 63

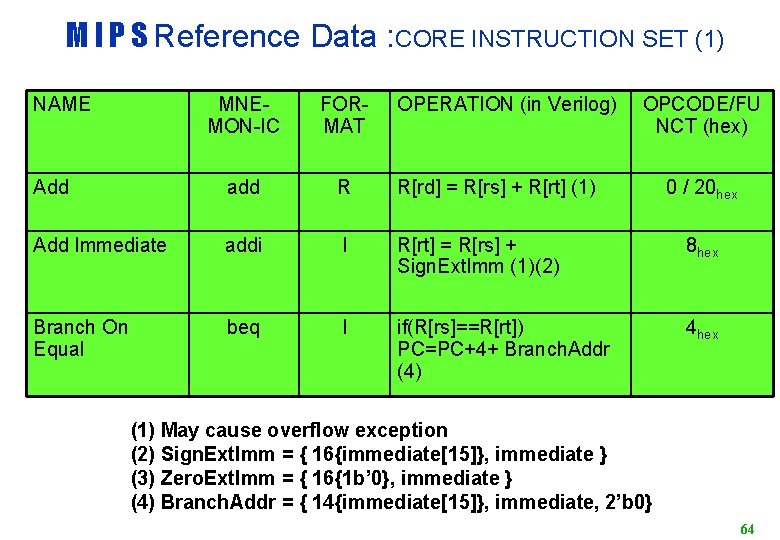

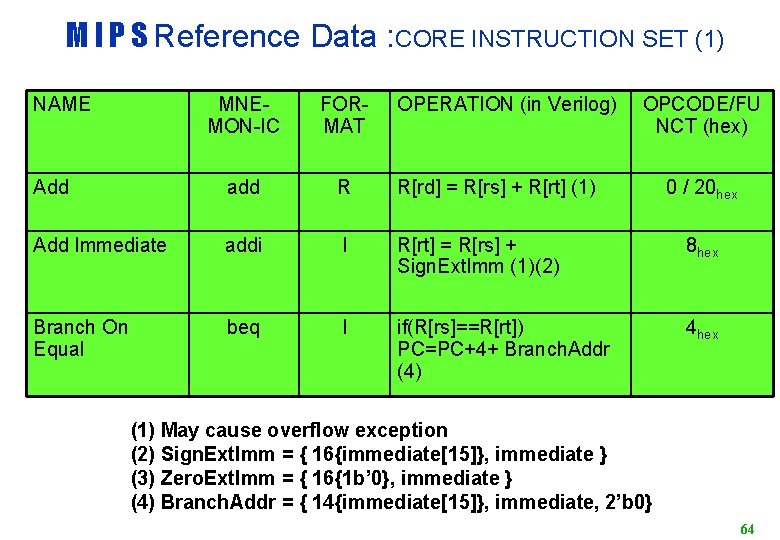

M I P S Reference Data : CORE INSTRUCTION SET (1) NAME MNEMON-IC FORMAT OPERATION (in Verilog) OPCODE/FU NCT (hex) Add add R R[rd] = R[rs] + R[rt] (1) Add Immediate addi I R[rt] = R[rs] + Sign. Ext. Imm (1)(2) 8 hex Branch On Equal beq I if(R[rs]==R[rt]) PC=PC+4+ Branch. Addr (4) 4 hex 0 / 20 hex (1) May cause overflow exception (2) Sign. Ext. Imm = { 16{immediate[15]}, immediate } (3) Zero. Ext. Imm = { 16{1 b’ 0}, immediate } (4) Branch. Addr = { 14{immediate[15]}, immediate, 2’b 0} 64

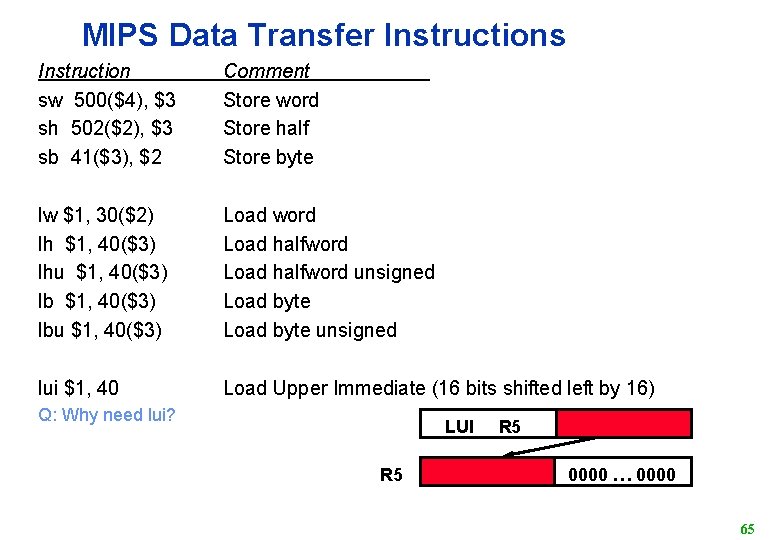

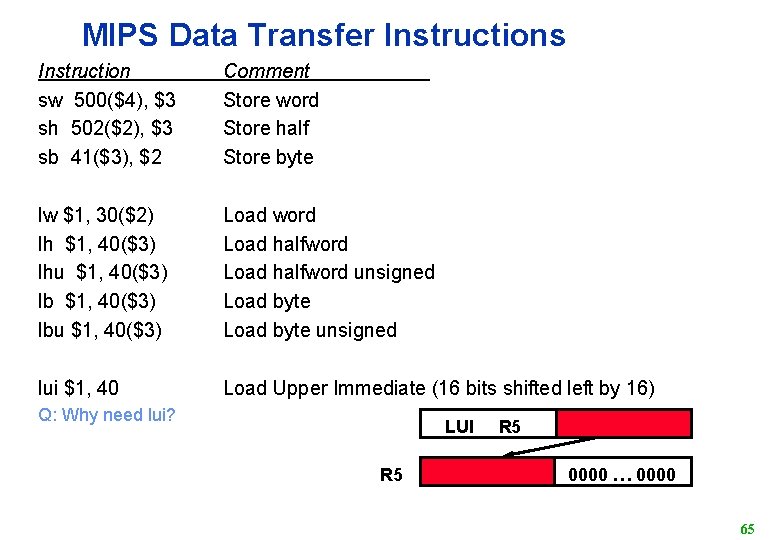

MIPS Data Transfer Instructions Instruction sw 500($4), $3 sh 502($2), $3 sb 41($3), $2 Comment Store word Store half Store byte lw $1, 30($2) lh $1, 40($3) lhu $1, 40($3) lbu $1, 40($3) Load word Load halfword unsigned Load byte unsigned lui $1, 40 Load Upper Immediate (16 bits shifted left by 16) Q: Why need lui? LUI R 5 0000 … 0000 65

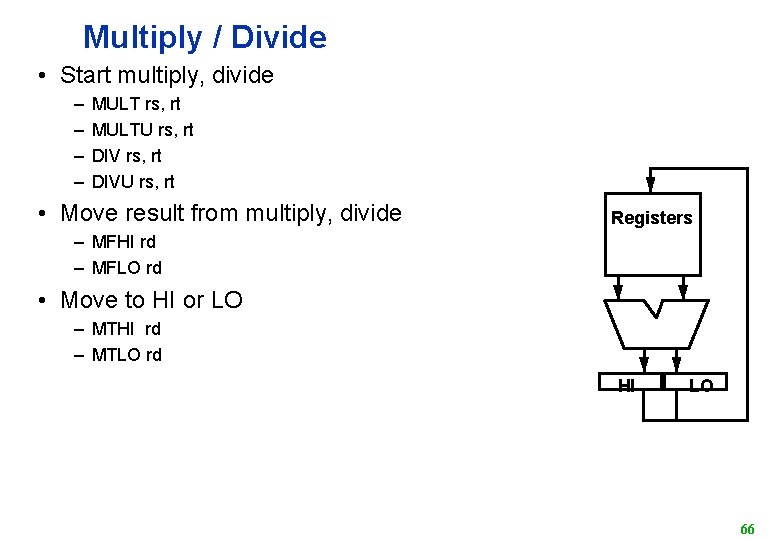

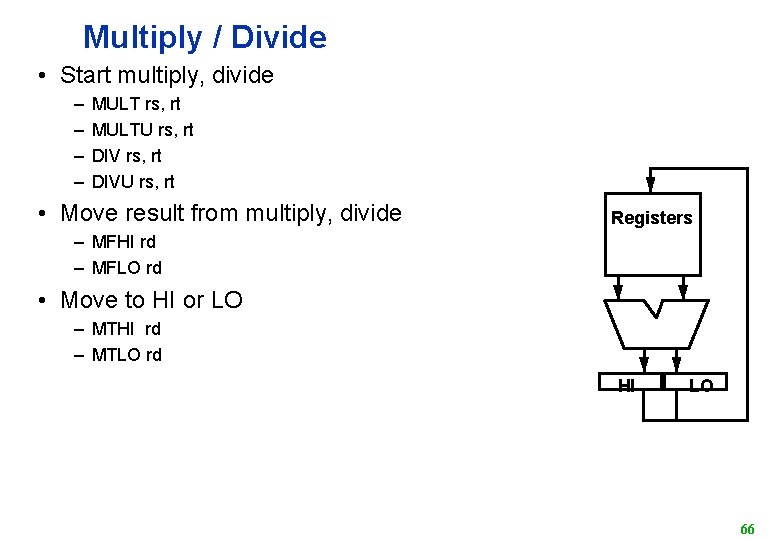

Multiply / Divide • Start multiply, divide – – MULT rs, rt MULTU rs, rt DIVU rs, rt • Move result from multiply, divide Registers – MFHI rd – MFLO rd • Move to HI or LO – MTHI rd – MTLO rd HI LO 66

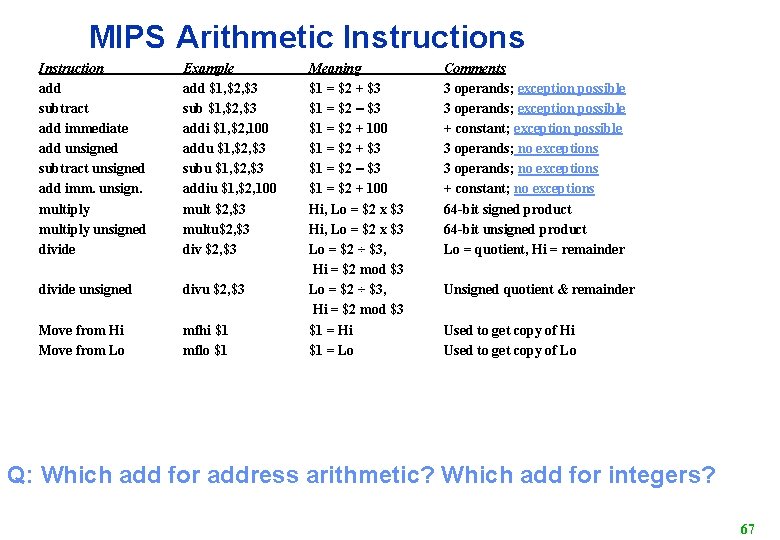

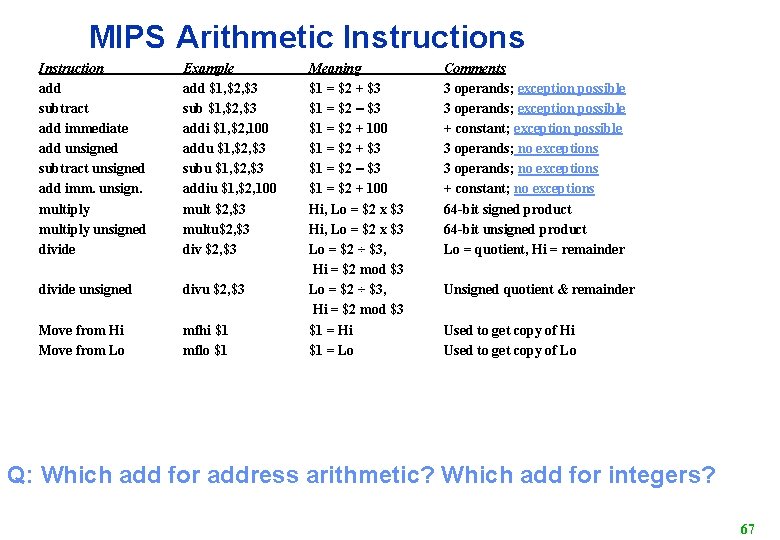

MIPS Arithmetic Instructions Instruction add subtract add immediate add unsigned subtract unsigned add imm. unsign. multiply unsigned divide Example add $1, $2, $3 sub $1, $2, $3 addi $1, $2, 100 addu $1, $2, $3 subu $1, $2, $3 addiu $1, $2, 100 mult $2, $3 multu$2, $3 divide unsigned divu $2, $3 Move from Hi Move from Lo mfhi $1 mflo $1 Meaning $1 = $2 + $3 $1 = $2 – $3 $1 = $2 + 100 Hi, Lo = $2 x $3 Lo = $2 ÷ $3, Hi = $2 mod $3 $1 = Hi $1 = Lo Comments 3 operands; exception possible + constant; exception possible 3 operands; no exceptions + constant; no exceptions 64 -bit signed product 64 -bit unsigned product Lo = quotient, Hi = remainder Unsigned quotient & remainder Used to get copy of Hi Used to get copy of Lo Q: Which add for address arithmetic? Which add for integers? 67

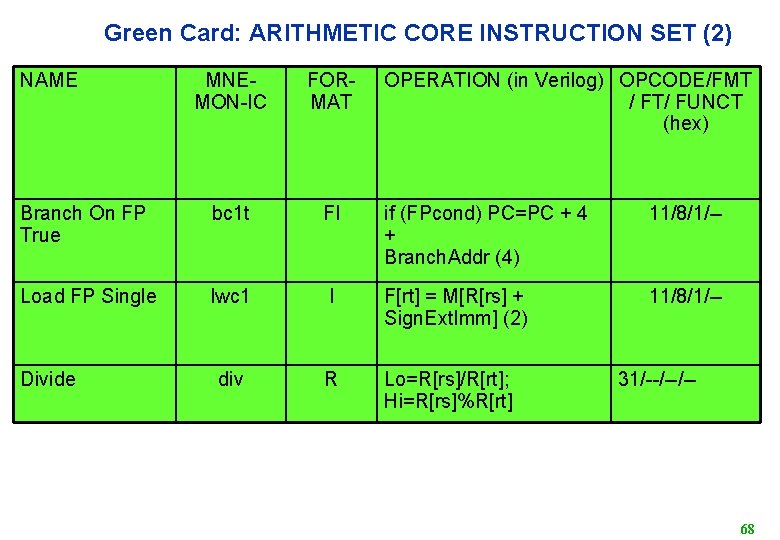

Green Card: ARITHMETIC CORE INSTRUCTION SET (2) NAME MNEMON-IC FORMAT Branch On FP True bc 1 t FI Load FP Single lwc 1 div Divide OPERATION (in Verilog) OPCODE/FMT / FT/ FUNCT (hex) if (FPcond) PC=PC + 4 + Branch. Addr (4) 11/8/1/-- I F[rt] = M[R[rs] + Sign. Ext. Imm] (2) 11/8/1/-- R Lo=R[rs]/R[rt]; Hi=R[rs]%R[rt] 31/--/--/-- 68

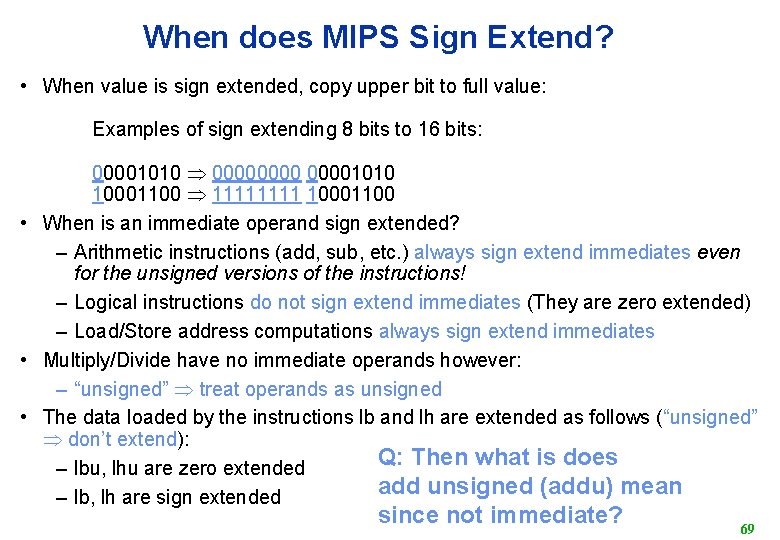

When does MIPS Sign Extend? • When value is sign extended, copy upper bit to full value: Examples of sign extending 8 bits to 16 bits: 00001010 00001010 10001100 1111 10001100 • When is an immediate operand sign extended? – Arithmetic instructions (add, sub, etc. ) always sign extend immediates even for the unsigned versions of the instructions! – Logical instructions do not sign extend immediates (They are zero extended) – Load/Store address computations always sign extend immediates • Multiply/Divide have no immediate operands however: – “unsigned” treat operands as unsigned • The data loaded by the instructions lb and lh are extended as follows (“unsigned” don’t extend): Q: Then what is does – lbu, lhu are zero extended add unsigned (addu) mean – lb, lh are sign extended since not immediate? 69

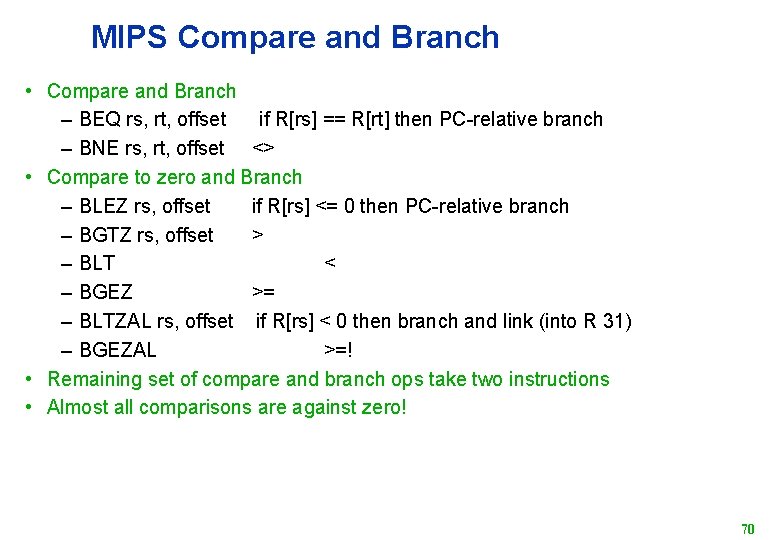

MIPS Compare and Branch • Compare and Branch – BEQ rs, rt, offset if R[rs] == R[rt] then PC-relative branch – BNE rs, rt, offset <> • Compare to zero and Branch – BLEZ rs, offset if R[rs] <= 0 then PC-relative branch – BGTZ rs, offset > – BLT < – BGEZ >= – BLTZAL rs, offset if R[rs] < 0 then branch and link (into R 31) – BGEZAL >=! • Remaining set of compare and branch ops take two instructions • Almost all comparisons are against zero! 70

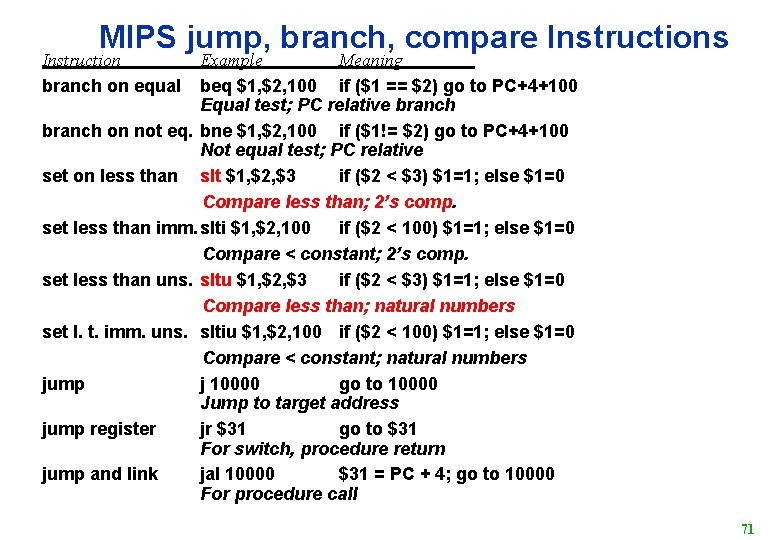

MIPS jump, branch, compare Instructions Instruction branch on equal Example Meaning beq $1, $2, 100 if ($1 == $2) go to PC+4+100 Equal test; PC relative branch on not eq. bne $1, $2, 100 if ($1!= $2) go to PC+4+100 Not equal test; PC relative set on less than slt $1, $2, $3 if ($2 < $3) $1=1; else $1=0 Compare less than; 2’s comp. set less than imm. slti $1, $2, 100 if ($2 < 100) $1=1; else $1=0 Compare < constant; 2’s comp. set less than uns. sltu $1, $2, $3 if ($2 < $3) $1=1; else $1=0 Compare less than; natural numbers set l. t. imm. uns. sltiu $1, $2, 100 if ($2 < 100) $1=1; else $1=0 Compare < constant; natural numbers jump j 10000 go to 10000 Jump to target address jump register jr $31 go to $31 For switch, procedure return jump and link jal 10000 $31 = PC + 4; go to 10000 For procedure call 71

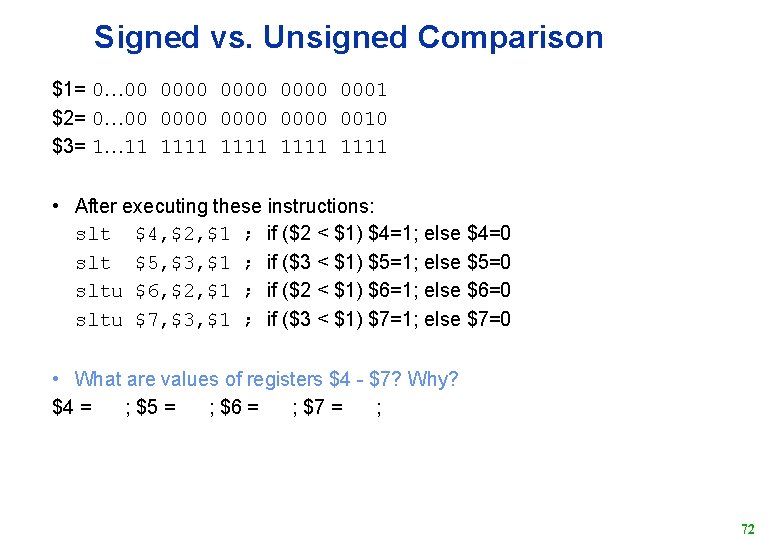

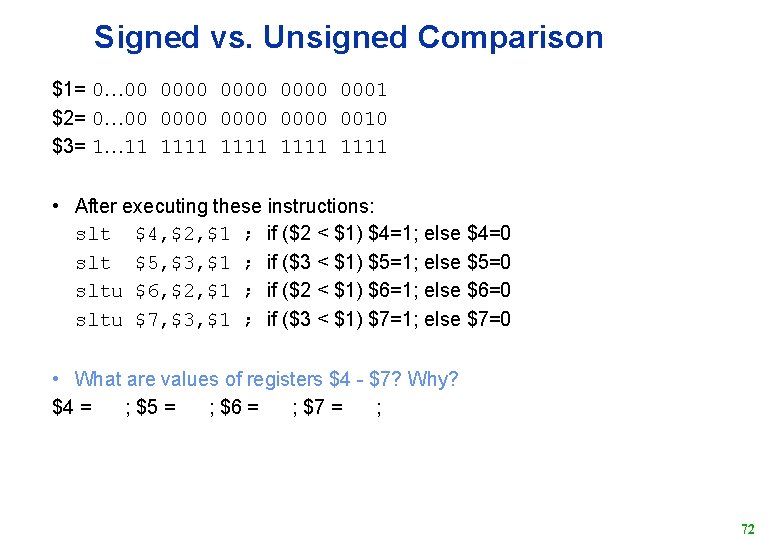

Signed vs. Unsigned Comparison $1= 0… 00 0000 0001 $2= 0… 00 0000 0010 $3= 1… 11 1111 • After executing these instructions: slt $4, $2, $1 ; if ($2 < $1) $4=1; else $4=0 slt $5, $3, $1 ; if ($3 < $1) $5=1; else $5=0 sltu $6, $2, $1 ; if ($2 < $1) $6=1; else $6=0 sltu $7, $3, $1 ; if ($3 < $1) $7=1; else $7=0 • What are values of registers $4 - $7? Why? $4 = ; $5 = ; $6 = ; $7 = ; 72

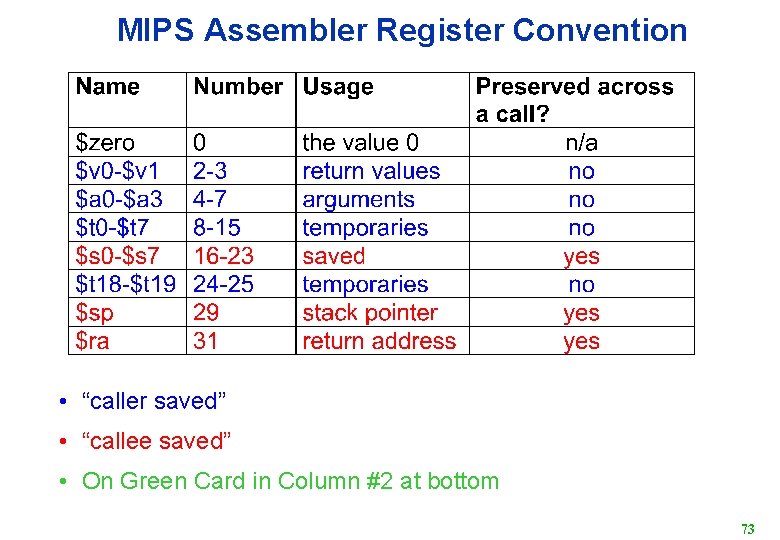

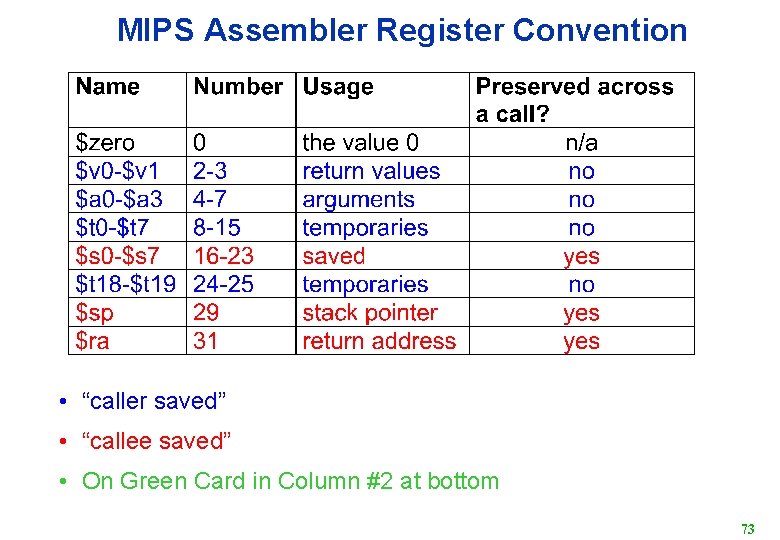

MIPS Assembler Register Convention • “caller saved” • “callee saved” • On Green Card in Column #2 at bottom 73

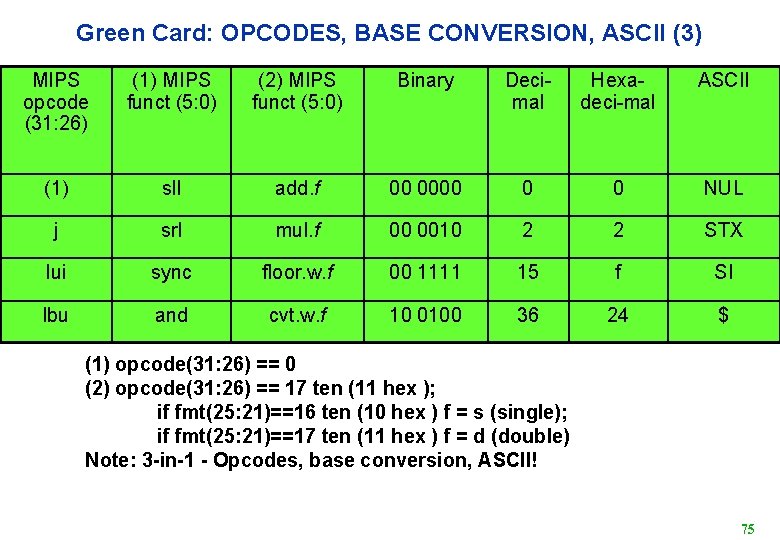

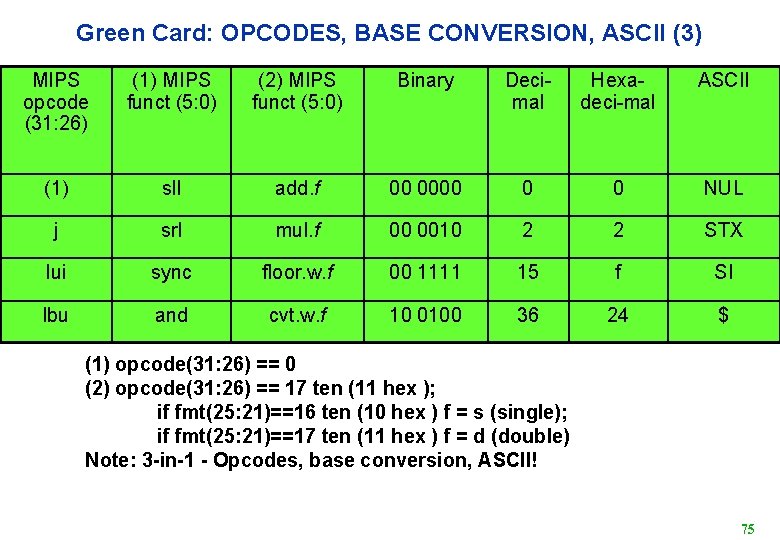

Green Card: OPCODES, BASE CONVERSION, ASCII (3) MIPS opcode (31: 26) (1) MIPS funct (5: 0) (2) MIPS funct (5: 0) Binary Decimal Hexadeci-mal ASCII (1) sll add. f 00 0000 0 0 NUL j srl mul. f 00 0010 2 2 STX lui sync floor. w. f 00 1111 15 f SI lbu and cvt. w. f 10 0100 36 24 $ (1) opcode(31: 26) == 0 (2) opcode(31: 26) == 17 ten (11 hex ); if fmt(25: 21)==16 ten (10 hex ) f = s (single); if fmt(25: 21)==17 ten (11 hex ) f = d (double) Note: 3 -in-1 - Opcodes, base conversion, ASCII! 75

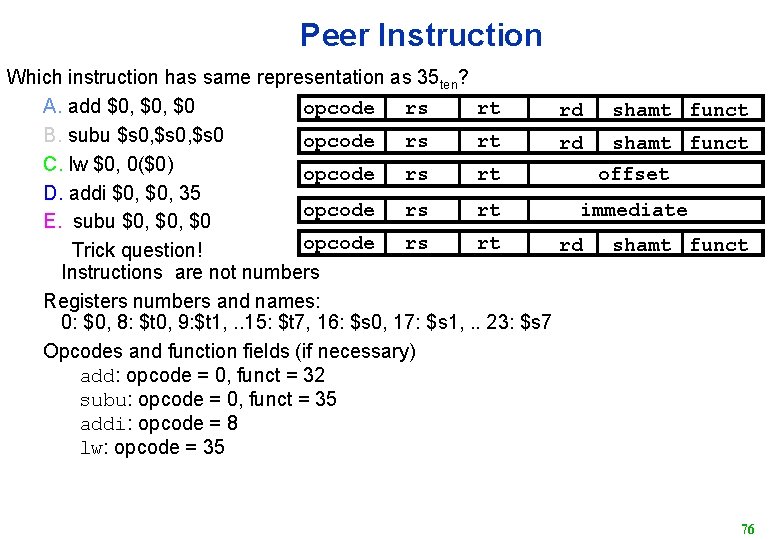

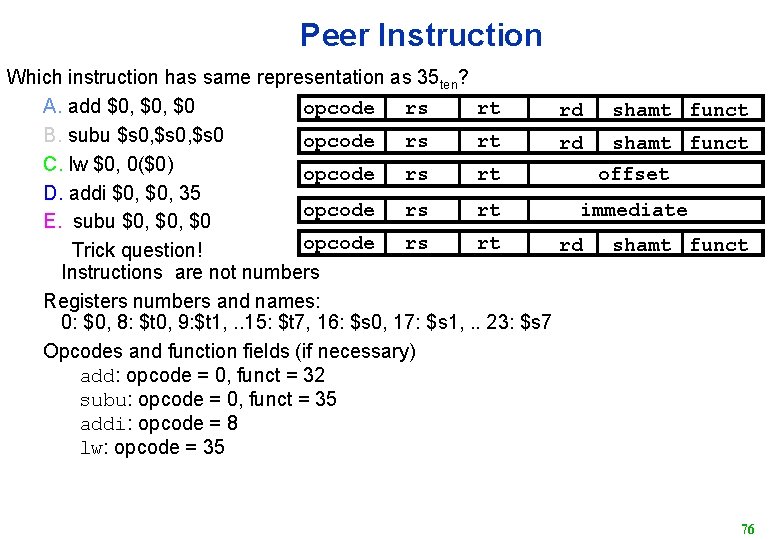

Peer Instruction Which instruction has same representation as 35 ten? A. add $0, $0 opcode rs rt rd shamt funct B. subu $s 0, $s 0 opcode rs rt rd shamt funct C. lw $0, 0($0) opcode rs rt offset D. addi $0, 35 opcode rs rt immediate E. subu $0, $0 opcode rs rt rd shamt funct F. Trick question! Instructions are not numbers Registers numbers and names: 0: $0, 8: $t 0, 9: $t 1, . . 15: $t 7, 16: $s 0, 17: $s 1, . . 23: $s 7 Opcodes and function fields (if necessary) add: opcode = 0, funct = 32 subu: opcode = 0, funct = 35 addi: opcode = 8 lw: opcode = 35 76

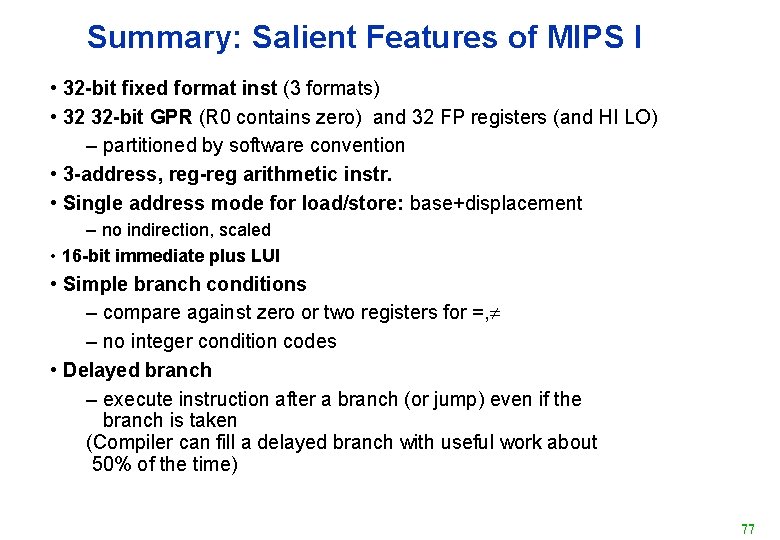

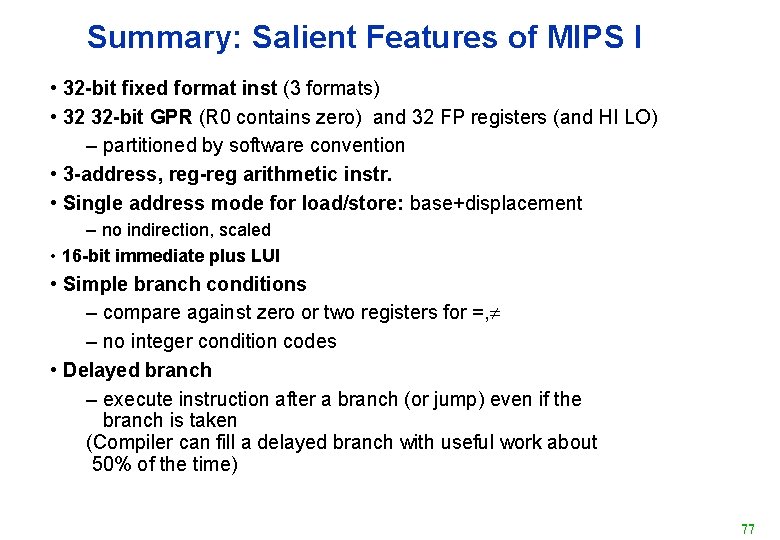

Summary: Salient Features of MIPS I • 32 -bit fixed format inst (3 formats) • 32 32 -bit GPR (R 0 contains zero) and 32 FP registers (and HI LO) – partitioned by software convention • 3 -address, reg-reg arithmetic instr. • Single address mode for load/store: base+displacement – no indirection, scaled • 16 -bit immediate plus LUI • Simple branch conditions – compare against zero or two registers for =, – no integer condition codes • Delayed branch – execute instruction after a branch (or jump) even if the branch is taken (Compiler can fill a delayed branch with useful work about 50% of the time) 77

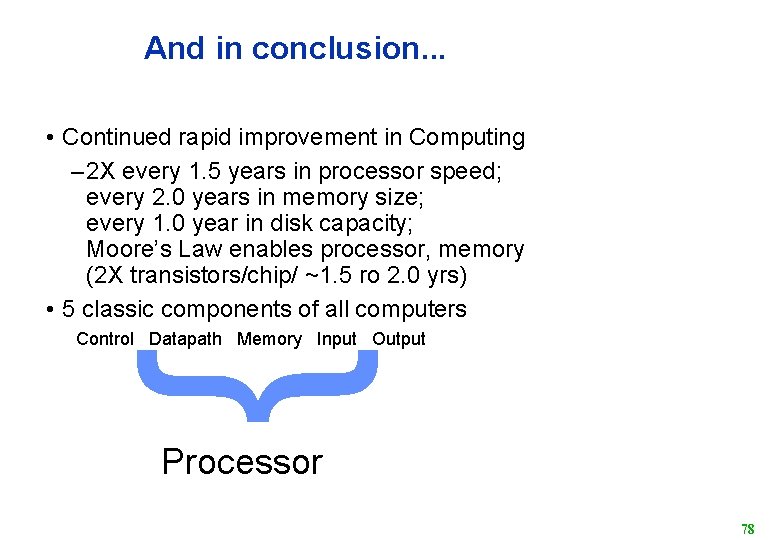

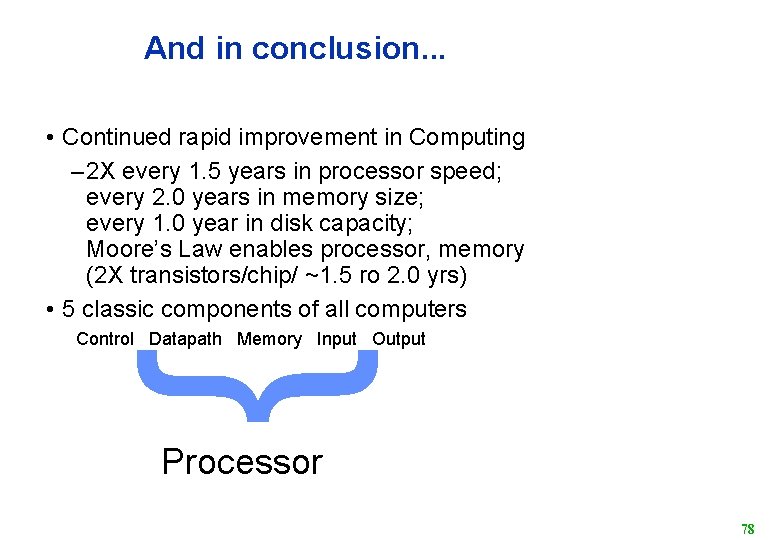

And in conclusion. . . • Continued rapid improvement in Computing – 2 X every 1. 5 years in processor speed; every 2. 0 years in memory size; every 1. 0 year in disk capacity; Moore’s Law enables processor, memory (2 X transistors/chip/ ~1. 5 ro 2. 0 yrs) • 5 classic components of all computers } Control Datapath Memory Input Output Processor 78

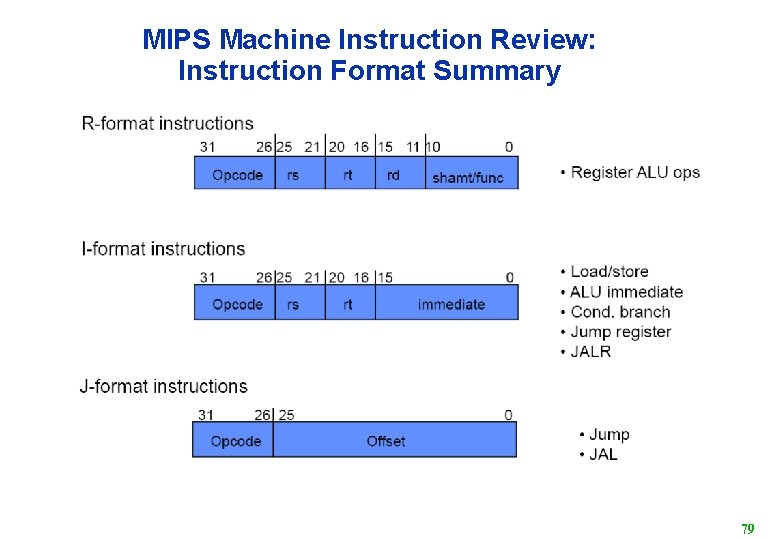

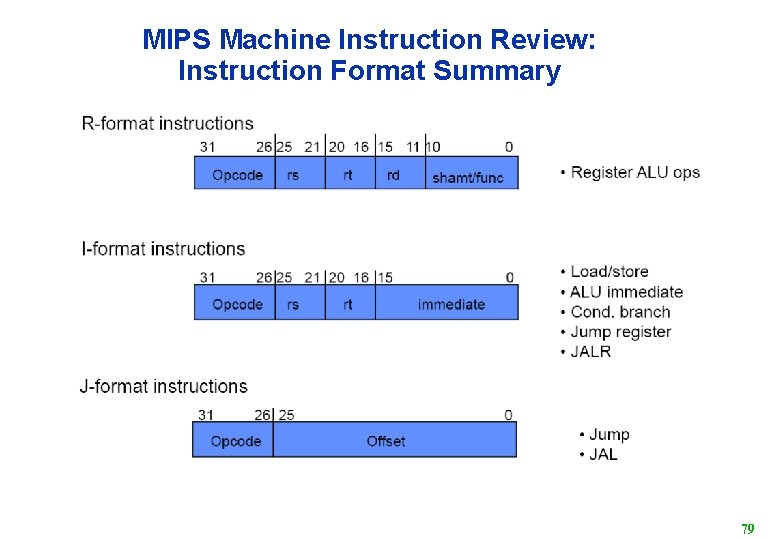

MIPS Machine Instruction Review: Instruction Format Summary 79

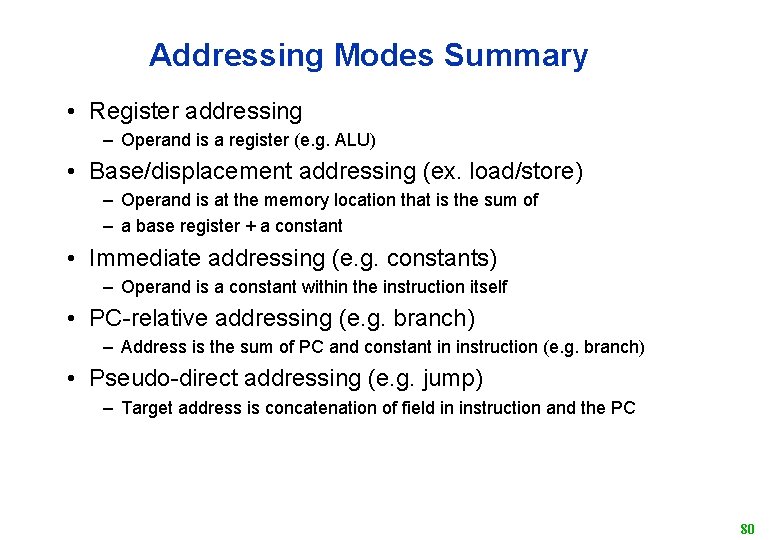

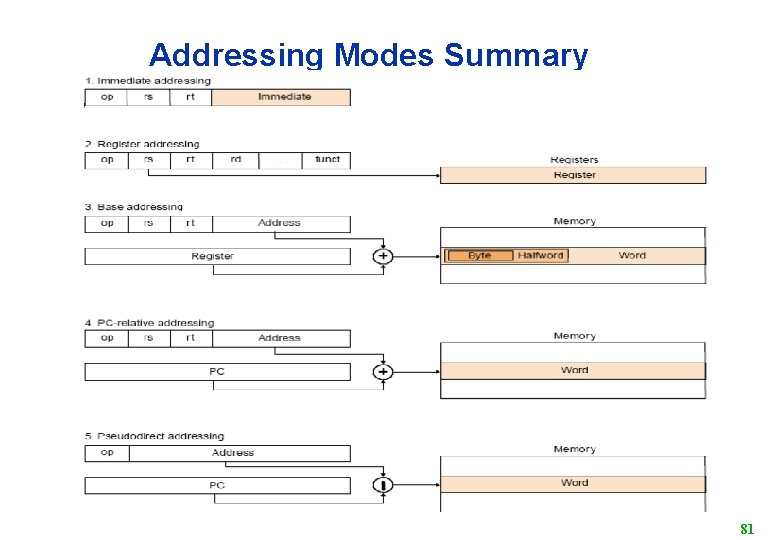

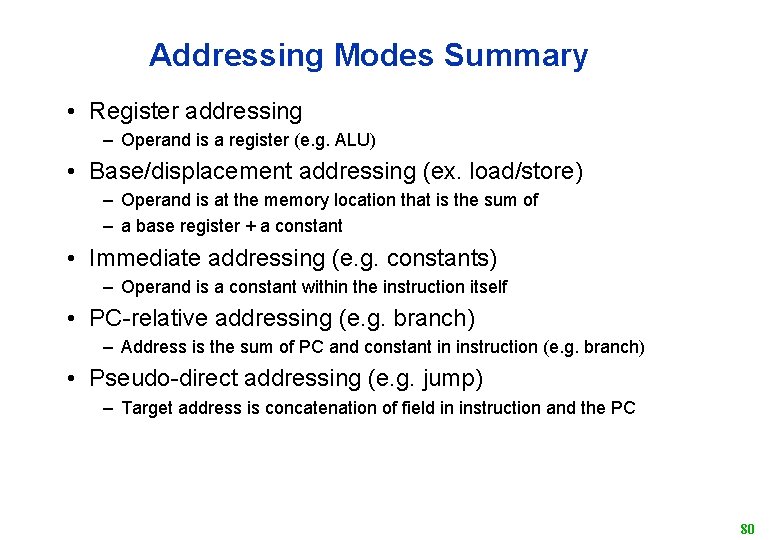

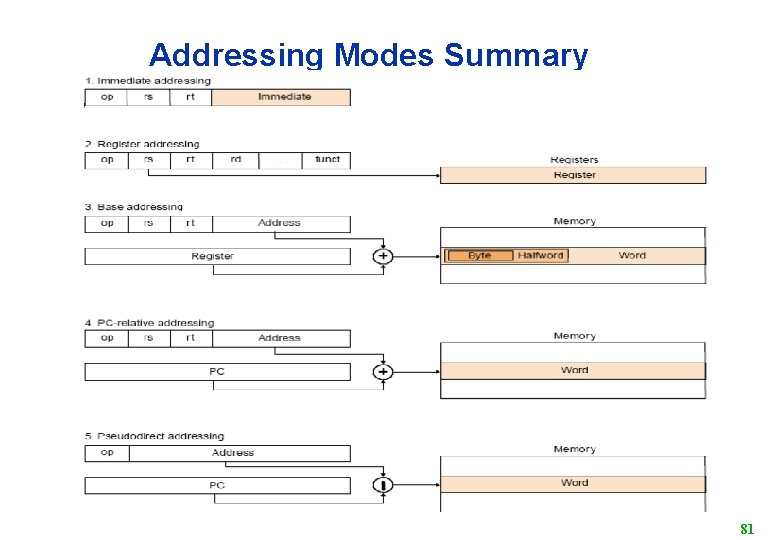

Addressing Modes Summary • Register addressing – Operand is a register (e. g. ALU) • Base/displacement addressing (ex. load/store) – Operand is at the memory location that is the sum of – a base register + a constant • Immediate addressing (e. g. constants) – Operand is a constant within the instruction itself • PC-relative addressing (e. g. branch) – Address is the sum of PC and constant in instruction (e. g. branch) • Pseudo-direct addressing (e. g. jump) – Target address is concatenation of field in instruction and the PC 80

Addressing Modes Summary 81

Home. Work • Readings: – Read Chapter 2. 5 -2. 14, then Appendix C and D. 82

Acknowledgements • These slides contain material from courses: – UCB CS 152. – Stanford EE 108 B 83