Basic Computer Organization v Since the 1940s computers

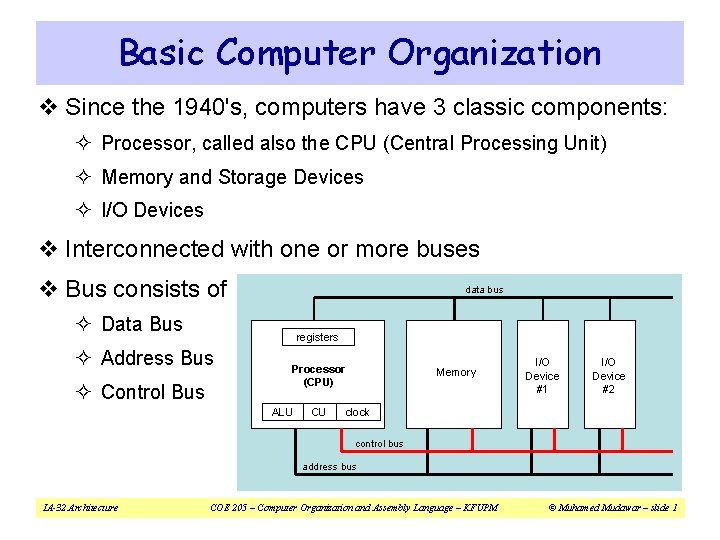

Basic Computer Organization v Since the 1940's, computers have 3 classic components: ² Processor, called also the CPU (Central Processing Unit) ² Memory and Storage Devices ² I/O Devices v Interconnected with one or more buses v Bus consists of data bus ² Data Bus registers ² Address Bus ² Control Bus Processor (CPU) ALU CU Memory I/O Device #1 I/O Device #2 clock control bus address bus IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 1

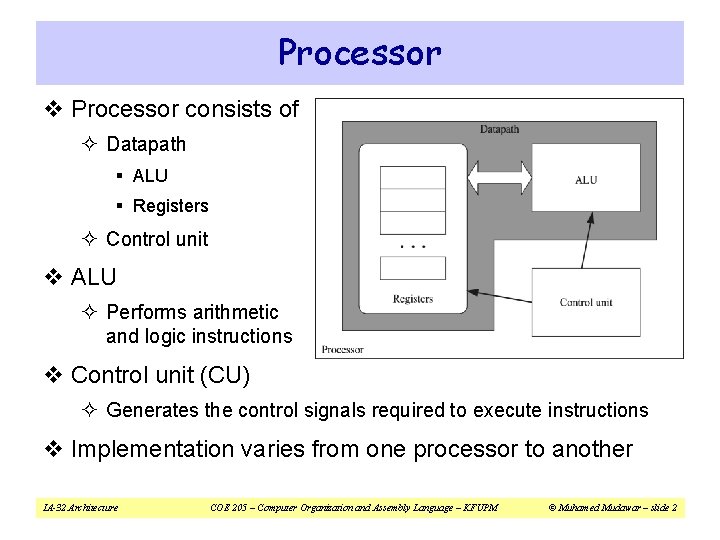

Processor v Processor consists of ² Datapath § ALU § Registers ² Control unit v ALU ² Performs arithmetic and logic instructions v Control unit (CU) ² Generates the control signals required to execute instructions v Implementation varies from one processor to another IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 2

What is a Microprocessor? • A processor is built from a large number of integrated circuits • A microprocessor is a processor packaged as a single Ic(chip). • A microcomputer is a computer that uses a microprocessor as its CPU. • 8 -bit, 16 -bit, 32 -bit microprocessor: refers to number of bits manipulated in one operation. • It requires external memory to execute programs. • It cannot directly interface to I/O devices, peripheral IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 3

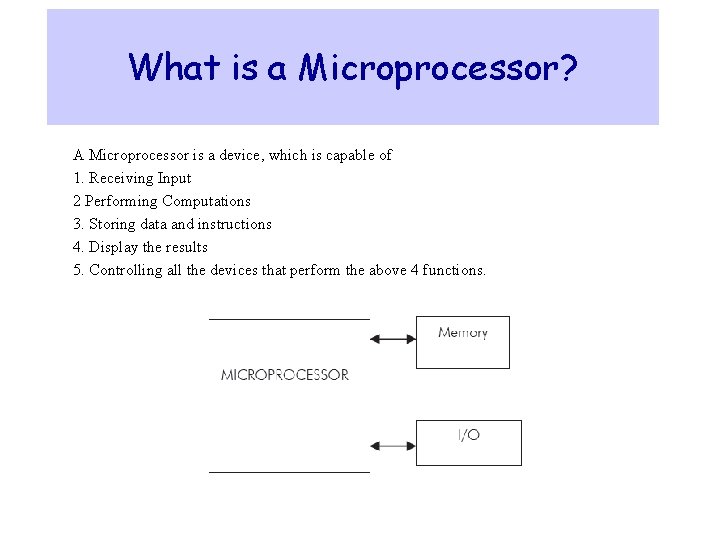

What is a Microprocessor? A Microprocessor is a device, which is capable of 1. Receiving Input 2 Performing Computations 3. Storing data and instructions 4. Display the results 5. Controlling all the devices that perform the above 4 functions.

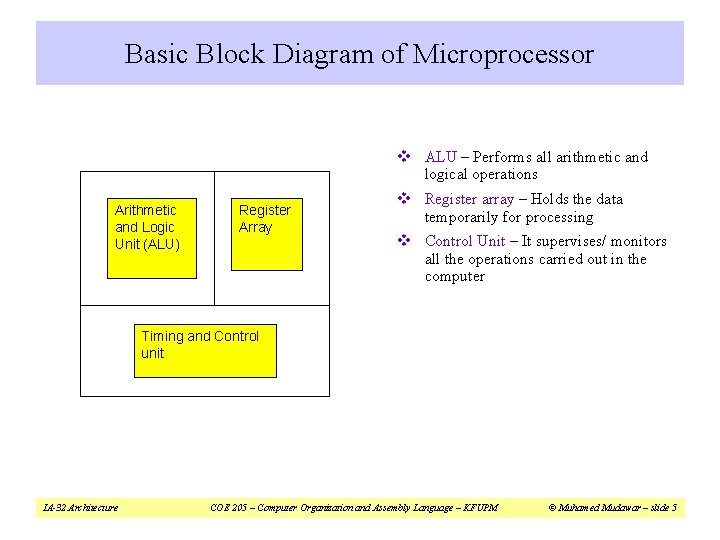

Basic Block Diagram of Microprocessor v ALU – Performs all arithmetic and logical operations Arithmetic and Logic Unit (ALU) Register Array v Register array – Holds the data temporarily for processing v Control Unit – It supervises/ monitors all the operations carried out in the computer Timing and Control unit IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 5

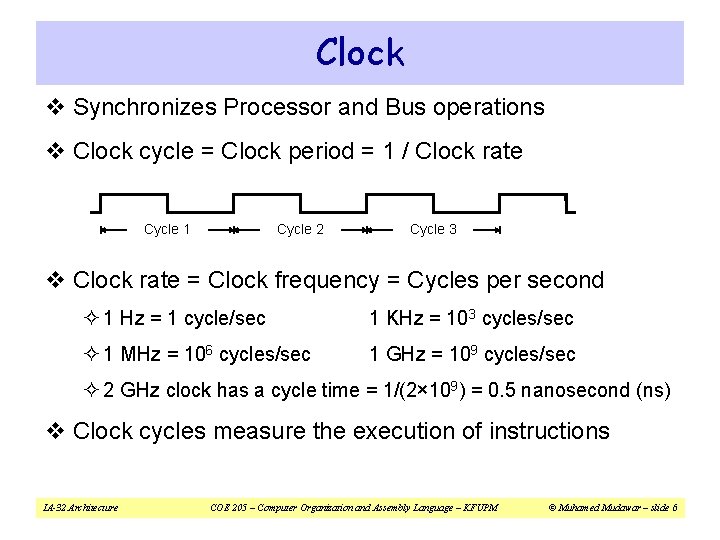

Clock v Synchronizes Processor and Bus operations v Clock cycle = Clock period = 1 / Clock rate Cycle 1 Cycle 2 Cycle 3 v Clock rate = Clock frequency = Cycles per second ² 1 Hz = 1 cycle/sec 1 KHz = 103 cycles/sec ² 1 MHz = 106 cycles/sec 1 GHz = 109 cycles/sec ² 2 GHz clock has a cycle time = 1/(2× 109) = 0. 5 nanosecond (ns) v Clock cycles measure the execution of instructions IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 6

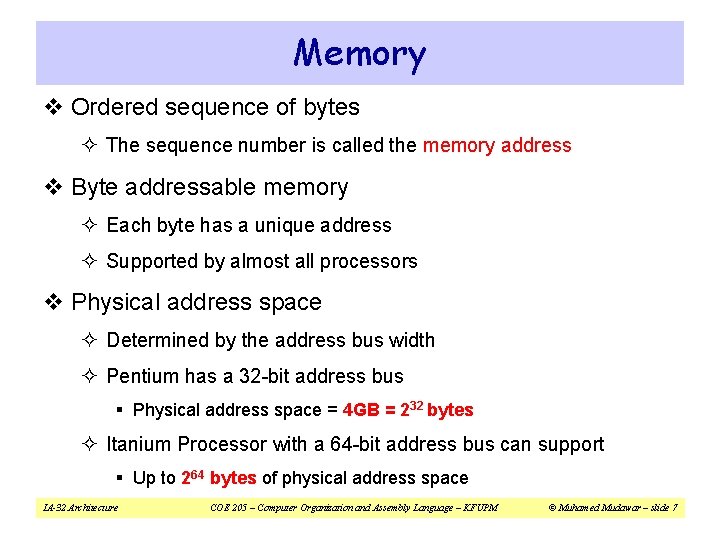

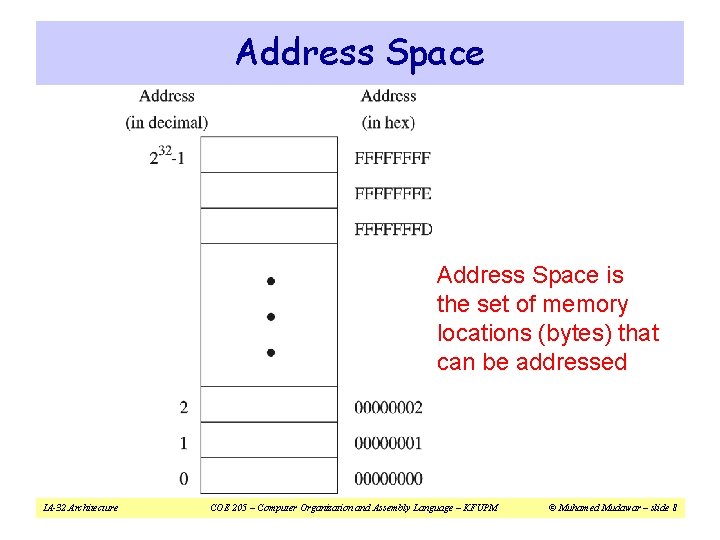

Memory v Ordered sequence of bytes ² The sequence number is called the memory address v Byte addressable memory ² Each byte has a unique address ² Supported by almost all processors v Physical address space ² Determined by the address bus width ² Pentium has a 32 -bit address bus § Physical address space = 4 GB = 232 bytes ² Itanium Processor with a 64 -bit address bus can support § Up to 264 bytes of physical address space IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 7

Address Space is the set of memory locations (bytes) that can be addressed IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 8

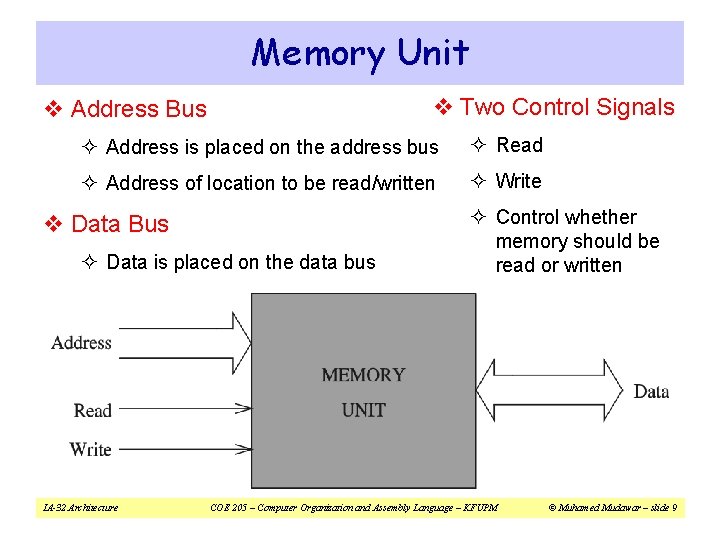

Memory Unit v Two Control Signals v Address Bus ² Address is placed on the address bus ² Read ² Address of location to be read/written ² Write v Data Bus ² Data is placed on the data bus IA-32 Architecture ² Control whether memory should be read or written COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 9

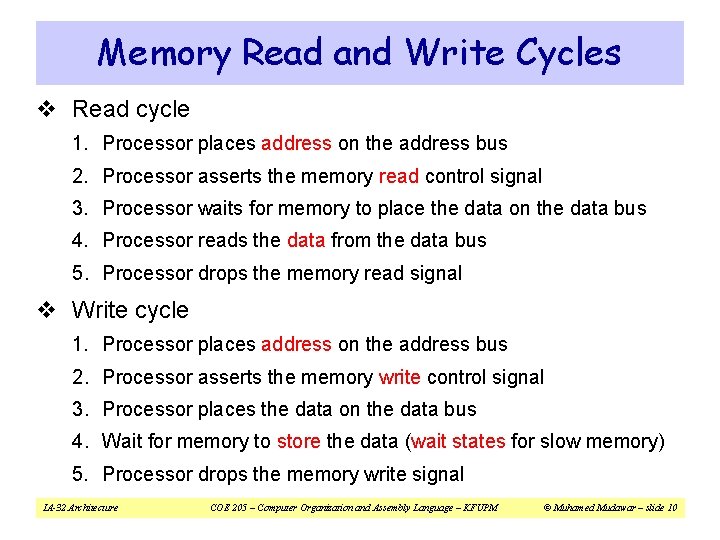

Memory Read and Write Cycles v Read cycle 1. Processor places address on the address bus 2. Processor asserts the memory read control signal 3. Processor waits for memory to place the data on the data bus 4. Processor reads the data from the data bus 5. Processor drops the memory read signal v Write cycle 1. Processor places address on the address bus 2. Processor asserts the memory write control signal 3. Processor places the data on the data bus 4. Wait for memory to store the data (wait states for slow memory) 5. Processor drops the memory write signal IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 10

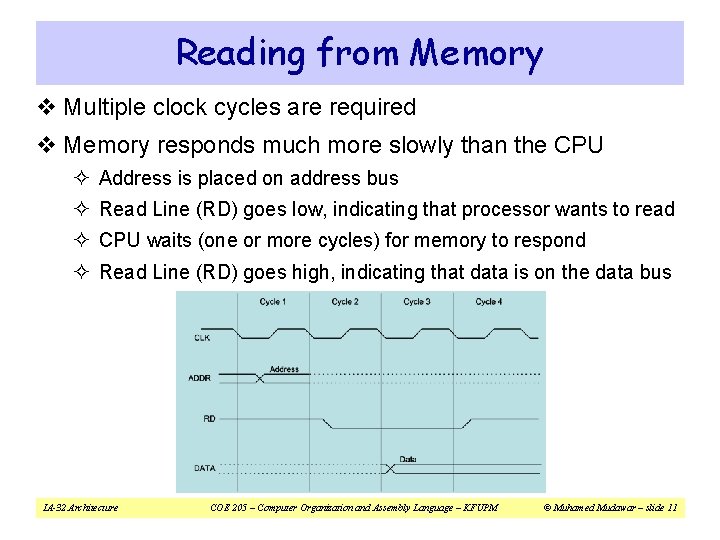

Reading from Memory v Multiple clock cycles are required v Memory responds much more slowly than the CPU ² Address is placed on address bus ² Read Line (RD) goes low, indicating that processor wants to read ² CPU waits (one or more cycles) for memory to respond ² Read Line (RD) goes high, indicating that data is on the data bus IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 11

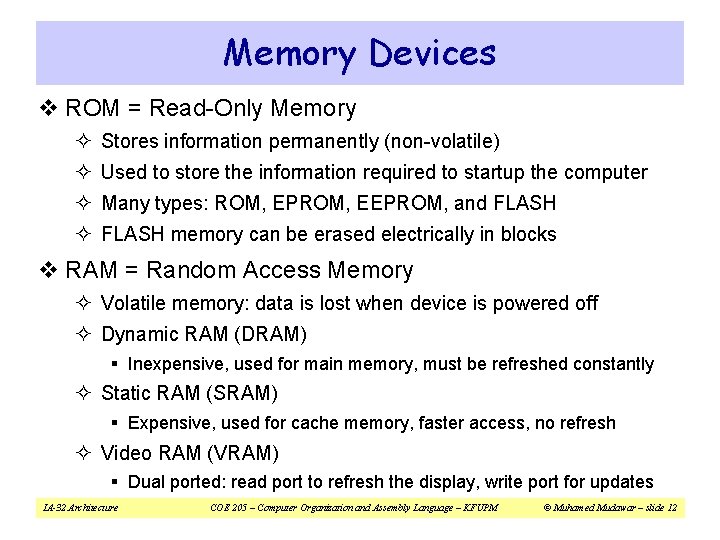

Memory Devices v ROM = Read-Only Memory ² Stores information permanently (non-volatile) ² Used to store the information required to startup the computer ² Many types: ROM, EPROM, EEPROM, and FLASH ² FLASH memory can be erased electrically in blocks v RAM = Random Access Memory ² Volatile memory: data is lost when device is powered off ² Dynamic RAM (DRAM) § Inexpensive, used for main memory, must be refreshed constantly ² Static RAM (SRAM) § Expensive, used for cache memory, faster access, no refresh ² Video RAM (VRAM) § Dual ported: read port to refresh the display, write port for updates IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 12

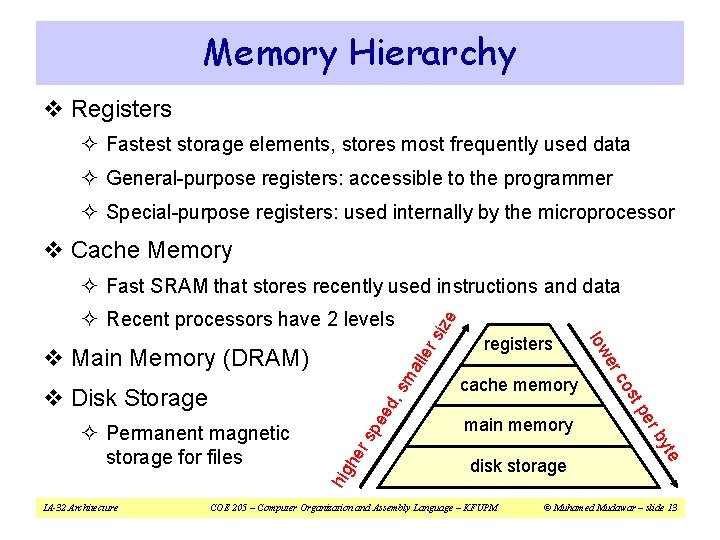

Memory Hierarchy v Registers ² Fastest storage elements, stores most frequently used data ² General-purpose registers: accessible to the programmer ² Special-purpose registers: used internally by the microprocessor v Cache Memory ² Fast SRAM that stores recently used instructions and data lle rs ma sp ee d, s he r hig COE 205 – Computer Organization and Assembly Language – KFUPM yte rb disk storage pe main memory t os IA-32 Architecture cache memory c er v Disk Storage registers low v Main Memory (DRAM) ² Permanent magnetic storage for files ize ² Recent processors have 2 levels © Muhamed Mudawar – slide 13

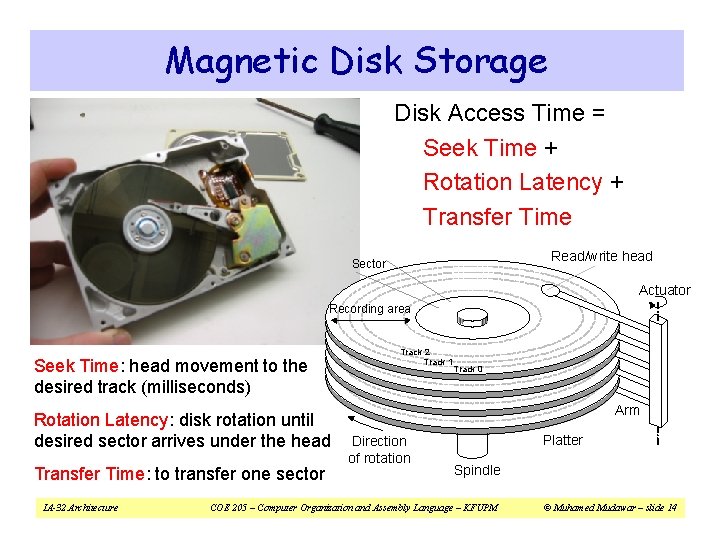

Magnetic Disk Storage Disk Access Time = Seek Time + Rotation Latency + Transfer Time Read/write head Sector Actuator Recording area Seek Time: head movement to the desired track (milliseconds) Rotation Latency: disk rotation until desired sector arrives under the head Transfer Time: to transfer one sector IA-32 Architecture Track 2 Track 1 Track 0 Arm Direction of rotation Platter Spindle COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 14

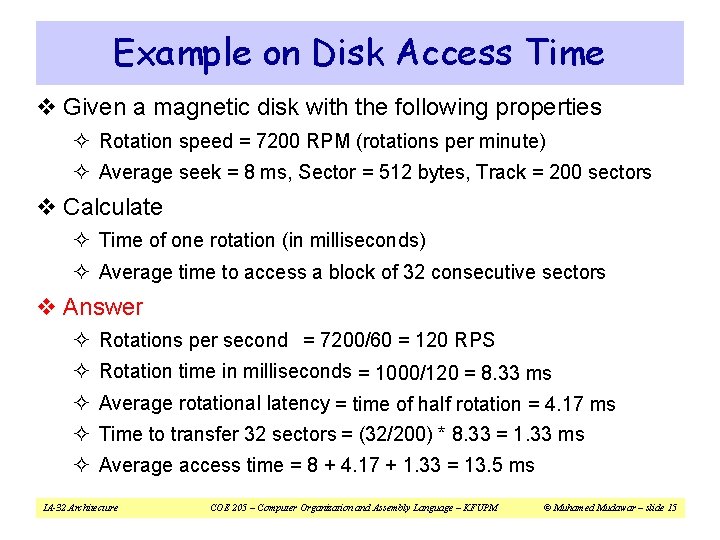

Example on Disk Access Time v Given a magnetic disk with the following properties ² Rotation speed = 7200 RPM (rotations per minute) ² Average seek = 8 ms, Sector = 512 bytes, Track = 200 sectors v Calculate ² Time of one rotation (in milliseconds) ² Average time to access a block of 32 consecutive sectors v Answer ² Rotations per second = 7200/60 = 120 RPS ² Rotation time in milliseconds = 1000/120 = 8. 33 ms ² Average rotational latency = time of half rotation = 4. 17 ms ² Time to transfer 32 sectors = (32/200) * 8. 33 = 1. 33 ms ² Average access time = 8 + 4. 17 + 1. 33 = 13. 5 ms IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 15

Next. . . v Basic Computer Organization v Intel Microprocessors v Instruction Execution Cycle IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 16

History of Microprocessor v The very first microprocessor is considered to be the Intel 4004. It was released in 1971 and was a 4 Bit processor. v Then the 8 bit 8008 microprocessor. It was developed by Intel in 1972 v The first multi-chip 16 bit processor was released by National Semiconductor in 1973 v Intel upgraded the 8008 into a 16 bit version they called the 8086. It was the first of the x 86 family by which many modern PCs are powered. IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 17

Intel Microprocessors v Intel introduced the 8086 microprocessor in 1979 v 8086, 8087, 8088, and 80186 processors ² 16 -bit processors with 16 -bit registers ² 8087 Floating-Point co-processor ² Uses segmentation and real-address mode to address memory ² 8088 is a less expensive version of 8086 § Uses an 8 -bit data bus ² 80186 is a faster version of 8086 IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 18

Intel 80286 and 80386 Processors v 80286 was introduced in 1982 ² 24 -bit address bus 224 bytes = 16 MB address space ² Introduced protected mode v 80386 was introduced in 1985 ² First 32 -bit processor with 32 -bit general-purpose registers ² First processor to define the IA-32 architecture ² 32 -bit data bus and 32 -bit address bus ² 232 bytes 4 GB address space ² Introduced paging, virtual memory IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 19

Intel 80486 and Pentium Processors v 80486 was introduced 1989 ² Improved version of Intel 80386 ² On-chip Floating-Point unit (DX versions) ² On-chip unified Instruction/Data Cache (8 KB) ² Uses Pipelining: can execute up to 1 instruction per clock cycle v Pentium (80586) was introduced in 1993 ² Wider 64 -bit data bus, but address bus is still 32 bits ² Two execution pipelines: U-pipe and V-pipe § Superscalar performance: can execute 2 instructions per clock cycle ² Separate 8 KB instruction and 8 KB data caches IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 20

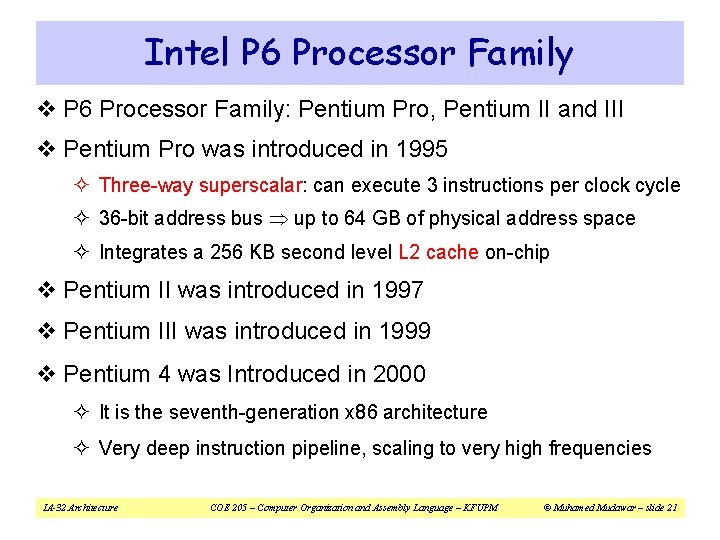

Intel P 6 Processor Family v P 6 Processor Family: Pentium Pro, Pentium II and III v Pentium Pro was introduced in 1995 ² Three-way superscalar: can execute 3 instructions per clock cycle ² 36 -bit address bus up to 64 GB of physical address space ² Integrates a 256 KB second level L 2 cache on-chip v Pentium II was introduced in 1997 v Pentium III was introduced in 1999 v Pentium 4 was Introduced in 2000 ² It is the seventh-generation x 86 architecture ² Very deep instruction pipeline, scaling to very high frequencies IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 21

CISC and RISC v CISC – Complex Instruction Set Computer ² Large and complex instruction set ² Variable width instructions ² Requires microcode interpreter § Each instruction is decoded into a sequence of micro-operations ² Example: Intel x 86 family v RISC – Reduced Instruction Set Computer ² Small and simple instruction set ² All instructions have the same width ² Simpler instruction formats and addressing modes ² Decoded and executed directly by hardware ² Examples: ARM, MIPS, Power. PC, SPARC, etc. IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 22

Next. . . v Basic Computer Organization v Intel Microprocessors v Instruction Execution Cycle IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 23

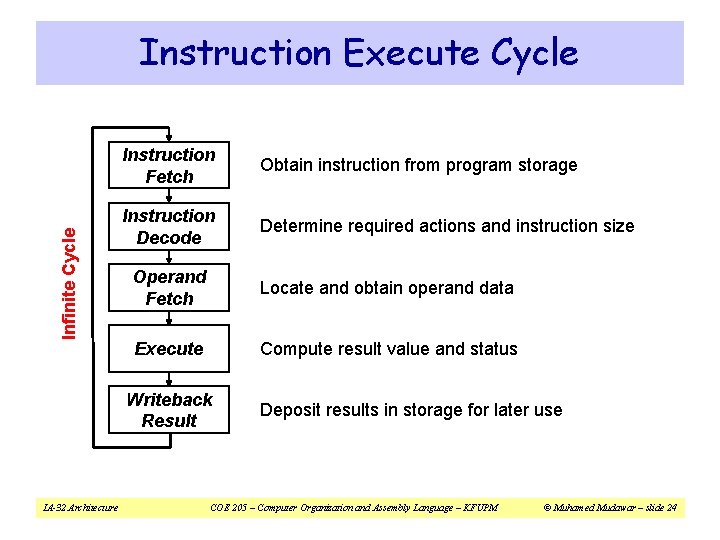

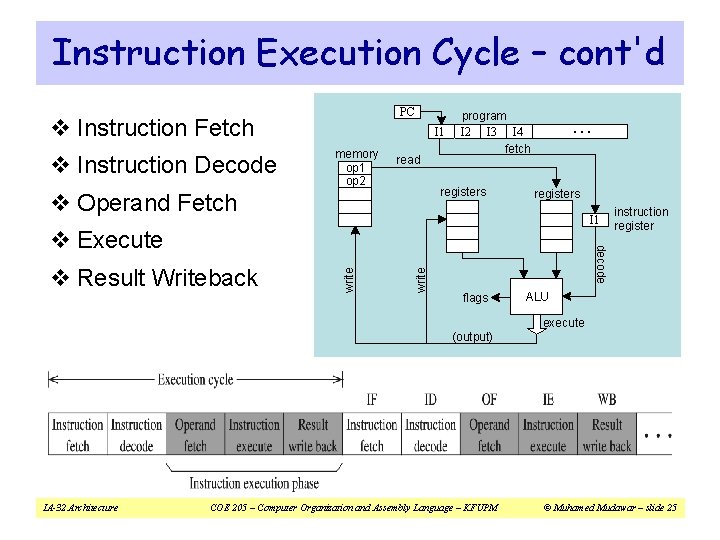

Infinite Cycle Instruction Execute Cycle Instruction Fetch Obtain instruction from program storage Instruction Decode Determine required actions and instruction size Operand Fetch Locate and obtain operand data Execute Compute result value and status Writeback Result IA-32 Architecture Deposit results in storage for later use COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 24

Instruction Execution Cycle – cont'd PC v Instruction Fetch v Instruction Decode I 1 memory op 1 op 2 read program I 2 I 3 I 4 fetch registers v Operand Fetch . . . registers I 1 write v Result Writeback decode v Execute instruction register flags ALU execute (output) IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 25

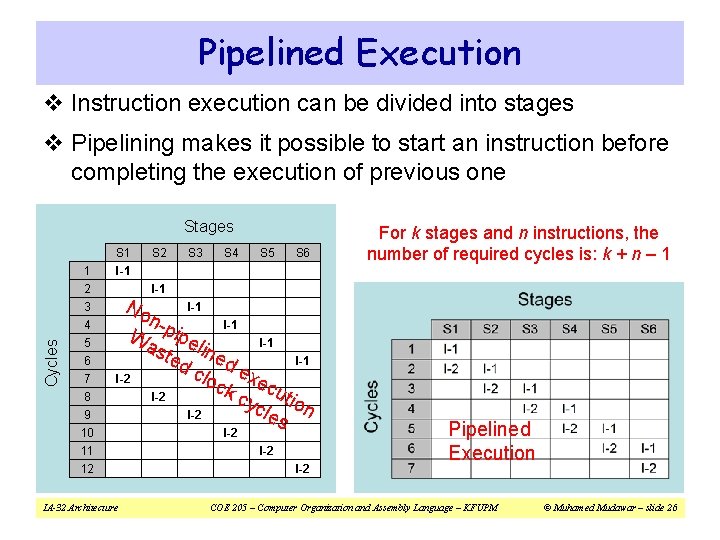

Pipelined Execution v Instruction execution can be divided into stages v Pipelining makes it possible to start an instruction before completing the execution of previous one Stages Cycles 1 2 3 4 5 6 7 8 9 10 11 S 1 I-1 S 2 S 3 S 4 S 5 S 6 I-1 No n-p I-1 Wa ipe I-1 ste line I-1 dc de I-2 loc xec k c ut I-2 yc ion les I-2 12 IA-32 Architecture For k stages and n instructions, the number of required cycles is: k + n – 1 I-2 I-2 Pipelined Execution COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 26

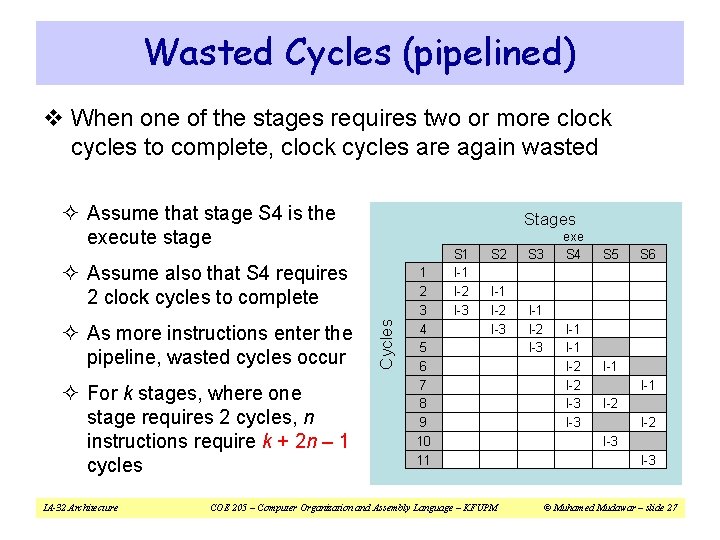

Wasted Cycles (pipelined) v When one of the stages requires two or more clock cycles to complete, clock cycles are again wasted ² Assume that stage S 4 is the execute stage Stages ² As more instructions enter the pipeline, wasted cycles occur ² For k stages, where one stage requires 2 cycles, n instructions require k + 2 n – 1 cycles IA-32 Architecture Cycles ² Assume also that S 4 requires 2 clock cycles to complete 1 2 3 4 5 6 7 8 9 10 11 S 1 I-2 I-3 S 2 I-1 I-2 I-3 COE 205 – Computer Organization and Assembly Language – KFUPM S 3 I-1 I-2 I-3 exe S 4 I-1 I-2 I-3 S 5 S 6 I-1 I-2 I-3 © Muhamed Mudawar – slide 27

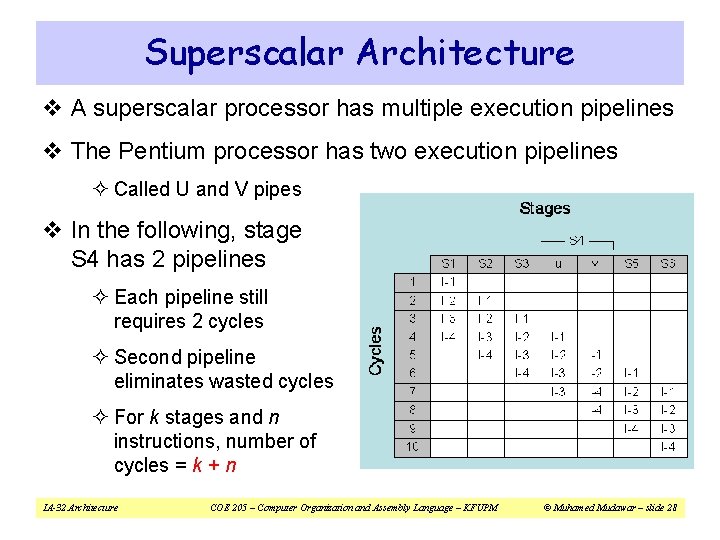

Superscalar Architecture v A superscalar processor has multiple execution pipelines v The Pentium processor has two execution pipelines ² Called U and V pipes v In the following, stage S 4 has 2 pipelines ² Each pipeline still requires 2 cycles ² Second pipeline eliminates wasted cycles ² For k stages and n instructions, number of cycles = k + n IA-32 Architecture COE 205 – Computer Organization and Assembly Language – KFUPM © Muhamed Mudawar – slide 28

- Slides: 28