TwoChannel Batch by Batch Intensity Monitor for Main

Two-Channel Batch by Batch Intensity Monitor for Main Injector BBI 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 1

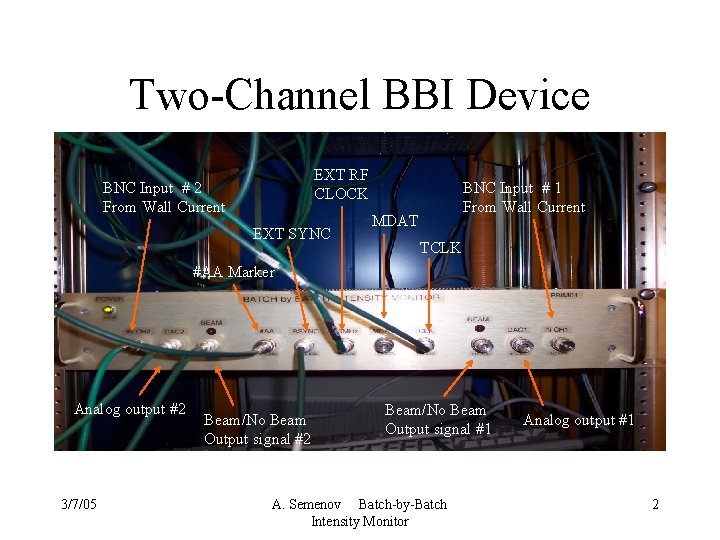

Two-Channel BBI Device EXT RF CLOCK BNC Input # 2 From Wall Current EXT SYNC MDAT BNC Input # 1 From Wall Current TCLK #AA Marker Analog output #2 Beam/No Beam Output signal #2 3/7/05 Beam/No Beam Output signal #1 A. Semenov Batch-by-Batch Intensity Monitor Analog output #1 2

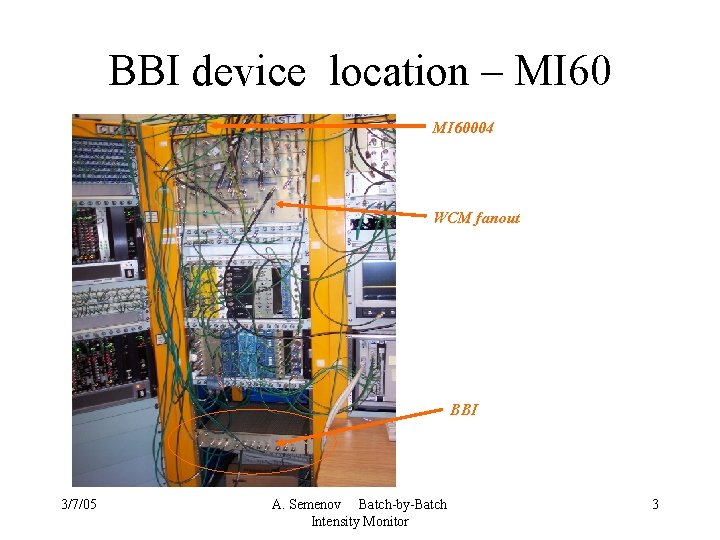

BBI device location – MI 60004 WCM fanout BBI 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 3

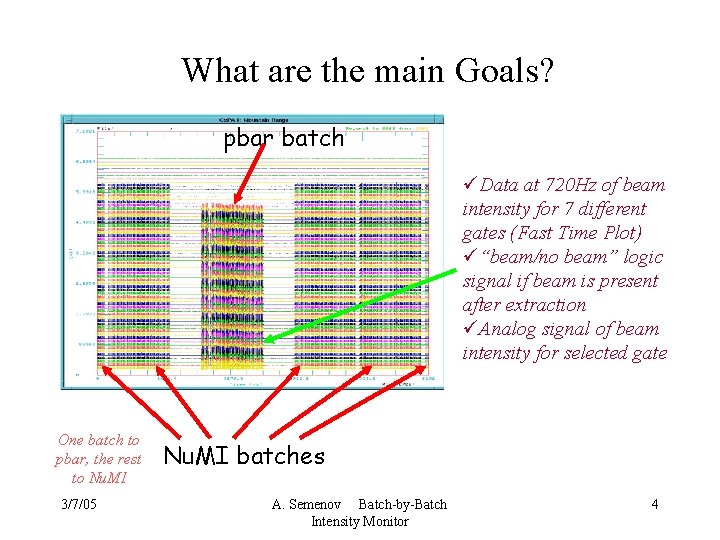

What are the main Goals? pbar batch üData at 720 Hz of beam intensity for 7 different gates (Fast Time Plot) ü“beam/no beam” logic signal if beam is present after extraction üAnalog signal of beam intensity for selected gate One batch to pbar, the rest to Nu. MI 3/7/05 Nu. MI batches A. Semenov Batch-by-Batch Intensity Monitor 4

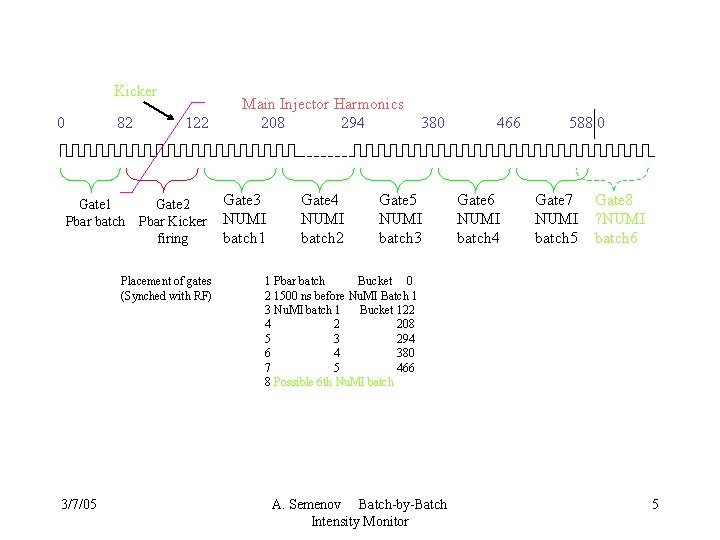

Kicker Main Injector Harmonics 0 82 122 208 294 380 466 588 0 Gate 1 Pbar batch Gate 2 Pbar Kicker firing Gate 3 NUMI batch 1 Placement of gates (Synched with RF) 3/7/05 Gate 4 NUMI batch 2 Gate 5 NUMI batch 3 Gate 6 NUMI batch 4 Gate 7 NUMI batch 5 Gate 8 ? NUMI batch 6 1 Pbar batch Bucket 0 2 1500 ns before Nu. MI Batch 1 3 Nu. MI batch 1 Bucket 122 4 208 5 3 294 6 4 380 7 5 466 8 Possible 6 th Nu. MI batch A. Semenov Batch-by-Batch Intensity Monitor 5

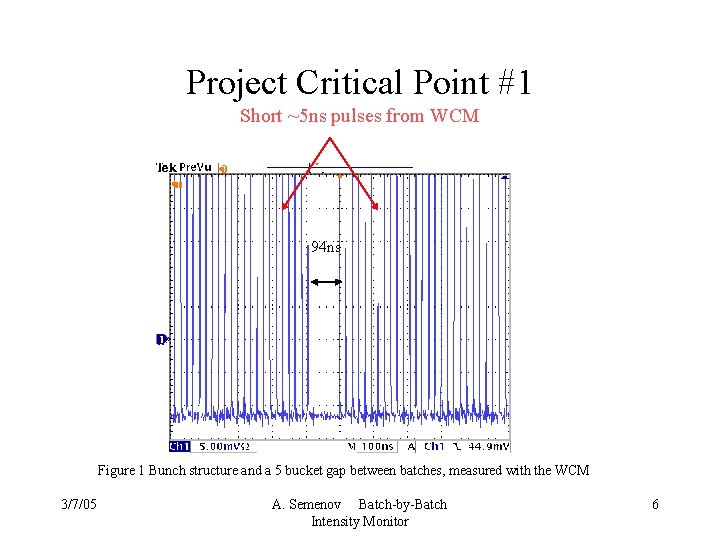

Project Critical Point #1 Short ~5 ns pulses from WCM 94 ns Figure 1 Bunch structure and a 5 bucket gap between batches, measured with the WCM 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 6

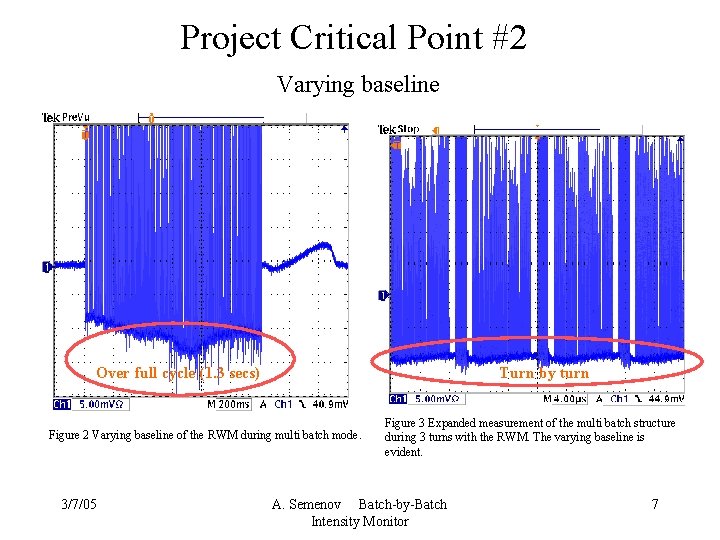

Project Critical Point #2 Varying baseline Over full cycle (1. 3 secs) Turn by turn Figure 2 Varying baseline of the RWM during multi batch mode. 3/7/05 Figure 3 Expanded measurement of the multi batch structure during 3 turns with the RWM. The varying baseline is evident. A. Semenov Batch-by-Batch Intensity Monitor 7

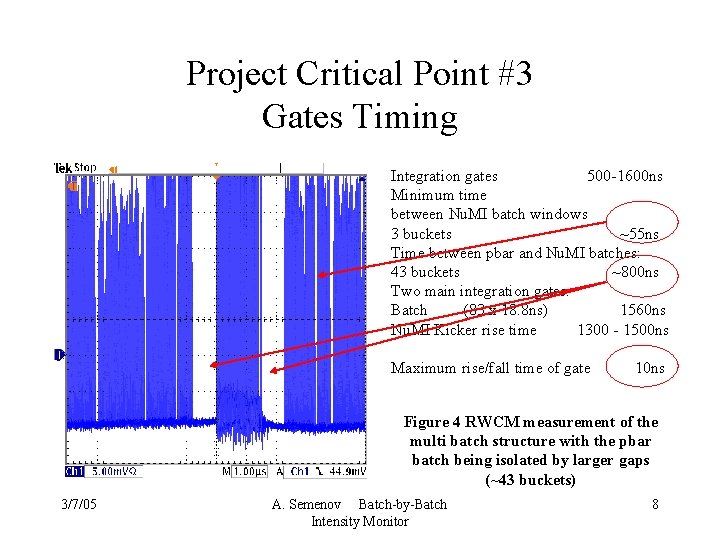

Project Critical Point #3 Gates Timing Integration gates 500 -1600 ns Minimum time between Nu. MI batch windows 3 buckets ~55 ns Time between pbar and Nu. MI batches: 43 buckets ~800 ns Two main integration gates: Batch (83 x 18. 8 ns) 1560 ns Nu. MI Kicker rise time 1300 - 1500 ns Maximum rise/fall time of gate 10 ns Figure 4 RWСM measurement of the multi batch structure with the pbar batch being isolated by larger gaps (~43 buckets) 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 8

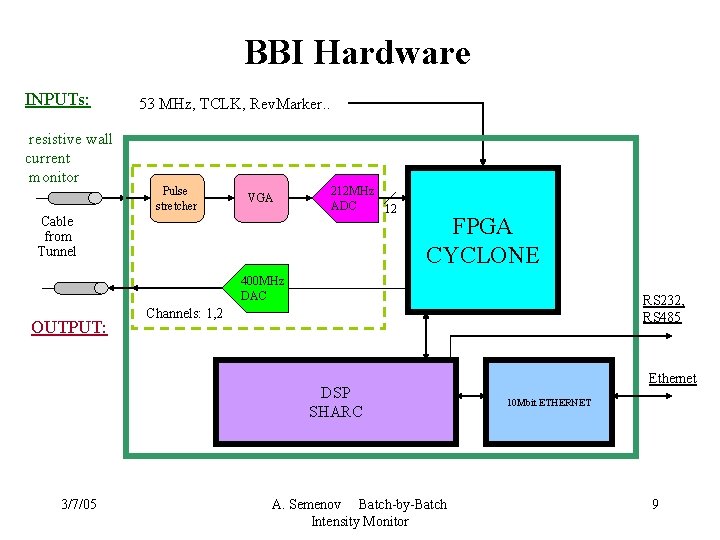

BBI Hardware INPUTs: resistive wall current monitor 53 MHz, TCLK, Rev. Marker. . Pulse stretcher VGA Cable from Tunnel 212 MHz ADC 12 FPGA CYCLONE 400 MHz DAC OUTPUT: RS 232, RS 485 Channels: 1, 2 DSP SHARC 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor Ethernet 10 Mbit ETHERNET 9

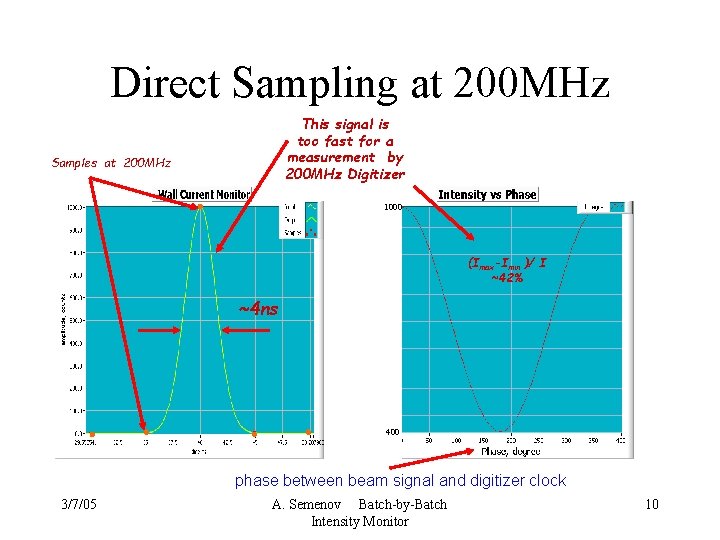

Direct Sampling at 200 MHz This signal is too fast for a measurement by 200 MHz Digitizer Samples at 200 MHz 1000 (Imax-Imin )/ I ~42% ~4 ns 400 phase between beam signal and digitizer clock 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 10

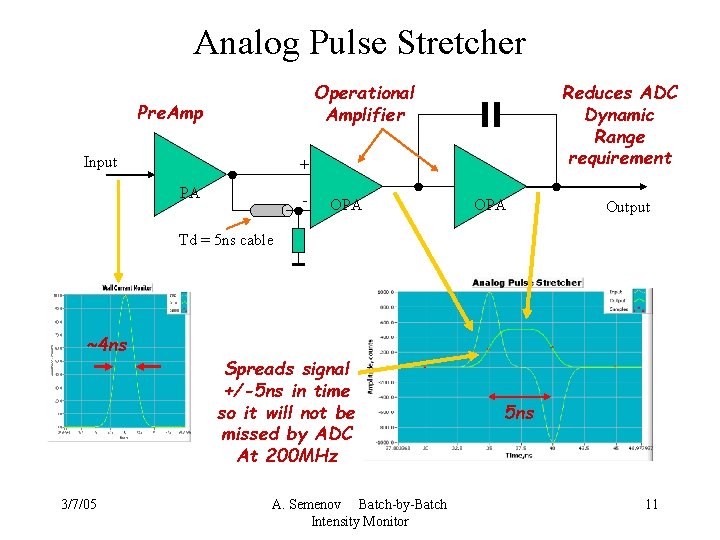

Analog Pulse Stretcher Operational Amplifier Pre. Amp Input Reduces ADC Dynamic Range requirement + PA - OPA Output Td = 5 ns cable ~4 ns 3/7/05 Spreads signal +/-5 ns in time so it will not be missed by ADC At 200 MHz A. Semenov Batch-by-Batch Intensity Monitor 5 ns 11

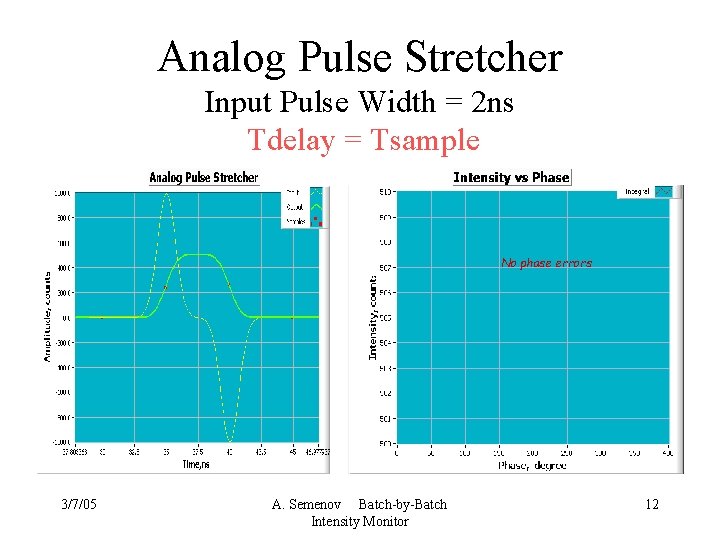

Analog Pulse Stretcher Input Pulse Width = 2 ns Tdelay = Tsample No phase errors 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 12

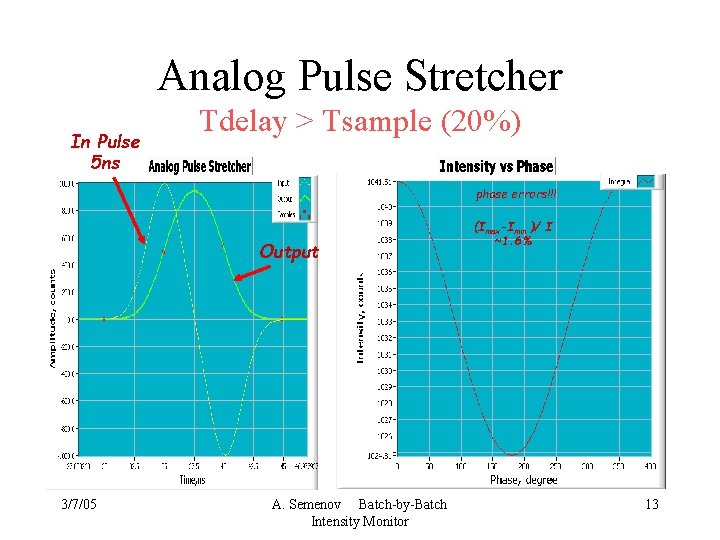

Analog Pulse Stretcher In Pulse 5 ns Tdelay > Tsample (20%) phase errors!!! Output 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor (Imax-Imin )/ I ~1. 6% 13

FPGA Baseline Correction How define baseline? • • it is natural for our case to define "baseline" as a line “not containing peaks" It means that for base line correction algorithm we should use at list 2 parameters – threshold (to detect a peak amplitude above baseline) and window ( to separate a slow fluctuation of base line signal and peak signal in time domain region) 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 14

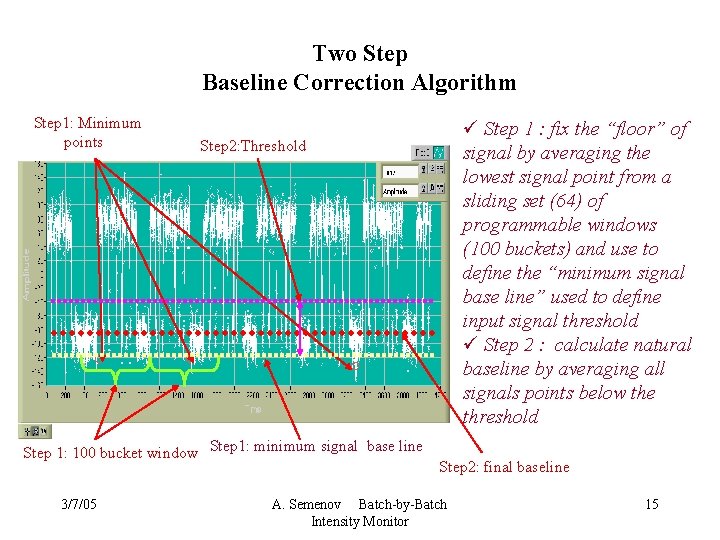

Two Step Baseline Correction Algorithm Step 1: Minimum points Step 2: Threshold Step 1: 100 bucket window Step 1: minimum signal base line 3/7/05 ü Step 1 : fix the “floor” of signal by averaging the lowest signal point from a sliding set (64) of programmable windows (100 buckets) and use to define the “minimum signal base line” used to define input signal threshold ü Step 2 : calculate natural baseline by averaging all signals points below the threshold Step 2: final baseline A. Semenov Batch-by-Batch Intensity Monitor 15

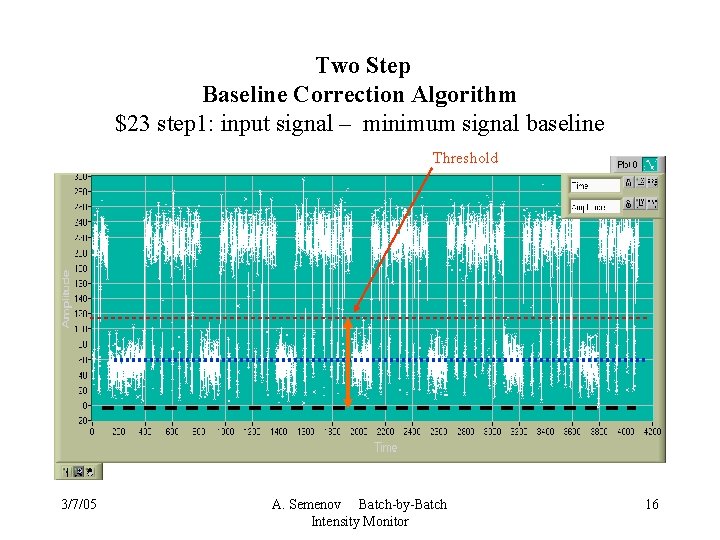

Two Step Baseline Correction Algorithm $23 step 1: input signal – minimum signal baseline Threshold 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 16

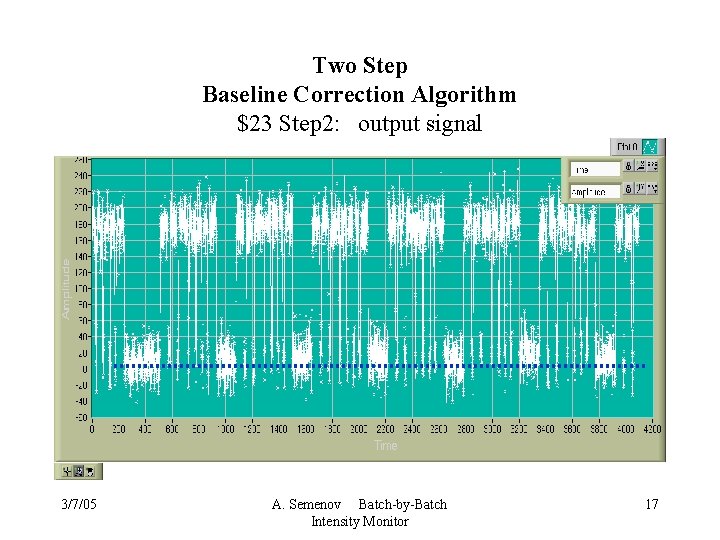

Two Step Baseline Correction Algorithm $23 Step 2: output signal 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 17

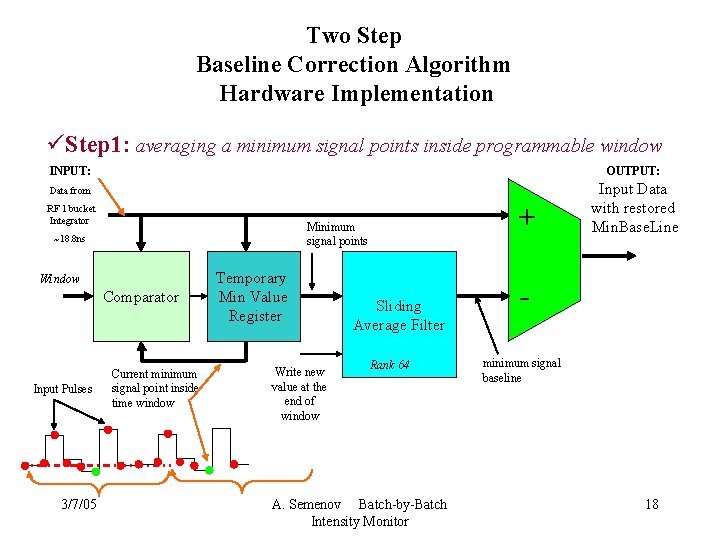

Two Step Baseline Correction Algorithm Hardware Implementation üStep 1: averaging a minimum signal points inside programmable window INPUT: OUTPUT: Data from RF 1 bucket Integrator ~18. 8 ns Window Comparator Input Pulses 3/7/05 + Minimum signal points Current minimum signal point inside time window Temporary Min Value Register Write new value at the end of window Sliding Average Filter Rank 64 A. Semenov Batch-by-Batch Intensity Monitor Input Data with restored Min. Base. Line minimum signal baseline 18

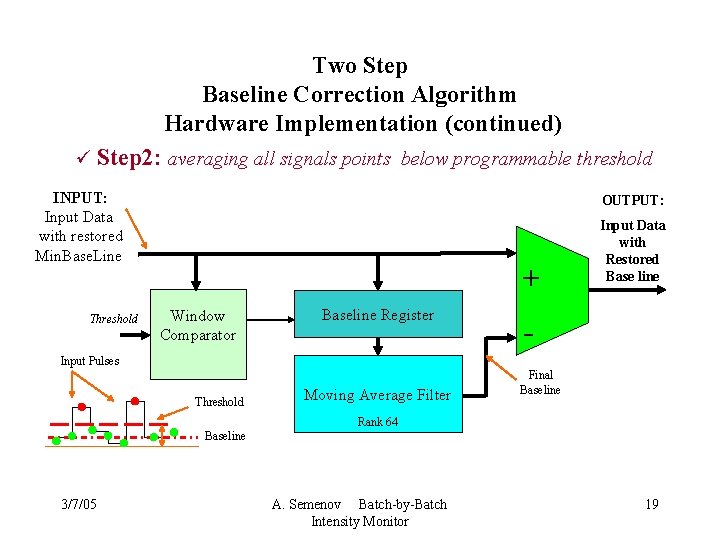

Two Step Baseline Correction Algorithm Hardware Implementation (continued) ü Step 2: averaging all signals points below programmable threshold INPUT: Input Data with restored Min. Base. Line Threshold OUTPUT: + Window Comparator Baseline Register Input Data with Restored Base line - Input Pulses Threshold Moving Average Filter Final Baseline Rank 64 Baseline 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 19

FPGA Design From ADC Intensity (gate #0) RF INT Start TCLK Rev Marker DAC Gate Integrator #0 BLC Stop Mean# Stop >= Beam/No Beam SHARC SPORT 32 bit, 10 Mbit To SHARC DSP Threshold FIFO Start Intensity #0 Mean# Delay Gate Integrator #6 RF, 53 MHz PLL Multiplier Timestamp counter ADC CLOCK 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 20

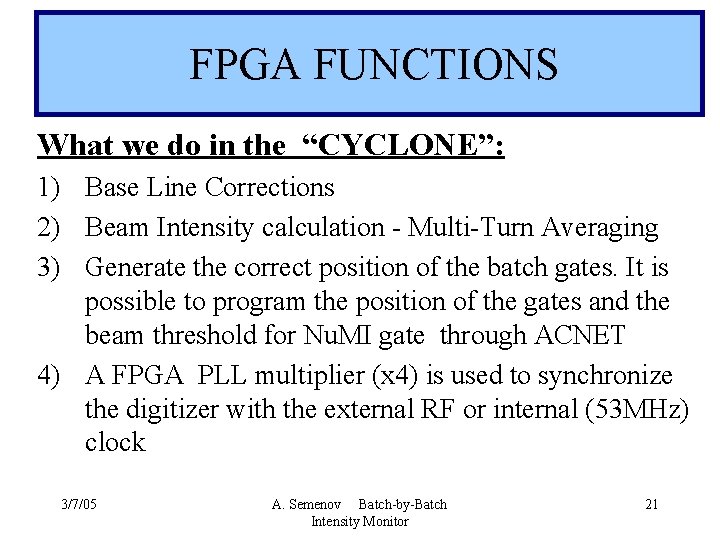

FPGA FUNCTIONS What we do in the “CYCLONE”: 1) Base Line Corrections 2) Beam Intensity calculation - Multi-Turn Averaging 3) Generate the correct position of the batch gates. It is possible to program the position of the gates and the beam threshold for Nu. MI gate through ACNET 4) A FPGA PLL multiplier (x 4) is used to synchronize the digitizer with the external RF or internal (53 MHz) clock 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 21

FPGA FUTURES What we do in the “CYCLONE” (continued): 5) Ability to trigger on TCLK events 6) Multi-Turn “Scope Trace” buffer to analyze input and post-processing signals (4 K samples) 7) 10 Mbit, 32 bit serial interface to SHARC DSP 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 22

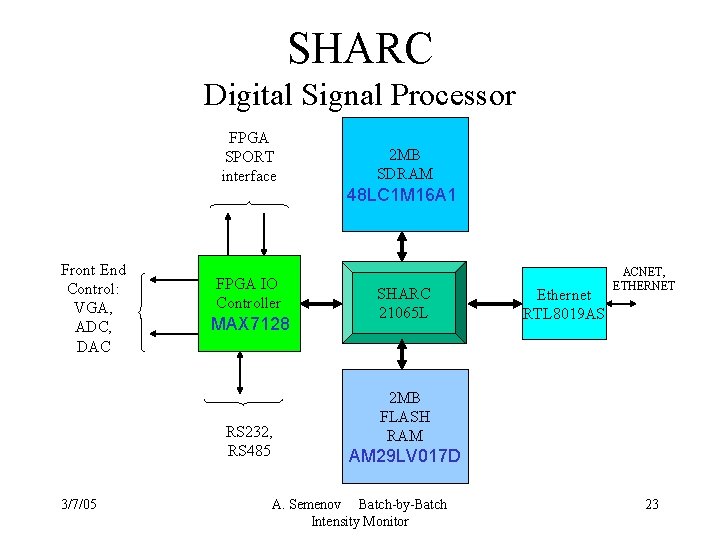

SHARC Digital Signal Processor FPGA SPORT interface Front End Control: VGA, ADC, DAC FPGA IO Controller MAX 7128 RS 232, RS 485 3/7/05 2 MB SDRAM 48 LC 1 M 16 A 1 SHARC 21065 L Ethernet RTL 8019 AS ACNET, ETHERNET 2 MB FLASH RAM AM 29 LV 017 D A. Semenov Batch-by-Batch Intensity Monitor 23

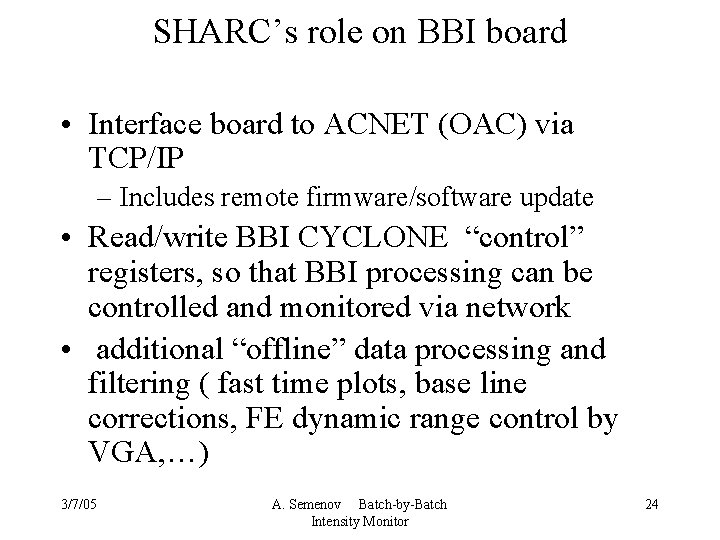

SHARC’s role on BBI board • Interface board to ACNET (OAC) via TCP/IP – Includes remote firmware/software update • Read/write BBI CYCLONE “control” registers, so that BBI processing can be controlled and monitored via network • additional “offline” data processing and filtering ( fast time plots, base line corrections, FE dynamic range control by VGA, …) 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 24

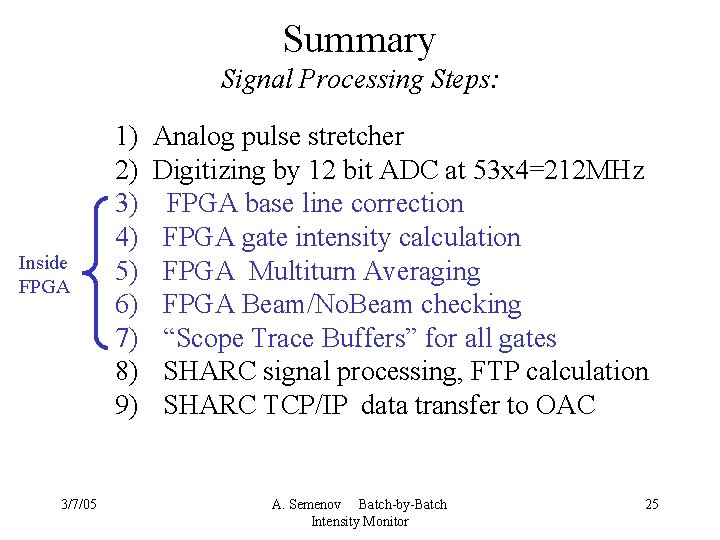

Summary Signal Processing Steps: Inside FPGA 3/7/05 1) Analog pulse stretcher 2) Digitizing by 12 bit ADC at 53 x 4=212 MHz 3) FPGA base line correction 4) FPGA gate intensity calculation 5) FPGA Multiturn Averaging 6) FPGA Beam/No. Beam checking 7) “Scope Trace Buffers” for all gates 8) SHARC signal processing, FTP calculation 9) SHARC TCP/IP data transfer to OAC A. Semenov Batch-by-Batch Intensity Monitor 25

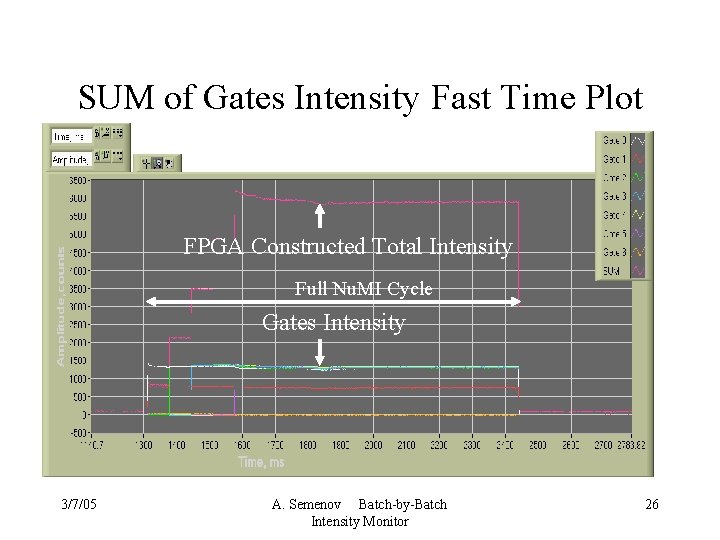

SUM of Gates Intensity Fast Time Plot FPGA Constructed Total Intensity Full Nu. MI Cycle Gates Intensity 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 26

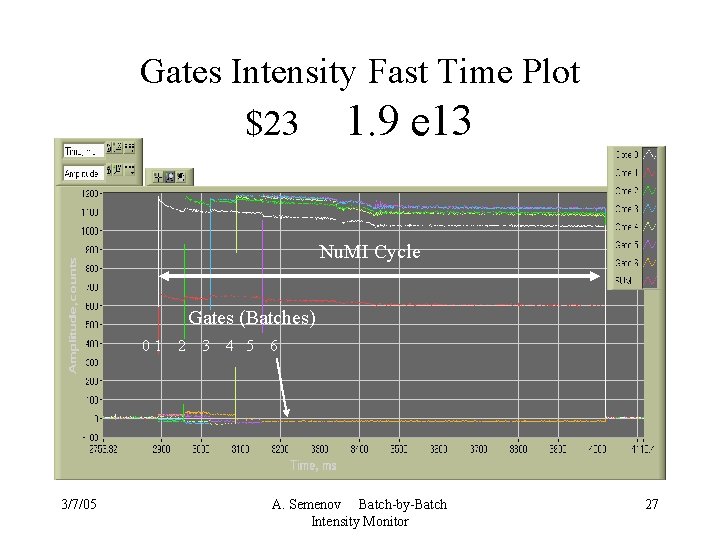

Gates Intensity Fast Time Plot $23 1. 9 e 13 Nu. MI Cycle Gates (Batches) 0 1 2 3 4 5 6 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 27

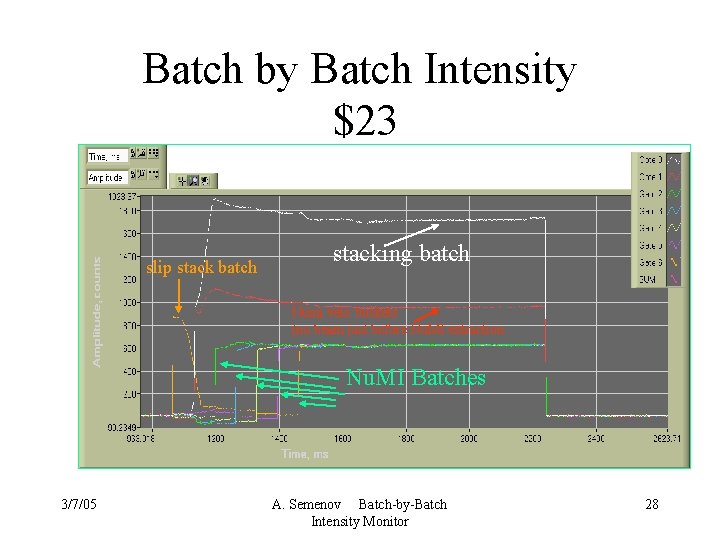

Batch by Batch Intensity $23 slip stack batch stacking batch Numi veto buckets (no beam just before Nu. MI extraction Nu. MI Batches 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 28

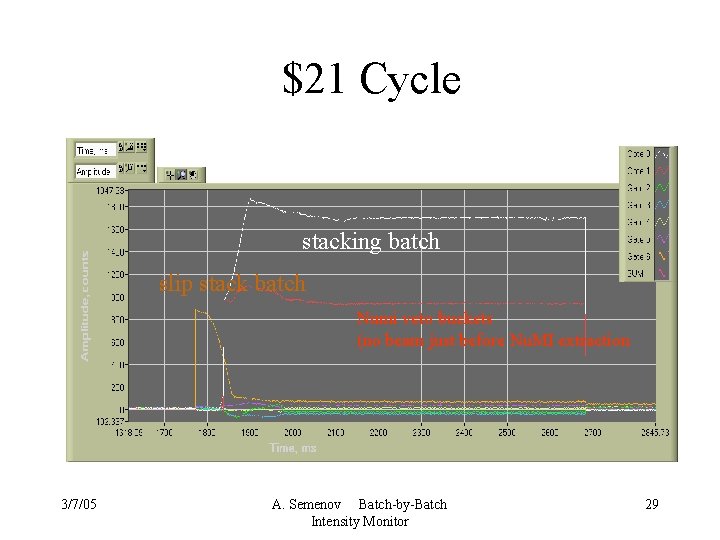

$21 Cycle stacking batch slip stack batch Numi veto buckets (no beam just before Nu. MI extraction 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 29

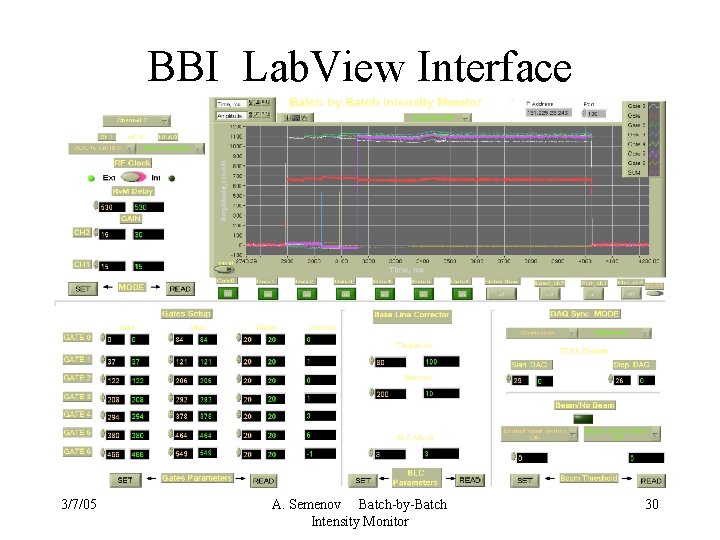

BBI Lab. View Interface 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 30

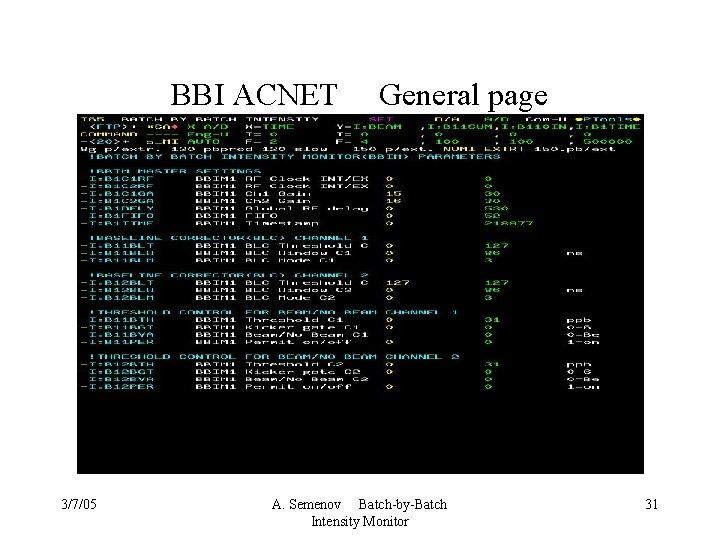

BBI ACNET General page 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 31

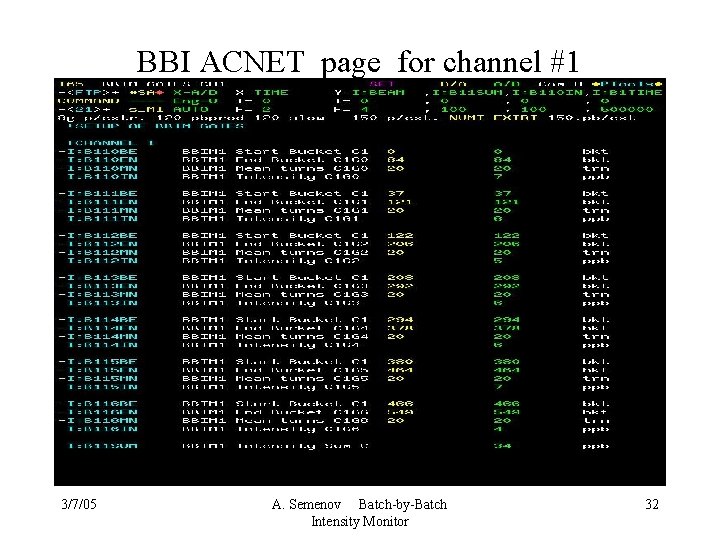

BBI ACNET page for channel #1 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 32

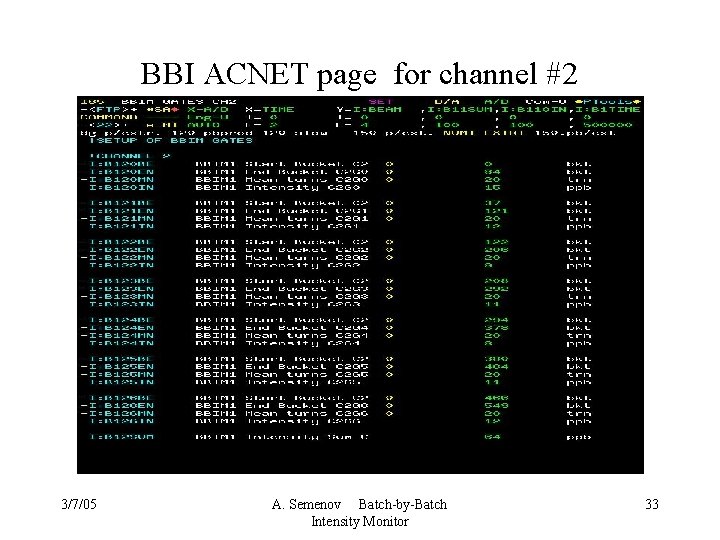

BBI ACNET page for channel #2 3/7/05 A. Semenov Batch-by-Batch Intensity Monitor 33

- Slides: 33