Prof dr Vlado Simeunovi OSNOVE RAUNARSKE TEHNIKE vlado

- Slides: 53

Prof. dr Vlado Simeunović OSNOVE RAČUNARSKE TEHNIKE vlado. simeunovic@gmail. com

Logičke mreže q. STANDARDNI KOMBINACIONI MODULI v Koderi v Dekoderi v Multiplekseri v Demultiplekseri v Sabirači v Aritmetičko-logičke jedinice q STANDARDNI SEKVENCIJALNI MODULI v Registri v Brojači v Memorije

Logičke mreže q Pomoću logičkih ili prekidačkih mreža mogu se ispuniti najrazličitiji funkcionalni zahtevi računarskih sistema. q Često korišćene prekidačke mreže su izdvojene kao standardni moduli. Iako su postupci za njihov razvoj definisani, za njihovo korišćenje i uključivanje u složenije logičke strukture je dovoljno znati veze između ulaza i izlaza. q U zavisnosti od elemenata od kojih su napravljeni, standardni moduli mogu biti: § kombinacioni – sadrže samo logičke elemente (koderi, dekoderi, multiplekseri, demultiplekseri, sabirači, ALU itd. ) § sekvencijalni – osim logičkih, sadrže i memorijske elemente (registri, brojači, memorije itd. )

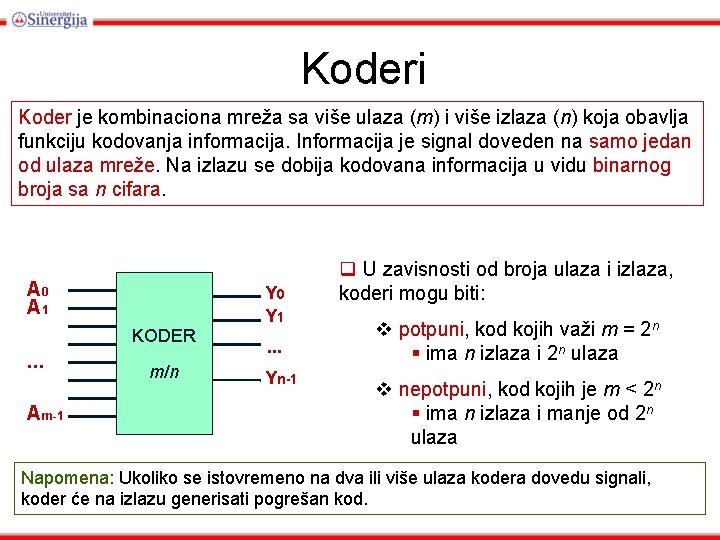

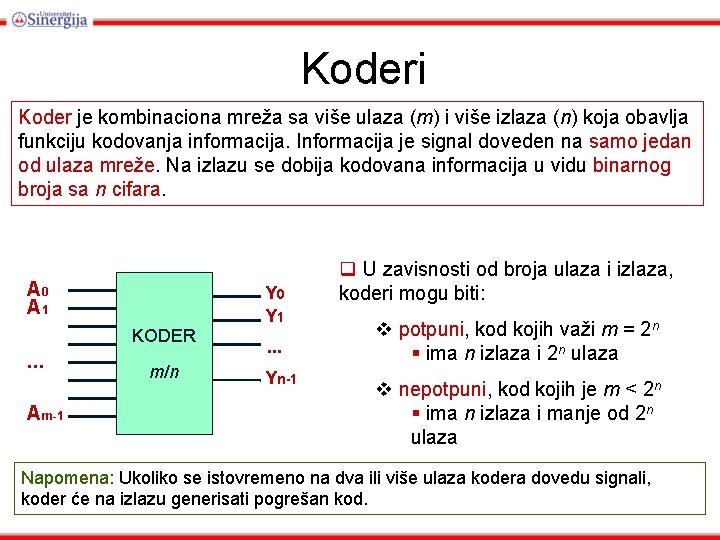

Koderi Koder je kombinaciona mreža sa više ulaza (m) i više izlaza (n) koja obavlja funkciju kodovanja informacija. Informacija je signal doveden na samo jedan od ulaza mreže. Na izlazu se dobija kodovana informacija u vidu binarnog broja sa n cifara. A A 0 A 1 KODER . . . Am-1 m/n Y 0 Y 1. . . Yn-1 B C q U zavisnosti od broja ulaza i izlaza, koderi mogu biti: v potpuni, kod kojih važi m = 2 n § ima n izlaza i 2 n ulaza v nepotpuni, kod kojih je m < 2 n § ima n izlaza i manje od 2 n ulaza Napomena: Ukoliko se istovremeno na dva ili više ulaza kodera dovedu signali, koder će na izlazu generisati pogrešan kod.

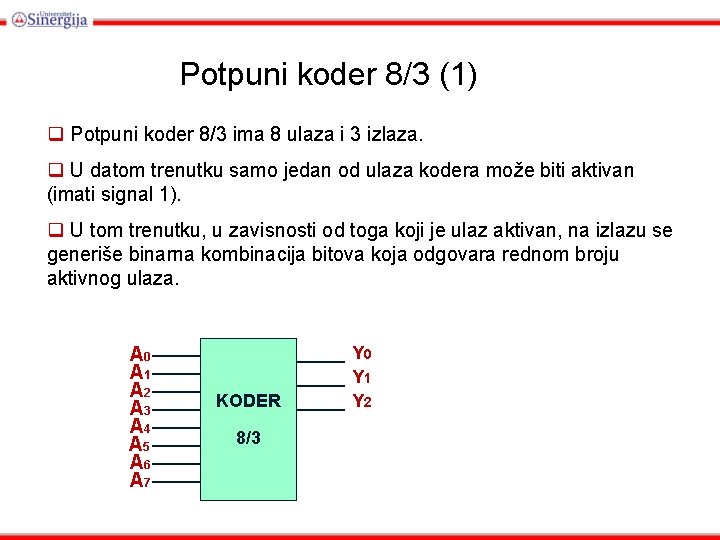

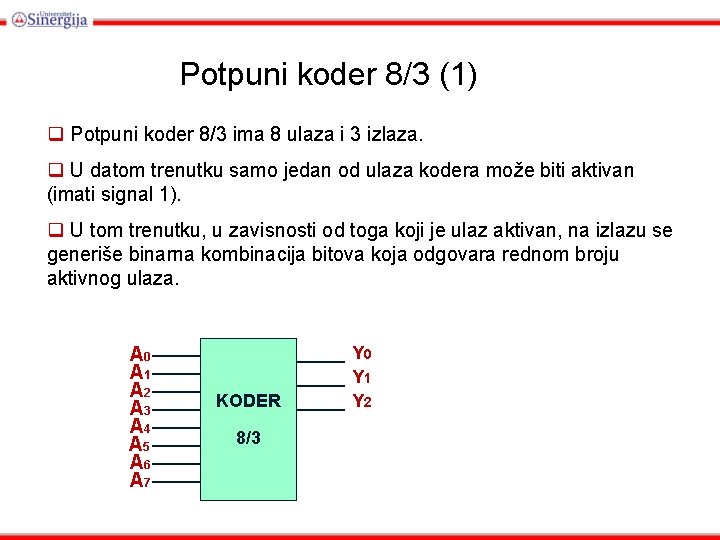

Potpuni koder 8/3 (1) q Potpuni koder 8/3 ima 8 ulaza i 3 izlaza. q U datom trenutku samo jedan od ulaza kodera može biti aktivan (imati signal 1). q U tom trenutku, u zavisnosti od toga koji je ulaz aktivan, na izlazu se generiše binarna kombinacija bitova koja odgovara rednom broju aktivnog ulaza. A 0 A 1 A 2 A 3 A 4 A 5 A 6 A 7 KODER 8/3 Y 0 Y 1 Y 2

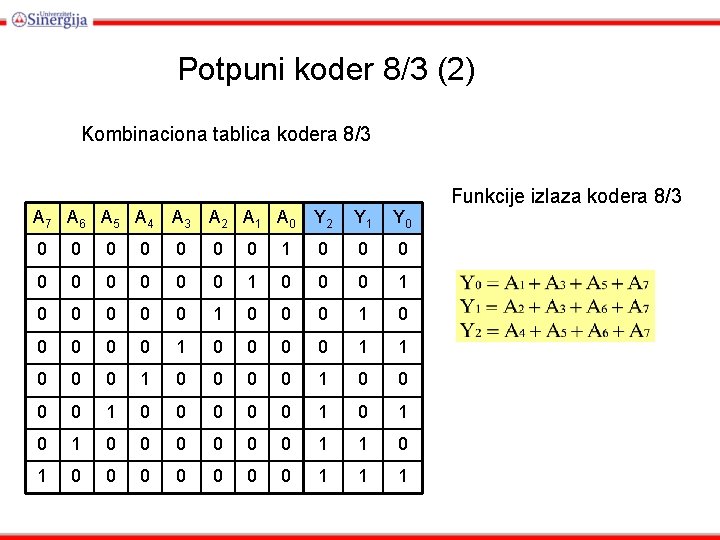

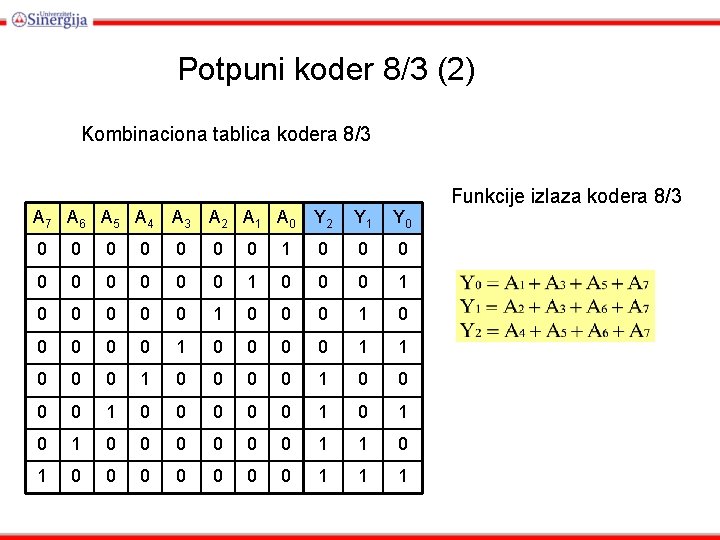

Potpuni koder 8/3 (2) Kombinaciona tablica kodera 8/3 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 Y 2 Y 1 Y 0 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 0 0 0 0 1 0 1 0 0 0 1 1 0 0 0 0 1 1 1 Funkcije izlaza kodera 8/3

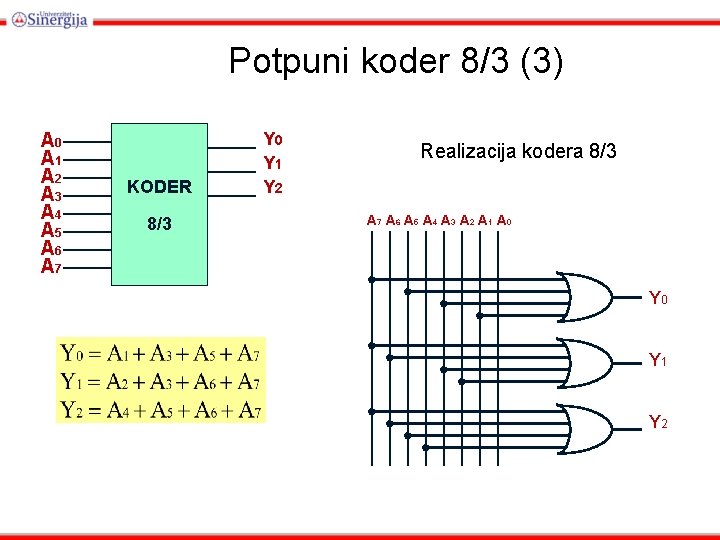

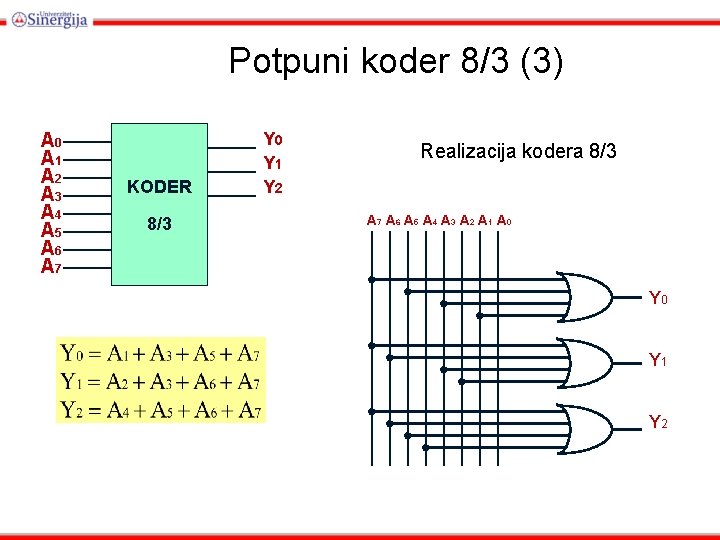

Potpuni koder 8/3 (3) A 0 A 1 A 2 A 3 A 4 A 5 A 6 A 7 KODER 8/3 Y 0 Y 1 Y 2 Realizacija kodera 8/3 A 7 A 6 A 5 A 4 A 3 A 2 A 1 A 0 Y 1 Y 2

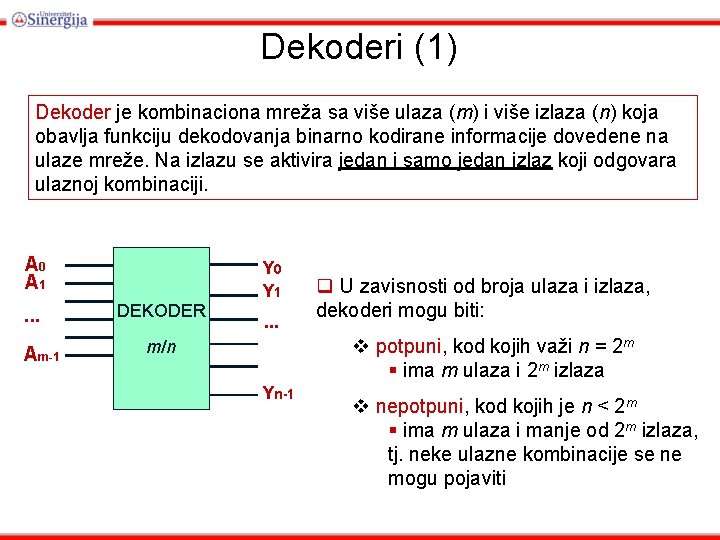

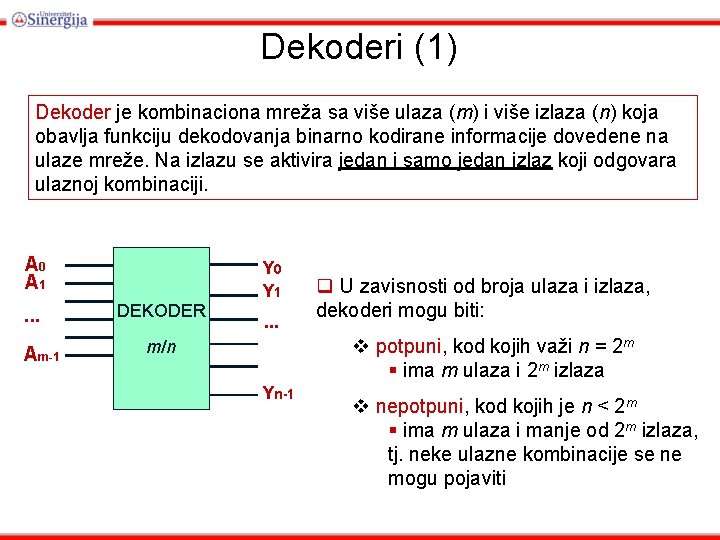

Dekoderi (1) Dekoder je kombinaciona mreža sa više ulaza (m) i više izlaza (n) koja obavlja funkciju dekodovanja binarno kodirane informacije dovedene na ulaze mreže. Na izlazu se aktivira jedan i samo jedan izlaz koji odgovara ulaznoj kombinaciji. A 0 A 1. . . Am-1 DEKODER Y 0 Y 1. . . q U zavisnosti od broja ulaza i izlaza, dekoderi mogu biti: v potpuni, kod kojih važi n = 2 m § ima m ulaza i 2 m izlaza m/n Yn-1 v nepotpuni, kod kojih je n < 2 m § ima m ulaza i manje od 2 m izlaza, tj. neke ulazne kombinacije se ne mogu pojaviti

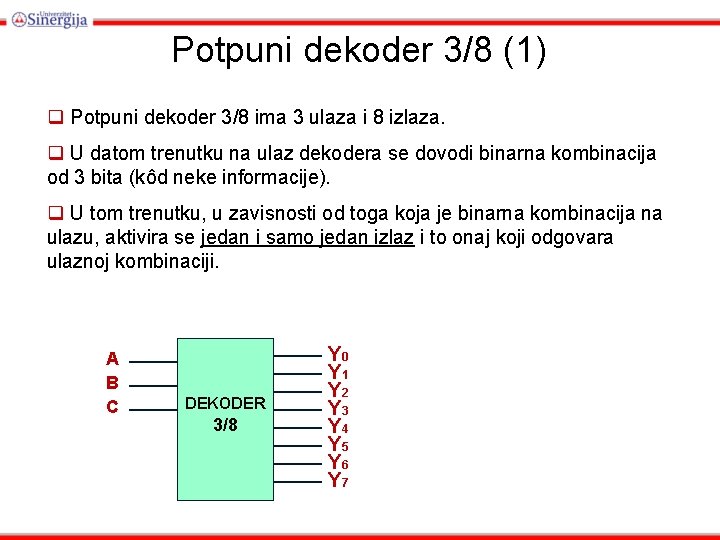

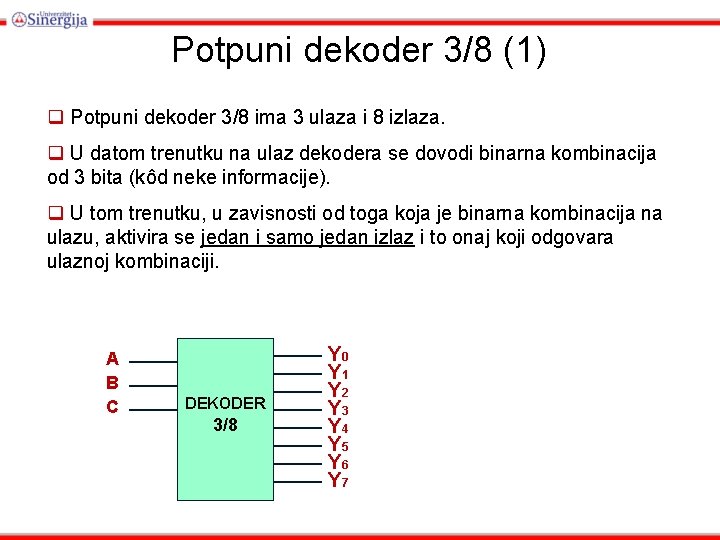

Potpuni dekoder 3/8 (1) q Potpuni dekoder 3/8 ima 3 ulaza i 8 izlaza. q U datom trenutku na ulaz dekodera se dovodi binarna kombinacija od 3 bita (kôd neke informacije). q U tom trenutku, u zavisnosti od toga koja je binarna kombinacija na ulazu, aktivira se jedan i samo jedan izlaz i to onaj koji odgovara ulaznoj kombinaciji. A B C DEKODER 3/8 Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7

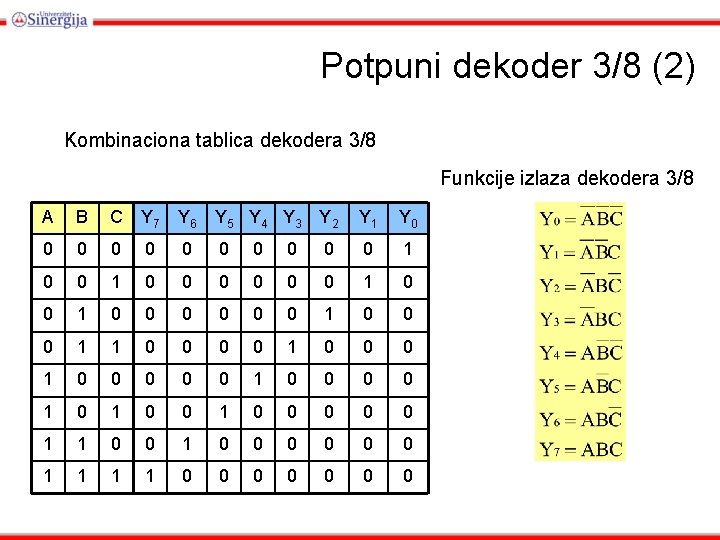

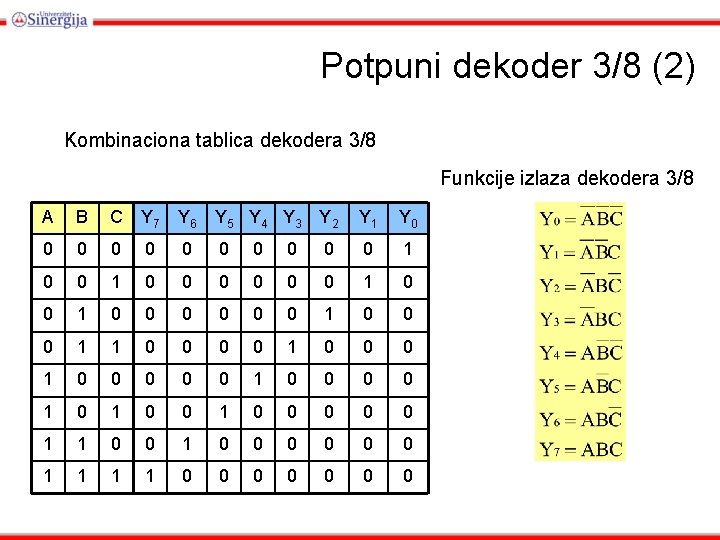

Potpuni dekoder 3/8 (2) Kombinaciona tablica dekodera 3/8 Funkcije izlaza dekodera 3/8 A B C Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 0 0 1 0 0 0 0 0 0 1 1 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 0 0 0

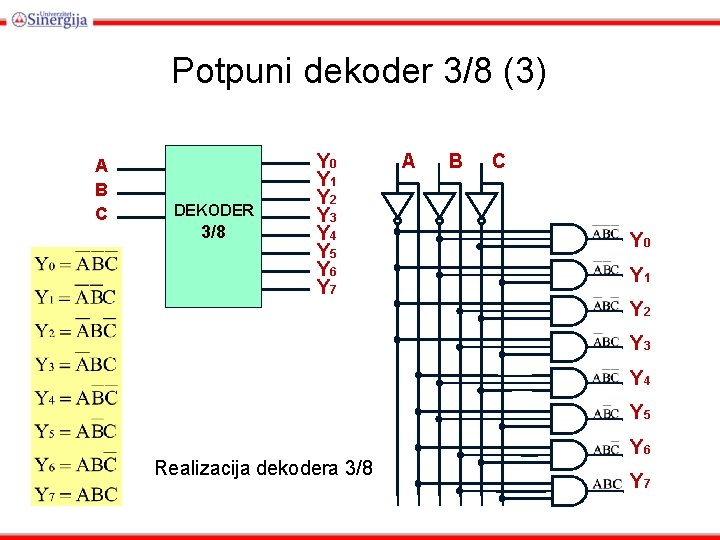

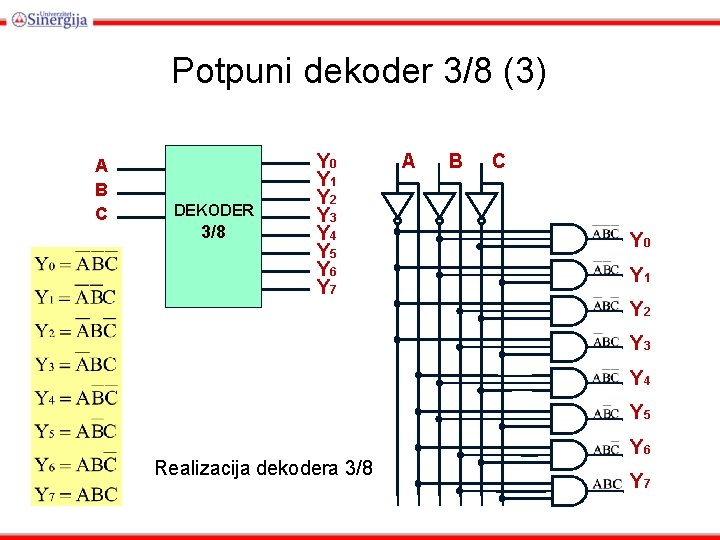

Potpuni dekoder 3/8 (3) A B C DEKODER 3/8 Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7 A B C Y 0 Y 1 Y 2 Y 3 Y 4 Y 5 Realizacija dekodera 3/8 Y 6 Y 7

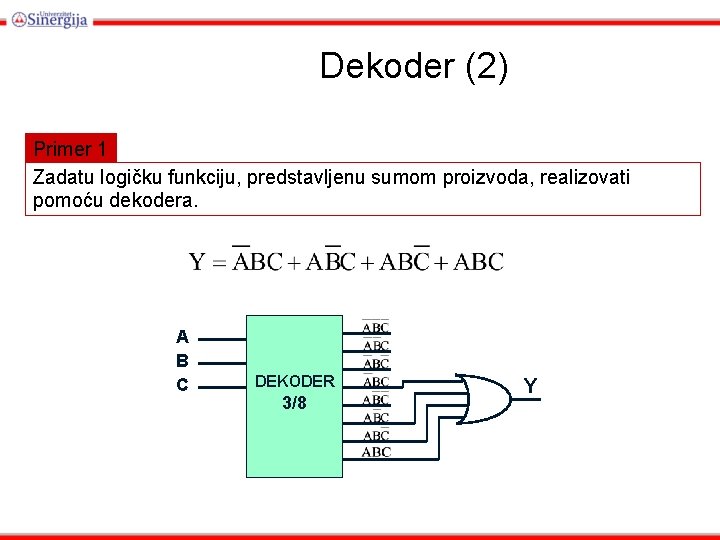

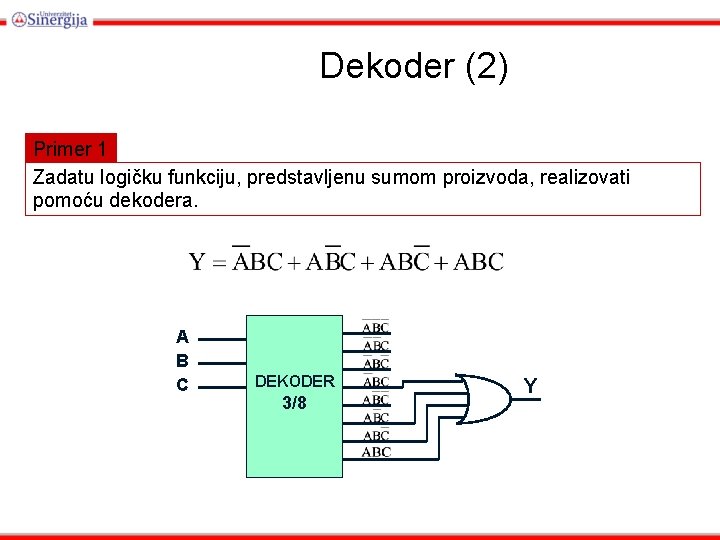

Dekoder (2) Primer 1 Zadatu logičku funkciju, predstavljenu sumom proizvoda, realizovati pomoću dekodera. A B C DEKODER 3/8 Y

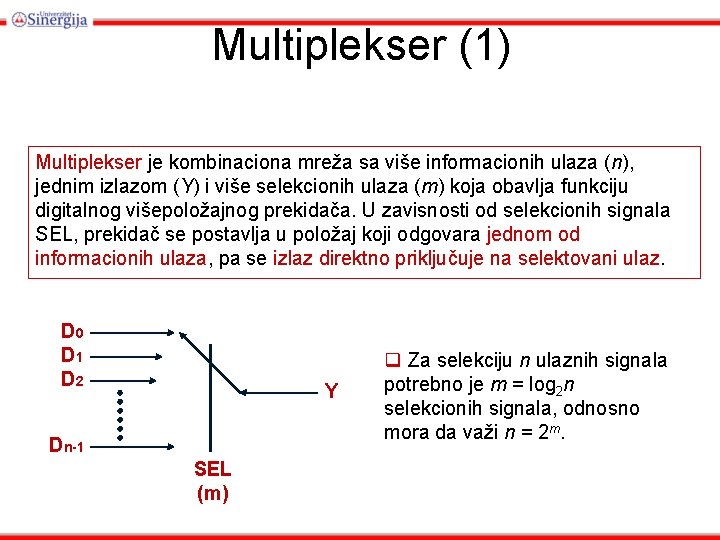

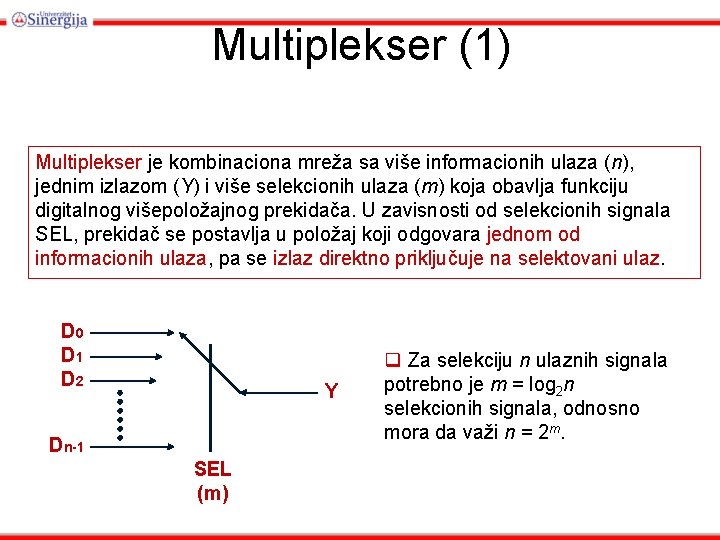

Multiplekser (1) Multiplekser je kombinaciona mreža sa više informacionih ulaza (n), jednim izlazom (Y) i više selekcionih ulaza (m) koja obavlja funkciju digitalnog višepoložajnog prekidača. U zavisnosti od selekcionih signala SEL, prekidač se postavlja u položaj koji odgovara jednom od informacionih ulaza, pa se izlaz direktno priključuje na selektovani ulaz. D 0 D 1 D 2 Y Dn-1 SEL (m) q Za selekciju n ulaznih signala potrebno je m = log 2 n selekcionih signala, odnosno mora da važi n = 2 m.

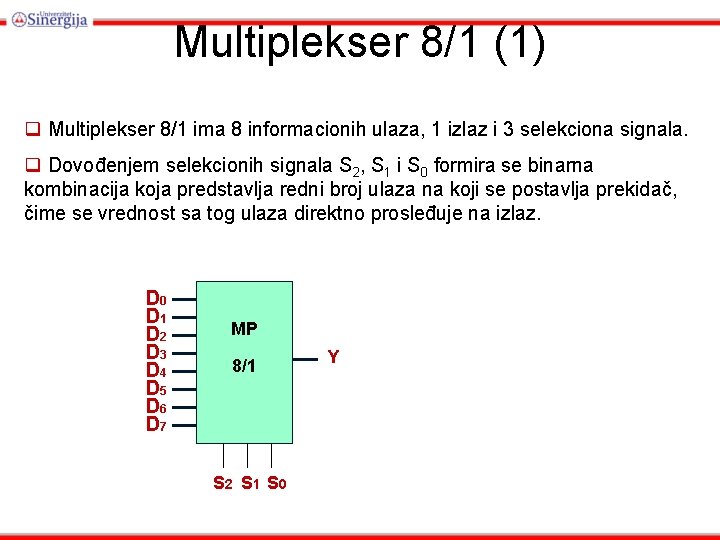

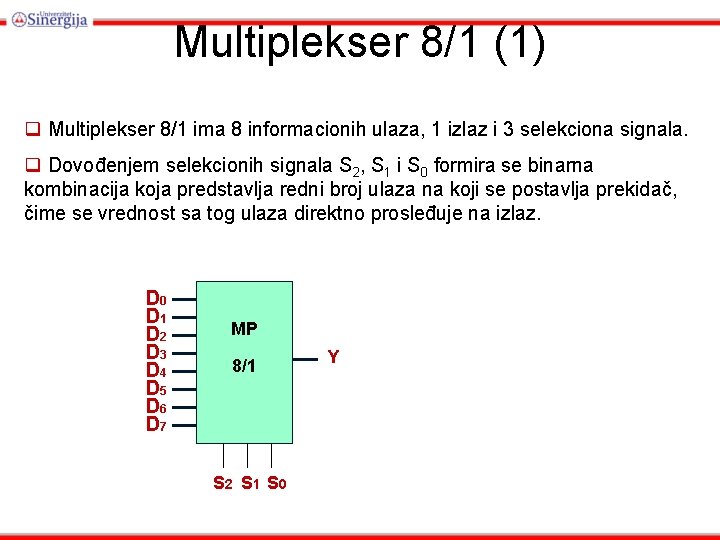

Multiplekser 8/1 (1) q Multiplekser 8/1 ima 8 informacionih ulaza, 1 izlaz i 3 selekciona signala. q Dovođenjem selekcionih signala S 2, S 1 i S 0 formira se binarna kombinacija koja predstavlja redni broj ulaza na koji se postavlja prekidač, čime se vrednost sa tog ulaza direktno prosleđuje na izlaz. D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 MP 8/1 S 2 S 1 S 0 Y

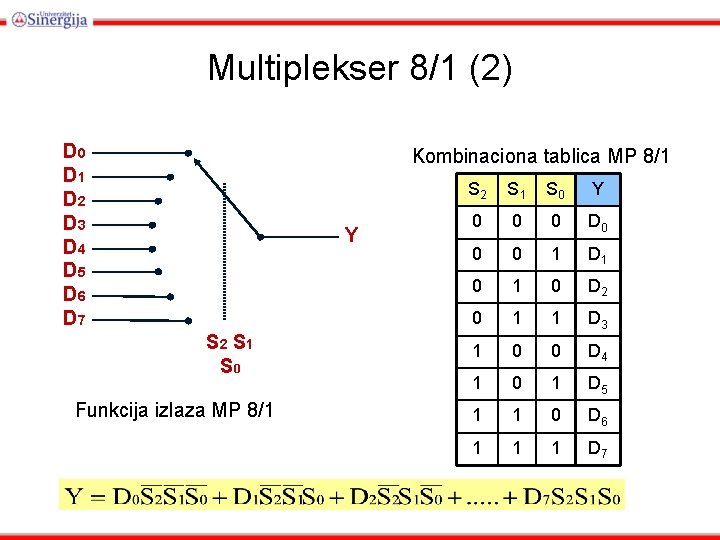

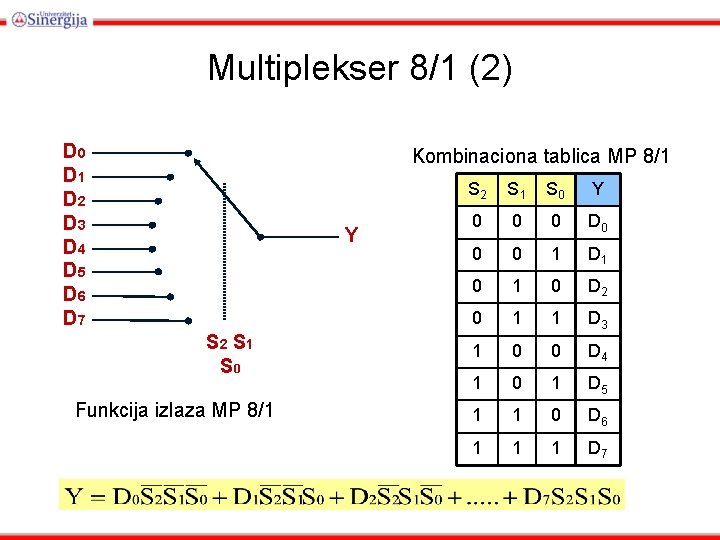

Multiplekser 8/1 (2) D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 Kombinaciona tablica MP 8/1 Y S 2 S 1 S 0 Funkcija izlaza MP 8/1 S 2 S 1 S 0 Y 0 0 0 D 0 0 0 1 D 1 0 D 2 0 1 1 D 3 1 0 0 D 4 1 0 1 D 5 1 1 0 D 6 1 1 1 D 7

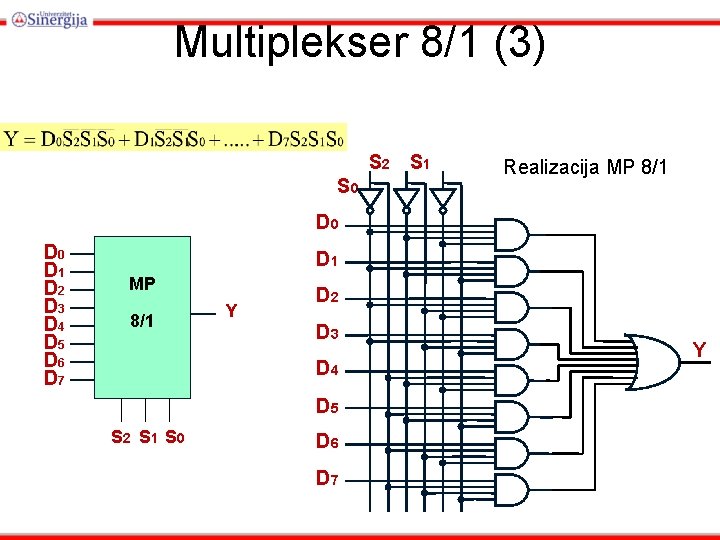

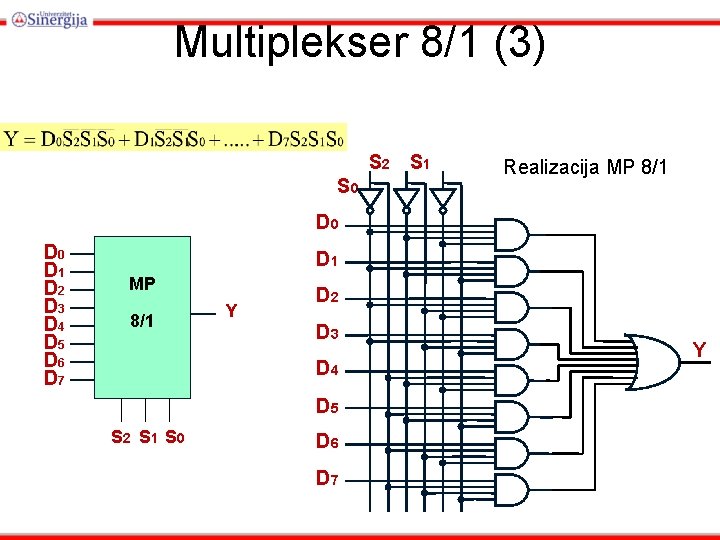

Multiplekser 8/1 (3) S 2 S 0 S 1 Realizacija MP 8/1 D 0 D 1 D 2 D 3 D 4 D 5 D 6 D 7 D 1 MP 8/1 Y D 2 D 3 D 4 D 5 S 2 S 1 S 0 D 6 D 7 Y

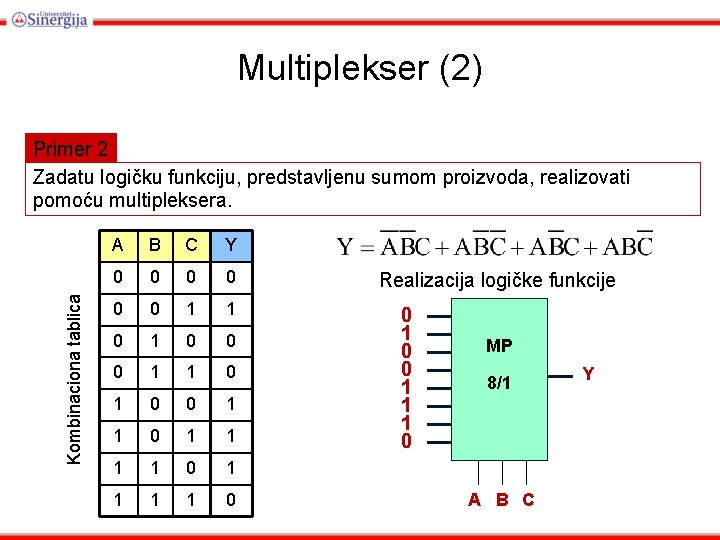

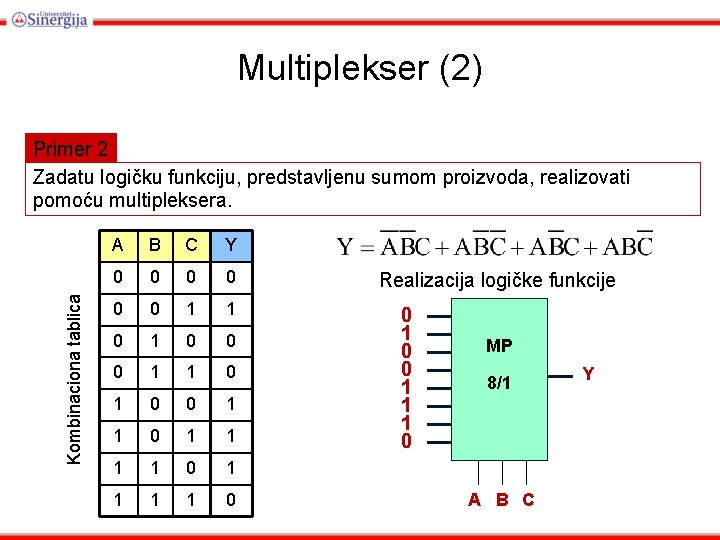

Multiplekser (2) Kombinaciona tablica Primer 2 Zadatu logičku funkciju, predstavljenu sumom proizvoda, realizovati pomoću multipleksera. A B C Y 0 0 0 1 1 0 1 1 1 1 0 Realizacija logičke funkcije 0 1 0 0 1 1 1 0 MP 8/1 A B C Y

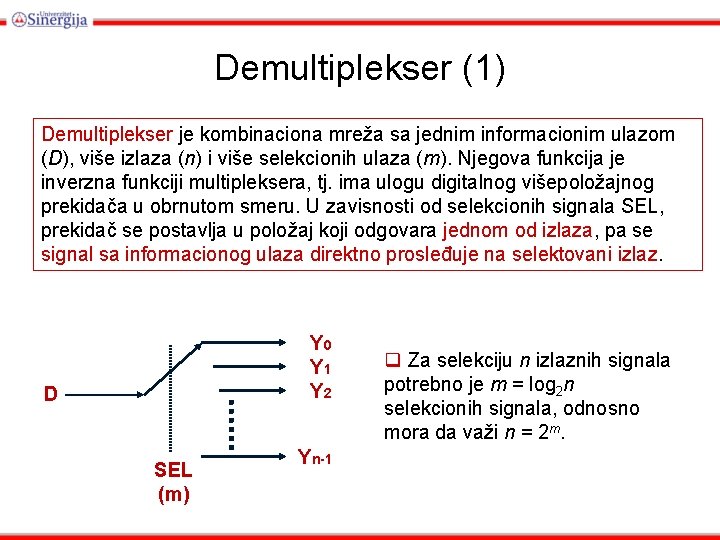

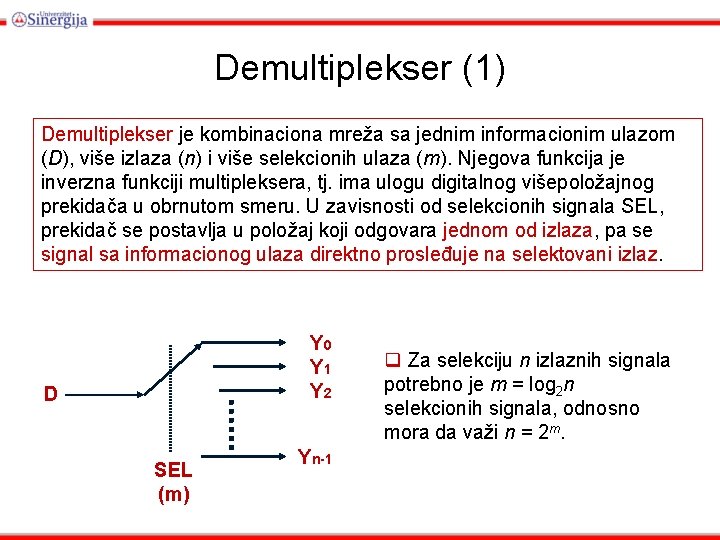

Demultiplekser (1) Demultiplekser je kombinaciona mreža sa jednim informacionim ulazom (D), više izlaza (n) i više selekcionih ulaza (m). Njegova funkcija je inverzna funkciji multipleksera, tj. ima ulogu digitalnog višepoložajnog prekidača u obrnutom smeru. U zavisnosti od selekcionih signala SEL, prekidač se postavlja u položaj koji odgovara jednom od izlaza, pa se signal sa informacionog ulaza direktno prosleđuje na selektovani izlaz. Y 0 Y 1 Y 2 D SEL (m) Yn-1 q Za selekciju n izlaznih signala potrebno je m = log 2 n selekcionih signala, odnosno mora da važi n = 2 m.

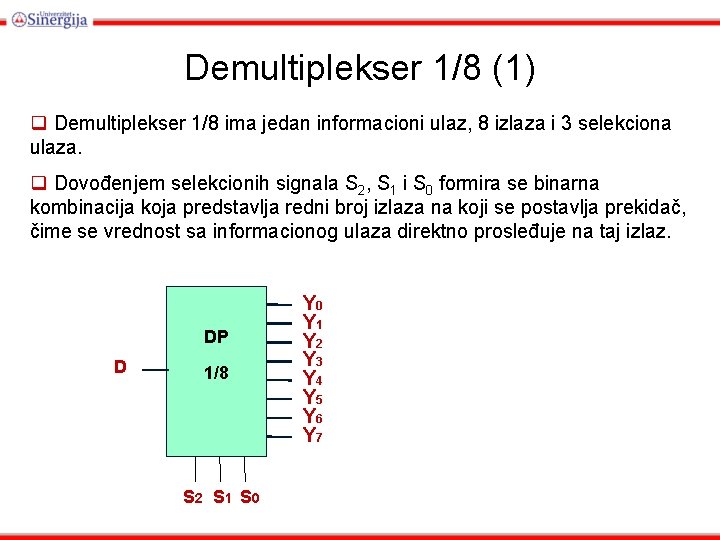

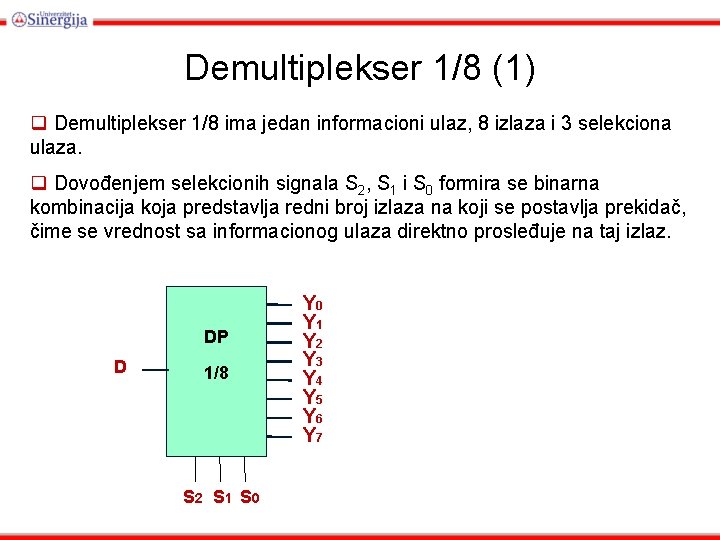

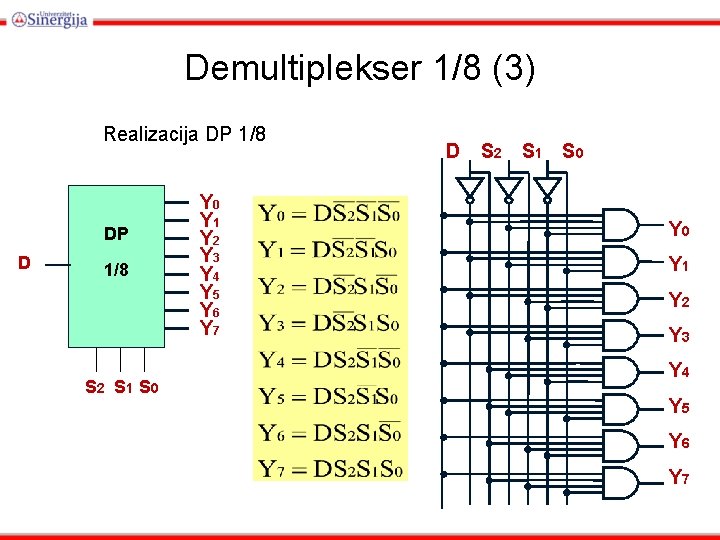

Demultiplekser 1/8 (1) q Demultiplekser 1/8 ima jedan informacioni ulaz, 8 izlaza i 3 selekciona ulaza. q Dovođenjem selekcionih signala S 2, S 1 i S 0 formira se binarna kombinacija koja predstavlja redni broj izlaza na koji se postavlja prekidač, čime se vrednost sa informacionog ulaza direktno prosleđuje na taj izlaz. DP D 1/8 S 2 S 1 S 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7

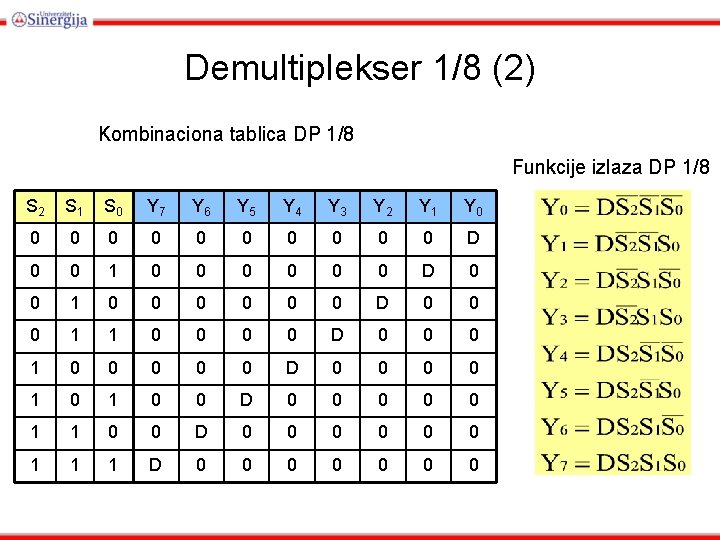

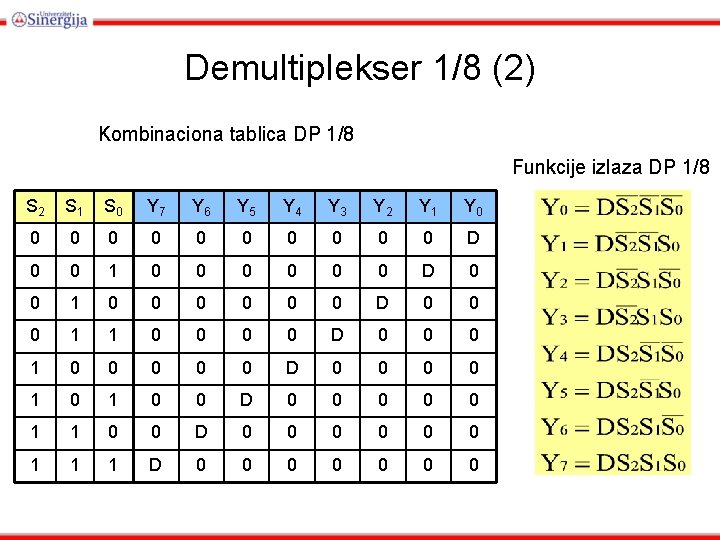

Demultiplekser 1/8 (2) Kombinaciona tablica DP 1/8 Funkcije izlaza DP 1/8 S 2 S 1 S 0 Y 7 Y 6 Y 5 Y 4 Y 3 Y 2 Y 1 Y 0 0 0 D 0 0 1 0 0 0 D 0 0 0 1 1 0 0 D 0 0 0 1 0 0 0 D 0 0 1 0 0 D 0 0 0 1 1 1 D 0 0 0 0

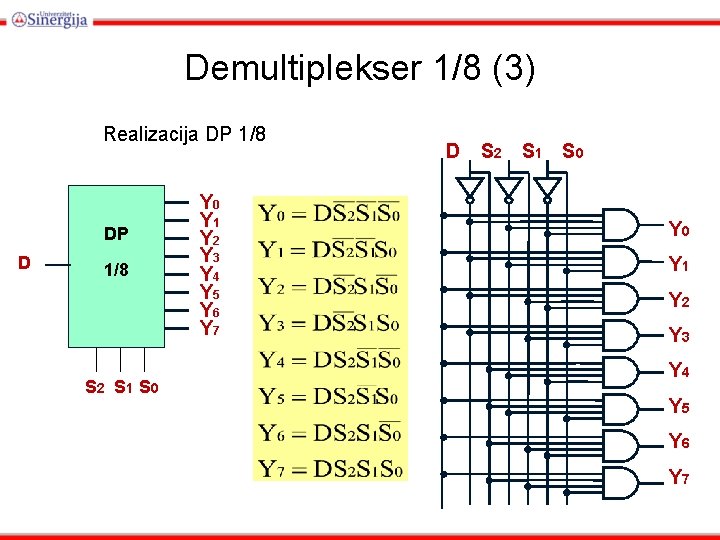

Demultiplekser 1/8 (3) Realizacija DP 1/8 DP D 1/8 S 2 S 1 S 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7 D S 2 S 1 S 0 Y 1 Y 2 Y 3 Y 4 Y 5 Y 6 Y 7

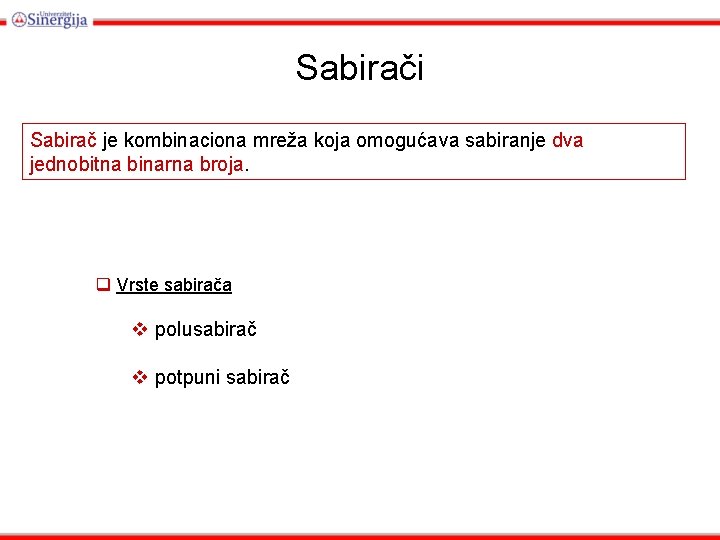

Sabirači Sabirač je kombinaciona mreža koja omogućava sabiranje dva jednobitna binarna broja. q Vrste sabirača v polusabirač v potpuni sabirač

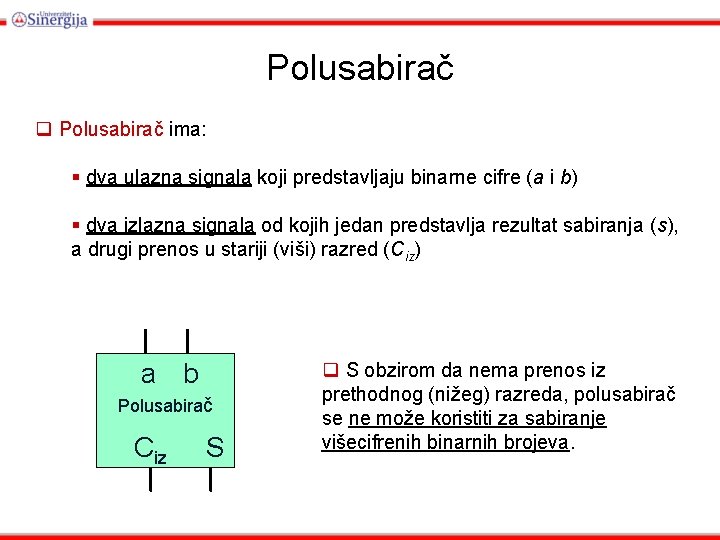

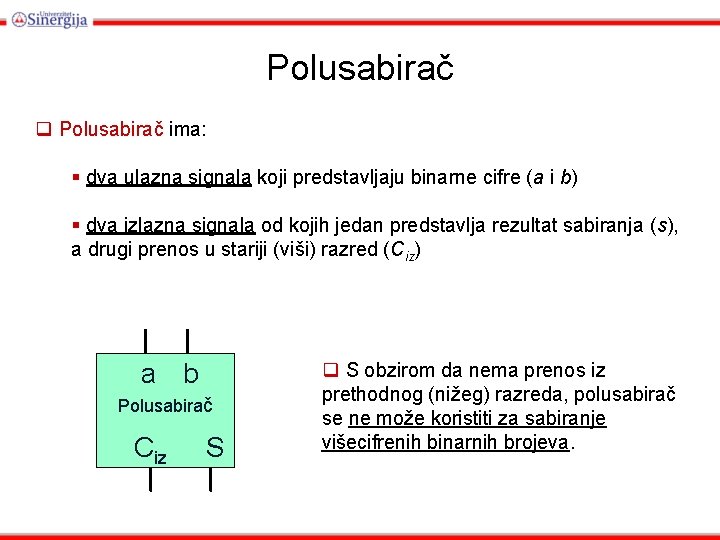

Polusabirač q Polusabirač ima: § dva ulazna signala koji predstavljaju binarne cifre (a i b) § dva izlazna signala od kojih jedan predstavlja rezultat sabiranja (s), a drugi prenos u stariji (viši) razred (Ciz) a b Polusabirač Ciz S q S obzirom da nema prenos iz prethodnog (nižeg) razreda, polusabirač se ne može koristiti za sabiranje višecifrenih binarnih brojeva.

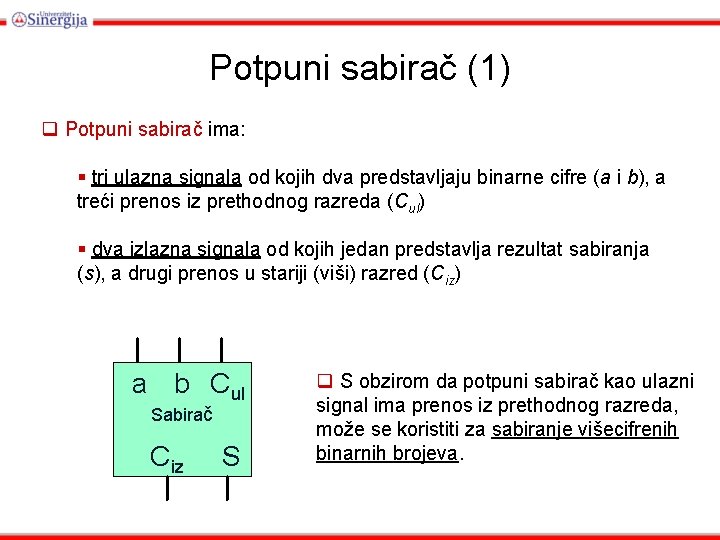

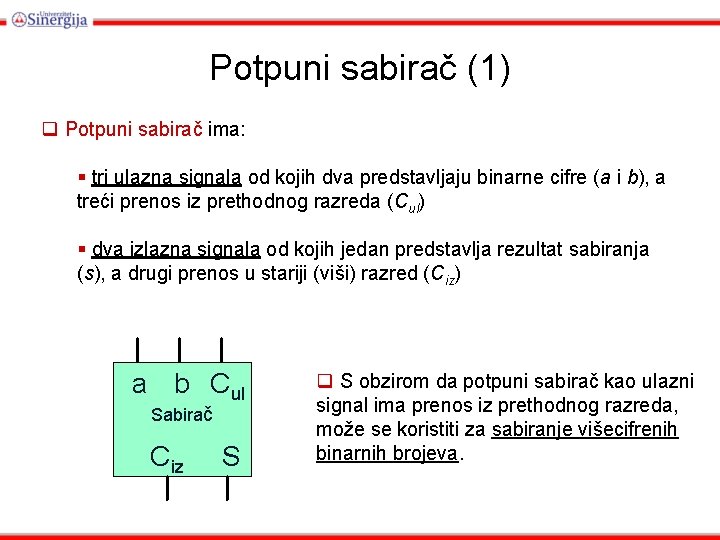

Potpuni sabirač (1) q Potpuni sabirač ima: § tri ulazna signala od kojih dva predstavljaju binarne cifre (a i b), a treći prenos iz prethodnog razreda (Cul) § dva izlazna signala od kojih jedan predstavlja rezultat sabiranja (s), a drugi prenos u stariji (viši) razred (Ciz) a b Cul Sabirač Ciz S q S obzirom da potpuni sabirač kao ulazni signal ima prenos iz prethodnog razreda, može se koristiti za sabiranje višecifrenih binarnih brojeva.

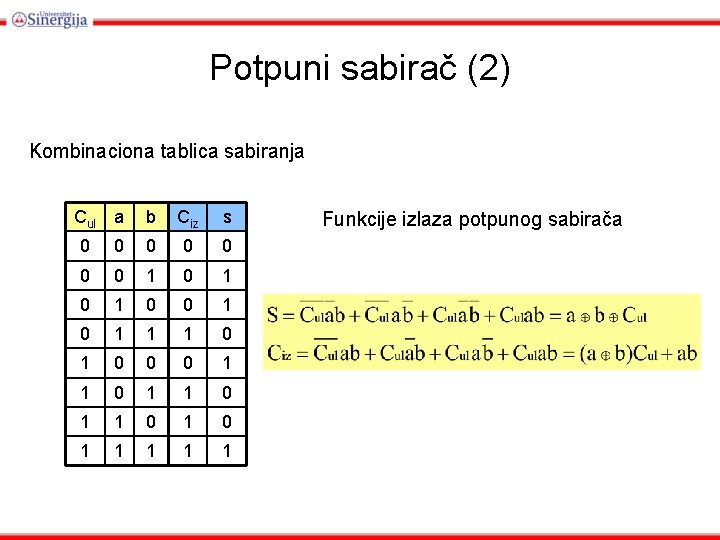

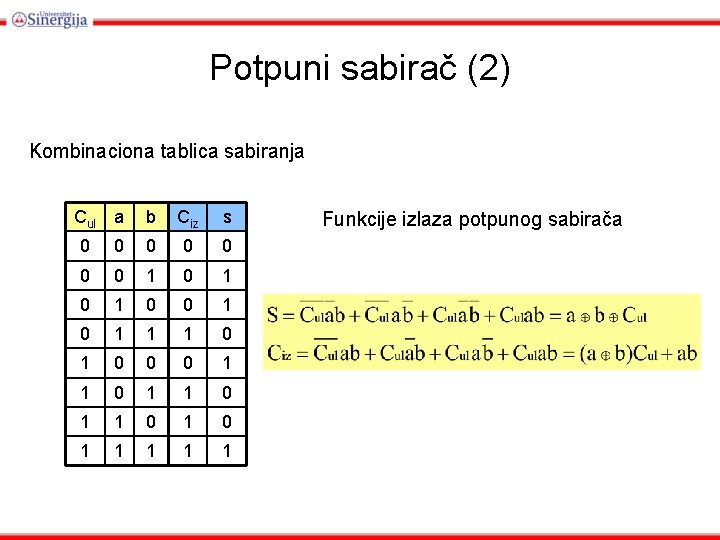

Potpuni sabirač (2) Kombinaciona tablica sabiranja Cul a b Ciz s 0 0 0 0 1 0 1 0 1 1 1 0 0 0 1 1 0 1 1 1 Funkcije izlaza potpunog sabirača

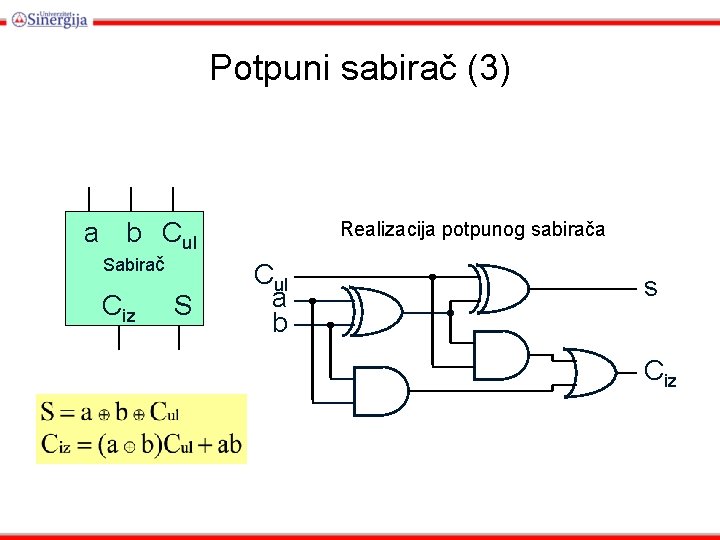

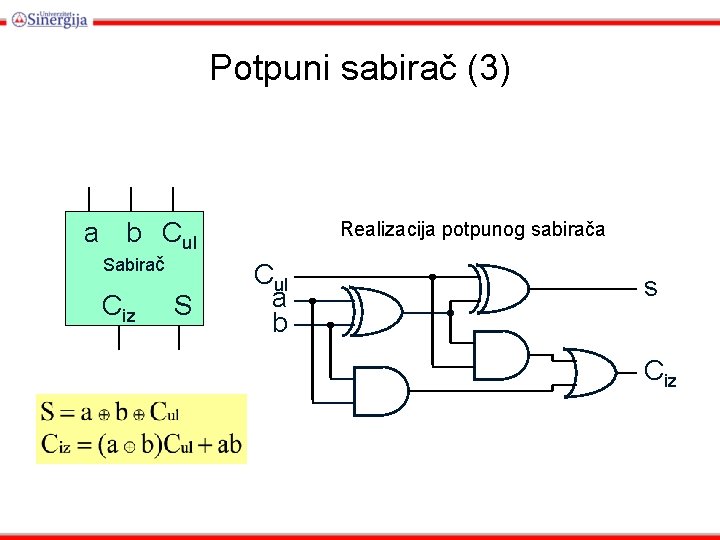

Potpuni sabirač (3) a b Cul Sabirač Ciz S Realizacija potpunog sabirača Cul a b s Ciz

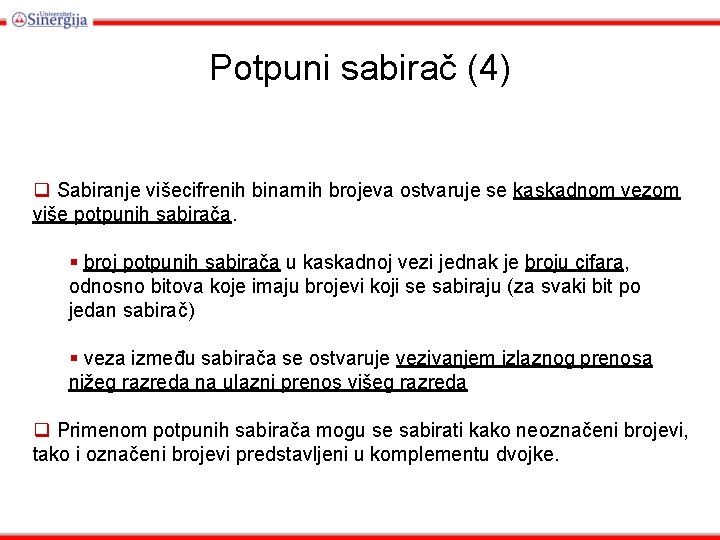

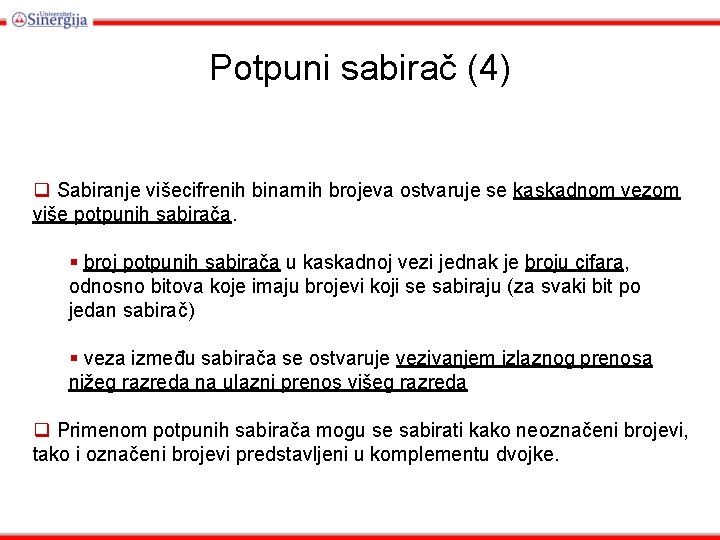

Potpuni sabirač (4) q Sabiranje višecifrenih binarnih brojeva ostvaruje se kaskadnom vezom više potpunih sabirača. § broj potpunih sabirača u kaskadnoj vezi jednak je broju cifara, odnosno bitova koje imaju brojevi koji se sabiraju (za svaki bit po jedan sabirač) § veza između sabirača se ostvaruje vezivanjem izlaznog prenosa nižeg razreda na ulazni prenos višeg razreda q Primenom potpunih sabirača mogu se sabirati kako neoznačeni brojevi, tako i označeni brojevi predstavljeni u komplementu dvojke.

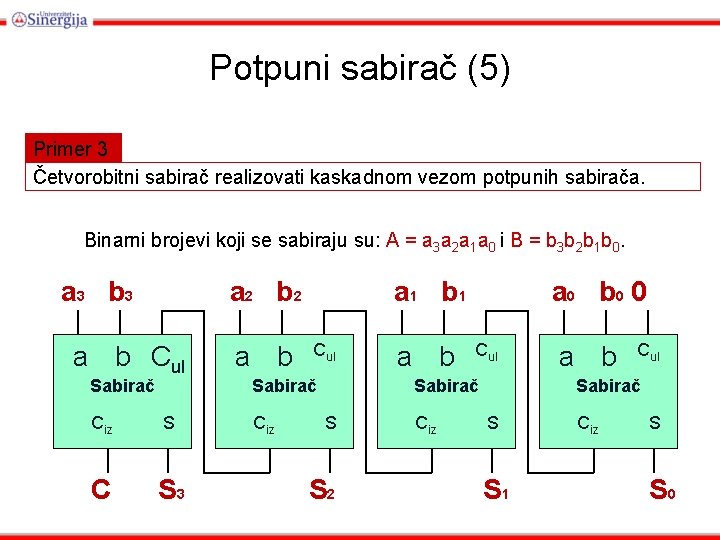

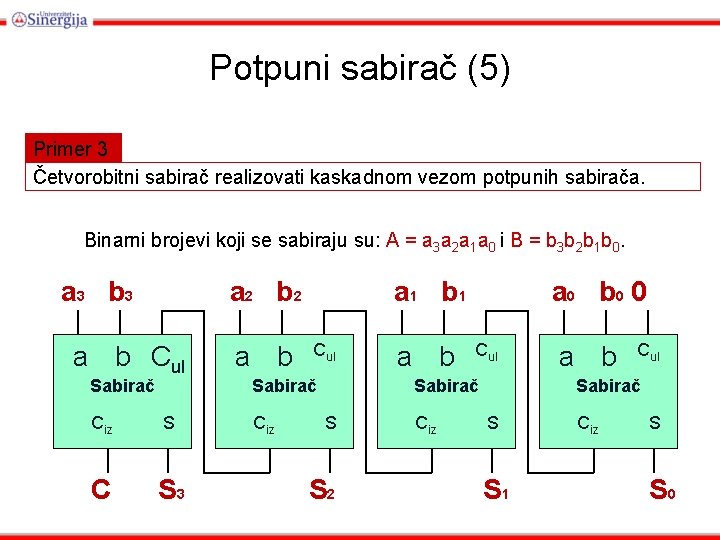

Potpuni sabirač (5) Primer 3 Četvorobitni sabirač realizovati kaskadnom vezom potpunih sabirača. Binarni brojevi koji se sabiraju su: A = a 3 a 2 a 1 a 0 i B = b 3 b 2 b 1 b 0. a 3 b 3 a 2 b 2 a b Cul Sabirač Ciz S C S 3 a b a 1 b 1 Cul Sabirač Ciz a b a 0 b 0 0 Cul Sabirač S S 2 Ciz a b Cul Sabirač S S 1 Ciz S S 0

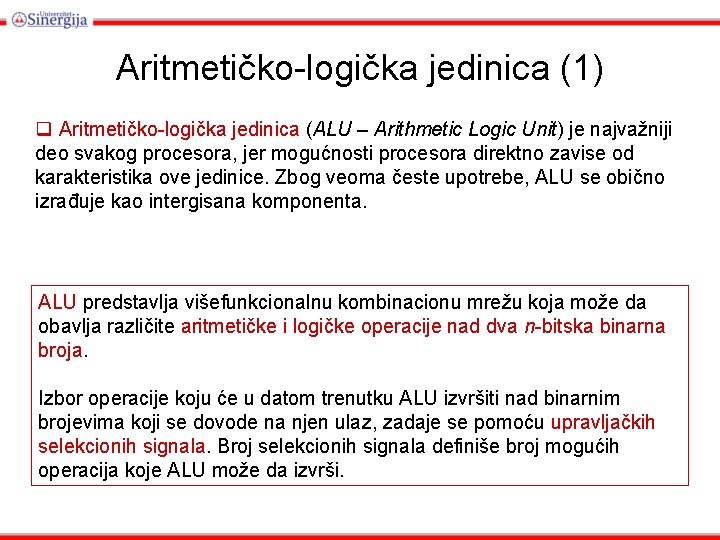

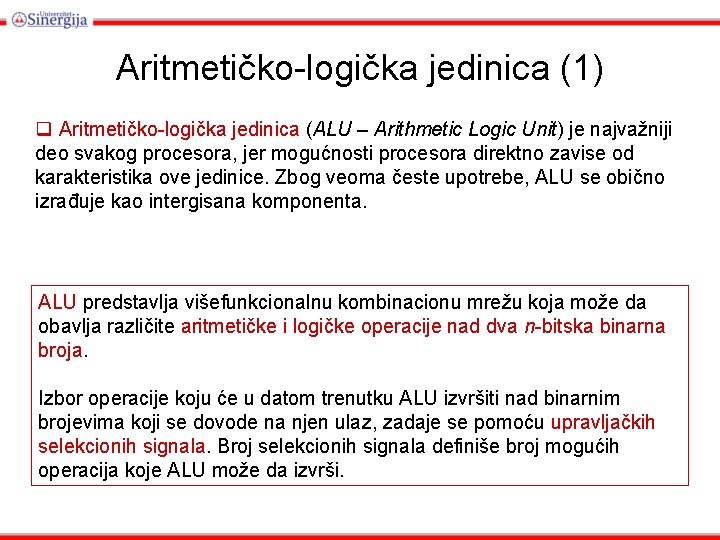

Aritmetičko-logička jedinica (1) q Aritmetičko-logička jedinica (ALU – Arithmetic Logic Unit) je najvažniji deo svakog procesora, jer mogućnosti procesora direktno zavise od karakteristika ove jedinice. Zbog veoma česte upotrebe, ALU se obično izrađuje kao intergisana komponenta. ALU predstavlja višefunkcionalnu kombinacionu mrežu koja može da obavlja različite aritmetičke i logičke operacije nad dva n-bitska binarna broja. Izbor operacije koju će u datom trenutku ALU izvršiti nad binarnim brojevima koji se dovode na njen ulaz, zadaje se pomoću upravljačkih selekcionih signala. Broj selekcionih signala definiše broj mogućih operacija koje ALU može da izvrši.

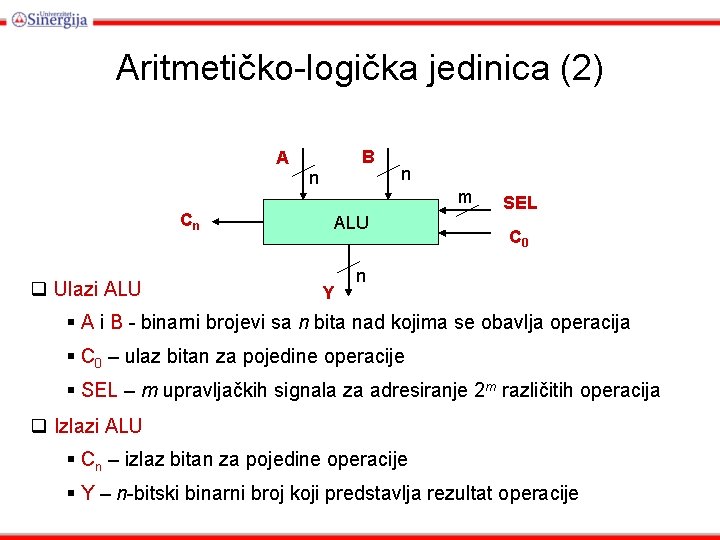

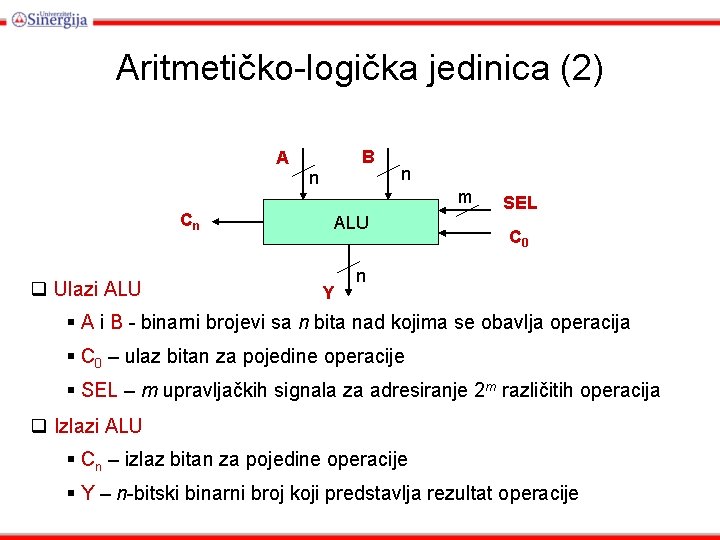

Aritmetičko-logička jedinica (2) B A n Cn q Ulazi ALU n m ALU Y SEL C 0 n § A i B - binarni brojevi sa n bita nad kojima se obavlja operacija § C 0 – ulaz bitan za pojedine operacije § SEL – m upravljačkih signala za adresiranje 2 m različitih operacija q Izlazi ALU § Cn – izlaz bitan za pojedine operacije § Y – n-bitski binarni broj koji predstavlja rezultat operacije

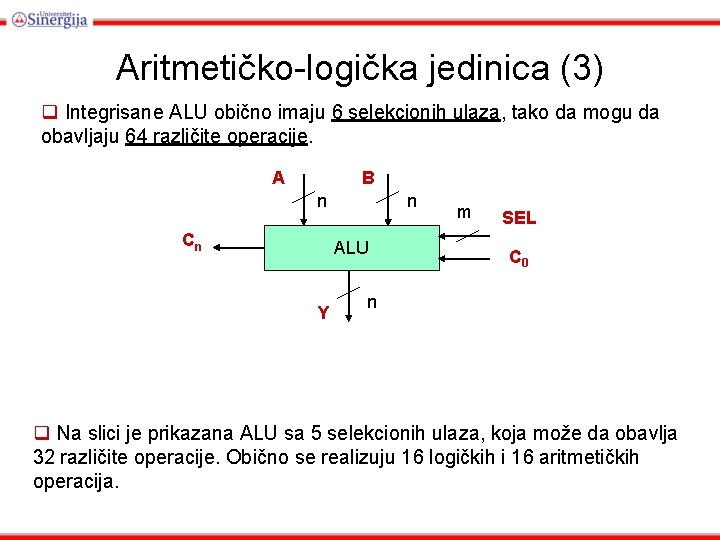

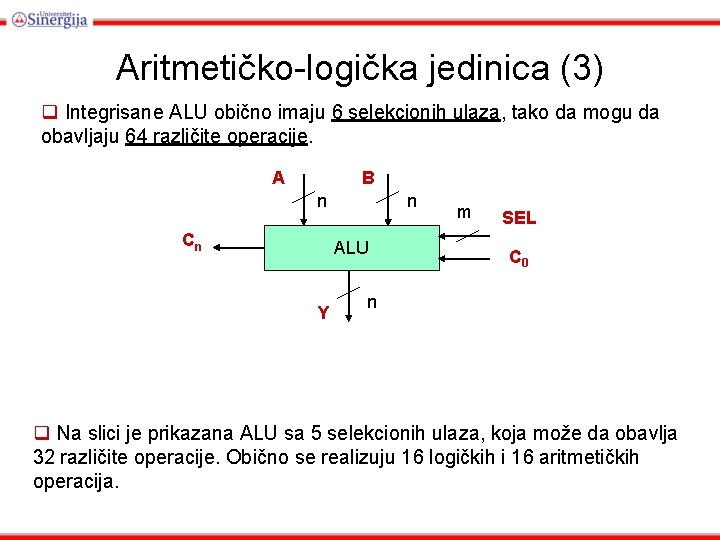

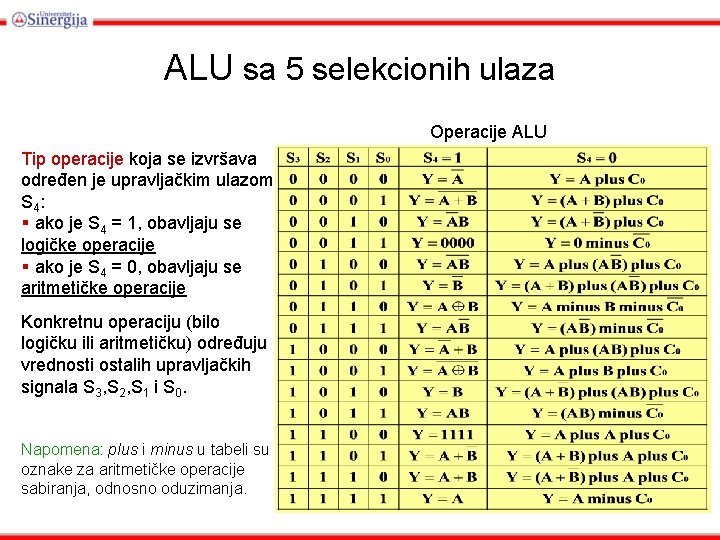

Aritmetičko-logička jedinica (3) q Integrisane ALU obično imaju 6 selekcionih ulaza, tako da mogu da obavljaju 64 različite operacije. A B n Cn n ALU Y m SEL C 0 n q Na slici je prikazana ALU sa 5 selekcionih ulaza, koja može da obavlja 32 različite operacije. Obično se realizuju 16 logičkih i 16 aritmetičkih operacija.

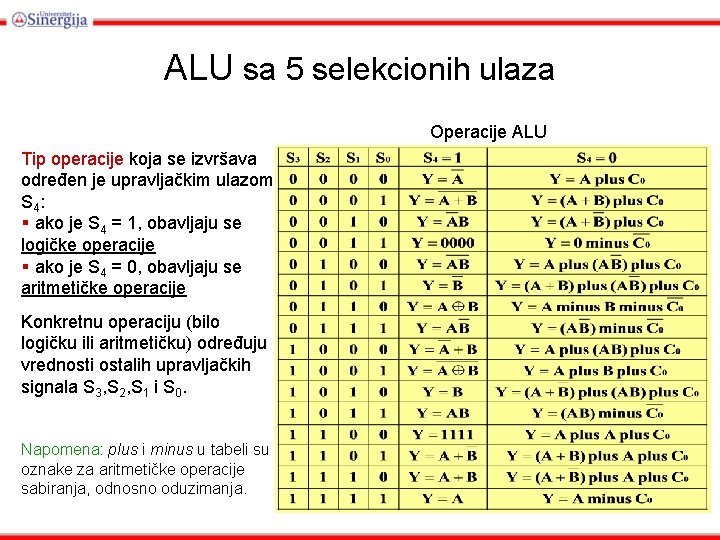

ALU sa 5 selekcionih ulaza Operacije ALU Tip operacije koja se izvršava određen je upravljačkim ulazom S 4: § ako je S 4 = 1, obavljaju se logičke operacije § ako je S 4 = 0, obavljaju se aritmetičke operacije Konkretnu operaciju (bilo logičku ili aritmetičku) određuju vrednosti ostalih upravljačkih signala S 3, S 2, S 1 i S 0. Napomena: plus i minus u tabeli su oznake za aritmetičke operacije sabiranja, odnosno oduzimanja.

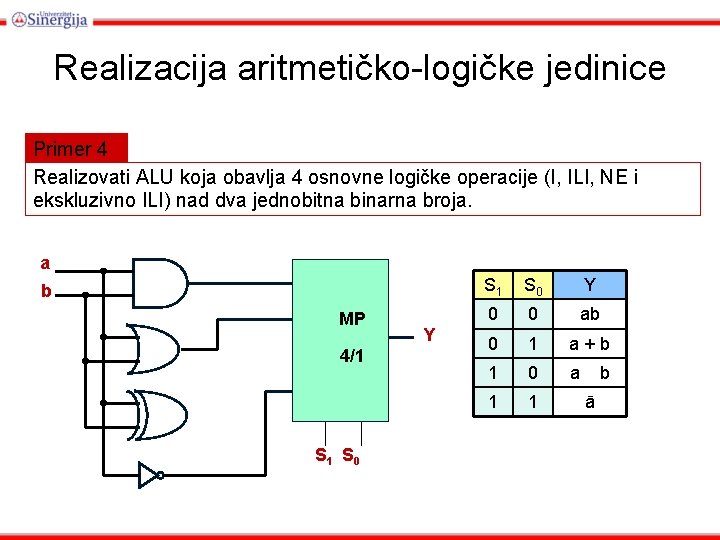

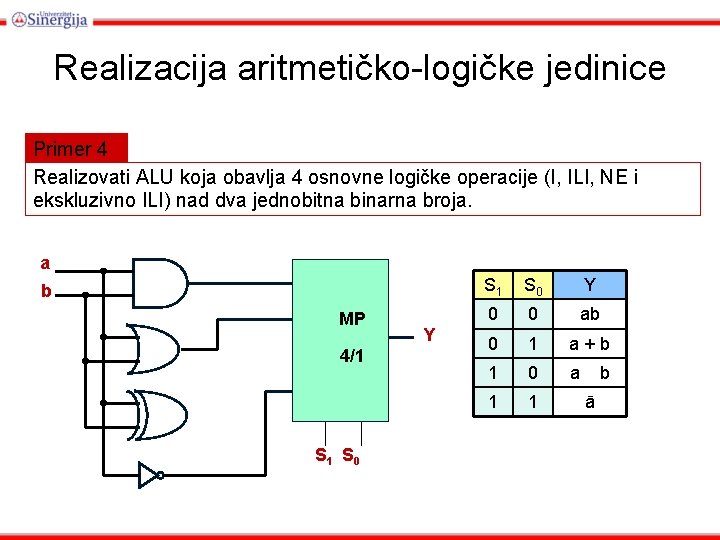

Realizacija aritmetičko-logičke jedinice Primer 4 Realizovati ALU koja obavlja 4 osnovne logičke operacije (I, ILI, NE i ekskluzivno ILI) nad dva jednobitna binarna broja. a b MP MP 4/1 S 1 S 0 Y 0 0 ab 0 1 a+b 1 0 a 1 1 b ā

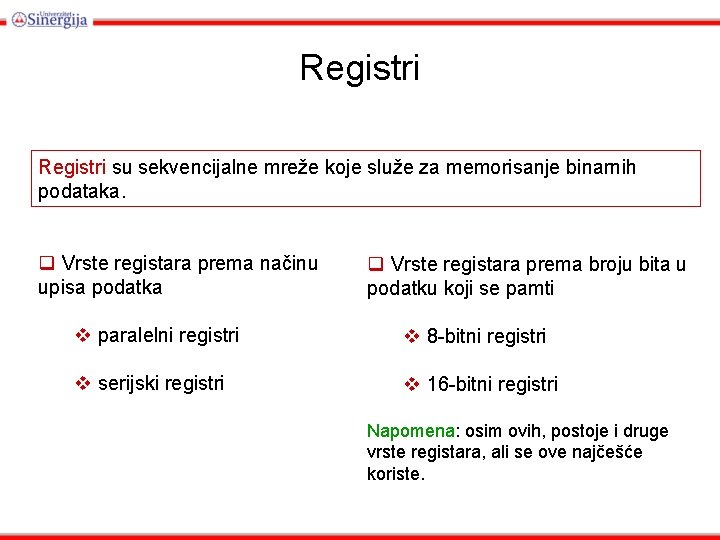

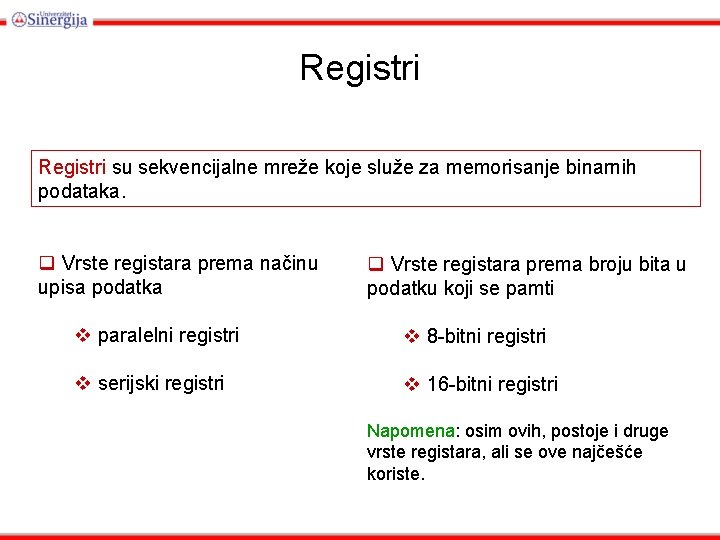

Registri su sekvencijalne mreže koje služe za memorisanje binarnih podataka. q Vrste registara prema načinu upisa podatka q Vrste registara prema broju bita u podatku koji se pamti v paralelni registri v 8 -bitni registri v serijski registri v 16 -bitni registri Napomena: osim ovih, postoje i druge vrste registara, ali se ove najčešće koriste.

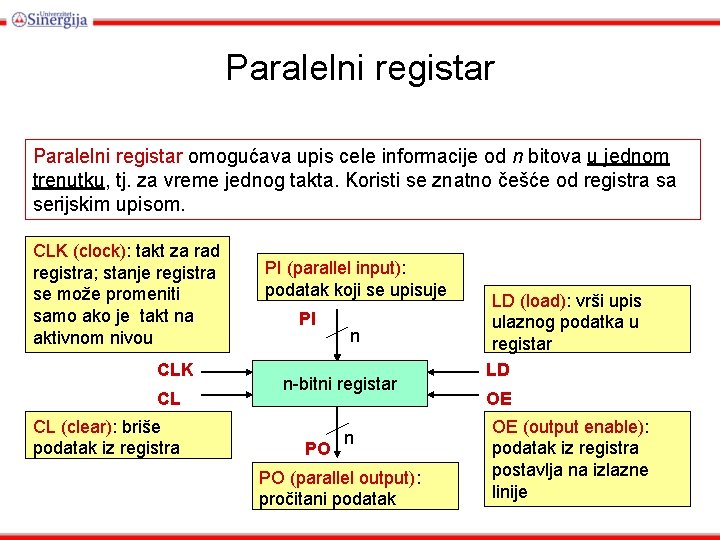

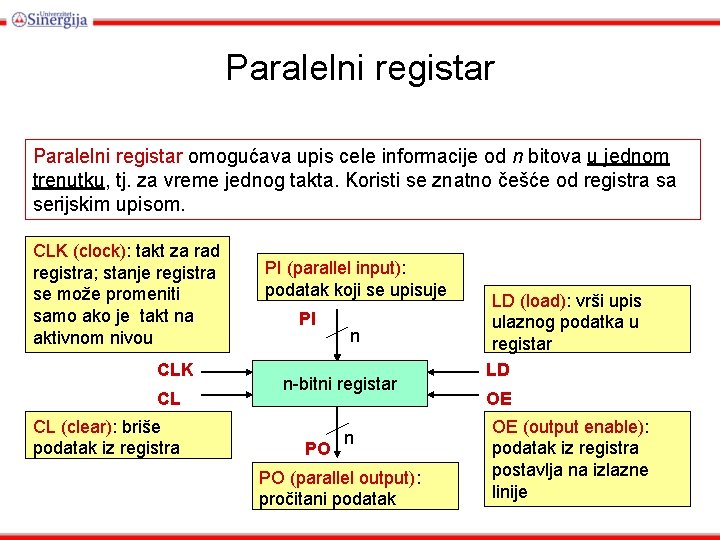

Paralelni registar omogućava upis cele informacije od n bitova u jednom trenutku, tj. za vreme jednog takta. Koristi se znatno češće od registra sa serijskim upisom. CLK (clock): takt za rad registra; stanje registra se može promeniti samo ako je takt na aktivnom nivou CLK CL CL (clear): briše podatak iz registra PI (parallel input): podatak koji se upisuje PI n n-bitni registar PO n PO (parallel output): pročitani podatak LD (load): vrši upis ulaznog podatka u registar LD OE OE (output enable): podatak iz registra postavlja na izlazne linije

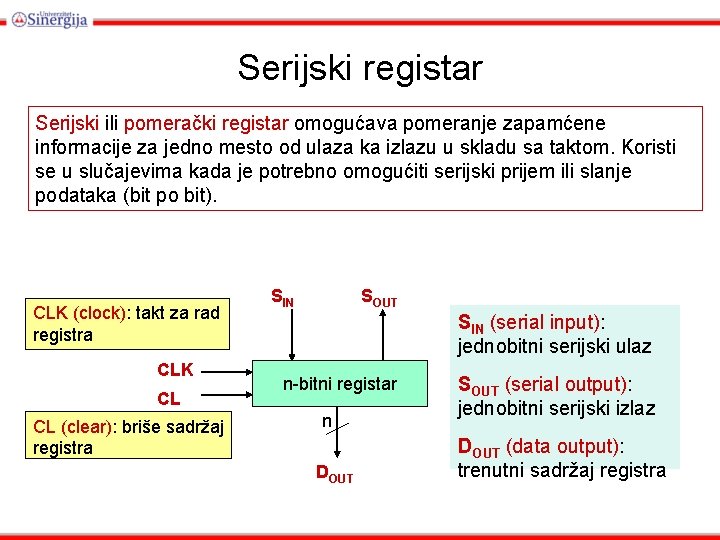

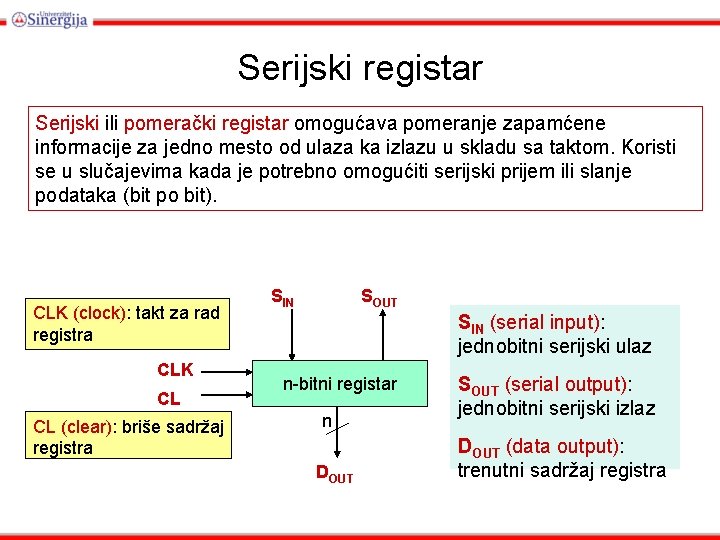

Serijski registar Serijski ili pomerački registar omogućava pomeranje zapamćene informacije za jedno mesto od ulaza ka izlazu u skladu sa taktom. Koristi se u slučajevima kada je potrebno omogućiti serijski prijem ili slanje podataka (bit po bit). CLK (clock): takt za rad registra CLK CL CL (clear): briše sadržaj registra SIN SOUT SIN (serial input): jednobitni serijski ulaz n-bitni registar n DOUT SOUT (serial output): jednobitni serijski izlaz DOUT (data output): trenutni sadržaj registra

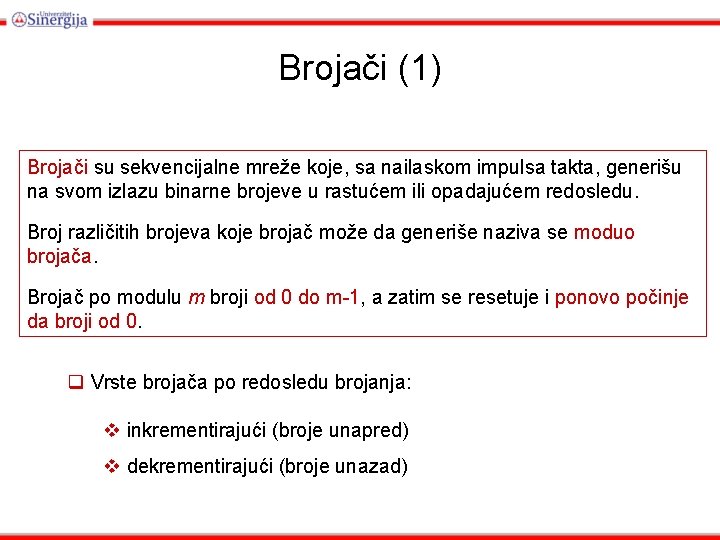

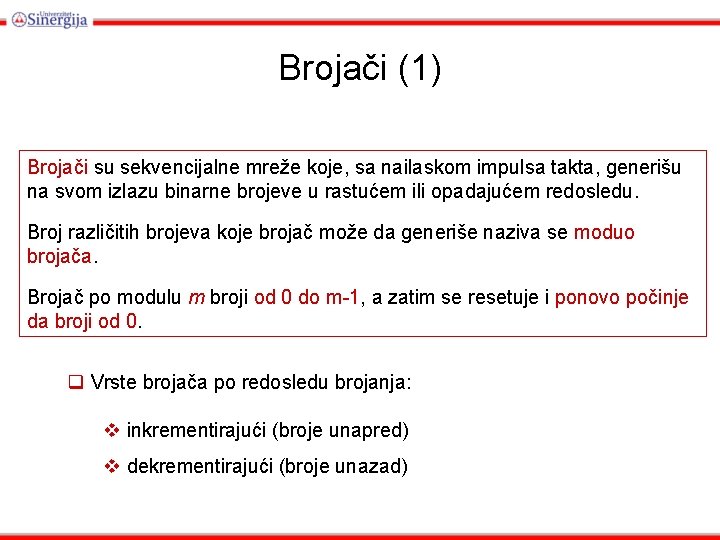

Brojači (1) Brojači su sekvencijalne mreže koje, sa nailaskom impulsa takta, generišu na svom izlazu binarne brojeve u rastućem ili opadajućem redosledu. Broj različitih brojeva koje brojač može da generiše naziva se moduo brojača. Brojač po modulu m broji od 0 do m-1, a zatim se resetuje i ponovo počinje da broji od 0. q Vrste brojača po redosledu brojanja: v inkrementirajući (broje unapred) v dekrementirajući (broje unazad)

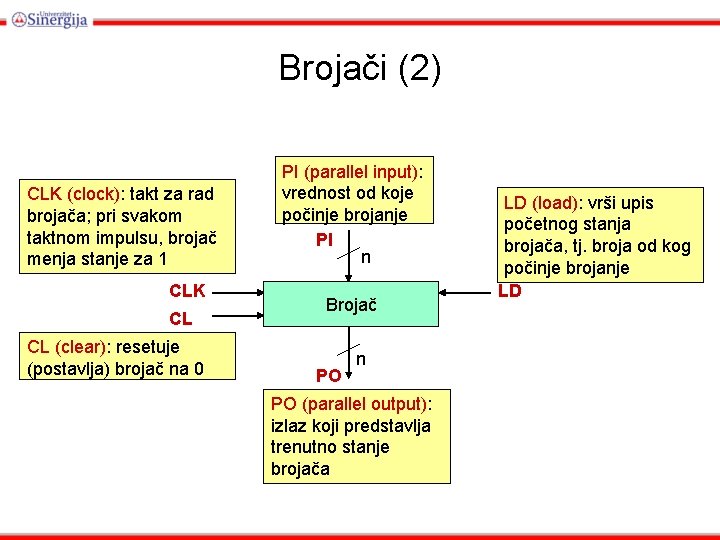

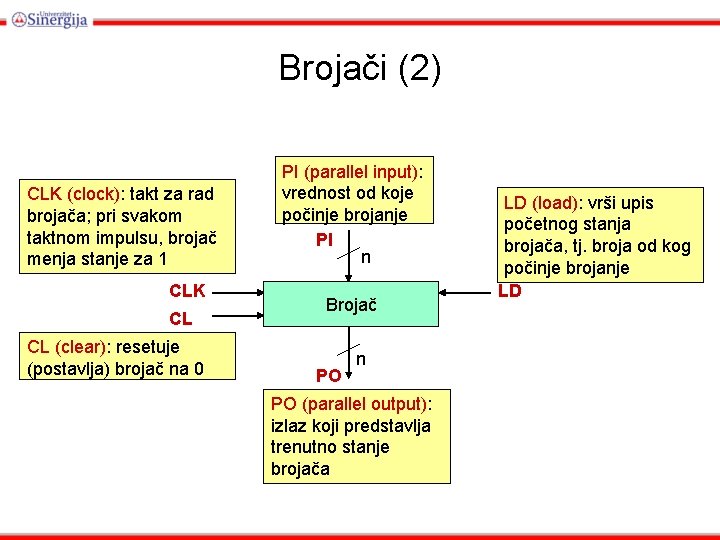

Brojači (2) CLK (clock): takt za rad brojača; pri svakom taktnom impulsu, brojač menja stanje za 1 CLK CL CL (clear): resetuje (postavlja) brojač na 0 PI (parallel input): vrednost od koje počinje brojanje PI n Brojač PO n PO (parallel output): izlaz koji predstavlja trenutno stanje brojača LD (load): vrši upis početnog stanja brojača, tj. broja od kog počinje brojanje LD

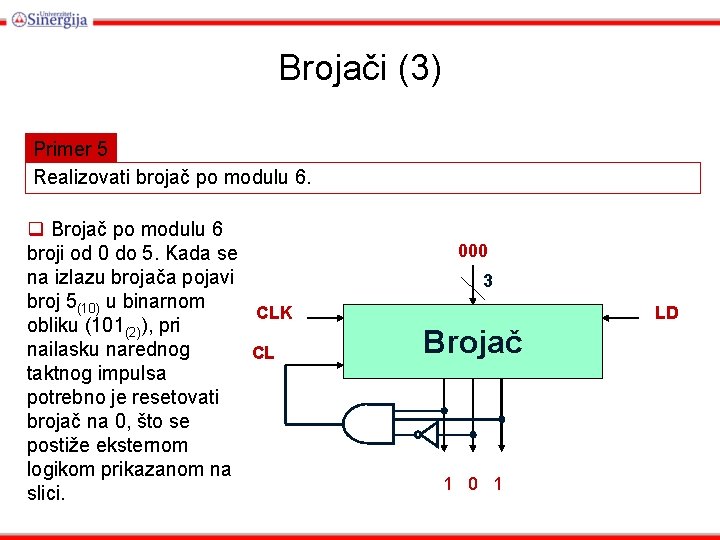

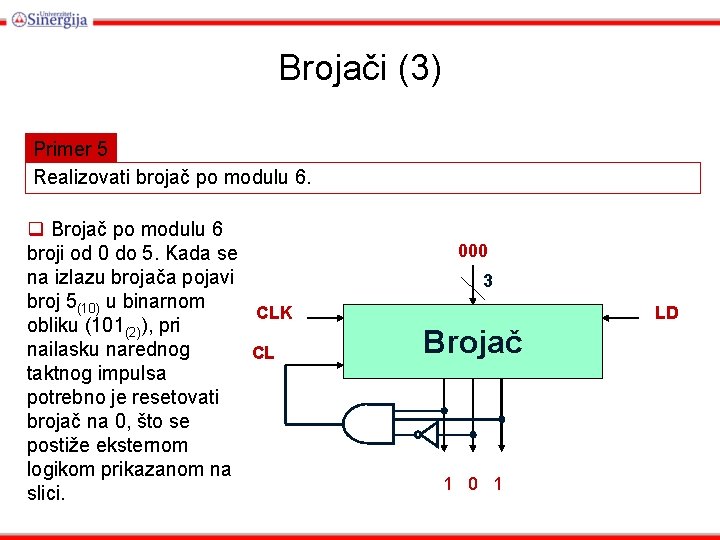

Brojači (3) Primer 5 Realizovati brojač po modulu 6. q Brojač po modulu 6 broji od 0 do 5. Kada se na izlazu brojača pojavi broj 5(10) u binarnom CLK obliku (101(2)), pri nailasku narednog CL taktnog impulsa potrebno je resetovati brojač na 0, što se postiže eksternom logikom prikazanom na slici. 000 3 LD Brojač 1 0 1

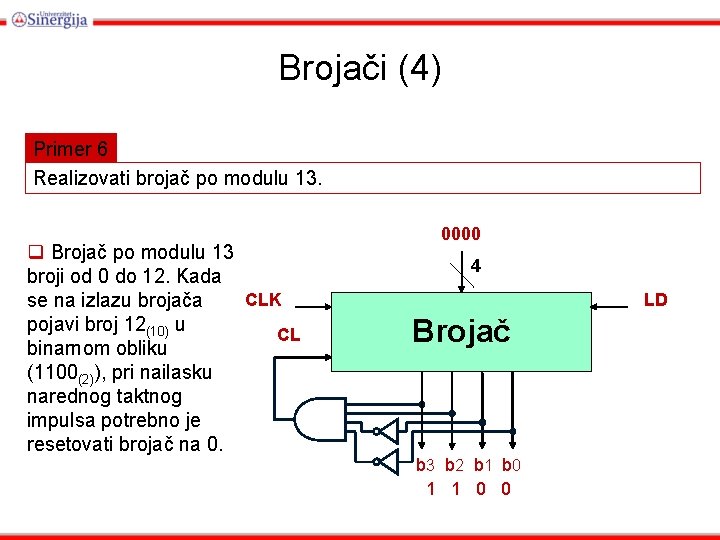

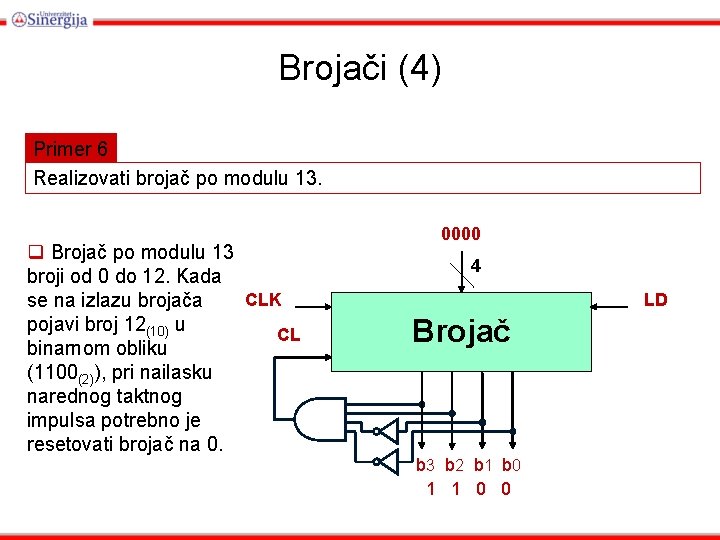

Brojači (4) Primer 6 Realizovati brojač po modulu 13. q Brojač po modulu 13 broji od 0 do 12. Kada CLK se na izlazu brojača pojavi broj 12(10) u CL binarnom obliku (1100(2)), pri nailasku narednog taktnog impulsa potrebno je resetovati brojač na 0. 0000 4 LD Brojač b 3 b 2 b 1 b 0 1 1 0 0

Memorije (1) Memorije služe za pamćenje veće količine binarnih informacija. Karakteristike idealne memorije: § visoka gustina pakovanja § trajnost čuvanja podataka § kratko vreme upisa i čitanja podataka § veliki broj upisa pre otkaza memorije § niska potrošnja § niska cena

Memorije (2) q S obzirom da nijedna vrsta memorije ne zadovoljava sve karakteristike idealne memorije, razvijeno je više vrsta memorija koje, prema potrebi, zadovoljavaju samo neke od navedenih karakteristika. q Osnovna podela memorija: § nepermanentne memorije § permanentne memorije

Nepermanentne memorije su memorije koje gube informacije koje su u njima zapisane ukoliko im se isključi napajanje. q Najčešće korišćena nepermanentna memorija je RAM (Random Access Memory) – memorija sa ravnopravnim pristupom. q RAM se sastoji od memorijske matrice sa 2 n ćelija (kapacitet memorije), pri čemu se u svaku ćeliju može smestiti jedna n-bitska reč. Svakoj ćeliji je pridružen broj, tj. adresa.

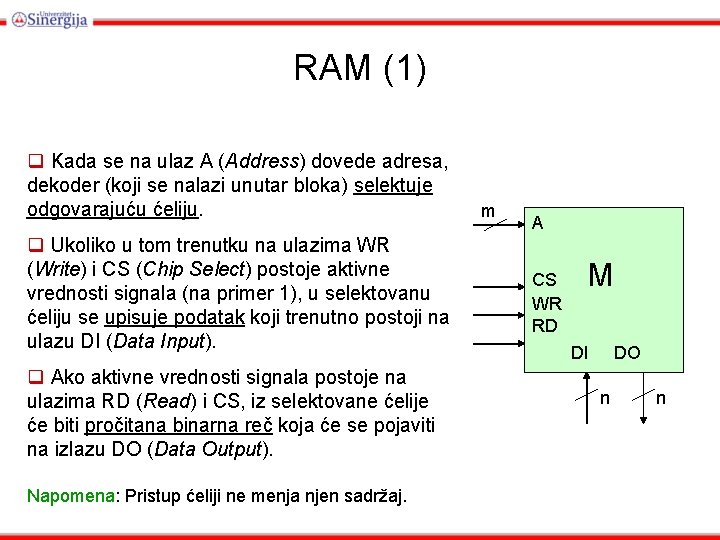

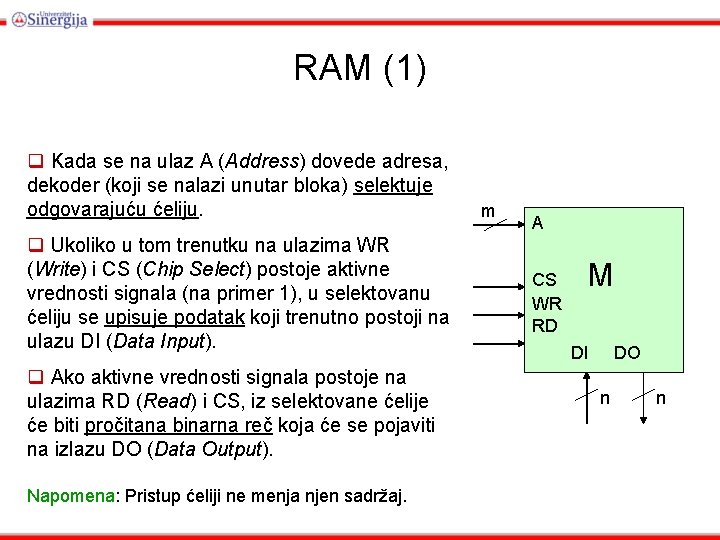

RAM (1) q Kada se na ulaz A (Address) dovede adresa, dekoder (koji se nalazi unutar bloka) selektuje odgovarajuću ćeliju. q Ukoliko u tom trenutku na ulazima WR (Write) i CS (Chip Select) postoje aktivne vrednosti signala (na primer 1), u selektovanu ćeliju se upisuje podatak koji trenutno postoji na ulazu DI (Data Input). q Ako aktivne vrednosti signala postoje na ulazima RD (Read) i CS, iz selektovane ćelije će biti pročitana binarna reč koja će se pojaviti na izlazu DO (Data Output). Napomena: Pristup ćeliji ne menja njen sadržaj. m A CS WR RD M DI DO n n

RAM (2) q RAM se može realizovati na različite načine. Za njihovo konstruisanje, osim logičkih i memorijskih elemenata, mogu se koristiti i elektronske komponente, na primer kondenzatori. q RAM memorije se dele na: v statičke - SRAM (Static RAM) v dinamičke – DRAM (Dynamic RAM)

Statička memorija q Statička memorija je napravljena od memorijskih elementa koji omogućavaju pamćenje sadržaja sve dok se on ne promeni, ili dok se ne isključi napajanje (nepermanentna memorija). q Osnovne karakteristike statičke memorije: § mala gustina pakovanja § velika brzina rada (vreme pristupa reda ns) § mala verovatnoća greške § mala potrošnja električne energije § loš odnos kapacitet/cena

Dinamička memorija (1) q Dinamička memorija predstavlja jedan vid elektronske tabele u kojoj se čuvaju podaci. Svaku ćeliju u tabeli čini par kondenzator-tranzistor koji pamti informaciju od jednog bita. q Pošto ćelija sadrži kondenzator, njen sadržaj se mora povremeno osvežavati. Upravo zbog stalnog osvežavanja, u naziv memorije je uveden termin “dinamička”. q Proces osvežavanja se u potpunosti obavlja u hardveru memorije na svakih par ms, vrlo je brz (reda ns) i neprimetan je za korisnika. Memorija je slobodna za upis i čitanje u preko 98% vremena.

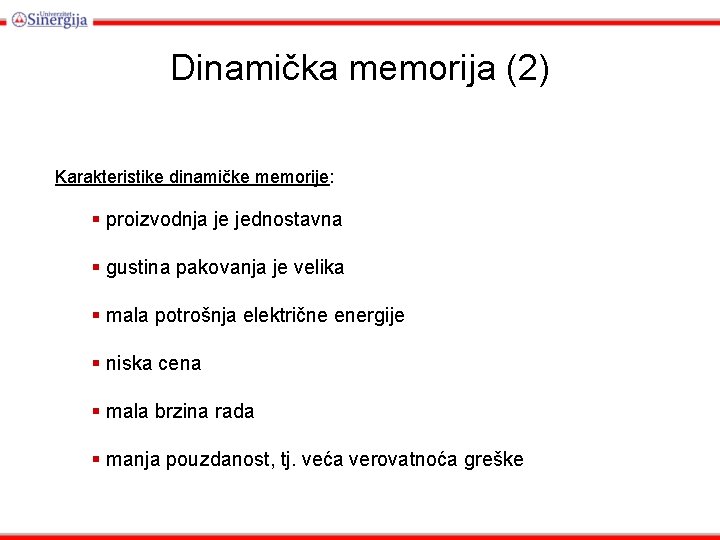

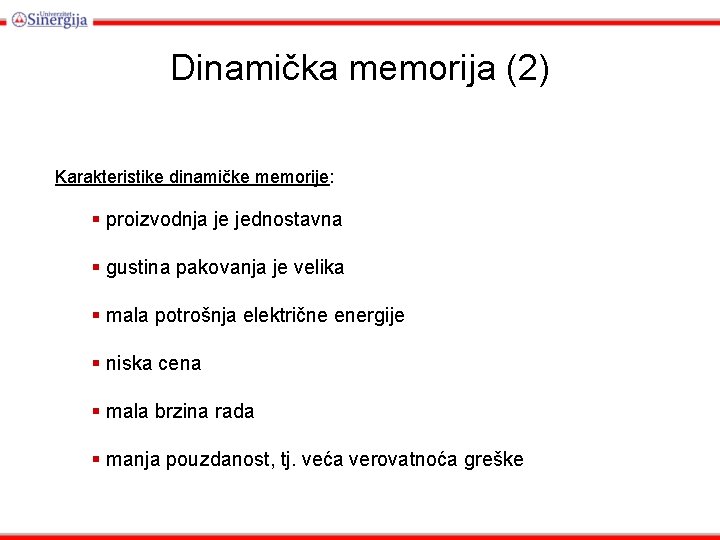

Dinamička memorija (2) Karakteristike dinamičke memorije: § proizvodnja je jednostavna § gustina pakovanja je velika § mala potrošnja električne energije § niska cena § mala brzina rada § manja pouzdanost, tj. veća verovatnoća greške

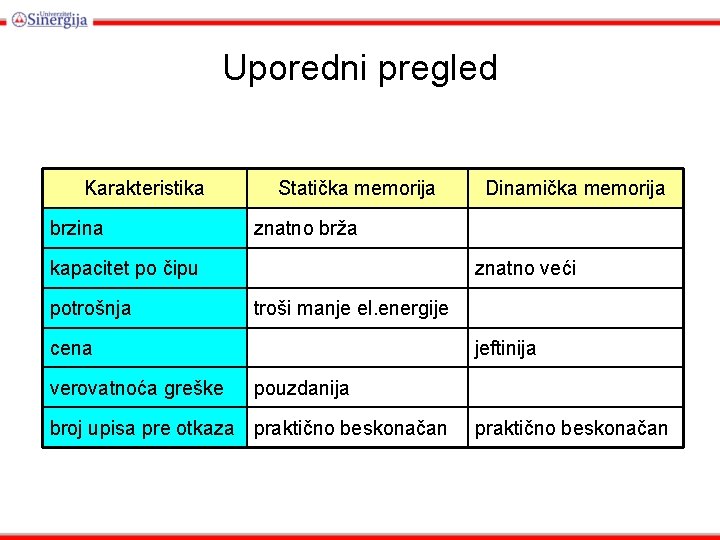

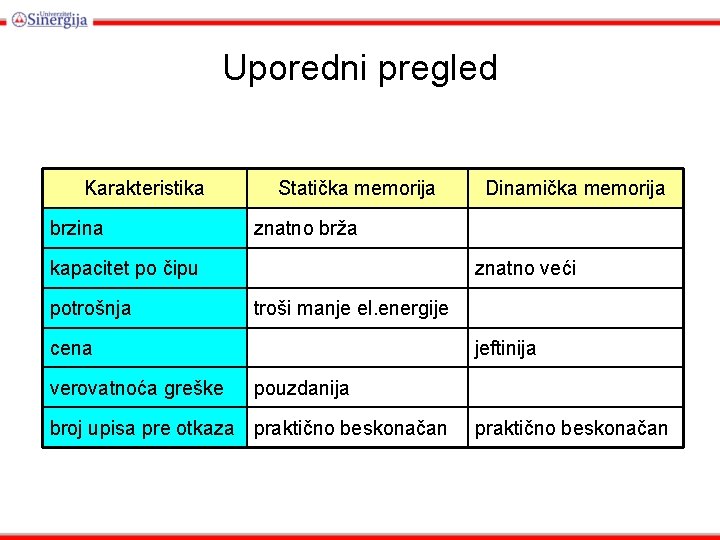

Uporedni pregled Karakteristika brzina Statička memorija znatno brža kapacitet po čipu potrošnja znatno veći troši manje el. energije cena verovatnoća greške Dinamička memorija jeftinija pouzdanija broj upisa pre otkaza praktično beskonačan

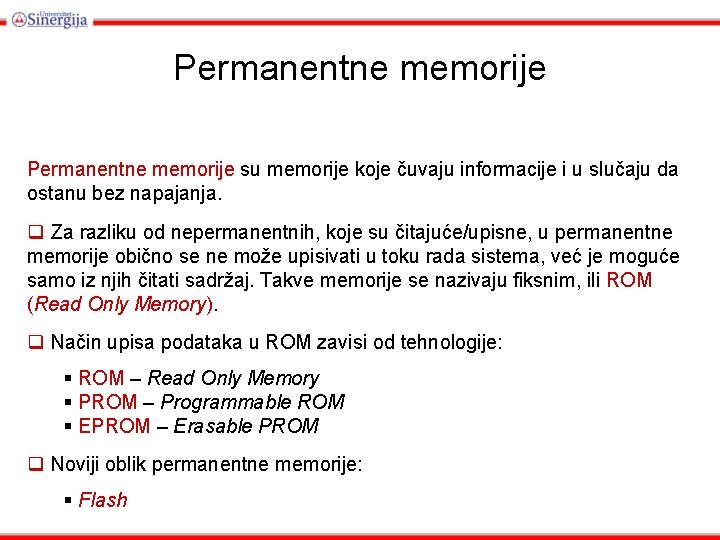

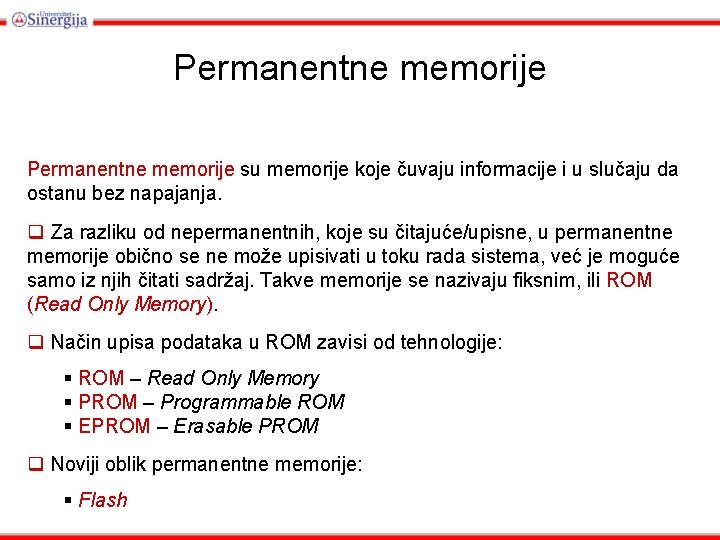

Permanentne memorije su memorije koje čuvaju informacije i u slučaju da ostanu bez napajanja. q Za razliku od nepermanentnih, koje su čitajuće/upisne, u permanentne memorije obično se ne može upisivati u toku rada sistema, već je moguće samo iz njih čitati sadržaj. Takve memorije se nazivaju fiksnim, ili ROM (Read Only Memory). q Način upisa podataka u ROM zavisi od tehnologije: § ROM – Read Only Memory § PROM – Programmable ROM § EPROM – Erasable PROM q Noviji oblik permanentne memorije: § Flash

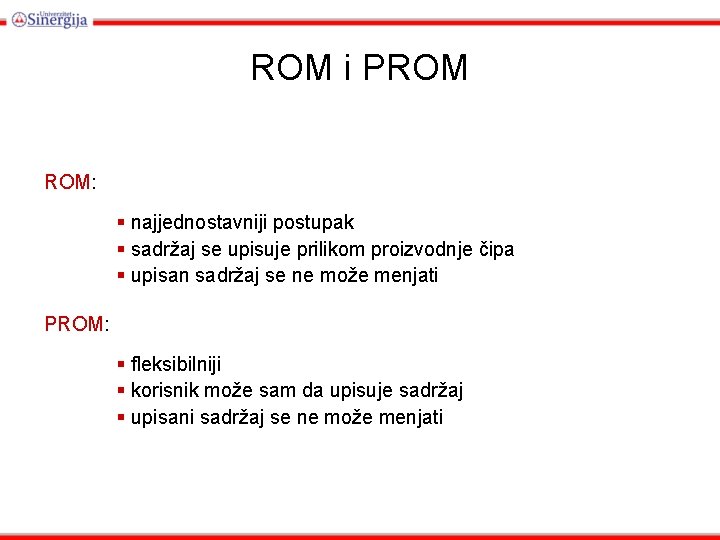

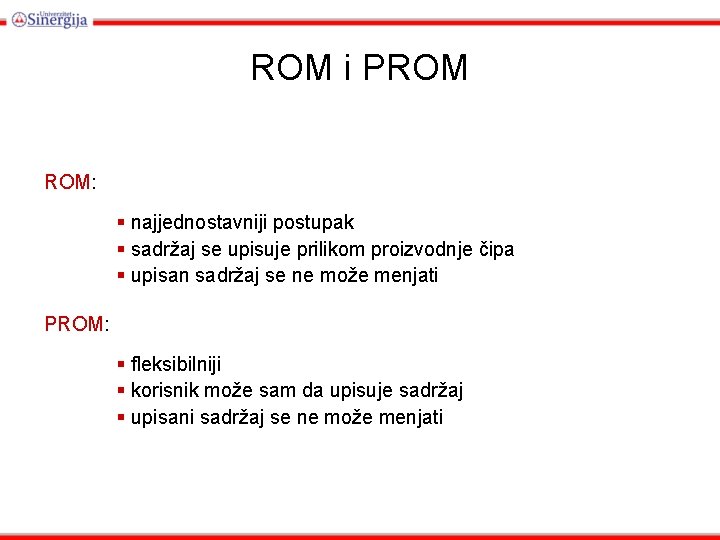

ROM i PROM ROM: § najjednostavniji postupak § sadržaj se upisuje prilikom proizvodnje čipa § upisan sadržaj se ne može menjati PROM: § fleksibilniji § korisnik može sam da upisuje sadržaj § upisani sadržaj se ne može menjati

EPROM q Osim upisa, EPROM ima i mogućnost brisanja sadržaja. q Na kućištu memorije nalazi se mali stakleni prozor kroz koji se može videti unutrašnjost memorijskog čipa. Brisanje sadržaja se vrši tako što se kroz ovaj stakleni prozor ultraljubičastom svetlošću osvetli unutrašnjost čipa u trajanju od dvadesetak minuta. Nakon toga, čip je prazan i može se ponovo programirati. q Jedan čip se može izbrisati nekoliko desetina puta, nakon čega postaje neupotrebljiv.

Fleš q Fleš predstavlja najnoviji oblik permanentne poluprovodničke memorije, čije ime potiče od engleske reči flash (munja), koja treba da asocira na veliku brzinu upisa podataka u ovu memoriju (nekoliko µs po bajtu). q Fleš memorija koristi tehnologiju elektronskog upisa i brisanja podataka, pri čemu se prilikom upisa i brisanja ne može pristupati svakom bajtu pojedinačno. Bajtovi su organizovani po blokovima i prilikom promene sadržaja (upis ili brisanje podataka) moguć je pristup samo celim blokovima. Čitanje se obavlja bajt po bajt. q Karakteristike ove memorije su velika brzina čitanja, veliki kapacitet i velika pouzdanost.

Vlado žabot

Vlado žabot Vlado simeunovic

Vlado simeunovic Vlado leko

Vlado leko Vlado taneski

Vlado taneski Stanka hrastelj

Stanka hrastelj Vlado simeunovic

Vlado simeunovic Vlado kožljan

Vlado kožljan Kurokulum

Kurokulum Vlado belaj

Vlado belaj Tehnike skoka u dalj

Tehnike skoka u dalj Kronološka kompozicija

Kronološka kompozicija Motivacija u nastavi

Motivacija u nastavi Ciglasto uvijanje kose

Ciglasto uvijanje kose Ana zekavica

Ana zekavica Koje su osnovne grane tehnike

Koje su osnovne grane tehnike Tehnike pisanja

Tehnike pisanja Osnovne grane tehnike

Osnovne grane tehnike Kreativne tehnike u nastavi

Kreativne tehnike u nastavi Taktilne pjesničke slike

Taktilne pjesničke slike Tehnike prikupljanja podataka

Tehnike prikupljanja podataka Recikliranje ee otpada

Recikliranje ee otpada Drama 5 razred ispit

Drama 5 razred ispit Dnevnik malog perice prezentacija

Dnevnik malog perice prezentacija Projektna nastava primjer

Projektna nastava primjer Tehnike prikupljanja podataka

Tehnike prikupljanja podataka Metalno doba podjela

Metalno doba podjela Metode rada

Metode rada Vrste kitica

Vrste kitica Mandibularna anestezija

Mandibularna anestezija Kreativne tehnike u nastavi

Kreativne tehnike u nastavi Tehnike prikupljanja podataka

Tehnike prikupljanja podataka Osnove arhitekture

Osnove arhitekture Osnove zdravstvene njege

Osnove zdravstvene njege Osnove zdravstvene struke

Osnove zdravstvene struke Osnove imunologije

Osnove imunologije Slidetodoc

Slidetodoc Genetuka

Genetuka Osnove financ

Osnove financ Nastavne metode

Nastavne metode Osnove pedagogije

Osnove pedagogije Osnove zdravstvene njege nada prlić pdf

Osnove zdravstvene njege nada prlić pdf Francuska gramatika

Francuska gramatika Osnove interneta

Osnove interneta Osnove zaštite na radu

Osnove zaštite na radu Osnove rada u programu prikupljanje i unos podataka

Osnove rada u programu prikupljanje i unos podataka Vrste turizma

Vrste turizma Matematicke osnove racunara

Matematicke osnove racunara Realnost informatika

Realnost informatika Opste osnove predskolskog programa

Opste osnove predskolskog programa 3. deklinacija suglasničke osnove

3. deklinacija suglasničke osnove Java objektno orijentisano programiranje

Java objektno orijentisano programiranje Osnove php programiranja

Osnove php programiranja Osnove algoritama

Osnove algoritama Informatika osnove

Informatika osnove