MMU Memory Management Unit Chapter 14 1 Memory

- Slides: 65

MMU Memory Management Unit Chapter # 14 1 Memory Management Unit

Presented by: Group#13 • Asmaa Rabie Abdualaziz • Islam Ameen Abdualaziz • Doaa Ahmed Mohamed • Sherif Mohamed Medhat Presented to: to • Dr. Amr Wassal • CMP 2012 2 Memory Management Unit

Agenda • • • 3 1. What we will learn from chapter ? 2. Introduction 3. Moving From An MPU To An MMU 4. How Virtual Memory works 4. 1 The components of a virtual memory system 4. 2 Defining Regions Using Pages 4. 3 Multitasking and The MMU 4. 4 Memory Organization in a Virtual Memory System 5. Details Of The ARM MMU 6. Page Table 6. 1 Level 1 6. 2 Translation Table Base Address 6. 3 Level 2 7. Translation Lookaside Buffer 7. 1 L 1 Page table virtual-to-physical memory translation using 1 MB sections 7. 2 Two-level virtual-to-physical address translation using coarse page tables 7. 3 TLB Operations 8. Domain & Access permission 9. Caches and Write Buffer 10. Coprocessor 15 and MMU configuration 11. Fast Context Switch Extension (FCSE) 12. A small virtual memory system Memory Management Unit

What will we learn from chapter? Learn basics of ARM MMU and some basic concepts that underlie the use of the virtual memory 4 Memory Management Unit

Agenda • • • 5 1. What we will learn from chapter ? 2. Introduction 3. Moving From An MPU To An MMU 4. How Virtual Memory works 4. 1 The components of a virtual memory system 4. 2 Defining Regions Using Pages 4. 3 Multitasking and The MMU 4. 4 Memory Organization in a Virtual Memory System 5. Details Of The ARM MMU 6. Page Table 6. 1 Level 1 6. 2 Translation Table Base Address 6. 3 Level 2 7. Translation Lookaside Buffer 7. 1 L 1 Page table virtual-to-physical memory translation using 1 MB sections 7. 2 Two-level virtual-to-physical address translation using coarse page tables 7. 3 TLB Operations 8. Domain & Access permission 9. Caches and Write Buffer 10. Coprocessor 15 and MMU configuration 11. Fast Context Switch Extension (FCSE) 12. A small virtual memory system Memory Management Unit

Introduction • Virtual addresses: Assign by Compiler and Linker • Physical addresses : Access the actual hardware components 6 Memory Management Unit

Agenda • • • 7 1. What we will learn from chapter ? 2. Introduction 3. Moving From An MPU To An MMU 4. How Virtual Memory works 4. 1 The components of a virtual memory system 4. 2 Defining Regions Using Pages 4. 3 Multitasking and The MMU 4. 4 Memory Organization in a Virtual Memory System 5. Details Of The ARM MMU 6. Page Table 6. 1 Level 1 6. 2 Translation Table Base Address 6. 3 Level 2 7. Translation Lookaside Buffer 7. 1 L 1 Page table virtual-to-physical memory translation using 1 MB sections 7. 2 Two-level virtual-to-physical address translation using coarse page tables 7. 3 TLB Operations 8. Domain & Access permission 9. Caches and Write Buffer 10. Coprocessor 15 and MMU configuration 11. Fast Context Switch Extension (FCSE) 12. A small virtual memory system Memory Management Unit

Moving From An MPU To An MMU • What is the difference between active and dormant region? • Difference Between MPU & MMU 8 Memory Management Unit

Agenda • • • 9 1. What we will learn from chapter ? 2. Introduction 3. Moving From An MPU To An MMU 4. How Virtual Memory works 4. 1 The components of a virtual memory system 4. 2 Defining Regions Using Pages 4. 3 Multitasking and The MMU 4. 4 Memory Organization in a Virtual Memory System 5. Details Of The ARM MMU 6. Page Table 6. 1 Level 1 6. 2 Translation Table Base Address 6. 3 Level 2 7. Translation Lookaside Buffer 7. 1 L 1 Page table virtual-to-physical memory translation using 1 MB sections 7. 2 Two-level virtual-to-physical address translation using coarse page tables 7. 3 TLB Operations 8. Domain & Access permission 9. Caches and Write Buffer 10. Coprocessor 15 and MMU configuration 11. Fast Context Switch Extension (FCSE) 12. A small virtual memory system Memory Management Unit

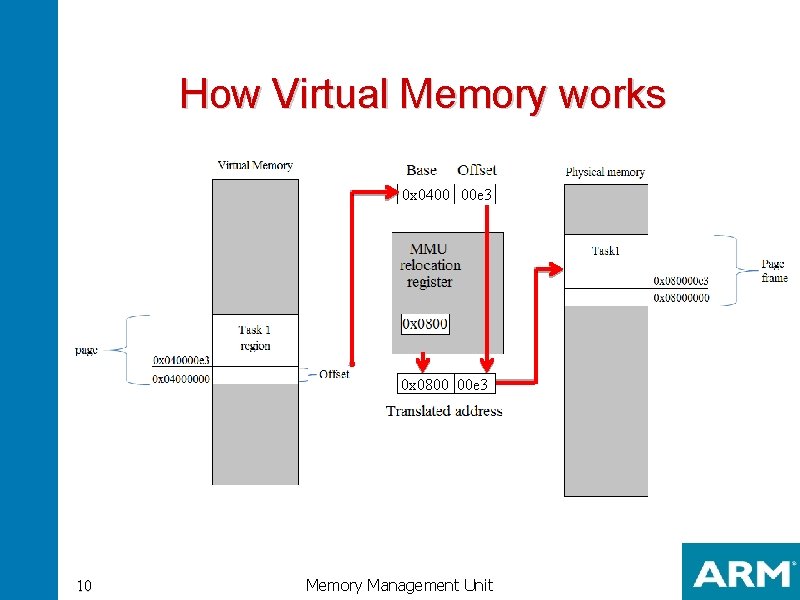

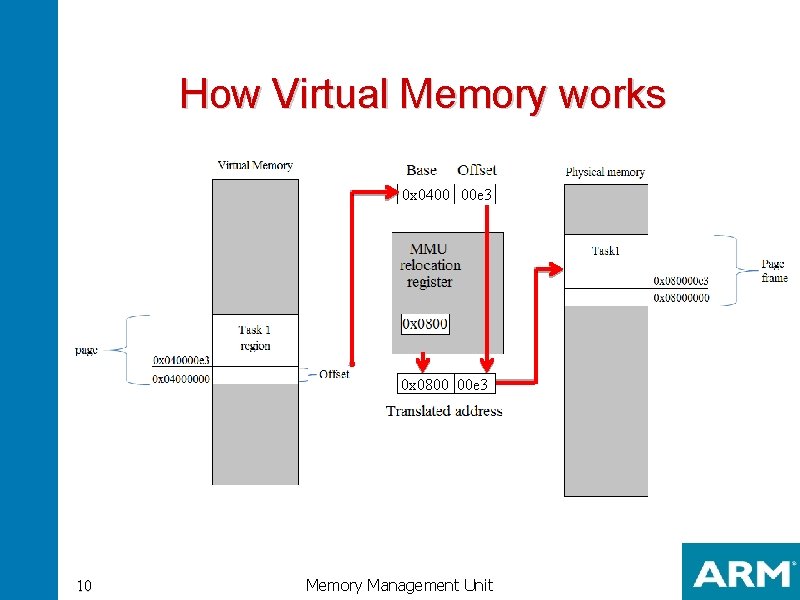

How Virtual Memory works 0 x 0400 00 e 3 0 x 0800 00 e 3 10 Memory Management Unit

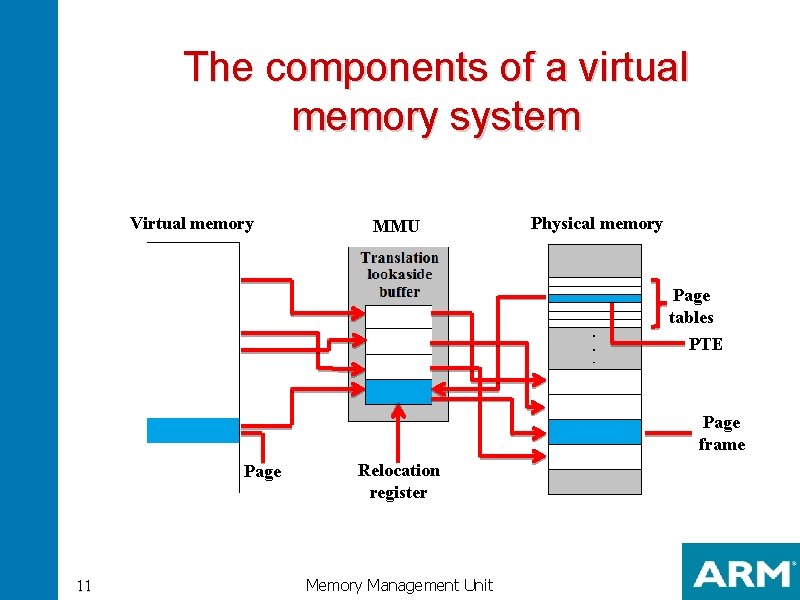

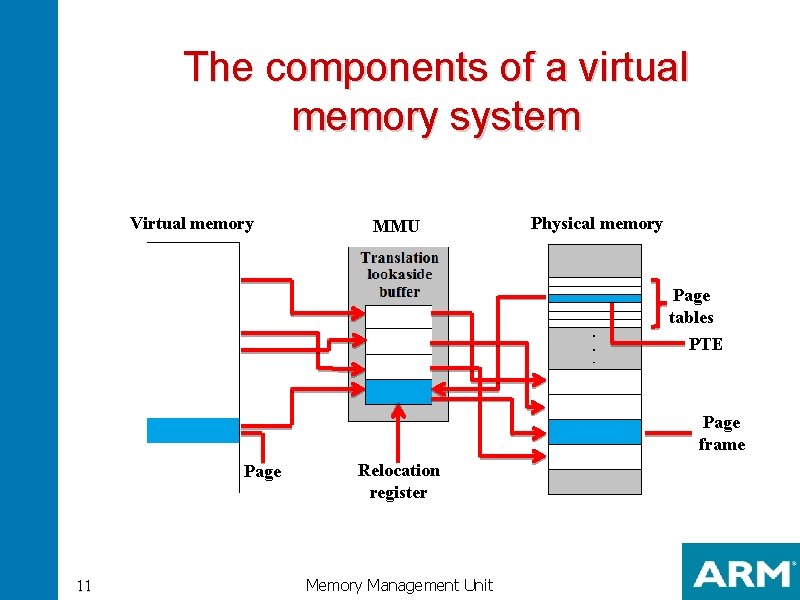

The components of a virtual memory system Virtual memory MMU Physical memory Page tables PTE Page frame Page 11 Relocation register Memory Management Unit

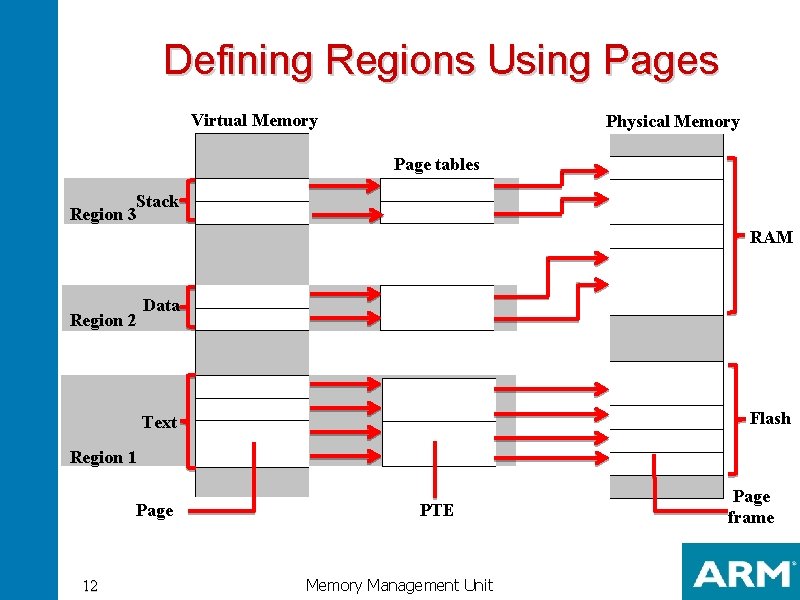

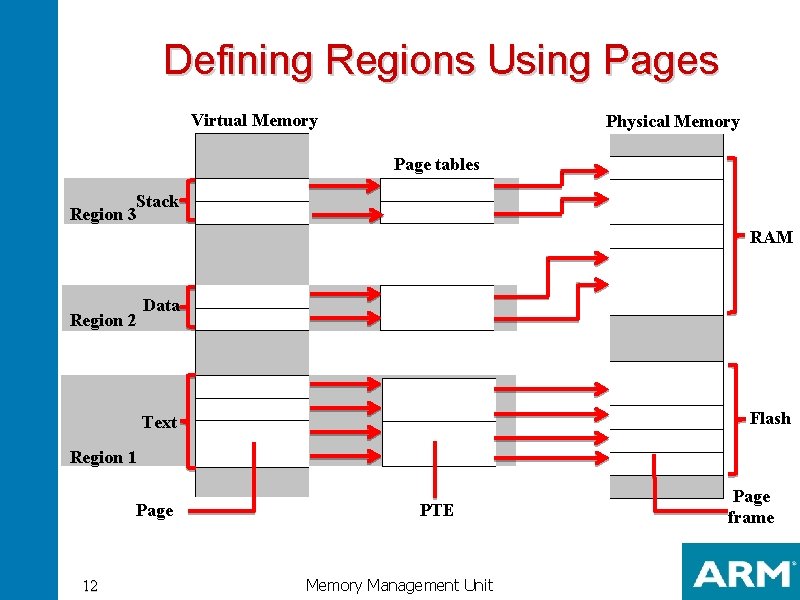

Defining Regions Using Pages Virtual Memory Physical Memory Page tables Stack Region 3 RAM Region 2 Data Flash Text Region 1 Page 12 PTE Memory Management Unit Page frame

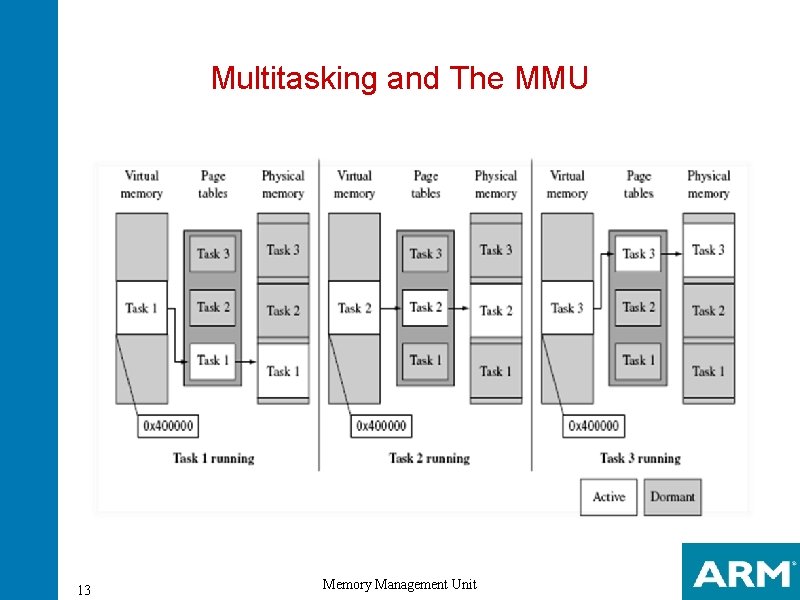

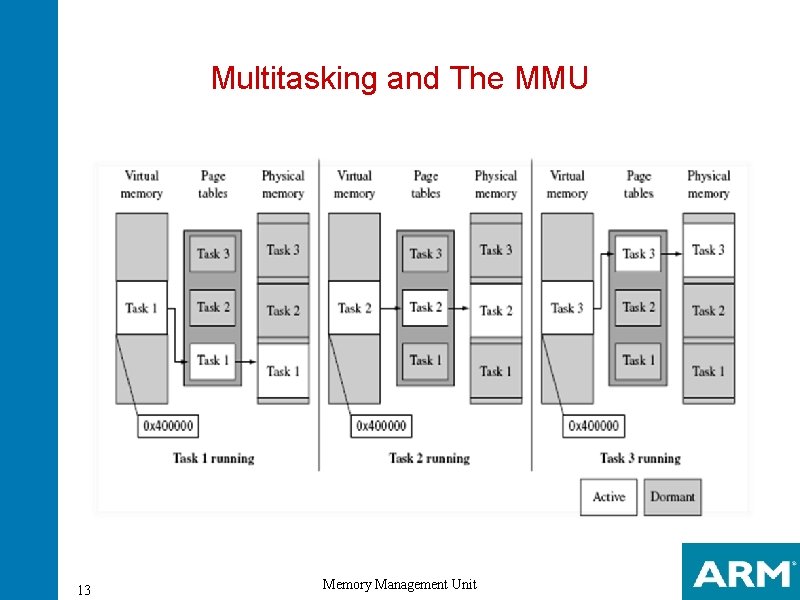

Multitasking and The MMU 13 Memory Management Unit

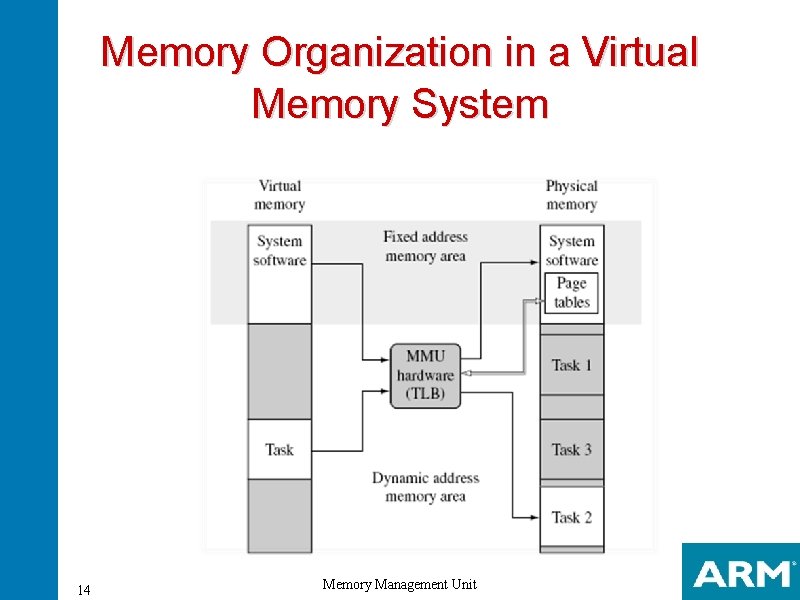

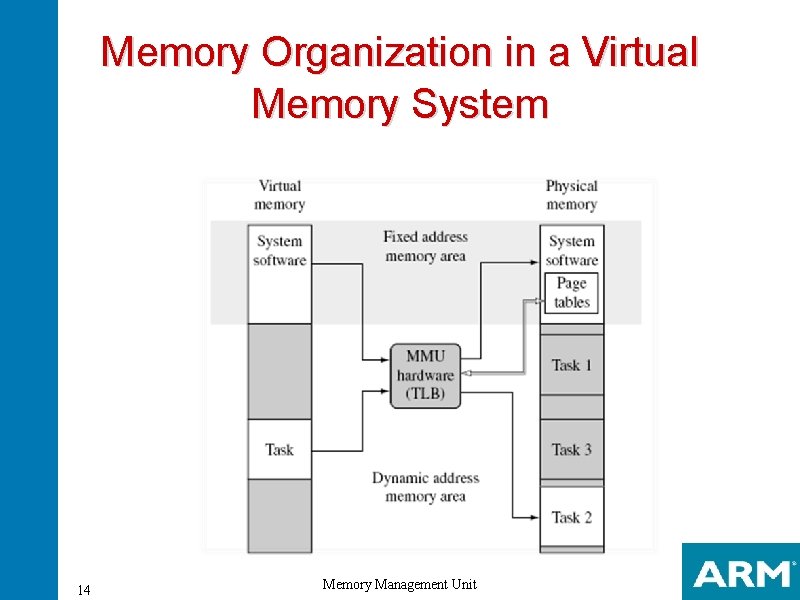

Memory Organization in a Virtual Memory System 14 Memory Management Unit

Agenda • • • 15 1. What we will learn from chapter ? 2. Introduction 3. Moving From An MPU To An MMU 4. How Virtual Memory works 4. 1 The components of a virtual memory system 4. 2 Defining Regions Using Pages 4. 3 Multitasking and The MMU 4. 4 Memory Organization in a Virtual Memory System 5. Details Of The ARM MMU 6. Page Table 6. 1 Level 1 6. 2 Translation Table Base Address 6. 3 Level 2 7. Translation Lookaside Buffer 7. 1 L 1 Page table virtual-to-physical memory translation using 1 MB sections 7. 2 Two-level virtual-to-physical address translation using coarse page tables 7. 3 TLB Operations 8. Domain & Access permission 9. Caches and Write Buffer 10. Coprocessor 15 and MMU configuration 11. Fast Context Switch Extension (FCSE) 12. A small virtual memory system Memory Management Unit

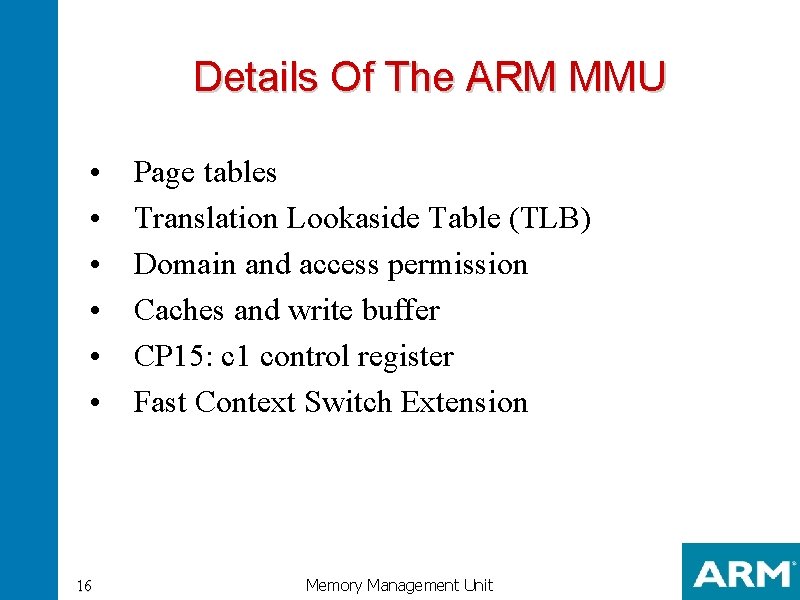

Details Of The ARM MMU • • • 16 Page tables Translation Lookaside Table (TLB) Domain and access permission Caches and write buffer CP 15: c 1 control register Fast Context Switch Extension Memory Management Unit

Agenda • • • 17 1. What we will learn from chapter ? 2. Introduction 3. Moving From An MPU To An MMU 4. How Virtual Memory works 4. 1 The components of a virtual memory system 4. 2 Defining Regions Using Pages 4. 3 Multitasking and The MMU 4. 4 Memory Organization in a Virtual Memory System 5. Details Of The ARM MMU 6. Page Table 6. 1 Level 1 6. 2 Translation Table Base Address 6. 3 Level 2 7. Translation Lookaside Buffer 7. 1 L 1 Page table virtual-to-physical memory translation using 1 MB sections 7. 2 Two-level virtual-to-physical address translation using coarse page tables 7. 3 TLB Operations 8. Domain & Access permission 9. Caches and Write Buffer 10. Coprocessor 15 and MMU configuration 11. Fast Context Switch Extension (FCSE) 12. A small virtual memory system Memory Management Unit

Page Table • L 1 Entries for translating 1 MB pages Pointers to the starting address to level 2 page tables • L 2 Fine page table Coarse page table 18 Memory Management Unit

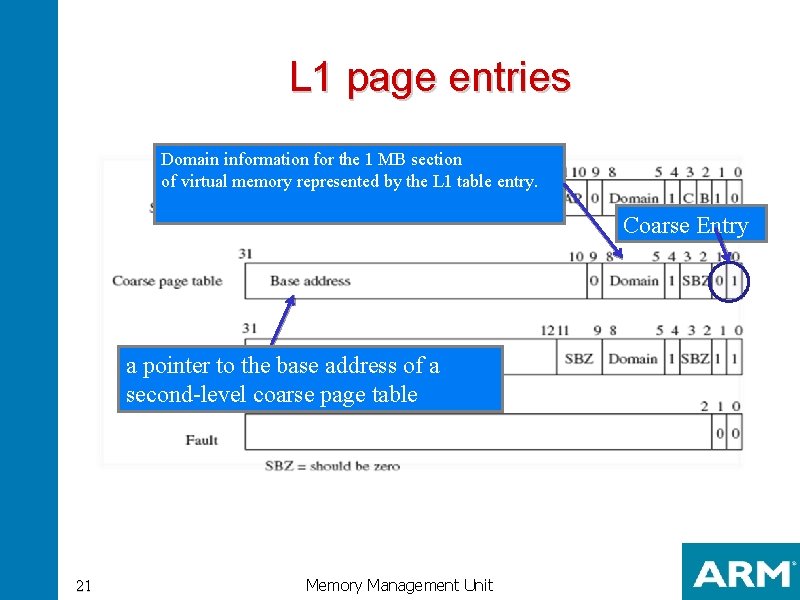

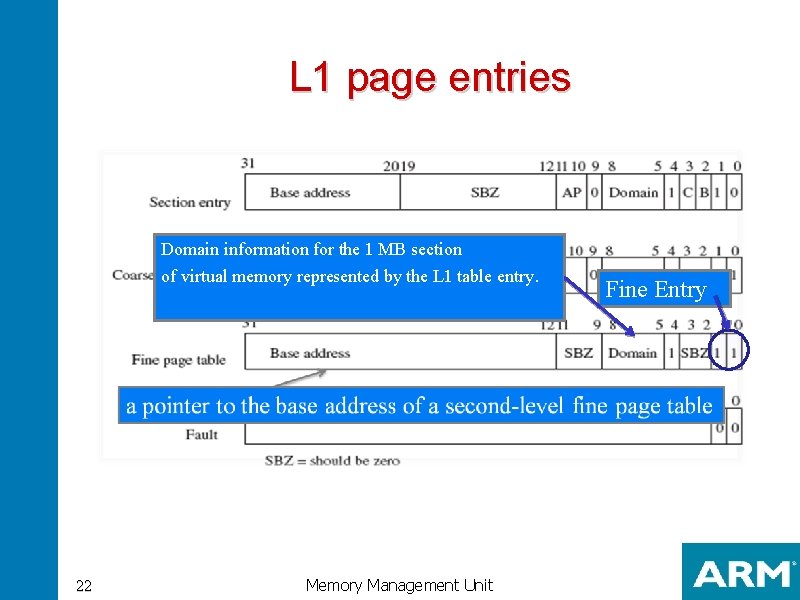

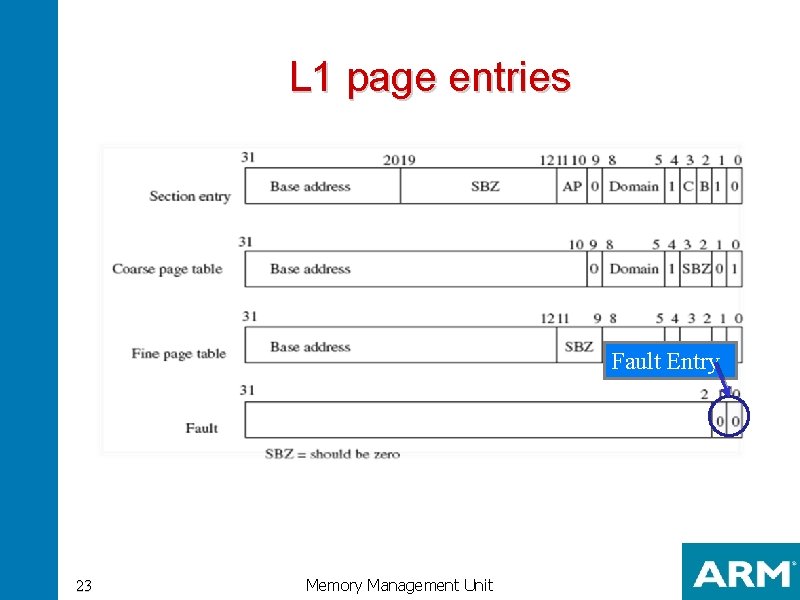

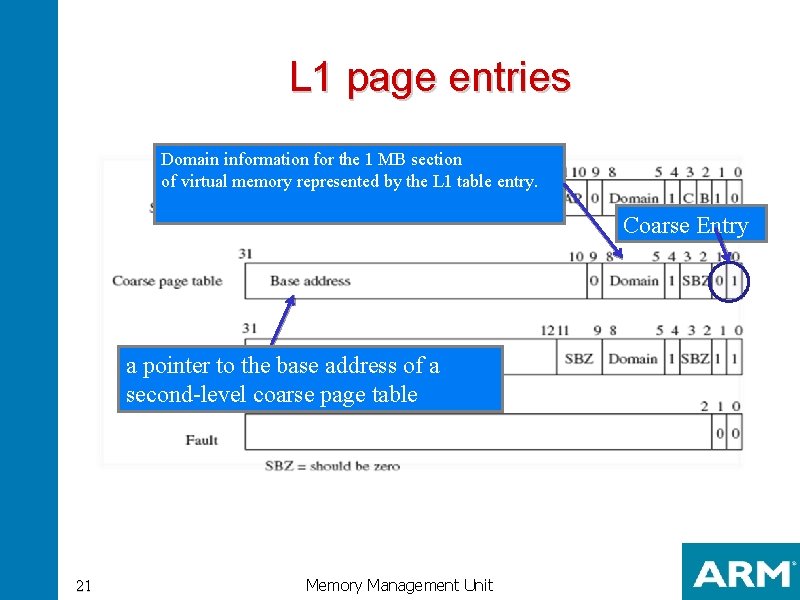

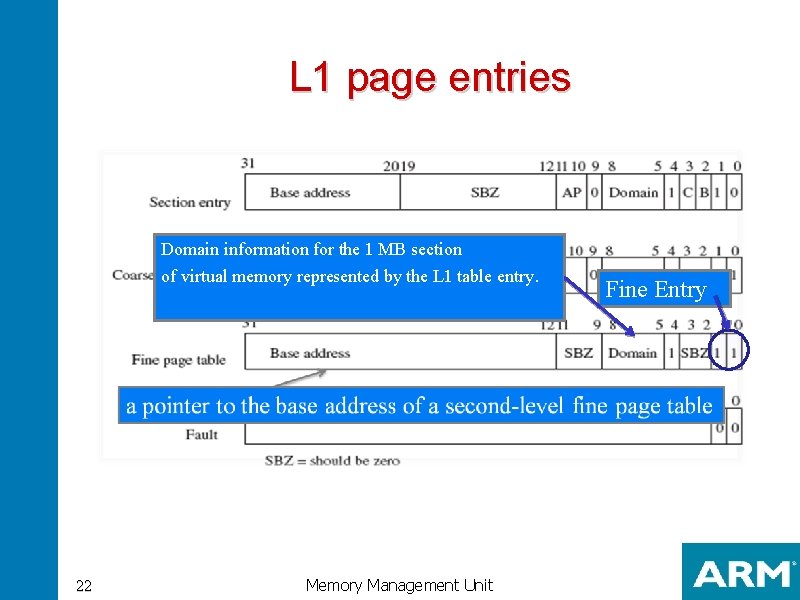

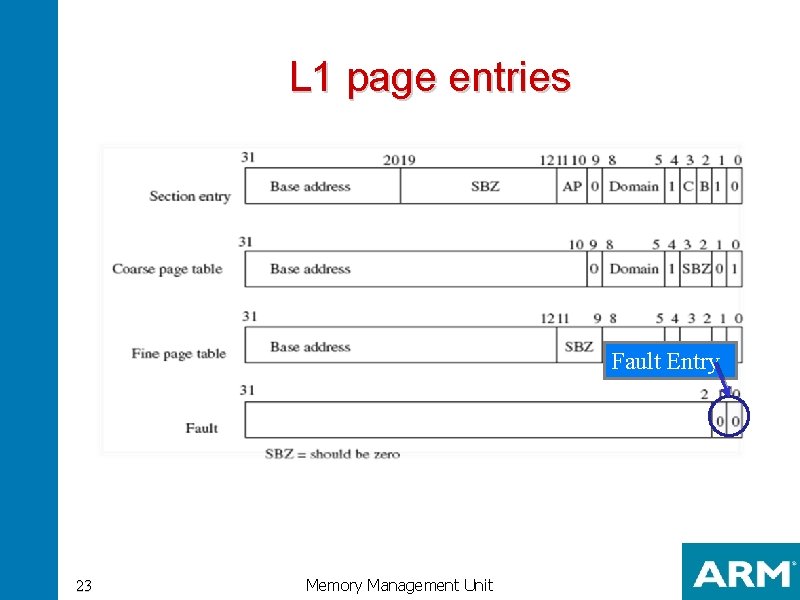

Level 1 page table accepts four types of entry • A 1 MB section translation entry • A directory entry that points to a fine L 2 page table • A directory entry that points to a coarse L 2 page table • A fault entry that generates an abort exception 19 Memory Management Unit

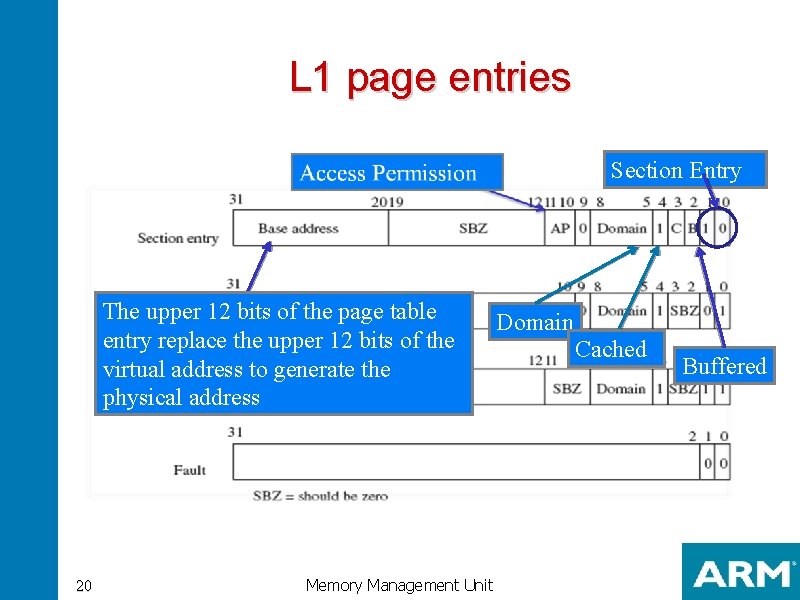

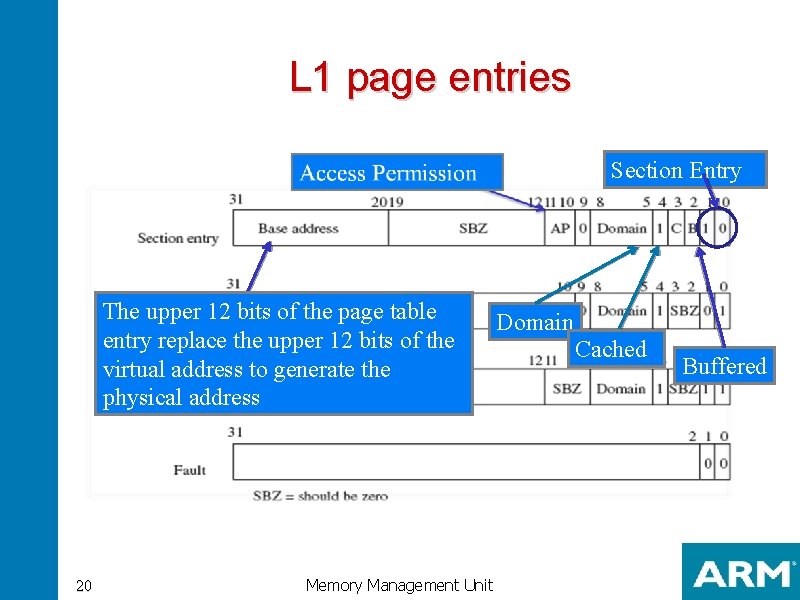

L 1 page entries Section Entry The upper 12 bits of the page table entry replace the upper 12 bits of the virtual address to generate the physical address 20 Memory Management Unit Domain Cached Buffered

L 1 page entries Domain information for the 1 MB section of virtual memory represented by the L 1 table entry. Coarse Entry a pointer to the base address of a second-level coarse page table 21 Memory Management Unit

L 1 page entries Domain information for the 1 MB section of virtual memory represented by the L 1 table entry. 22 Memory Management Unit Fine Entry

L 1 page entries Fault Entry 23 Memory Management Unit

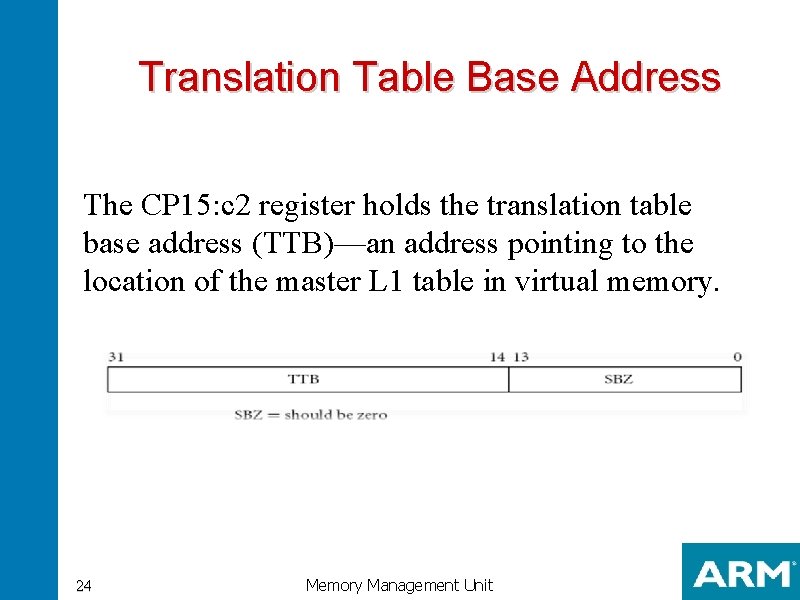

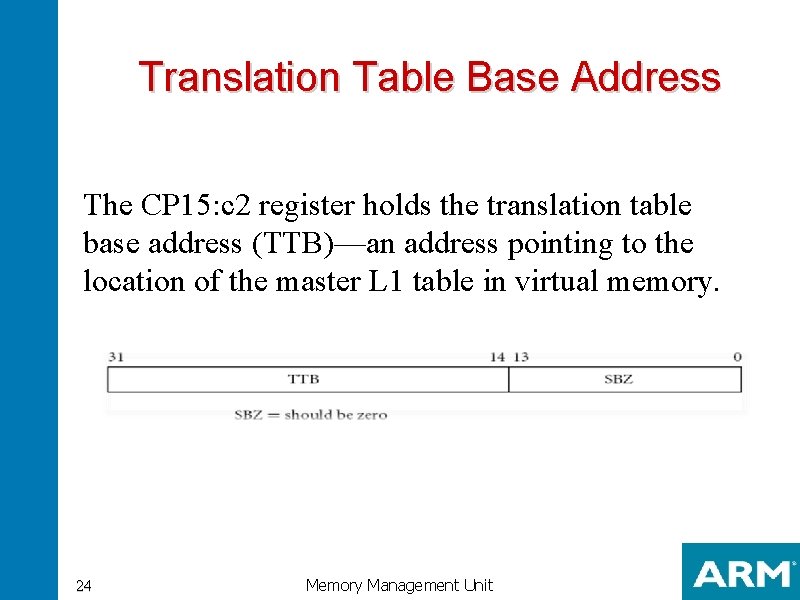

Translation Table Base Address The CP 15: c 2 register holds the translation table base address (TTB)—an address pointing to the location of the master L 1 table in virtual memory. 24 Memory Management Unit

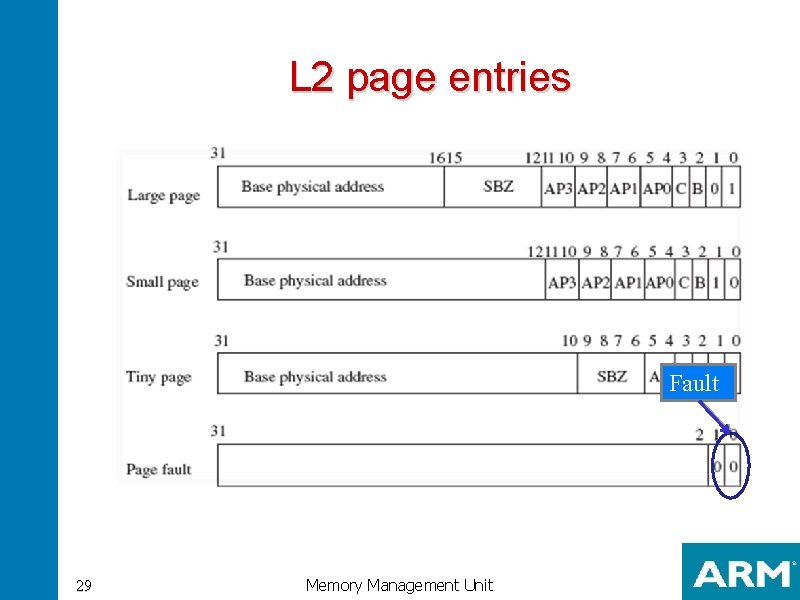

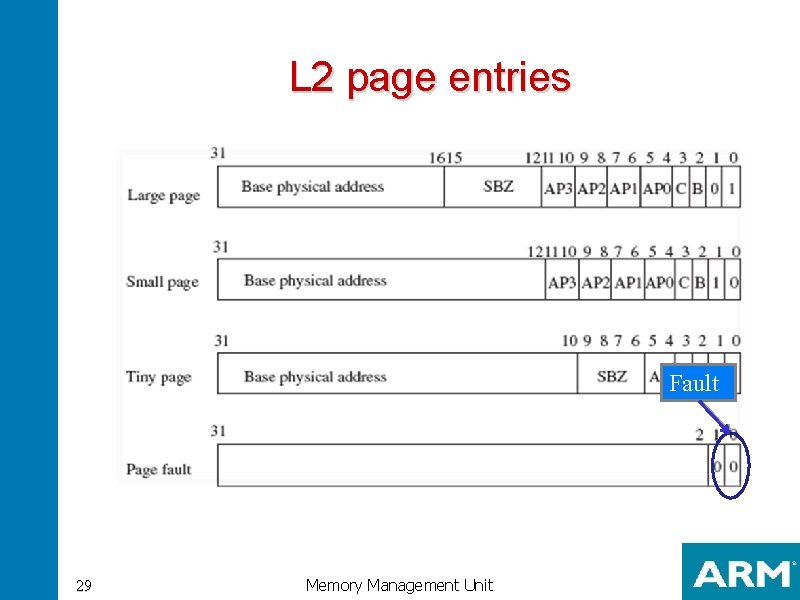

Level 2 page table accepts four types of entry • A large page entry defines the attributes for a 64 KB page frame. • A small page entry defines a 4 KB page frame. • A tiny page entry defines a 1 KB page frame. • A fault page entry generates a page fault abort exception when accessed. 25 Memory Management Unit

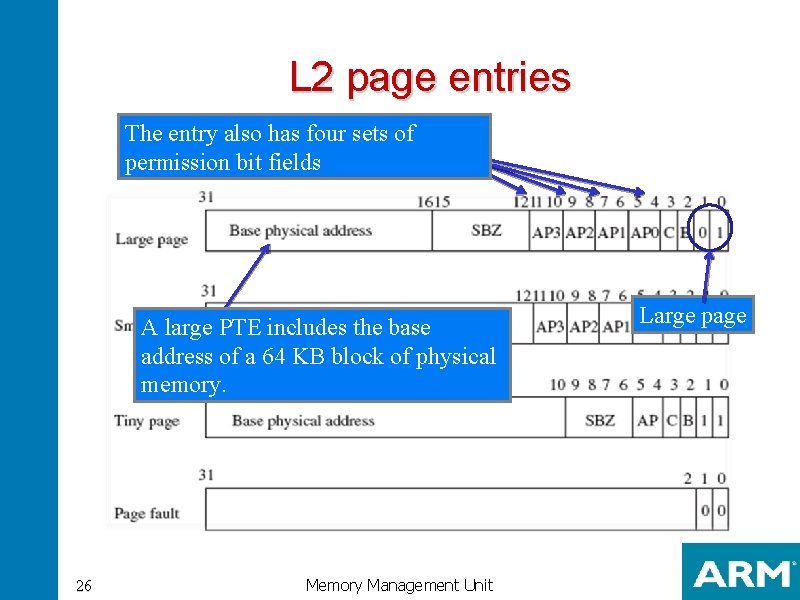

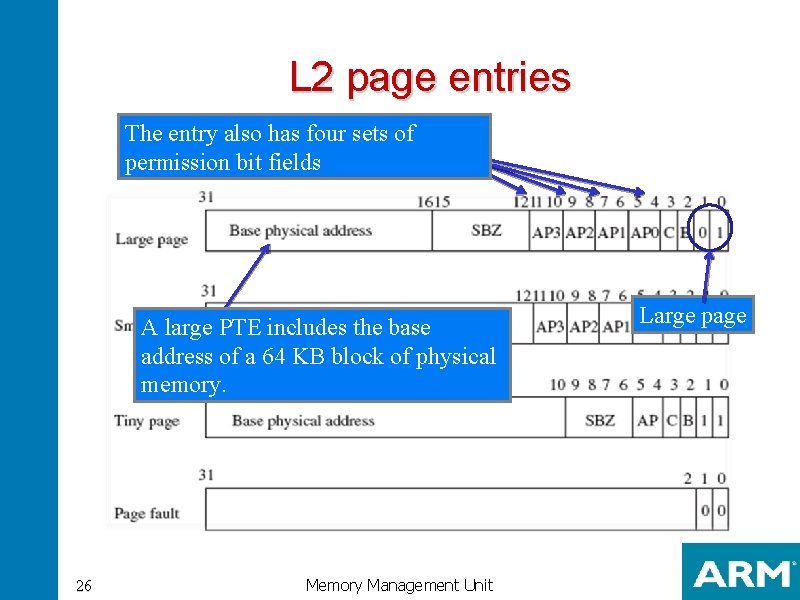

L 2 page entries The entry also has four sets of permission bit fields A large PTE includes the base address of a 64 KB block of physical memory. 26 Memory Management Unit Large page

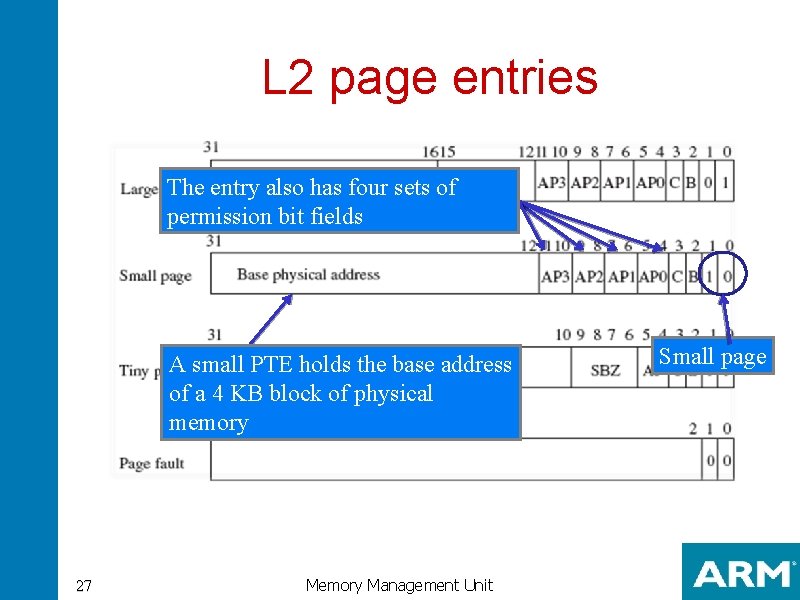

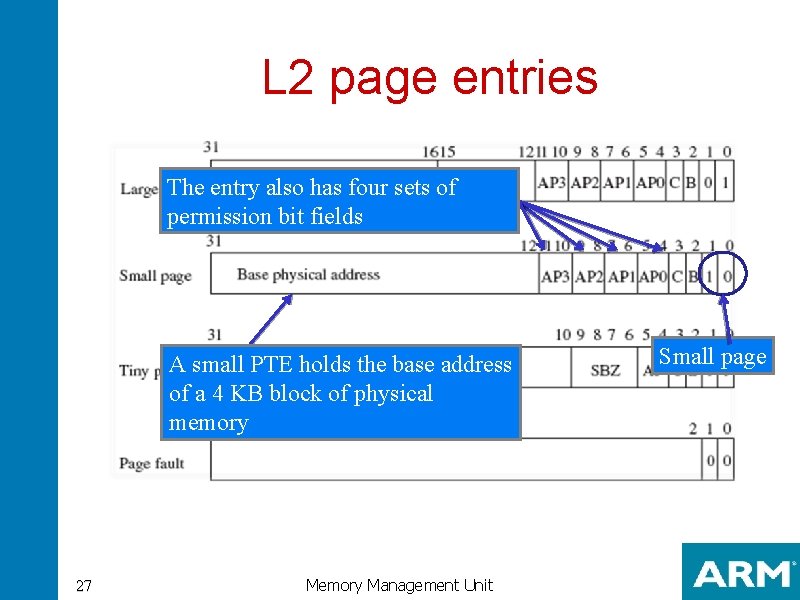

L 2 page entries The entry also has four sets of permission bit fields A small PTE holds the base address of a 4 KB block of physical memory 27 Memory Management Unit Small page

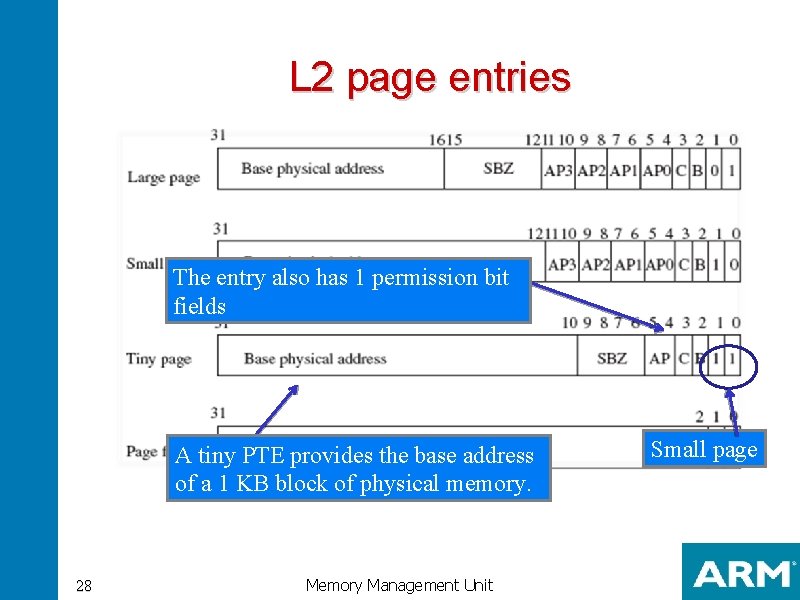

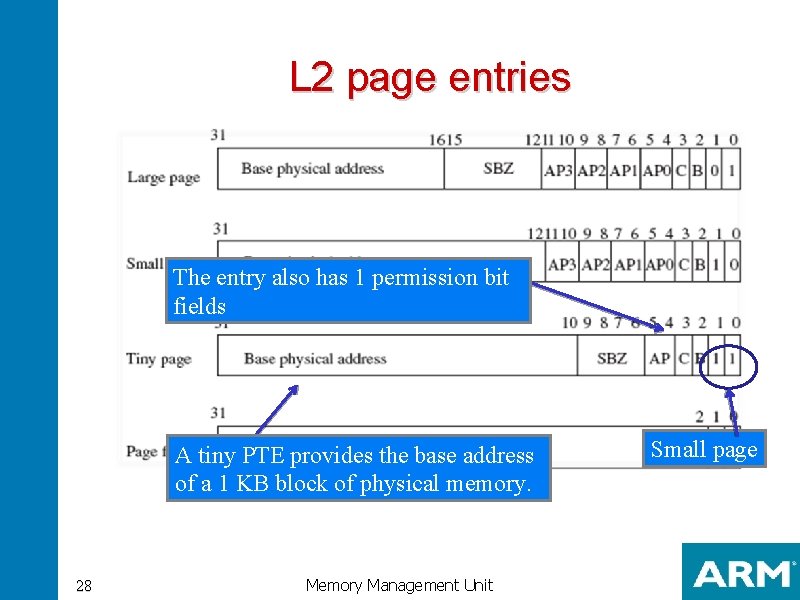

L 2 page entries The entry also has 1 permission bit fields A tiny PTE provides the base address of a 1 KB block of physical memory. 28 Memory Management Unit Small page

L 2 page entries Fault 29 Memory Management Unit

Agenda • • • 30 1. What we will learn from chapter ? 2. Introduction 3. Moving From An MPU To An MMU 4. How Virtual Memory works 4. 1 The components of a virtual memory system 4. 2 Defining Regions Using Pages 4. 3 Multitasking and The MMU 4. 4 Memory Organization in a Virtual Memory System 5. Details Of The ARM MMU 6. Page Table 6. 1 Level 1 6. 2 Translation Table Base Address 6. 3 Level 2 7. Translation Lookaside Buffer 7. 1 L 1 Page table virtual-to-physical memory translation using 1 MB sections 7. 2 Two-level virtual-to-physical address translation using coarse page tables 7. 3 TLB Operations 8. Domain & Access permission 9. Caches and Write Buffer 10. Coprocessor 15 and MMU configuration 11. Fast Context Switch Extension (FCSE) 12. A small virtual memory system Memory Management Unit

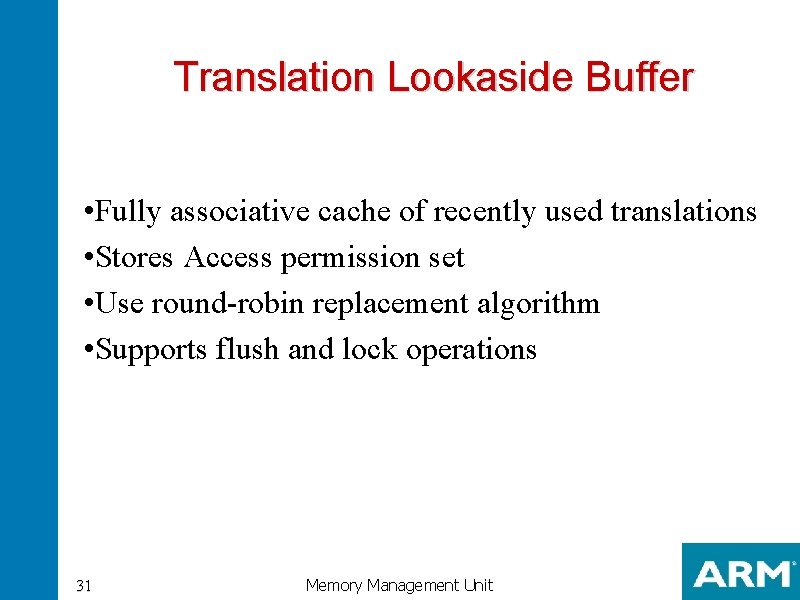

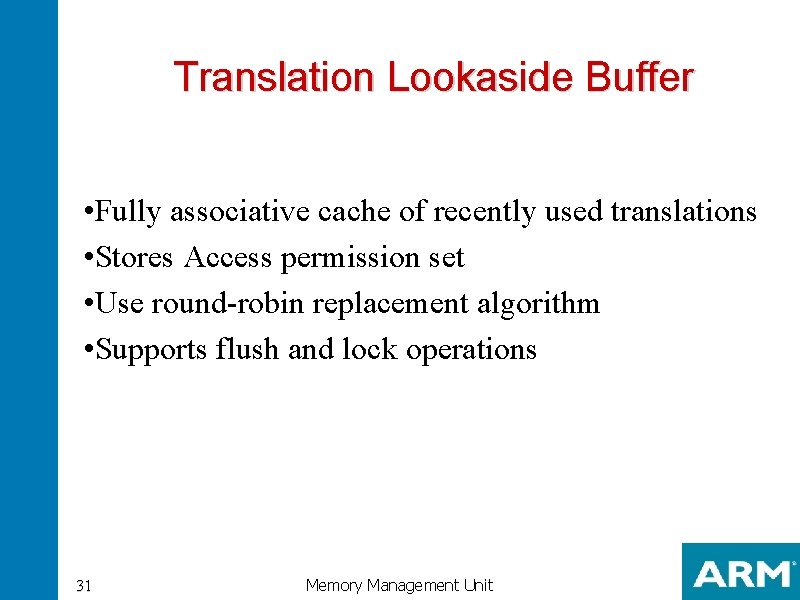

Translation Lookaside Buffer • Fully associative cache of recently used translations • Stores Access permission set • Use round-robin replacement algorithm • Supports flush and lock operations 31 Memory Management Unit

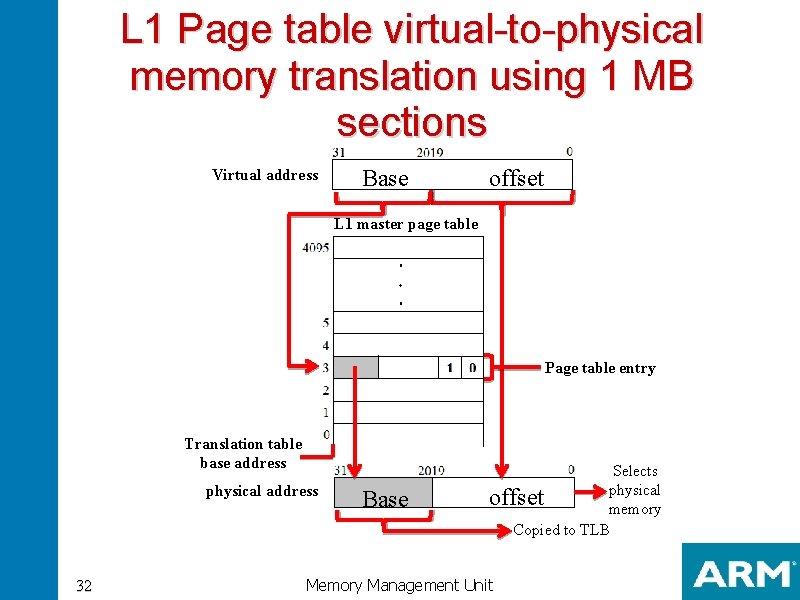

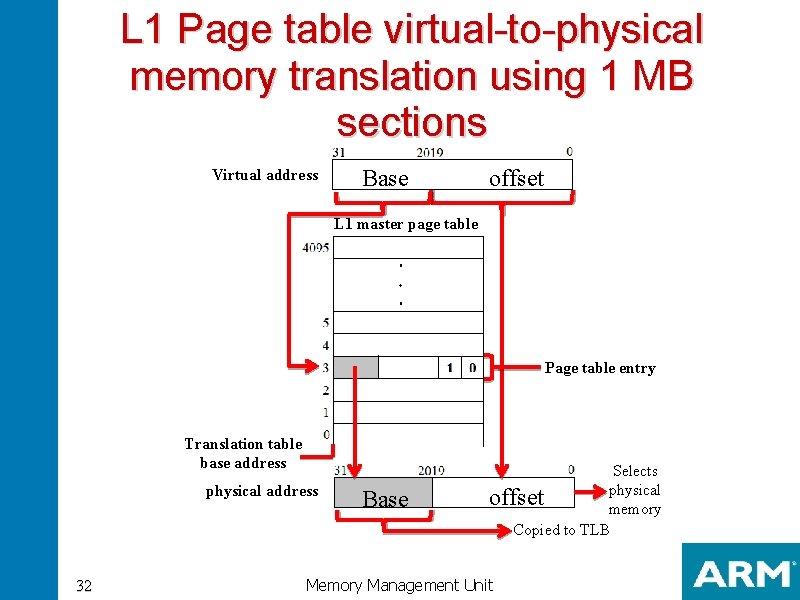

L 1 Page table virtual-to-physical memory translation using 1 MB sections Virtual address Base offset L 1 master page table Page table entry Translation table base address physical address 32 Base Selects physical offset memory Copied to TLB Memory Management Unit

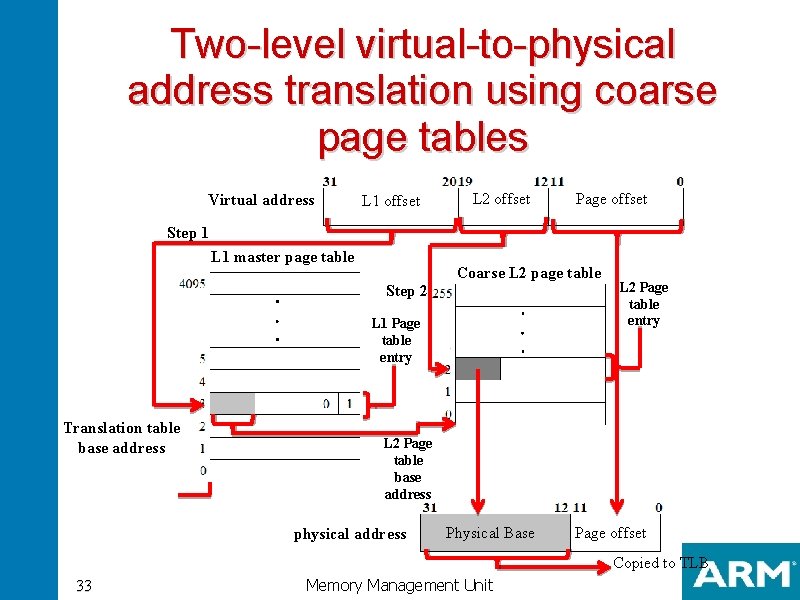

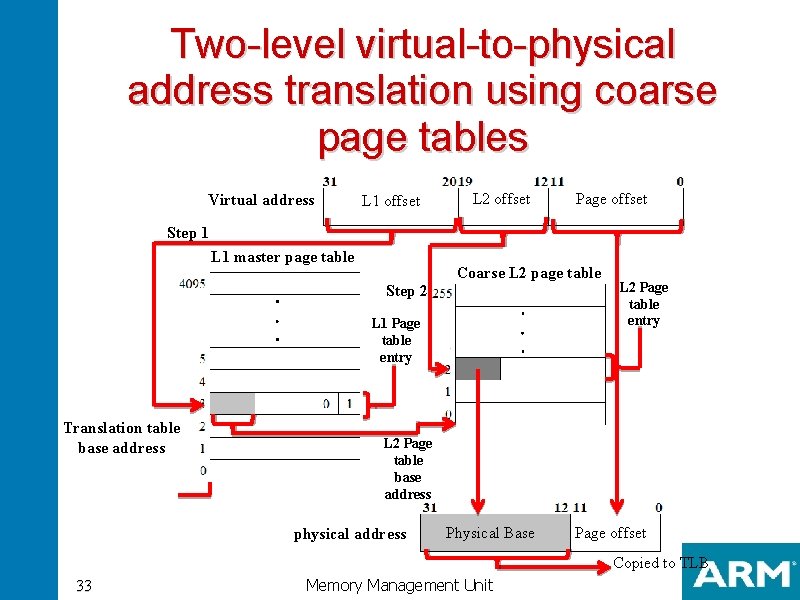

Two-level virtual-to-physical address translation using coarse page tables Virtual address L 1 offset L 2 offset Page offset Step 1 L 1 master page table Coarse L 2 page table Step 2 L 1 Page table entry Translation table base address L 2 Page table entry L 2 Page table base address physical address Physical Base Page offset Copied to TLB 33 Memory Management Unit

TLB Operations 42 f 4 6726 3889 ab 56 35 de 9001 f 8 d 9 8845 8787 7842 8 fd 3 9999 34 Lock down 6726 Flush 9001 8 fd 3 Memory Management Unit

Agenda • • • 35 1. What we will learn from chapter ? 2. Introduction 3. Moving From An MPU To An MMU 4. How Virtual Memory works 4. 1 The components of a virtual memory system 4. 2 Defining Regions Using Pages 4. 3 Multitasking and The MMU 4. 4 Memory Organization in a Virtual Memory System 5. Details Of The ARM MMU 6. Page Table 6. 1 Level 1 6. 2 Translation Table Base Address 6. 3 Level 2 7. Translation Lookaside Buffer 7. 1 L 1 Page table virtual-to-physical memory translation using 1 MB sections 7. 2 Two-level virtual-to-physical address translation using coarse page tables 7. 3 TLB Operations 8. Domain & Access permission 9. Caches and Write Buffer 10. Coprocessor 15 and MMU configuration 11. Fast Context Switch Extension (FCSE) 12. A small virtual memory system Memory Management Unit

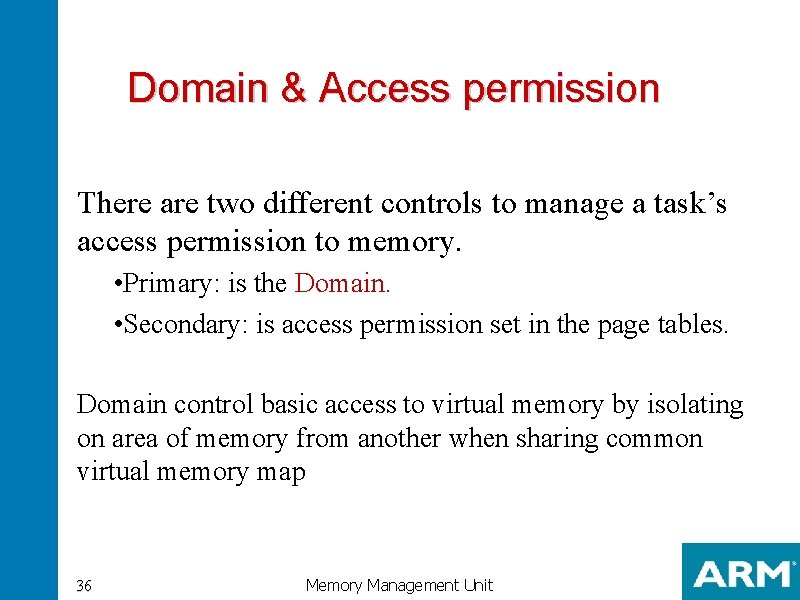

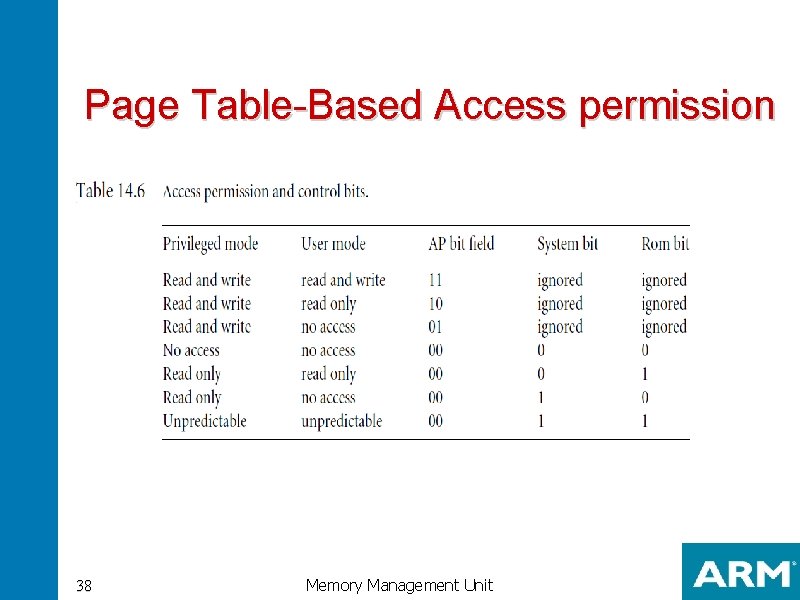

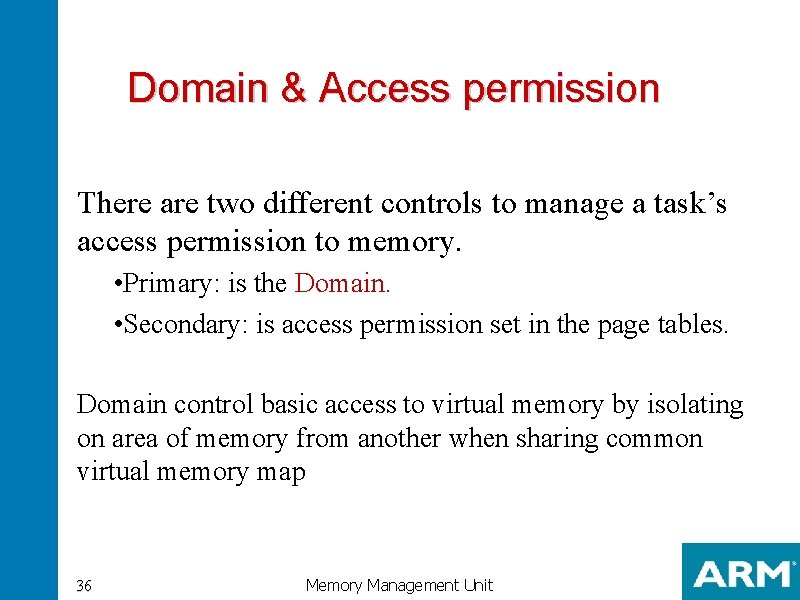

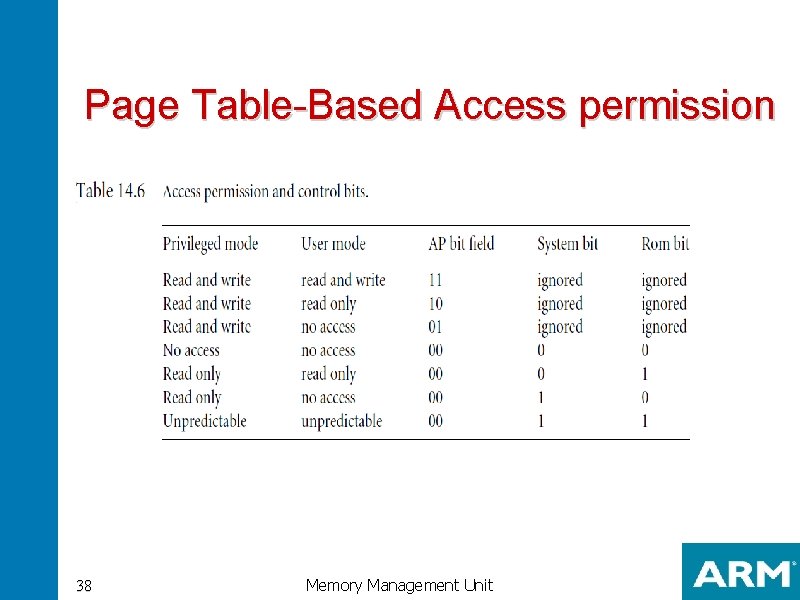

Domain & Access permission There are two different controls to manage a task’s access permission to memory. • Primary: is the Domain. • Secondary: is access permission set in the page tables. Domain control basic access to virtual memory by isolating on area of memory from another when sharing common virtual memory map 36 Memory Management Unit

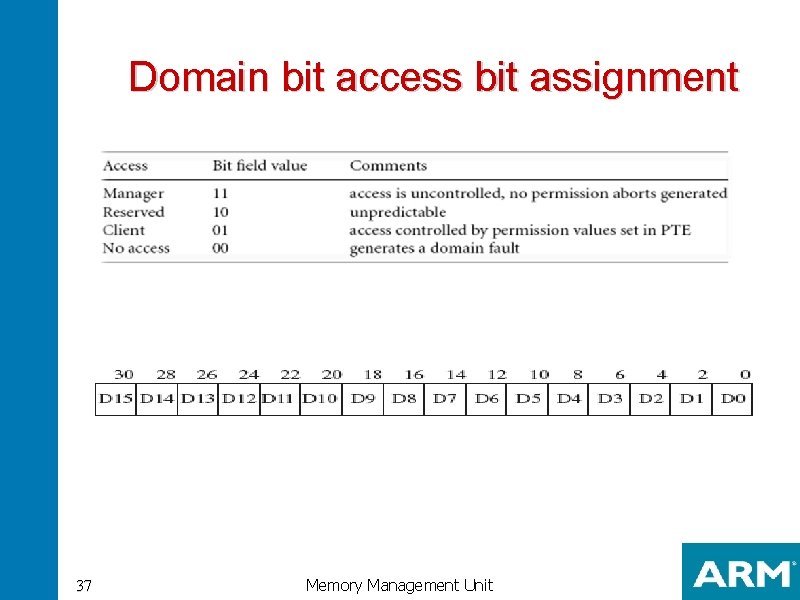

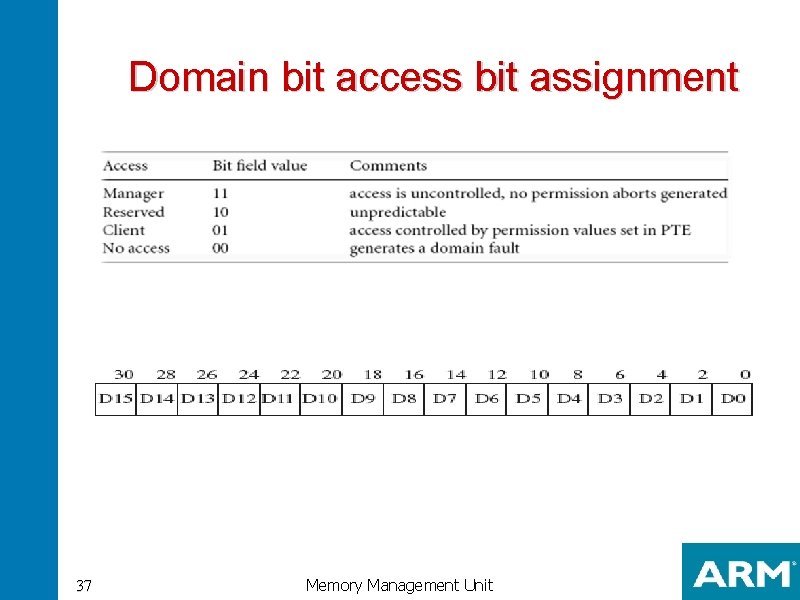

Domain bit access bit assignment 37 Memory Management Unit

Page Table-Based Access permission 38 Memory Management Unit

Agenda • • • 39 1. What we will learn from chapter ? 2. Introduction 3. Moving From An MPU To An MMU 4. How Virtual Memory works 4. 1 The components of a virtual memory system 4. 2 Defining Regions Using Pages 4. 3 Multitasking and The MMU 4. 4 Memory Organization in a Virtual Memory System 5. Details Of The ARM MMU 6. Page Table 6. 1 Level 1 6. 2 Translation Table Base Address 6. 3 Level 2 7. Translation Lookaside Buffer 7. 1 L 1 Page table virtual-to-physical memory translation using 1 MB sections 7. 2 Two-level virtual-to-physical address translation using coarse page tables 7. 3 TLB Operations 8. Domain & Access permission 9. Caches and Write Buffer 10. Coprocessor 15 and MMU configuration 11. Fast Context Switch Extension (FCSE) 12. A small virtual memory system Memory Management Unit

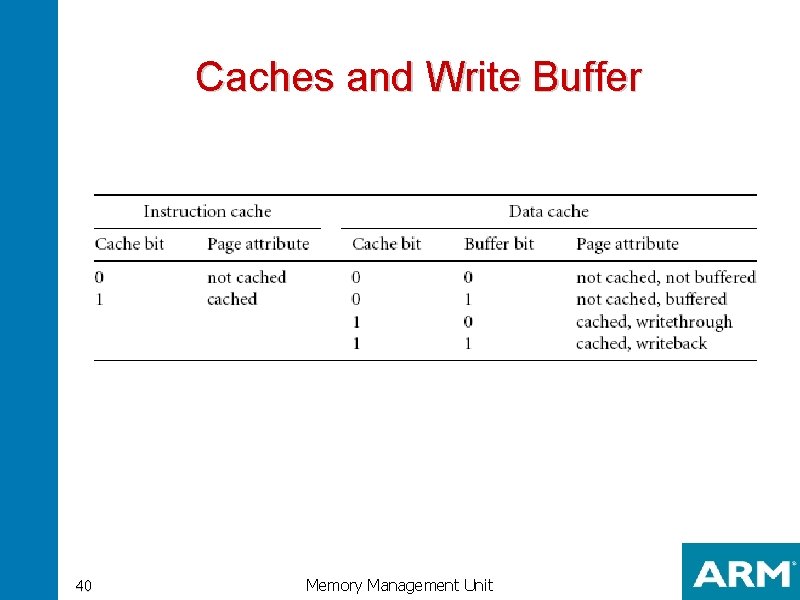

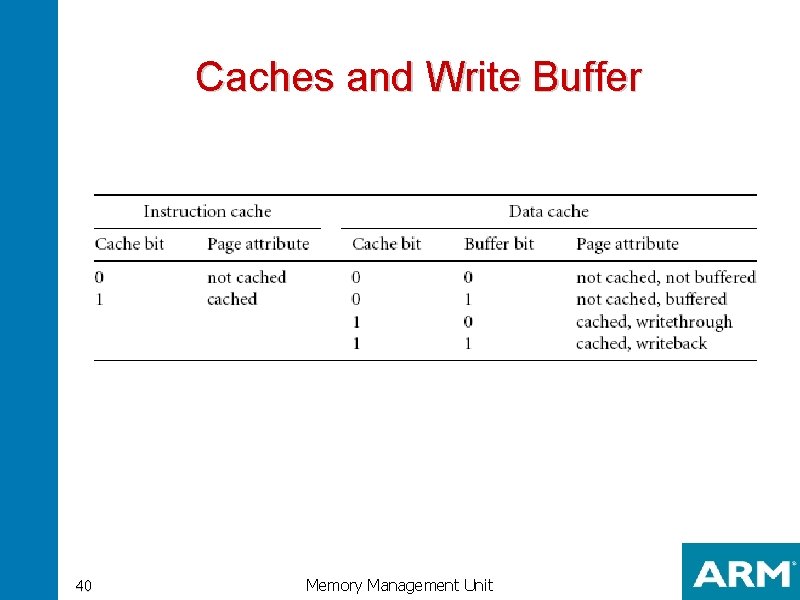

Caches and Write Buffer 40 Memory Management Unit

Agenda • • • 41 1. What we will learn from chapter ? 2. Introduction 3. Moving From An MPU To An MMU 4. How Virtual Memory works 4. 1 The components of a virtual memory system 4. 2 Defining Regions Using Pages 4. 3 Multitasking and The MMU 4. 4 Memory Organization in a Virtual Memory System 5. Details Of The ARM MMU 6. Page Table 6. 1 Level 1 6. 2 Translation Table Base Address 6. 3 Level 2 7. Translation Lookaside Buffer 7. 1 L 1 Page table virtual-to-physical memory translation using 1 MB sections 7. 2 Two-level virtual-to-physical address translation using coarse page tables 7. 3 TLB Operations 8. Domain & Access permission 9. Caches and Write Buffer 10. Coprocessor 15 and MMU configuration 11. Fast Context Switch Extension (FCSE) 12. A small virtual memory system Memory Management Unit

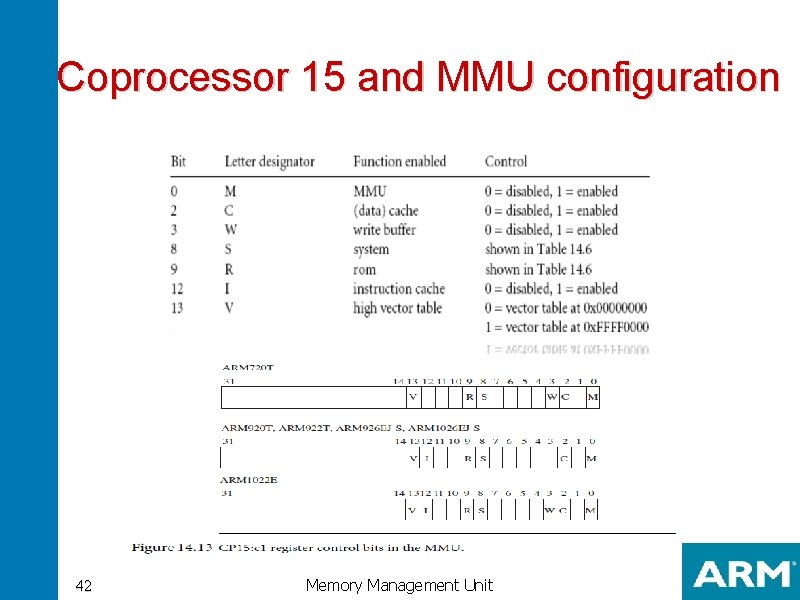

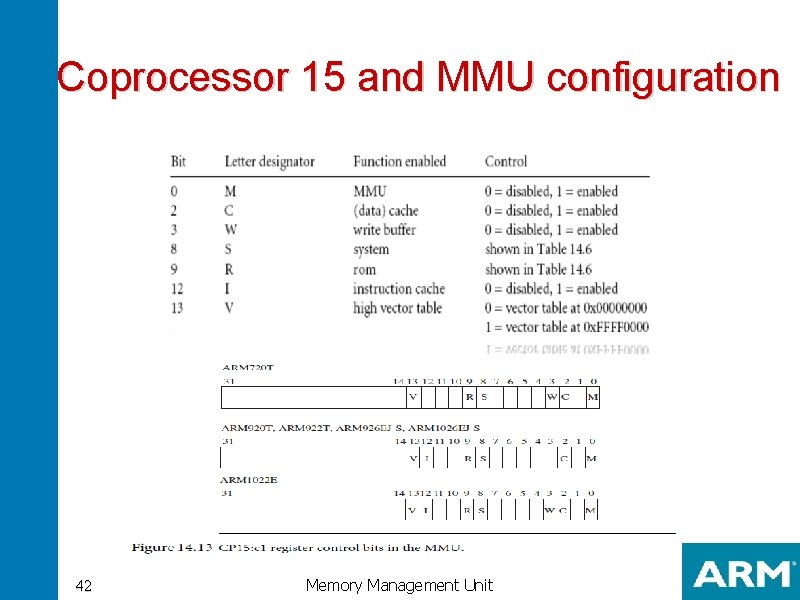

Coprocessor 15 and MMU configuration 42 Memory Management Unit

Agenda • • • 43 1. What we will learn from chapter ? 2. Introduction 3. Moving From An MPU To An MMU 4. How Virtual Memory works 4. 1 The components of a virtual memory system 4. 2 Defining Regions Using Pages 4. 3 Multitasking and The MMU 4. 4 Memory Organization in a Virtual Memory System 5. Details Of The ARM MMU 6. Page Table 6. 1 Level 1 6. 2 Translation Table Base Address 6. 3 Level 2 7. Translation Lookaside Buffer 7. 1 L 1 Page table virtual-to-physical memory translation using 1 MB sections 7. 2 Two-level virtual-to-physical address translation using coarse page tables 7. 3 TLB Operations 8. Domain & Access permission 9. Caches and Write Buffer 10. Coprocessor 15 and MMU configuration 11. Fast Context Switch Extension (FCSE) 12. A small virtual memory system Memory Management Unit

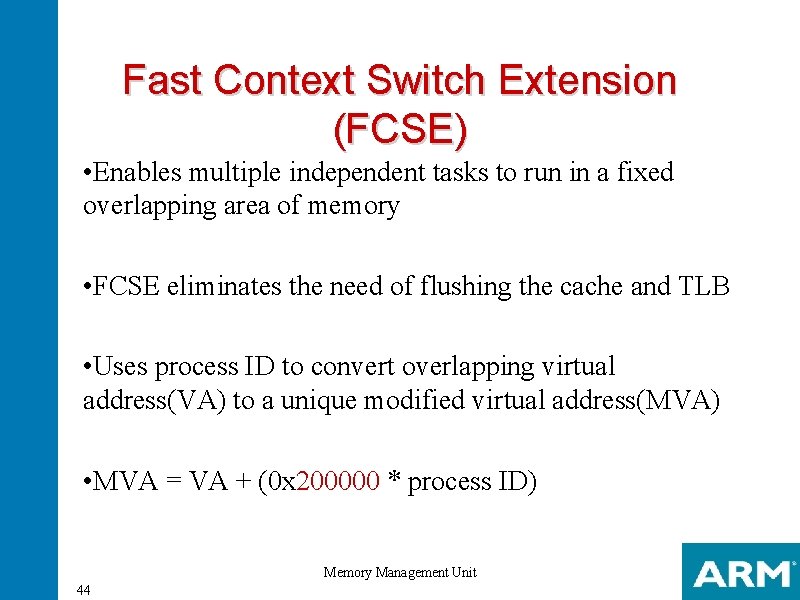

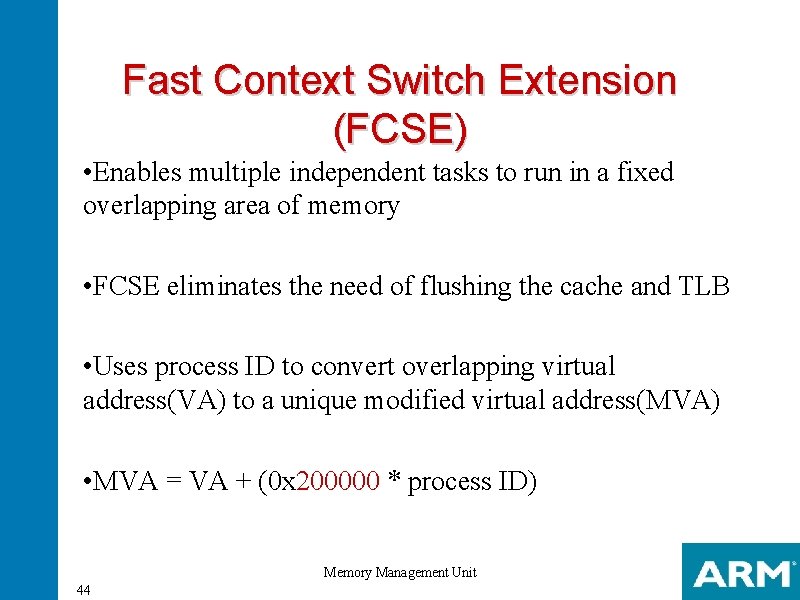

Fast Context Switch Extension (FCSE) • Enables multiple independent tasks to run in a fixed overlapping area of memory • FCSE eliminates the need of flushing the cache and TLB • Uses process ID to convert overlapping virtual address(VA) to a unique modified virtual address(MVA) • MVA = VA + (0 x 200000 * process ID) Memory Management Unit 44

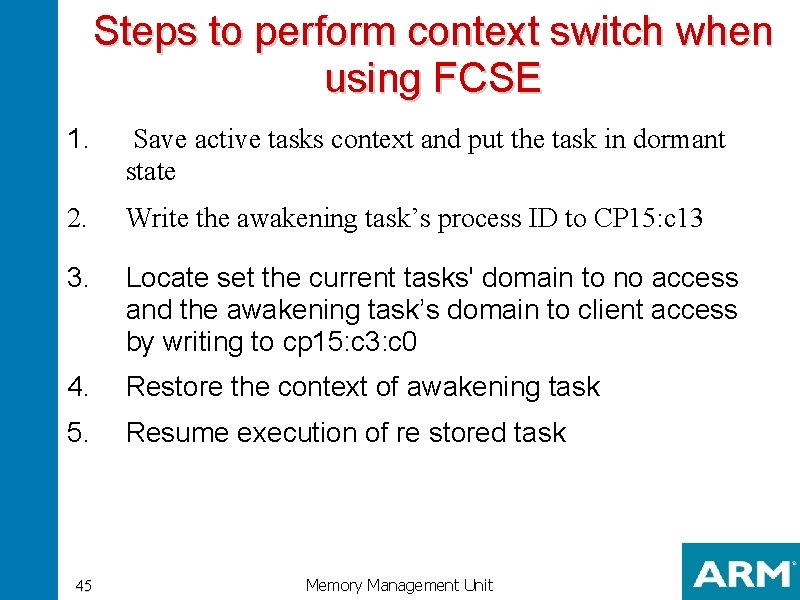

Steps to perform context switch when using FCSE 1. Save active tasks context and put the task in dormant state 2. Write the awakening task’s process ID to CP 15: c 13 3. Locate set the current tasks' domain to no access and the awakening task’s domain to client access by writing to cp 15: c 3: c 0 4. Restore the context of awakening task 5. Resume execution of re stored task 45 Memory Management Unit

Agenda • • • 46 1. What we will learn from chapter ? 2. Introduction 3. Moving From An MPU To An MMU 4. How Virtual Memory works 4. 1 The components of a virtual memory system 4. 2 Defining Regions Using Pages 4. 3 Multitasking and The MMU 4. 4 Memory Organization in a Virtual Memory System 5. Details Of The ARM MMU 6. Page Table 6. 1 Level 1 6. 2 Translation Table Base Address 6. 3 Level 2 7. Translation Lookaside Buffer 7. 1 L 1 Page table virtual-to-physical memory translation using 1 MB sections 7. 2 Two-level virtual-to-physical address translation using coarse page tables 7. 3 TLB Operations 8. Domain & Access permission 9. Caches and Write Buffer 10. Coprocessor 15 and MMU configuration 11. Fast Context Switch Extension (FCSE) 12. A small virtual memory system Memory Management Unit

A small virtual memory system • 3 Tasks • The same execution region • 256 MB of memory for peripheral devices Very simple example! 47 Memory Management Unit

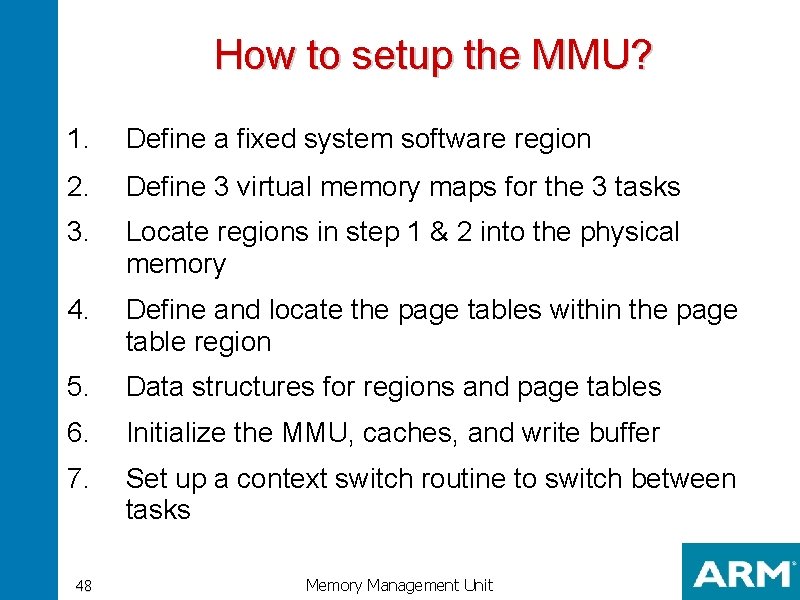

How to setup the MMU? 1. Define a fixed system software region 2. Define 3 virtual memory maps for the 3 tasks 3. Locate regions in step 1 & 2 into the physical memory 4. Define and locate the page tables within the page table region 5. Data structures for regions and page tables 6. Initialize the MMU, caches, and write buffer 7. Set up a context switch routine to switch between tasks 48 Memory Management Unit

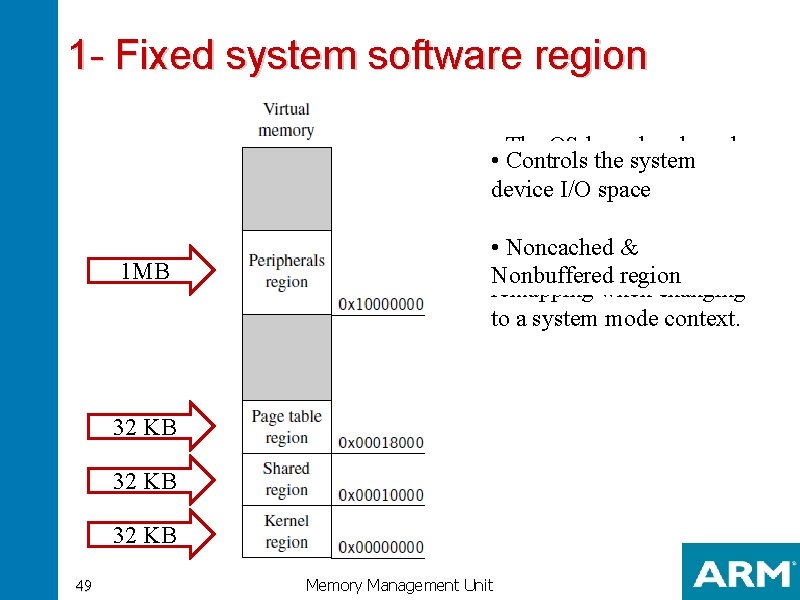

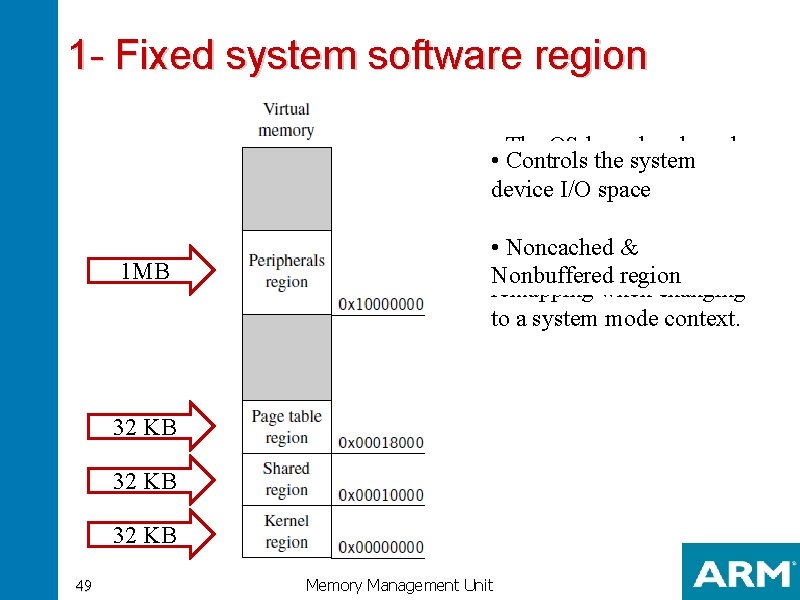

1 - Fixed system software region 1 MB • • • The OSfor kernel code and Shared libraries 16 KB the master Controls the system data table device I/O space • The transition routines • for addressing tofour avoid switching from • Fixed 1 Noncached KB each for the & the complexity ofto user privileged mode L 2 tables. Nonbuffered region remapping when changing mode during a context to a system context. switch • 12 KB freemode memory 32 KB 49 Memory Management Unit

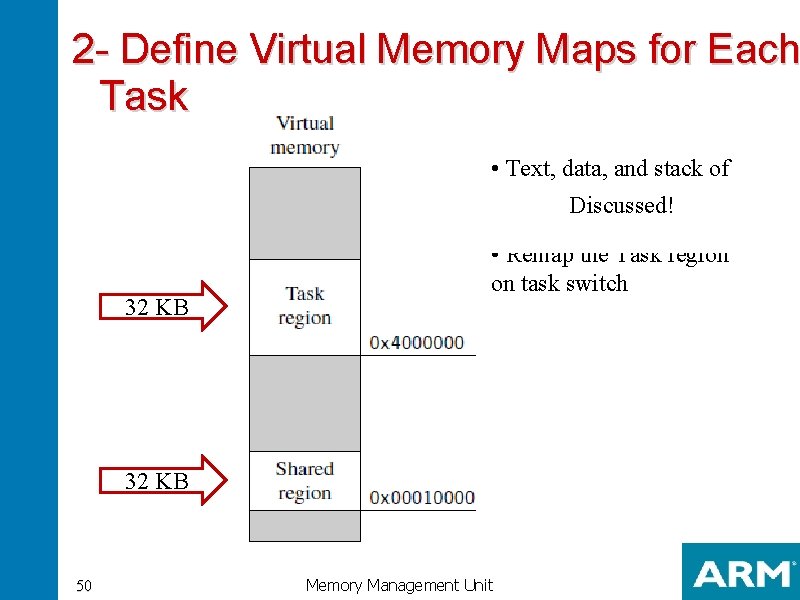

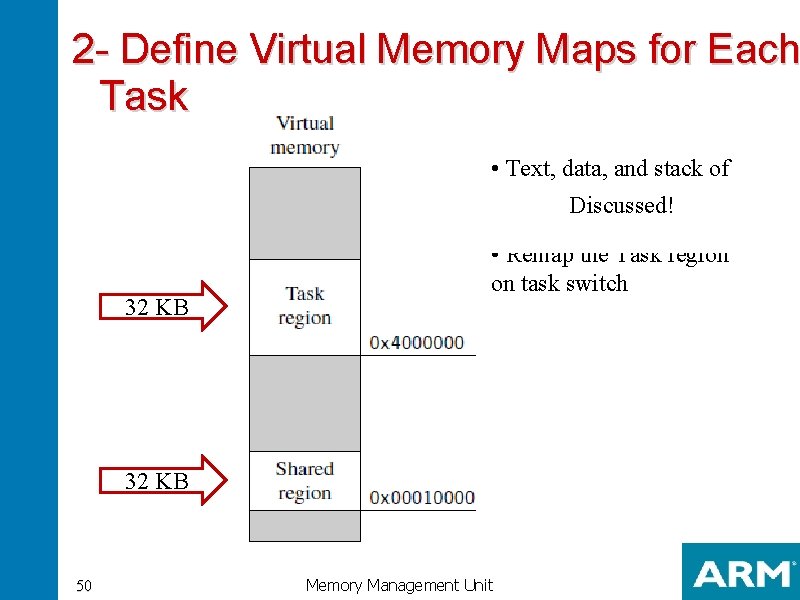

2 - Define Virtual Memory Maps for Each Task • Text, data, and stack of the running user task. Discussed! 32 KB • Remap the Task region on task switch 32 KB 50 Memory Management Unit

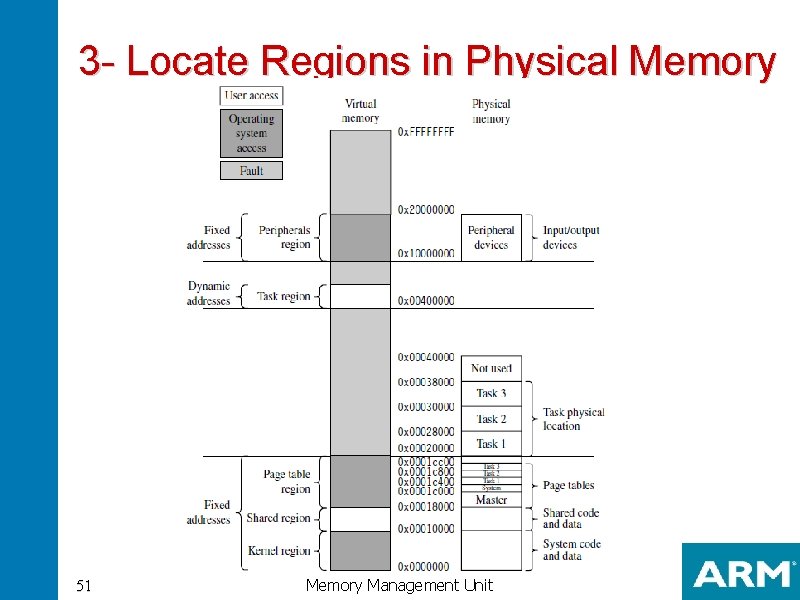

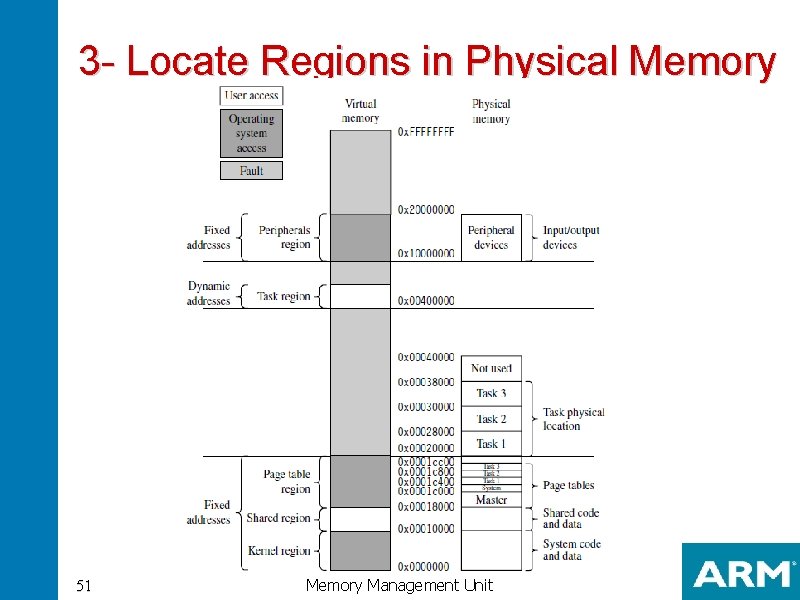

3 - Locate Regions in Physical Memory 51 Memory Management Unit

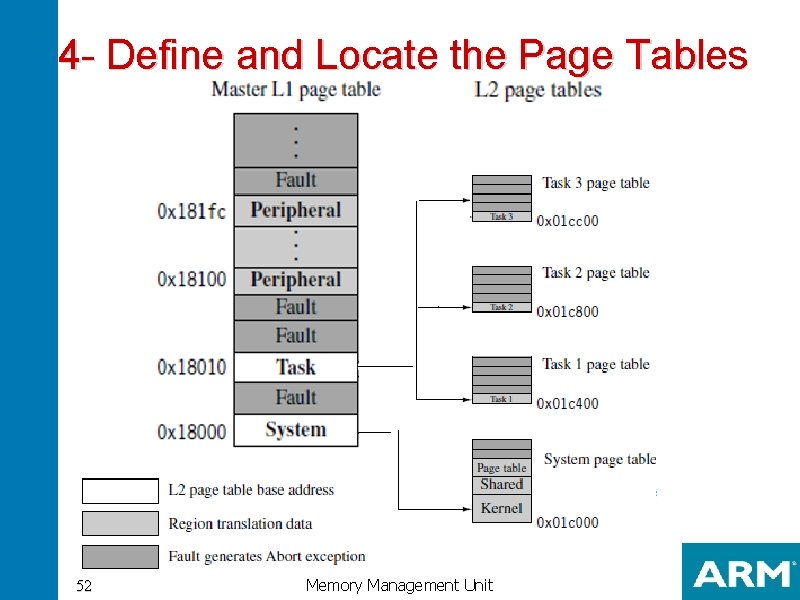

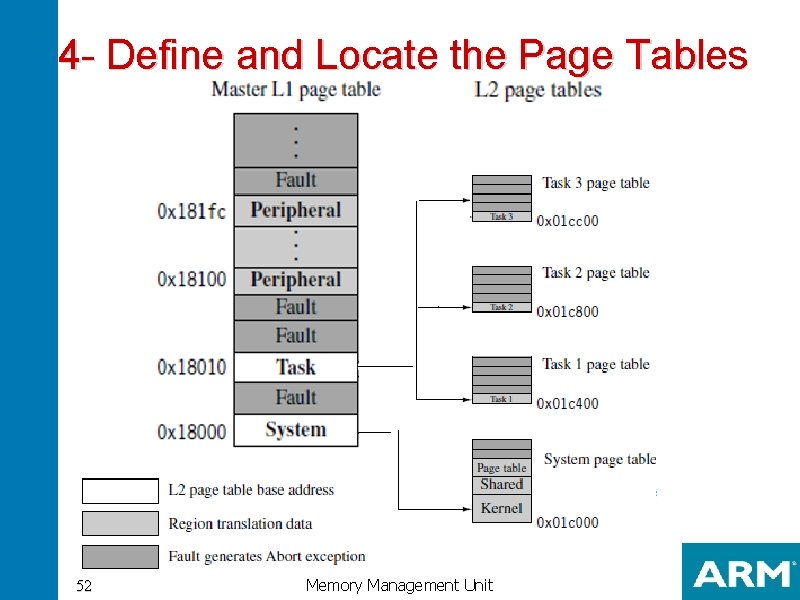

4 - Define and Locate the Page Tables 52 Memory Management Unit

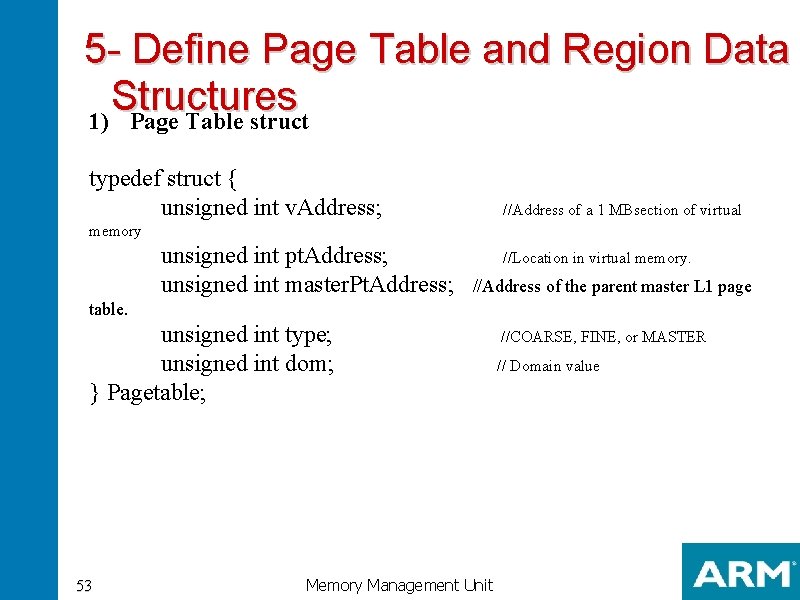

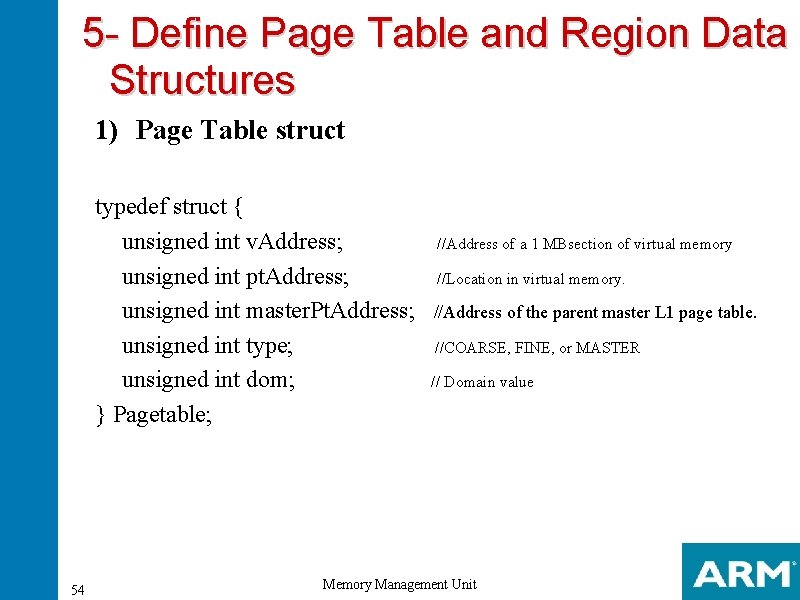

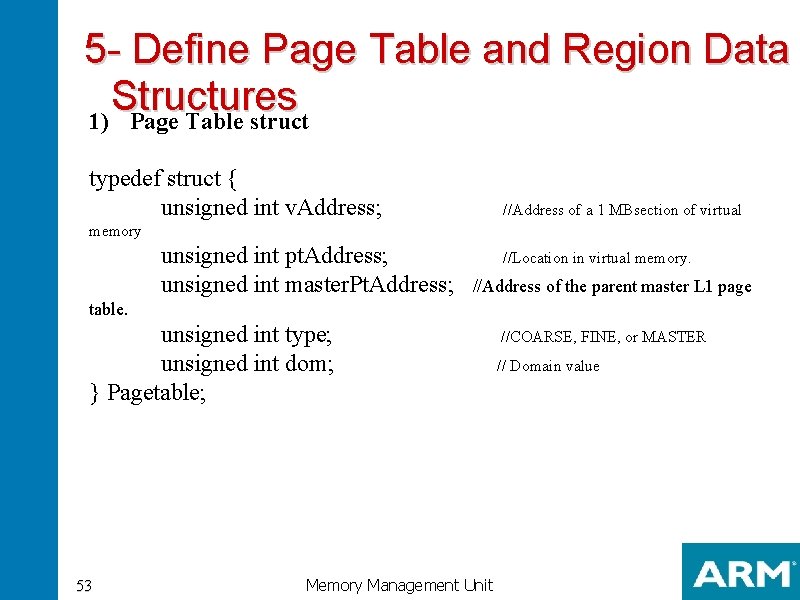

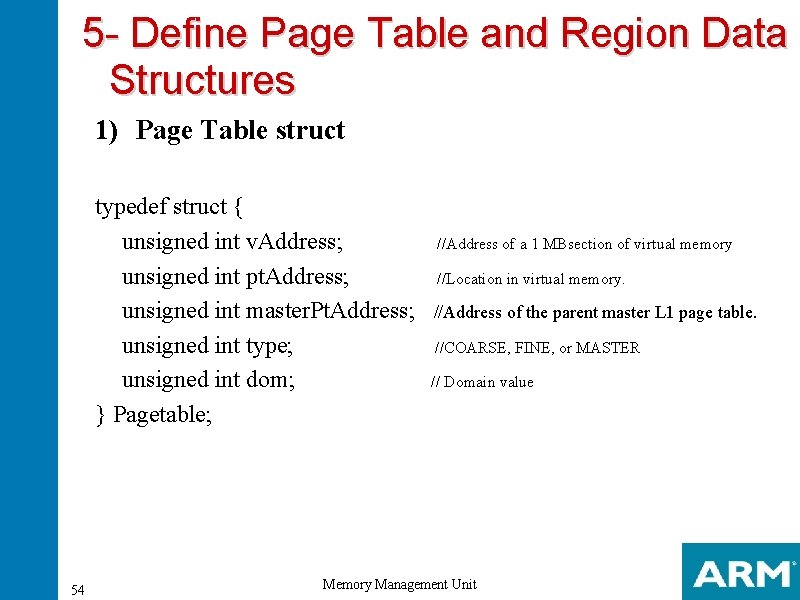

5 - Define Page Table and Region Data Structures 1) Page Table struct typedef struct { unsigned int v. Address; //Address of a 1 MBsection of virtual memory unsigned int pt. Address; unsigned int master. Pt. Address; //Location in virtual memory. //Address of the parent master L 1 page table. unsigned int type; unsigned int dom; } Pagetable; 53 Memory Management Unit //COARSE, FINE, or MASTER // Domain value

5 - Define Page Table and Region Data Structures 1) Page Table struct typedef struct { unsigned int v. Address; unsigned int pt. Address; unsigned int master. Pt. Address; unsigned int type; unsigned int dom; } Pagetable; 54 //Address of a 1 MBsection of virtual memory //Location in virtual memory. //Address of the parent master L 1 page table. //COARSE, FINE, or MASTER // Domain value Memory Management Unit

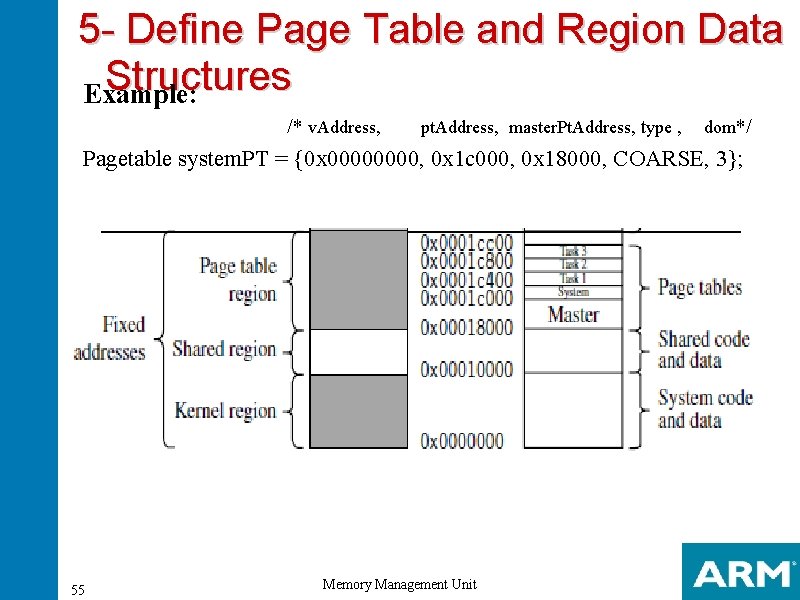

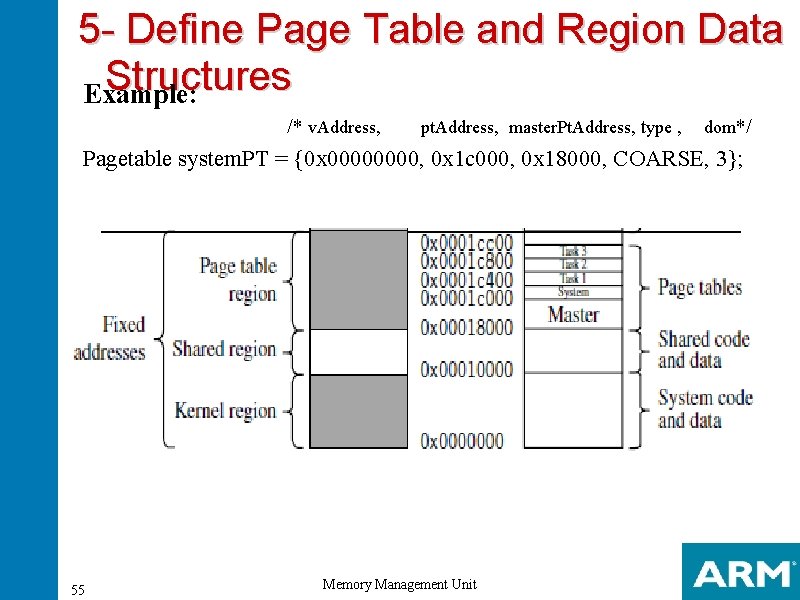

5 - Define Page Table and Region Data Structures Example: /* v. Address, pt. Address, master. Pt. Address, type , dom*/ Pagetable system. PT = {0 x 0000, 0 x 1 c 000, 0 x 18000, COARSE, 3}; 55 Memory Management Unit

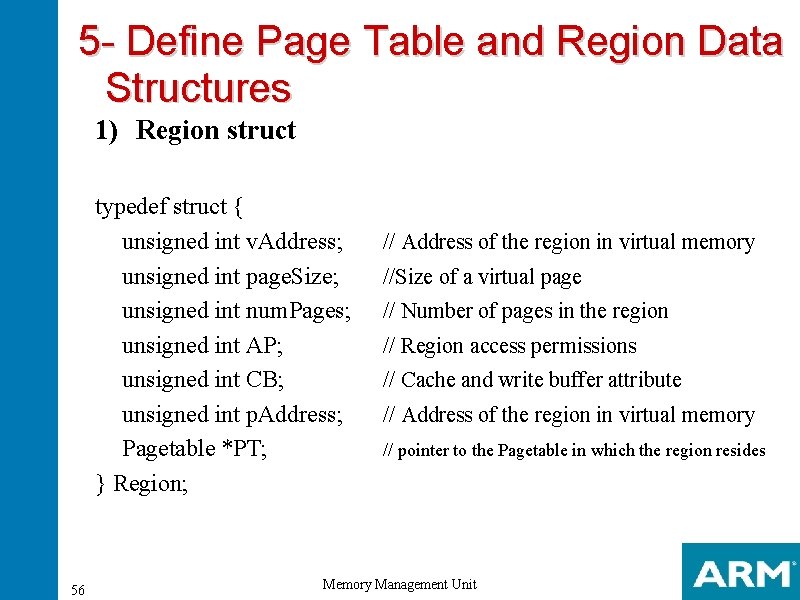

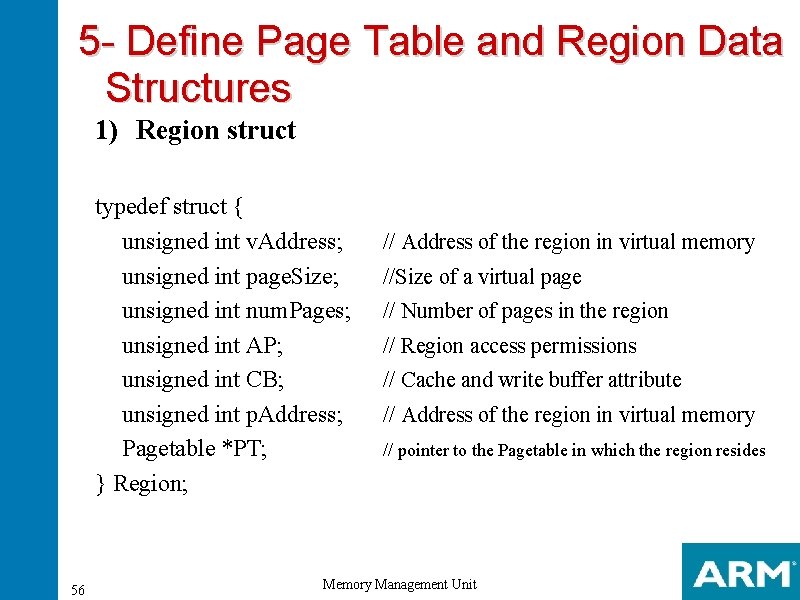

5 - Define Page Table and Region Data Structures 1) Region struct typedef struct { unsigned int v. Address; unsigned int page. Size; unsigned int num. Pages; unsigned int AP; unsigned int CB; unsigned int p. Address; Pagetable *PT; } Region; 56 // Address of the region in virtual memory //Size of a virtual page // Number of pages in the region // Region access permissions // Cache and write buffer attribute // Address of the region in virtual memory // pointer to the Pagetable in which the region resides Memory Management Unit

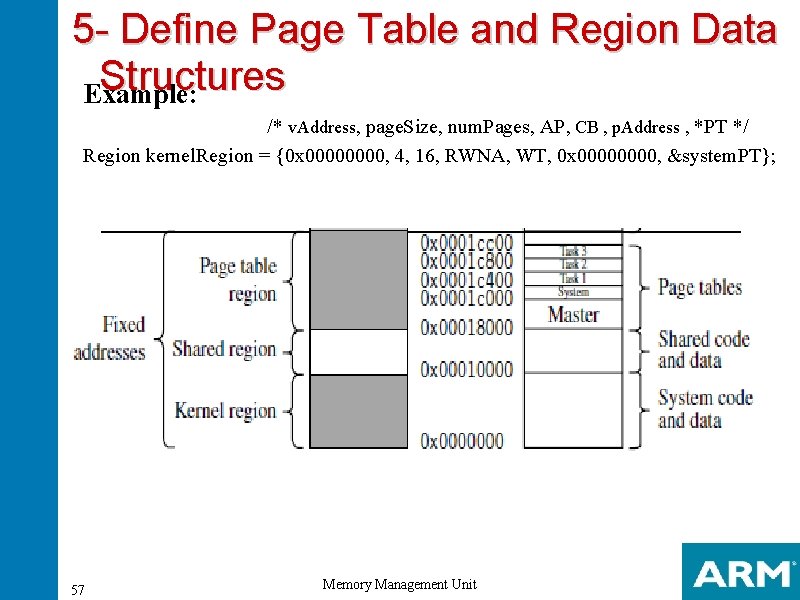

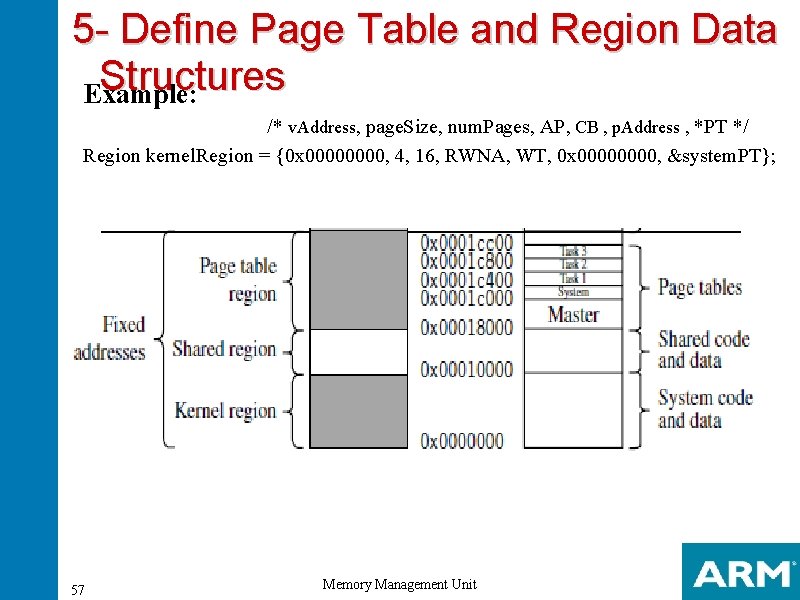

5 - Define Page Table and Region Data Structures Example: /* v. Address, page. Size, num. Pages, AP, CB , p. Address , *PT */ Region kernel. Region = {0 x 0000, 4, 16, RWNA, WT, 0 x 0000, &system. PT}; 57 Memory Management Unit

6 - Initialize the MMU, caches, and write buffer 1. Initialize the page tables in main memory by filling them with FAULT entries 2. Fill in the page tables with translations that map regions to physical memory. 3. Activate the page tables. 4. Assign domain access rights. 5. Enable the MMU and cache hardware 58 Memory Management Unit

6 - Initialize the MMU, caches, and write buffer 1)Initialize the page tables: mmu. Init. PT(Pagetable *); 59 • Fill the Page Table by Fault entries • The size of the table is determined by reading the type of Page table defined in pt->type (Master, Coarse, Fine) Memory Management Unit

6 - Initialize the MMU, caches, and write buffer 2)Filling Page Tables with Translations mmu. Map. Region(Region * region ){ switch (region->PT->type){ case SECTION mmu. Map. Section. Table. Region(region); case COARSE: mmu. Map. Coarse. Table. Region(region); case FINE: mmu. Map. Fine. Table. Region(region); } } 60 Memory Management Unit

6 - Initialize the MMU, caches, and write buffer 3) Activating a Page Table 61 • Why? • mmu. Attach. PT(Pagetable *pt); • It activates an L 1 master page table by placing its address into the TTB in the CP 15: c 2: c 0 register • Or activates an L 2 page table by placing its base address into an L 1 master page table entry Memory Management Unit

6 - Initialize the MMU, caches, and write buffer 4) Assigning Domain Access and Enabling the MMU 62 • All active memory areas must have a domain assignment • The minimum domain configuration places all regions in the same domain and sets the domain access to client access. • void domain. Access. Set(unsigned int value, unsigned int mask); Memory Management Unit

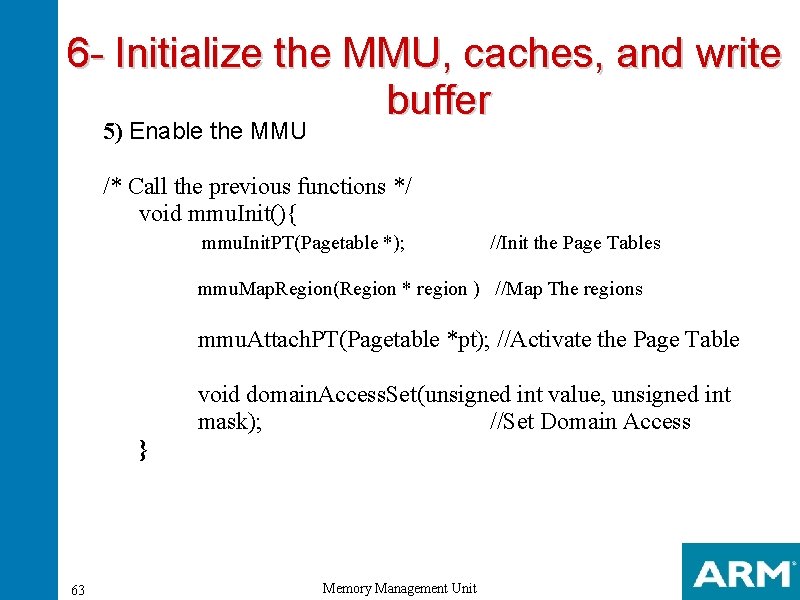

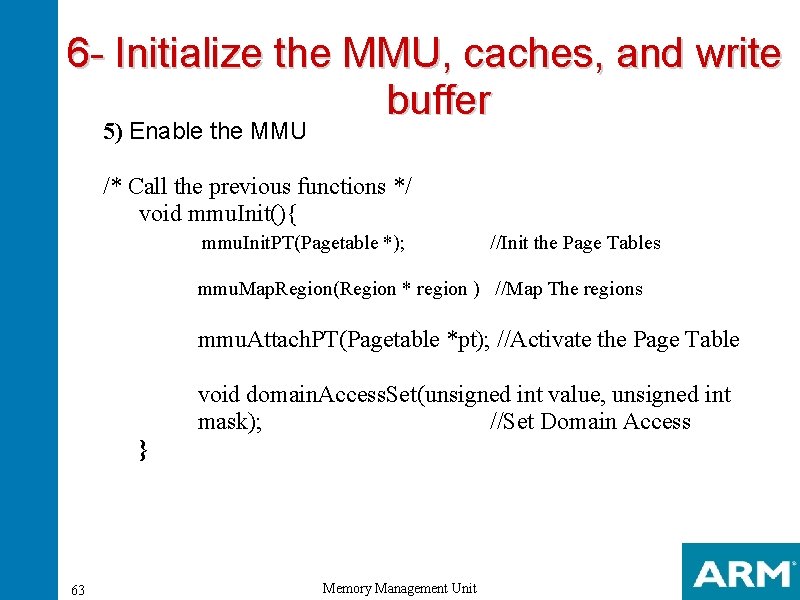

6 - Initialize the MMU, caches, and write buffer 5) Enable the MMU /* Call the previous functions */ void mmu. Init(){ mmu. Init. PT(Pagetable *); //Init the Page Tables mmu. Map. Region(Region * region ) //Map The regions mmu. Attach. PT(Pagetable *pt); //Activate the Page Table void domain. Access. Set(unsigned int value, unsigned int mask); //Set Domain Access } 63 Memory Management Unit

7 - Establish a Context Switch Procedure 1. Save the active task context and place the task in a dormant state. 2. Flush the caches 3. Flush the TLB to remove translations for the retiring task 4. Configure the MMU to use new page tables 5. Restore the context of the awakening task 6. Resume execution of the restored task 64 Memory Management Unit

Any Questions 65 Memory Management Unit