Virtual Memory System Rajesh Menon CS 550 Fall

- Slides: 26

Virtual Memory System Rajesh Menon CS 550 Fall 2003 1

Topics Covered in this study Ø VMS • History • Future? Ø The Processor Mode and the Process • Processor Modes • Process States • VMS OS model • Scheduling • SMP 2

Topics Covered in this study (cont’d) Ø Memory Management • Demand Paged Virtual Memory • Memory management subsystem Ø VMS data structures • Process Data Structures • Memory management Data Structures Ø Process Synchronization • Process Synchronization between two processes • Mutual Exclusion of Critical Regions 3

DEC VMS Ø Gained importance from 1980 – 1990 Ø VMS touted to be a leading-edge technology • Virtual Memory • 32 bit address space • 128 bit floating point number precision • Batch, Interactive and real-time processing Ø DEC was taken over by COMPAQ and COMPAQ later merged with HP. 4

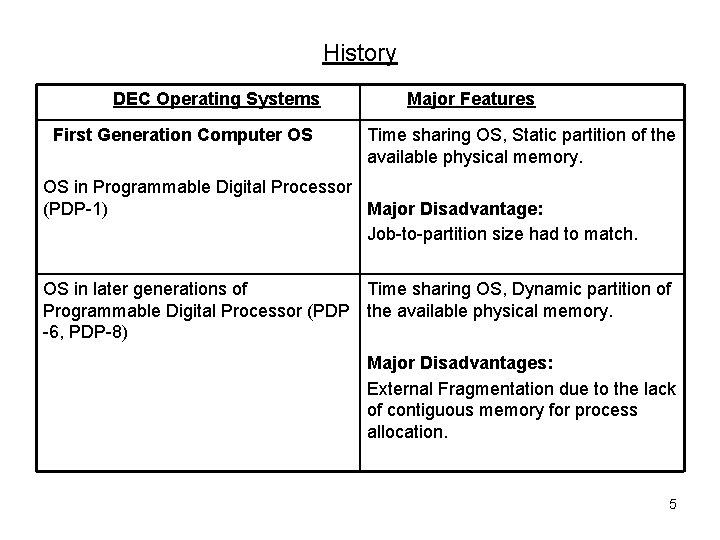

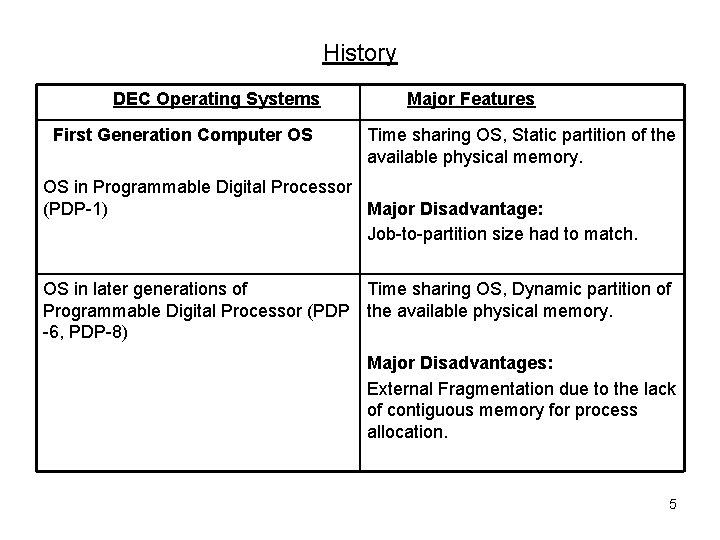

History DEC Operating Systems First Generation Computer OS Major Features Time sharing OS, Static partition of the available physical memory. OS in Programmable Digital Processor (PDP-1) Major Disadvantage: Job-to-partition size had to match. OS in later generations of Time sharing OS, Dynamic partition of Programmable Digital Processor (PDP the available physical memory. -6, PDP-8) Major Disadvantages: External Fragmentation due to the lack of contiguous memory for process allocation. 5

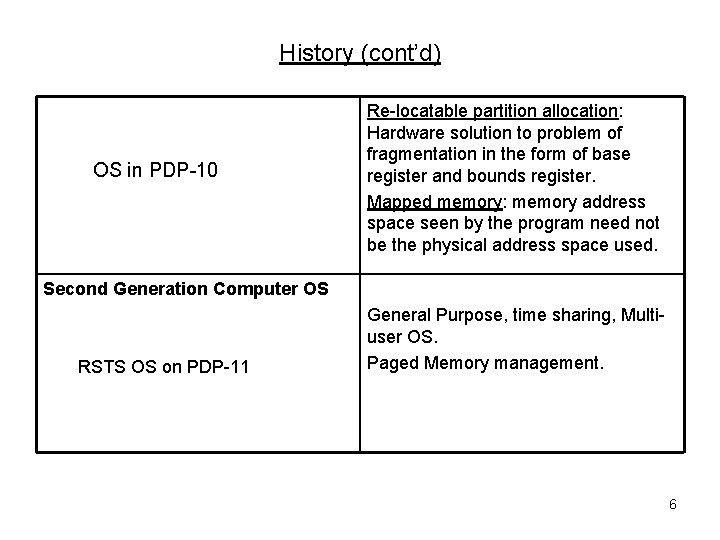

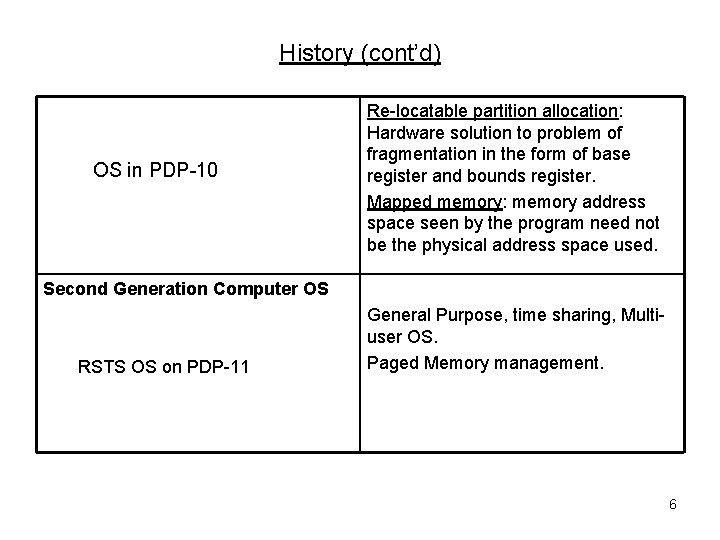

History (cont’d) OS in PDP-10 Re-locatable partition allocation: Hardware solution to problem of fragmentation in the form of base register and bounds register. Mapped memory: memory address space seen by the program need not be the physical address space used. Second Generation Computer OS RSTS OS on PDP-11 General Purpose, time sharing, Multiuser OS. Paged Memory management. 6

History (cont’d) Third Generation Computer OS VMS (Virtual Management System) on VAX (Virtual Address Extension) Demand paged virtual memory. Modern Age Computer OS SMP, Clustering. Open. VMS 7

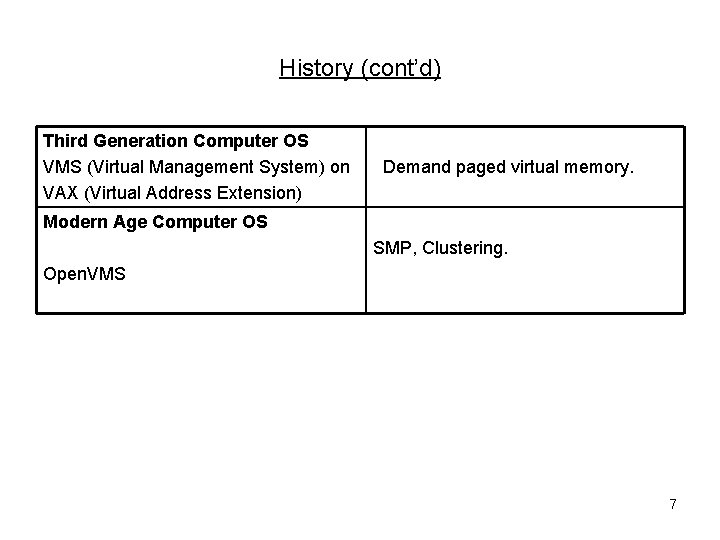

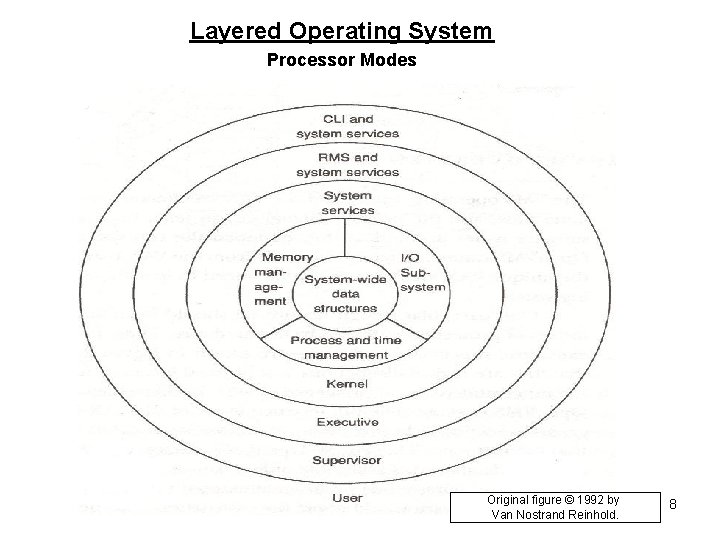

Layered Operating System Processor Modes Original figure © 1992 by Van Nostrand Reinhold. 8

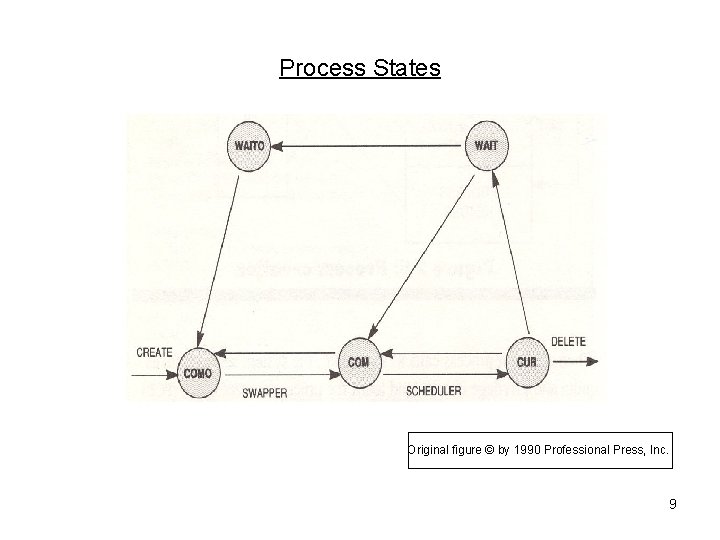

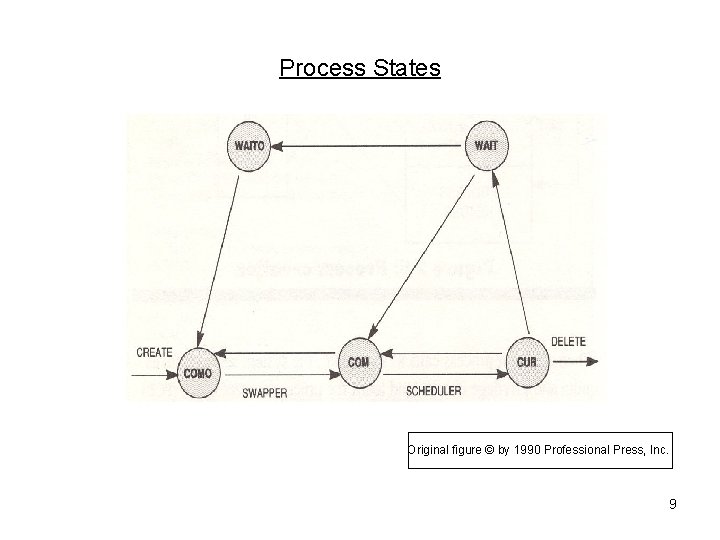

Process States Original figure © by 1990 Professional Press, Inc. 9

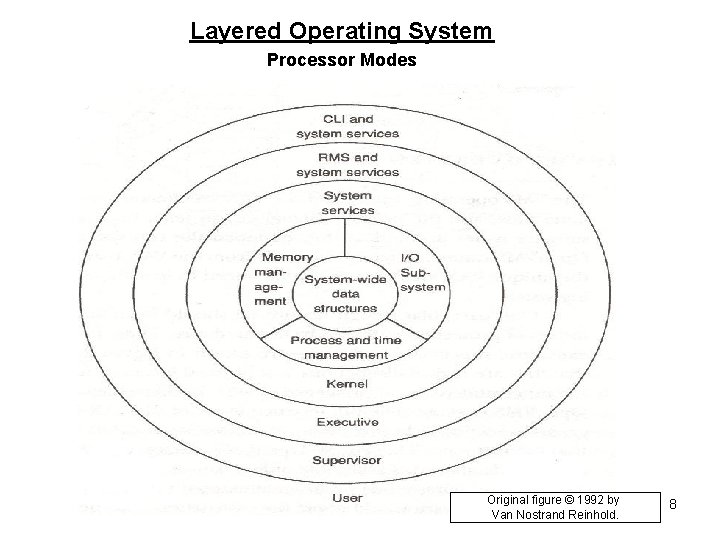

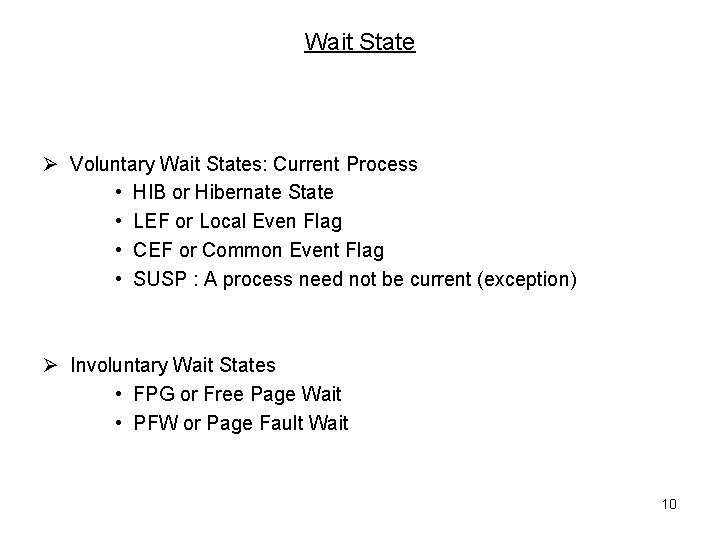

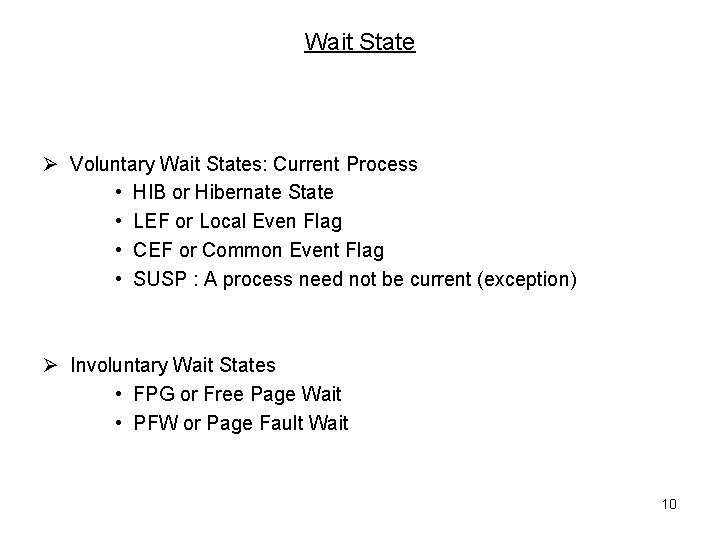

Wait State Ø Voluntary Wait States: Current Process • HIB or Hibernate State • LEF or Local Even Flag • CEF or Common Event Flag • SUSP : A process need not be current (exception) Ø Involuntary Wait States • FPG or Free Page Wait • PFW or Page Fault Wait 10

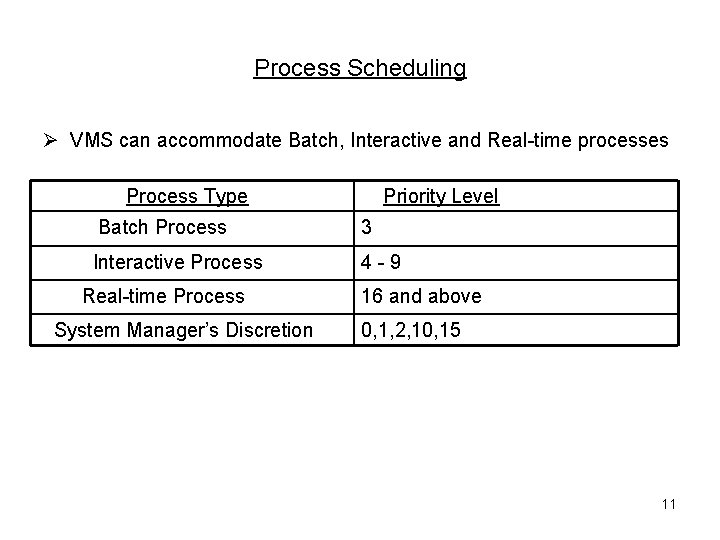

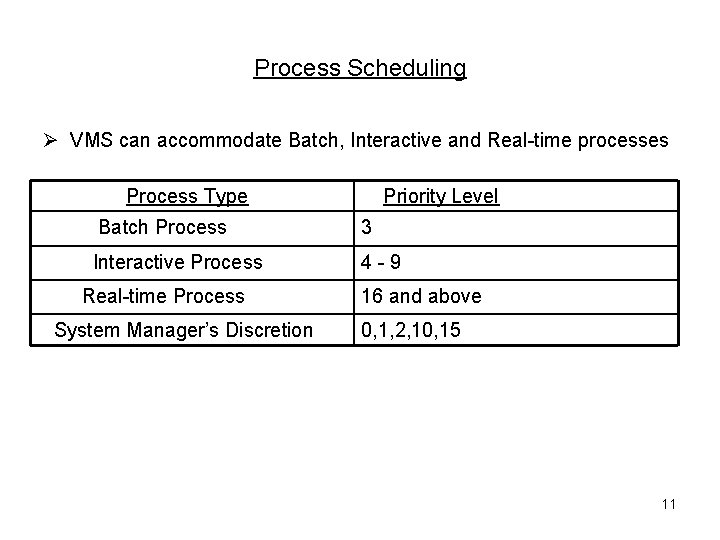

Process Scheduling Ø VMS can accommodate Batch, Interactive and Real-time processes Process Type Priority Level Batch Process 3 Interactive Process 4 -9 Real-time Process System Manager’s Discretion 16 and above 0, 1, 2, 10, 15 11

Process Scheduling (cont’d) Ø VMS scheduling is preemptive based on the priority Ø First-Come-First-Out (FIFO): Batch processes or processes with similar priority, Free list, Modified list Ø Round Robin: Employed by Short-term Scheduler Ø Shortest Job First (SJF): Print queue Ø Shortest Remaining Time (SRT): variation of SJF Ø Aging 12

Process Scheduling (cont’d) Scheduler is invoked under these circumstances. • System Event Occurs: Short-term Scheduler or Medium-term Scheduler • Quantum expires: Short-term Scheduler • Perform wait service: Short-term or Medium-term Scheduler 13

Memory Management Ø Demand paged virtual memory system: Mitigates shortcomings of partitioned memory Ø Process has a virtual address on creation Ø Process and Physical Memory divided into pages of 512 bytes in size. Ø Mapping : Virtual address translated to physical address Ø Translation-not-valid Exception Ø Principle of Locality – Active pages Ø Working set (Resident Set): set of active pages, LRU algorithm with reference bit, size varies 14

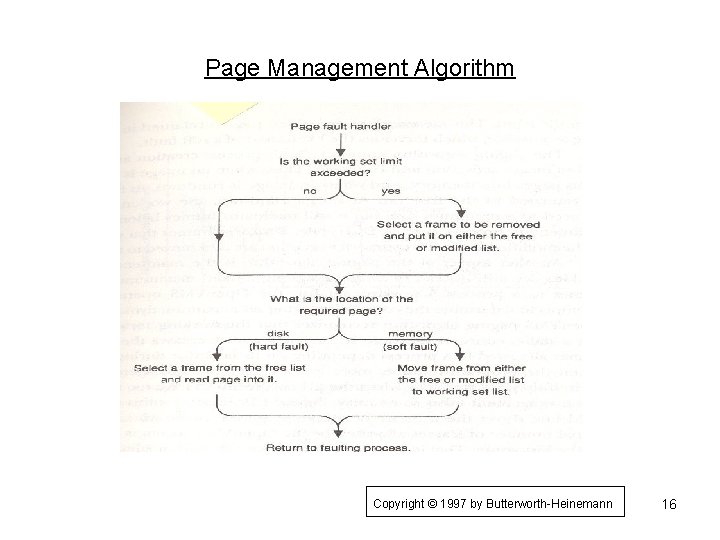

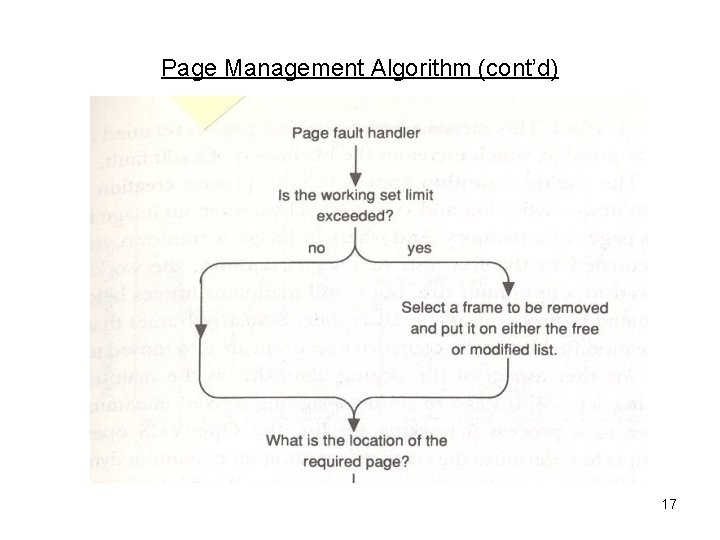

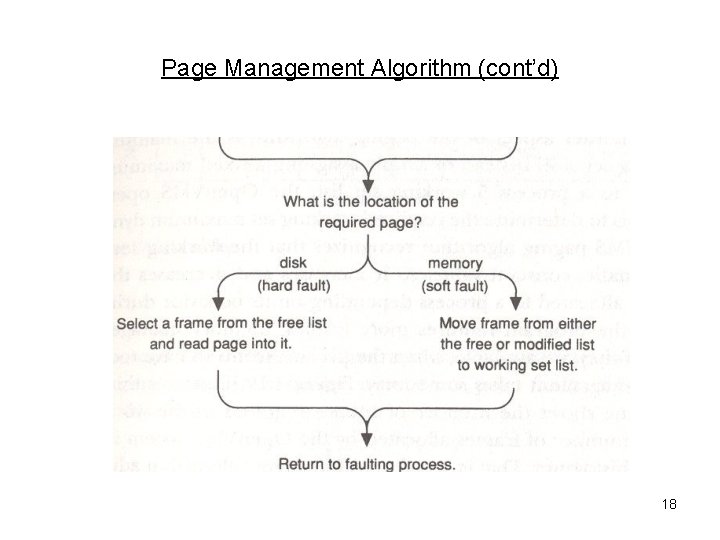

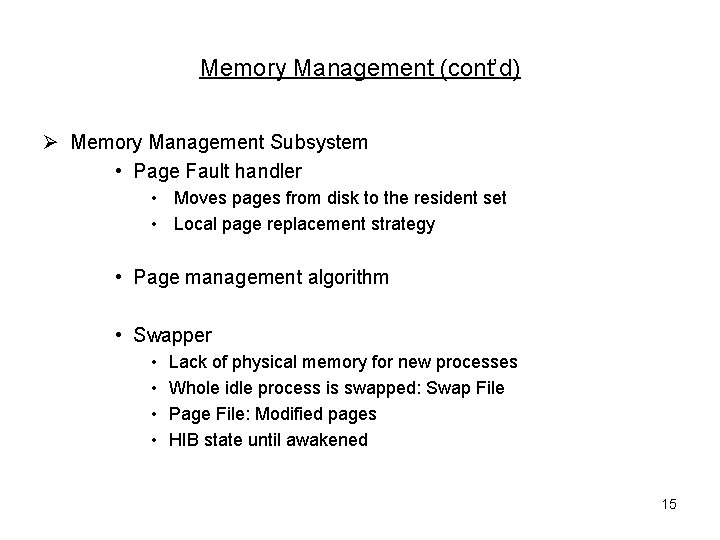

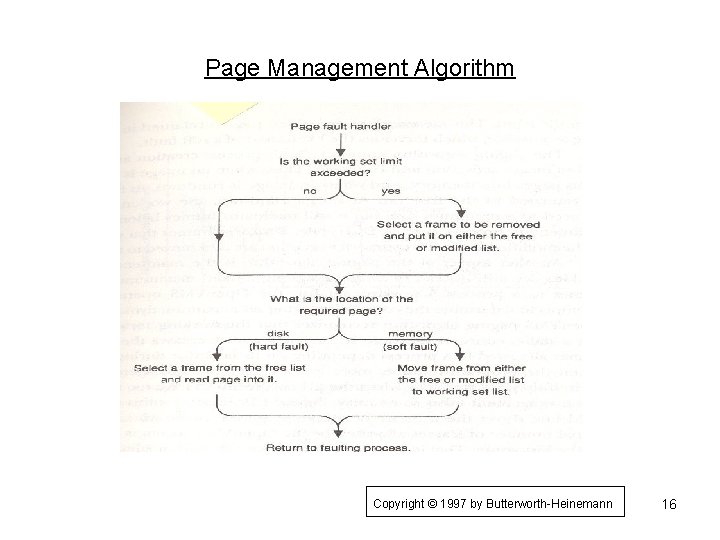

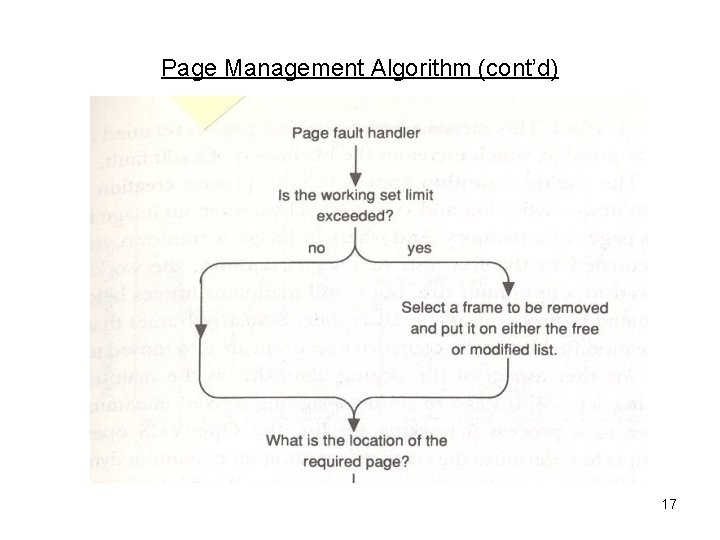

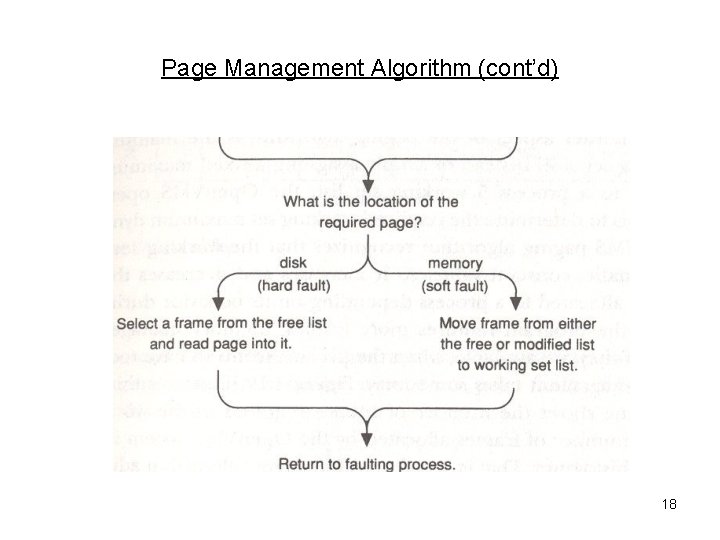

Memory Management (cont’d) Ø Memory Management Subsystem • Page Fault handler • Moves pages from disk to the resident set • Local page replacement strategy • Page management algorithm • Swapper • • Lack of physical memory for new processes Whole idle process is swapped: Swap File Page File: Modified pages HIB state until awakened 15

Page Management Algorithm Copyright © 1997 by Butterworth-Heinemann 16

Page Management Algorithm (cont’d) 17

Page Management Algorithm (cont’d) 18

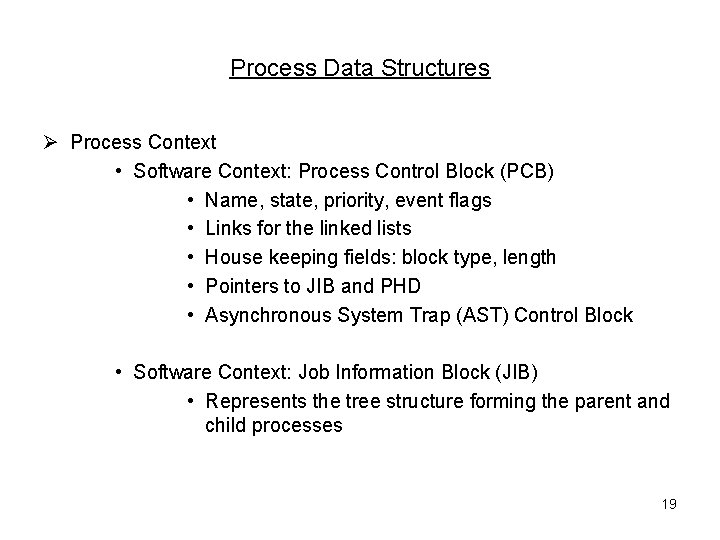

Process Data Structures Ø Process Context • Software Context: Process Control Block (PCB) • Name, state, priority, event flags • Links for the linked lists • House keeping fields: block type, length • Pointers to JIB and PHD • Asynchronous System Trap (AST) Control Block • Software Context: Job Information Block (JIB) • Represents the tree structure forming the parent and child processes 19

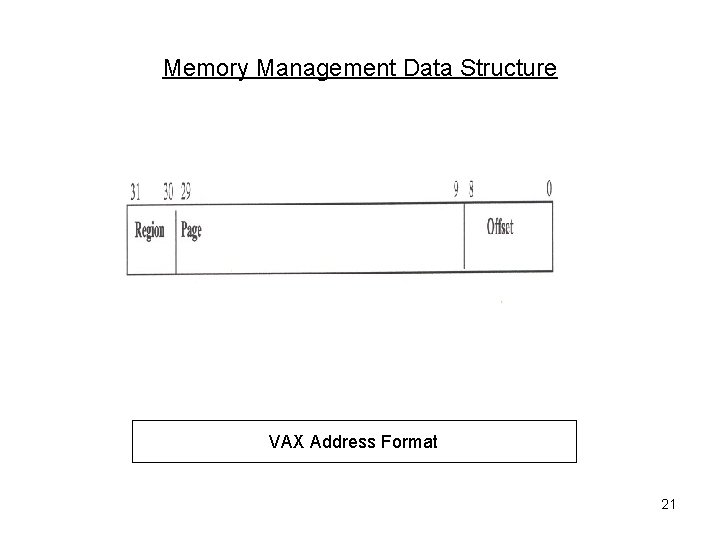

Process Data Structures (Cont’d) Ø Hardware Context: Process Header (PHD): includes hardware PCB • Resident set of processes • P 0 and P 1 page tables • Hardware PCB: stacks, registers, base and length registers Ø Virtual address space: S 0, P 1 regions 20

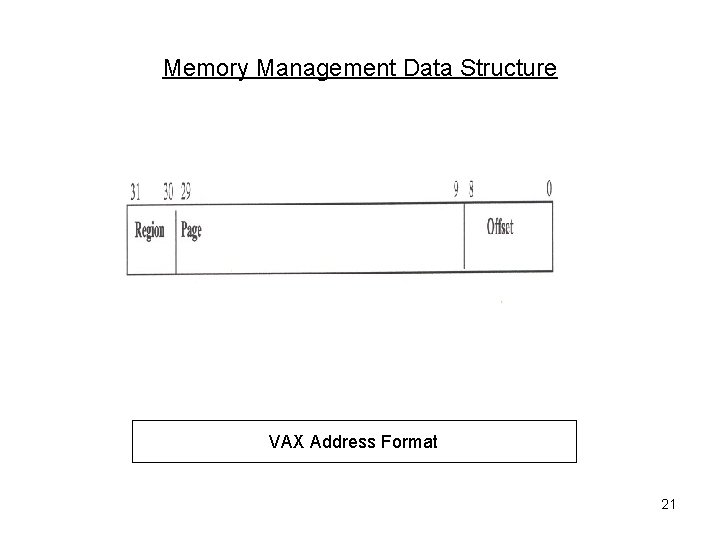

Memory Management Data Structure VAX Address Format 21

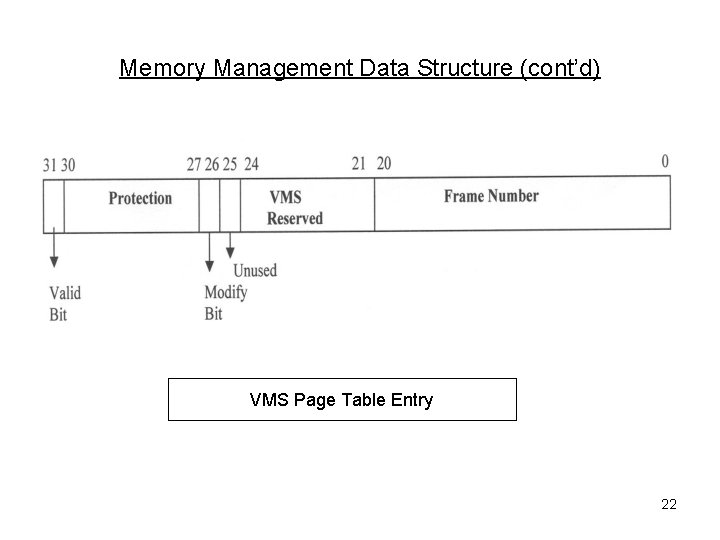

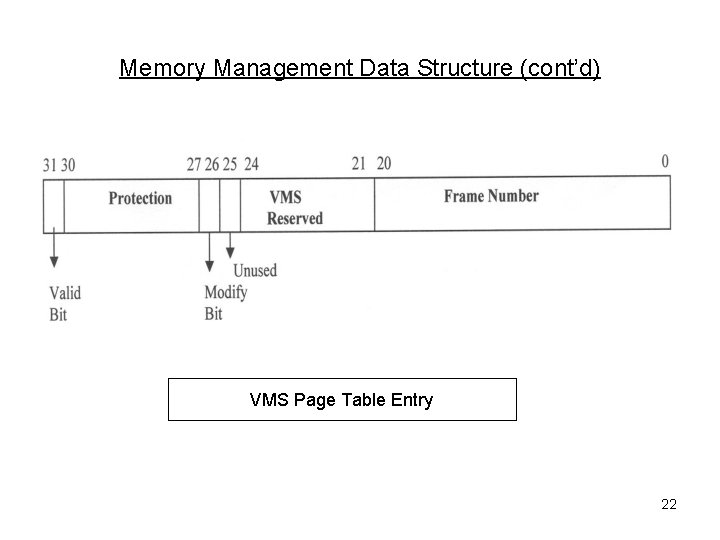

Memory Management Data Structure (cont’d) VMS Page Table Entry 22

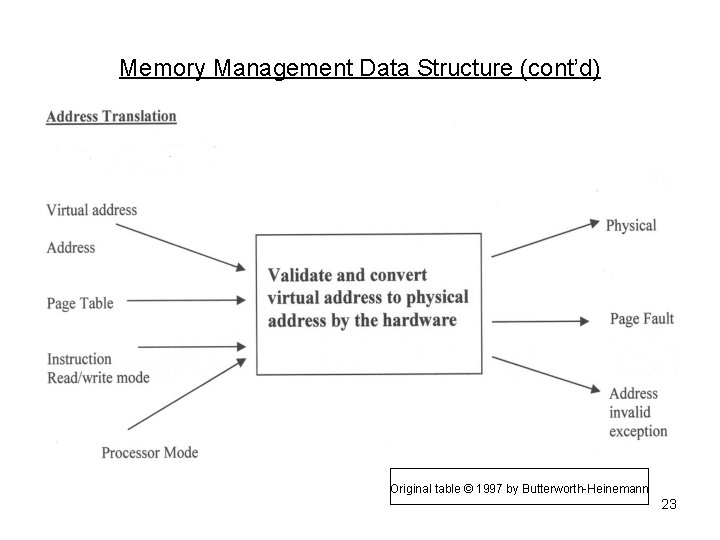

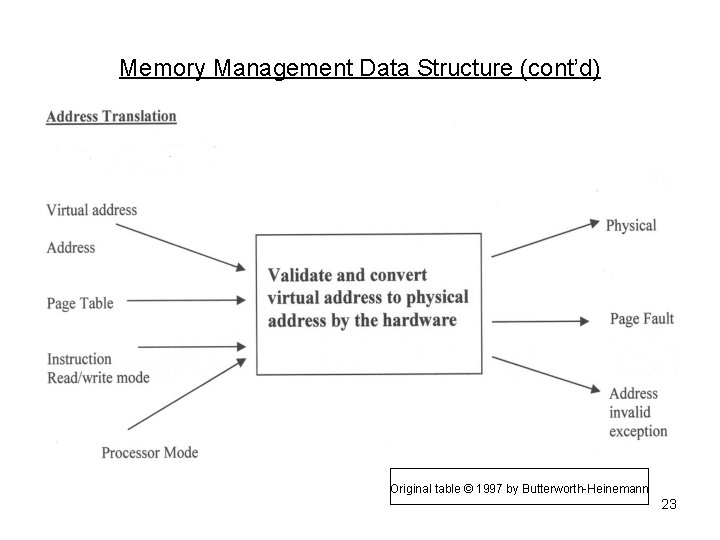

Memory Management Data Structure (cont’d) Original table © 1997 by Butterworth-Heinemann 23

Process Synchronization Ø Synchronization between two processes • Hibernate – Wake: System services • Event Flag: Set Event Flag, Clear Event Flag, Wait For Event Flag • Mailbox: I/O between processes Ø Mutual Exclusion of Critical Region • Lock and Unlock system service: Semaphore 24

VMS: Advantages and Disadvantages o Advantages • ‘One architecture, one operating system’ • VAX implementation of peer-to-peer relationship o Disadvantages • Totally a CISC architecture and prominence of RISC architecture • VAX assembly language • Flaw in the implementation of IPL • Poor management of the problem of critical selection 25

VMS: Advantages and Disadvantages (Cont’d) o Future… • Open. VMS • DEC Alpha • HP’s systems with Intel’s new 1. 5 GHz Itanium 2 chips: rx 4640, rx 7620, rx 8620 26