Memory Hierarchy memory hierarchy A memory hierarchy consists

- Slides: 20

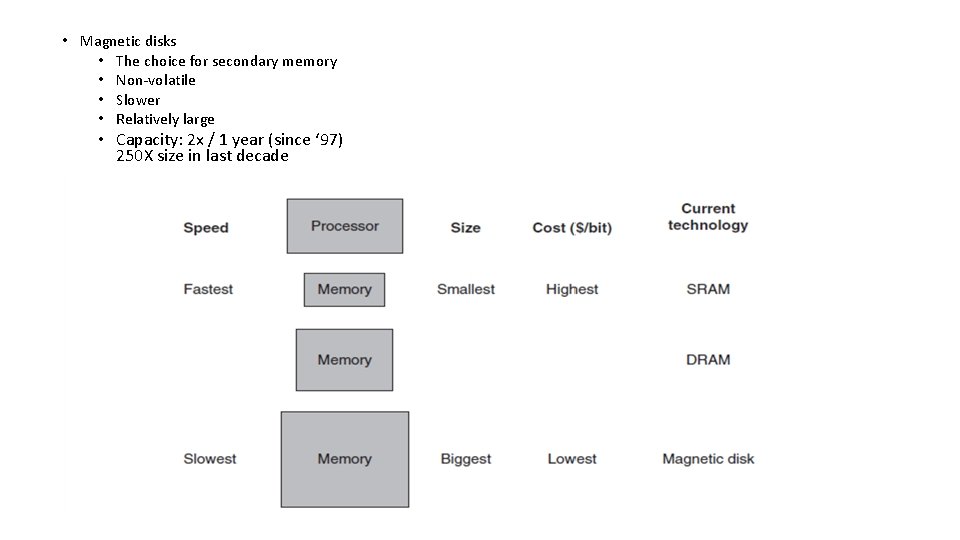

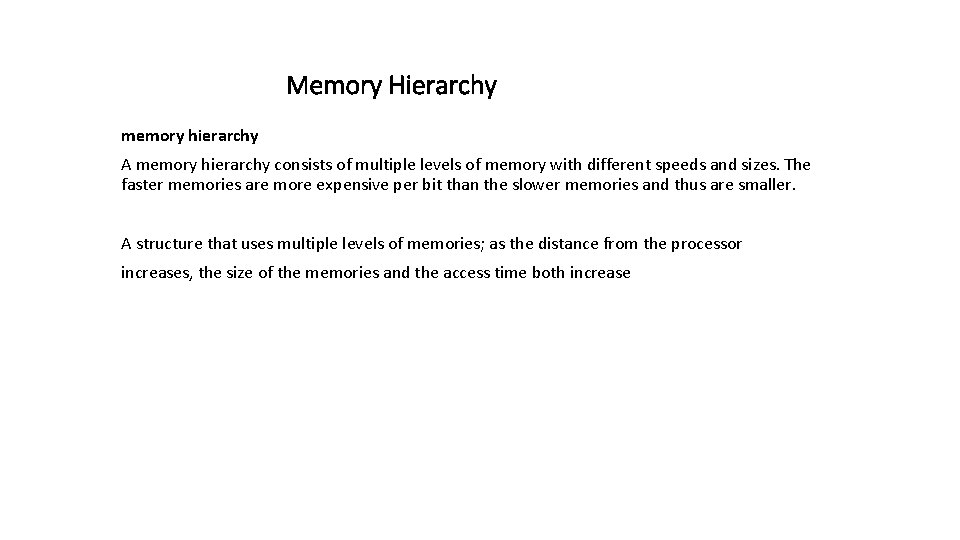

Memory Hierarchy memory hierarchy A memory hierarchy consists of multiple levels of memory with different speeds and sizes. The faster memories are more expensive per bit than the slower memories and thus are smaller. A structure that uses multiple levels of memories; as the distance from the processor increases, the size of the memories and the access time both increase

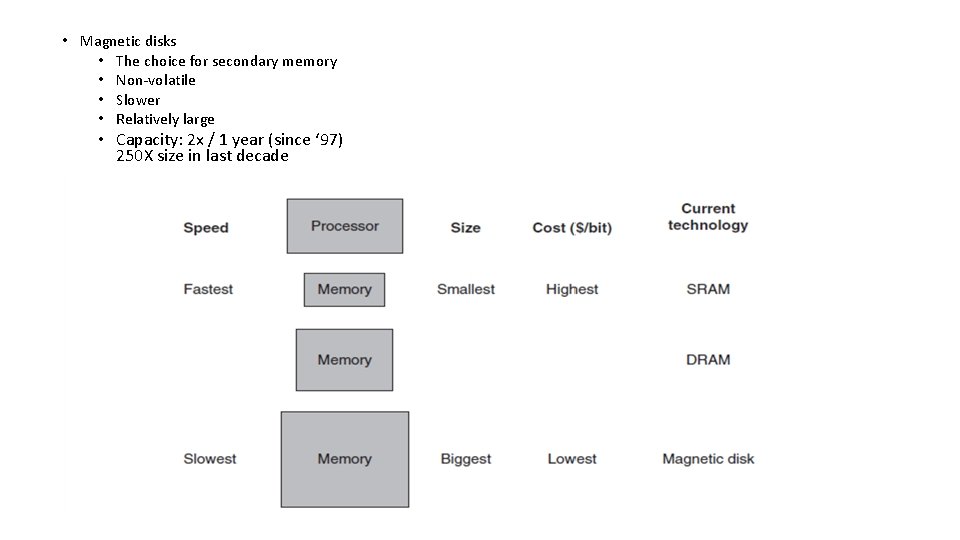

• Magnetic disks • The choice for secondary memory • Non-volatile • Slower • Relatively large • Capacity: 2 x / 1 year (since ‘ 97) 250 X size in last decade

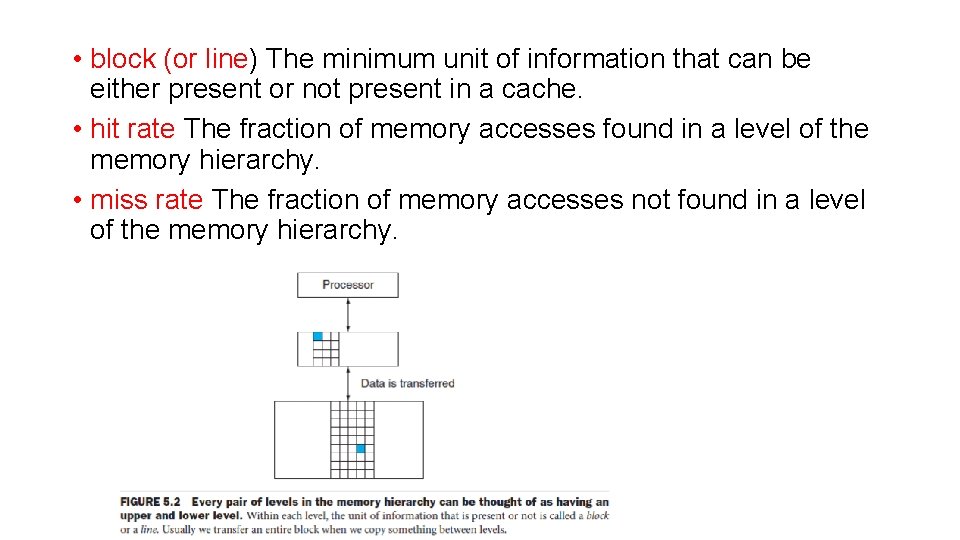

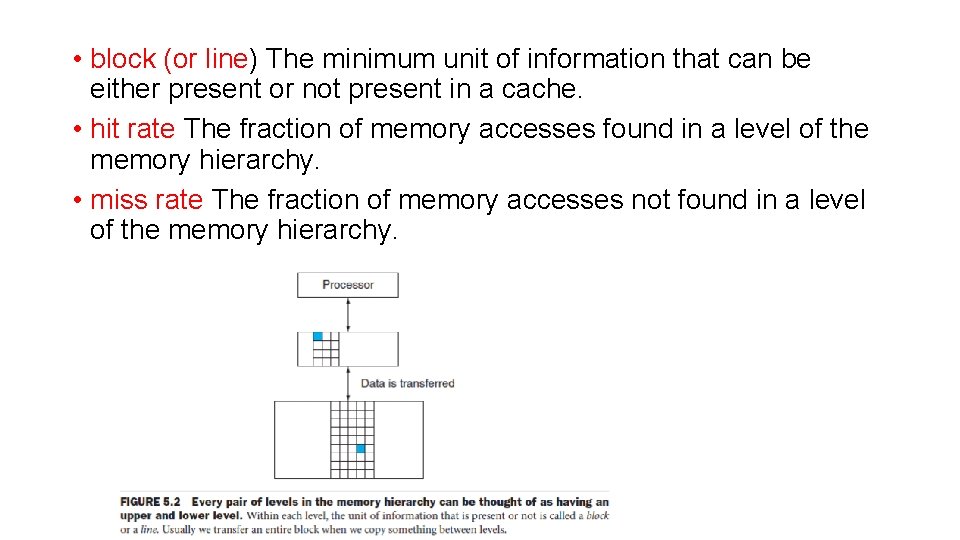

• block (or line) The minimum unit of information that can be either present or not present in a cache. • hit rate The fraction of memory accesses found in a level of the memory hierarchy. • miss rate The fraction of memory accesses not found in a level of the memory hierarchy.

• Hit time is the time to access the upper level • of the memory hierarchy, which includes the time needed to determine whether • the access is a hit or a miss (that is, the time needed to look through the books on the desk). • The miss penalty is the time to replace a block in the upper level with the corresponding block from the lower level, plus the time to deliver this block to the processor

The Basics of Caches • Cache: a safe place for hiding or storing things. • Cache memory is a small-sized type of volatile computer memory that provides high-speed data access to a processor and stores frequently used computer programs, applications and data. It stores and retains data only until a computer is powered up.

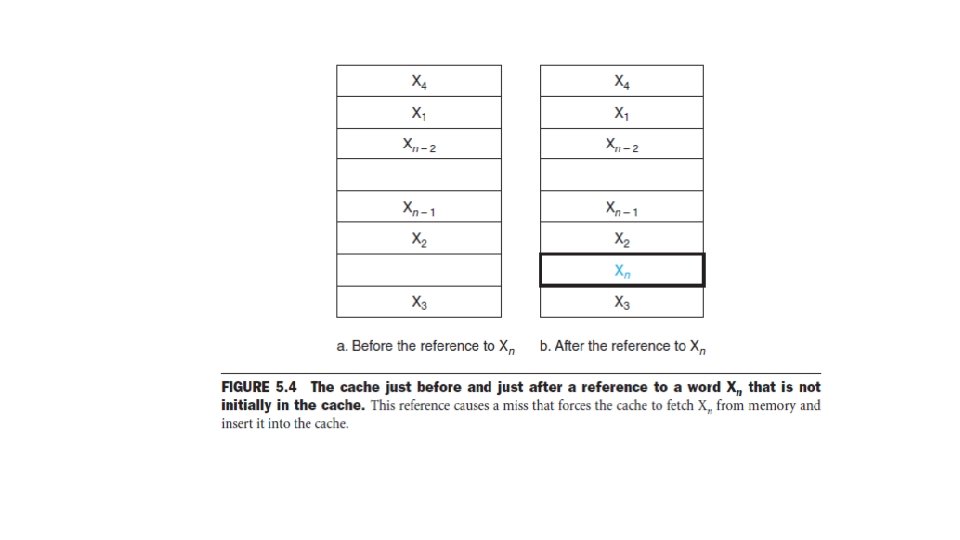

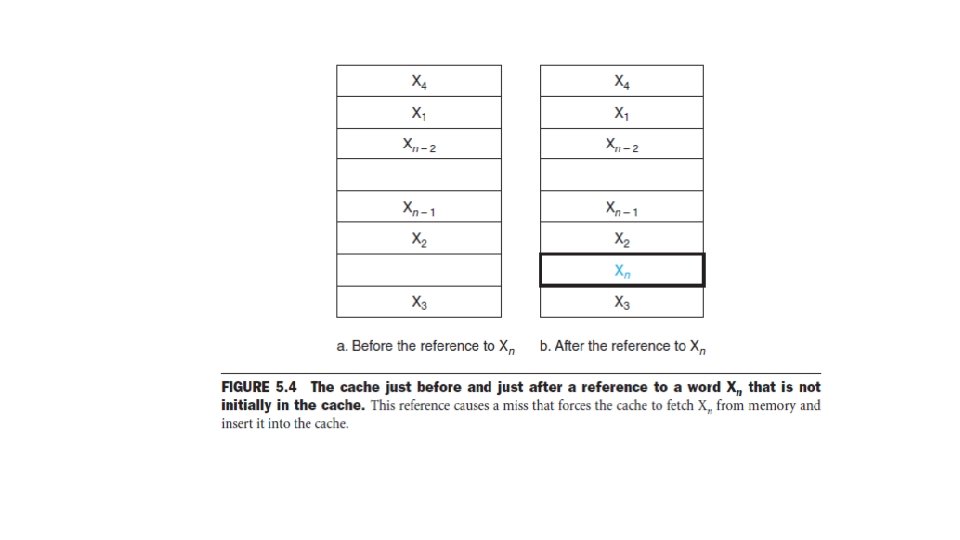

• How do we know if a data item is in the cache? Moreover, if it is, how do we find it? • If each word can go in exactly one place in the cache, then it is • straightforward to find the word if it is in the cache. • The simplest way to assign a location in the cache for each word in memory is to assign the cache location based on the address of the word in memory. This cache structure is called direct mapped,

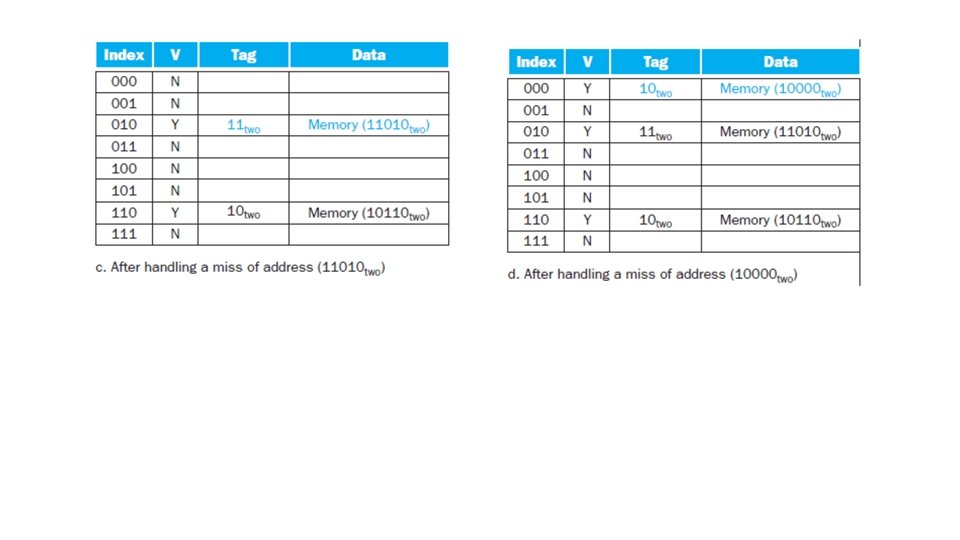

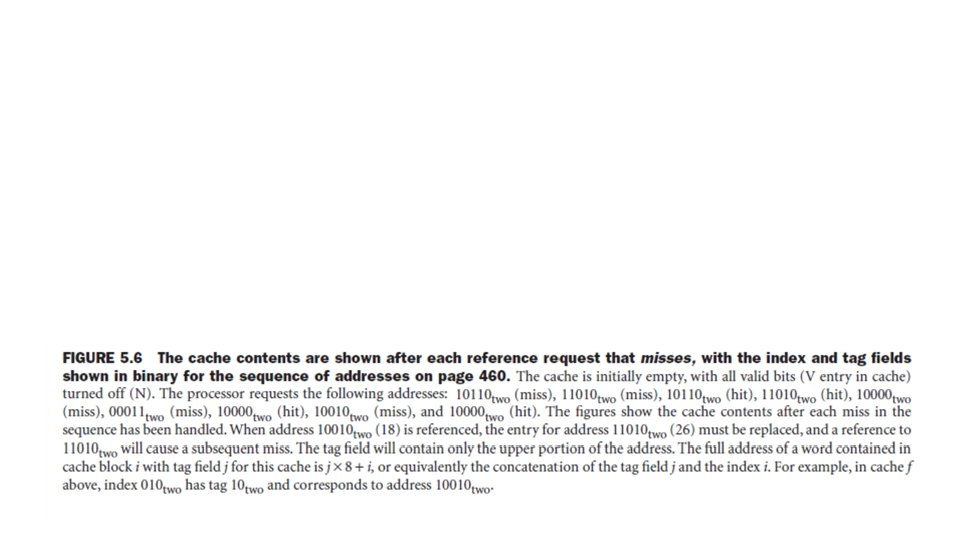

Direct Mapping Technique: The simplest way of associating main memory blocks with cache block is the direct mapping technique. In this technique, block k of main memory maps into block k modulo m of the cache, where m is the total number of blocks in cache. • If the number of entries in the cache is a power of 2, then modulo can be computed • simply by using the low-order log 2 (cache size in blocks) bits of the address. • Thus, an 8 -block cache uses the three lowest bits (8 = 23) of the block address. In this example, the value of m is 8. In direct mapping technique, one particular block of main memory can be transferred to a particular block of cache which is derived by the modulo function. Since more than one main memory block is mapped onto a given cache block position, contention may arise for that position. This situation may occurs even when the cache is not full. Contention is resolved by allowing the new block to overwrite the currently resident block. So the replacement algorithm is trivial.

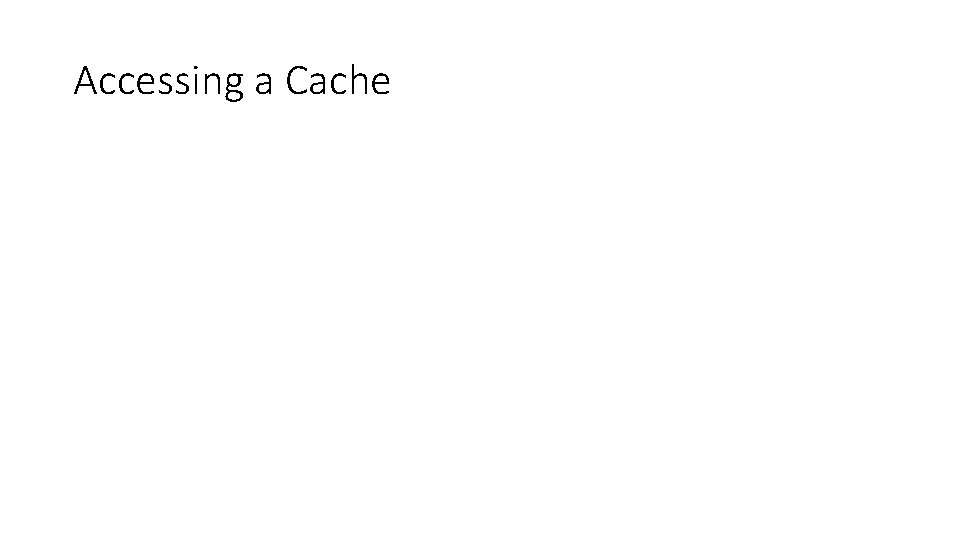

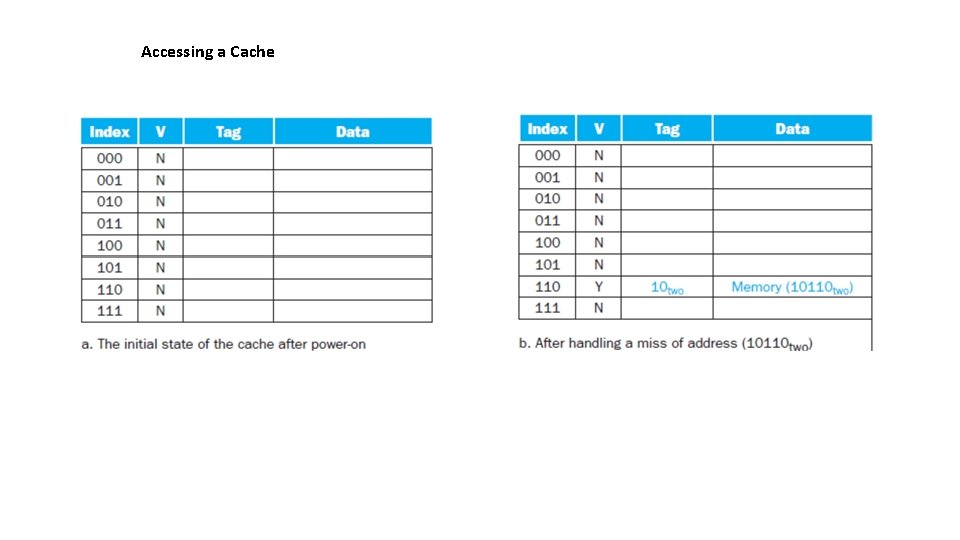

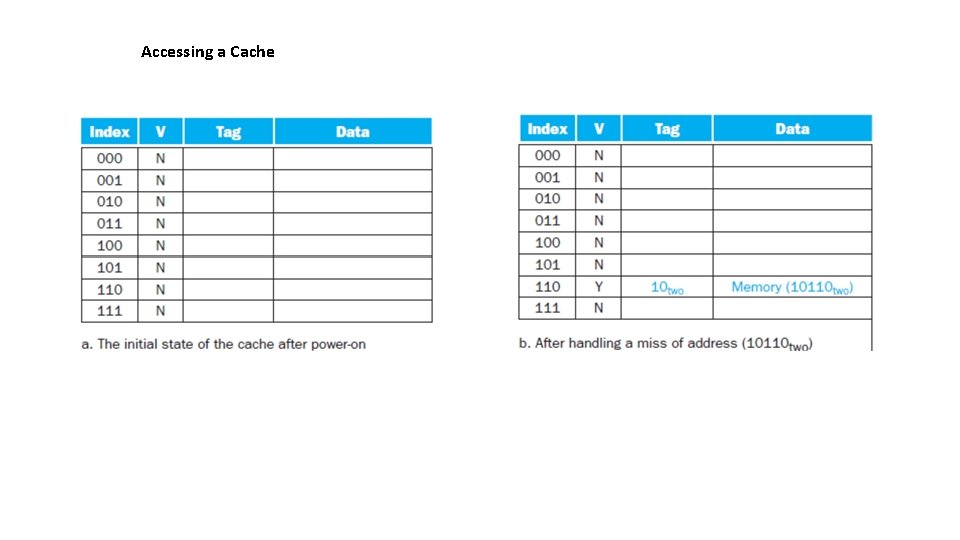

Accessing a Cache

Accessing a Cache

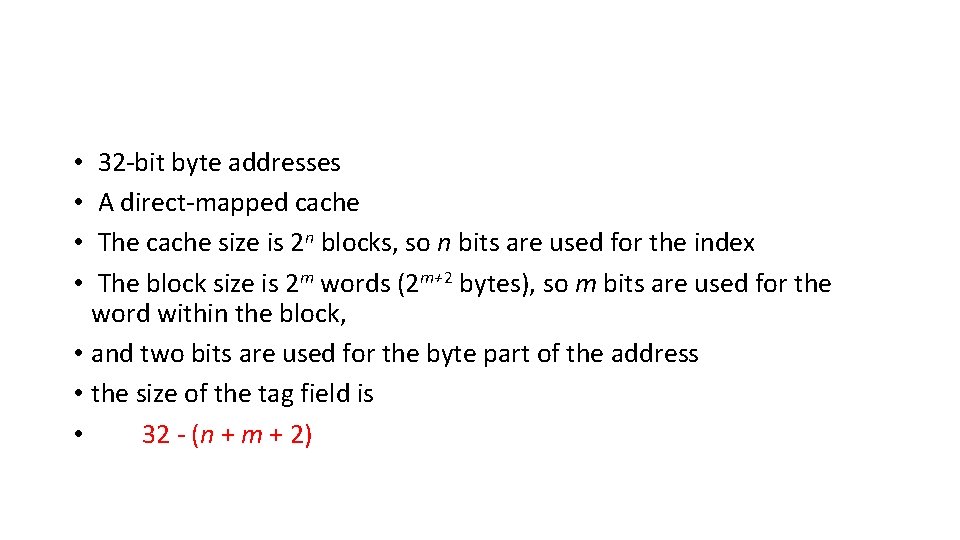

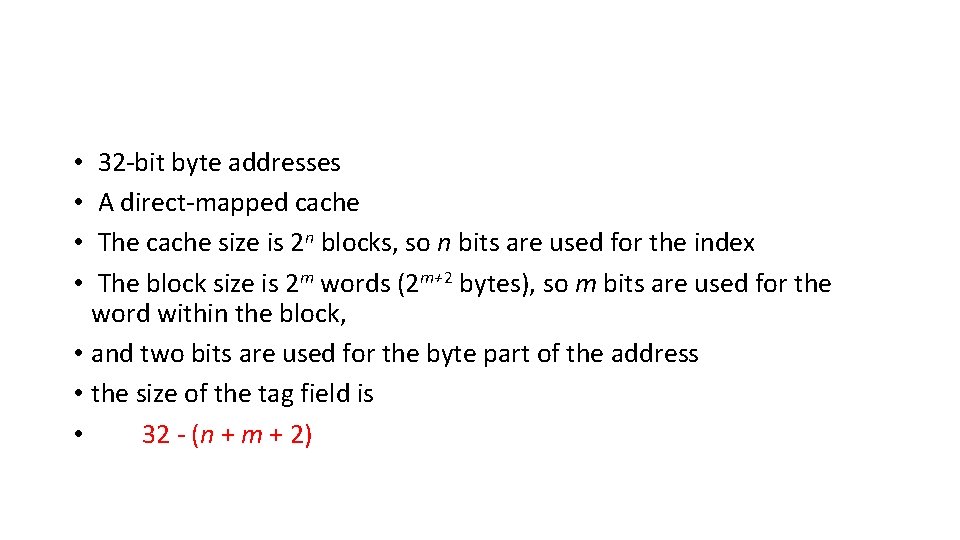

32 -bit byte addresses A direct-mapped cache The cache size is 2 n blocks, so n bits are used for the index The block size is 2 m words (2 m+2 bytes), so m bits are used for the word within the block, • and two bits are used for the byte part of the address • the size of the tag field is • 32 - (n + m + 2) • •

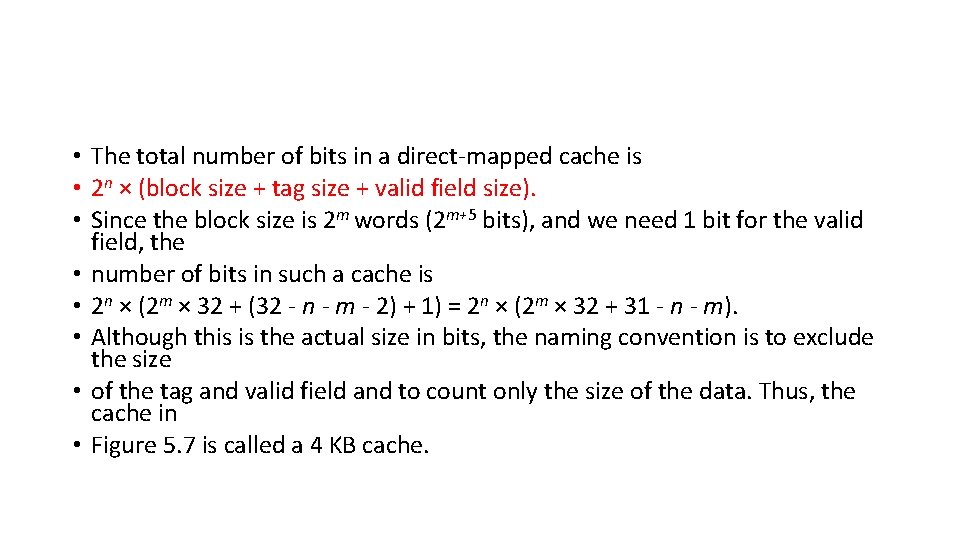

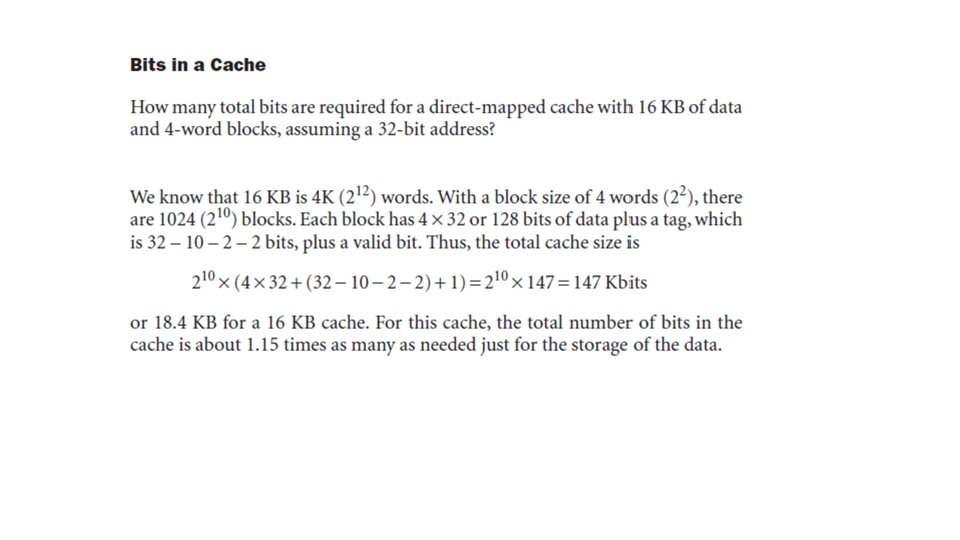

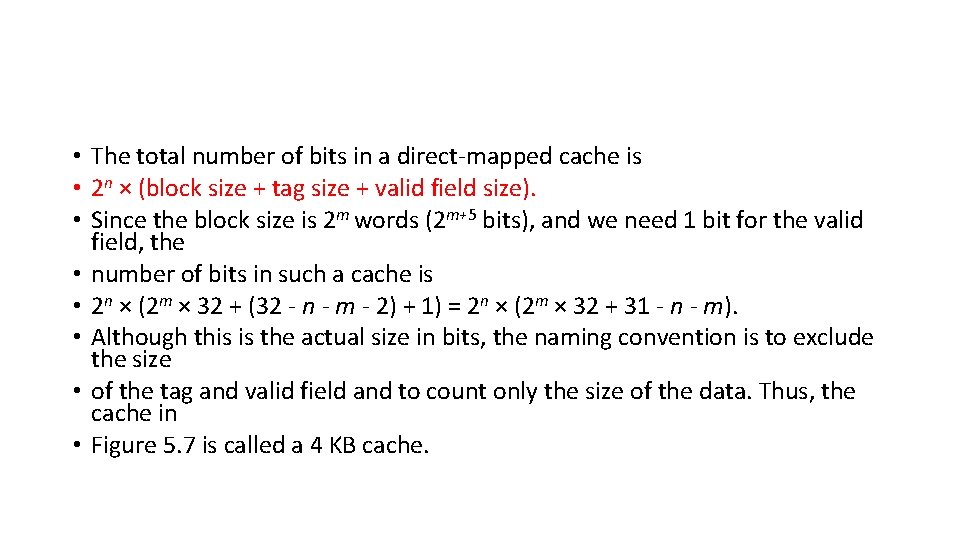

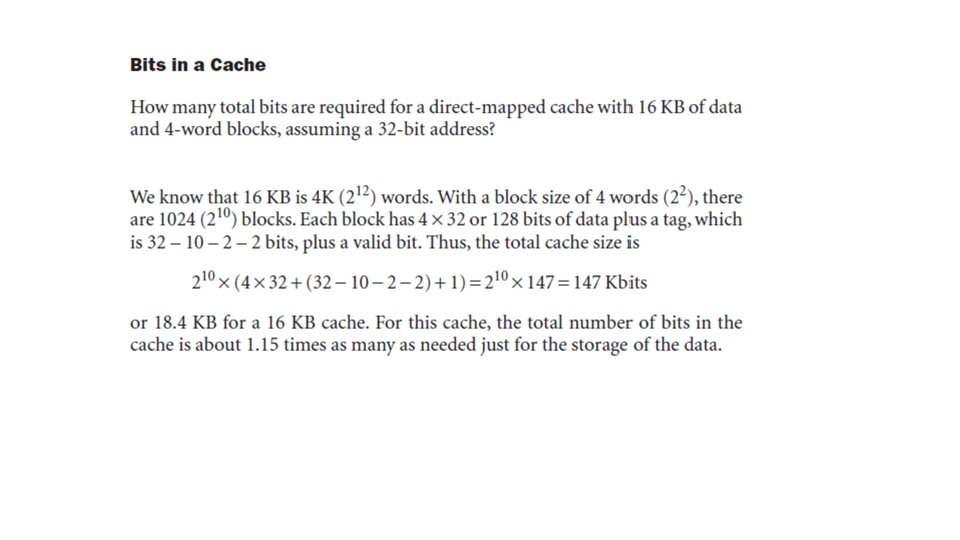

• The total number of bits in a direct-mapped cache is • 2 n × (block size + tag size + valid field size). • Since the block size is 2 m words (2 m+5 bits), and we need 1 bit for the valid field, the • number of bits in such a cache is • 2 n × (2 m × 32 + (32 - n - m - 2) + 1) = 2 n × (2 m × 32 + 31 - n - m). • Although this is the actual size in bits, the naming convention is to exclude the size • of the tag and valid field and to count only the size of the data. Thus, the cache in • Figure 5. 7 is called a 4 KB cache.

• Mapping an Address to a Multiword Cache Block • Consider a cache with 64 blocks and a block size of 16 bytes. To what blocknumber does byte address 1200 map? • . The block is given by • (Block address) modulo (Number of blocks in the cache)

• where the address of the block is