Chapter 6 Memory Linda Null Julia Lobur Figure

Chapter 6 Memory Linda Null, Julia Lobur

Figure 06. UN 01: "RAM/abr. /: Rarely Adequate Memory. because the more memory a computer has, the faster it can produce error messages. " - Anonymous

![Figure 06. UN 02: "640 k [of memory] ought to be enough for anybody. Figure 06. UN 02: "640 k [of memory] ought to be enough for anybody.](http://slidetodoc.com/presentation_image/0143b8b1a037af98a431c95182495eb1/image-3.jpg)

Figure 06. UN 02: "640 k [of memory] ought to be enough for anybody. " - Anonymous CREDIT UPDATE NEEDED: Anonymous

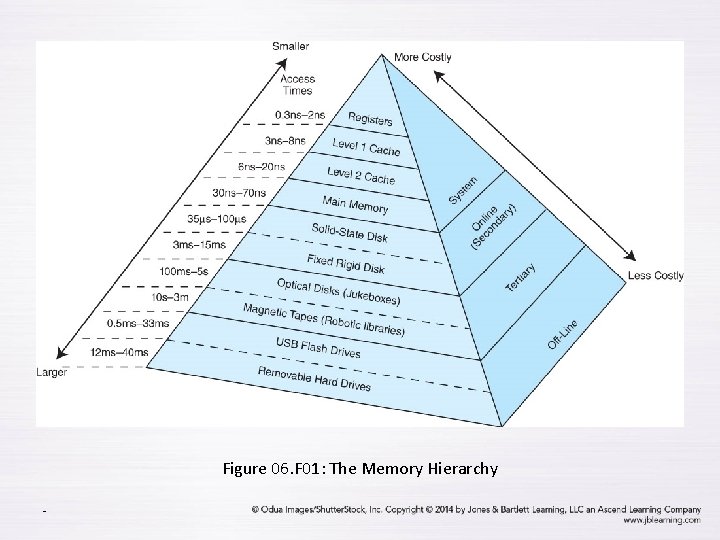

Figure 06. F 01: The Memory Hierarchy -

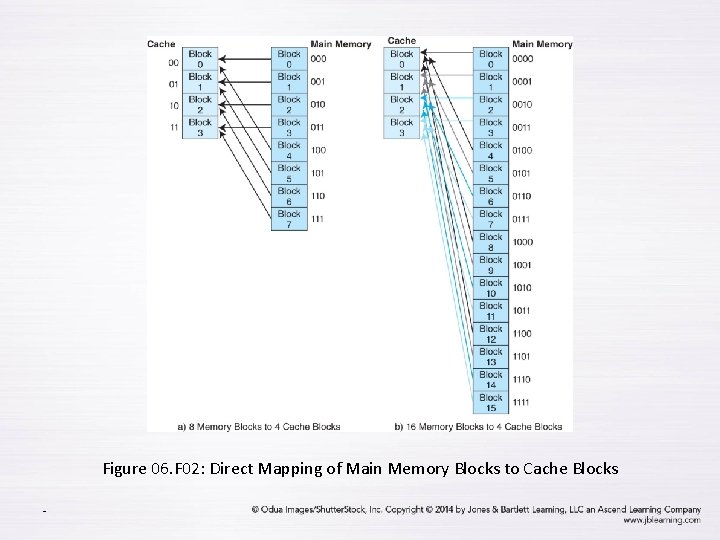

Figure 06. F 02: Direct Mapping of Main Memory Blocks to Cache Blocks -

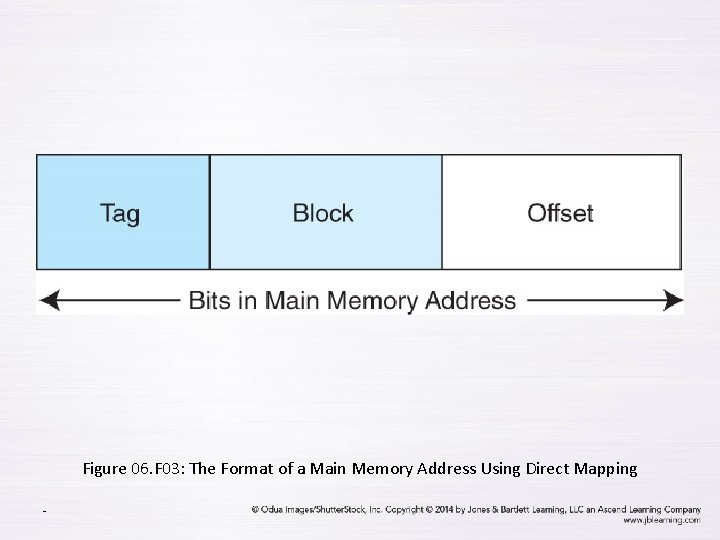

Figure 06. F 03: The Format of a Main Memory Address Using Direct Mapping -

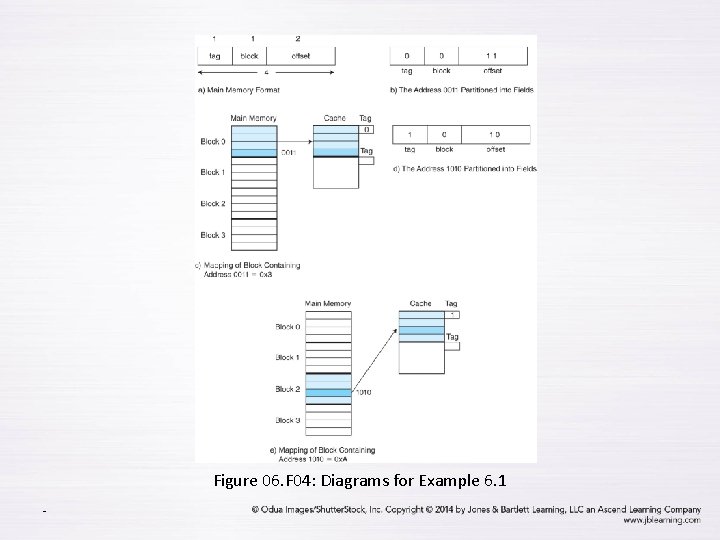

Figure 06. F 04: Diagrams for Example 6. 1 -

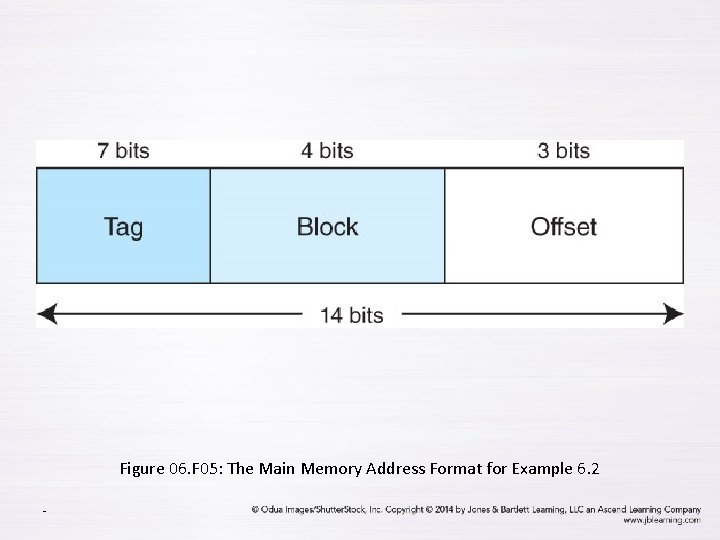

Figure 06. F 05: The Main Memory Address Format for Example 6. 2 -

Figure 06. F 06: The Memory from Example 6. 3 Mapped to Cache -

Figure 06. F 07: The Main Memory Address Format for Example 6. 3 -

Figure 06. F 08: The Main Memory Address 9 = 1001₂ Split into Fields -

Figure 06. F 09: Associative Cache -

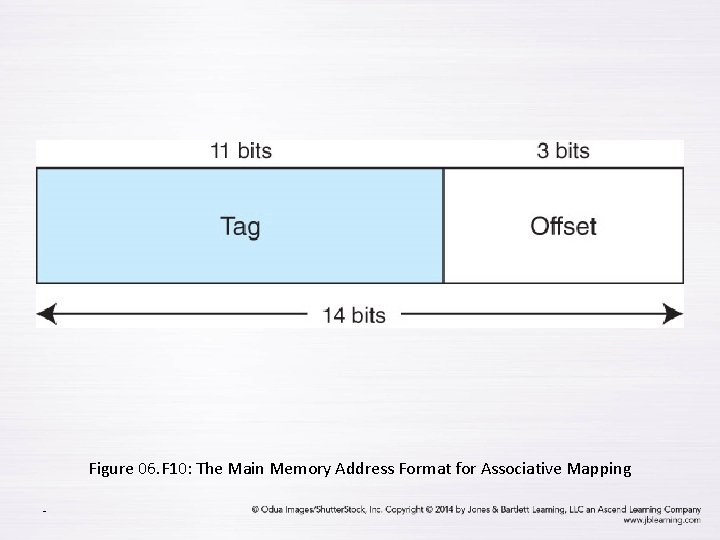

Figure 06. F 10: The Main Memory Address Format for Associative Mapping -

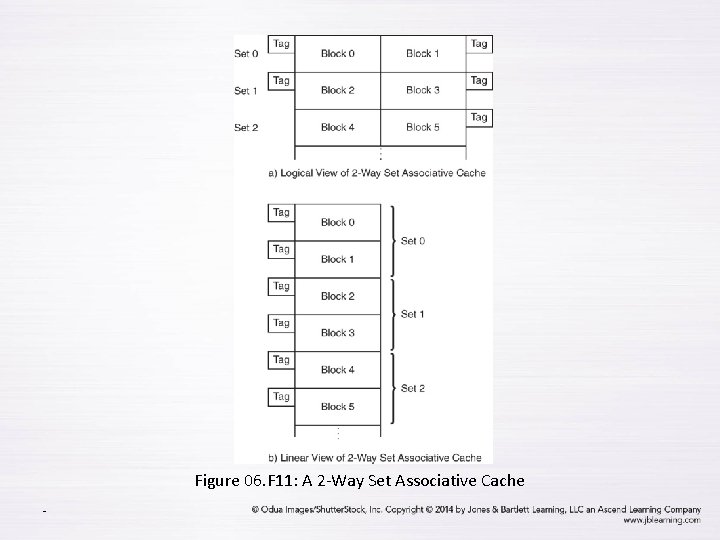

Figure 06. F 11: A 2 -Way Set Associative Cache -

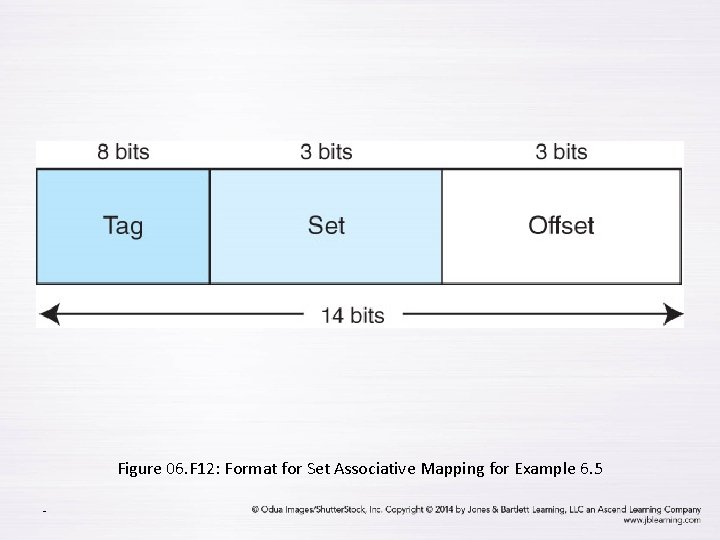

Figure 06. F 12: Format for Set Associative Mapping for Example 6. 5 -

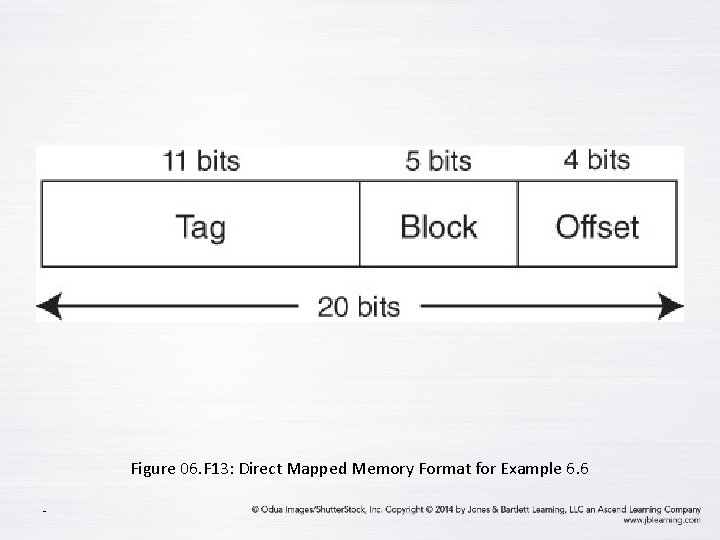

Figure 06. F 13: Direct Mapped Memory Format for Example 6. 6 -

Figure 06. F 14: The Address 0 x 326 A 0 from Example 6. 6 Divided into Fields for Direct Mapping -

Figure 06. F 15: Fully Associative Memory Format for Example 6. 6 -

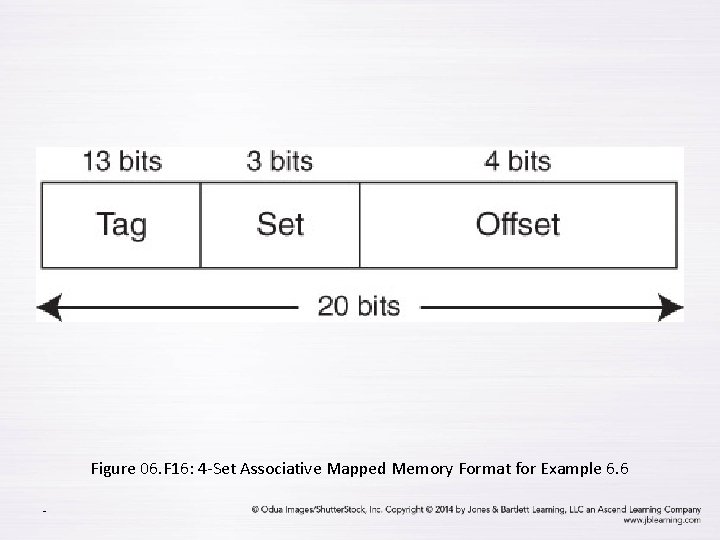

Figure 06. F 16: 4 -Set Associative Mapped Memory Format for Example 6. 6 -

Figure 06. F 17: The Address 0 x 326 A 0 from Example 6. 6 Divided into Fields for Set Associative Mapping -

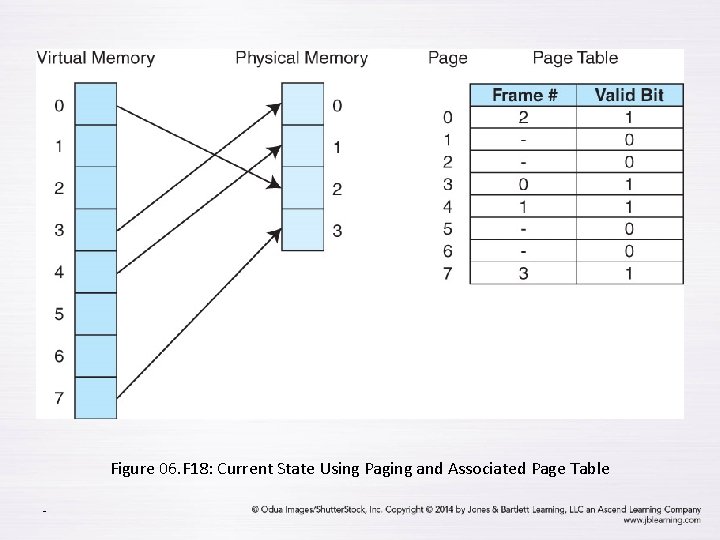

Figure 06. F 18: Current State Using Paging and Associated Page Table -

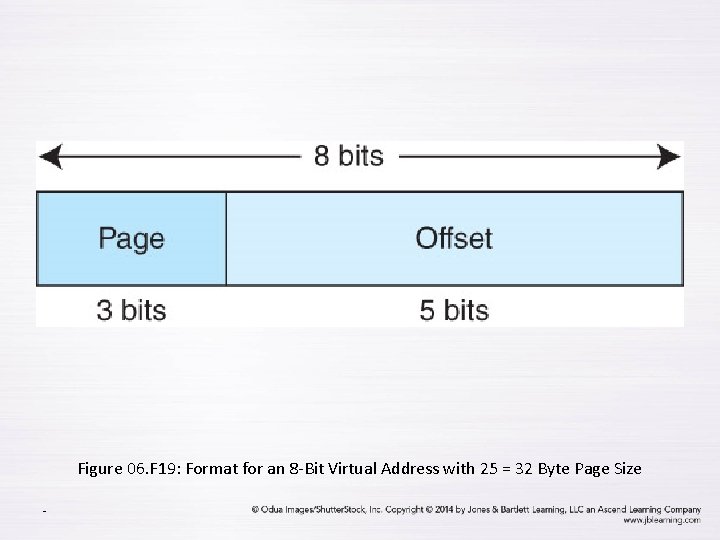

Figure 06. F 19: Format for an 8 -Bit Virtual Address with 25 = 32 Byte Page Size -

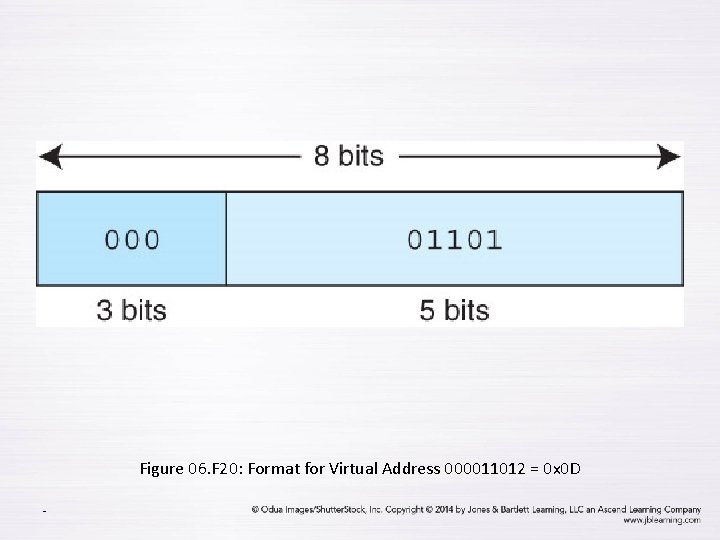

Figure 06. F 20: Format for Virtual Address 000011012 = 0 x 0 D -

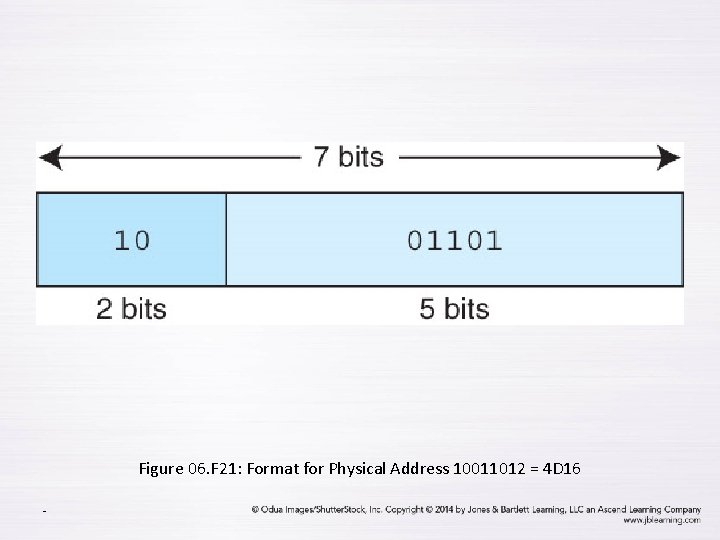

Figure 06. F 21: Format for Physical Address 10011012 = 4 D 16 -

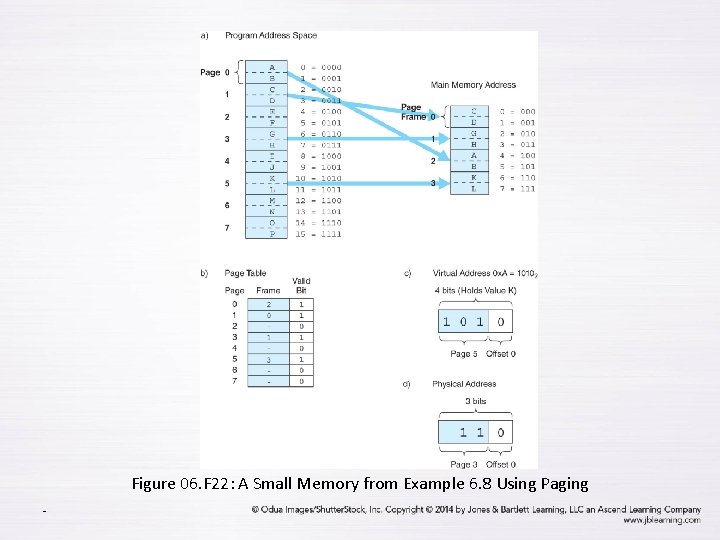

Figure 06. F 22: A Small Memory from Example 6. 8 Using Paging -

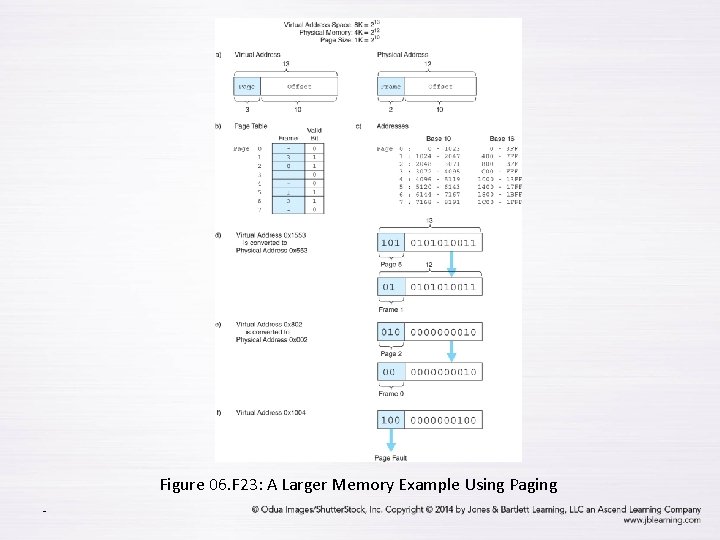

Figure 06. F 23: A Larger Memory Example Using Paging -

Figure 06. F 24: Format for Virtual Address 0 x 1211232 A -

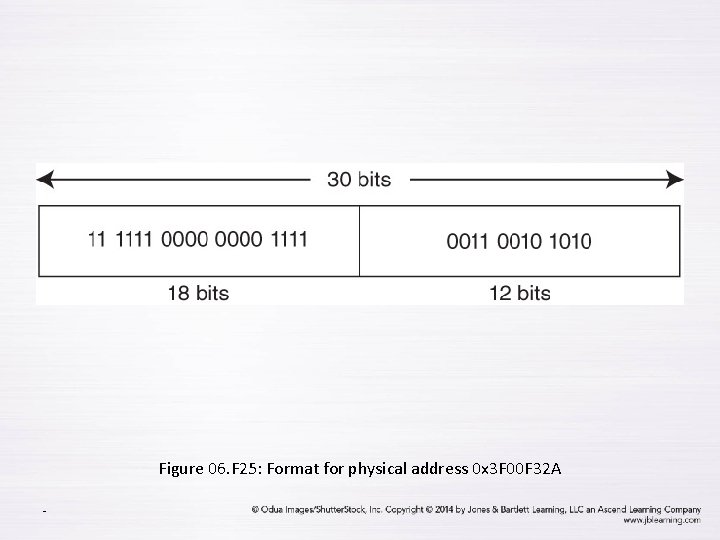

Figure 06. F 25: Format for physical address 0 x 3 F 00 F 32 A -

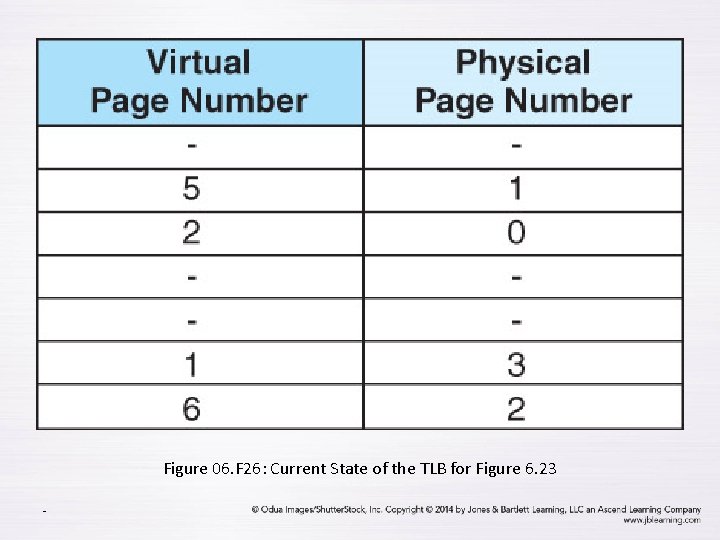

Figure 06. F 26: Current State of the TLB for Figure 6. 23 -

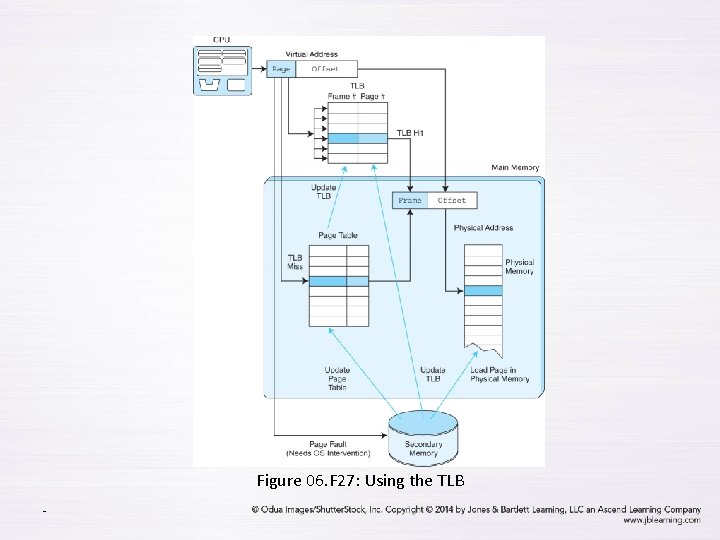

Figure 06. F 27: Using the TLB -

Figure 06. F 28: Putting It All Together: The TLB, Page Table, Cache, and Main Memory -

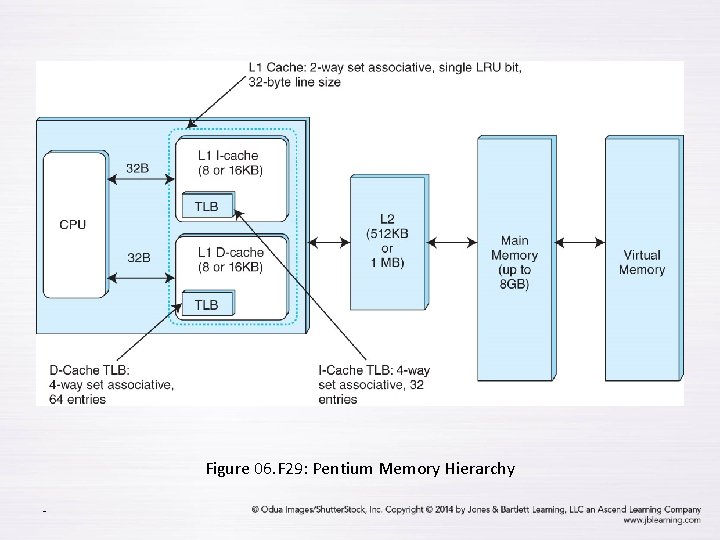

Figure 06. F 29: Pentium Memory Hierarchy -

- Slides: 32