Virtual Caches 4422005 Virtual Caches Virtual Address Virtual

- Slides: 42

Virtual Caches ���� �� ����� 4422005

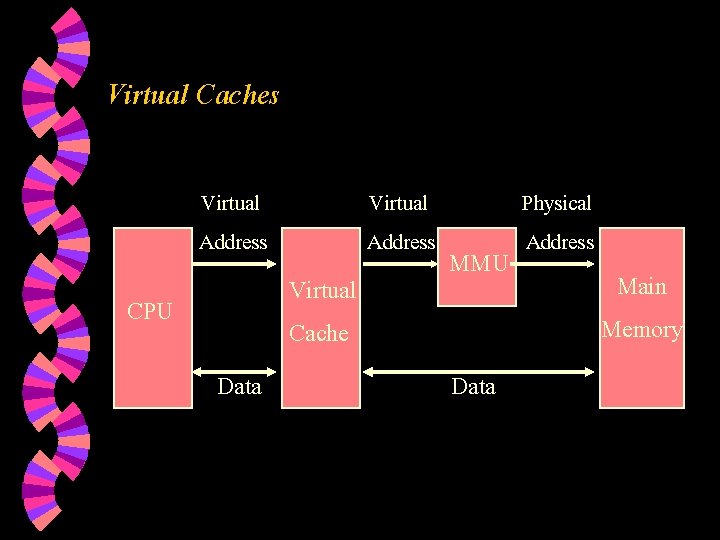

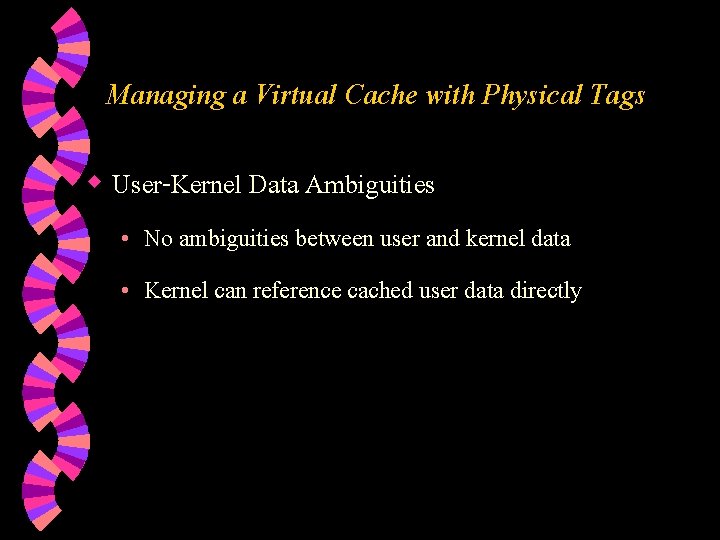

Virtual Caches Virtual Address Virtual Cache CPU Data MMU Data Physical Address Main Memory

Virtual Caches w Problems with Virtual Caches • Ambiguities • Aliases

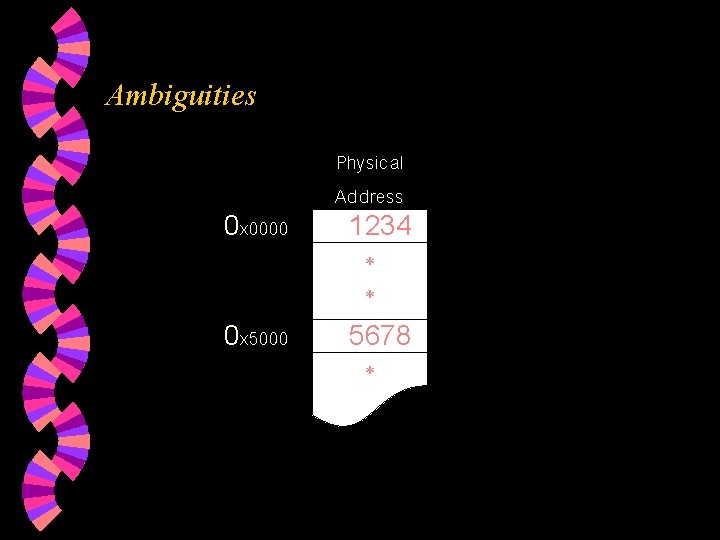

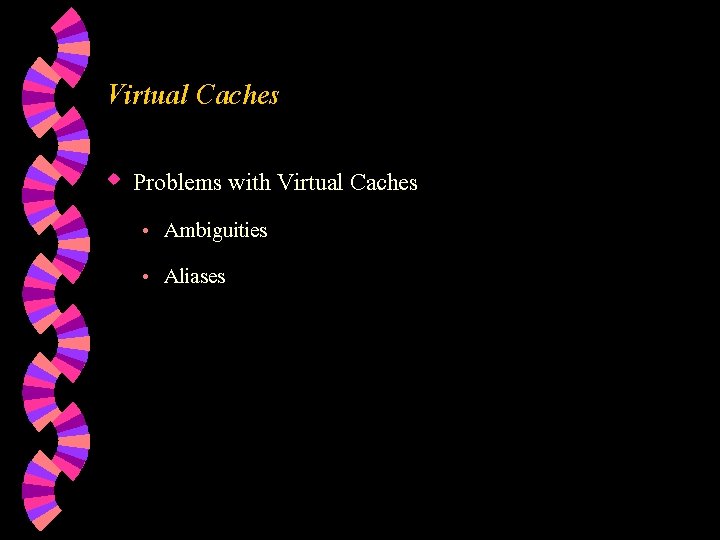

Ambiguities 0 x 0000 0 x 5000 Physical Address 1234 * * 5678 *

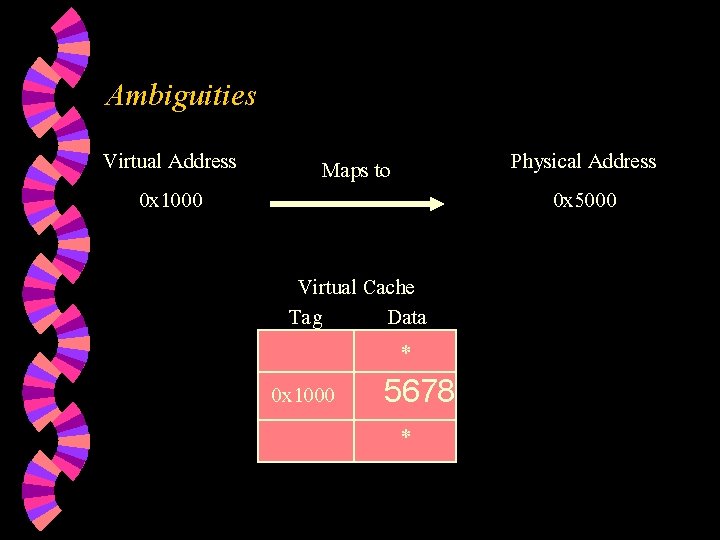

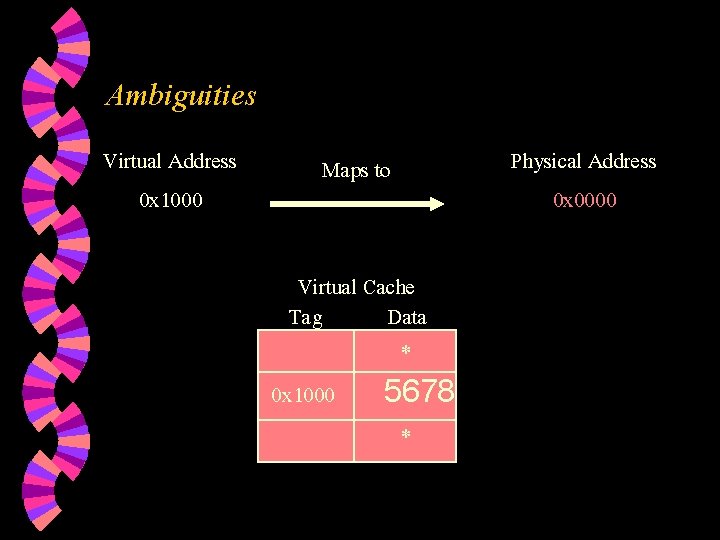

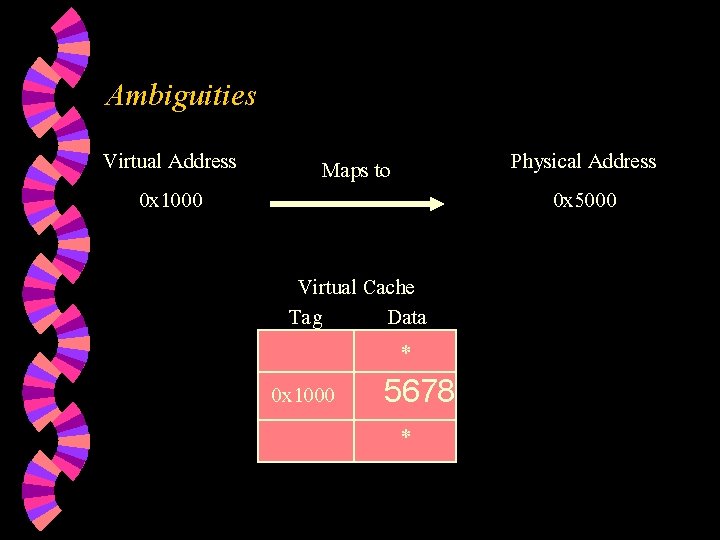

Ambiguities Virtual Address 0 x 1000 Maps to Virtual Cache Tag Data * 0 x 1000 5678 * Physical Address 0 x 5000

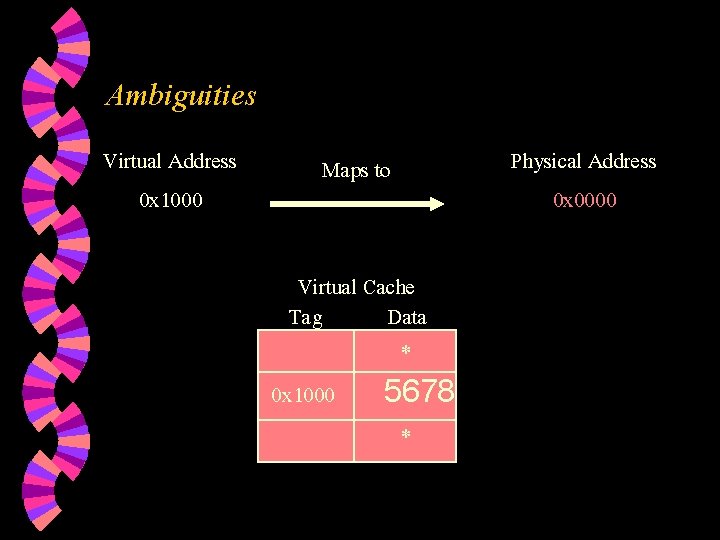

Ambiguities Virtual Address 0 x 1000 Maps to Virtual Cache Tag Data * 0 x 1000 5678 * Physical Address 0 x 0000

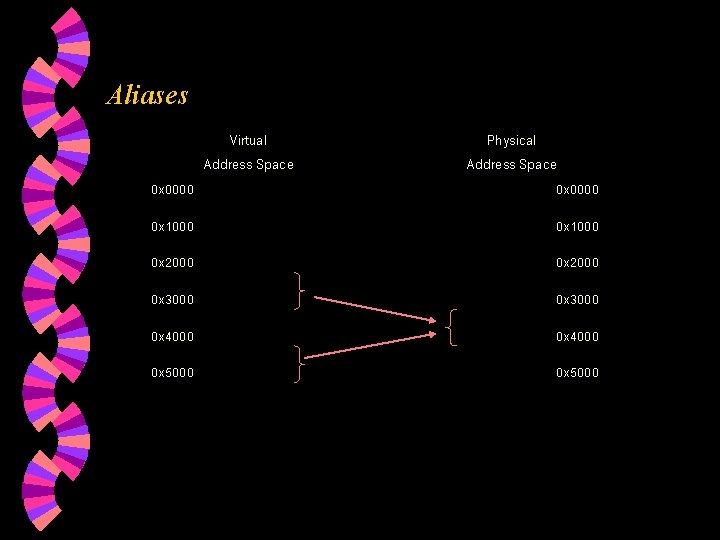

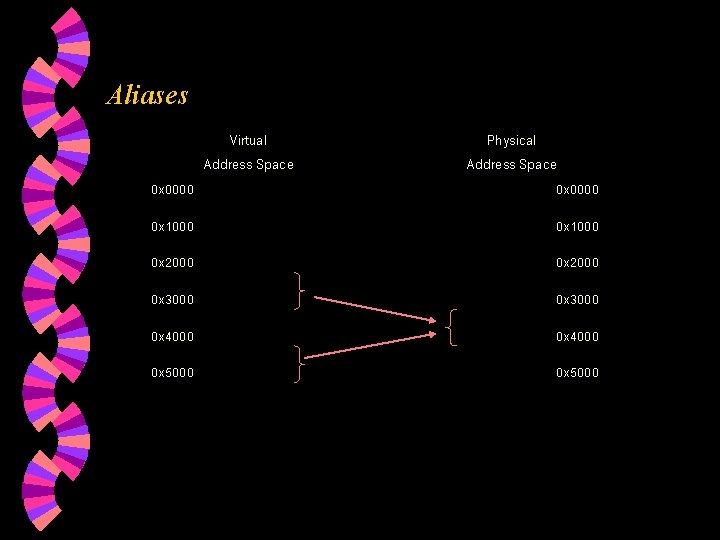

Aliases 0 x 0000 Virtual Address Space Physical Address Space 0 x 0000 0 x 1000 0 x 2000 0 x 3000 0 x 4000 0 x 5000

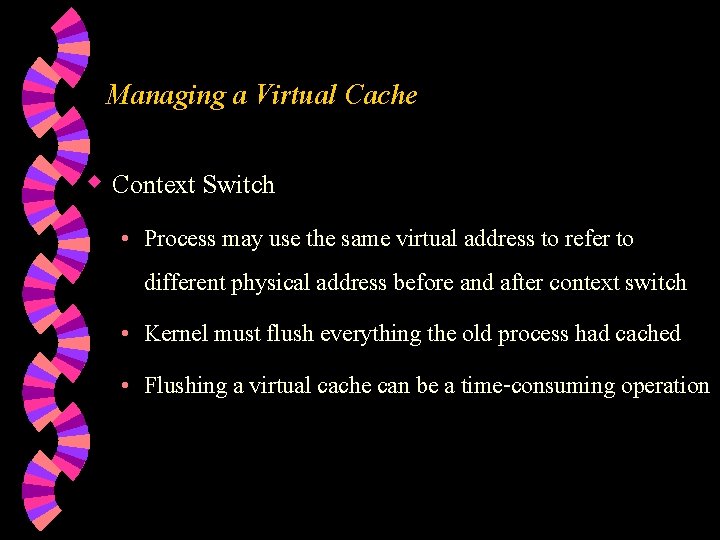

Managing a Virtual Cache w Context Switch • Process may use the same virtual address to refer to different physical address before and after context switch • Kernel must flush everything the old process had cached • Flushing a virtual cache can be a time-consuming operation

Managing a Virtual Cache w Fork • the child receive a complete copy of the parent’s address space • Flushing during each context switch eliminates most inconsistencies between parent’s and child’s data • But must consider about during the copy operations

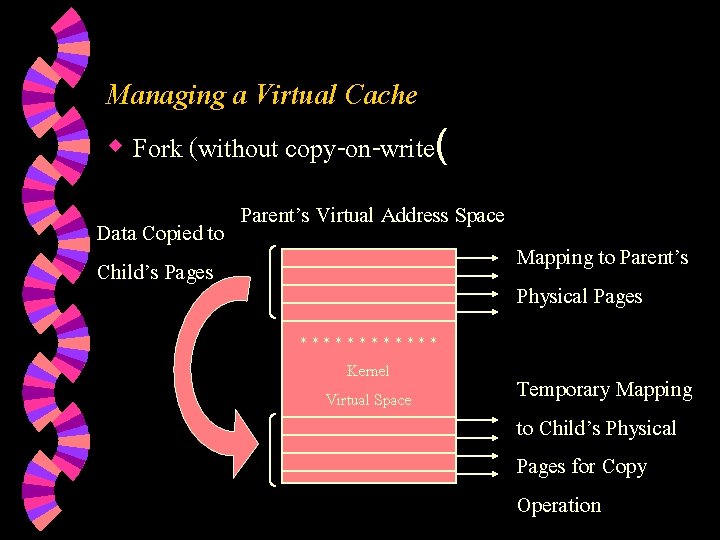

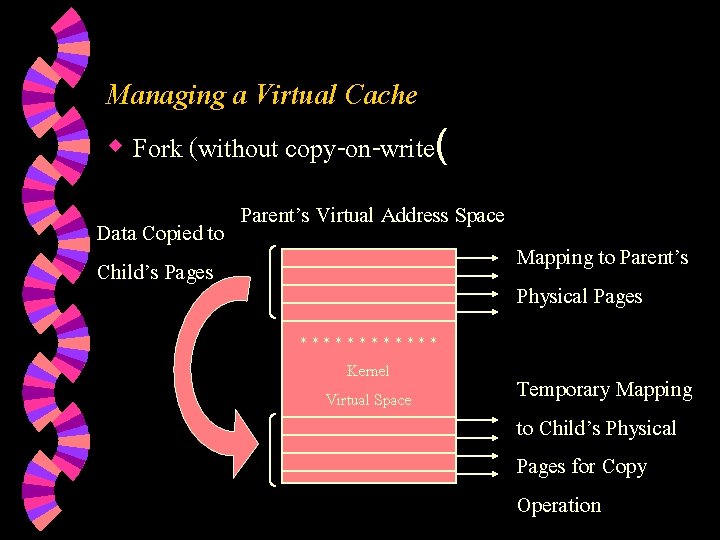

Managing a Virtual Cache w Fork (without copy-on-write( Data Copied to Child’s Pages Parent’s Virtual Address Space ****** Kernel Virtual Space Mapping to Parent’s Physical Pages Temporary Mapping to Child’s Physical Pages for Copy Operation

Managing a Virtual Cache w Fork • If write-through caching is used, No special flushing is needed during fork since at least one context switch must occur before the child executes • If write-back caching is used, Main memory must be validated before temporary mapping is removed

Managing a Virtual Cache w Fork • if fork is implemented with copy-on-write • if write-through, no flushing is needed at fork time • if write-back, main memory must be validated

Managing a Virtual Cache w Exec • Discards the process’s current address space and replaces it with a new one for the new program the process will run • Possible to occur ambiguities • Kernel must invalidated all user data from cache before execution begins

Managing a Virtual Cache w Exit • Address space of process is discarded • Last step of exit is to perform context switch that flushed the cache

Managing a Virtual Cache w Brk and Sbrk • use to grow and shrink the process’s bss segment • growing bss causes no cache problems • shrink bss, kernel must invalidates data from cache

Managing a Virtual Cache w Shared Memory and Mapped Files • no special cache management is needed since the cache is flushed at each context switch • if single process attaches shared memory segment at different address?

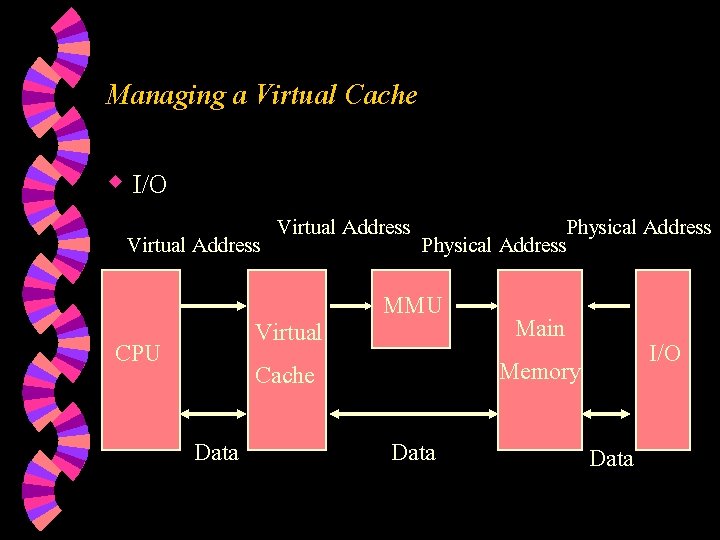

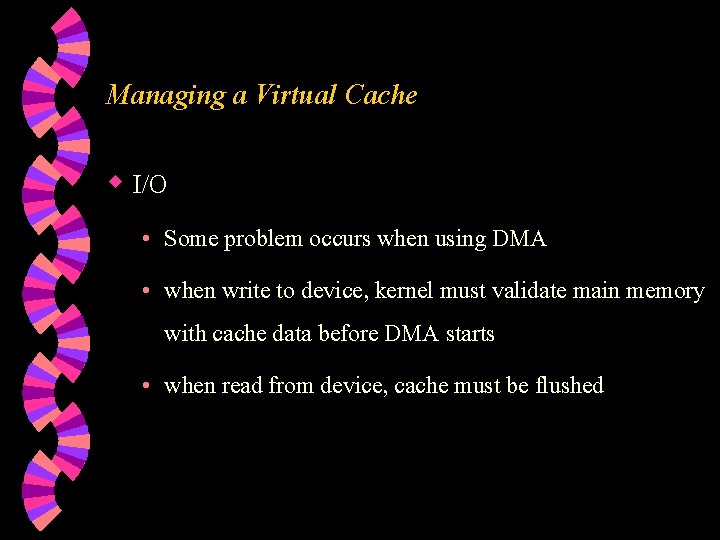

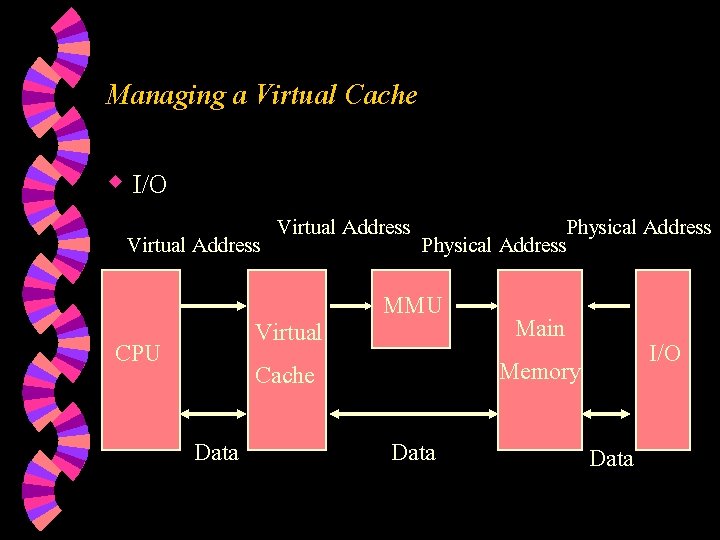

Managing a Virtual Cache w I/O Virtual Address Virtual Cache CPU Data Physical Address MMU Data Main Memory I/O Data

Managing a Virtual Cache w I/O • Some problem occurs when using DMA • when write to device, kernel must validate main memory with cache data before DMA starts • when read from device, cache must be flushed

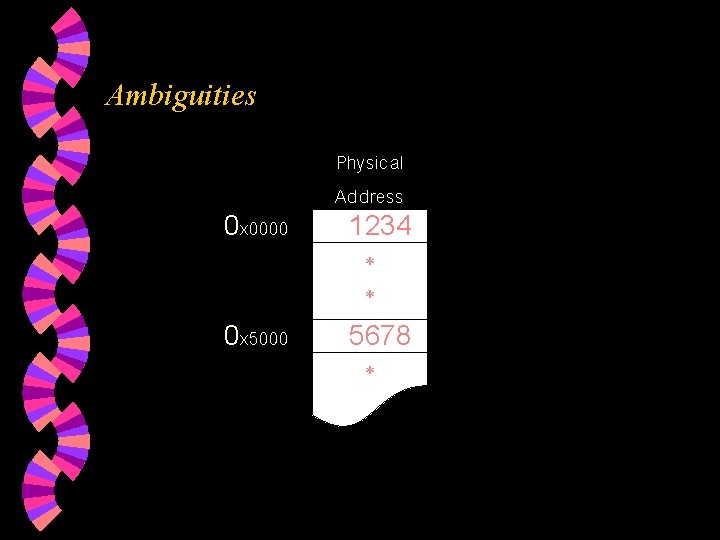

Managing a Virtual Cache w User-Kernel Data Ambiguities • to prevent cached kernel data from user process, cache must be flushed • Apollo DN-4000, add bit indicate user or kernel mode

Virtual Caches with Keys ���� �� ����� 4422005

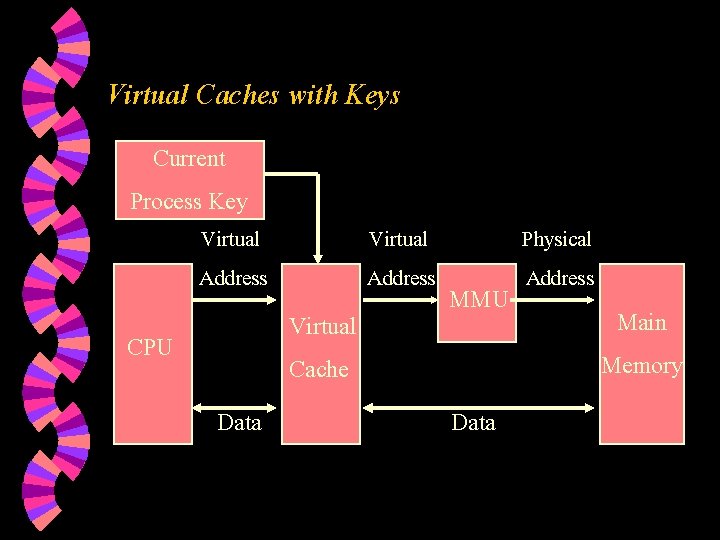

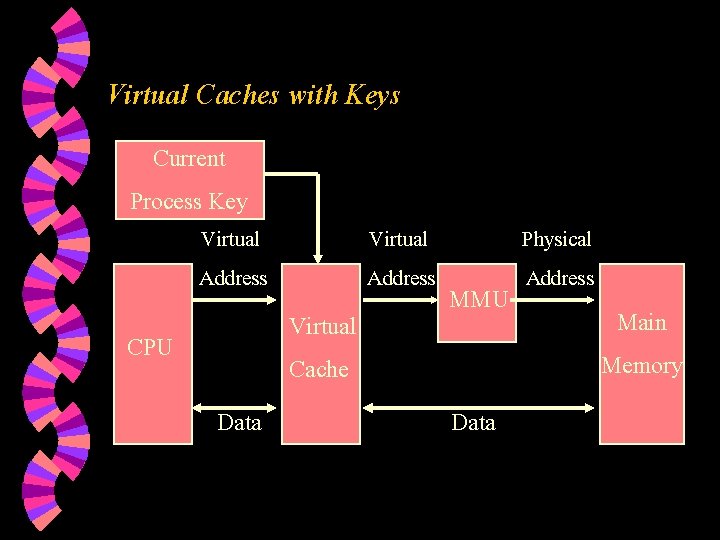

Virtual Caches with Keys Current Process Key Virtual Address Virtual Cache CPU Data MMU Data Physical Address Main Memory

Managing a Virtual Cache with Keys w Context Switch • Normally no need to flush the cache as long as enough keys that unique can be assigned to each processes • when reassigning key, all entries tagged with affected key must be flushed

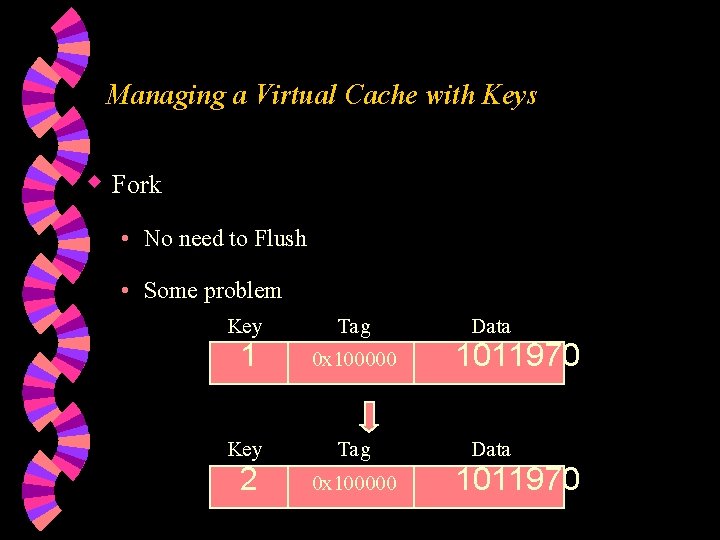

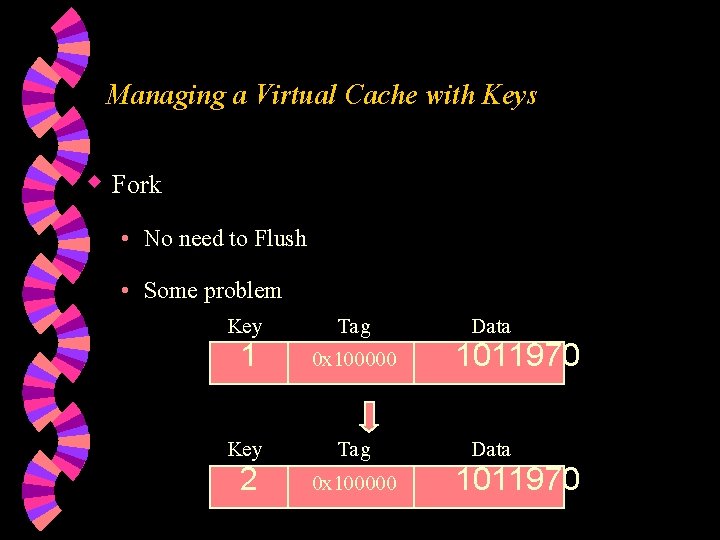

Managing a Virtual Cache with Keys w Fork • No need to Flush • Some problem Key 1 Tag 0 x 100000 Data 1011970 Key 2 Tag 0 x 100000 Data 1011970

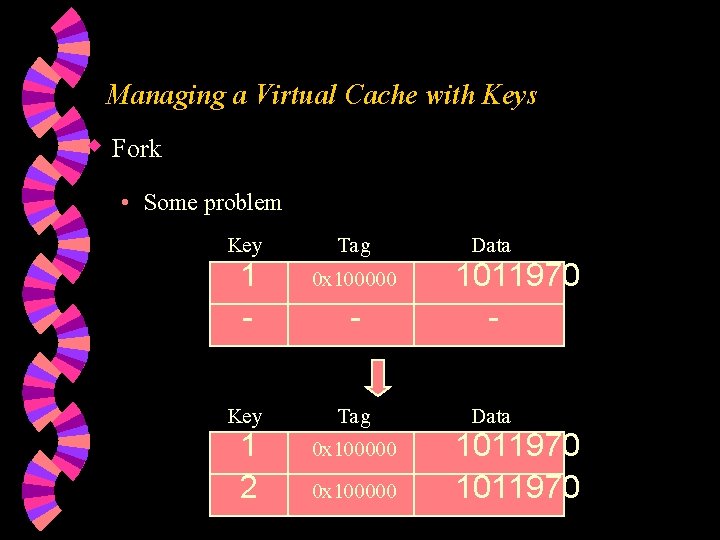

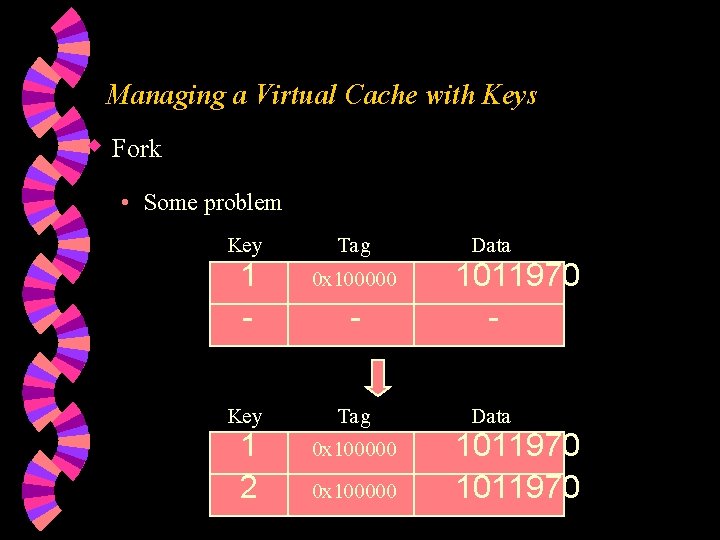

Managing a Virtual Cache with Keys w Fork • Some problem Key 1 - Tag 0 x 100000 - Data 1011970 - Key 1 2 Tag 0 x 100000 Data 1011970

Managing a Virtual Cache with Keys w Exec • A unique key must be chosen for new address space • if reassigning key, all entries tagged with affected key must be flushed

Managing a Virtual Cache with Keys w Exit • not necessary to invalidate cache at exit time • cache is flushed during context switch

Managing a Virtual Cache with Keys w Brk and Sbrk • Same as pure virtual cache

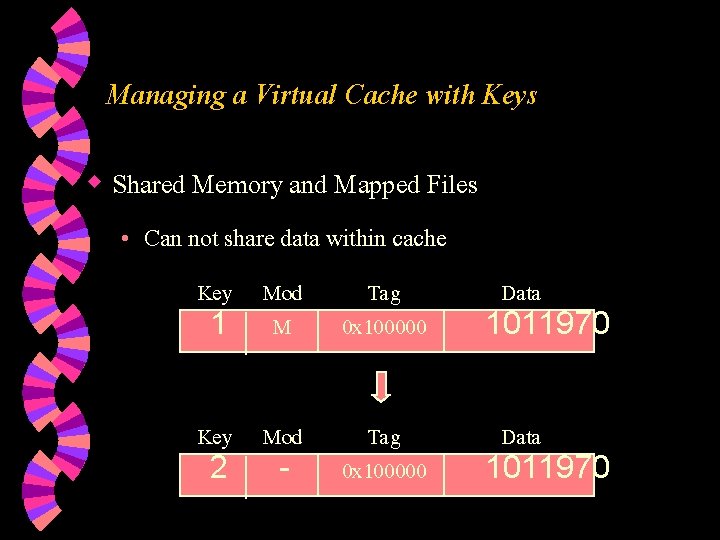

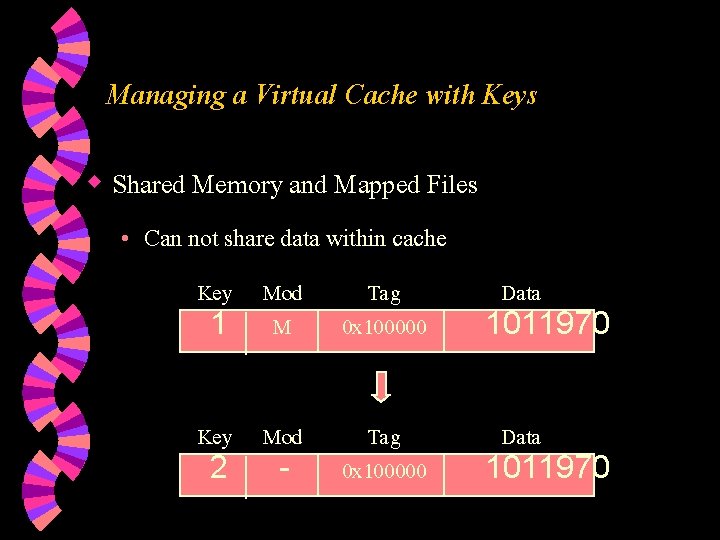

Managing a Virtual Cache with Keys w Shared Memory and Mapped Files • Can not share data within cache Key Mod 1 M Tag 0 x 100000 Data 1011970 Key Mod 2 - Tag 0 x 100000 Data 1011970

Managing a Virtual Cache with Keys w I/O • Same as pure virtual cache

Managing a Virtual Cache with Keys w User-Kernel Data Ambiguities • Kernel process have special key • User process can not access kernel data • Kernel process can not share user data

Virtual Cache Usage in MMUs w Special-purpose cache, Translation Lookside Buffer (TLB) or Address translation Cache (ATC( • caching most recently used page mapping • speed up virtual-to-physical address translation process • must be flush on each context switch

Virtual Caches with Physical Address Tags ���� �� ����� 4422005

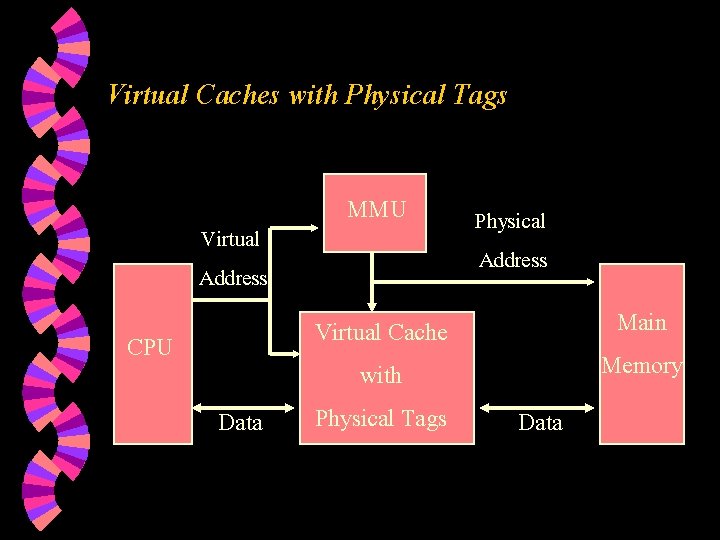

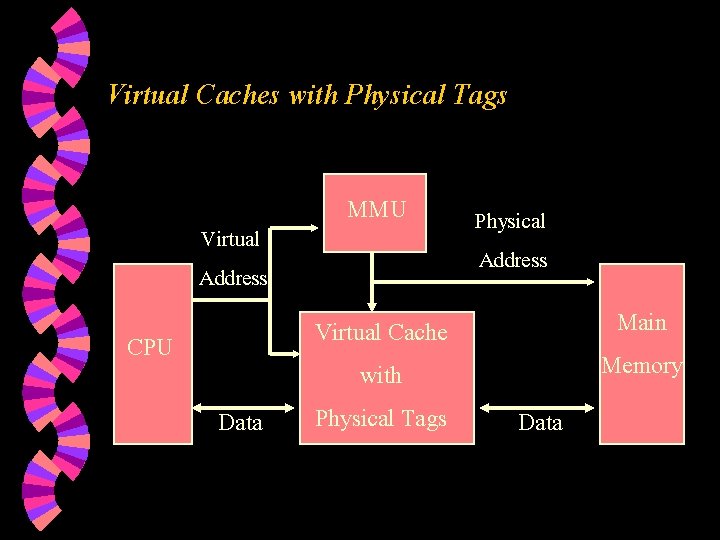

Virtual Caches with Physical Tags Virtual Address CPU Data MMU Virtual Cache with Physical Tags Physical Address Main Memory Data

Managing a Virtual Cache with Physical Tags w Context Switch • Normally no need to flush the cache • No keys to mange as virtual cache with keys

Managing a Virtual Cache with Physical Tags w Fork • No cache flushing is required fork • Data can be shared in cache • No aliases can occur

Managing a Virtual Cache with Physical Tags w Exec • Address space not be use by any process • exec deallocates pages, must be ensure that stale data is removed prior to allocating page to new process

Managing a Virtual Cache with Physical Tags w Exit • Can be either flushed at system call or postponed until physical page are reuse

Managing a Virtual Cache with Physical Tags w Brk and Sbrk • Like exec and exit • Can be either flushed at system call or postponed until physical page are reuse

Managing a Virtual Cache with Physical Tags w Shared Memory and Mapped Files • Can share data in cache • Better hit ratio for shared memory

Managing a Virtual Cache with Physical Tags w I/O • Same as pure virtual cache

Managing a Virtual Cache with Physical Tags w User-Kernel Data Ambiguities • No ambiguities between user and kernel data • Kernel can reference cached user data directly

The End