Mikroelektronikai tervezrendszerek ttekints A mikroelektronikai CAD elemei Szimultor

- Slides: 37

Mikroelektronikai tervezőrendszerek Áttekintés

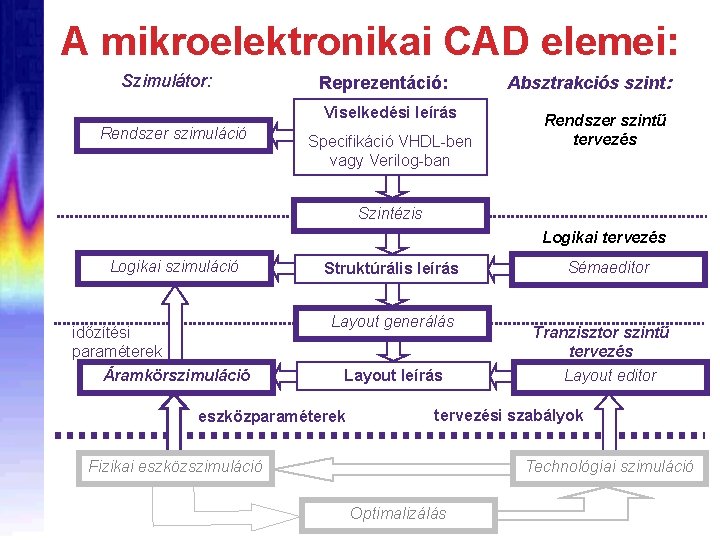

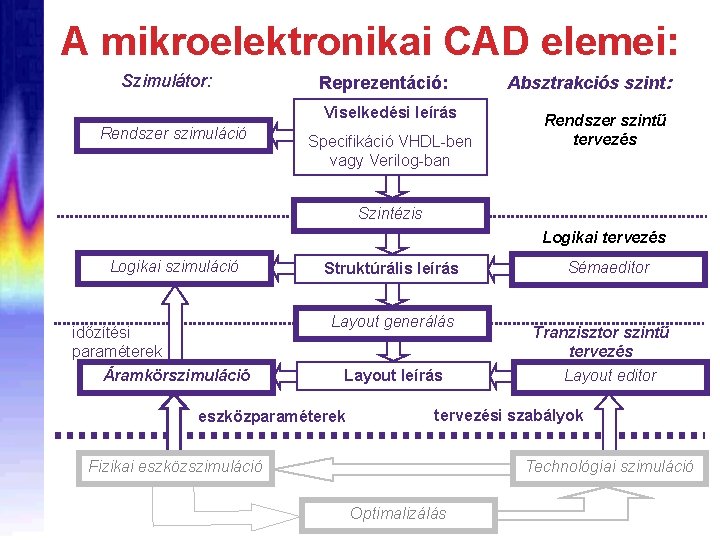

A mikroelektronikai CAD elemei: Szimulátor: Reprezentáció: Viselkedési leírás Rendszer szimuláció Specifikáció VHDL-ben vagy Verilog-ban Absztrakciós szint: Rendszer szintű tervezés Szintézis Logikai tervezés Logikai szimuláció időzítési paraméterek Áramkörszimuláció Struktúrális leírás Layout generálás Layout leírás eszközparaméterek Sémaeditor Tranzisztor szintű tervezés Layout editor tervezési szabályok Fizikai eszközszimuláció Technológiai szimuláció Optimalizálás

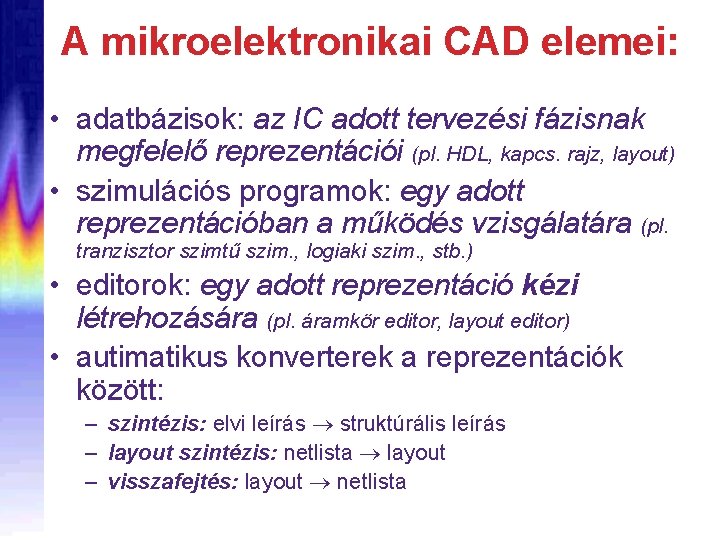

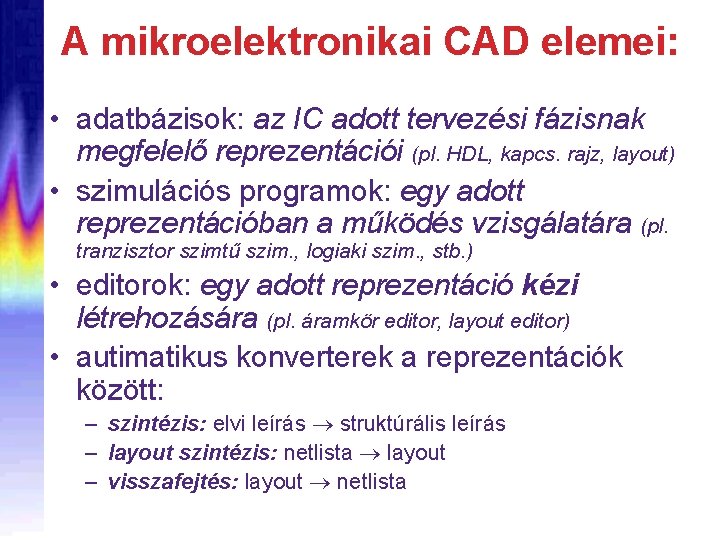

A mikroelektronikai CAD elemei: • adatbázisok: az IC adott tervezési fázisnak megfelelő reprezentációi (pl. HDL, kapcs. rajz, layout) • szimulációs programok: egy adott reprezentációban a működés vzisgálatára (pl. tranzisztor szimtű szim. , logiaki szim. , stb. ) • editorok: egy adott reprezentáció kézi létrehozására (pl. áramkör editor, layout editor) • autimatikus konverterek a reprezentációk között: – szintézis: elvi leírás struktúrális leírás – layout szintézis: netlista layout – visszafejtés: layout netlista

A felsorolt elemek nem utalnak semmiféle realizációs módszerre! Ez miért lehetséges? • IC technológák tervezése - alkalmazás tervezés: élesen szétválasztva. • Kapocs közöttük: terevezési szabályok, eszközparaméterek. Ennek milyen következményei vannak? • Nyílt tervezőrendszerek lehetségesek (ugyanaz a szoftver teteszőleges technológiára, realizációs módra). • A digitális IC tervezéséhez nem kellenek mély mikroelektronikai ismeretek.

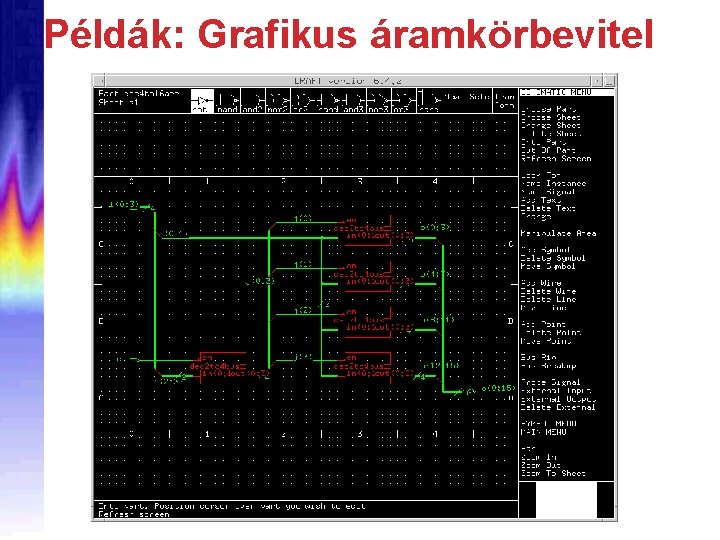

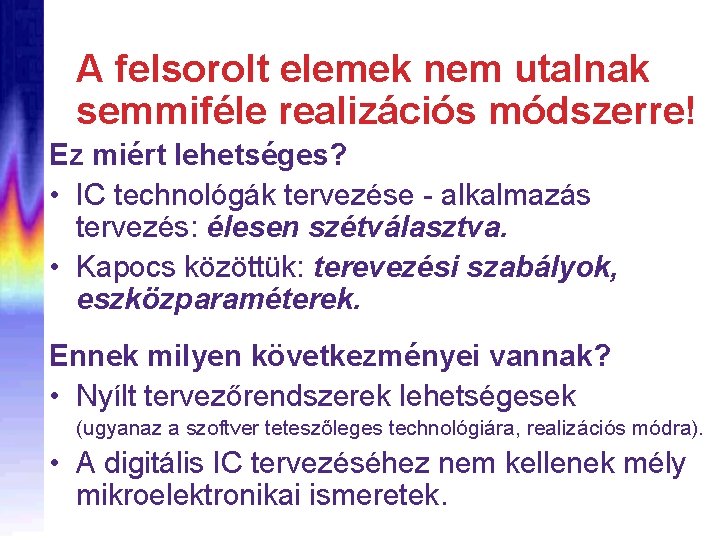

Példák: Grafikus áramkörbevitel

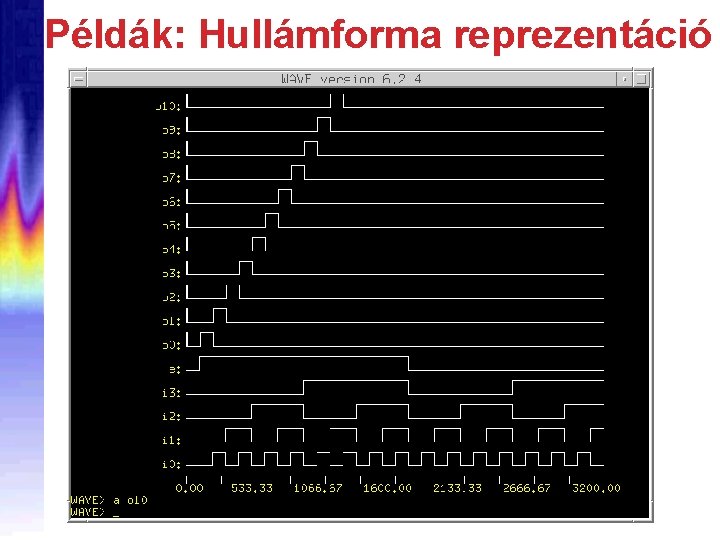

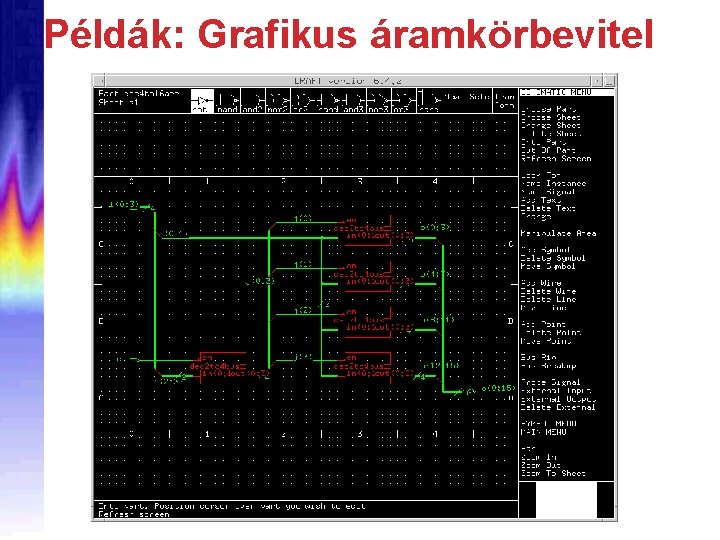

Példák: Hullámforma reprezentáció

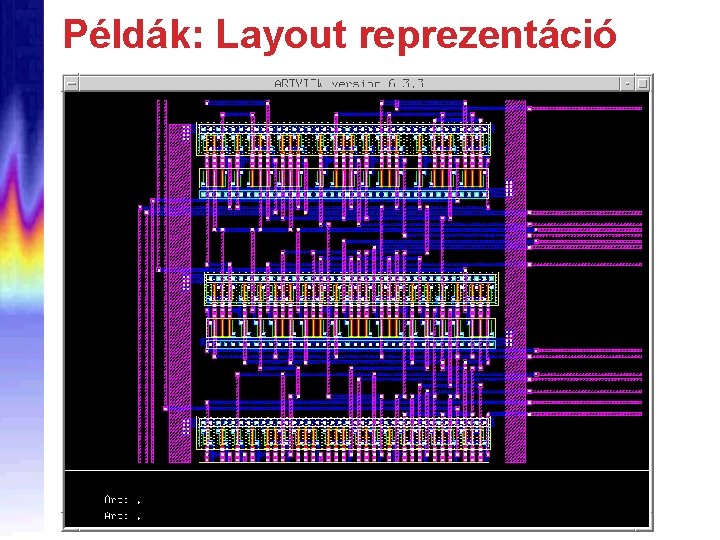

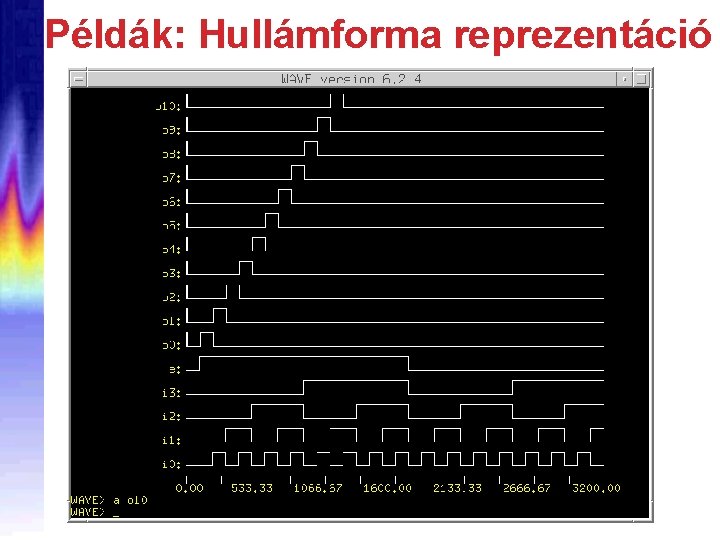

Példák: Layout reprezentáció

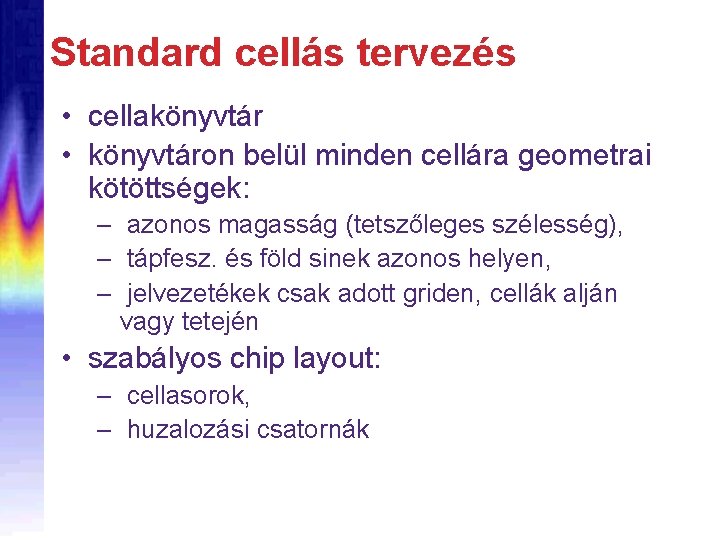

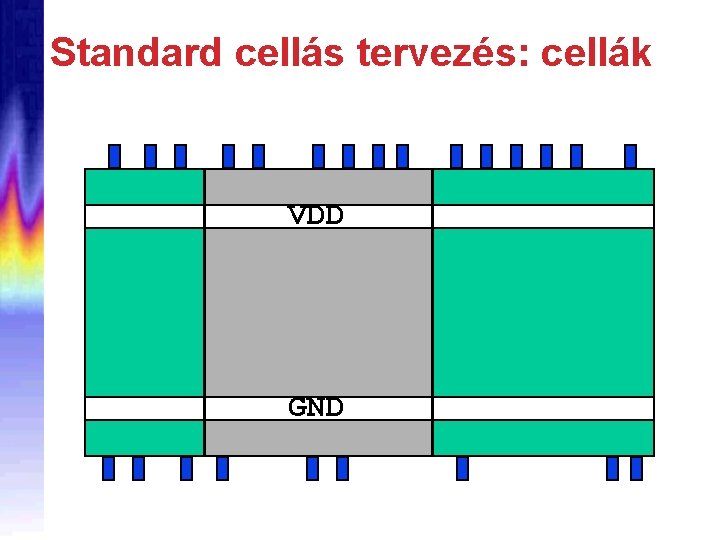

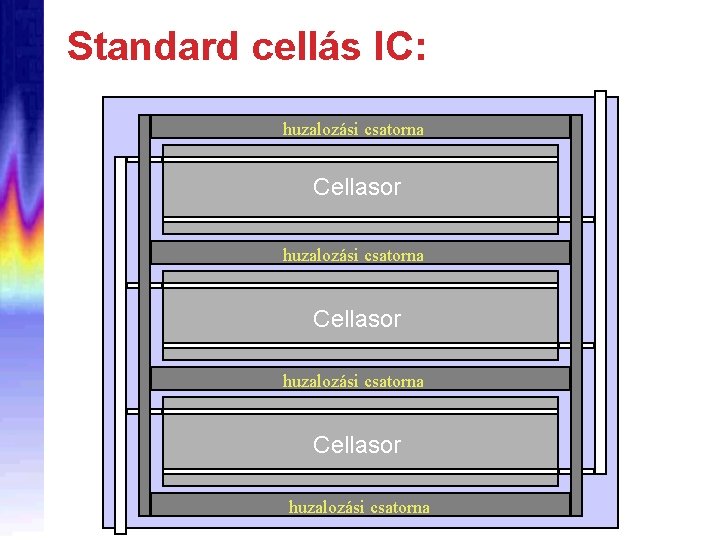

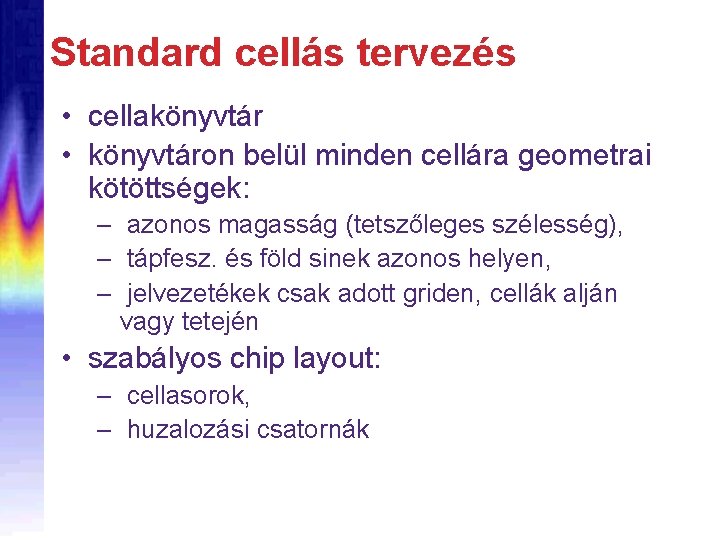

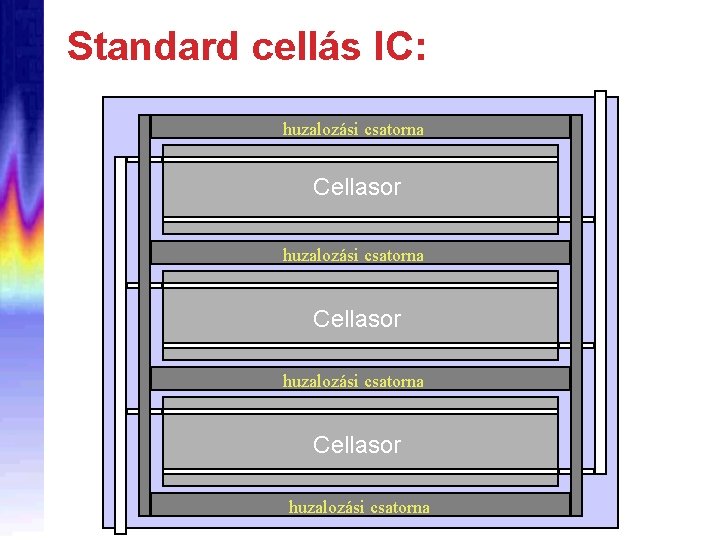

Standard cellás tervezés • cellakönyvtár • könyvtáron belül minden cellára geometrai kötöttségek: – azonos magasság (tetszőleges szélesség), – tápfesz. és föld sinek azonos helyen, – jelvezetékek csak adott griden, cellák alján vagy tetején • szabályos chip layout: – cellasorok, – huzalozási csatornák

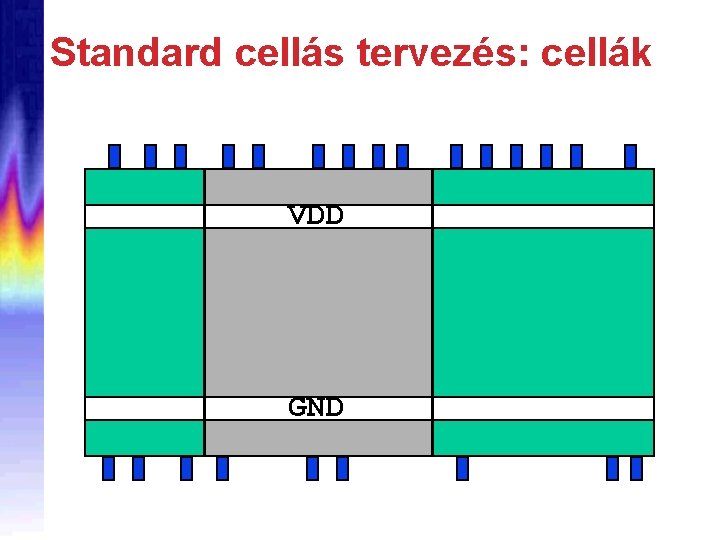

Standard cellás tervezés: cellák VDD GND

Standard cellás IC: huzalozási csatorna Cellasor huzalozási csatorna

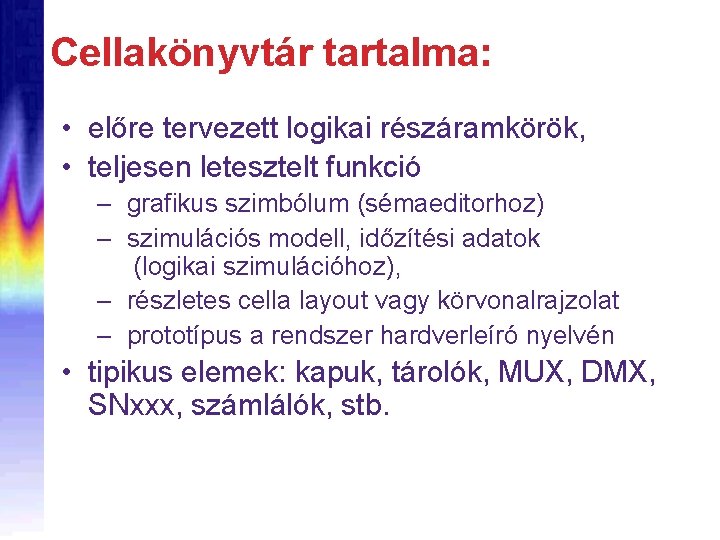

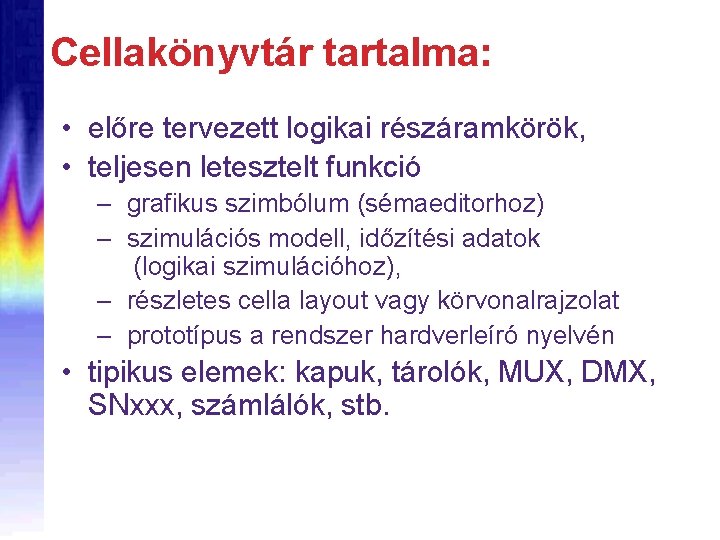

Cellakönyvtár tartalma: • előre tervezett logikai részáramkörök, • teljesen letesztelt funkció – grafikus szimbólum (sémaeditorhoz) – szimulációs modell, időzítési adatok (logikai szimulációhoz), – részletes cella layout vagy körvonalrajzolat – prototípus a rendszer hardverleíró nyelvén • tipikus elemek: kapuk, tárolók, MUX, DMX, SNxxx, számlálók, stb.

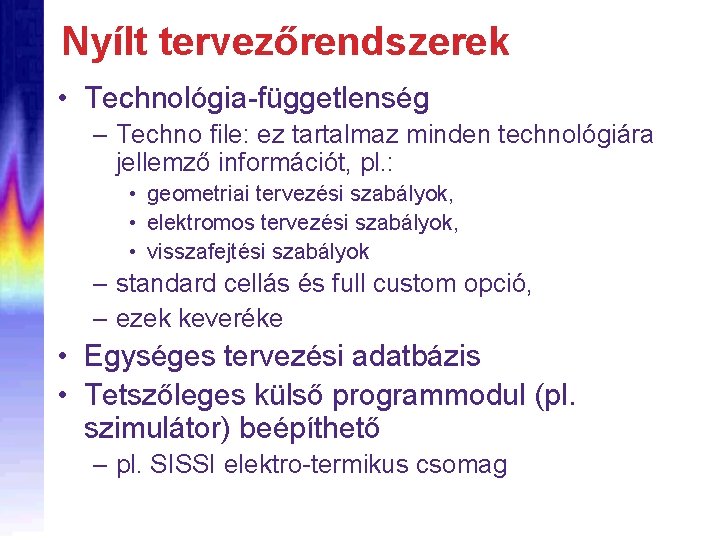

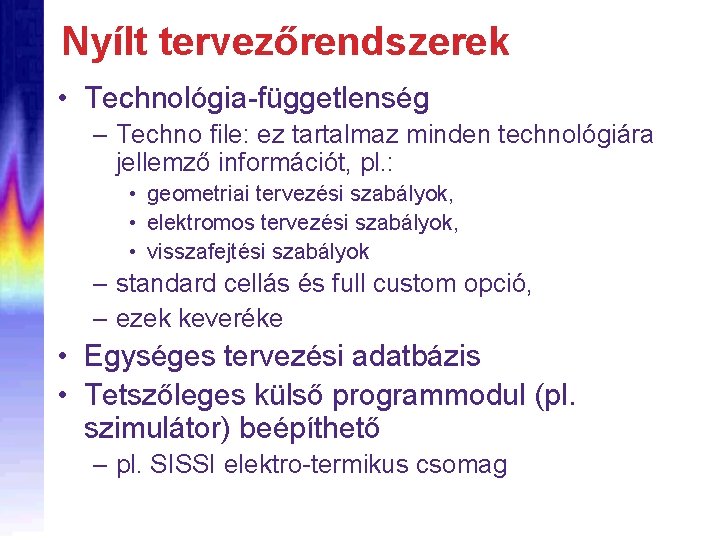

Nyílt tervezőrendszerek • Technológia-függetlenség – Techno file: ez tartalmaz minden technológiára jellemző információt, pl. : • geometriai tervezési szabályok, • elektromos tervezési szabályok, • visszafejtési szabályok – standard cellás és full custom opció, – ezek keveréke • Egységes tervezési adatbázis • Tetszőleges külső programmodul (pl. szimulátor) beépíthető – pl. SISSI elektro-termikus csomag

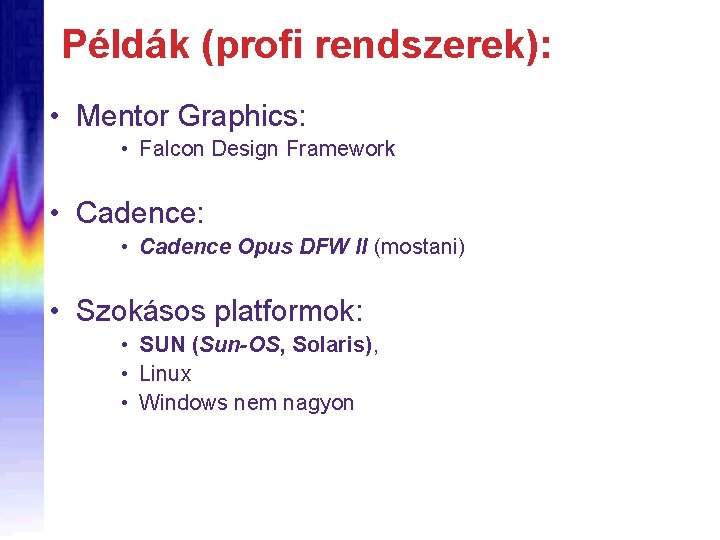

Példák (profi rendszerek): • Mentor Graphics: • Falcon Design Framework • Cadence: • Cadence Opus DFW II (mostani) • Szokásos platformok: • SUN (Sun-OS, Solaris), • Linux • Windows nem nagyon

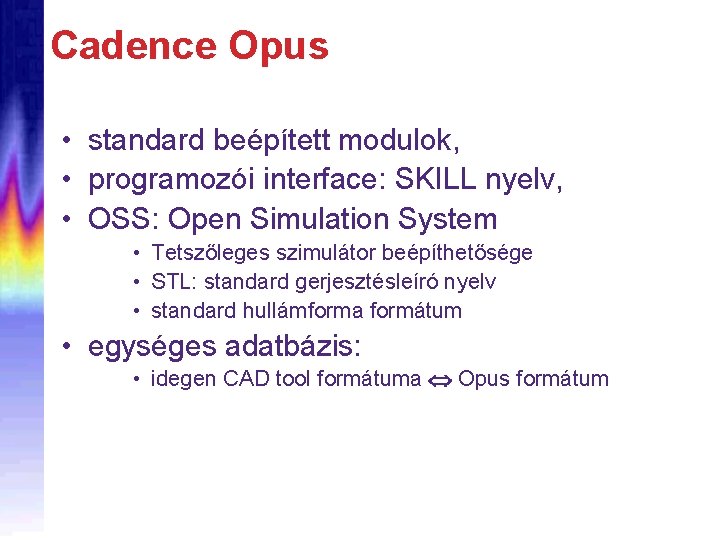

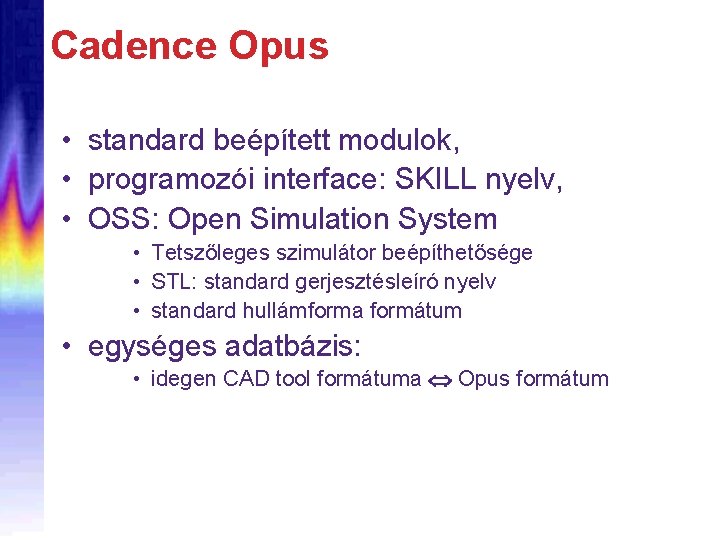

Cadence Opus • standard beépített modulok, • programozói interface: SKILL nyelv, • OSS: Open Simulation System • Tetszőleges szimulátor beépíthetősége • STL: standard gerjesztésleíró nyelv • standard hullámforma formátum • egységes adatbázis: • idegen CAD tool formátuma Opus formátum

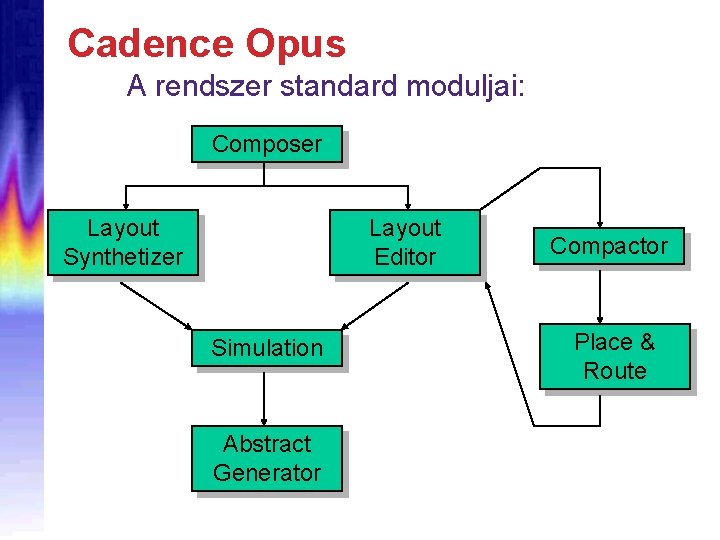

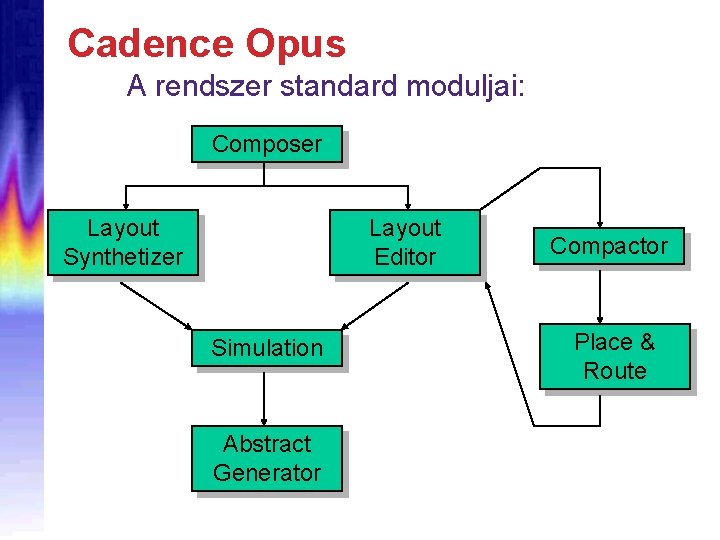

Cadence Opus A rendszer standard moduljai: Composer Layout Synthetizer Layout Editor Simulation Abstract Generator Compactor Place & Route

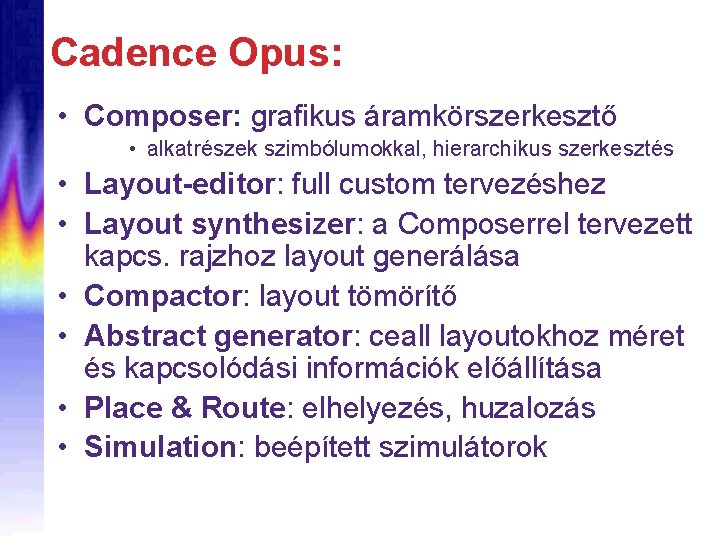

Cadence Opus: • Composer: grafikus áramkörszerkesztő • alkatrészek szimbólumokkal, hierarchikus szerkesztés • Layout-editor: full custom tervezéshez • Layout synthesizer: a Composerrel tervezett kapcs. rajzhoz layout generálása • Compactor: layout tömörítő • Abstract generator: ceall layoutokhoz méret és kapcsolódási információk előállítása • Place & Route: elhelyezés, huzalozás • Simulation: beépített szimulátorok

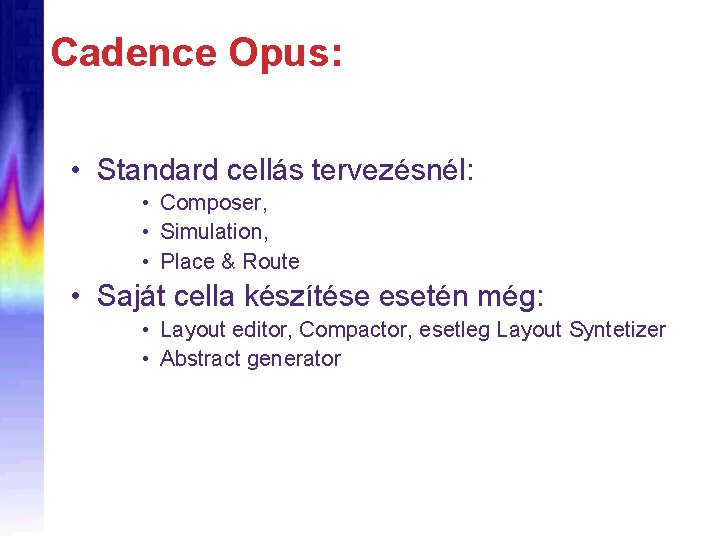

Cadence Opus: • Standard cellás tervezésnél: • Composer, • Simulation, • Place & Route • Saját cella készítése esetén még: • Layout editor, Compactor, esetleg Layout Syntetizer • Abstract generator

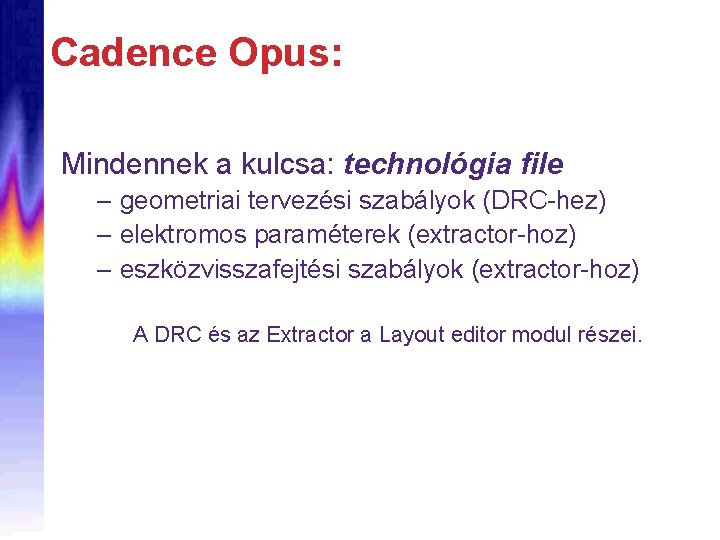

Cadence Opus: Mindennek a kulcsa: technológia file – geometriai tervezési szabályok (DRC-hez) – elektromos paraméterek (extractor-hoz) – eszközvisszafejtési szabályok (extractor-hoz) A DRC és az Extractor a Layout editor modul részei.

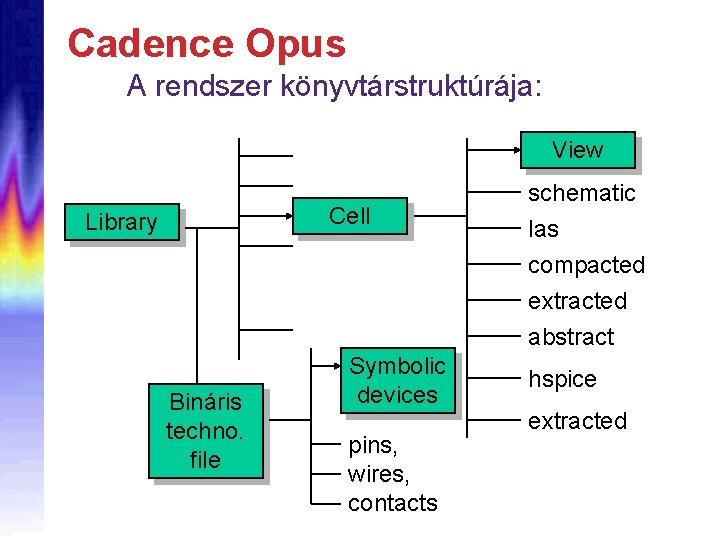

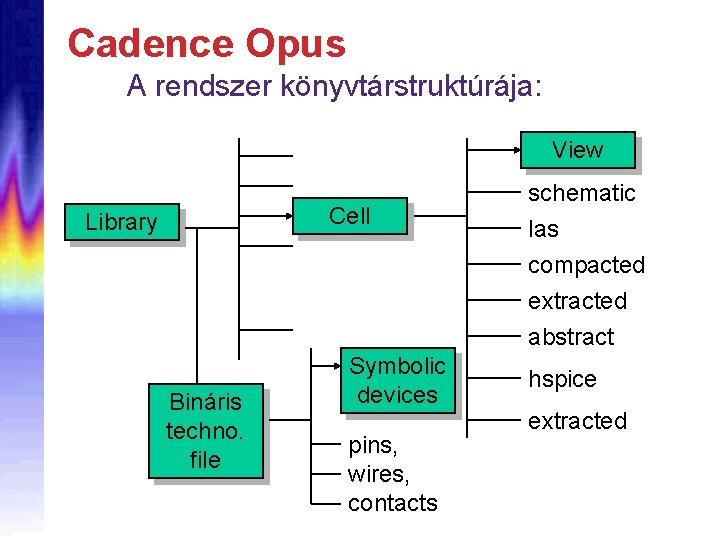

Cadence Opus A rendszer könyvtárstruktúrája: View Cell Library schematic las compacted extracted abstract Bináris techno. file Symbolic devices pins, wires, contacts hspice extracted

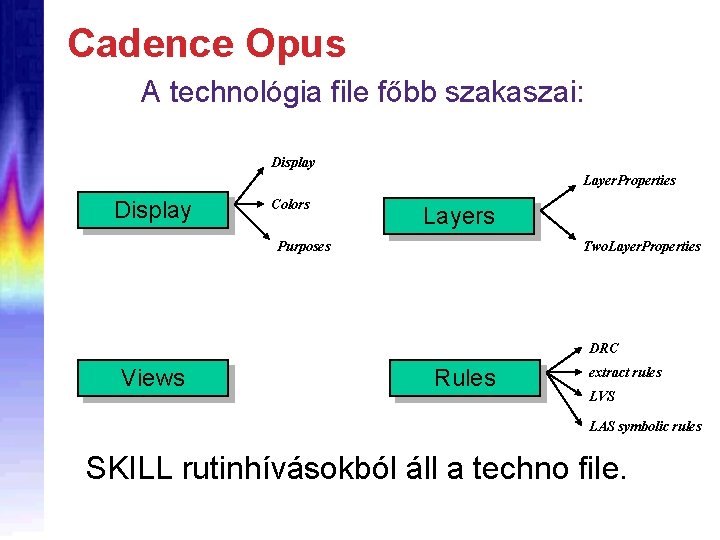

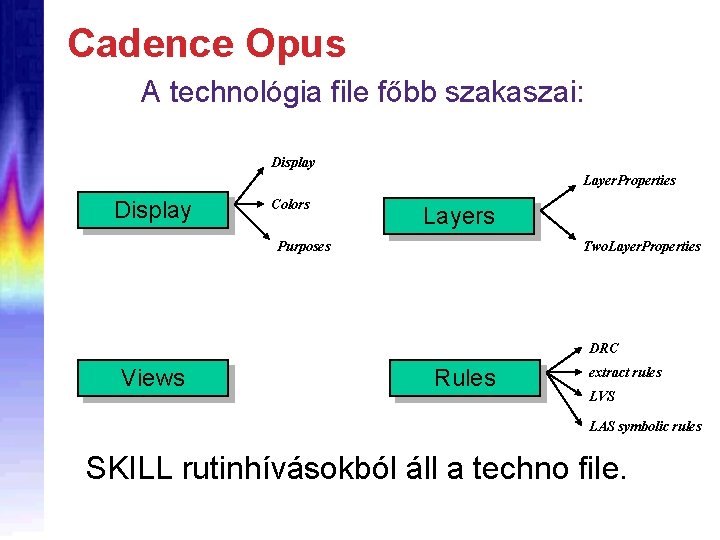

Cadence Opus A technológia file főbb szakaszai: Display Layer. Properties Display Colors Layers Purposes Two. Layer. Properties DRC Views Rules extract rules LVS LAS symbolic rules SKILL rutinhívásokból áll a techno file.

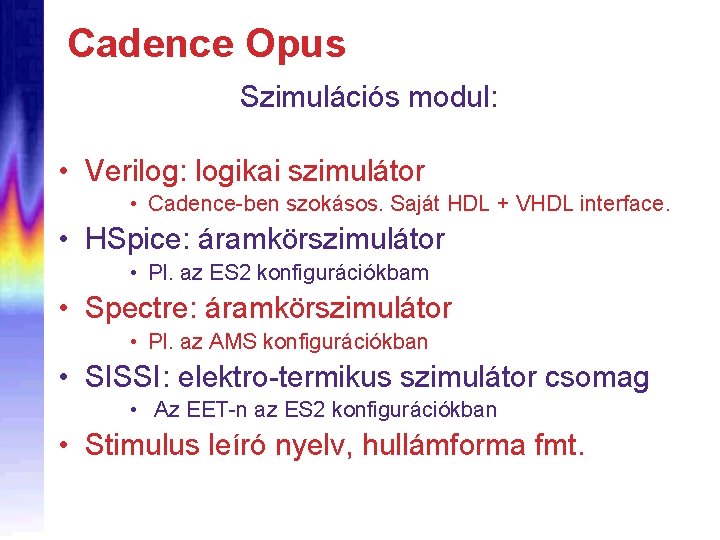

Cadence Opus Szimulációs modul: • Verilog: logikai szimulátor • Cadence-ben szokásos. Saját HDL + VHDL interface. • HSpice: áramkörszimulátor • Pl. az ES 2 konfigurációkbam • Spectre: áramkörszimulátor • Pl. az AMS konfigurációkban • SISSI: elektro-termikus szimulátor csomag • Az EET-n az ES 2 konfigurációkban • Stimulus leíró nyelv, hullámforma fmt.

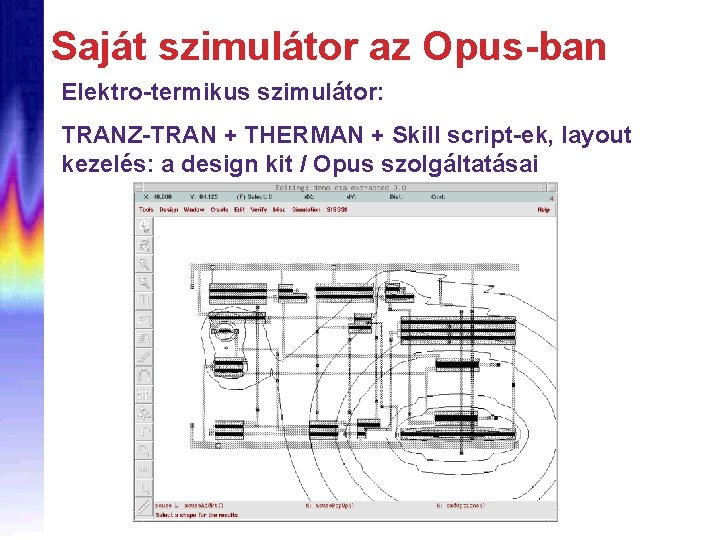

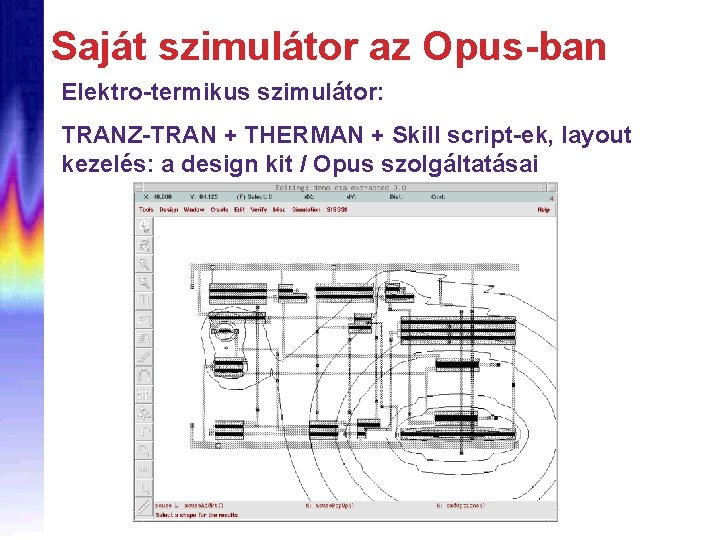

Saját szimulátor az Opus-ban Elektro-termikus szimulátor: TRANZ-TRAN + THERMAN + Skill script-ek, layout kezelés: a design kit / Opus szolgáltatásai

A design flow fogalma • Adott tervezőrendszerben, • adott stílusú tervezés (pl. standard cellás) esetén • bejárandó tervezési útvonal: – mely programok, – milyen sorrendben használandók. • Előírt program-használati sorrend • Kötelezően előállítandó file-ok (reprezentációk vagy view-k) • Ezek konzisztens volta

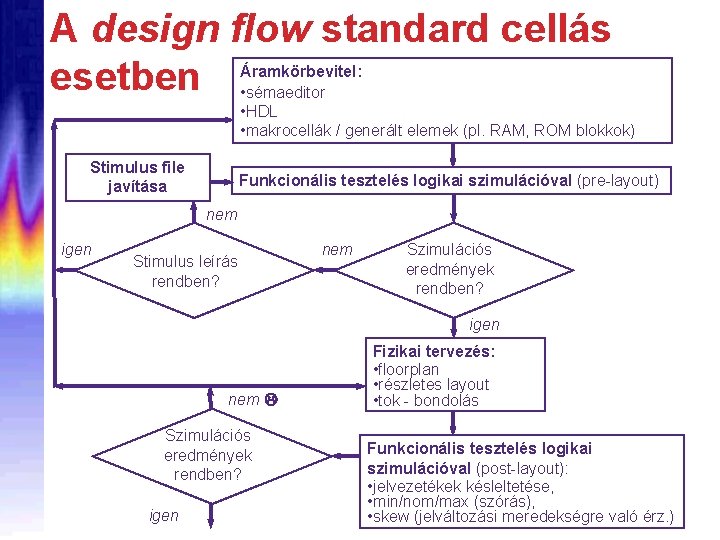

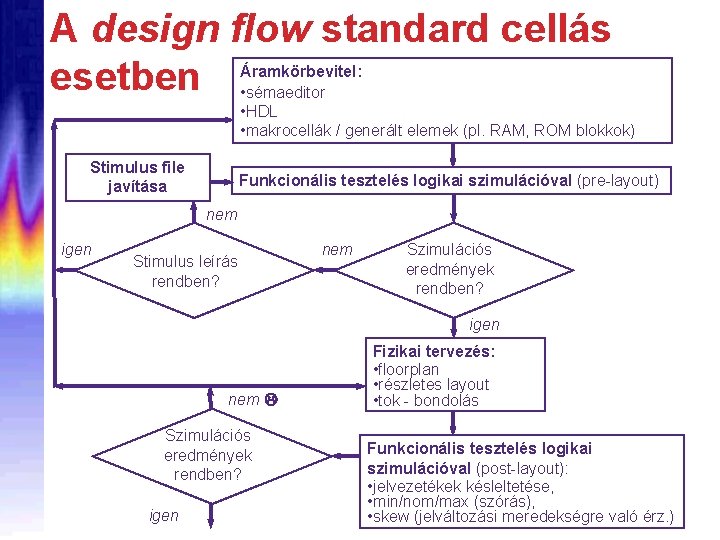

A design flow standard cellás esetben • Áramkörbevitel: sémaeditor • HDL • makrocellák / generált elemek (pl. RAM, ROM blokkok) Stimulus file javítása Funkcionális tesztelés logikai szimulációval (pre-layout) nem igen Stimulus leírás rendben? nem Szimulációs eredmények rendben? igen nem Szimulációs eredmények rendben? igen Fizikai tervezés: • floorplan • részletes layout • tok - bondolás Funkcionális tesztelés logikai szimulációval (post-layout): • jelvezetékek késleltetése, • min/nom/max (szórás), • skew (jelváltozási meredekségre való érz. )

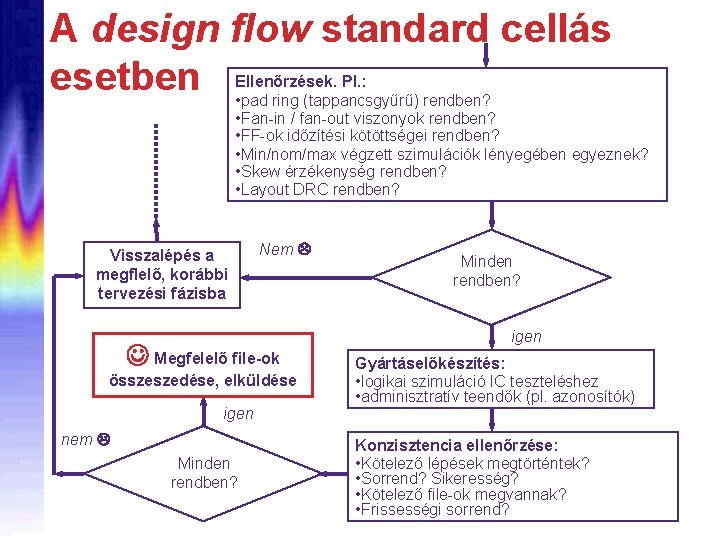

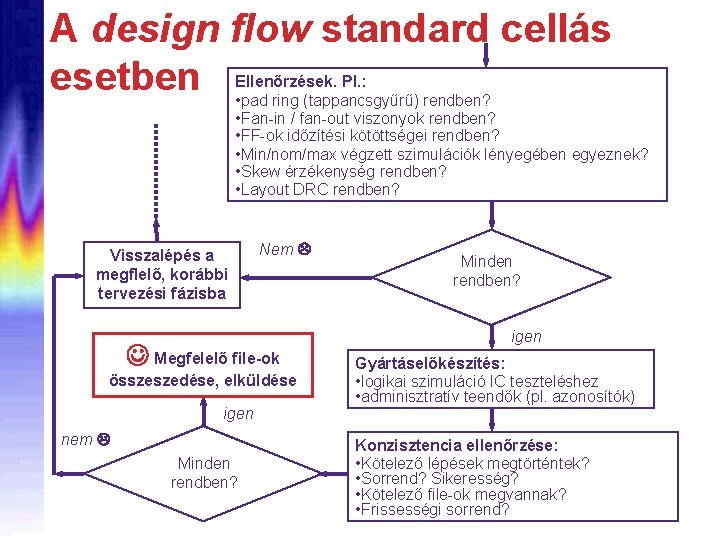

A design flow standard cellás esetben • Ellenőrzések. Pl. : pad ring (tappancsgyűrű) rendben? • Fan-in / fan-out viszonyok rendben? • FF-ok időzítési kötöttségei rendben? • Min/nom/max végzett szimulációk lényegében egyeznek? • Skew érzékenység rendben? • Layout DRC rendben? Visszalépés a megflelő, korábbi tervezési fázisba Nem Megfelelő file-ok összeszedése, elküldése igen nem Minden rendben? igen Gyártáselőkészítés: • logikai szimuláció IC teszteléshez • adminisztratív teendők (pl. azonosítók) Konzisztencia ellenőrzése: • Kötelező lépések megtörténtek? • Sorrend? Sikeresség? • Kötelező file-ok megvannak? • Frissességi sorrend?

Gyártásba küldendő file-ok • Áramkörleírás • Részletes layout terv • Tesztelés leírása (teszt vektorok és a hozzájuk tartozó helyes válaszok) • Tokozási, bondolási információ • Adminisztratív azonosítók

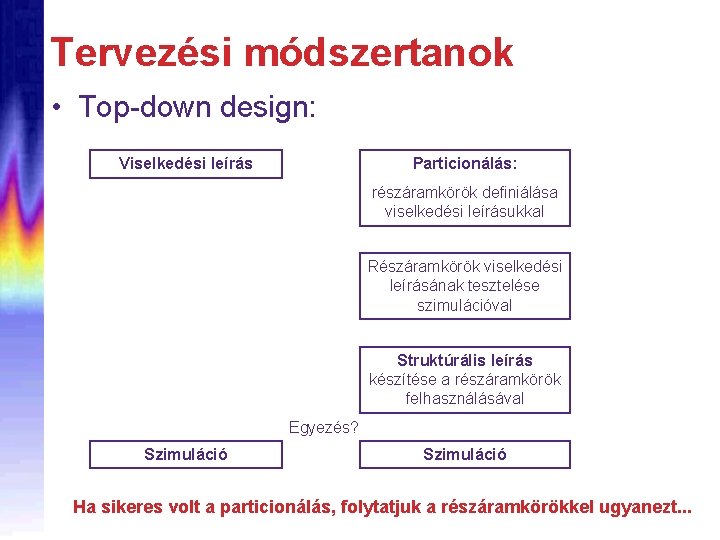

Tervezési módszertanok • Top-down design: A bonyolultabb rendszer tervezése felől haladunk az egyszerűbb felé: folyamatosan részekre bontjuk a feladatot. Meddig? Amíg olyan funkcióba nem ütközünk, ami megvan cellakönyvtári elemként.

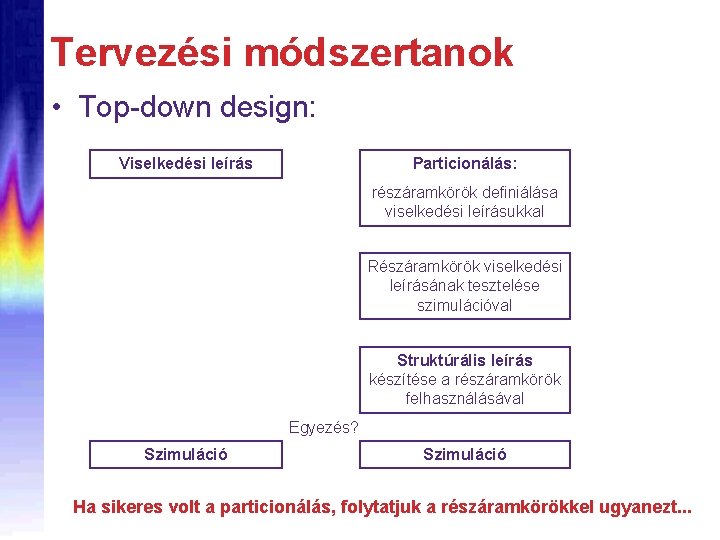

Tervezési módszertanok • Top-down design: Viselkedési leírás Particionálás: részáramkörök definiálása viselkedési leírásukkal Részáramkörök viselkedési leírásának tesztelése szimulációval Struktúrális leírás készítése a részáramkörök felhasználásával Egyezés? Szimuláció Ha sikeres volt a particionálás, folytatjuk a részáramkörökkel ugyanezt. . .

Tervezési módszertanok • Bottom-up design: Alapelemekből (cellakönyvtári elemekből) részáramköröket rakunk össze. Ezekből újabb, bonyolultabb részáramköröket rakunk össze, stb. Meddig? Amíg meg nem valósítottuk a specifikált áramkört. • Hierarchikus áramkörleírás készül (minden esetben)

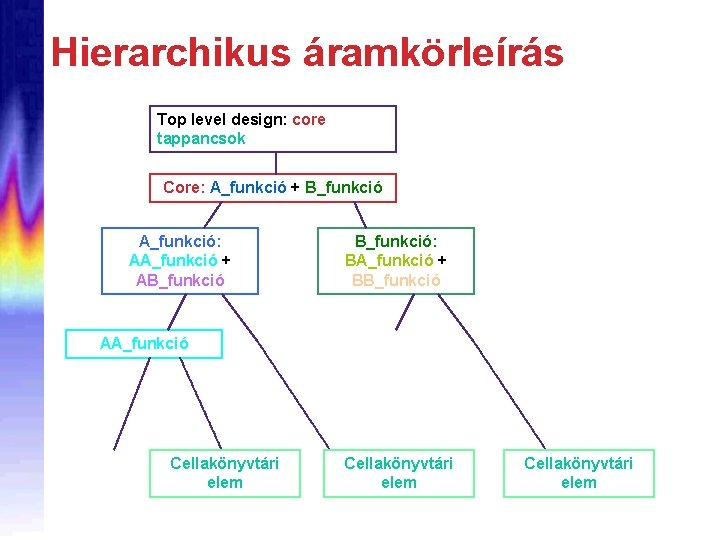

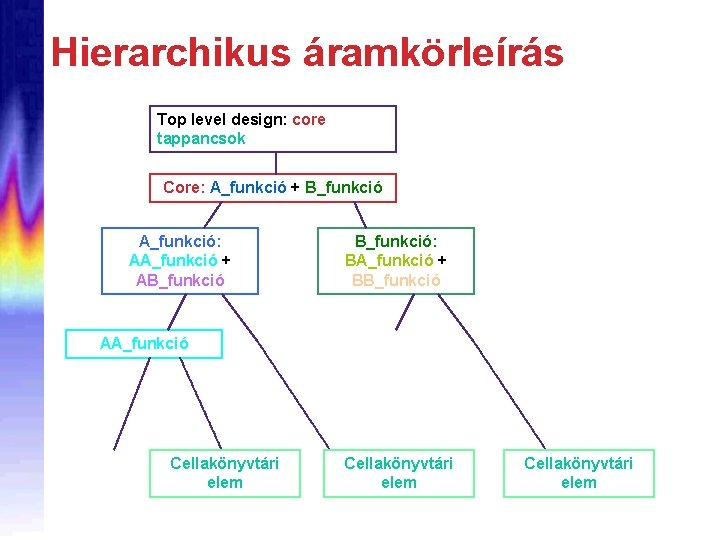

Hierarchikus áramkörleírás Top level design: core tappancsok Core: A_funkció + B_funkció A_funkció: AA_funkció + AB_funkció: BA_funkció + BB_funkció AA_funkció Cellakönyvtári elem

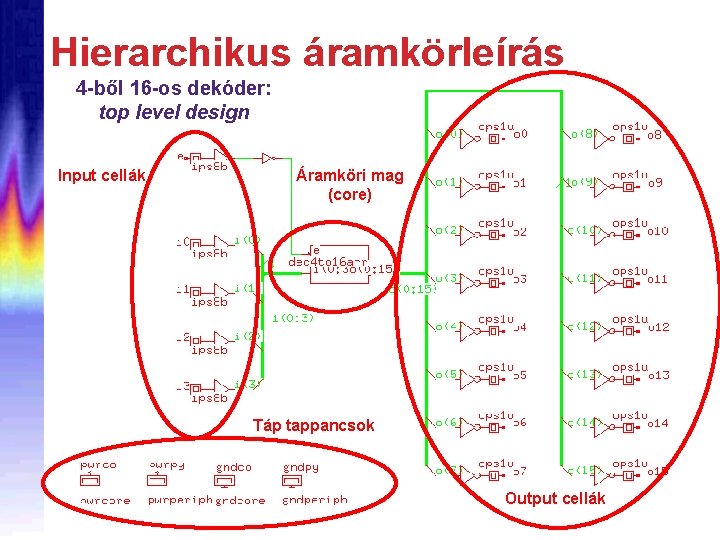

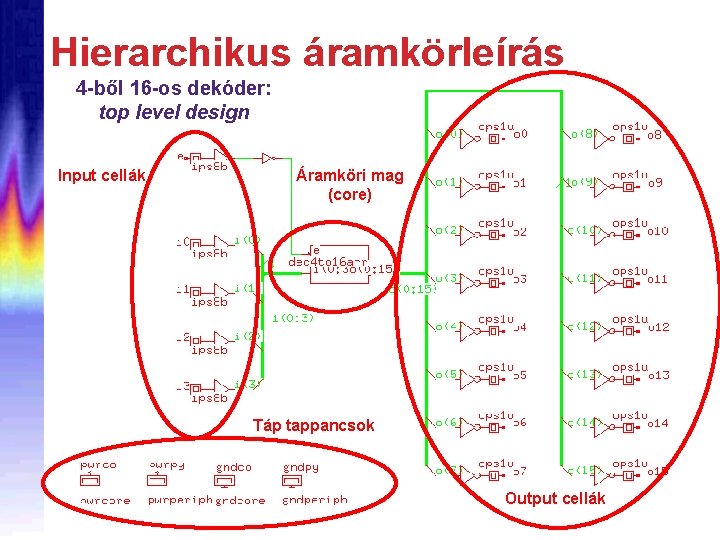

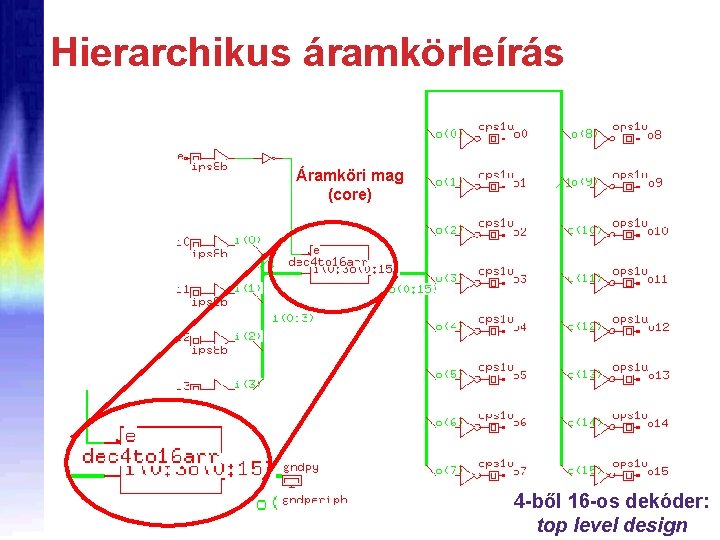

Hierarchikus áramkörleírás 4 -ből 16 -os dekóder: top level design Input cellák Áramköri mag (core) Táp tappancsok Output cellák

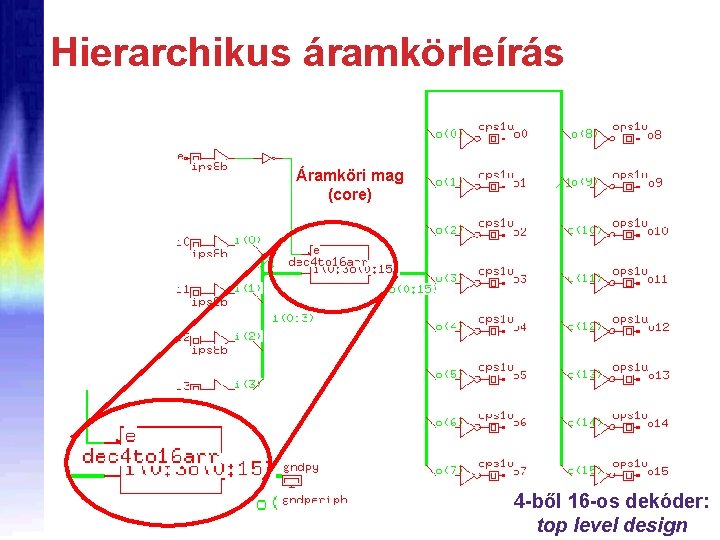

Hierarchikus áramkörleírás Áramköri mag (core) 4 -ből 16 -os dekóder: top level design

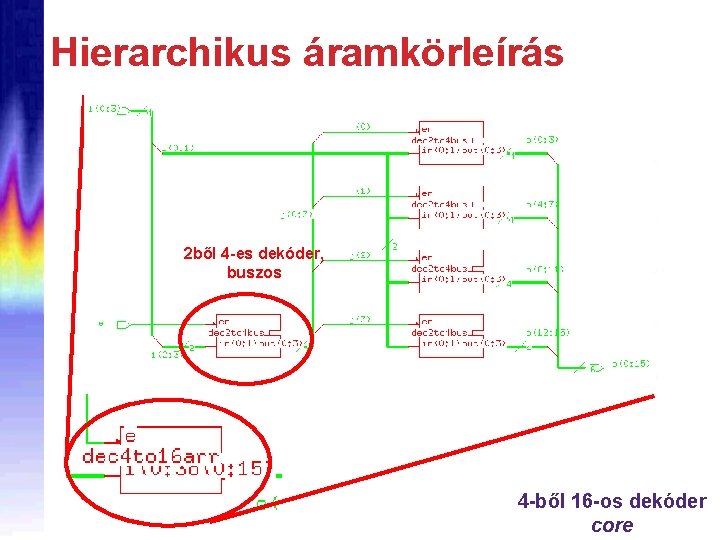

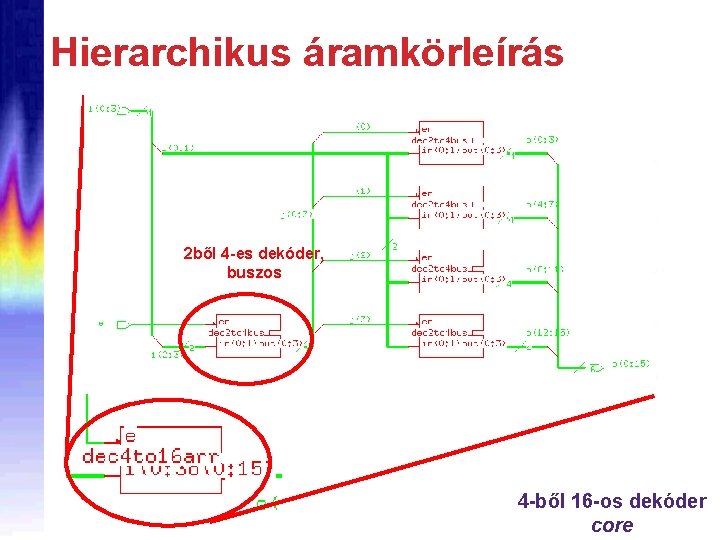

Hierarchikus áramkörleírás 2 ből 4 -es dekóder, buszos 4 -ből 16 -os dekóder core

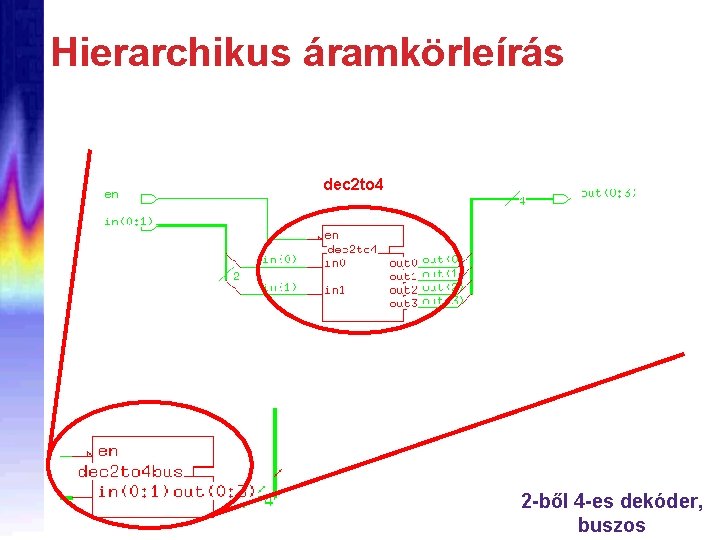

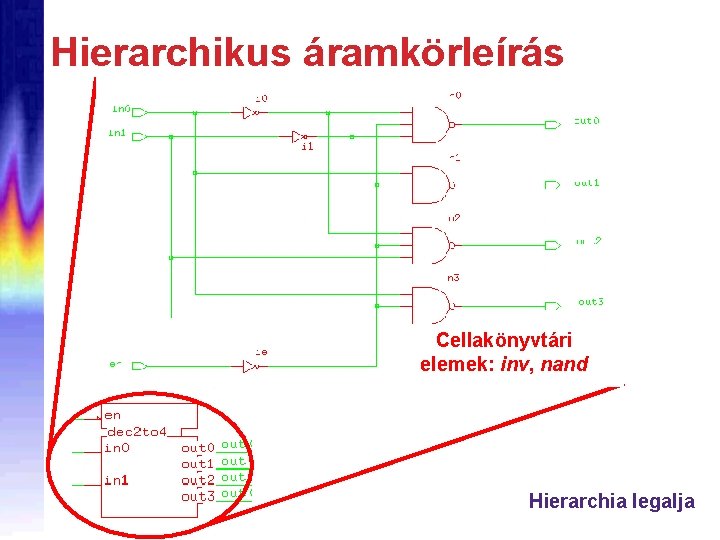

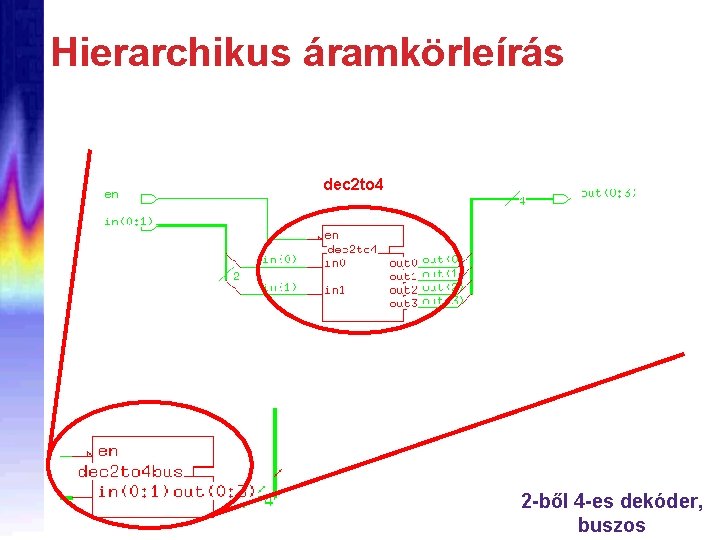

Hierarchikus áramkörleírás dec 2 to 4 2 -ből 4 -es dekóder, buszos

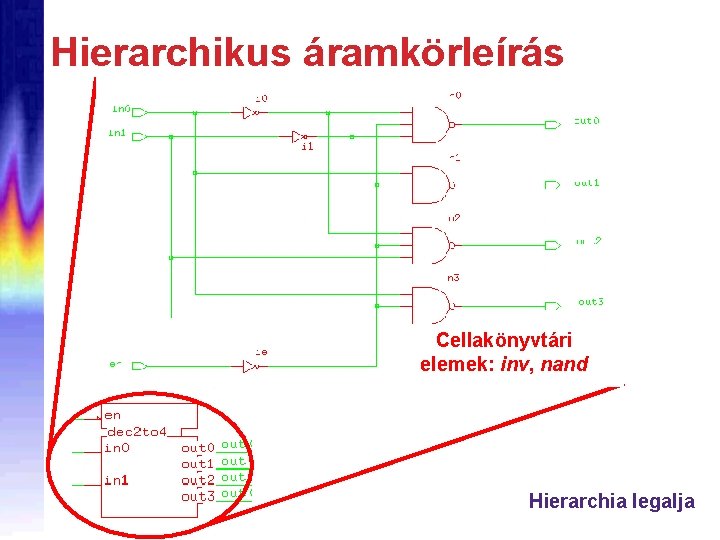

Hierarchikus áramkörleírás Cellakönyvtári elemek: inv, nand Hierarchia legalja

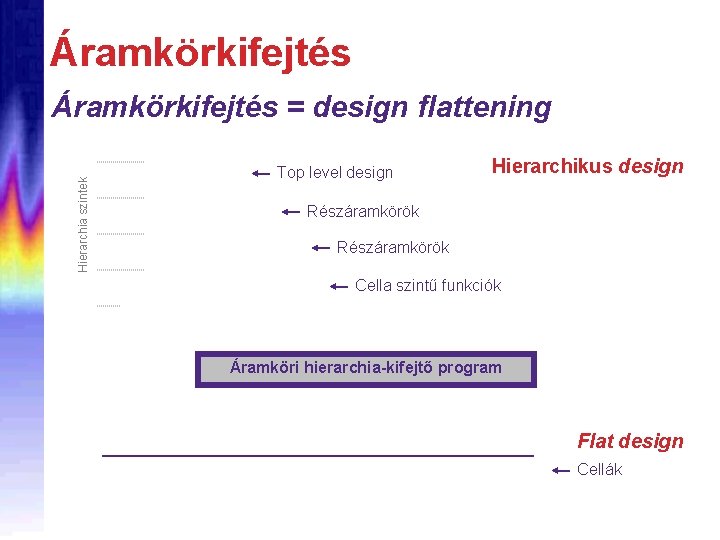

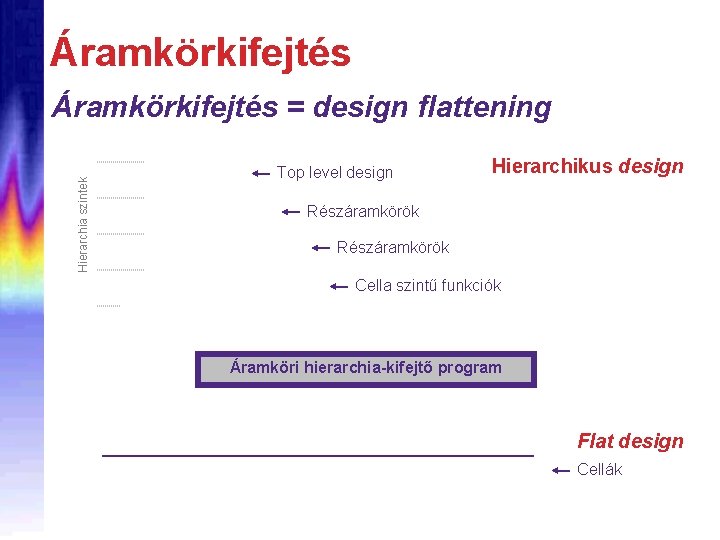

Áramkörkifejtés • A hierrachikus áramkörleírás lebontását a hierarchia kifejtésének nevezzük: – A top level design-ból kiindulva behelyettesítjük a hivatkozott részáramkörök struktúrális leírását – Rekurzíve folytatjuk, addig, amíg már csak cella hivatkozásokat nem tartalmaz a leírás. • A hierarchiától megfosztott áramkörleírást kifejtett áramkörleírásnak hívjuk. Angolul ez a flat design • Áramkörkifejtés = design flattening

Áramkörkifejtés Hierarchia szintek Áramkörkifejtés = design flattening Top level design Hierarchikus design Részáramkörök Cella szintű funkciók Áramköri hierarchia-kifejtő program Flat design Cellák

értéklánc elemei

értéklánc elemei Piac elemei

Piac elemei Szinekdoche

Szinekdoche üzleti kommunikáció fogalma

üzleti kommunikáció fogalma Adótényállás elemei

Adótényállás elemei Allegória irodalmi példa

Allegória irodalmi példa Belső kontrollrendszer elemei

Belső kontrollrendszer elemei Adótényállás elemei

Adótényállás elemei értéklánc elemei

értéklánc elemei Egy reflexív elemei

Egy reflexív elemei Multimédia elemei

Multimédia elemei önéletrajz tartalmi elemei

önéletrajz tartalmi elemei Megakaryopoiesis

Megakaryopoiesis Adótényállás elemei

Adótényállás elemei értéklánc elemei

értéklánc elemei Játszma szerkezeti elemei

Játszma szerkezeti elemei Belső kontrollrendszer elemei

Belső kontrollrendszer elemei Idej

Idej Adótényállás elemei

Adótényállás elemei Perkembangan autocad

Perkembangan autocad Bluestar plm

Bluestar plm Cad

Cad Las cad

Las cad Pit-cad

Pit-cad Cad algorithm

Cad algorithm Cad gl

Cad gl Bicarbonato en cetoacidosis diabetica

Bicarbonato en cetoacidosis diabetica Vulcan cad

Vulcan cad Lego cad software

Lego cad software Wild cad

Wild cad Drafting

Drafting Cad questions and answers

Cad questions and answers Impact cad software

Impact cad software Rasetr

Rasetr Tcvn 7284

Tcvn 7284 Disegno impianto elettrico

Disegno impianto elettrico Fac simile cad postale

Fac simile cad postale Cad

Cad