ESE 680 002 ESE 534 Computer Organization Day

![Mesh of Trees • Hierarchical Mesh • Build Tree in each column [Leighton/FOCS 1981] Mesh of Trees • Hierarchical Mesh • Build Tree in each column [Leighton/FOCS 1981]](https://slidetodoc.com/presentation_image_h2/b2abfea9b236cf6be34fe32ae713a261/image-20.jpg)

![Penn ESE 680 -002 Spring 2007 -- De. Hon [De. Hon/TRVLSI 2004] 63 Penn ESE 680 -002 Spring 2007 -- De. Hon [De. Hon/TRVLSI 2004] 63](https://slidetodoc.com/presentation_image_h2/b2abfea9b236cf6be34fe32ae713a261/image-63.jpg)

- Slides: 65

ESE 680 -002 (ESE 534): Computer Organization Day 18: March 21, 2007 Interconnect 6: Mo. T Penn ESE 680 -002 Spring 2007 -- De. Hon 1

Previously • HSRA/BFT – natural hierarchical network – Switches scale O(N) • Mesh – natural 2 D network – Switches scale W(Np+0. 5) Penn ESE 680 -002 Spring 2007 -- De. Hon 2

Today • • Good Mesh properties HSRA vs. Mesh Mo. T Grand unified network theory – Mo. T vs. HSRA – Mo. T vs. Mesh Penn ESE 680 -002 Spring 2007 -- De. Hon 3

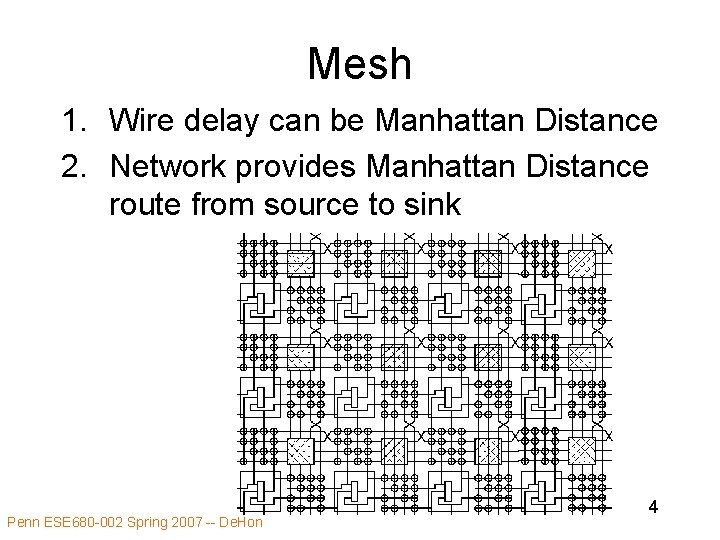

Mesh 1. Wire delay can be Manhattan Distance 2. Network provides Manhattan Distance route from source to sink Penn ESE 680 -002 Spring 2007 -- De. Hon 4

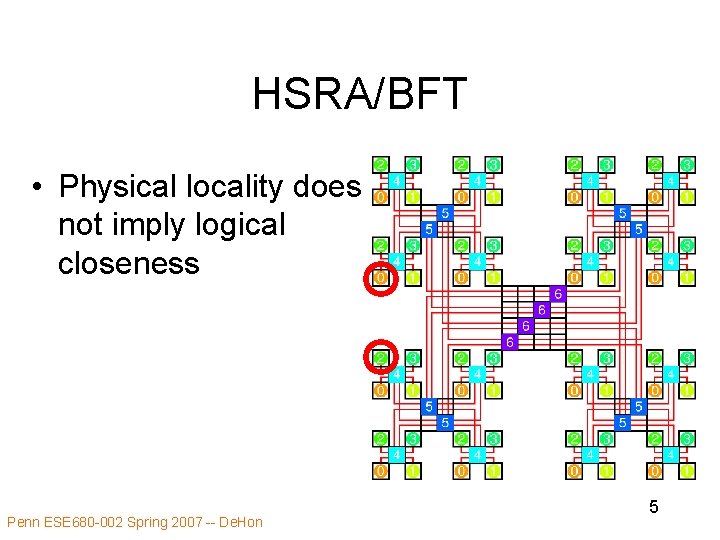

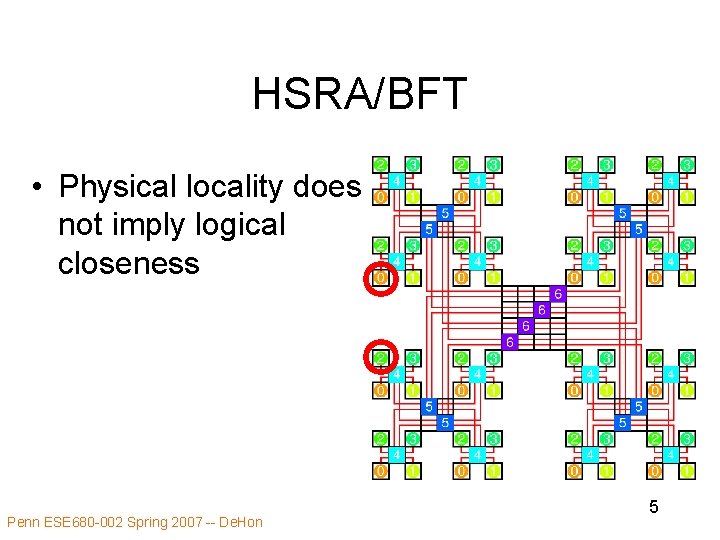

HSRA/BFT • Physical locality does not imply logical closeness Penn ESE 680 -002 Spring 2007 -- De. Hon 5

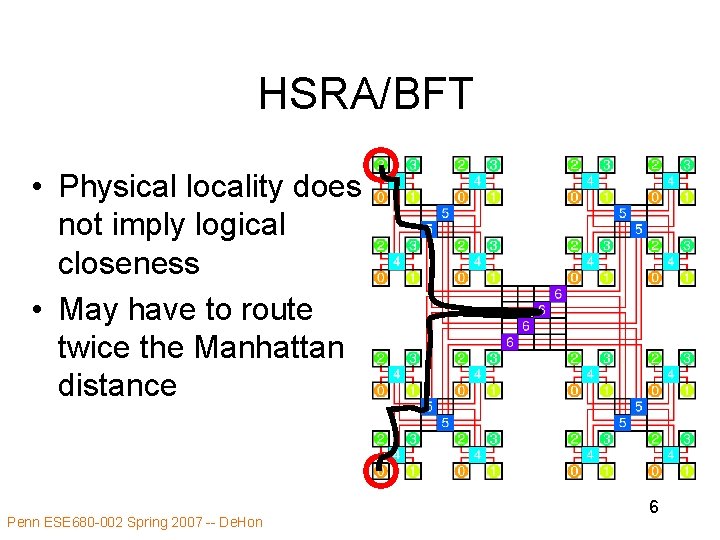

HSRA/BFT • Physical locality does not imply logical closeness • May have to route twice the Manhattan distance Penn ESE 680 -002 Spring 2007 -- De. Hon 6

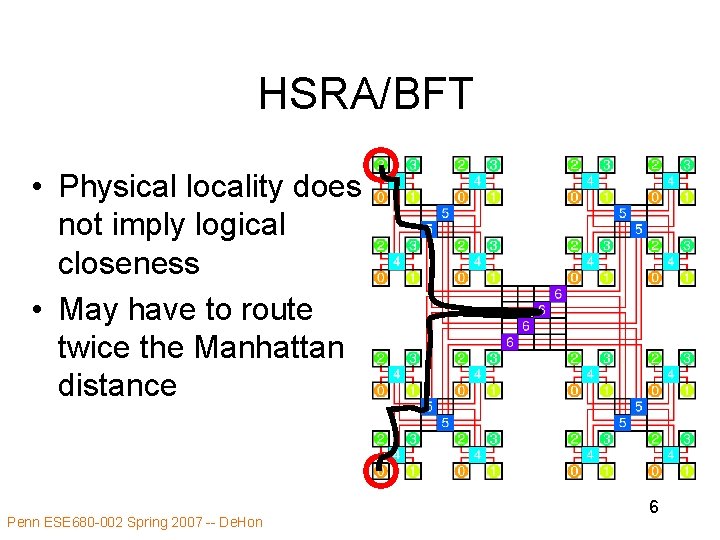

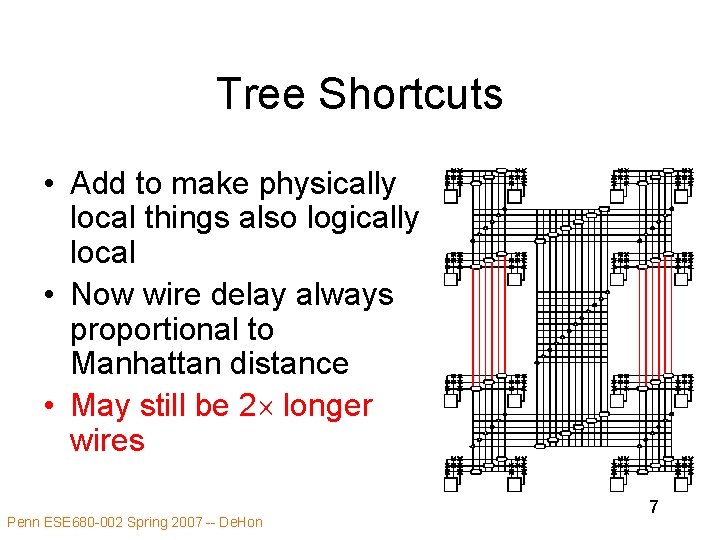

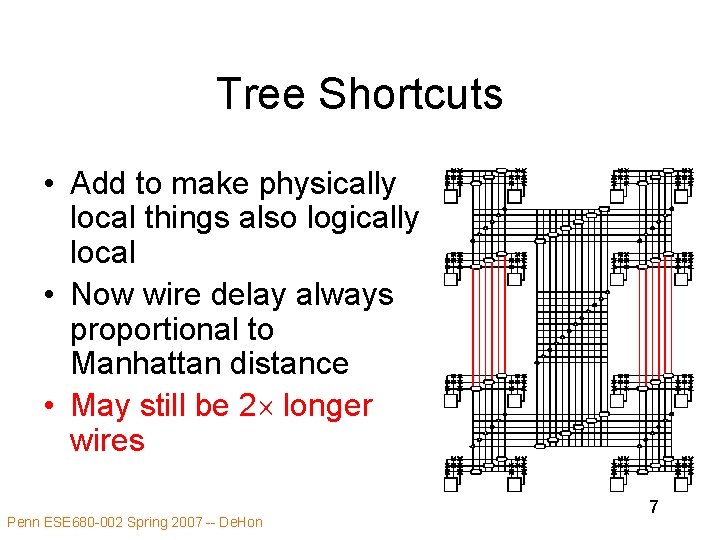

Tree Shortcuts • Add to make physically local things also logically local • Now wire delay always proportional to Manhattan distance • May still be 2 longer wires Penn ESE 680 -002 Spring 2007 -- De. Hon 7

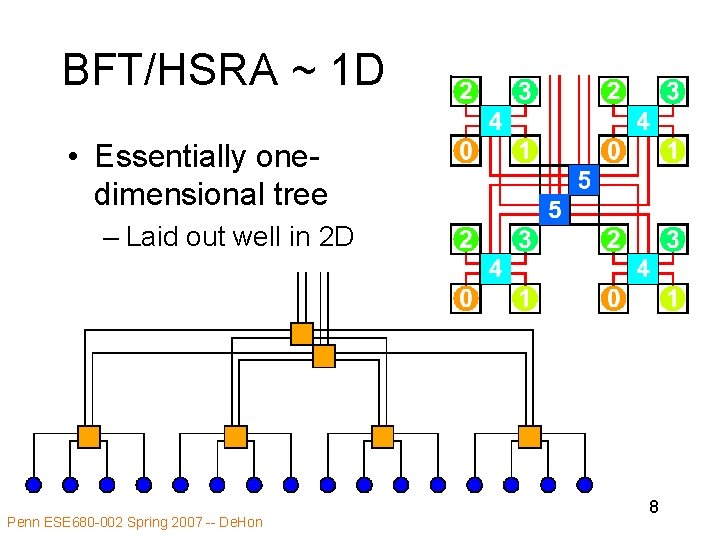

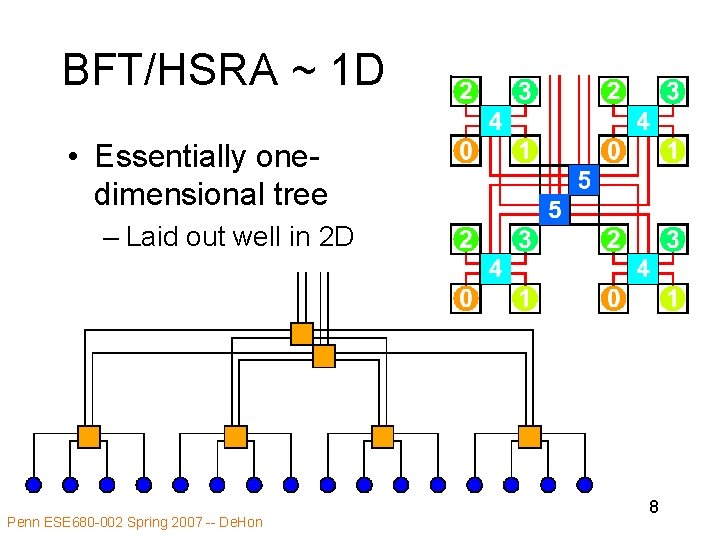

BFT/HSRA ~ 1 D • Essentially onedimensional tree – Laid out well in 2 D Penn ESE 680 -002 Spring 2007 -- De. Hon 8

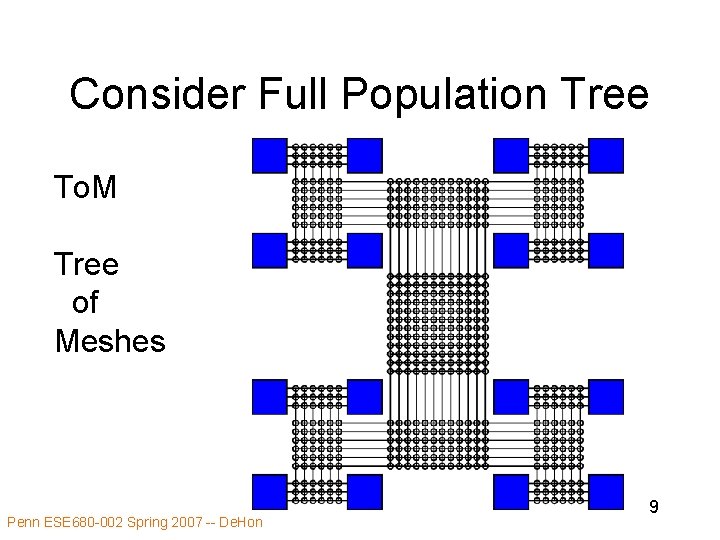

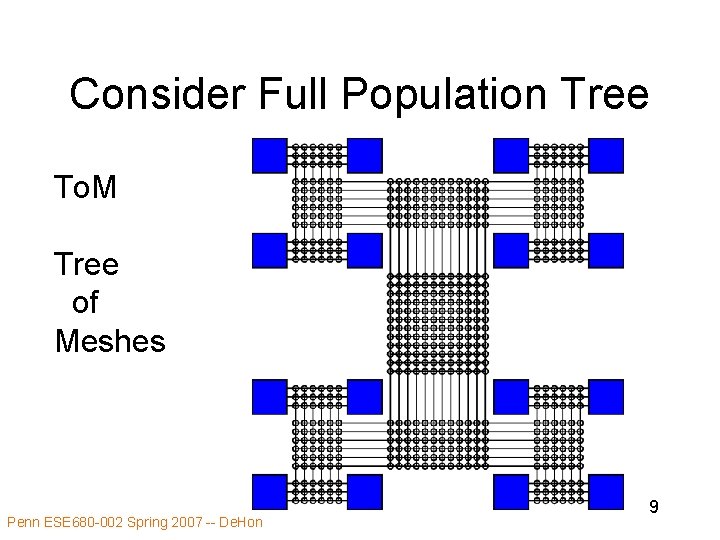

Consider Full Population Tree To. M Tree of Meshes Penn ESE 680 -002 Spring 2007 -- De. Hon 9

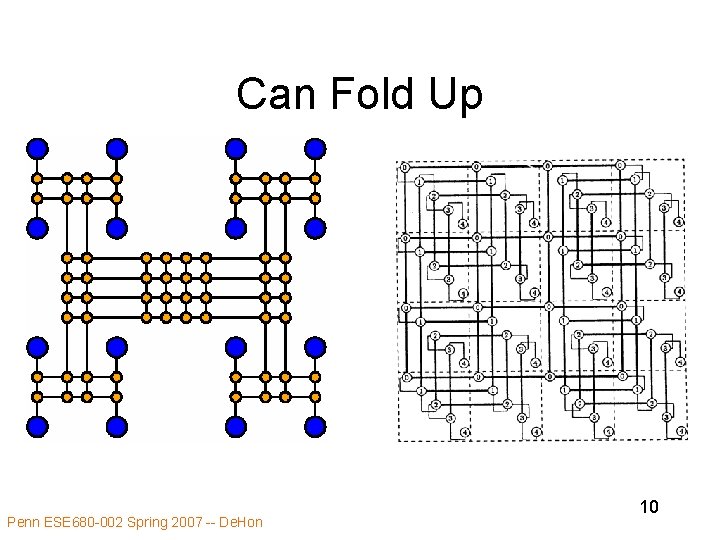

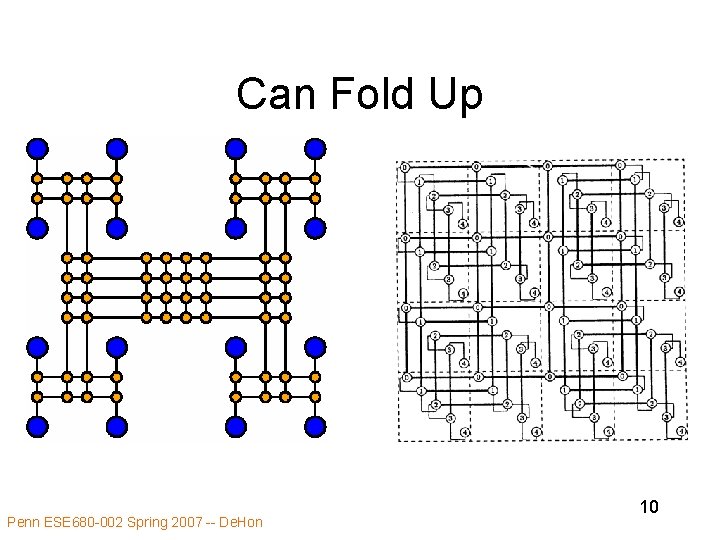

Can Fold Up Penn ESE 680 -002 Spring 2007 -- De. Hon 10

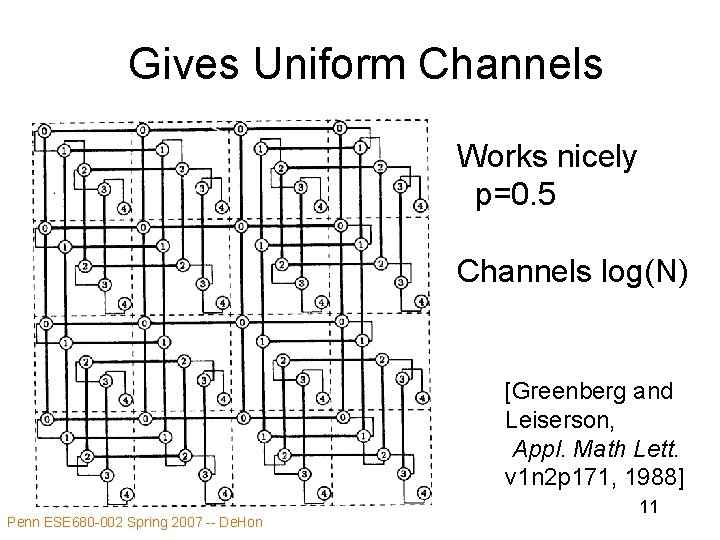

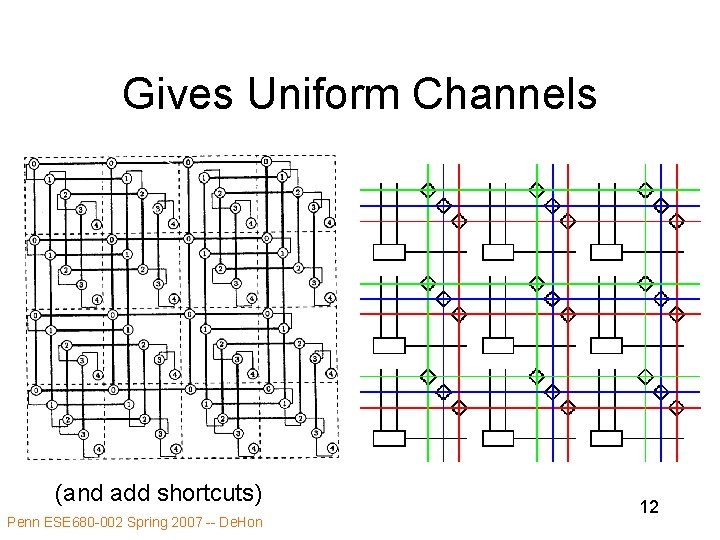

Gives Uniform Channels Works nicely p=0. 5 Channels log(N) [Greenberg and Leiserson, Appl. Math Lett. v 1 n 2 p 171, 1988] Penn ESE 680 -002 Spring 2007 -- De. Hon 11

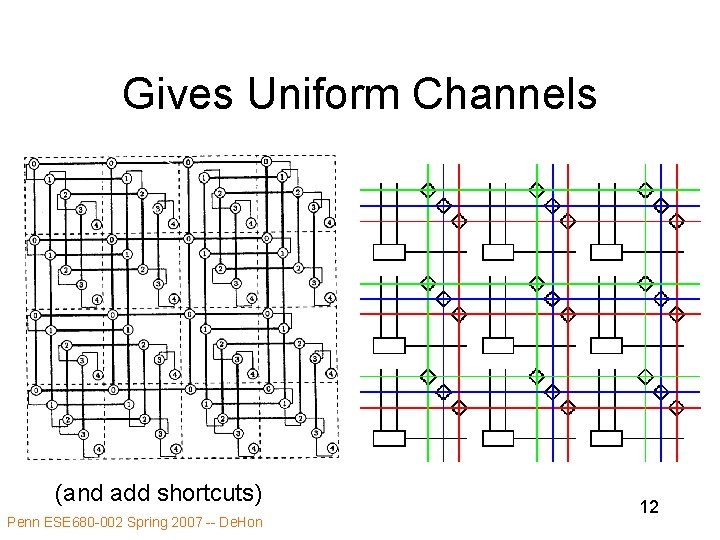

Gives Uniform Channels (and add shortcuts) Penn ESE 680 -002 Spring 2007 -- De. Hon 12

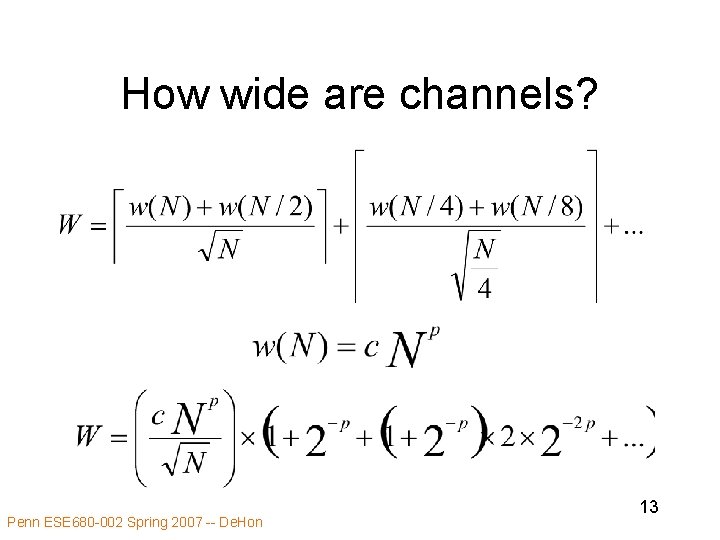

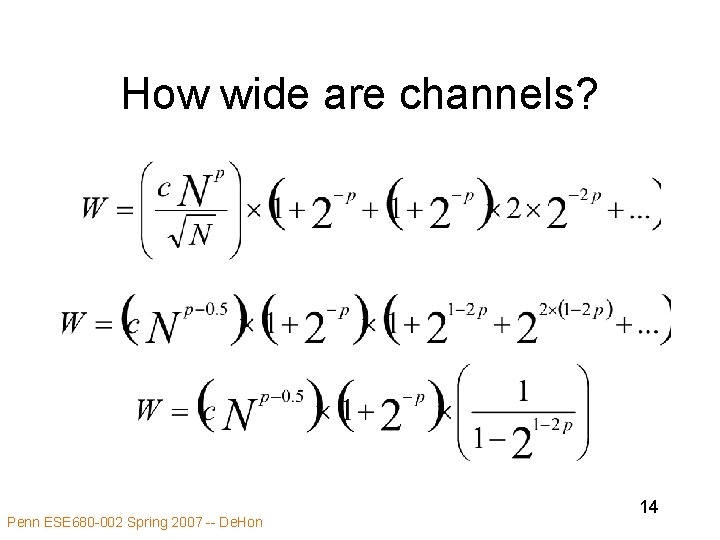

How wide are channels? Penn ESE 680 -002 Spring 2007 -- De. Hon 13

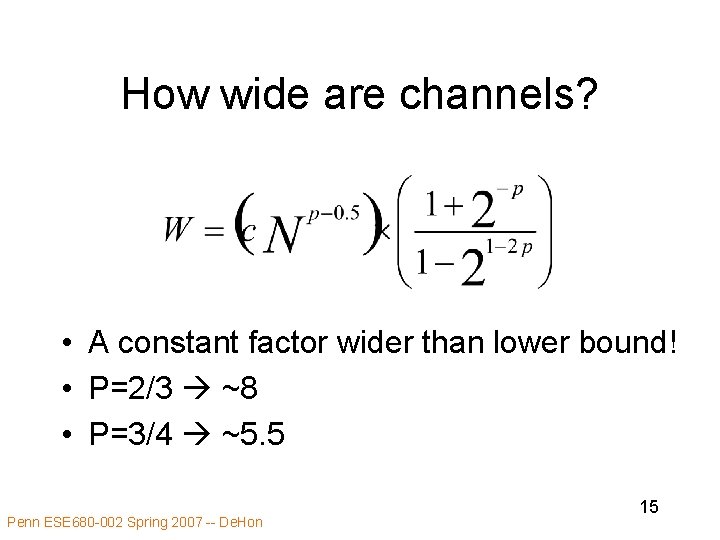

How wide are channels? Penn ESE 680 -002 Spring 2007 -- De. Hon 14

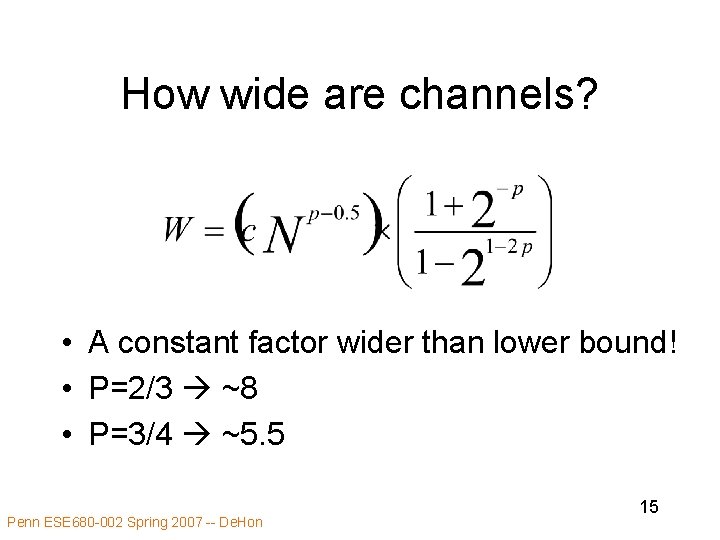

How wide are channels? • A constant factor wider than lower bound! • P=2/3 ~8 • P=3/4 ~5. 5 Penn ESE 680 -002 Spring 2007 -- De. Hon 15

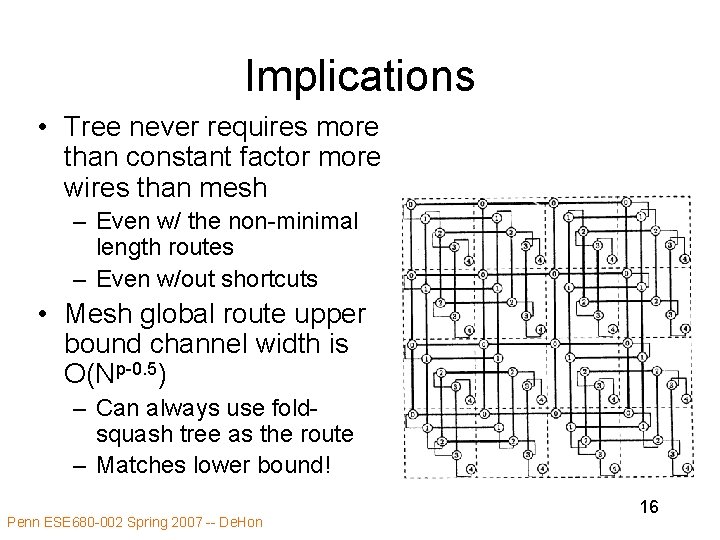

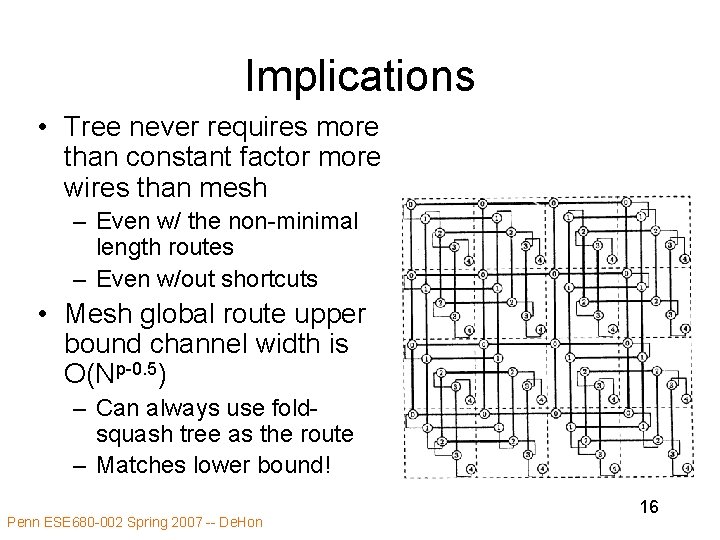

Implications • Tree never requires more than constant factor more wires than mesh – Even w/ the non-minimal length routes – Even w/out shortcuts • Mesh global route upper bound channel width is O(Np-0. 5) – Can always use foldsquash tree as the route – Matches lower bound! Penn ESE 680 -002 Spring 2007 -- De. Hon 16

Mo. T Penn ESE 680 -002 Spring 2007 -- De. Hon 17

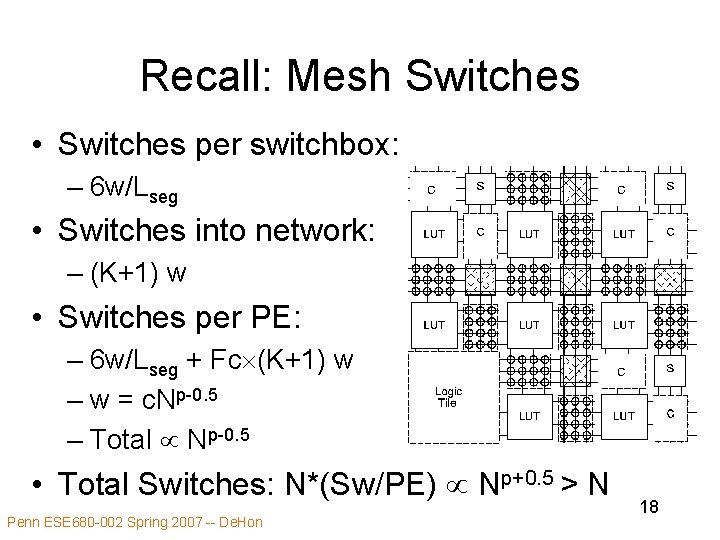

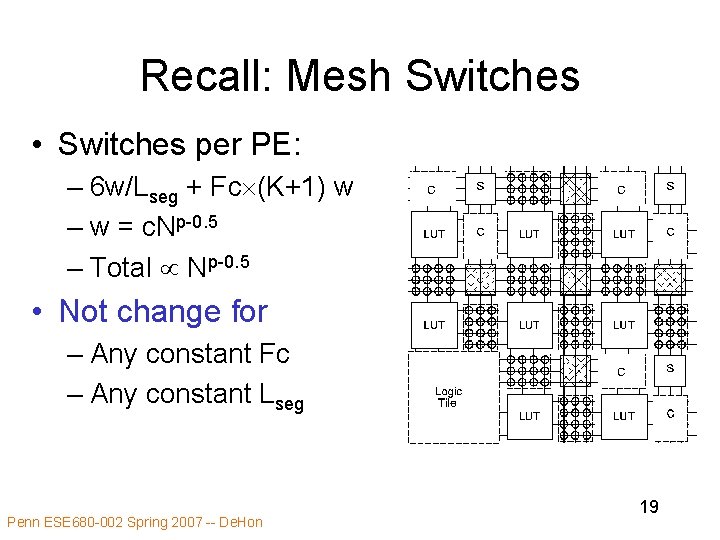

Recall: Mesh Switches • Switches per switchbox: – 6 w/Lseg • Switches into network: – (K+1) w • Switches per PE: – 6 w/Lseg + Fc (K+1) w – w = c. Np-0. 5 – Total Np-0. 5 • Total Switches: N*(Sw/PE) Np+0. 5 > N Penn ESE 680 -002 Spring 2007 -- De. Hon 18

Recall: Mesh Switches • Switches per PE: – 6 w/Lseg + Fc (K+1) w – w = c. Np-0. 5 – Total Np-0. 5 • Not change for – Any constant Fc – Any constant Lseg Penn ESE 680 -002 Spring 2007 -- De. Hon 19

![Mesh of Trees Hierarchical Mesh Build Tree in each column LeightonFOCS 1981 Mesh of Trees • Hierarchical Mesh • Build Tree in each column [Leighton/FOCS 1981]](https://slidetodoc.com/presentation_image_h2/b2abfea9b236cf6be34fe32ae713a261/image-20.jpg)

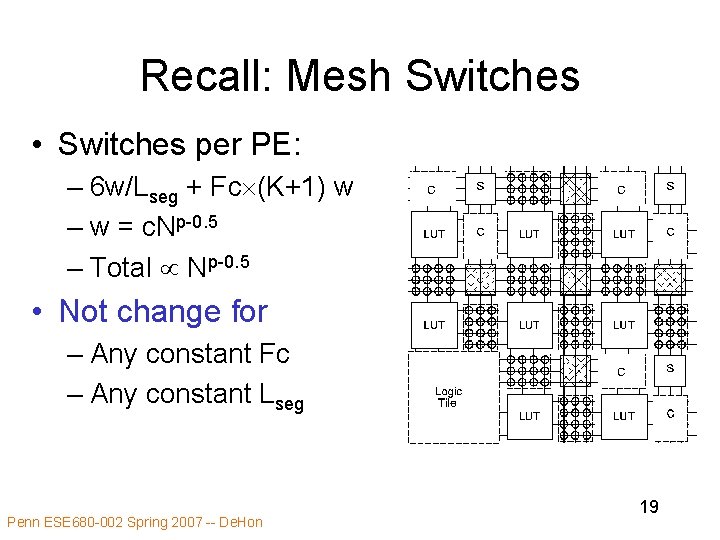

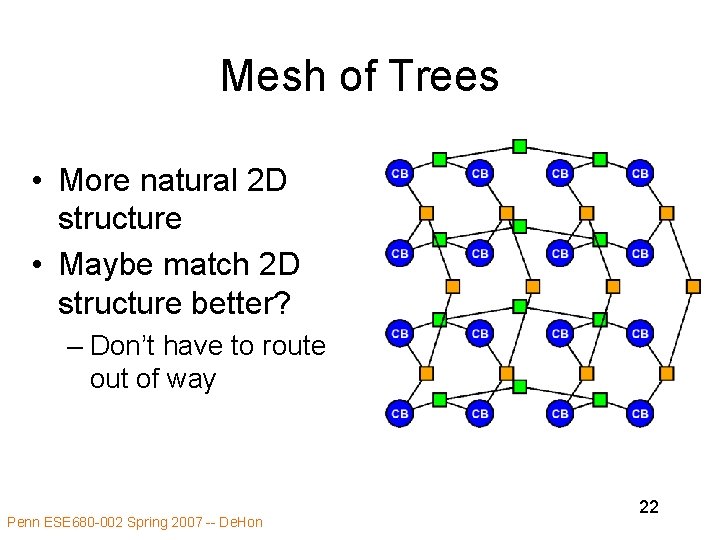

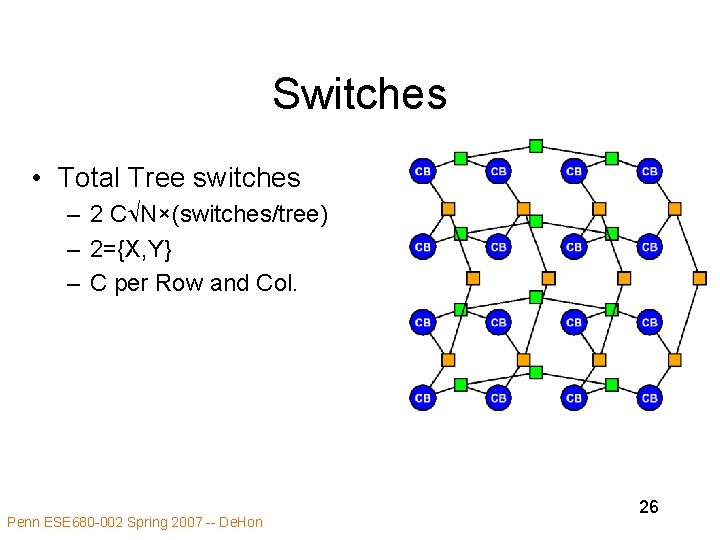

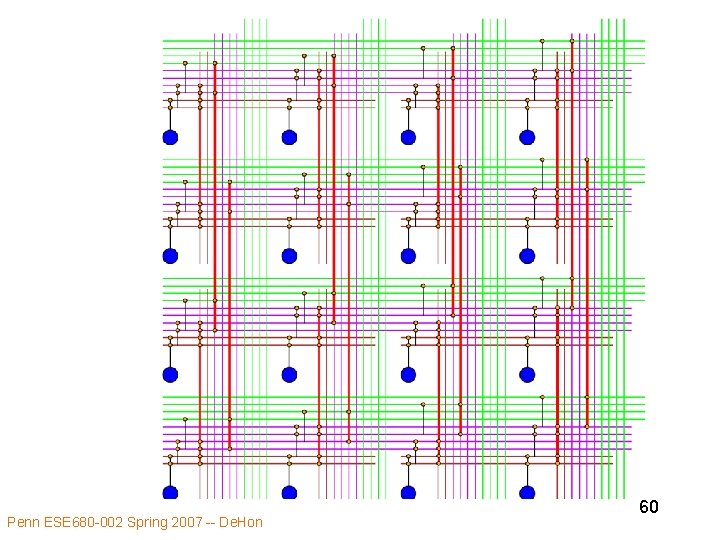

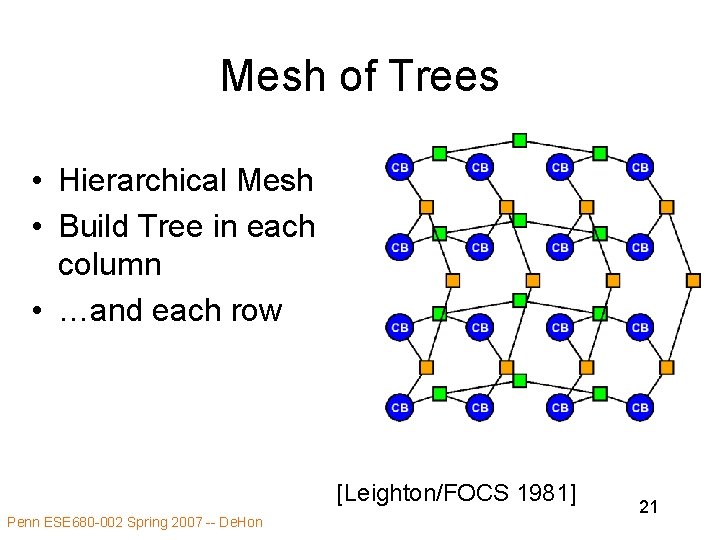

Mesh of Trees • Hierarchical Mesh • Build Tree in each column [Leighton/FOCS 1981] Penn ESE 680 -002 Spring 2007 -- De. Hon 20

Mesh of Trees • Hierarchical Mesh • Build Tree in each column • …and each row [Leighton/FOCS 1981] Penn ESE 680 -002 Spring 2007 -- De. Hon 21

Mesh of Trees • More natural 2 D structure • Maybe match 2 D structure better? – Don’t have to route out of way Penn ESE 680 -002 Spring 2007 -- De. Hon 22

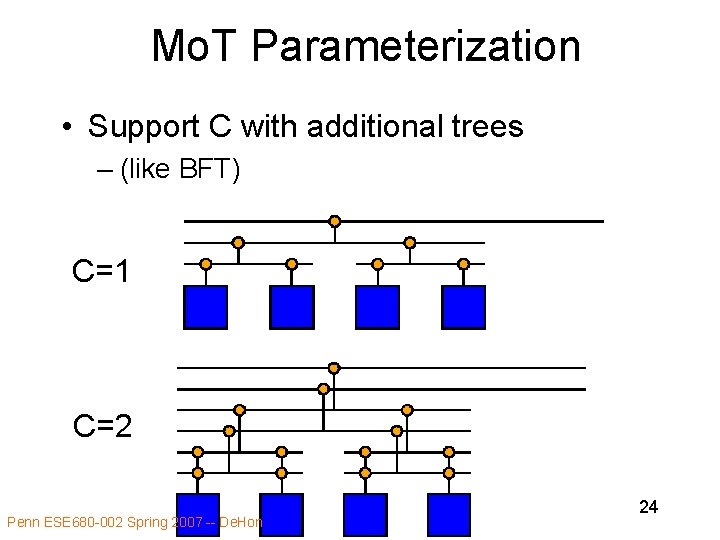

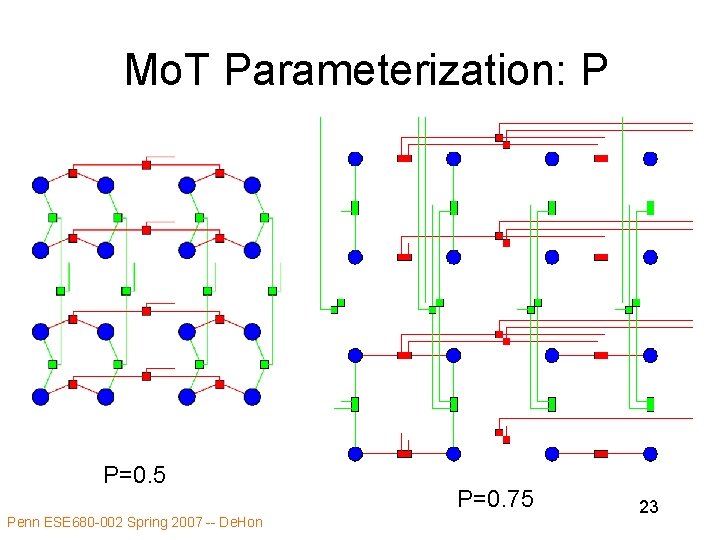

Mo. T Parameterization: P P=0. 5 Penn ESE 680 -002 Spring 2007 -- De. Hon P=0. 75 23

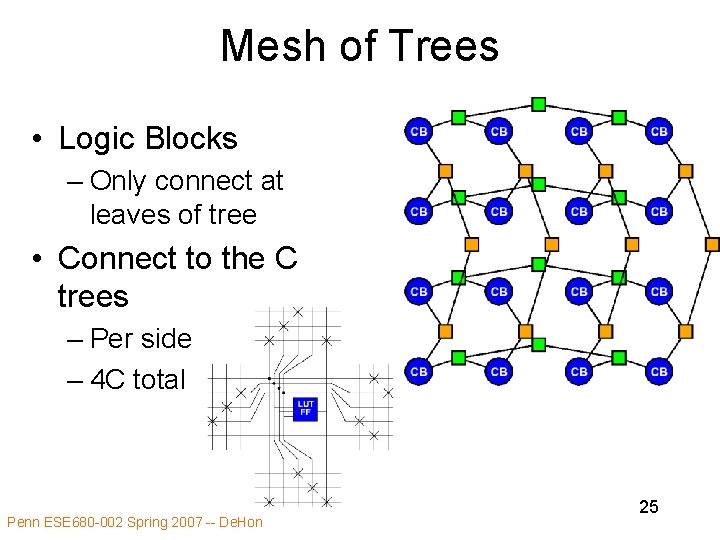

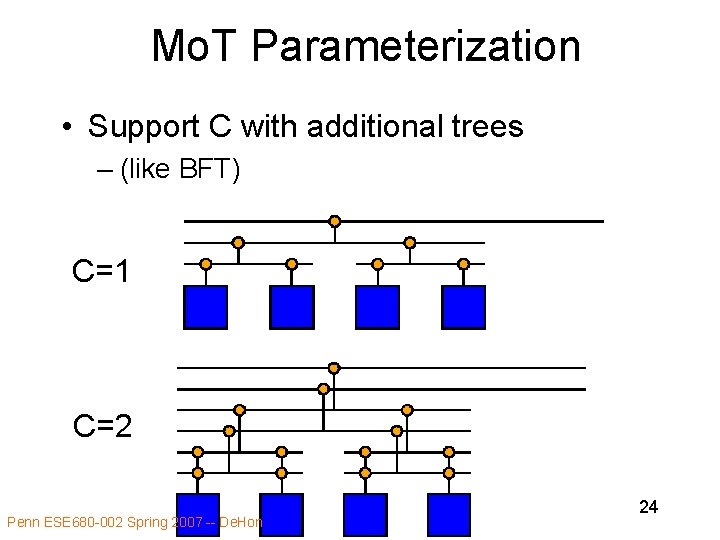

Mo. T Parameterization • Support C with additional trees – (like BFT) C=1 C=2 Penn ESE 680 -002 Spring 2007 -- De. Hon 24

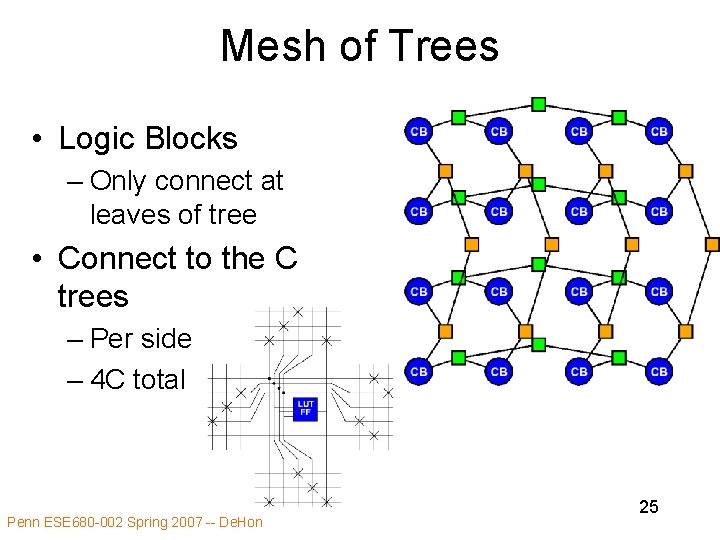

Mesh of Trees • Logic Blocks – Only connect at leaves of tree • Connect to the C trees – Per side – 4 C total Penn ESE 680 -002 Spring 2007 -- De. Hon 25

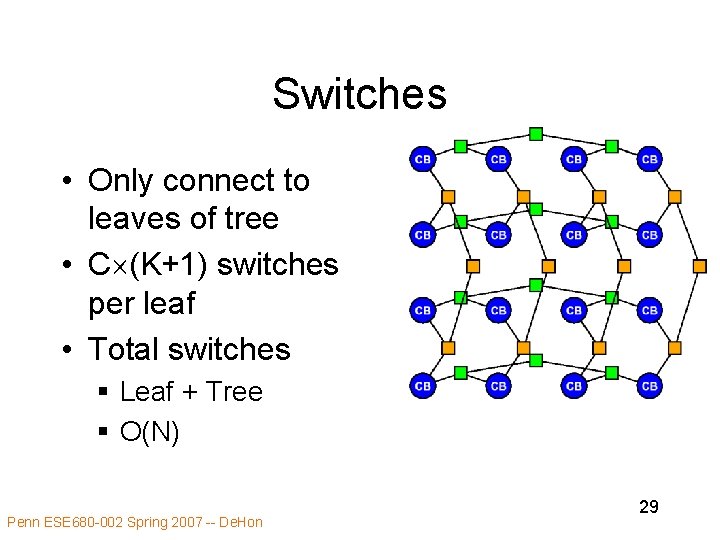

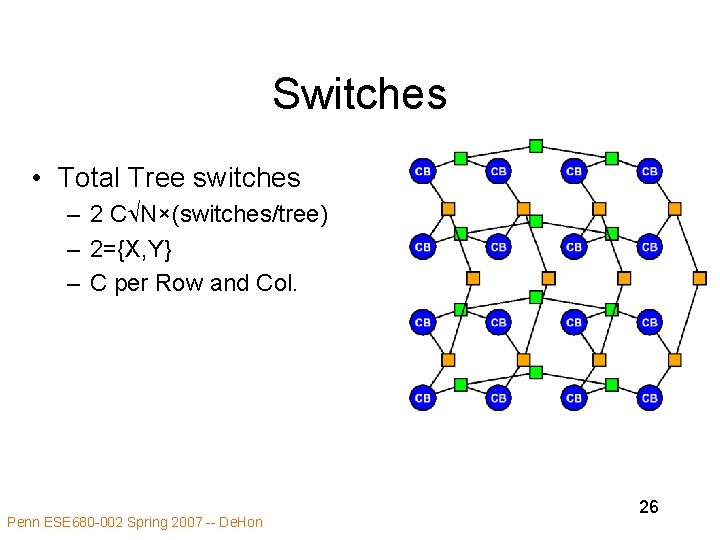

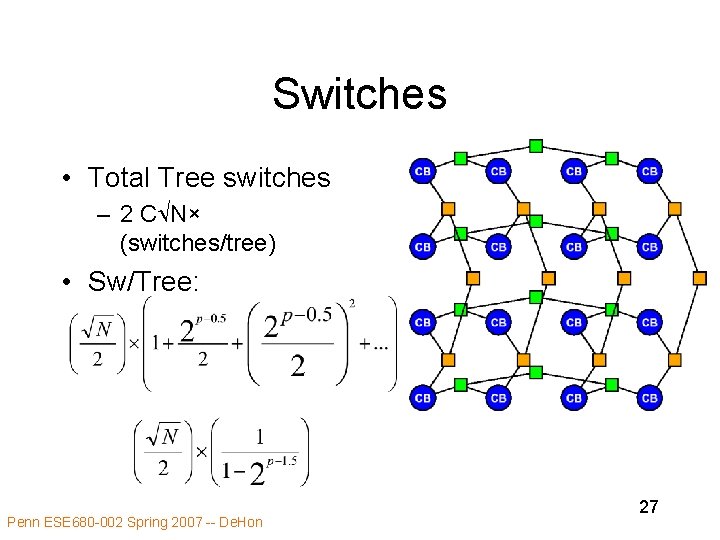

Switches • Total Tree switches – 2 C N×(switches/tree) – 2={X, Y} – C per Row and Col. Penn ESE 680 -002 Spring 2007 -- De. Hon 26

Switches • Total Tree switches – 2 C N× (switches/tree) • Sw/Tree: Penn ESE 680 -002 Spring 2007 -- De. Hon 27

Switches • Total Tree switches – 2 C N× (switches/tree) • Sw/Tree: Penn ESE 680 -002 Spring 2007 -- De. Hon 28

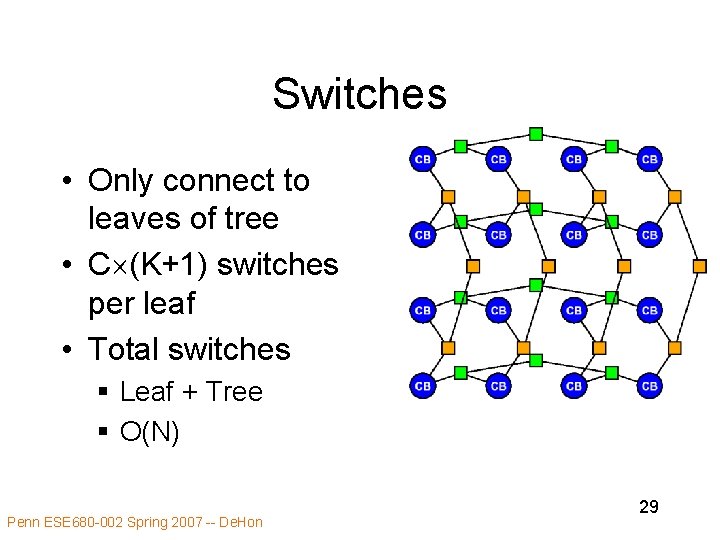

Switches • Only connect to leaves of tree • C (K+1) switches per leaf • Total switches § Leaf + Tree § O(N) Penn ESE 680 -002 Spring 2007 -- De. Hon 29

Wires • Design: O(Np) in top level • Total wire width of channels: O(Np) – Another geometric sum • No detail route guarantee (at present) – Likely amenable to expander design (Day 16) Penn ESE 680 -002 Spring 2007 -- De. Hon 30

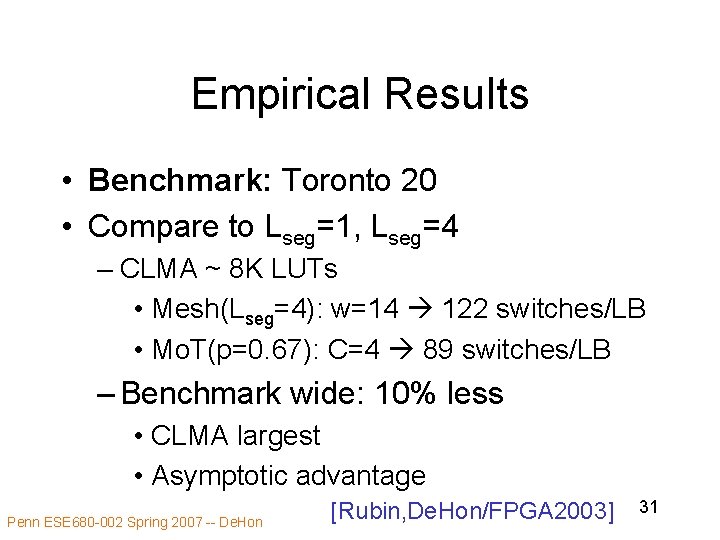

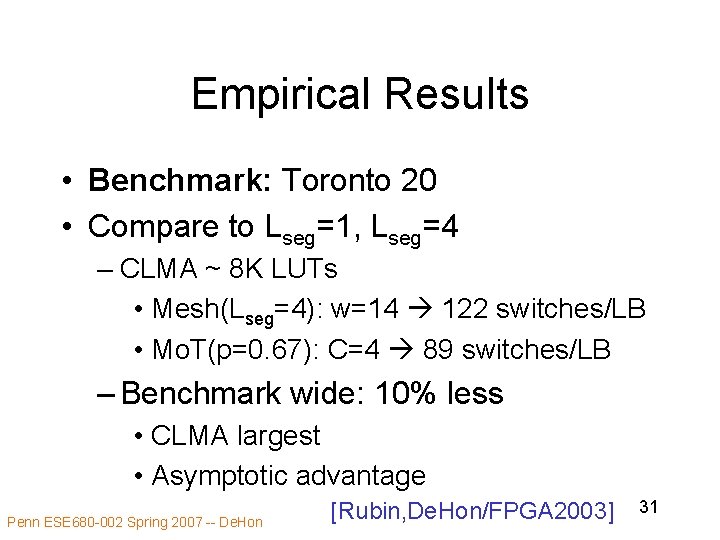

Empirical Results • Benchmark: Toronto 20 • Compare to Lseg=1, Lseg=4 – CLMA ~ 8 K LUTs • Mesh(Lseg=4): w=14 122 switches/LB • Mo. T(p=0. 67): C=4 89 switches/LB – Benchmark wide: 10% less • CLMA largest • Asymptotic advantage Penn ESE 680 -002 Spring 2007 -- De. Hon [Rubin, De. Hon/FPGA 2003] 31

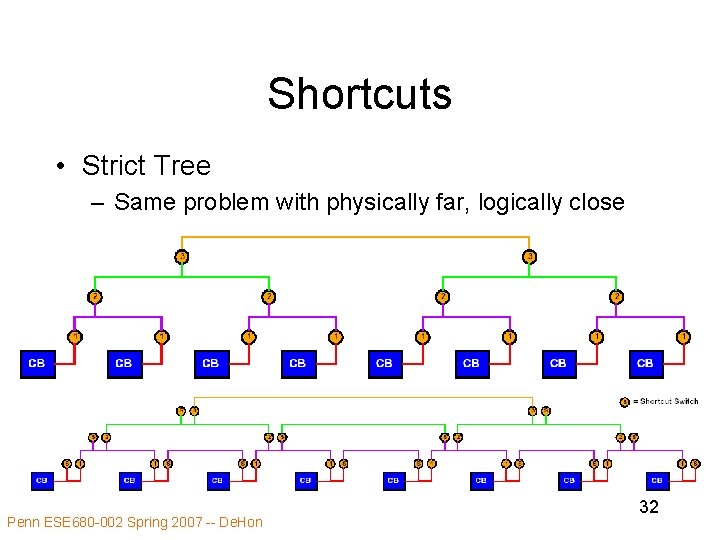

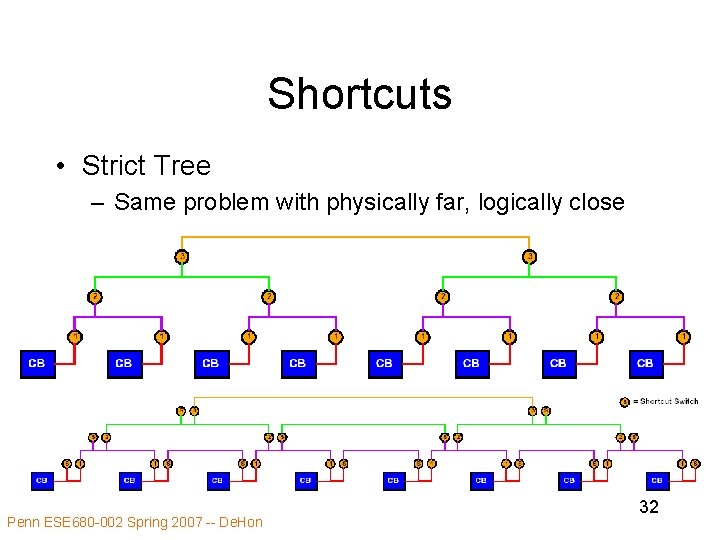

Shortcuts • Strict Tree – Same problem with physically far, logically close Penn ESE 680 -002 Spring 2007 -- De. Hon 32

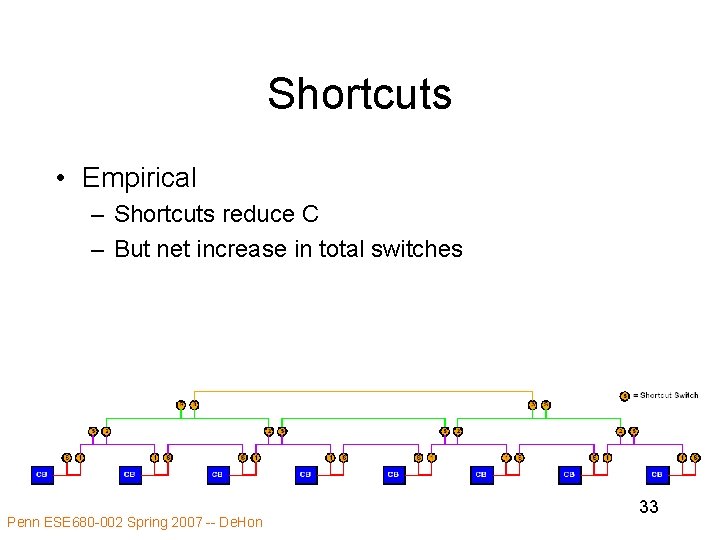

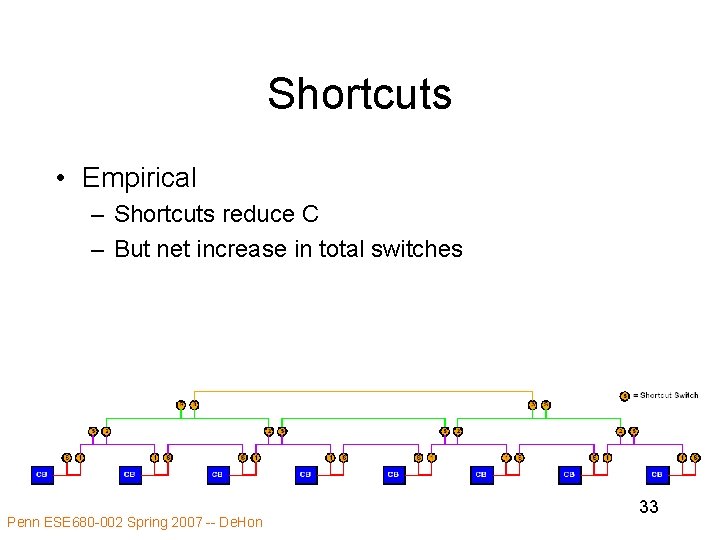

Shortcuts • Empirical – Shortcuts reduce C – But net increase in total switches Penn ESE 680 -002 Spring 2007 -- De. Hon 33

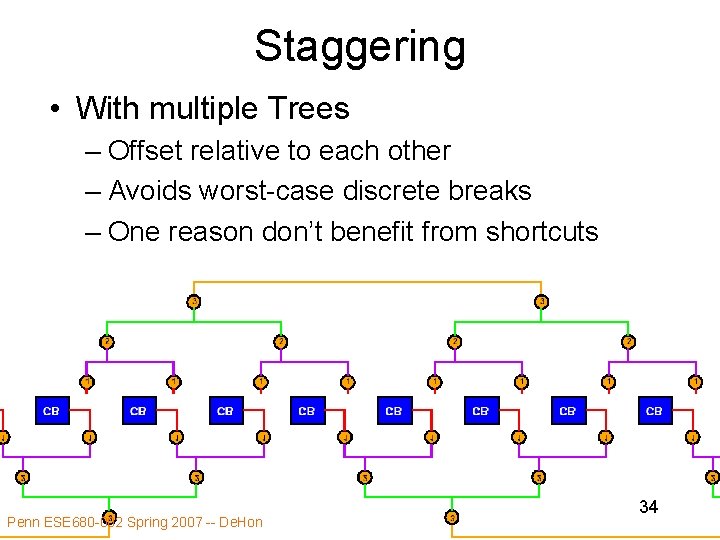

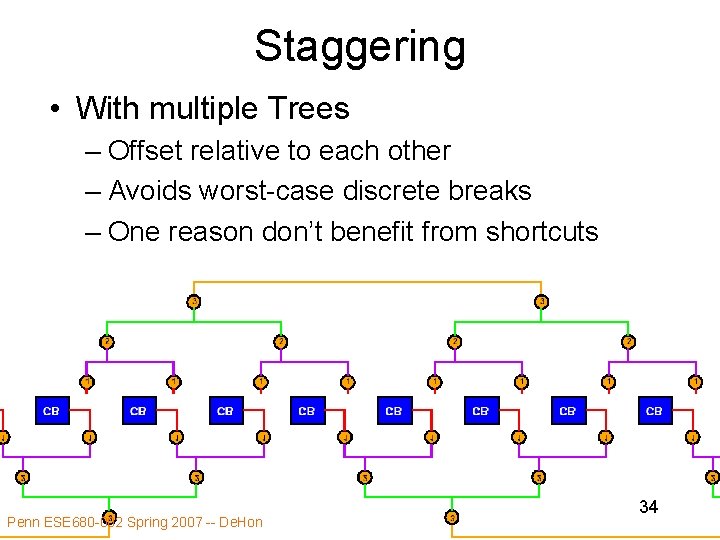

Staggering • With multiple Trees – Offset relative to each other – Avoids worst-case discrete breaks – One reason don’t benefit from shortcuts Penn ESE 680 -002 Spring 2007 -- De. Hon 34

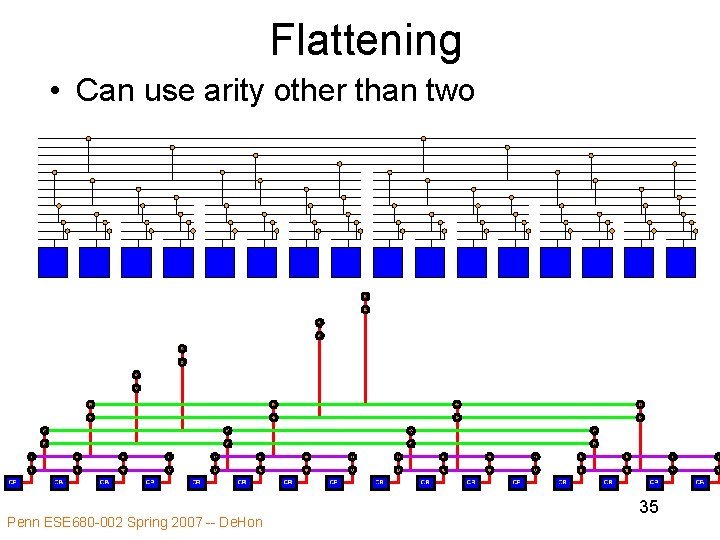

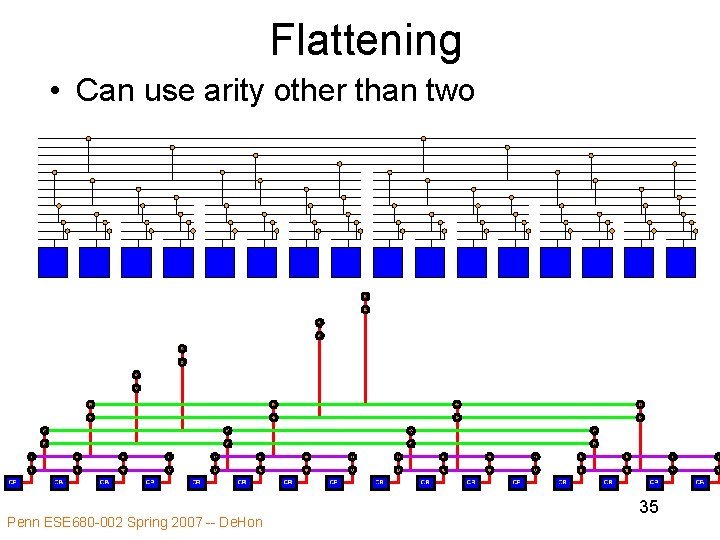

Flattening • Can use arity other than two Penn ESE 680 -002 Spring 2007 -- De. Hon 35

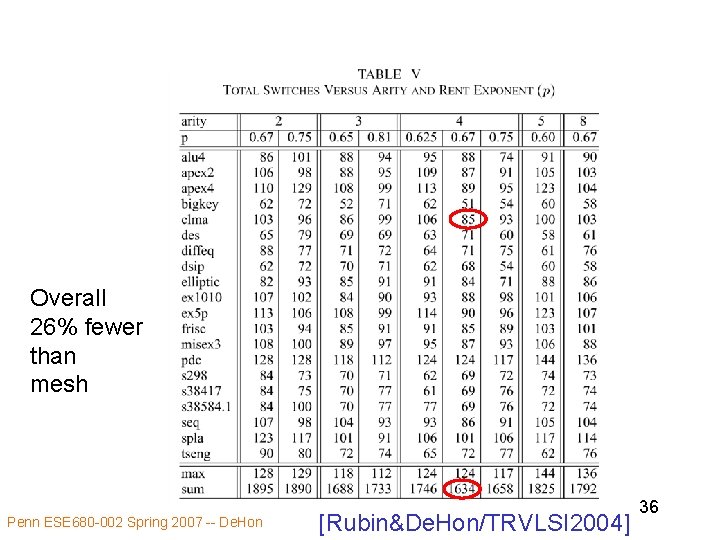

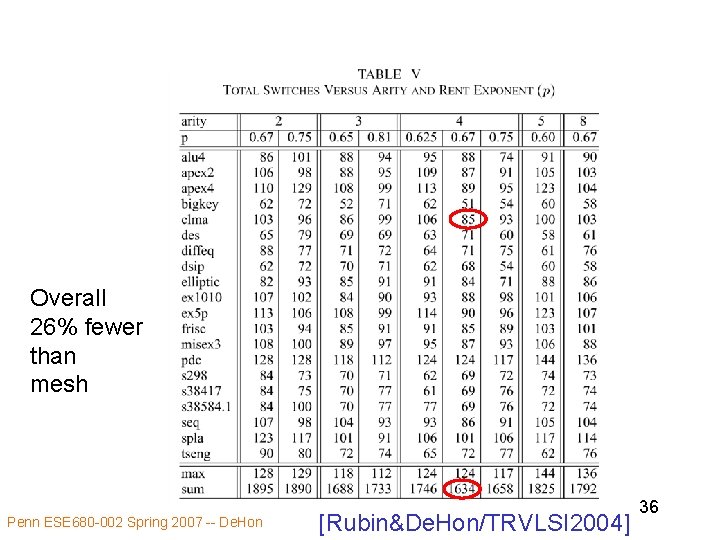

Overall 26% fewer than mesh Penn ESE 680 -002 Spring 2007 -- De. Hon [Rubin&De. Hon/TRVLSI 2004] 36

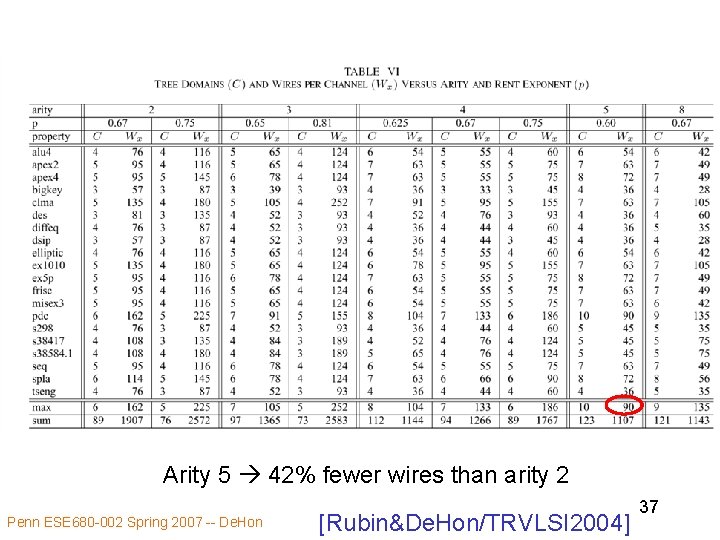

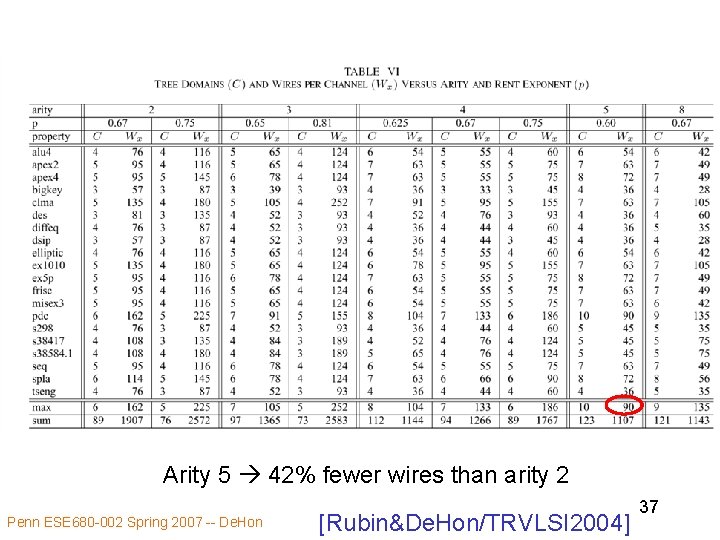

Arity 5 42% fewer wires than arity 2 Penn ESE 680 -002 Spring 2007 -- De. Hon [Rubin&De. Hon/TRVLSI 2004] 37

Mo. T Parameters • • Shortcuts Staggering Corner Turns – to come Arity Penn ESE 680 -002 Spring 2007 -- De. Hon 38

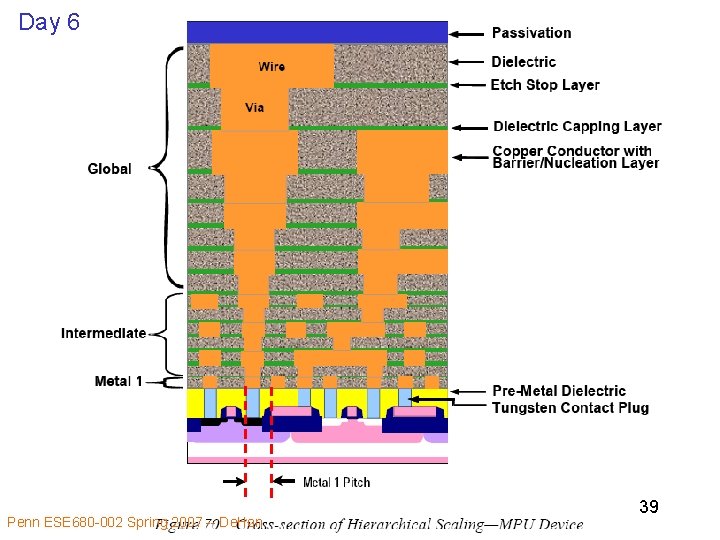

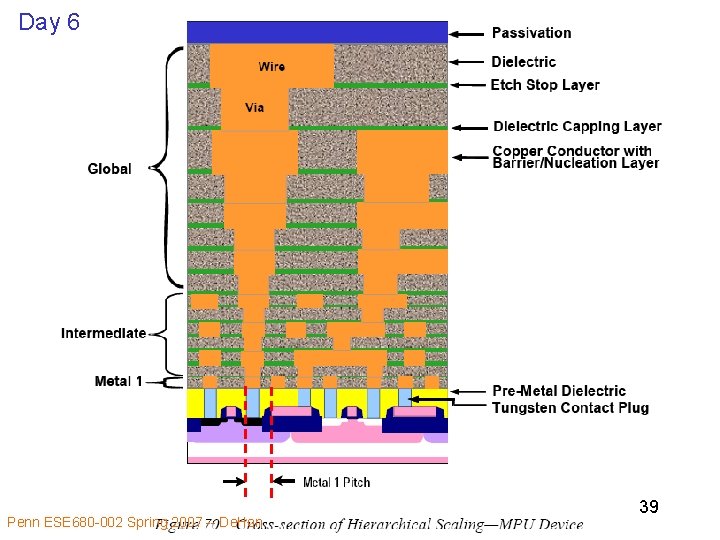

Day 6 Penn ESE 680 -002 Spring 2007 -- De. Hon 39

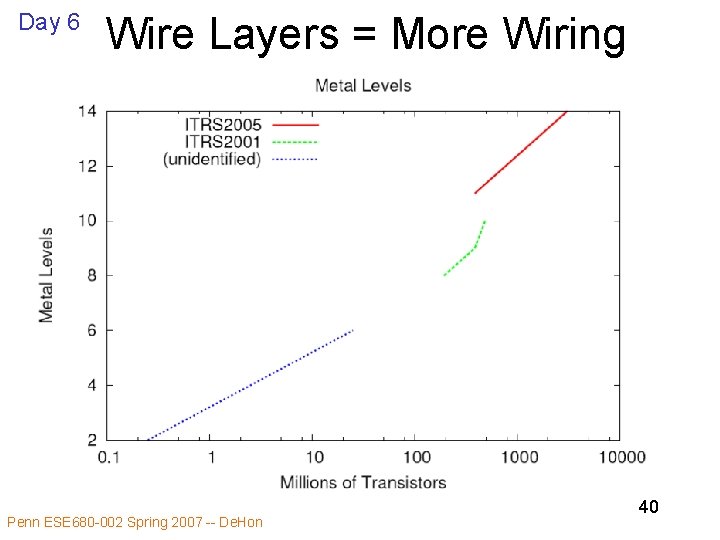

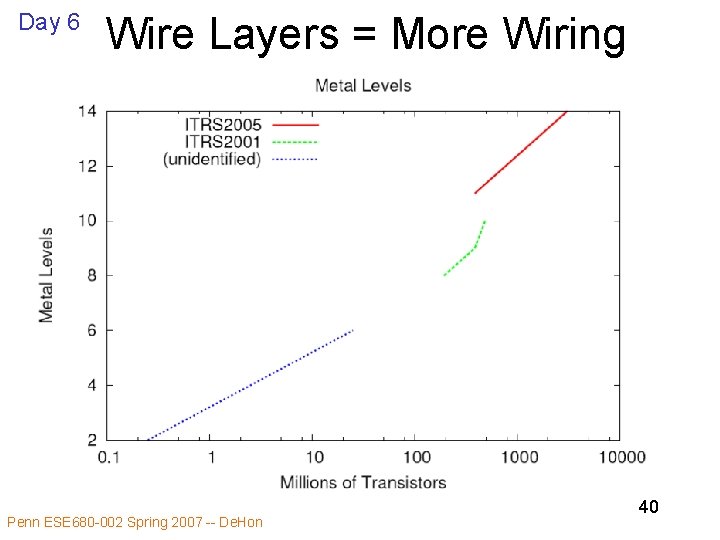

Day 6 Wire Layers = More Wiring Penn ESE 680 -002 Spring 2007 -- De. Hon 40

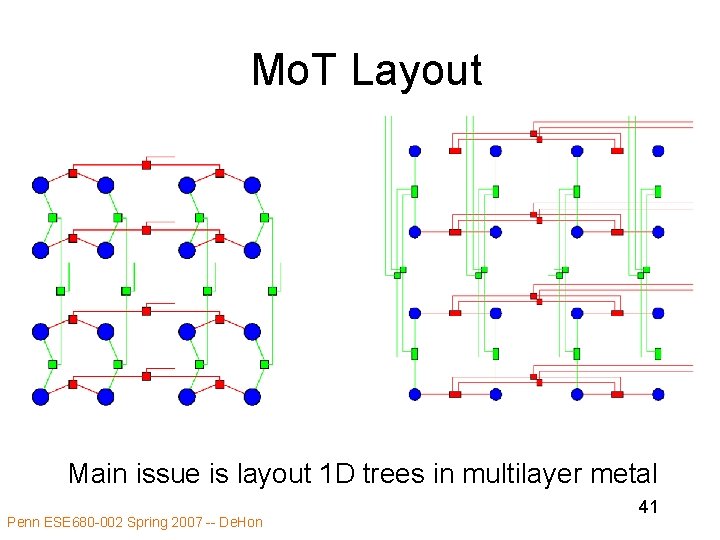

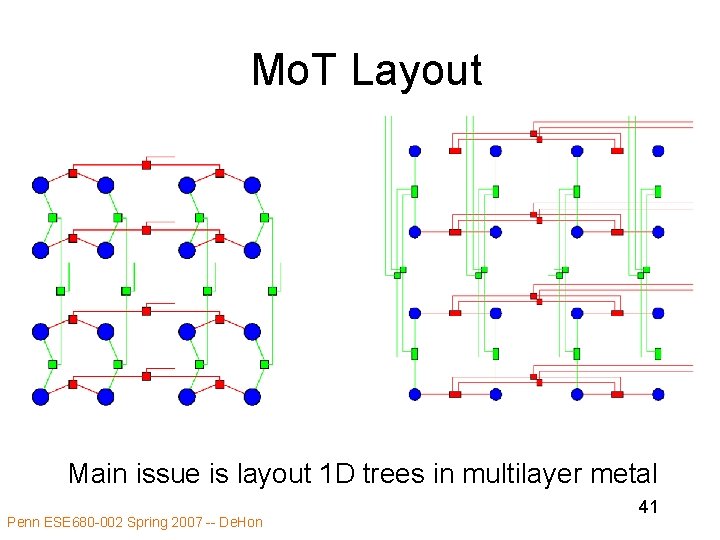

Mo. T Layout Main issue is layout 1 D trees in multilayer metal Penn ESE 680 -002 Spring 2007 -- De. Hon 41

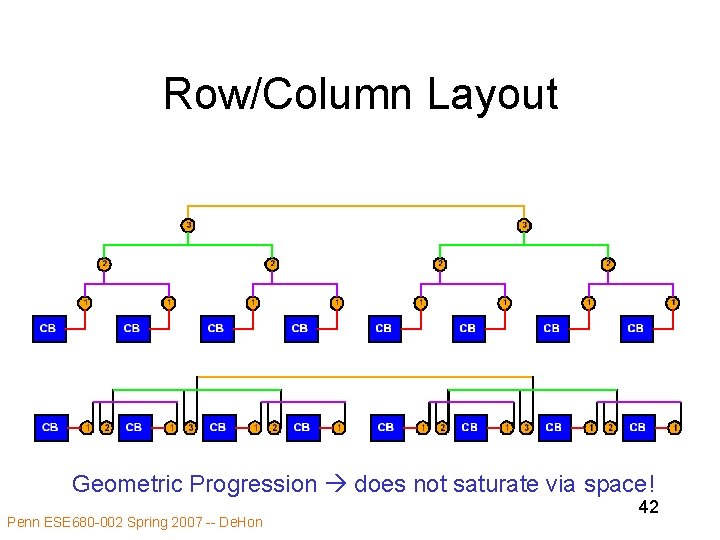

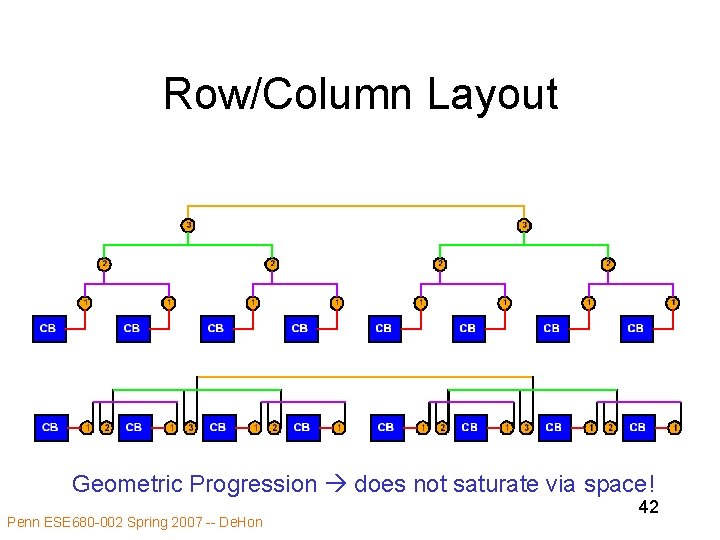

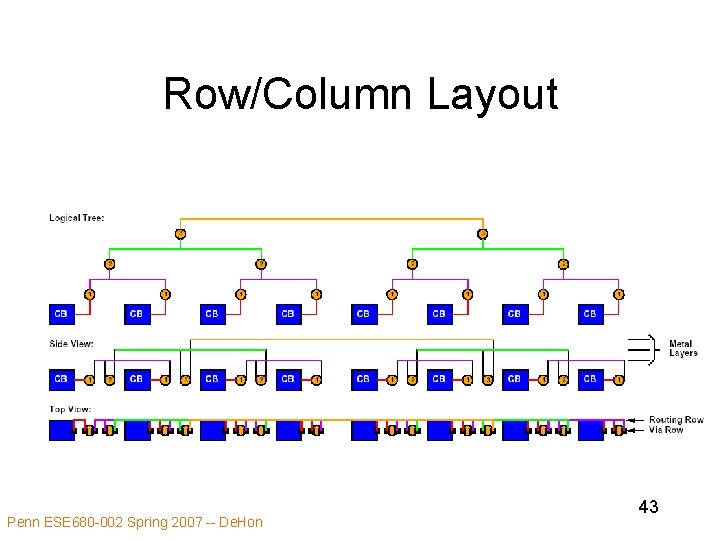

Row/Column Layout Geometric Progression does not saturate via space! Penn ESE 680 -002 Spring 2007 -- De. Hon 42

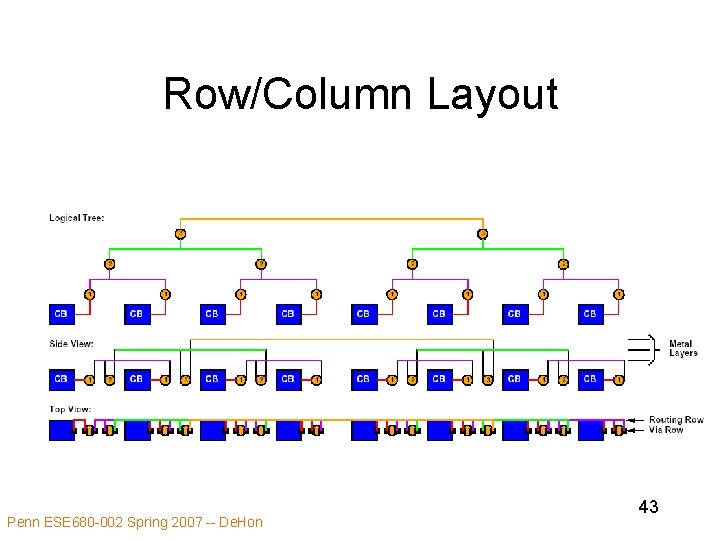

Row/Column Layout Penn ESE 680 -002 Spring 2007 -- De. Hon 43

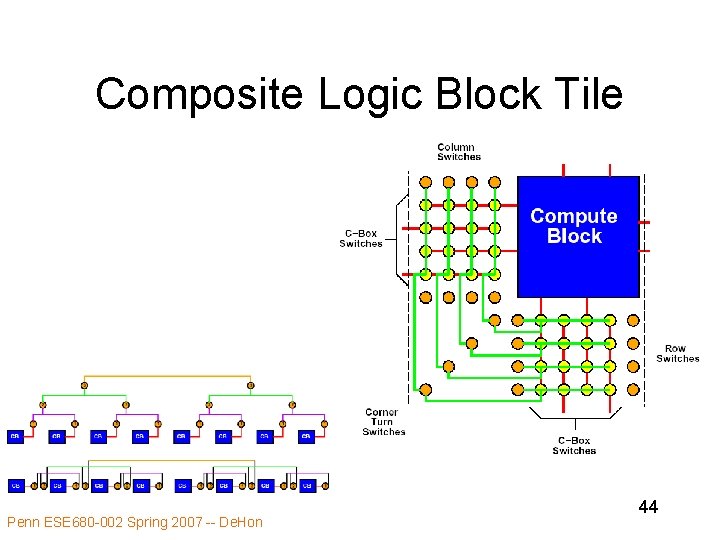

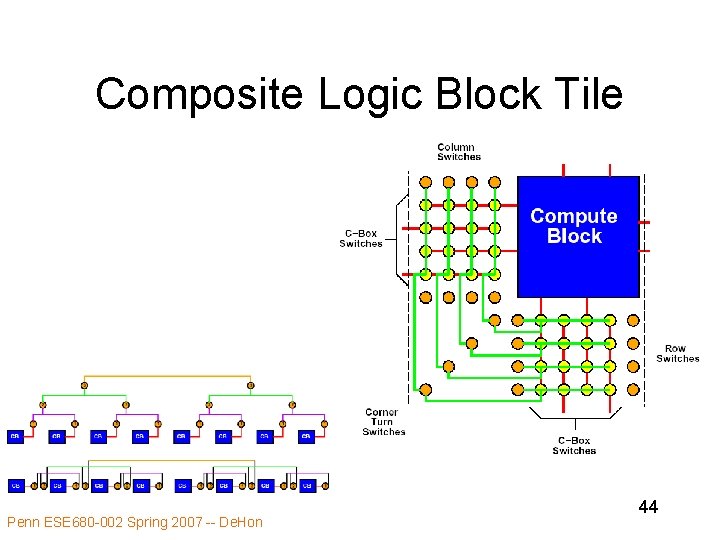

Composite Logic Block Tile Penn ESE 680 -002 Spring 2007 -- De. Hon 44

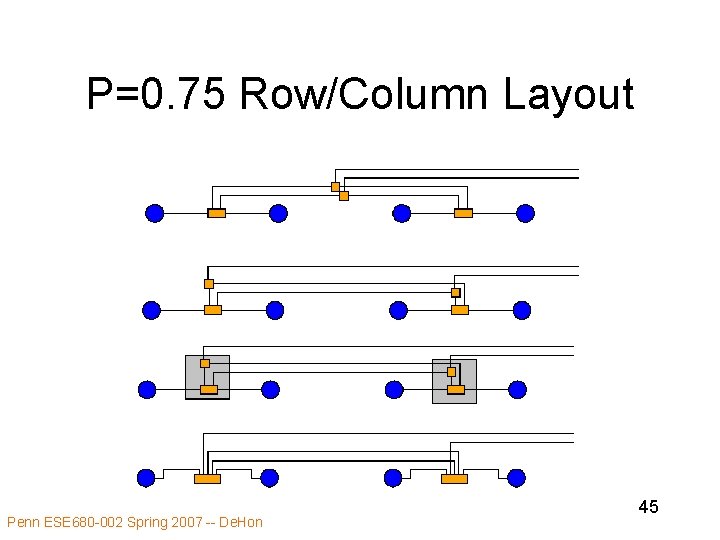

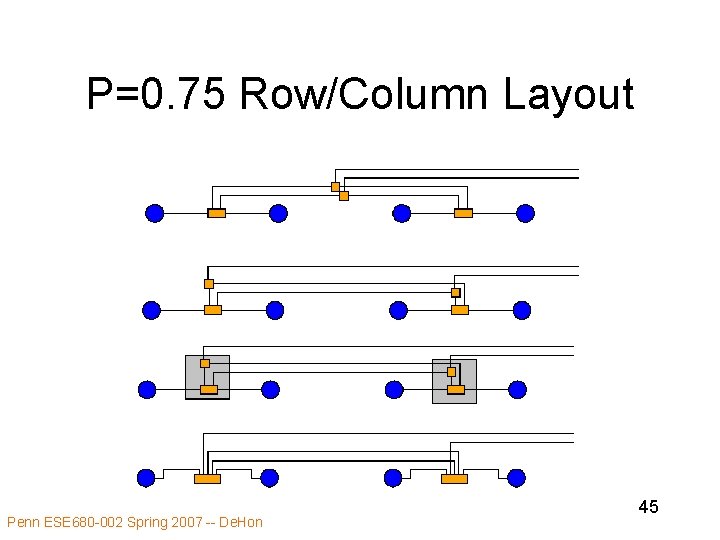

P=0. 75 Row/Column Layout Penn ESE 680 -002 Spring 2007 -- De. Hon 45

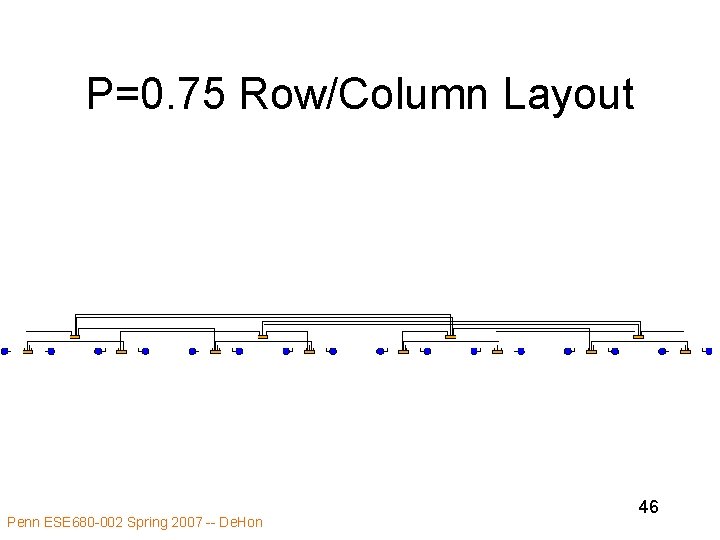

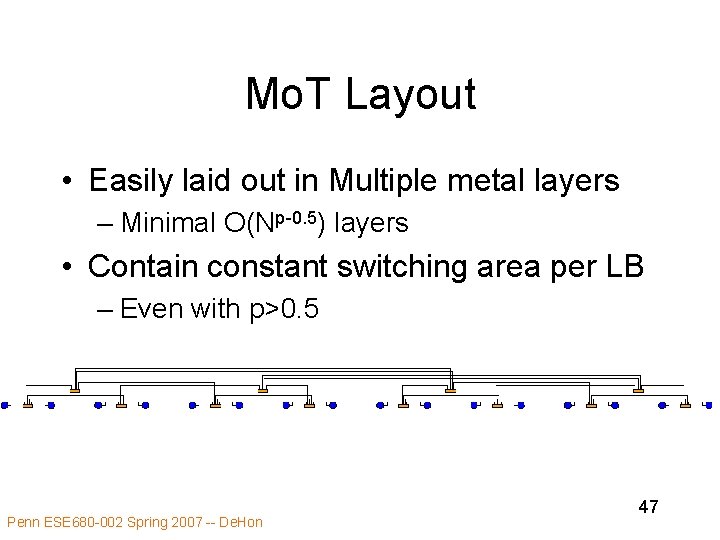

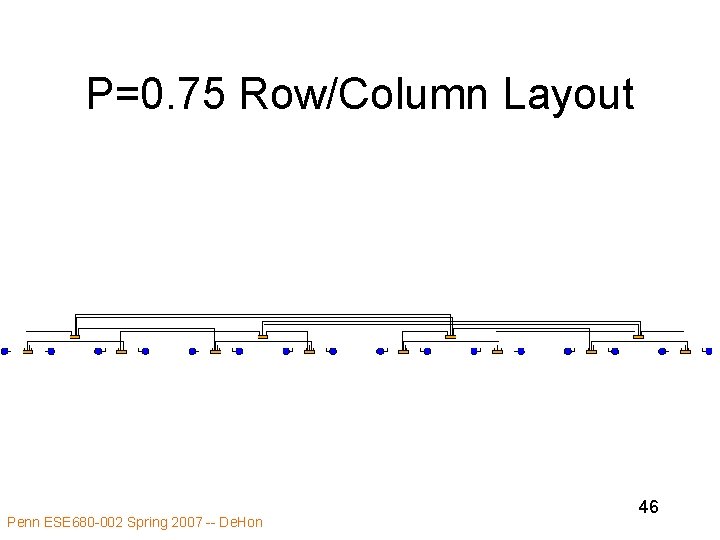

P=0. 75 Row/Column Layout Penn ESE 680 -002 Spring 2007 -- De. Hon 46

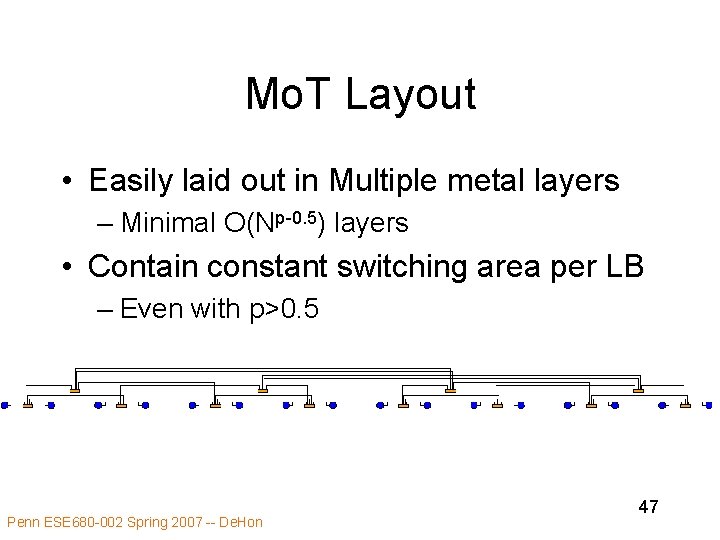

Mo. T Layout • Easily laid out in Multiple metal layers – Minimal O(Np-0. 5) layers • Contain constant switching area per LB – Even with p>0. 5 Penn ESE 680 -002 Spring 2007 -- De. Hon 47

Relation? Penn ESE 680 -002 Spring 2007 -- De. Hon 48

How Related? • What lessons translate amongst networks? • Once understand design space – Get closer together • Ideally – One big network design we can parameterize Penn ESE 680 -002 Spring 2007 -- De. Hon 49

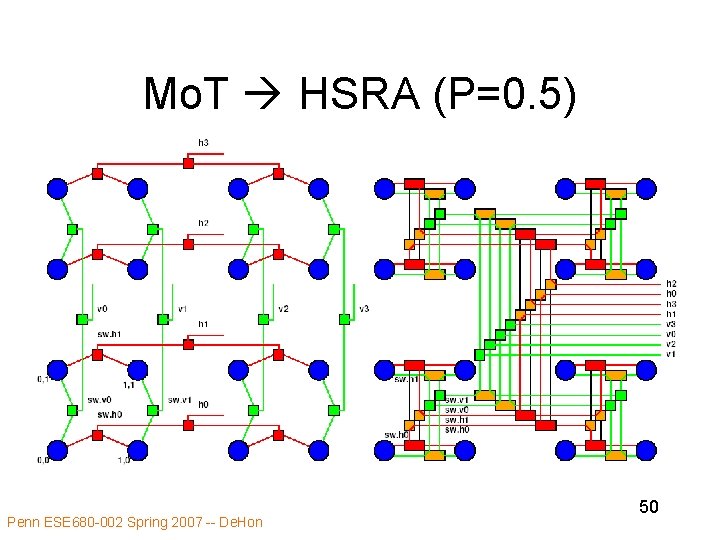

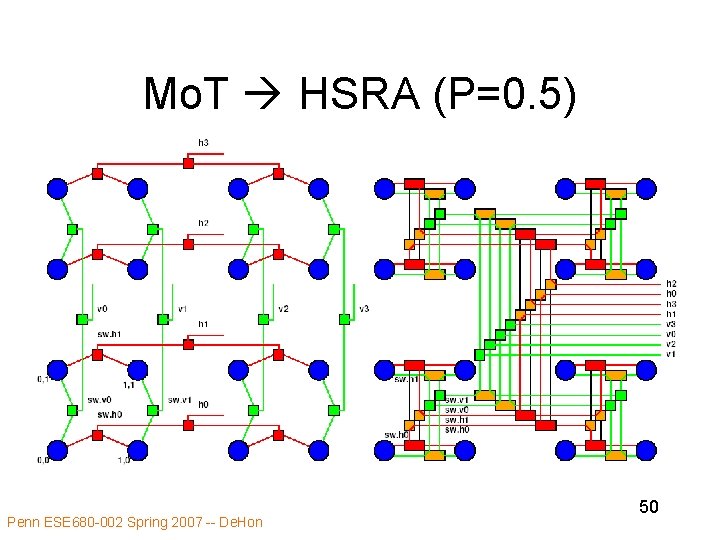

Mo. T HSRA (P=0. 5) Penn ESE 680 -002 Spring 2007 -- De. Hon 50

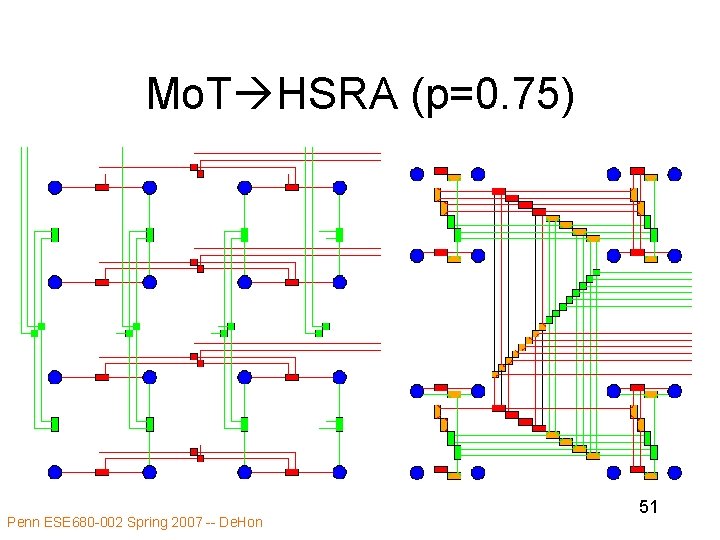

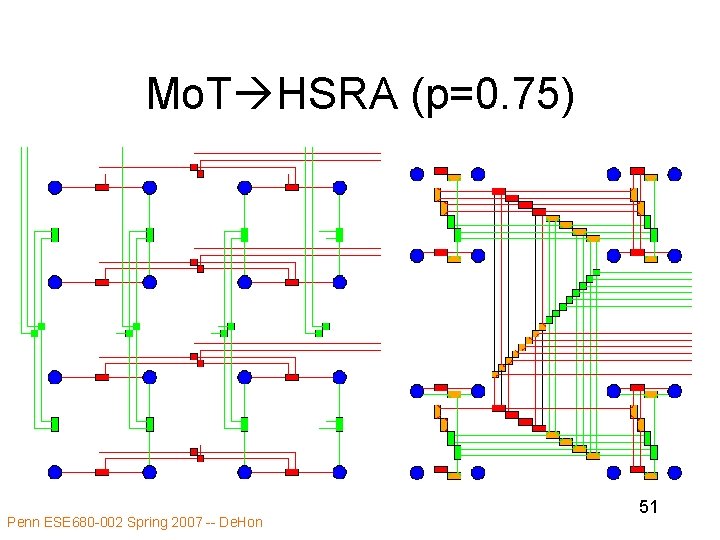

Mo. T HSRA (p=0. 75) Penn ESE 680 -002 Spring 2007 -- De. Hon 51

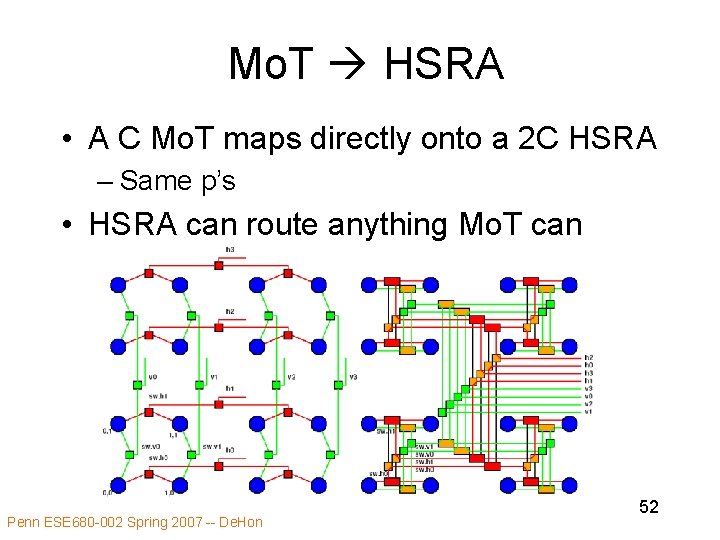

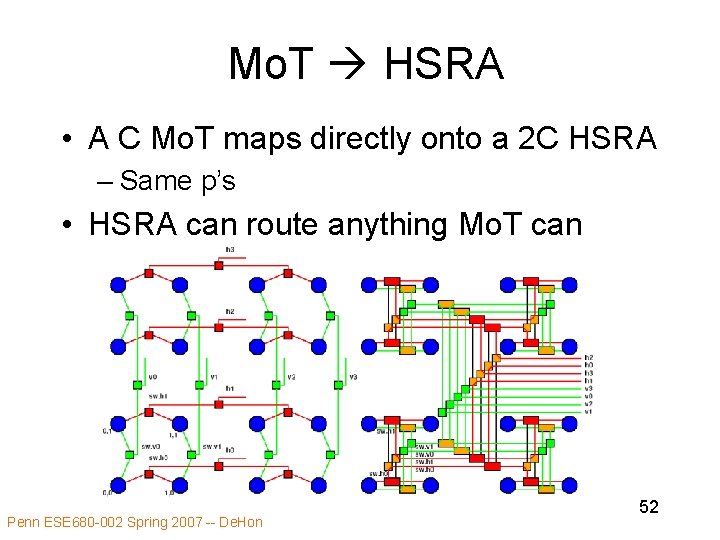

Mo. T HSRA • A C Mo. T maps directly onto a 2 C HSRA – Same p’s • HSRA can route anything Mo. T can Penn ESE 680 -002 Spring 2007 -- De. Hon 52

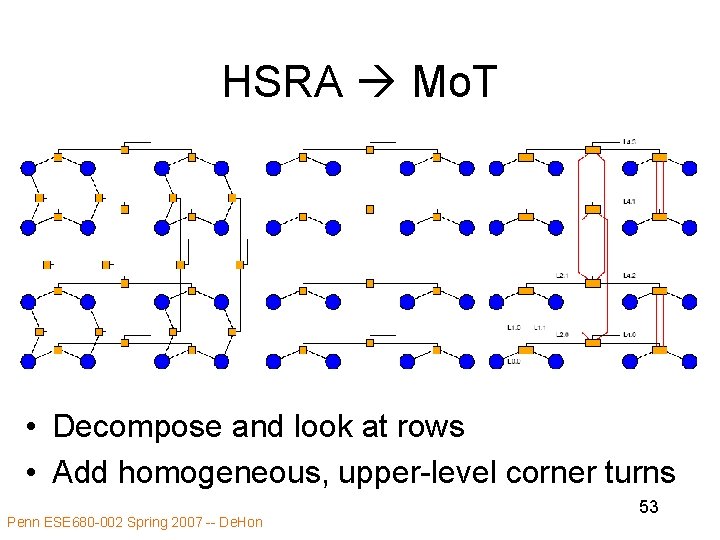

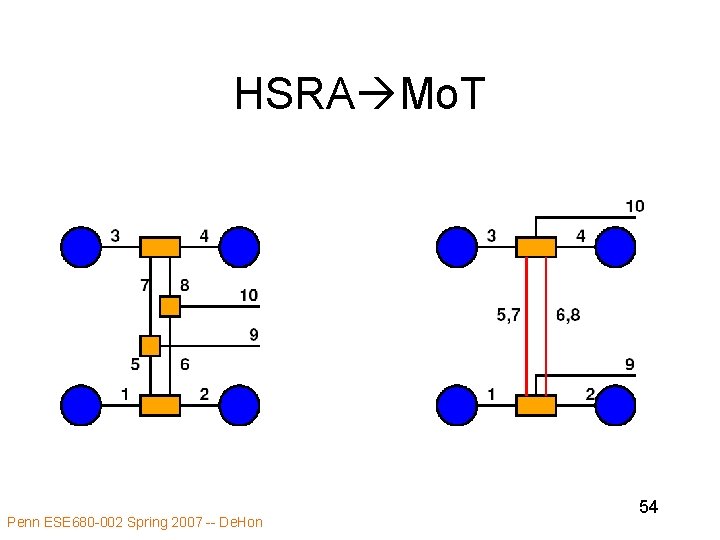

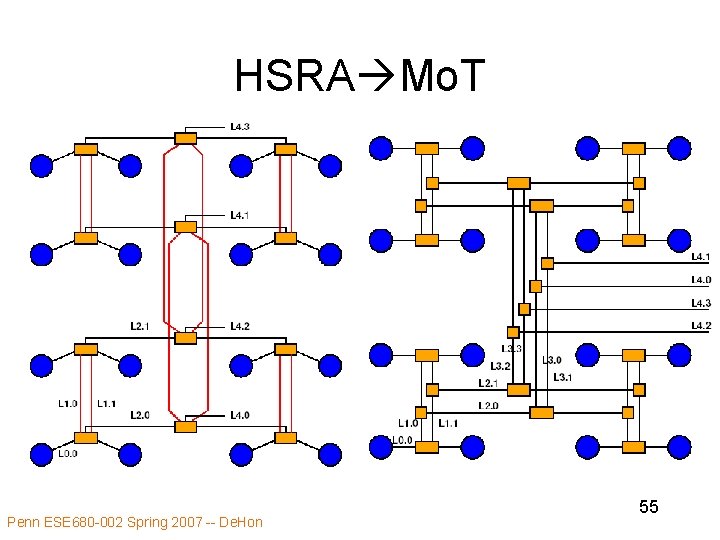

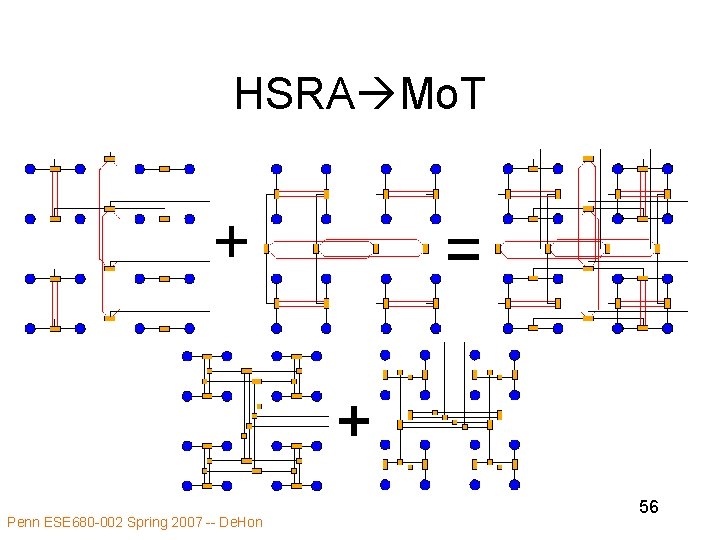

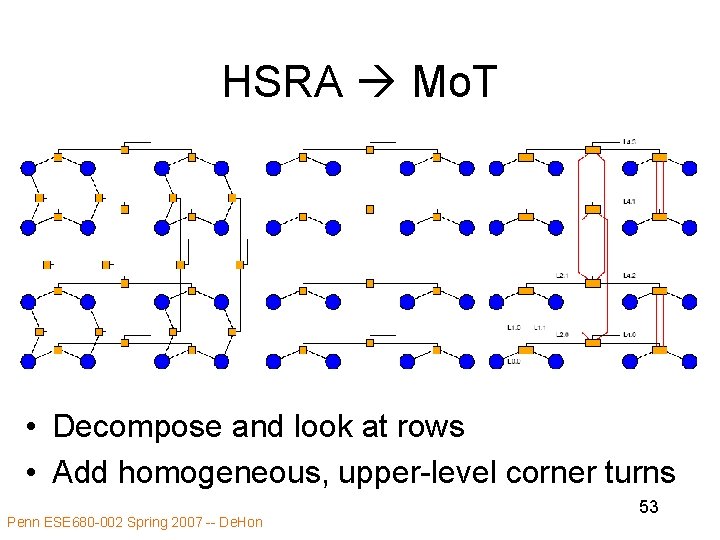

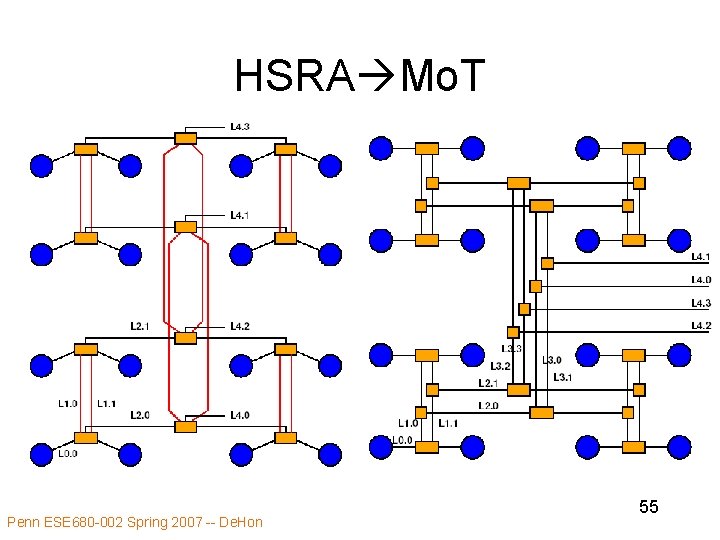

HSRA Mo. T • Decompose and look at rows • Add homogeneous, upper-level corner turns Penn ESE 680 -002 Spring 2007 -- De. Hon 53

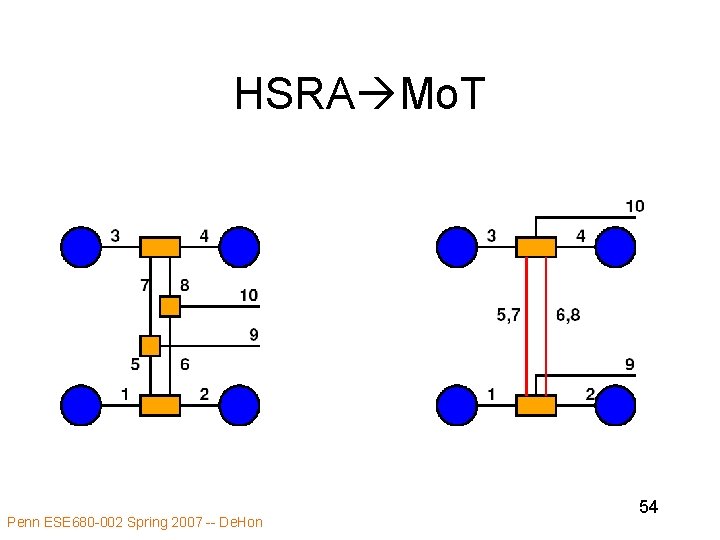

HSRA Mo. T Penn ESE 680 -002 Spring 2007 -- De. Hon 54

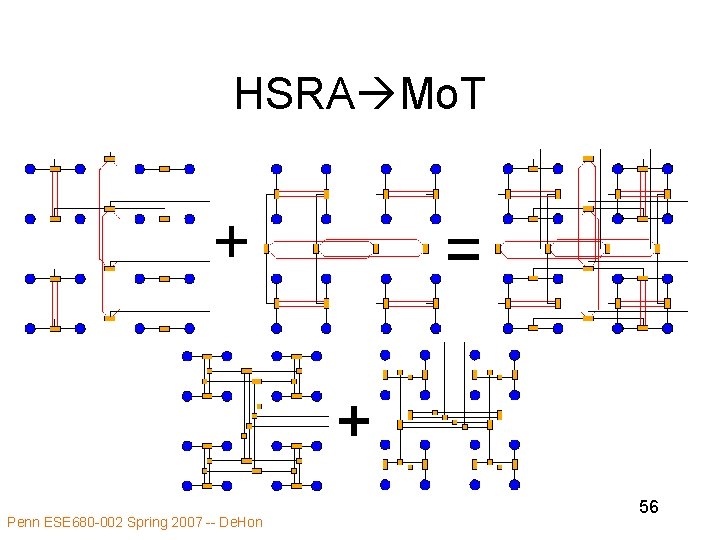

HSRA Mo. T Penn ESE 680 -002 Spring 2007 -- De. Hon 55

HSRA Mo. T Penn ESE 680 -002 Spring 2007 -- De. Hon 56

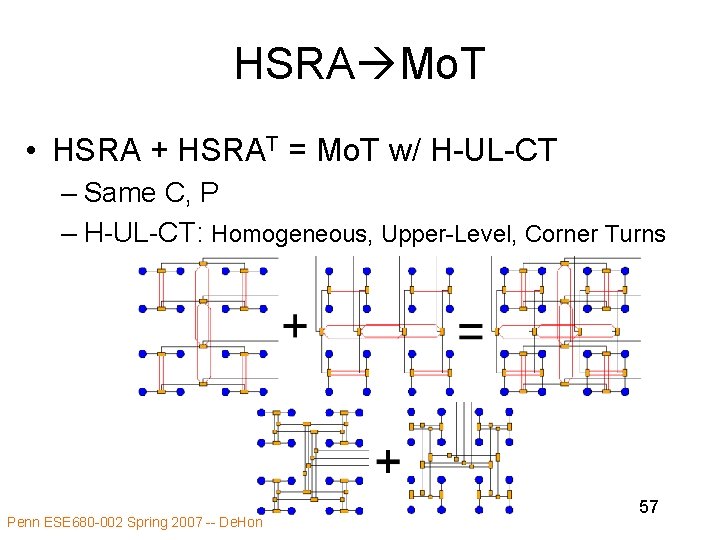

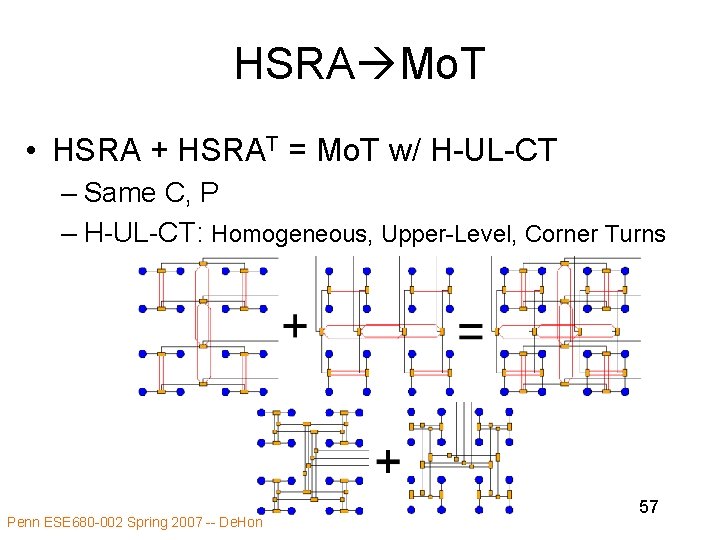

HSRA Mo. T • HSRA + HSRAT = Mo. T w/ H-UL-CT – Same C, P – H-UL-CT: Homogeneous, Upper-Level, Corner Turns Penn ESE 680 -002 Spring 2007 -- De. Hon 57

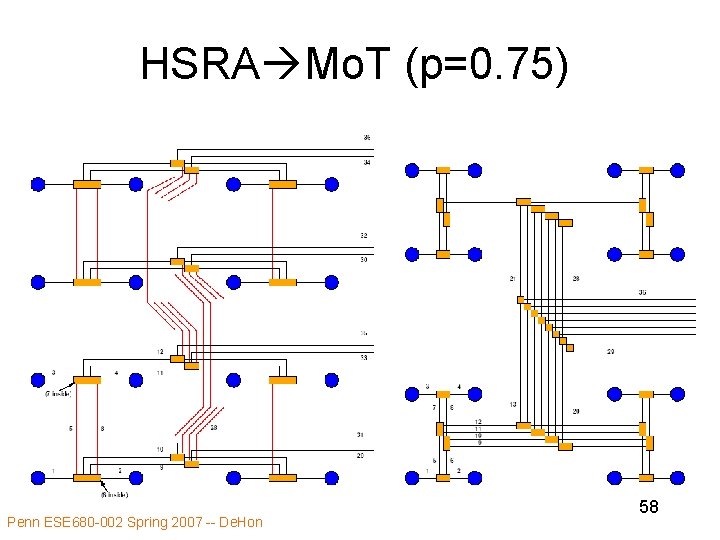

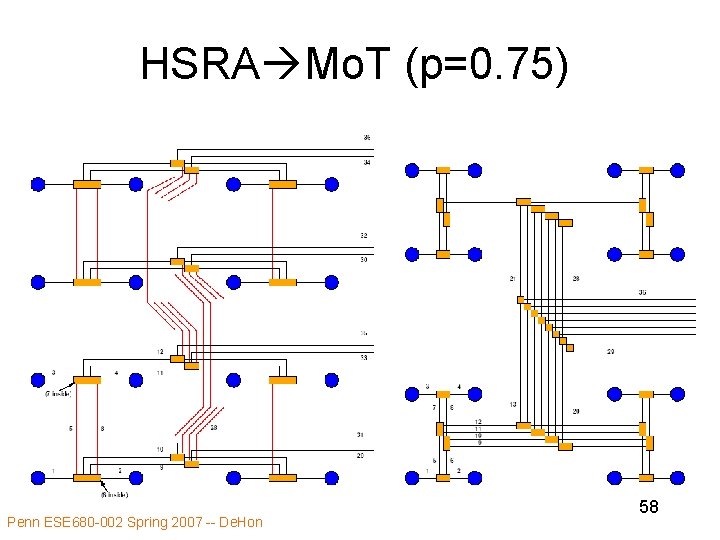

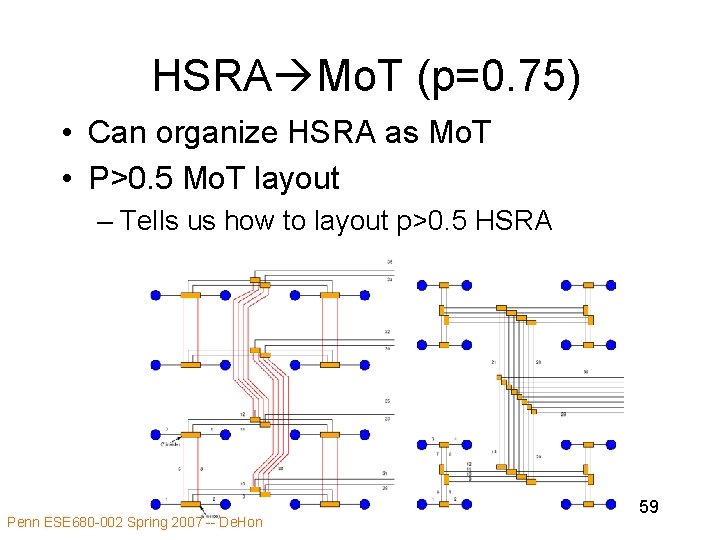

HSRA Mo. T (p=0. 75) Penn ESE 680 -002 Spring 2007 -- De. Hon 58

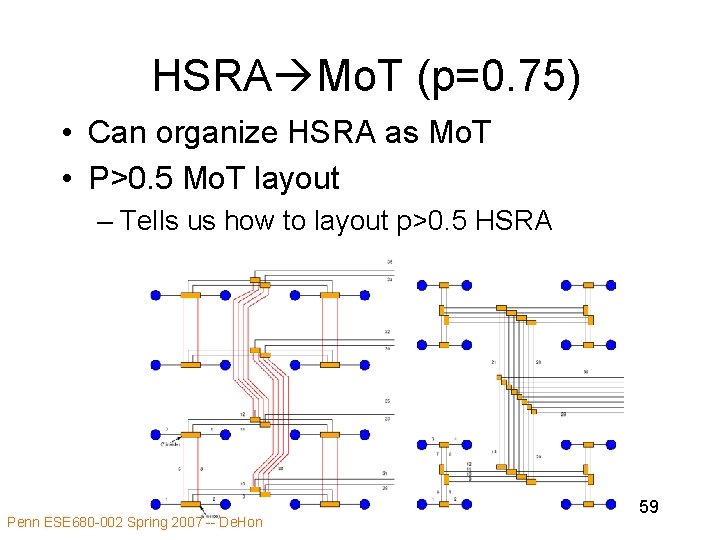

HSRA Mo. T (p=0. 75) • Can organize HSRA as Mo. T • P>0. 5 Mo. T layout – Tells us how to layout p>0. 5 HSRA Penn ESE 680 -002 Spring 2007 -- De. Hon 59

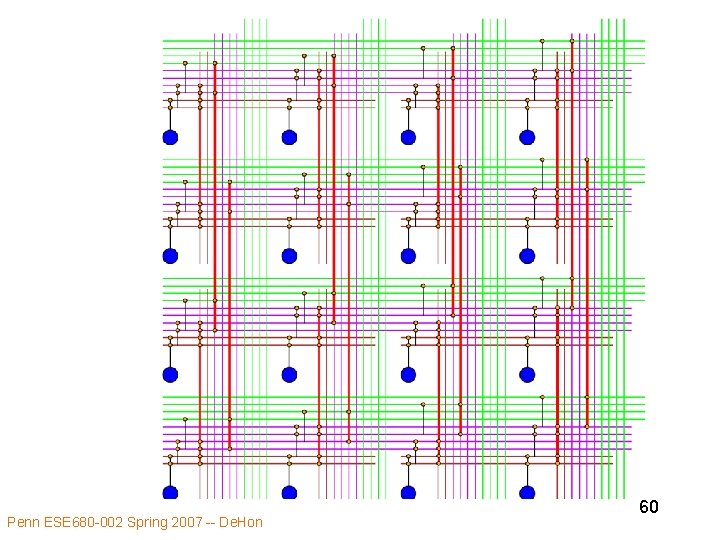

Penn ESE 680 -002 Spring 2007 -- De. Hon 60

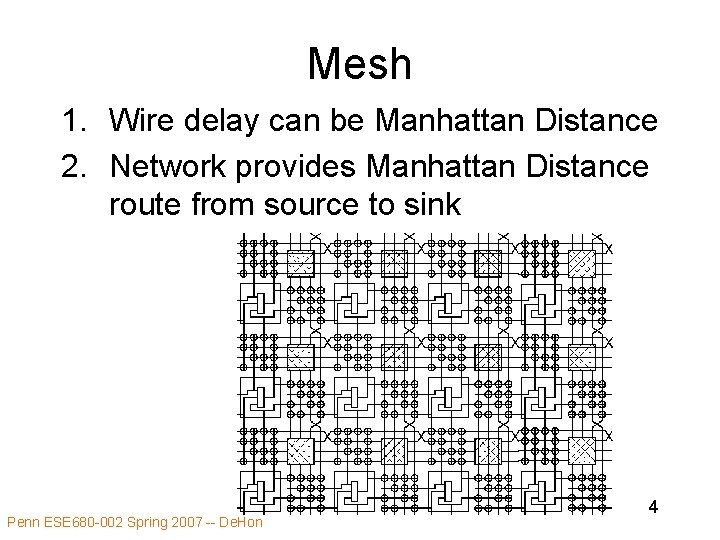

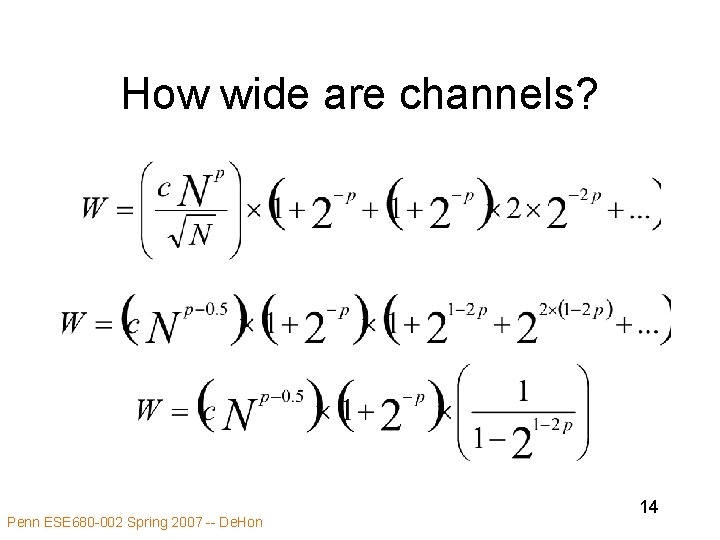

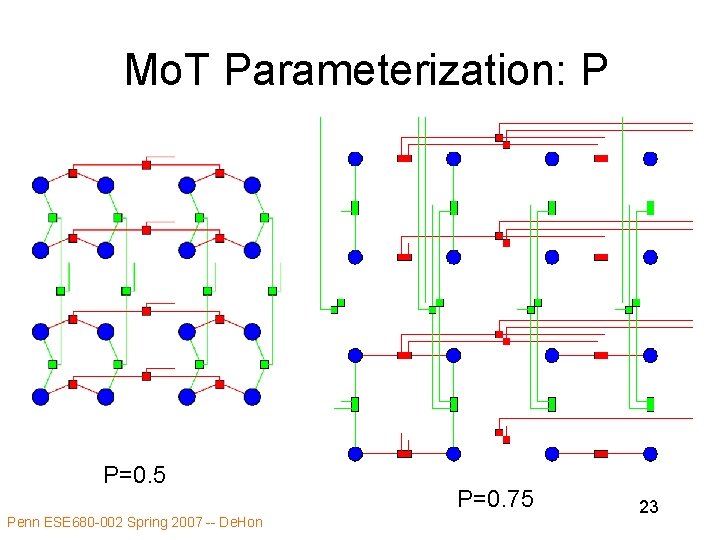

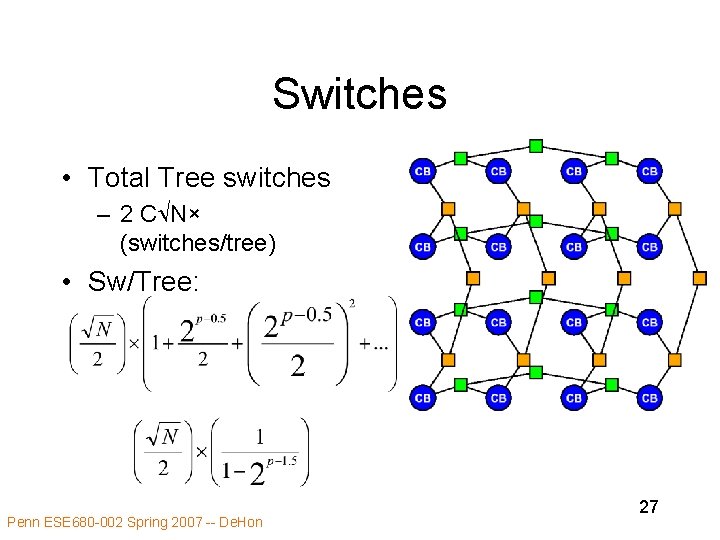

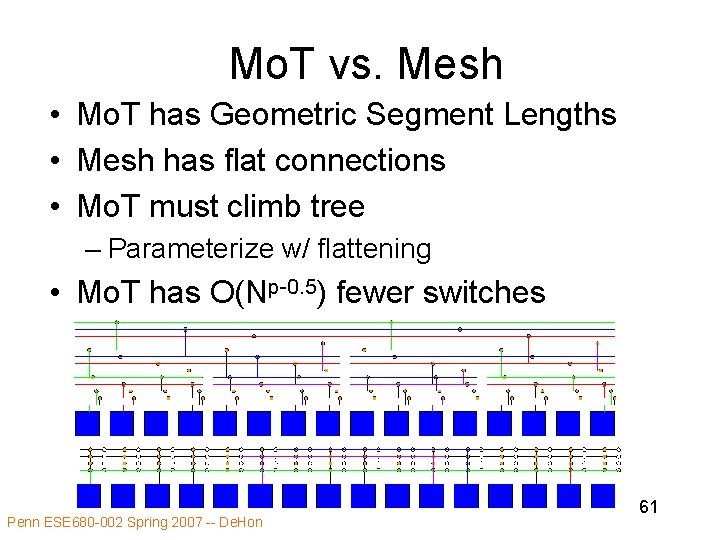

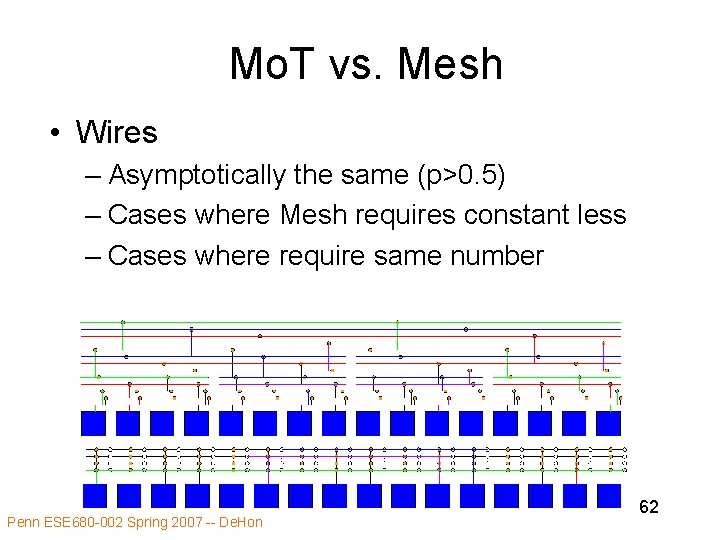

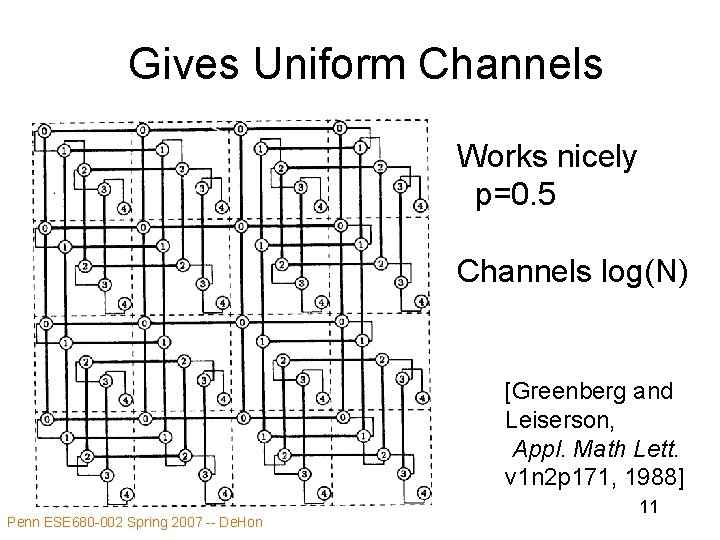

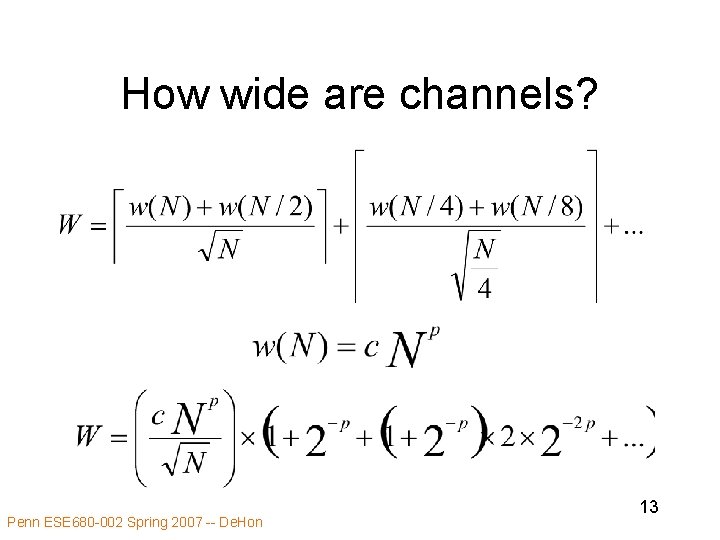

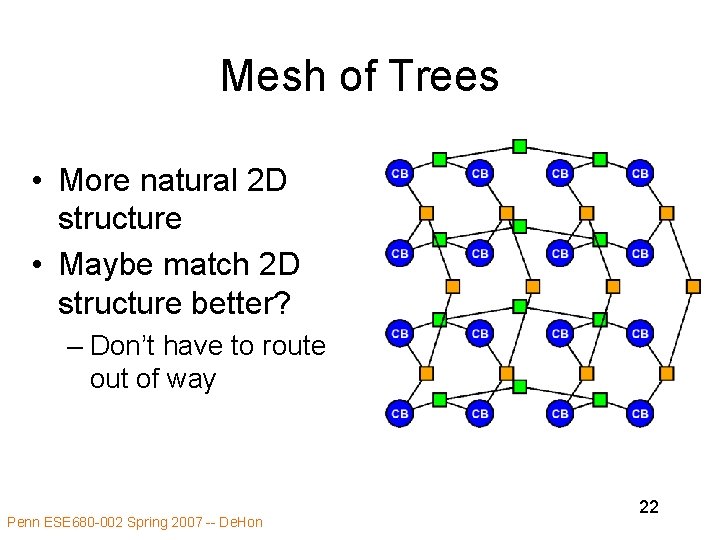

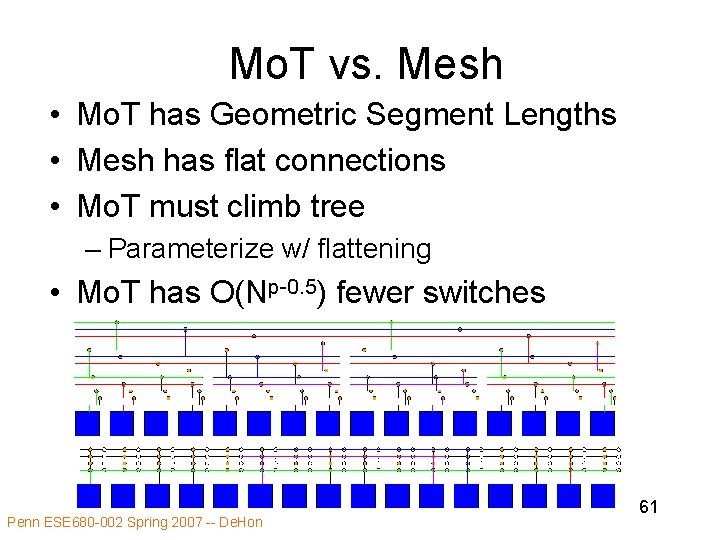

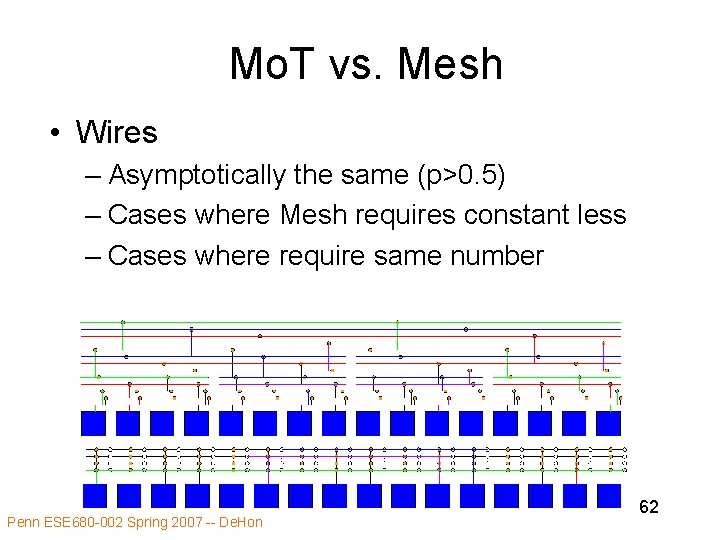

Mo. T vs. Mesh • Mo. T has Geometric Segment Lengths • Mesh has flat connections • Mo. T must climb tree – Parameterize w/ flattening • Mo. T has O(Np-0. 5) fewer switches Penn ESE 680 -002 Spring 2007 -- De. Hon 61

Mo. T vs. Mesh • Wires – Asymptotically the same (p>0. 5) – Cases where Mesh requires constant less – Cases where require same number Penn ESE 680 -002 Spring 2007 -- De. Hon 62

![Penn ESE 680 002 Spring 2007 De Hon De HonTRVLSI 2004 63 Penn ESE 680 -002 Spring 2007 -- De. Hon [De. Hon/TRVLSI 2004] 63](https://slidetodoc.com/presentation_image_h2/b2abfea9b236cf6be34fe32ae713a261/image-63.jpg)

Penn ESE 680 -002 Spring 2007 -- De. Hon [De. Hon/TRVLSI 2004] 63

Admin • Interconnect assignment due today • Retiming assignment out today – Monday lecture is key – Reading handed out last time for Monday Penn ESE 680 -002 Spring 2007 -- De. Hon 64

Big Ideas • Networks driven by same wiring requirements – Have similar wiring asymptotes • Can bound – Network differences – Worst-case mesh global routing • Hierarchy structure allows to save switches – O(N) vs. W(Np+0. 5) Penn ESE 680 -002 Spring 2007 -- De. Hon 65