Alfred L Crouch Chief Technologist Director of IJTAG

![1687 Hardware Architecture TRST* JTAG TAP Master Controller TMS TAP-IR[n: 0] TCK THE VIEW 1687 Hardware Architecture TRST* JTAG TAP Master Controller TMS TAP-IR[n: 0] TCK THE VIEW](https://slidetodoc.com/presentation_image_h/b85ce7423a9177dcc41e57bebbece8fa/image-12.jpg)

![Triple-Point Diagram [PVTF] Temperature Cost Limits ATE Test to minimum PVTF points ATE Test Triple-Point Diagram [PVTF] Temperature Cost Limits ATE Test to minimum PVTF points ATE Test](https://slidetodoc.com/presentation_image_h/b85ce7423a9177dcc41e57bebbece8fa/image-46.jpg)

- Slides: 95

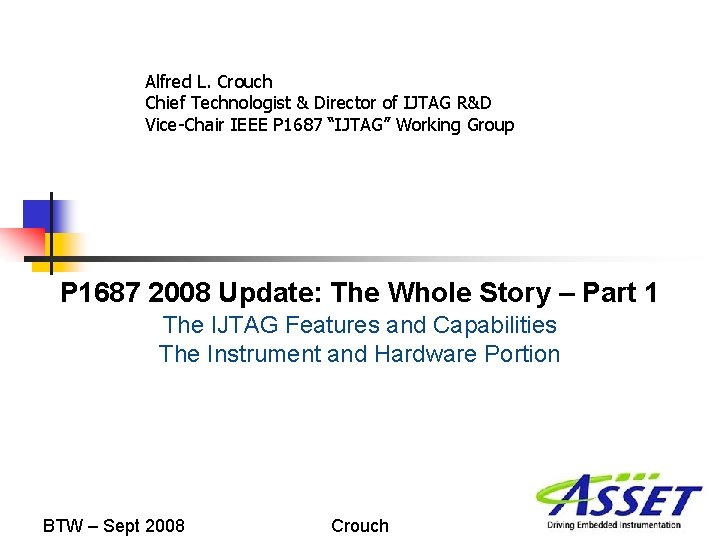

Alfred L. Crouch Chief Technologist & Director of IJTAG R&D Vice-Chair IEEE P 1687 “IJTAG” Working Group P 1687 2008 Update: The Whole Story The IJTAG Features and Capabilities BTW – Sept 2008 Crouch

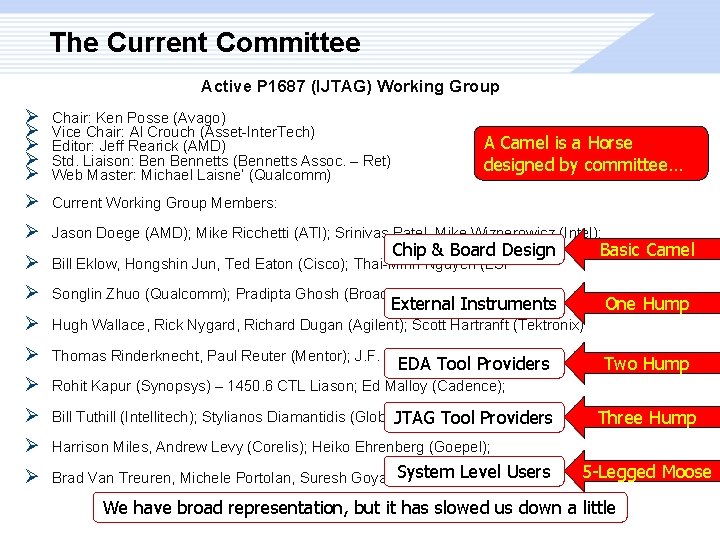

The Current Committee Active P 1687 (IJTAG) Working Group Ø Ø Ø Chair: Ken Posse (Avago) Vice Chair: Al Crouch (Asset-Inter. Tech) Editor: Jeff Rearick (AMD) Std. Liaison: Bennetts (Bennetts Assoc. – Ret) Web Master: Michael Laisne’ (Qualcomm) Ø Jason Doege (AMD); Mike Ricchetti (ATI); Srinivas Patel, Mike Wiznerowicz (Intel); Ø Bill Eklow, Hongshin Jun, Ted Eaton (Cisco); Thai-Minh Nguyen (LSI Ø Songlin Zhuo (Qualcomm); Pradipta Ghosh (Broadcom); Ø Hugh Wallace, Rick Nygard, Richard Dugan (Agilent); Scott Hartranft (Tektronix) Ø Thomas Rinderknecht, Paul Reuter (Mentor); J. F. Cote (Logic. Vision); Ø Rohit Kapur (Synopsys) – 1450. 6 CTL Liason; Ed Malloy (Cadence); Ø Bill Tuthill (Intellitech); Stylianos Diamantidis (Globe. Tech); John Potter (Asset-Inter. Tech); Three JTAG Tool Providers Ø Harrison Miles, Andrew Levy (Corelis); Heiko Ehrenberg (Goepel); Ø System Level Users Brad Van Treuren, Michele Portolan, Suresh Goyal (Alcatel-Lucent); A Camel is a Horse designed by committee… Current Working Group Members: Chip & Board Design Basic Camel One Hump External Instruments EDA Tool Providers Two Hump 5 -Legged Moose We have broad representation, but it has slowed us down a little

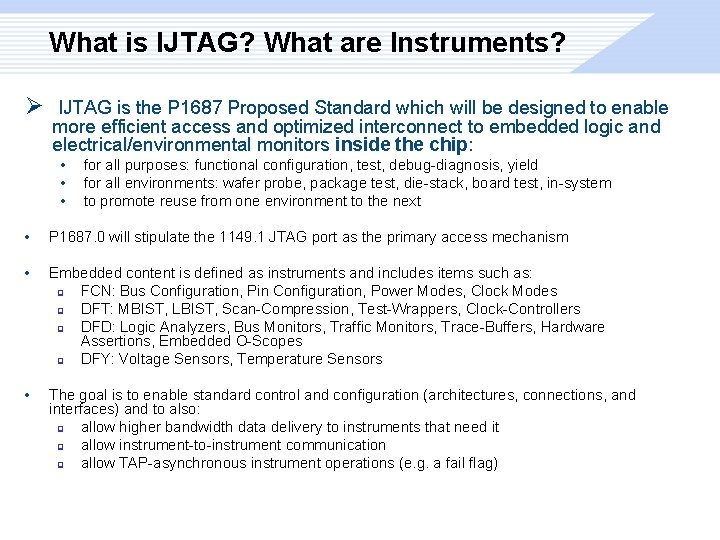

Some Semantics…from the Corporate Confusion Department… Ø Lots of new and used Acronyms and Abbreviations: • • • • IJTAG = Internal JTAG BSDL Zone = Boundary Scan Description Language Zone TDR = Test Data Register IIF = Instrument Interface Register GDR or GIR = Gateway Data or Gateway Instruction Register SIB = Select Instrument Bit MIB = Multiple-Input Bit GWEN = Gateway Enable Instruction HIP = Hierarchical Interface Port HDL = Hardware Description Language IDL = Instrument Description Language CDL = Connectivity Description Language PDL = Protocol Description Language S/C/U = Shift/Capture/Update

Alfred L. Crouch Chief Technologist & Director of IJTAG R&D Vice-Chair IEEE P 1687 “IJTAG” Working Group P 1687 2008 Update: The Whole Story – Part 1 The IJTAG Features and Capabilities The Instrument and Hardware Portion BTW – Sept 2008 Crouch

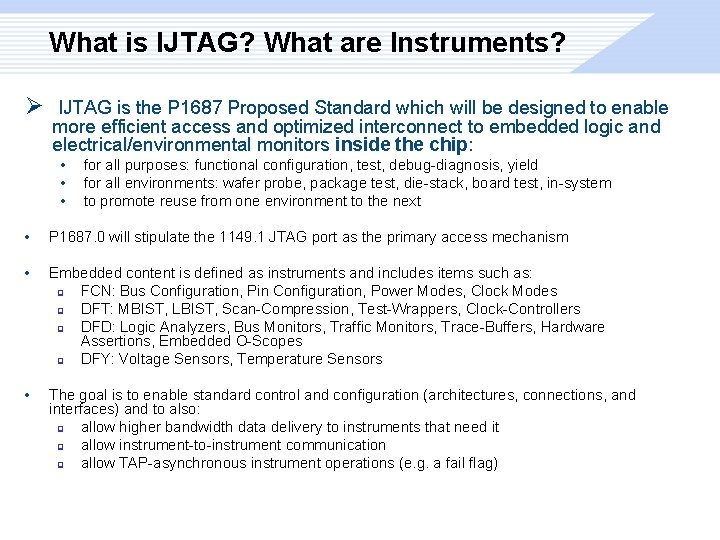

What is IJTAG? What are Instruments? Ø IJTAG is the P 1687 Proposed Standard which will be designed to enable more efficient access and optimized interconnect to embedded logic and electrical/environmental monitors inside the chip: • • • for all purposes: functional configuration, test, debug-diagnosis, yield for all environments: wafer probe, package test, die-stack, board test, in-system to promote reuse from one environment to the next • P 1687. 0 will stipulate the 1149. 1 JTAG port as the primary access mechanism • Embedded content is defined as instruments and includes items such as: q FCN: Bus Configuration, Pin Configuration, Power Modes, Clock Modes q DFT: MBIST, LBIST, Scan-Compression, Test-Wrappers, Clock-Controllers q DFD: Logic Analyzers, Bus Monitors, Traffic Monitors, Trace-Buffers, Hardware Assertions, Embedded O-Scopes q DFY: Voltage Sensors, Temperature Sensors • The goal is to enable standard control and configuration (architectures, connections, and interfaces) and to also: q allow higher bandwidth data delivery to instruments that need it q allow instrument-to-instrument communication q allow TAP-asynchronous instrument operations (e. g. a fail flag)

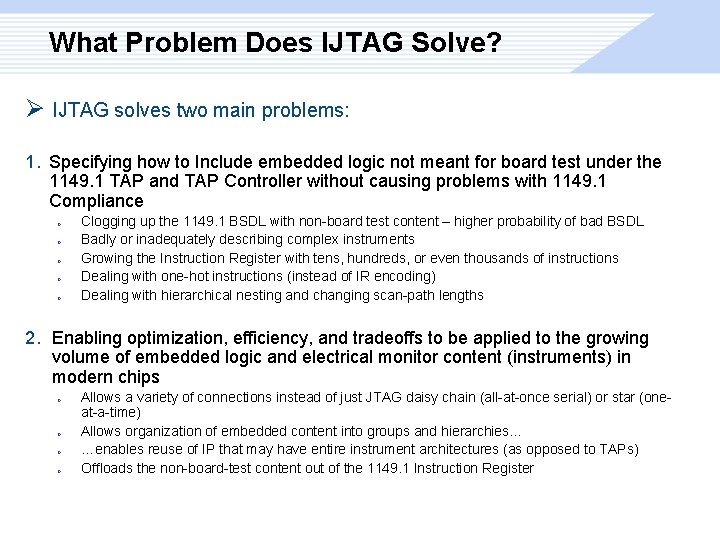

What Problem Does IJTAG Solve? Ø IJTAG solves two main problems: 1. Specifying how to Include embedded logic not meant for board test under the 1149. 1 TAP and TAP Controller without causing problems with 1149. 1 Compliance o o o Clogging up the 1149. 1 BSDL with non-board test content – higher probability of bad BSDL Badly or inadequately describing complex instruments Growing the Instruction Register with tens, hundreds, or even thousands of instructions Dealing with one-hot instructions (instead of IR encoding) Dealing with hierarchical nesting and changing scan-path lengths 2. Enabling optimization, efficiency, and tradeoffs to be applied to the growing volume of embedded logic and electrical monitor content (instruments) in modern chips o o Allows a variety of connections instead of just JTAG daisy chain (all-at-once serial) or star (oneat-a-time) Allows organization of embedded content into groups and hierarchies… …enables reuse of IP that may have entire instrument architectures (as opposed to TAPs) Offloads the non-board-test content out of the 1149. 1 Instruction Register

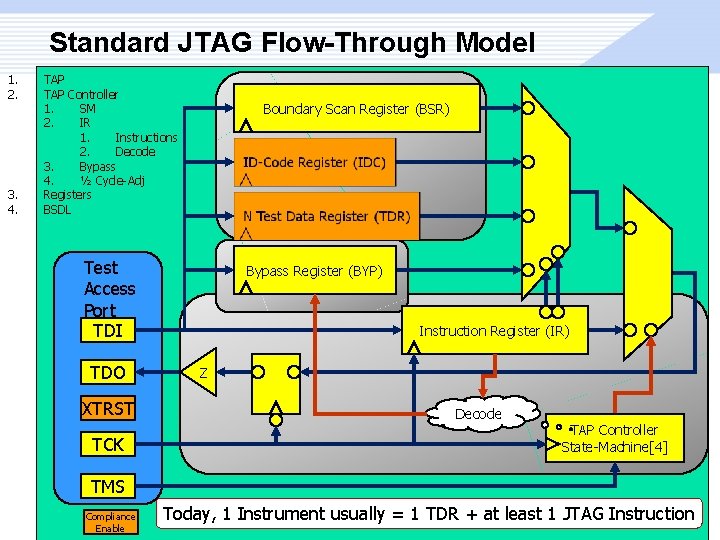

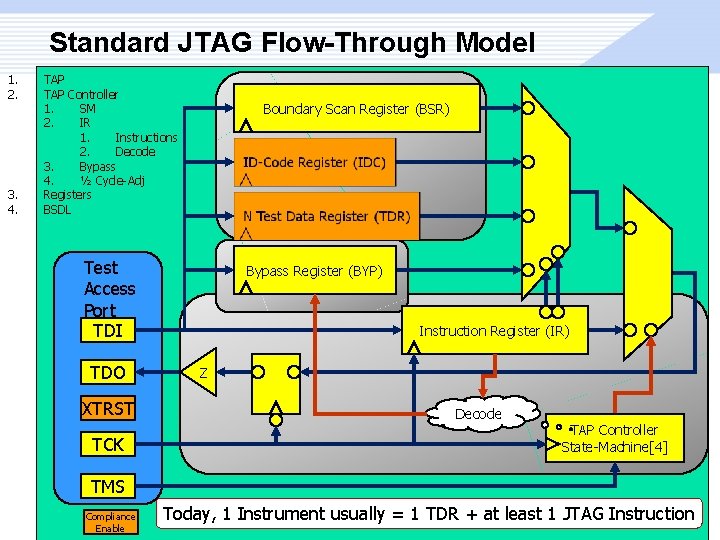

Standard JTAG Flow-Through Model 1. 2. 3. 4. TAP Controller 1. SM 2. IR 1. Instructions 2. Decode 3. Bypass 4. ½ Cycle-Adj Registers BSDL Boundary Scan Register (BSR) Test Access Port TDI TDO XTRST TCK Bypass Register (BYP) Instruction Register (IR) Z Decode TAP Controller State-Machine[4] TMS Compliance Enable Today, 1 Instrument usually = 1 TDR + at least 1 JTAG Instruction

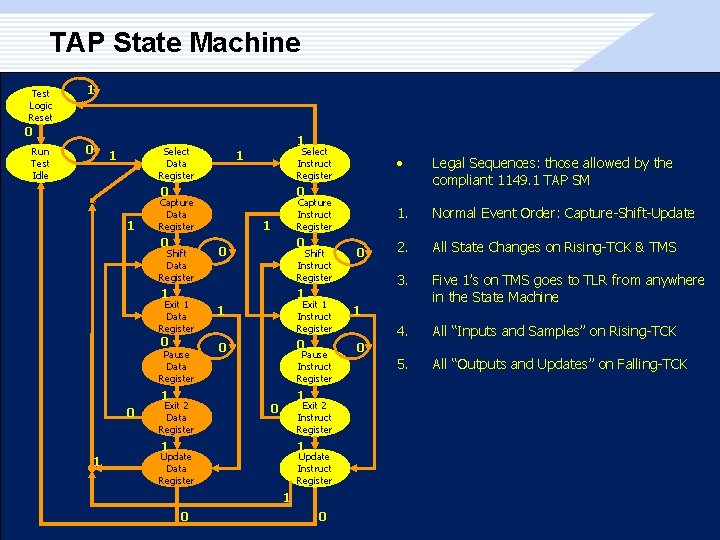

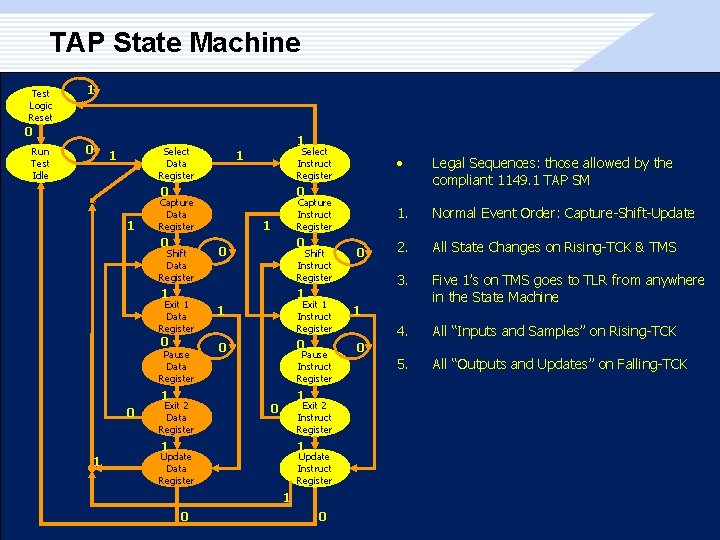

TAP State Machine Test Logic Reset 1 0 Run Test Idle 0 1 Select Data Register 1 Select Instruct Register 1 0 1 Shift Data Register Capture Instruct Register 1 0 0 Shift Instruct Register 1 Exit 1 Data Register 0 Pause Data Register 1 0 1 Exit 2 Data Register 0 1 Exit 1 Instruct Register 1 0 0 Pause Instruct Register 1 Exit 2 Instruct Register 0 1 1 Update Data Register Update Instruct Register 1 0 Legal Sequences: those allowed by the compliant 1149. 1 TAP SM 1. Normal Event Order: Capture-Shift-Update 2. All State Changes on Rising-TCK & TMS 3. Five 1’s on TMS goes to TLR from anywhere in the State Machine 4. All “Inputs and Samples” on Rising-TCK 5. All “Outputs and Updates” on Falling-TCK 0 Capture Data Register 0 • 0 1 0

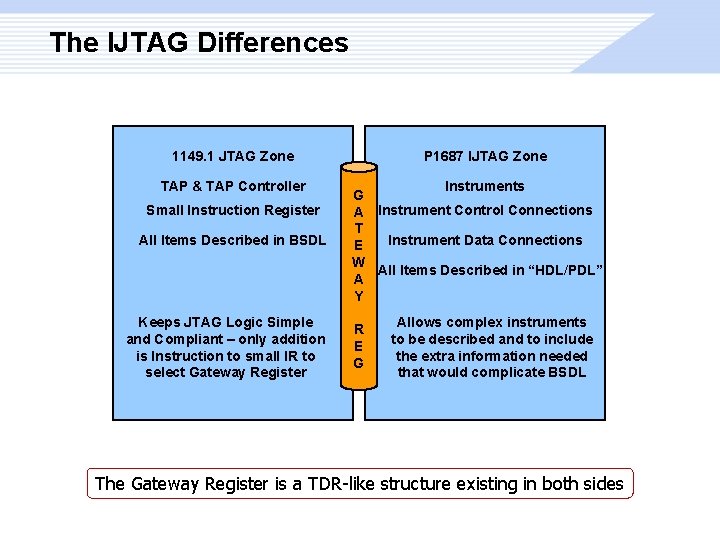

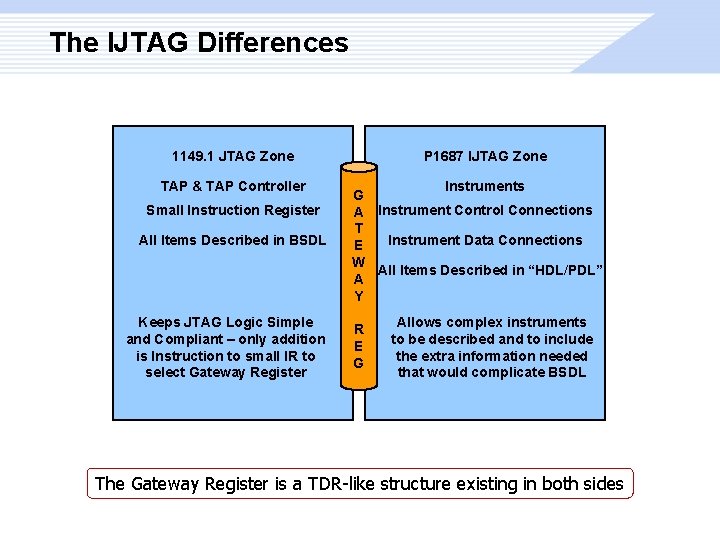

The IJTAG Differences 1149. 1 JTAG Zone TAP & TAP Controller Small Instruction Register All Items Described in BSDL Keeps JTAG Logic Simple and Compliant – only addition is Instruction to small IR to select Gateway Register P 1687 IJTAG Zone Instruments G A Instrument Control Connections T Instrument Data Connections E W All Items Described in “HDL/PDL” A Y R E G Allows complex instruments to be described and to include the extra information needed that would complicate BSDL The Gateway Register is a TDR-like structure existing in both sides

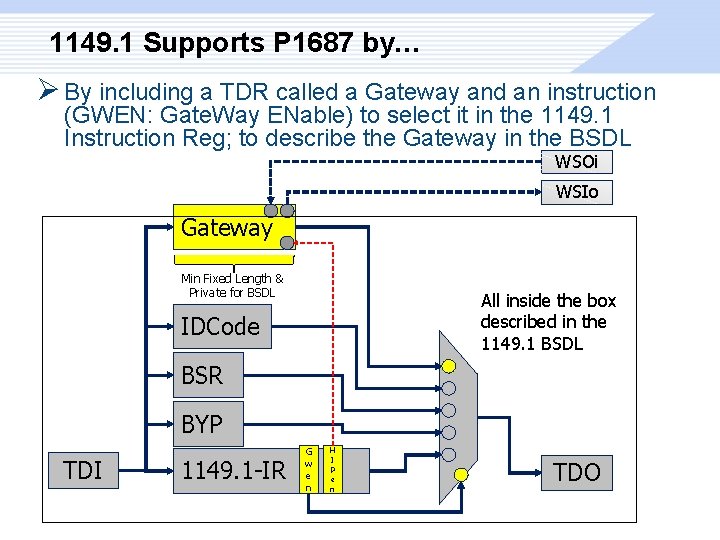

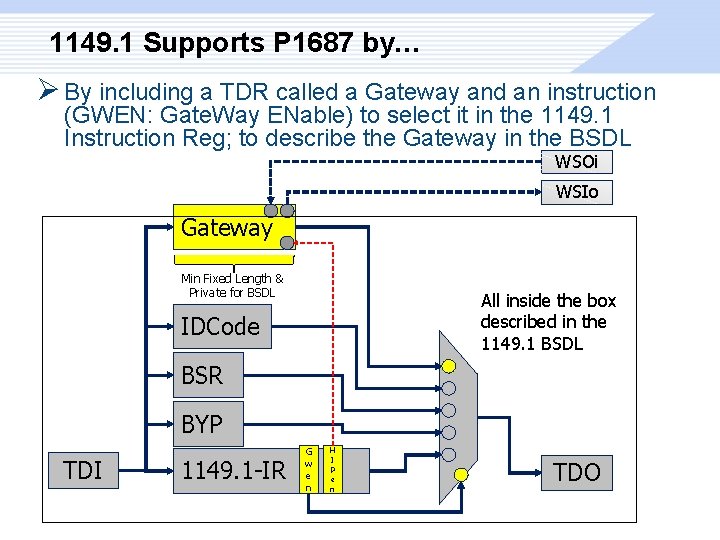

1149. 1 Supports P 1687 by… Ø By including a TDR called a Gateway and an instruction (GWEN: Gate. Way ENable) to select it in the 1149. 1 Instruction Reg; to describe the Gateway in the BSDL WSOi WSIo Gateway Min Fixed Length & Private for BSDL All inside the box described in the 1149. 1 BSDL IDCode BSR BYP TDI 1149. 1 -IR G w e n H I P e n TDO

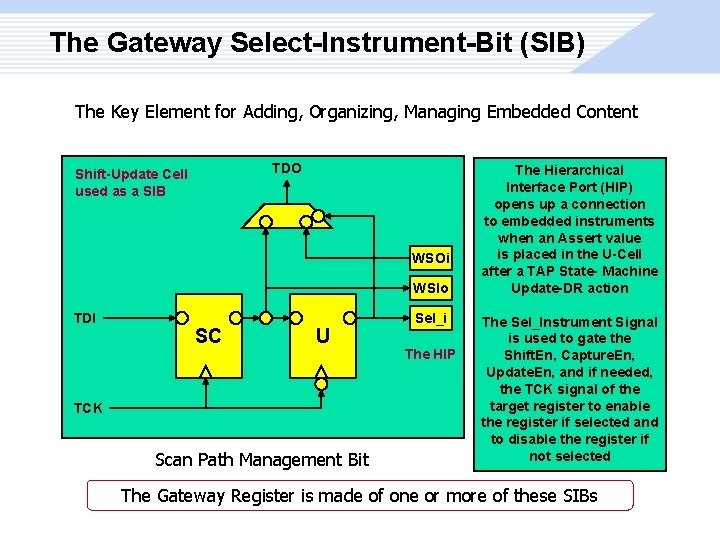

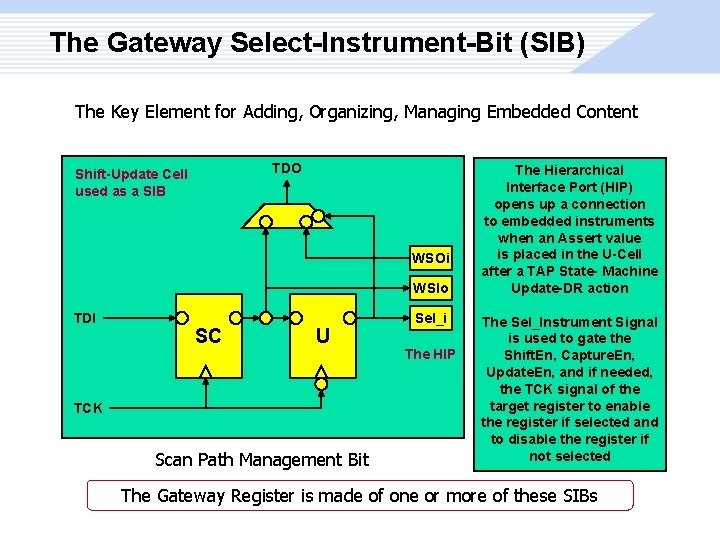

The Gateway Select-Instrument-Bit (SIB) The Key Element for Adding, Organizing, Managing Embedded Content TDO Shift-Update Cell used as a SIB WSOi WSIo TDI SC U TCK Scan Path Management Bit Sel_i The HIP The Hierarchical Interface Port (HIP) opens up a connection to embedded instruments when an Assert value is placed in the U-Cell after a TAP State- Machine Update-DR action The Sel_Instrument Signal is used to gate the Shift. En, Capture. En, Update. En, and if needed, the TCK signal of the target register to enable the register if selected and to disable the register if not selected The Gateway Register is made of one or more of these SIBs

![1687 Hardware Architecture TRST JTAG TAP Master Controller TMS TAPIRn 0 TCK THE VIEW 1687 Hardware Architecture TRST* JTAG TAP Master Controller TMS TAP-IR[n: 0] TCK THE VIEW](https://slidetodoc.com/presentation_image_h/b85ce7423a9177dcc41e57bebbece8fa/image-12.jpg)

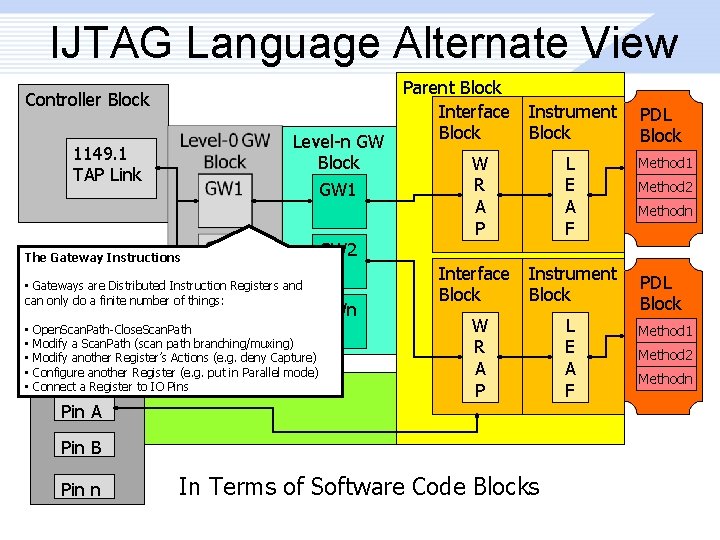

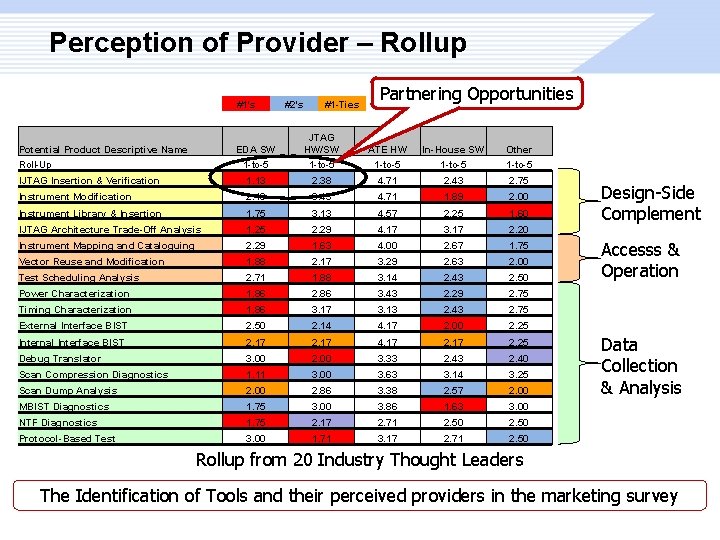

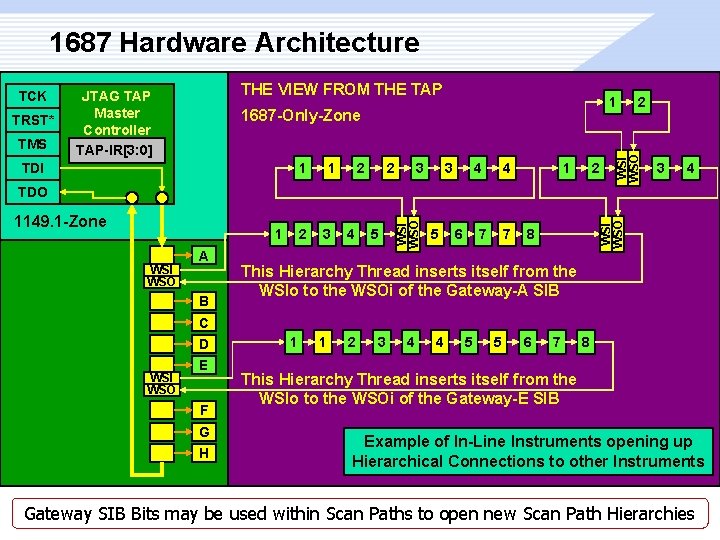

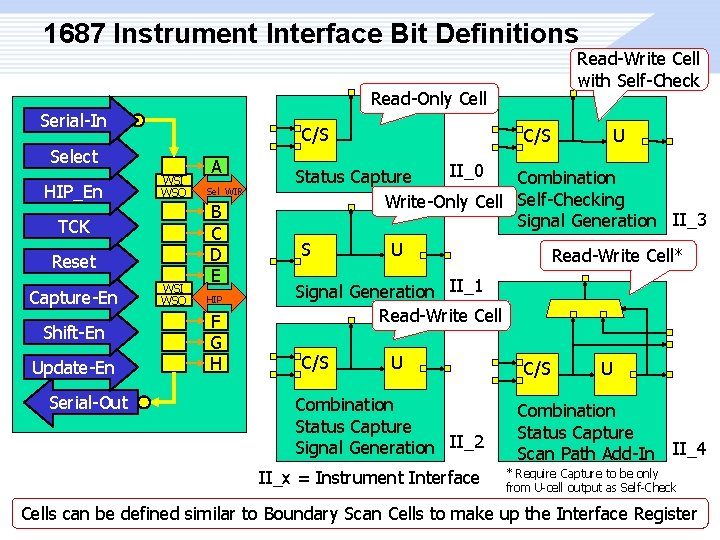

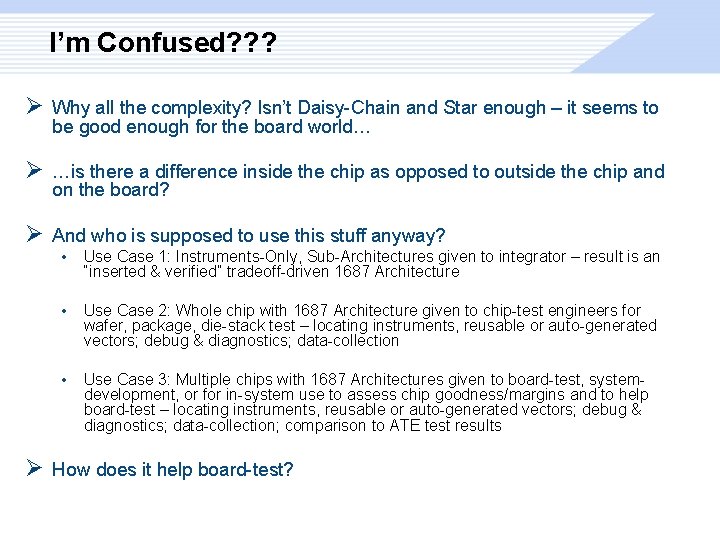

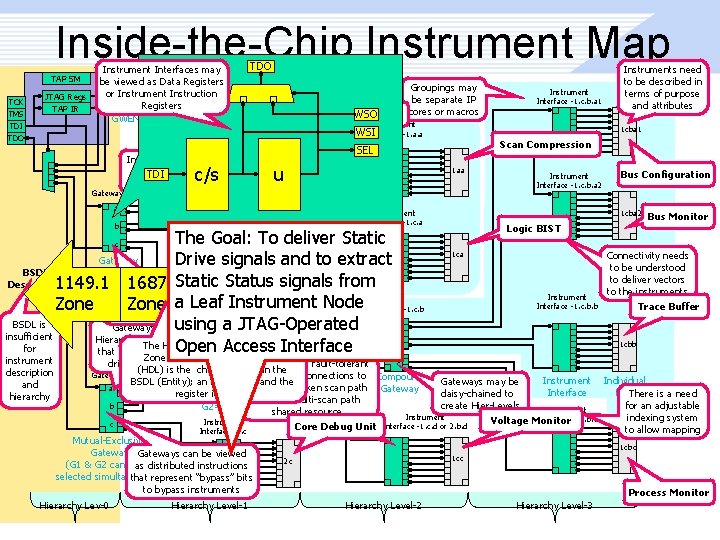

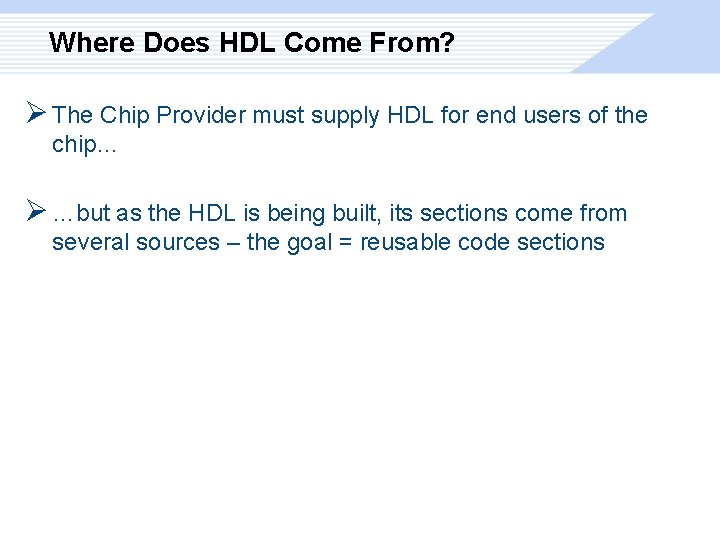

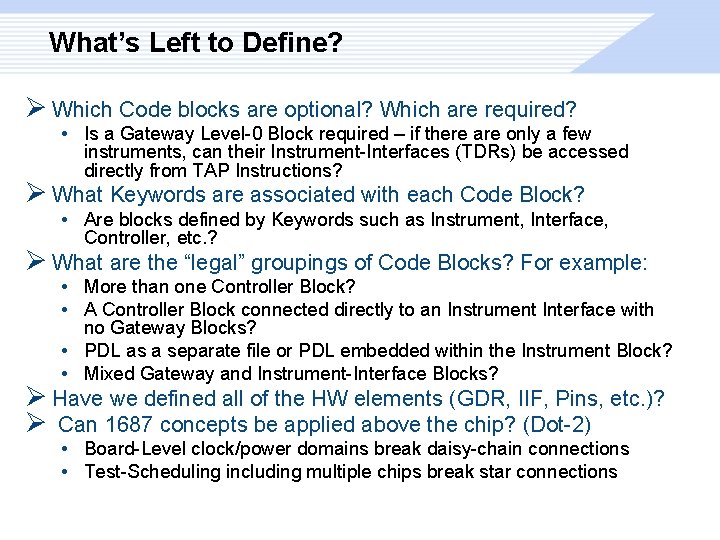

1687 Hardware Architecture TRST* JTAG TAP Master Controller TMS TAP-IR[n: 0] TCK THE VIEW FROM THE TAP In-Line Instruments TDI This Hierarchy Thread inserts from WSIo-to-WSOi of the Gateway-A SIB Instruments connected to the Gateway may be connected in several different schemes: TDO 1149. 1 -Zone 1. A HIP WSI WSO 1 2 3 4 C D E F 2. 3. B A Gateway Interface Register 5 All Activity in the 1687 -Zone is a DR-Scan from the TAPs Point-of-View G 4. 5. Flat – one gateway-bit is connected to one instrument Daisy-Chain – one gateway-bit is connected to many instrument serially and simultaneously Star – one gateway-bit is connected to some grouping of instruments Concatenate – one gateway-bit is connected to a serial string of instruments that insert into the TDI-TDO path as they are activated Hierarchy – one gateway-bit is connected to an instrument that may support further hierarchical connections H P 1687 -Gateway 1687 -Only-Zone The 1687 Zone is accessed by opening up Scan Paths to Embedded Instruments

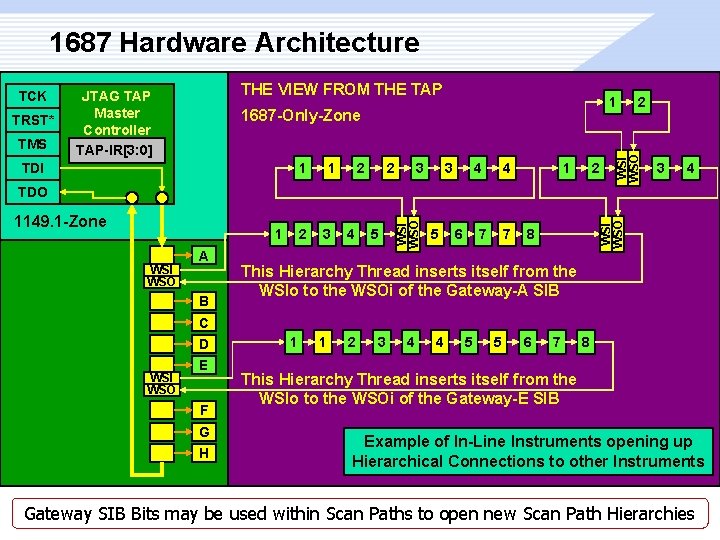

1687 Hardware Architecture TRST* TMS THE VIEW FROM THE TAP JTAG TAP Master Controller TAP-IR[3: 0] 1 1687 -Only-Zone TDI 1 1 2 2 3 3 4 4 1 2 2 WSI WSO TCK 3 4 1 A WSI WSO B 2 3 4 5 5 6 7 7 WSI WSO 1149. 1 -Zone WSI WSO TDO 8 This Hierarchy Thread inserts itself from the WSIo to the WSOi of the Gateway-A SIB C D WSI WSO E F G H 1 1 2 3 4 4 5 5 6 7 8 This Hierarchy Thread inserts itself from the WSIo to the WSOi of the Gateway-E SIB Example of In-Line Instruments opening up Hierarchical Connections to other Instruments Gateway SIB Bits may be used within Scan Paths to open new Scan Path Hierarchies

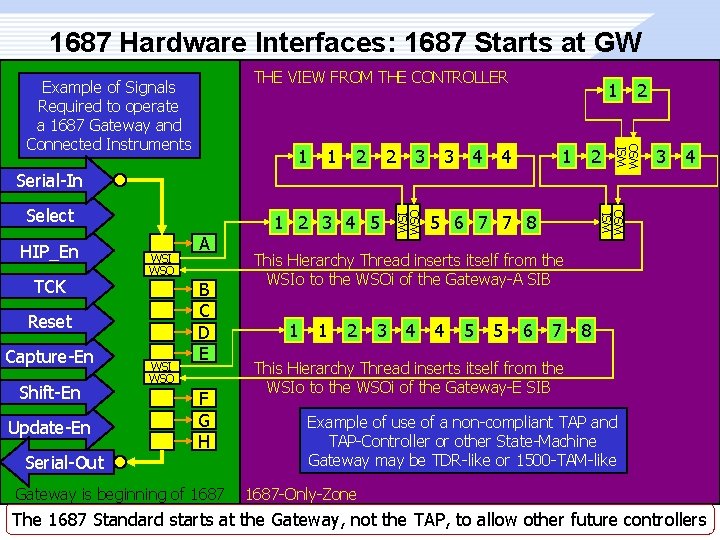

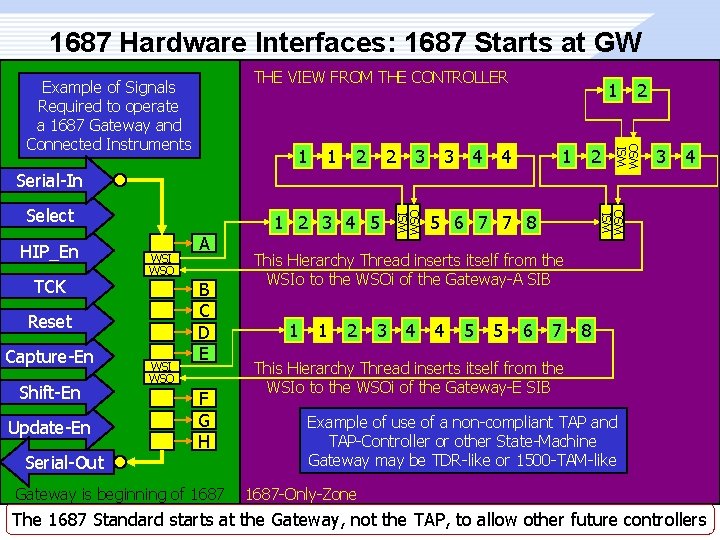

1687 Hardware Interfaces: 1687 Starts at GW THE VIEW FROM THE CONTROLLER 1 1 2 2 3 3 4 1 2 2 WSI WSO Example of Signals Required to operate a 1687 Gateway and Connected Instruments 3 4 HIP_En TCK WSI WSO Reset Capture-En Shift-En Update-En Serial-Out WSI WSO A B C D E F G H Gateway is beginning of 1687 1 2 3 4 5 WSI WSO Select WSI WSO Serial-In 5 6 7 7 8 This Hierarchy Thread inserts itself from the WSIo to the WSOi of the Gateway-A SIB 1 1 2 3 4 4 5 5 6 7 8 This Hierarchy Thread inserts itself from the WSIo to the WSOi of the Gateway-E SIB Example of use of a non-compliant TAP and TAP-Controller or other State-Machine Gateway may be TDR-like or 1500 -TAM-like 1687 -Only-Zone The 1687 Standard starts at the Gateway, not the TAP, to allow other future controllers

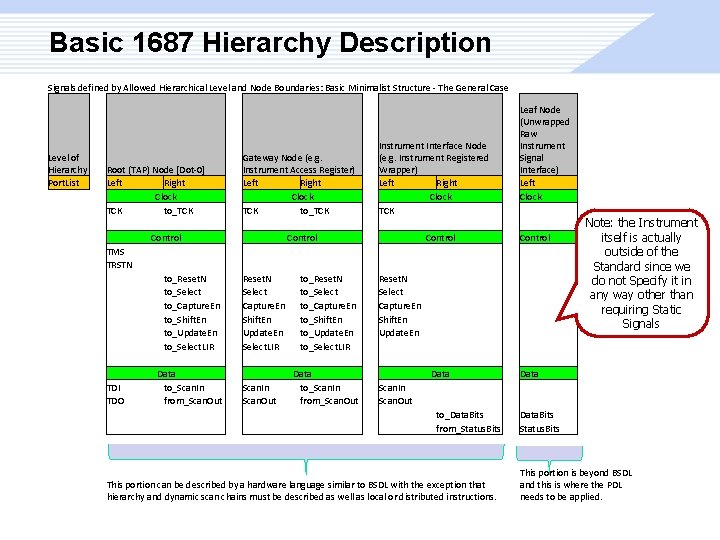

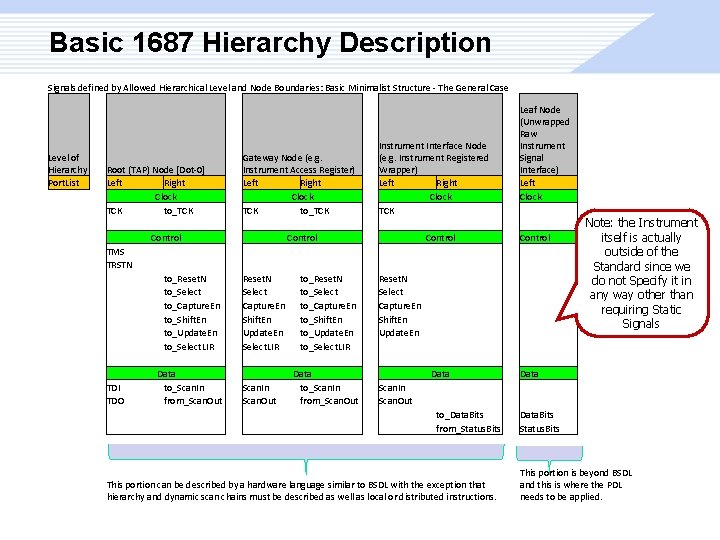

Basic 1687 Hierarchy Description Signals defined by Allowed Hierarchical Level and Node Boundaries: Basic Minimalist Structure - The General Case Level of Hierarchy Port. List Root (TAP) Node [Dot-0] Left Right Clock TCK to_TCK Control TMS TRSTN to_Reset. N to_Select to_Capture. En to_Shift. En to_Update. En to_Select. LIR Data TDI to_Scan. In TDO from_Scan. Out Gateway Node (e. g. Instrument Access Register) Left Right Clock TCK to_TCK Control Reset. N to_Reset. N Select to_Select Capture. En to_Capture. En Shift. En to_Shift. En Update. En to_Update. En Select. LIR to_Select. LIR Data Scan. In to_Scan. In Scan. Out from_Scan. Out Instrument Interface Node (e. g. Instrument Registered Wrapper) Left Right Clock TCK Control Reset. N Select Capture. En Shift. En Update. En Data Scan. In Scan. Out to_Data. Bits from_Status. Bits This portion can be described by a hardware language similar to BSDL with the exception that hierarchy and dynamic scan chains must be described as well as local or distributed instructions. Leaf Node (Unwrapped Raw Instrument Signal Interface) Left Clock Control Data. Bits Status. Bits Note: the Instrument itself is actually outside of the Standard since we do not Specify it in any way other than requiring Static Signals This portion is beyond BSDL and this is where the PDL needs to be applied.

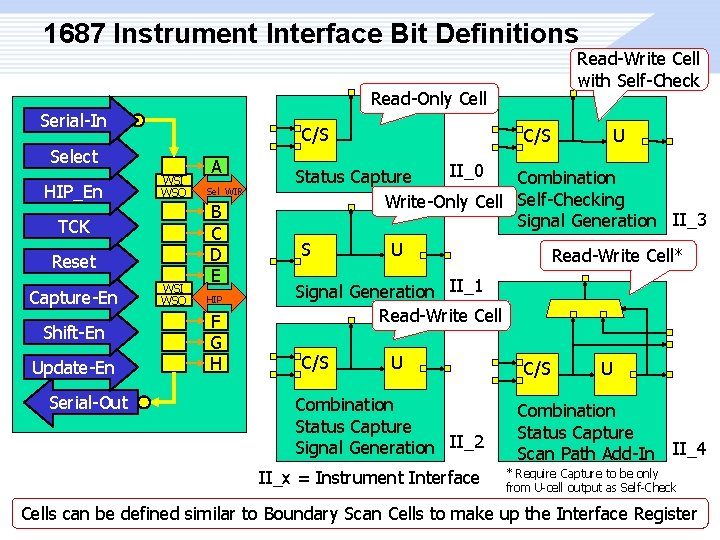

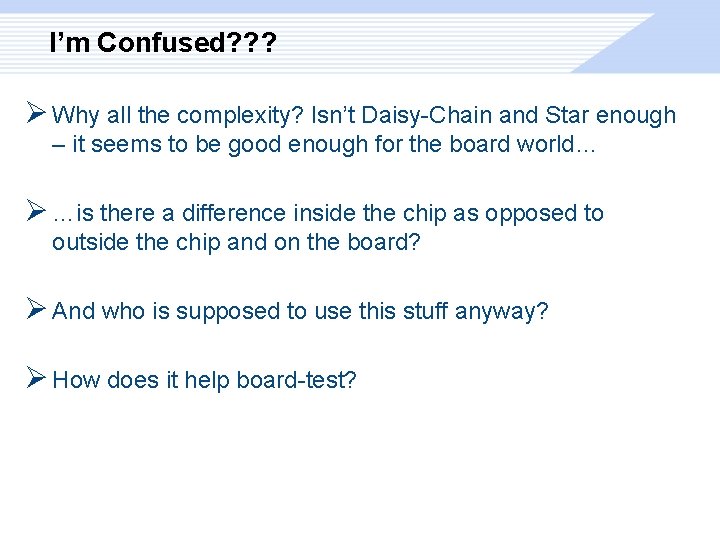

1687 Instrument Interface Bit Definitions Read-Write Cell with Self-Check Read-Only Cell Serial-In C/S Select HIP_En WSI WSO TCK Reset Capture-En Shift-En Update-En Serial-Out WSI WSO A Sel_WIR B C D E HIP F G H C/S U II_0 Status Capture Combination Write-Only Cell Self-Checking Signal Generation II_3 S U Read-Write Cell* Signal Generation II_1 Read-Write Cell C/S U Combination Status Capture Signal Generation II_2 II_x = Instrument Interface C/S U Combination Status Capture Scan Path Add-In II_4 * Require Capture to be only from U-cell output as Self-Check Cells can be defined similar to Boundary Scan Cells to make up the Interface Register

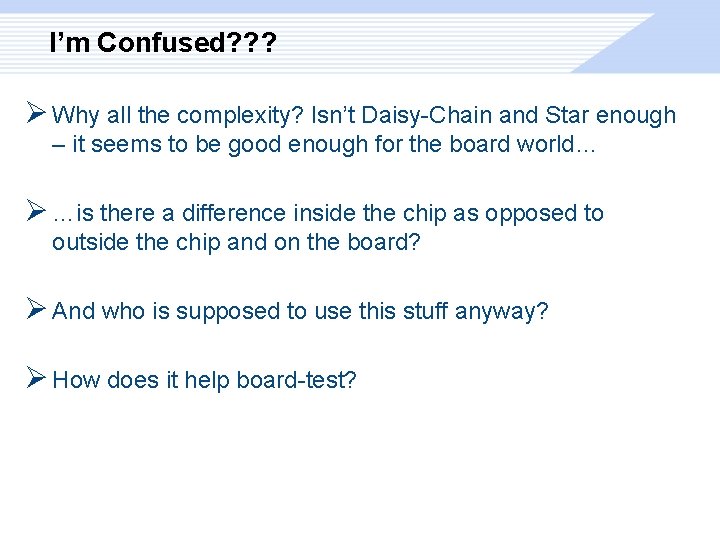

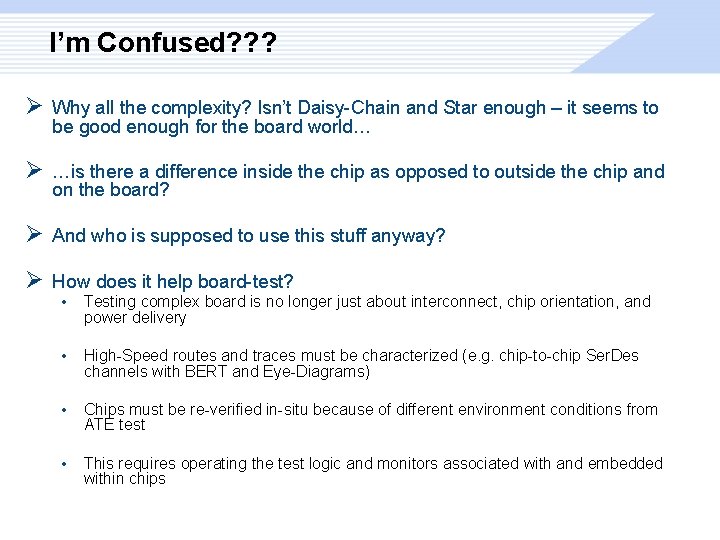

I’m Confused? ? ? Ø Why all the complexity? Isn’t Daisy-Chain and Star enough – it seems to be good enough for the board world… Ø …is there a difference inside the chip as opposed to outside the chip and on the board? Ø And who is supposed to use this stuff anyway? Ø How does it help board-test?

I’m Confused? ? ? Ø Why all the complexity? Isn’t Daisy-Chain and Star enough – it seems to be good enough for the board world… • Chip Designers still get measured by successful implementation of meeting their engineering and budget goals • Development of the access architecture versus chip tradeoffs is key Ø …is there a difference inside the chip as opposed to outside the chip and on the board? Ø And who is supposed to use this stuff anyway? Ø How does it help board-test?

I’m Confused? ? ? Ø Why all the complexity? Isn’t Daisy-Chain and Star enough – it seems to be good enough for the board world… Ø …is there a difference inside the chip as opposed to outside the chip and on the board? • Right now, chips have an incredible amount of “embedded” test, debug, and yield logic that must be accessed • One key technology is “power management” with requires shutting down clock domains and even power domains inside the chip Ø And who is supposed to use this stuff anyway? Ø How does it help board-test?

I’m Confused? ? ? Ø Why all the complexity? Isn’t Daisy-Chain and Star enough – it seems to be good enough for the board world… Ø …is there a difference inside the chip as opposed to outside the chip and on the board? Ø And who is supposed to use this stuff anyway? Ø • Use Case 1: Instruments-Only, Sub-Architectures given to integrator – result is an “inserted & verified” tradeoff-driven 1687 Architecture • Use Case 2: Whole chip with 1687 Architecture given to chip-test engineers for wafer, package, die-stack test – locating instruments, reusable or auto-generated vectors; debug & diagnostics; data-collection • Use Case 3: Multiple chips with 1687 Architectures given to board-test, systemdevelopment, or for in-system use to assess chip goodness/margins and to help board-test – locating instruments, reusable or auto-generated vectors; debug & diagnostics; data-collection; comparison to ATE test results How does it help board-test?

I’m Confused? ? ? Ø Why all the complexity? Isn’t Daisy-Chain and Star enough – it seems to be good enough for the board world… Ø …is there a difference inside the chip as opposed to outside the chip and on the board? Ø And who is supposed to use this stuff anyway? Ø How does it help board-test? • Testing complex board is no longer just about interconnect, chip orientation, and power delivery • High-Speed routes and traces must be characterized (e. g. chip-to-chip Ser. Des channels with BERT and Eye-Diagrams) • Chips must be re-verified in-situ because of different environment conditions from ATE test • This requires operating the test logic and monitors associated with and embedded within chips

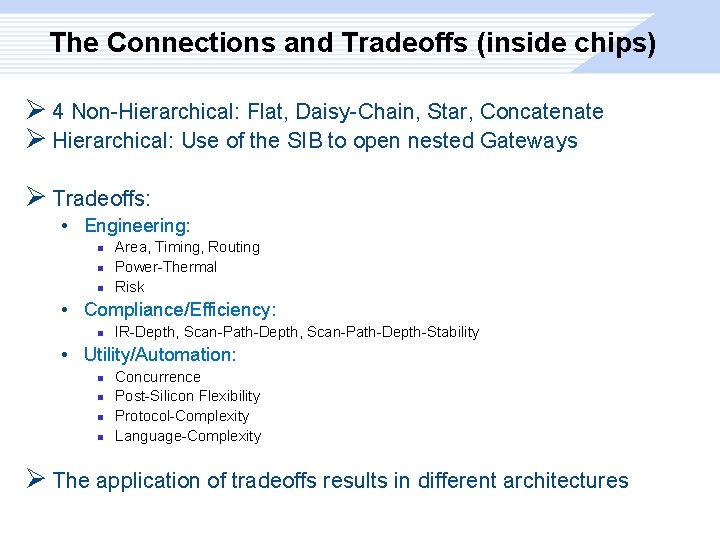

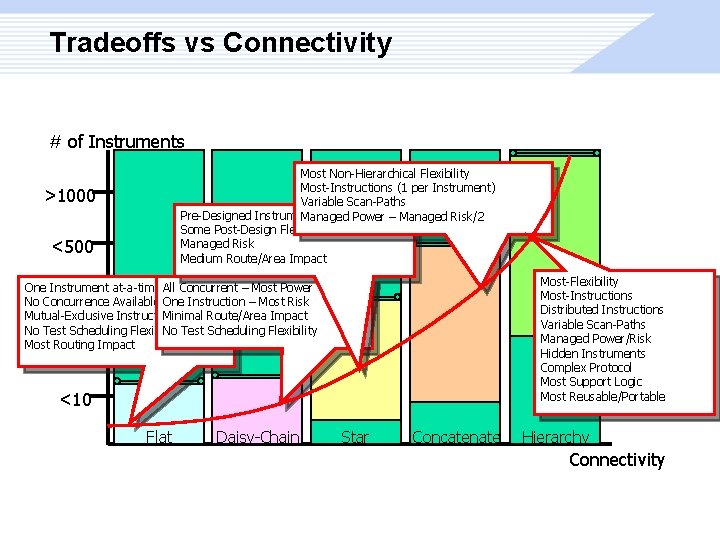

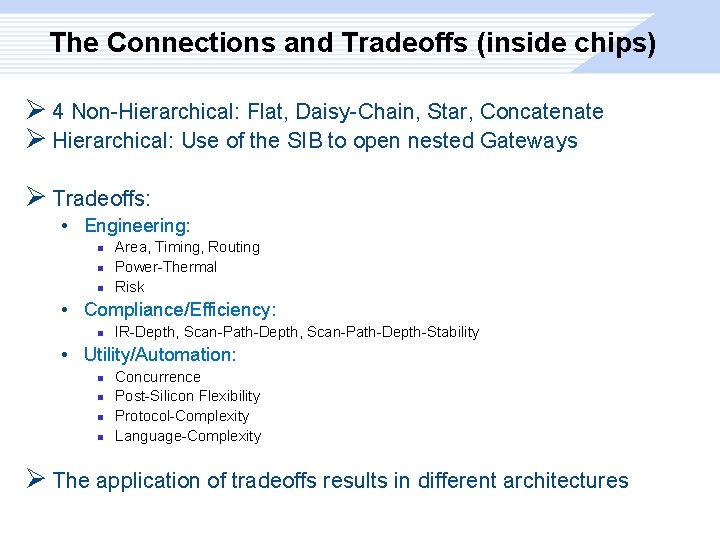

The Connections and Tradeoffs (inside chips) Ø 4 Non-Hierarchical: Flat, Daisy-Chain, Star, Concatenate Ø Hierarchical: Use of the SIB to open nested Gateways Ø Tradeoffs: • Engineering: n n n Area, Timing, Routing Power-Thermal Risk • Compliance/Efficiency: n IR-Depth, Scan-Path-Depth-Stability • Utility/Automation: n n Concurrence Post-Silicon Flexibility Protocol-Complexity Language-Complexity Ø The application of tradeoffs results in different architectures

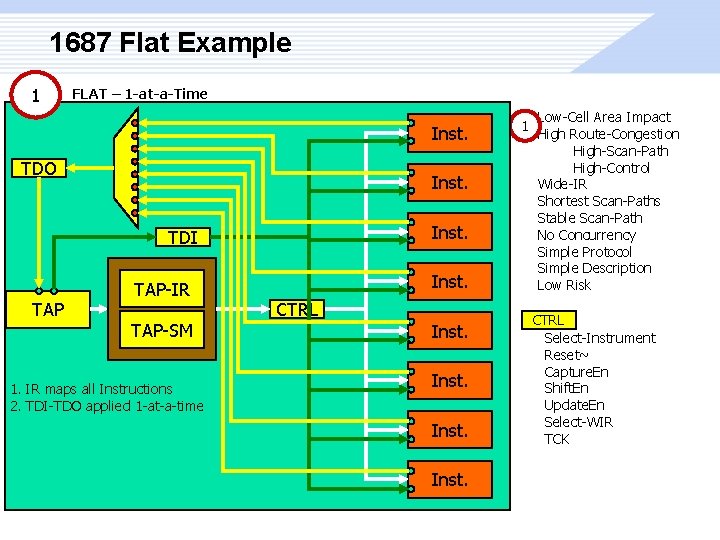

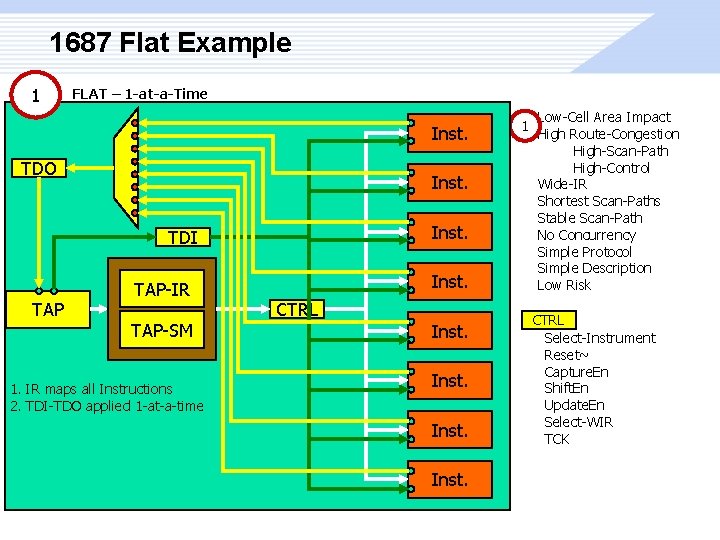

1687 Flat Example 1 FLAT – 1 -at-a-Time Inst. TDO Inst. TDI TAP-IR TAP-SM 1. IR maps all Instructions 2. TDI-TDO applied 1 -at-a-time Inst. CTRL Inst. 1 Low-Cell Area Impact High Route-Congestion High-Scan-Path High-Control Wide-IR Shortest Scan-Paths Stable Scan-Path No Concurrency Simple Protocol Simple Description Low Risk CTRL Select-Instrument Reset~ Capture. En Shift. En Update. En Select-WIR TCK

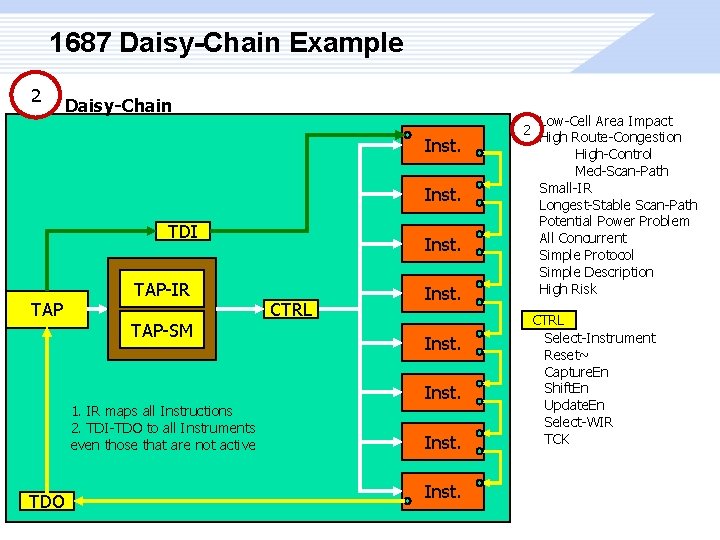

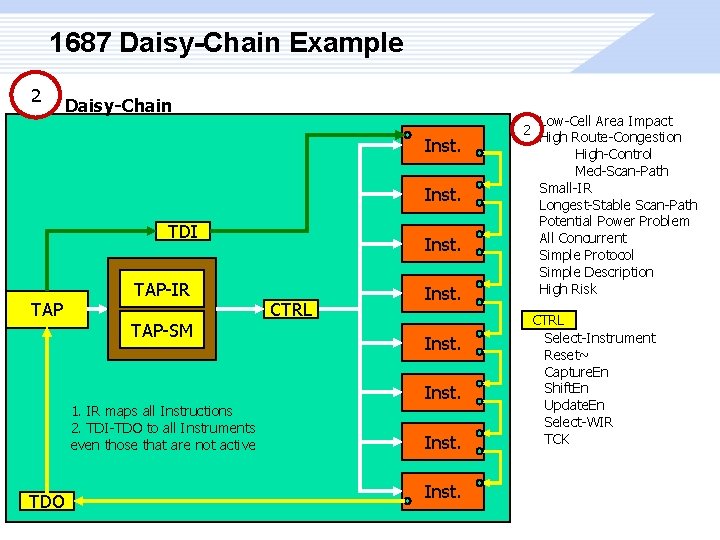

1687 Daisy-Chain Example 2 Daisy-Chain Inst. TDI TAP-IR TAP-SM 1. IR maps all Instructions 2. TDI-TDO to all Instruments even those that are not active TDO Inst. CTRL Inst. 2 Low-Cell Area Impact High Route-Congestion High-Control Med-Scan-Path Small-IR Longest-Stable Scan-Path Potential Power Problem All Concurrent Simple Protocol Simple Description High Risk CTRL Select-Instrument Reset~ Capture. En Shift. En Update. En Select-WIR TCK

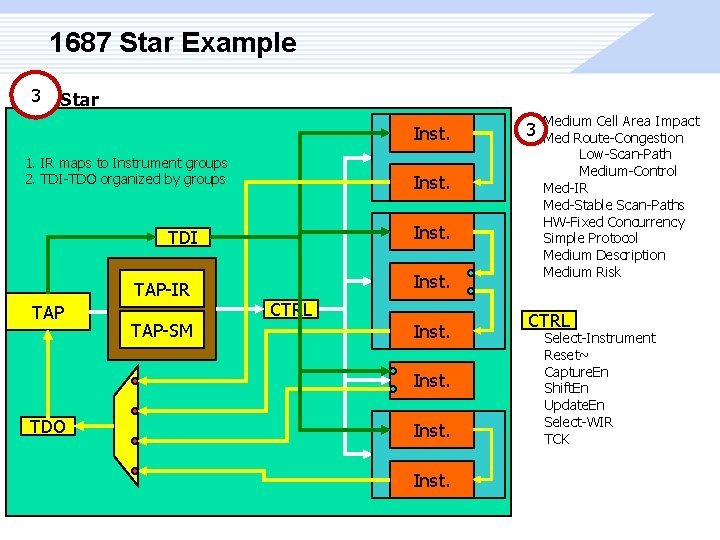

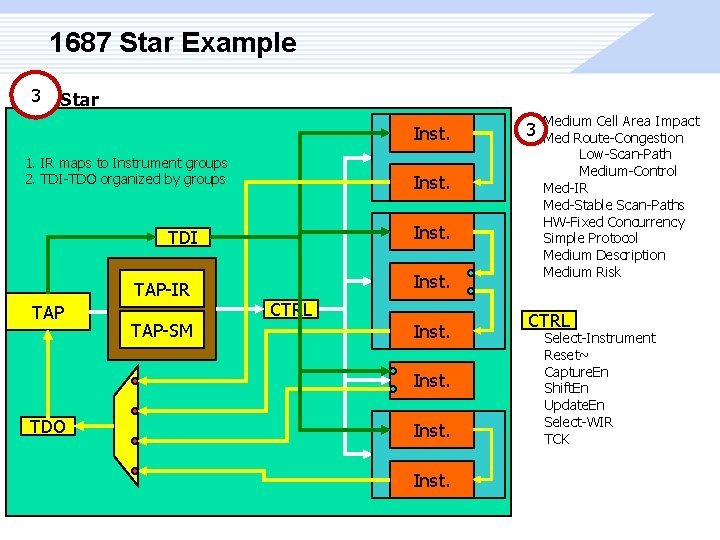

1687 Star Example 3 Star Inst. 1. IR maps to Instrument groups 2. TDI-TDO organized by groups Inst. TDI TAP-IR TAP-SM Inst. CTRL Inst. TDO Inst. 3 Medium Cell Area Impact Med Route-Congestion Low-Scan-Path Medium-Control Med-IR Med-Stable Scan-Paths HW-Fixed Concurrency Simple Protocol Medium Description Medium Risk CTRL Select-Instrument Reset~ Capture. En Shift. En Update. En Select-WIR TCK

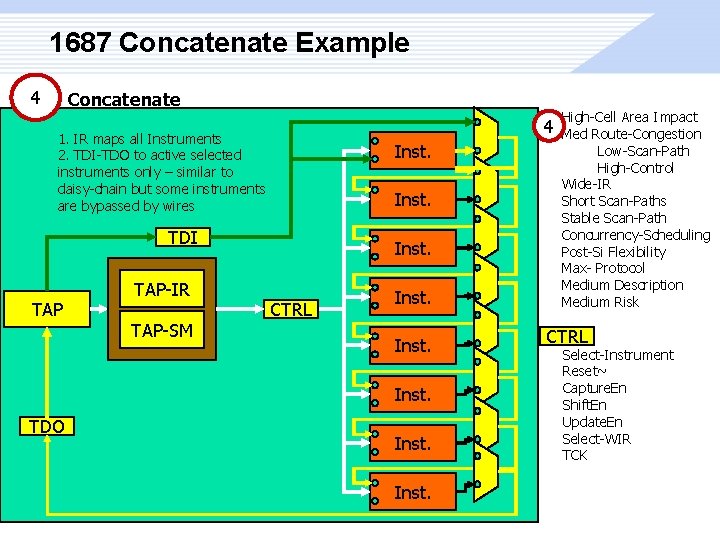

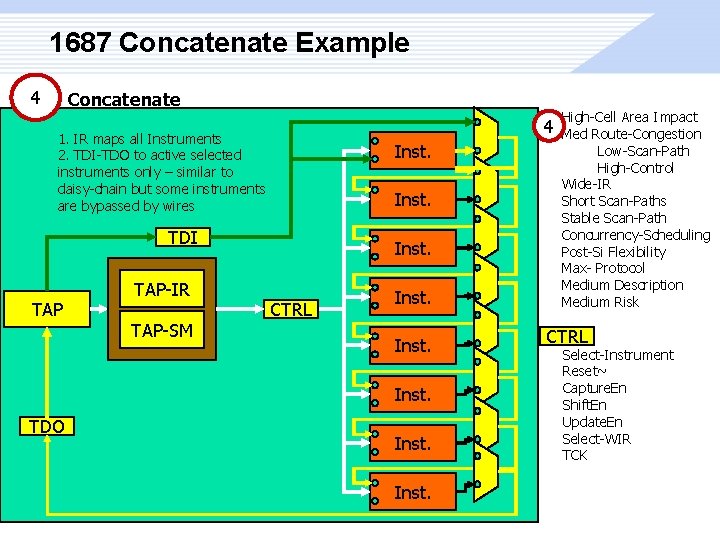

1687 Concatenate Example 4 Concatenate 4 1. IR maps all Instruments 2. TDI-TDO to active selected instruments only – similar to daisy-chain but some instruments are bypassed by wires Inst. TDI TAP-IR TAP-SM Inst. CTRL Inst. TDO Inst. High-Cell Area Impact Med Route-Congestion Low-Scan-Path High-Control Wide-IR Short Scan-Paths Stable Scan-Path Concurrency-Scheduling Post-Si Flexibility Max- Protocol Medium Description Medium Risk CTRL Select-Instrument Reset~ Capture. En Shift. En Update. En Select-WIR TCK

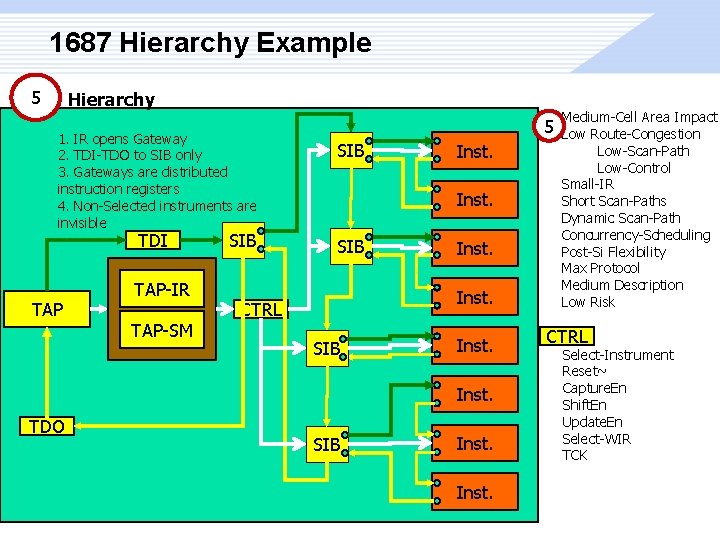

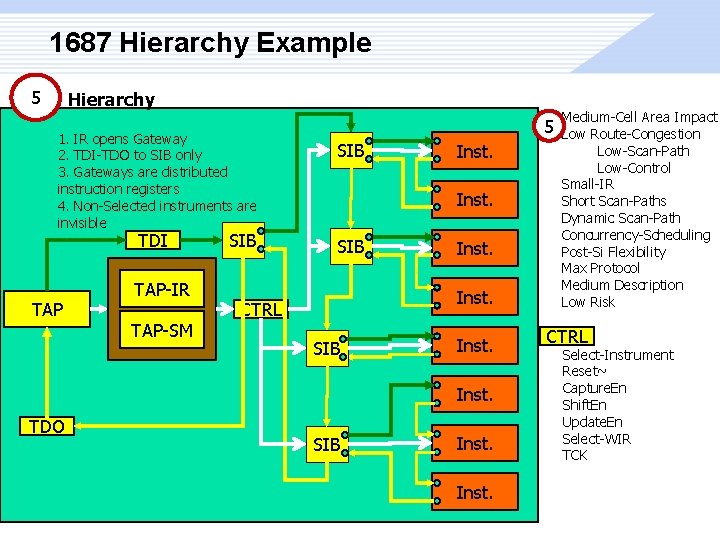

1687 Hierarchy Example 5 Hierarchy 1. IR opens Gateway 2. TDI-TDO to SIB only 3. Gateways are distributed instruction registers 4. Non-Selected instruments are invisible TDI TAP-IR TAP-SM SIB 5 SIB Inst. CTRL SIB Inst. TDO SIB Inst. Medium-Cell Area Impact Low Route-Congestion Low-Scan-Path Low-Control Small-IR Short Scan-Paths Dynamic Scan-Path Concurrency-Scheduling Post-Si Flexibility Max Protocol Medium Description Low Risk CTRL Select-Instrument Reset~ Capture. En Shift. En Update. En Select-WIR TCK

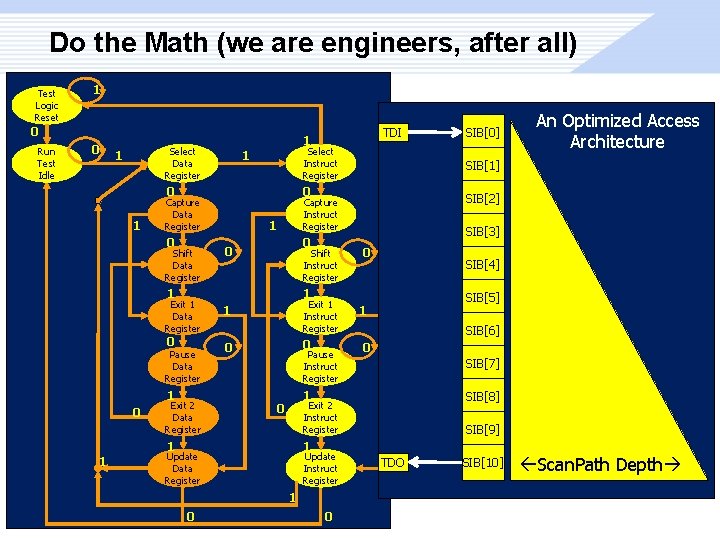

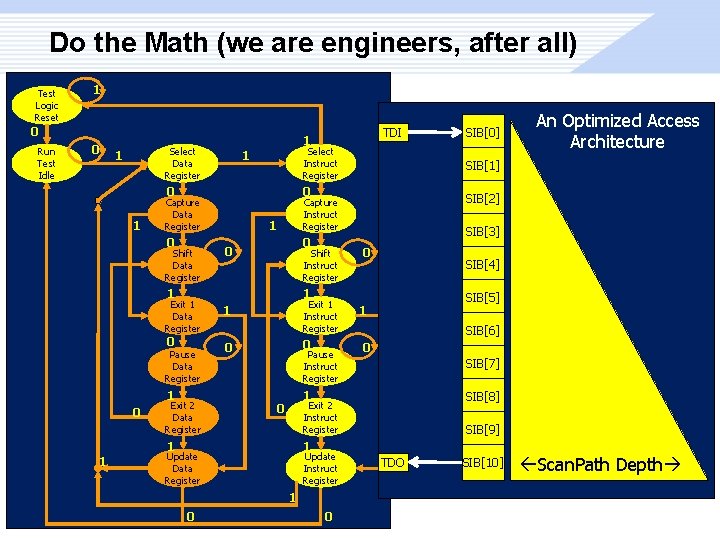

Do the Math (we are engineers, after all) Test Logic Reset 1 Ø Hierarchy –vs- Daisy-Chain: 0 Run Test Idle 0 1 TDI 1 Select Data Register SIB[0] Select 1 An Optimized Access Architecture • 5000 Bits of Daisy-Chain takes Instruct 5000 clocks each SIB[1] time an instrument is Register accessed (flush whole chain, put back whole value with modification 0 0 for 1 instrument) – 10 accesses (capture, shift, SIB[2] updates) requires Capture Instruct clocks (Se. DR, Ca. DR, Sh. DR, E 1 DR, Data 10 x 5000 shifts + 10 x 51 protocol Register 1 Register SIB[3] Up. DR) = 50050 clocks 0 0 Shift Data Register 0 Shift Instruct Register 0 SIB[4] • With 50 Bits of L-0 SIBs and each Bit expands to 100 Bits of L-1 SIBs 1 1 Hierarchy – addressing SIB[5] – is 5000 Bits the worst case Exit 1 in 2 -Levels of Exit 1 1 1 Instructis 50 Shifts + 5 Protocol Clocks to open instrument. Data (farthest from TDI) Register SIB[6] the 50 th L-0 then shifting 150 Bits to reach the last instrument in 0 SIB; 0 0 0 the chain; Pause times 10 accesses Pauseresults in 55+10 x 150=1555 clocks SIB[7] Data Register Instruct Register 1 optimal hierarchical 1 • Better more architectures. SIB[8] are easily possible – Exit 2 0 0 Data Instruct instruments that need to be accessed a lot should be nearest SIB Register Bit[1] of the Level-0 Gateway; earlier hierarchy. SIB[9] levels should have 1 1 shorter registers – the image should. TDO look like SIB[10] a right-triangle Update 1 Data Register Instruct Register 1 0 0 Scan. Path Depth

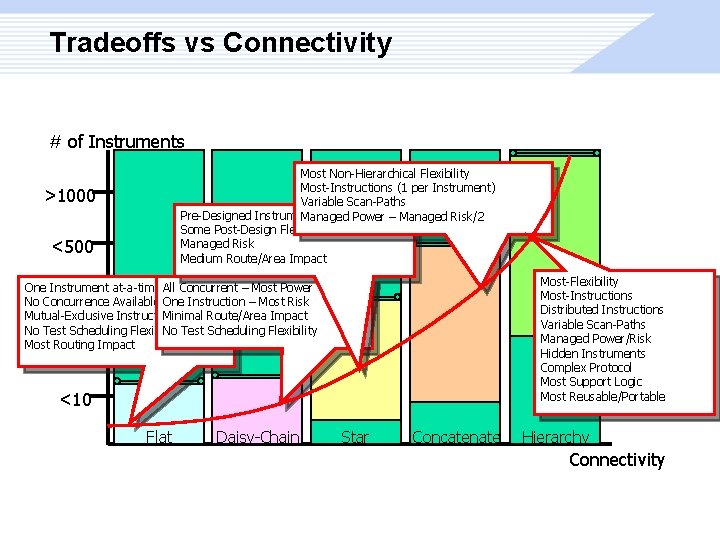

Tradeoffs vs Connectivity # of Instruments Most Non-Hierarchical Flexibility Most-Instructions (1 per Instrument) Variable Scan-Paths Pre-Designed Instrument Groups. Power – Managed Risk/2 Managed Some Post-Design Flexibility Managed Risk Medium Route/Area Impact >1000 <500 Most-Flexibility Most-Instructions Distributed Instructions Variable Scan-Paths Managed Power/Risk Hidden Instruments Complex Protocol Most Support Logic Most Reusable/Portable One Instrument at-a-time All Concurrent – Most Power <100 Available One Instruction – Most Risk No Concurrence Mutual-Exclusive Instructions Minimal Route/Area Impact No Test Scheduling Flexibility Most Routing <50 Impact <10 Flat Daisy-Chain Star Concatenate Hierarchy Connectivity

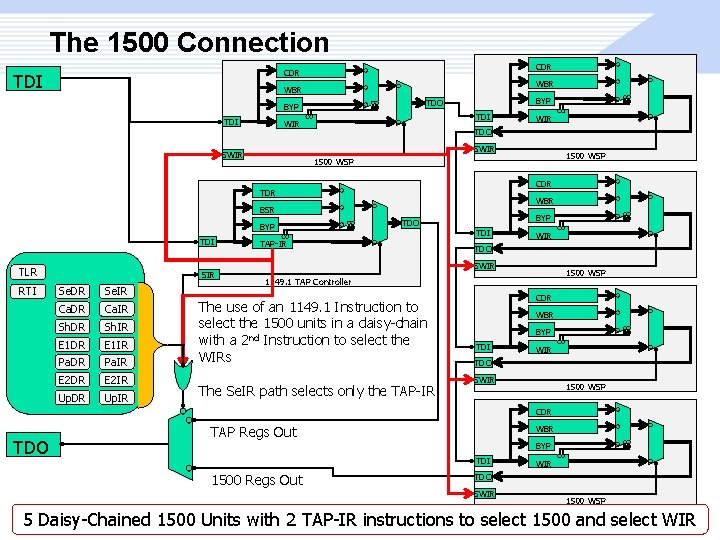

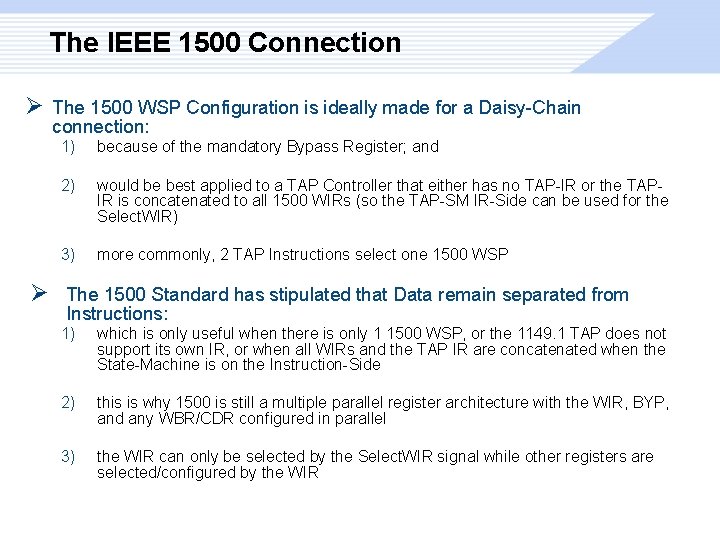

The IEEE 1500 Connection Ø Ø The 1500 WSP Configuration is ideally made for a Daisy-Chain connection: 1) because of the mandatory Bypass Register; and 2) would be best applied to a TAP Controller that either has no TAP-IR or the TAPIR is concatenated to all 1500 WIRs (so the TAP-SM IR-Side can be used for the Select. WIR) 3) more commonly, 2 TAP Instructions select one 1500 WSP The 1500 Standard has stipulated that Data remain separated from Instructions: 1) which is only useful when there is only 1 1500 WSP, or the 1149. 1 TAP does not support its own IR, or when all WIRs and the TAP IR are concatenated when the State-Machine is on the Instruction-Side 2) this is why 1500 is still a multiple parallel register architecture with the WIR, BYP, and any WBR/CDR configured in parallel 3) the WIR can only be selected by the Select. WIR signal while other registers are selected/configured by the WIR

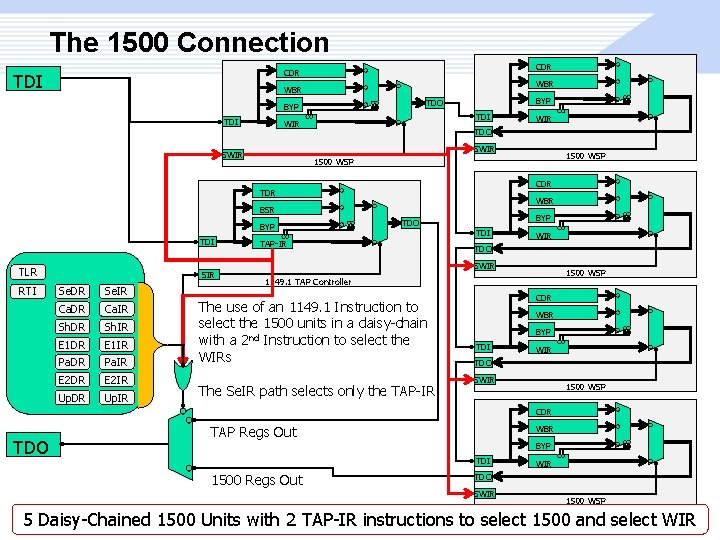

The 1500 Connection CDR TDI WBR TDI BYP TDO BYP TDI WIR SWIR CDR WBR BSR BYP TLR RTI SIR Se. DR Se. IR Ca. DR Ca. IR Sh. DR Sh. IR E 1 DR E 1 IR Pa. DR Pa. IR E 2 DR E 2 IR Up. DR Up. IR 1500 WSP TDR TDI WIR TDO TAP-IR BYP TDI WIR TDO SWIR 1500 WSP 1149. 1 TAP Controller The use of an 1149. 1 Instruction to select the 1500 units in a daisy-chain with a 2 nd Instruction to select the WIRs The Se. IR path selects only the TAP-IR CDR WBR BYP TDI WIR TDO SWIR 1500 WSP CDR TDO TAP Regs Out WBR BYP TDI 1500 Regs Out WIR TDO SWIR 1500 WSP 5 Daisy-Chained 1500 Units with 2 TAP-IR instructions to select 1500 and select WIR

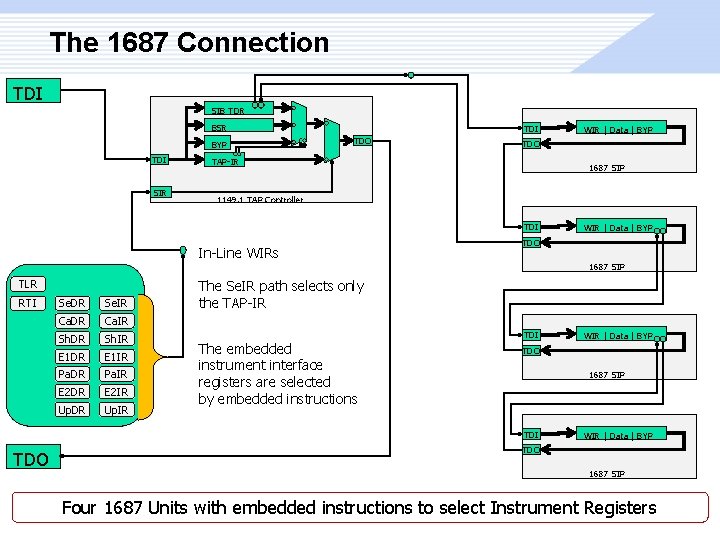

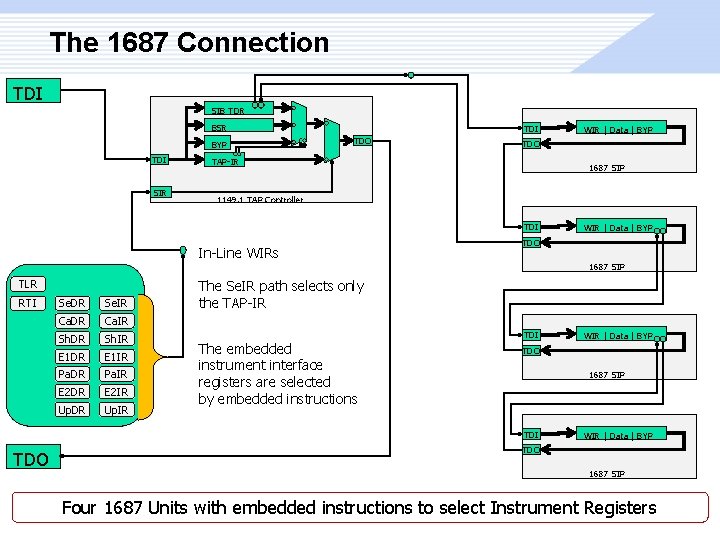

The 1687 Connection TDI SIB TDR BSR BYP TDI SIR TDI TDO WIR | Data | BYP TDO TAP-IR 1687 SIP 1149. 1 TAP Controller TDI In-Line WIRs WIR | Data | BYP TDO 1687 SIP TLR RTI Se. DR Se. IR Ca. DR Ca. IR Sh. DR Sh. IR E 1 DR E 1 IR Pa. DR Pa. IR E 2 DR E 2 IR Up. DR Up. IR The Se. IR path selects only the TAP-IR The embedded instrument interface registers are selected by embedded instructions TDI TDO 1687 SIP TDI TDO WIR | Data | BYP TDO 1687 SIP Four 1687 Units with embedded instructions to select Instrument Registers

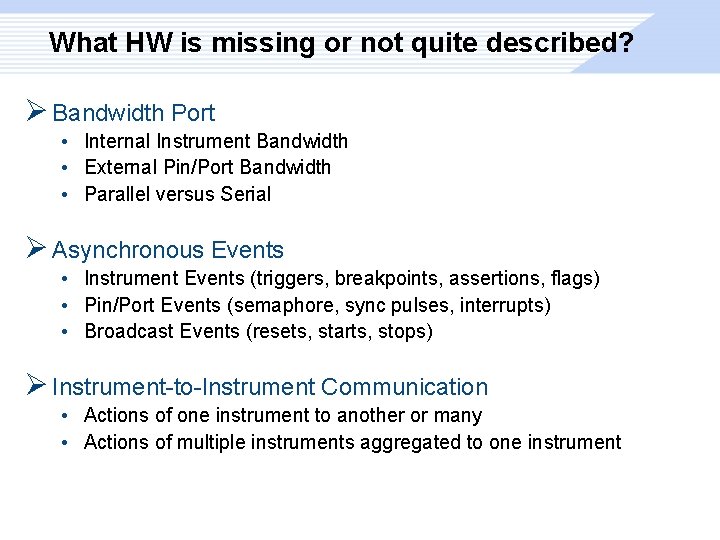

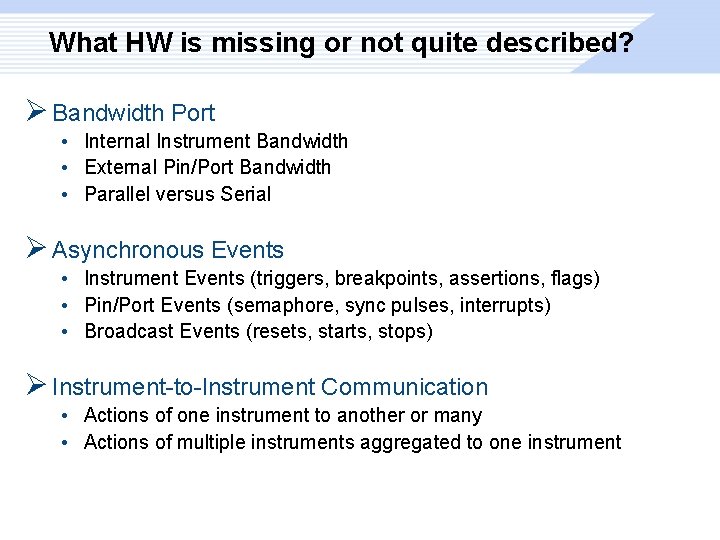

What HW is missing or not quite described? Ø Bandwidth Port • Internal Instrument Bandwidth • External Pin/Port Bandwidth • Parallel versus Serial Ø Asynchronous Events • Instrument Events (triggers, breakpoints, assertions, flags) • Pin/Port Events (semaphore, sync pulses, interrupts) • Broadcast Events (resets, starts, stops) Ø Instrument-to-Instrument Communication • Actions of one instrument to another or many • Actions of multiple instruments aggregated to one instrument

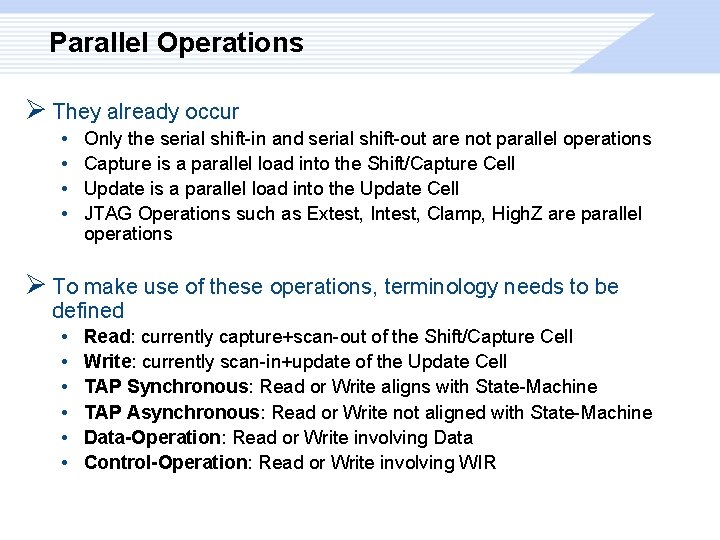

But “Serial and JTAG-Like” Isn’t Enough!!! Ø Many have expressed concerned with Bandwidth and non 1149. 1 Sequences • More instruments means more data – need higher bandwidth for some instruments • Coordination between instruments – need instrument-to-instrument communication • Non-1149. 1 Operations – need to conduct and describe TAPasynchronous instrument operations such as a “fail flag” or “action trigger” that occurs when a fail happens, not when the State. Machine happens to be in Capture-DR (e. g. capture the comparator bus immediately if a fail is detected)

Parallel Operations Ø They already occur • • Only the serial shift-in and serial shift-out are not parallel operations Capture is a parallel load into the Shift/Capture Cell Update is a parallel load into the Update Cell JTAG Operations such as Extest, Intest, Clamp, High. Z are parallel operations Ø To make use of these operations, terminology needs to be defined • • • Read: currently capture+scan-out of the Shift/Capture Cell Write: currently scan-in+update of the Update Cell TAP Synchronous: Read or Write aligns with State-Machine TAP Asynchronous: Read or Write not aligned with State-Machine Data-Operation: Read or Write involving Data Control-Operation: Read or Write involving WIR

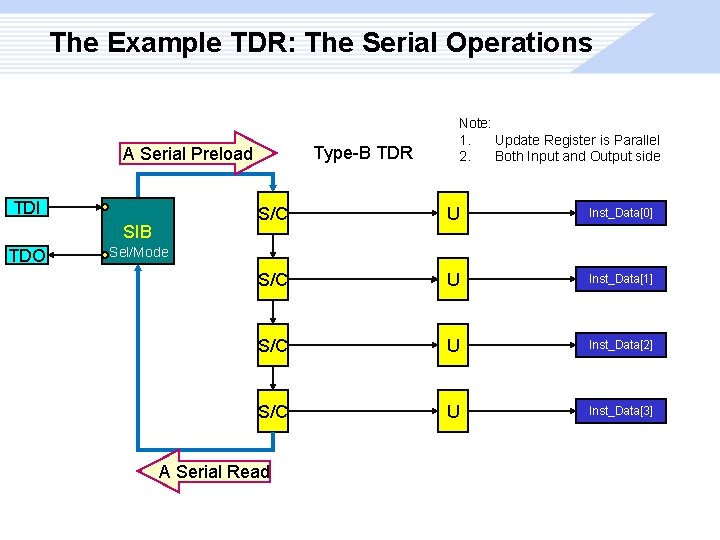

Parallel Notes Ø How does this replace a non-JTAG Instrument Interface? • Loading/Reading/Writing the parallel registers directly turns a multiclock-cycle serial operation into a single-clock-cycle operation – Bandwidth • Parallel Reads and Writes that are TAP-Synchronous use TCK to synchronize the data transfers • Parallel Reads and Writes that are not TAP-Synchronous can use any clock or trigger to synchronize the data transfers • Instruments can create the triggers that other instruments would use to conduct data/control transfers – facilitates Instrument-to. Instrument communication

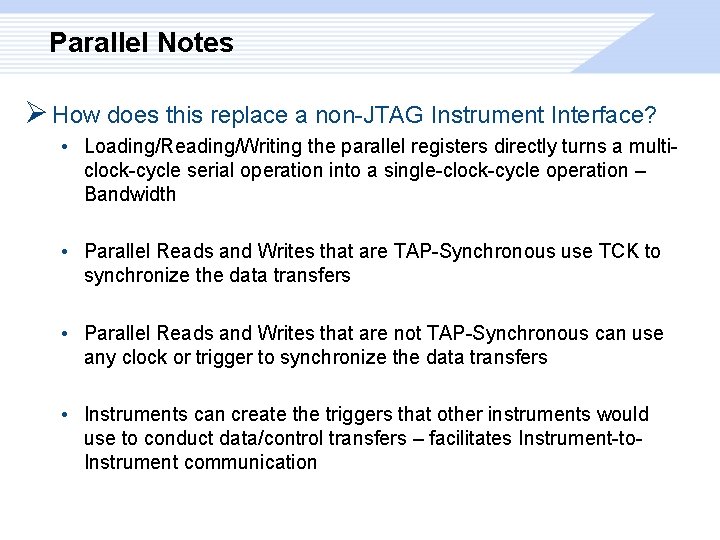

The Example TDR: The Serial Operations Type-B TDR A Serial Preload TDI SIB TDO Note: 1. Update Register is Parallel 2. Both Input and Output side S/C U Inst_Data[0] S/C U Inst_Data[1] S/C U Inst_Data[2] S/C U Inst_Data[3] Sel/Mode A Serial Read

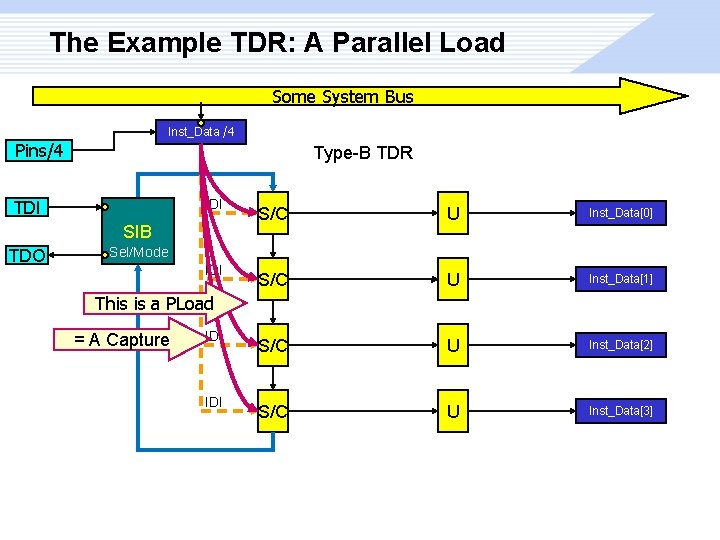

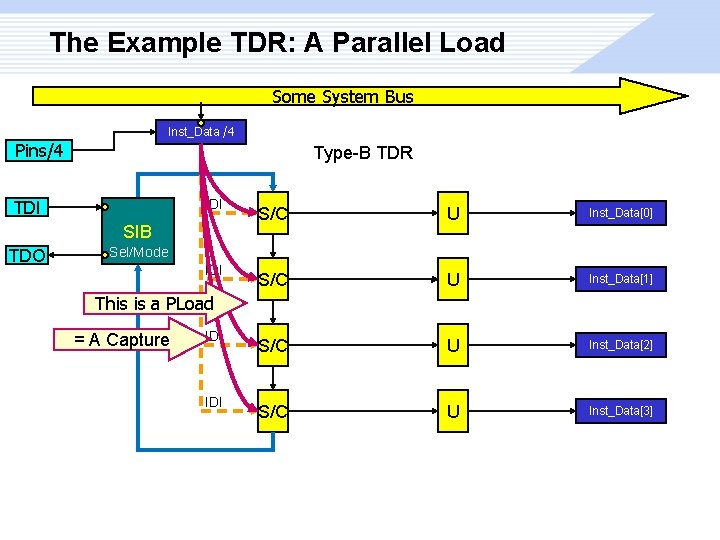

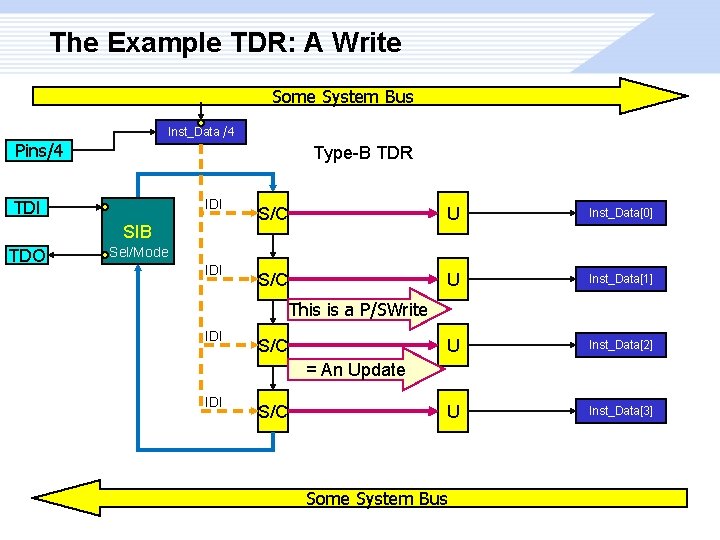

The Example TDR: A Parallel Load Some System Bus Inst_Data /4 Pins/4 Type-B TDR TDI IDI S/C U Inst_Data[0] IDI S/C U Inst_Data[1] IDI S/C U Inst_Data[2] IDI S/C U Inst_Data[3] SIB TDO Sel/Mode This is a PLoad = A Capture

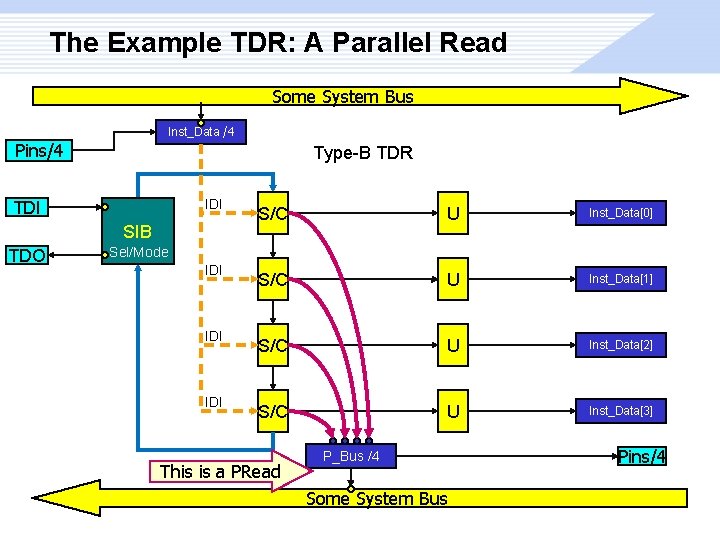

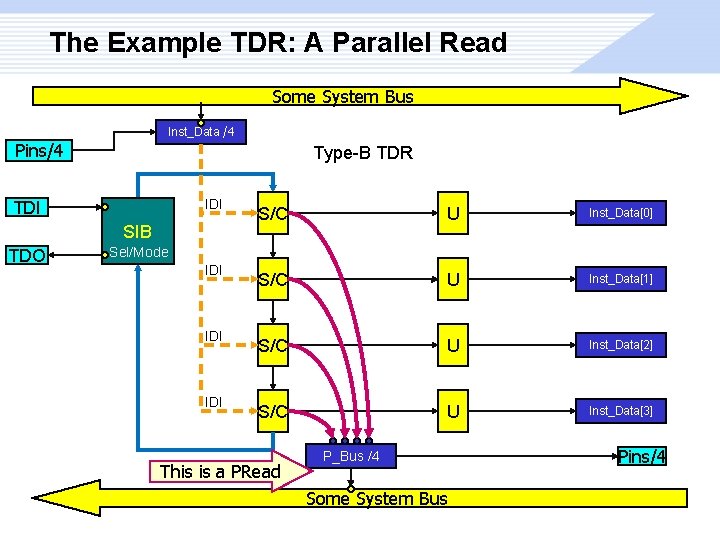

The Example TDR: A Parallel Read Some System Bus Inst_Data /4 Pins/4 Type-B TDR TDI IDI S/C U Inst_Data[0] IDI S/C U Inst_Data[1] IDI S/C U Inst_Data[2] IDI S/C U Inst_Data[3] SIB TDO Sel/Mode This is a PRead P_Bus /4 Some System Bus Pins/4

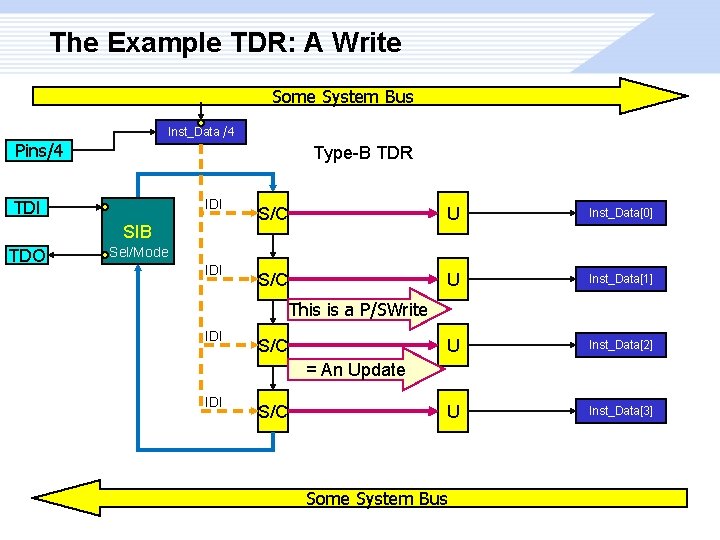

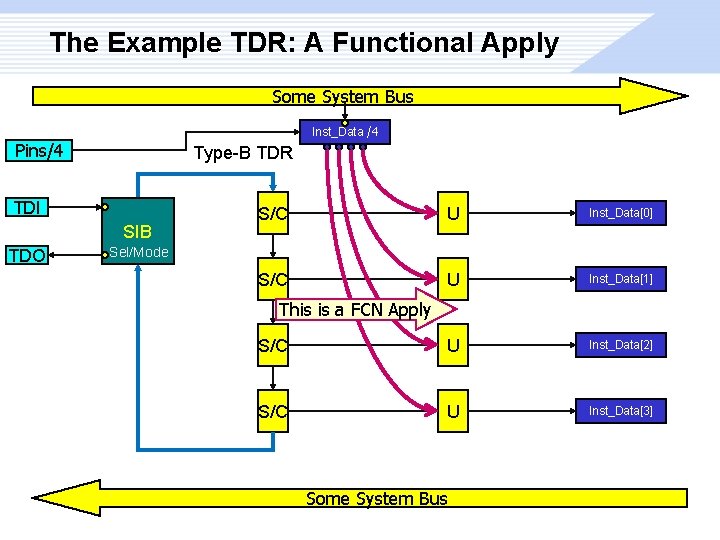

The Example TDR: A Write Some System Bus Inst_Data /4 Pins/4 Type-B TDR TDI IDI S/C U Inst_Data[0] IDI S/C U Inst_Data[1] U Inst_Data[2] U Inst_Data[3] SIB TDO Sel/Mode This is a P/SWrite IDI S/C = An Update IDI S/C Some System Bus

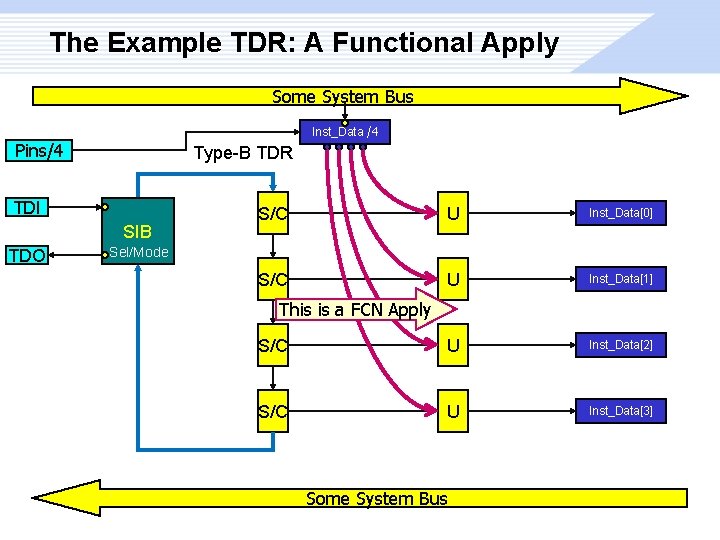

The Example TDR: A Functional Apply Some System Bus Inst_Data /4 Pins/4 Type-B TDR TDI SIB TDO S/C U Inst_Data[0] S/C U Inst_Data[1] S/C U Inst_Data[2] S/C U Inst_Data[3] Sel/Mode This is a FCN Apply Some System Bus

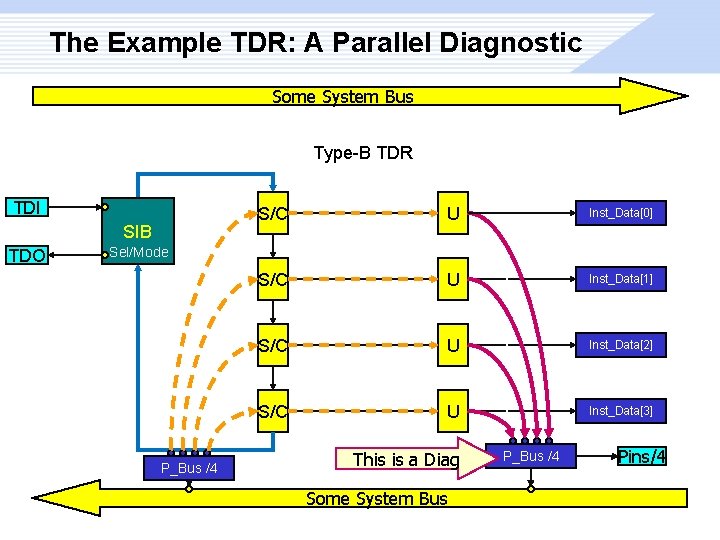

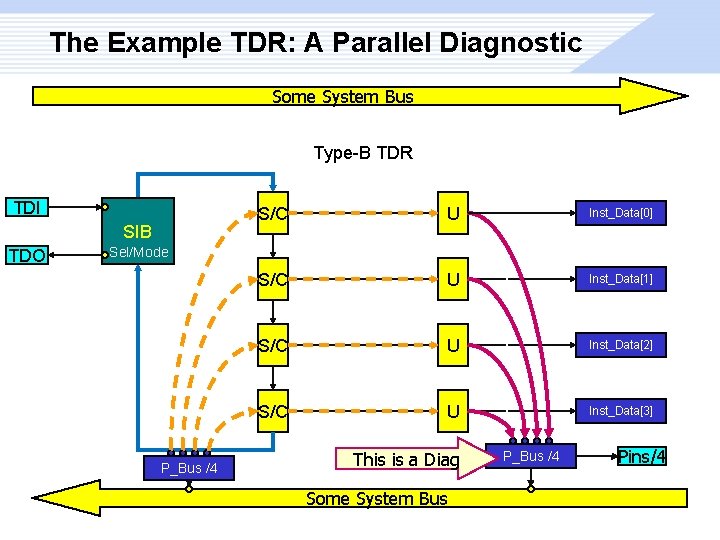

The Example TDR: A Parallel Diagnostic Some System Bus Type-B TDR TDI SIB TDO S/C U Inst_Data[0] S/C U Inst_Data[1] S/C U Inst_Data[2] S/C U Inst_Data[3] Sel/Mode P_Bus /4 This is a Diag Some System Bus P_Bus /4 Pins/4

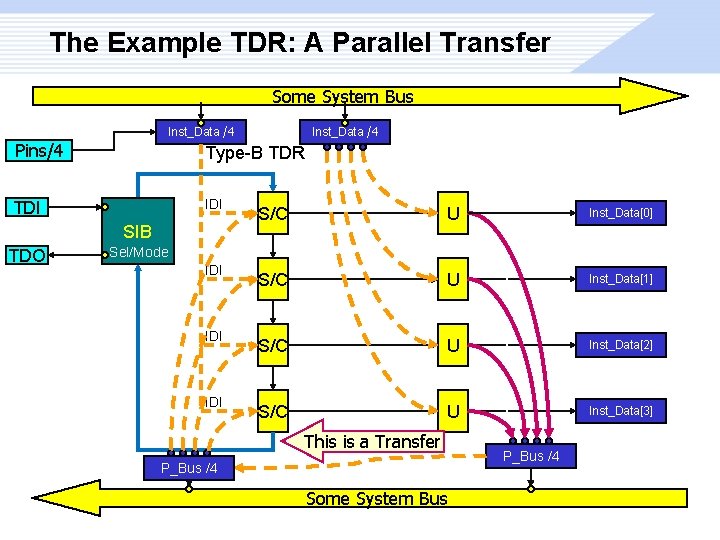

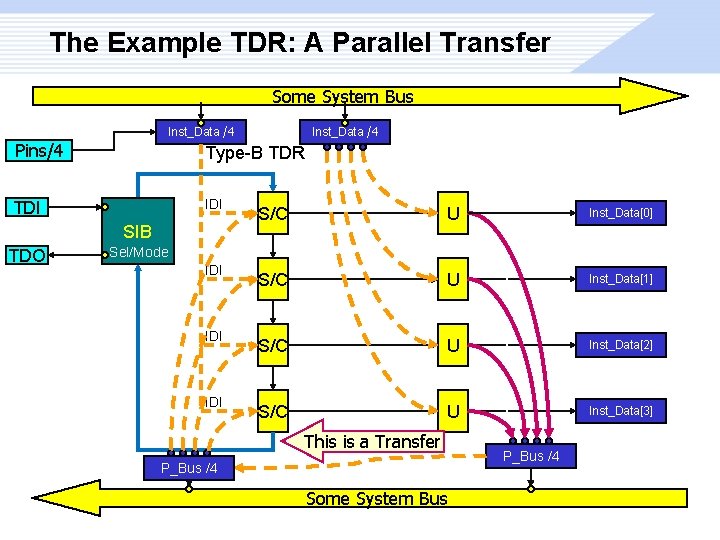

The Example TDR: A Parallel Transfer Some System Bus Inst_Data /4 Pins/4 Type-B TDR TDI IDI S/C U Inst_Data[0] IDI S/C U Inst_Data[1] IDI S/C U Inst_Data[2] IDI S/C U Inst_Data[3] SIB TDO Sel/Mode This is a Transfer P_Bus /4 Some System Bus P_Bus /4

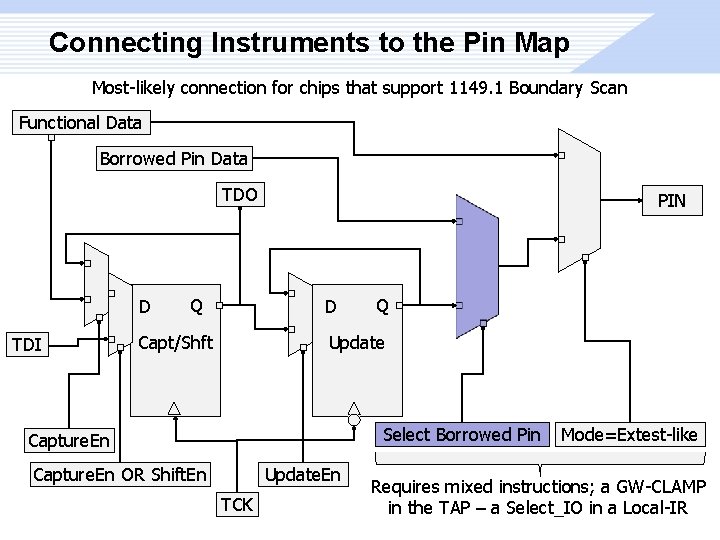

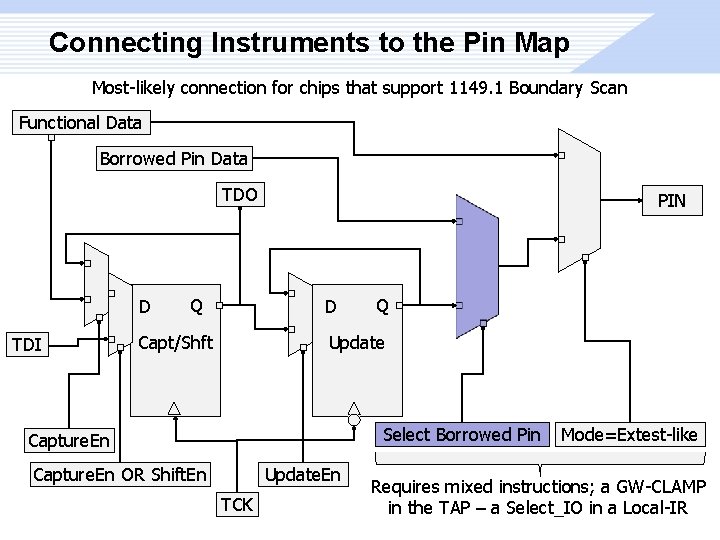

Connecting Instruments to the Pin Map Most-likely connection for chips that support 1149. 1 Boundary Scan Functional Data Borrowed Pin Data TDO D TDI Q PIN D Capt/Shft Q Update Select Borrowed Pin Capture. En OR Shift. En Update. En TCK Mode=Extest-like Requires mixed instructions; a GW-CLAMP in the TAP – a Select_IO in a Local-IR

I’m Board… Ø Let’s look at how this impacts the board-level today…

![TriplePoint Diagram PVTF Temperature Cost Limits ATE Test to minimum PVTF points ATE Test Triple-Point Diagram [PVTF] Temperature Cost Limits ATE Test to minimum PVTF points ATE Test](https://slidetodoc.com/presentation_image_h/b85ce7423a9177dcc41e57bebbece8fa/image-46.jpg)

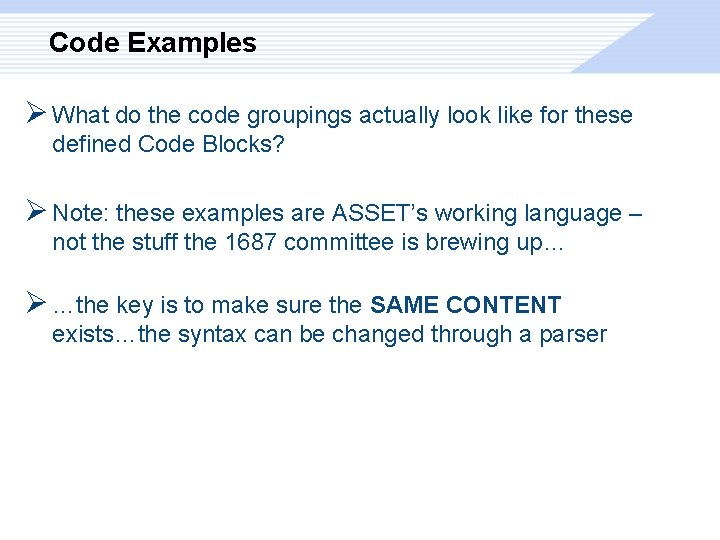

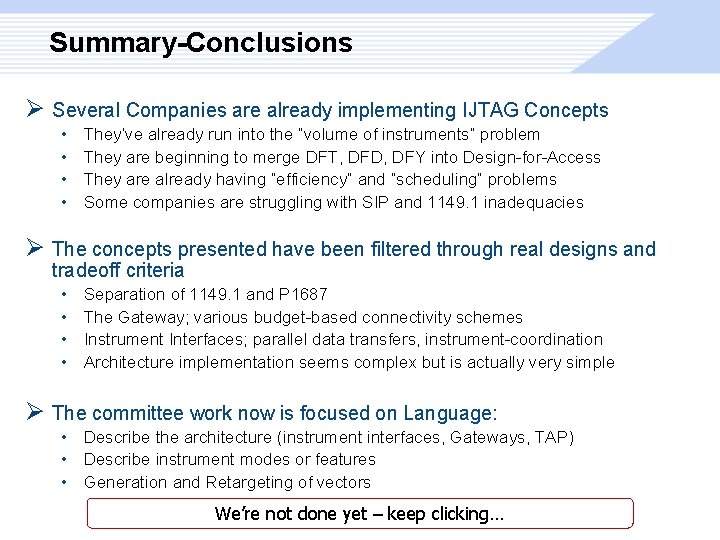

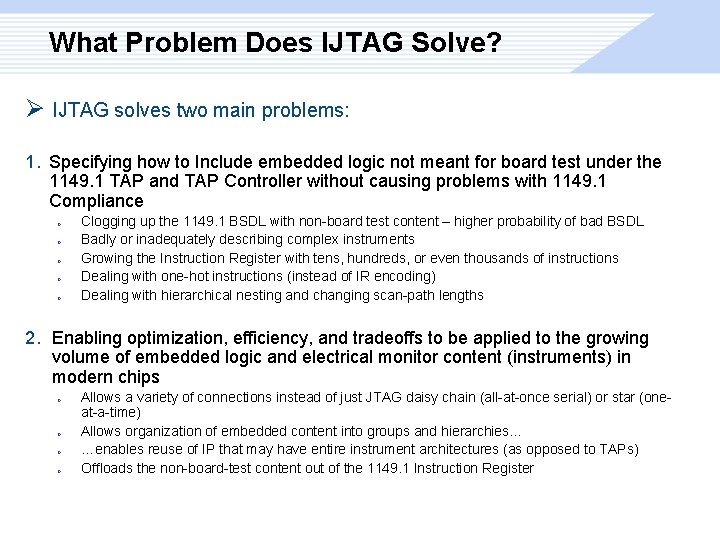

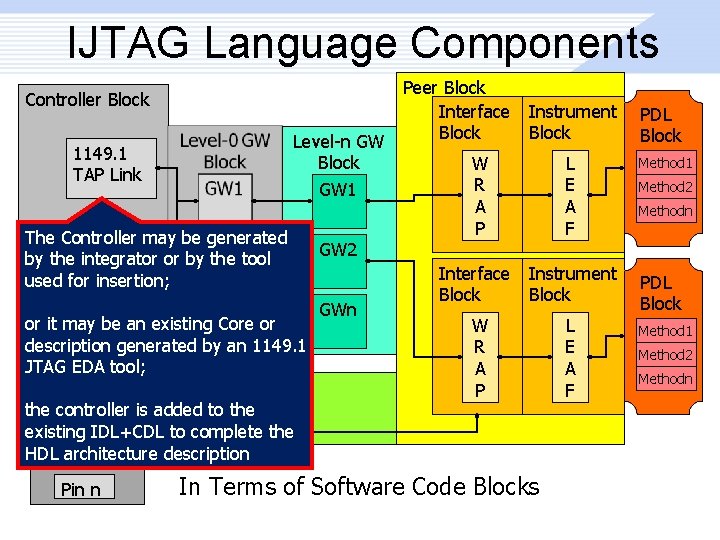

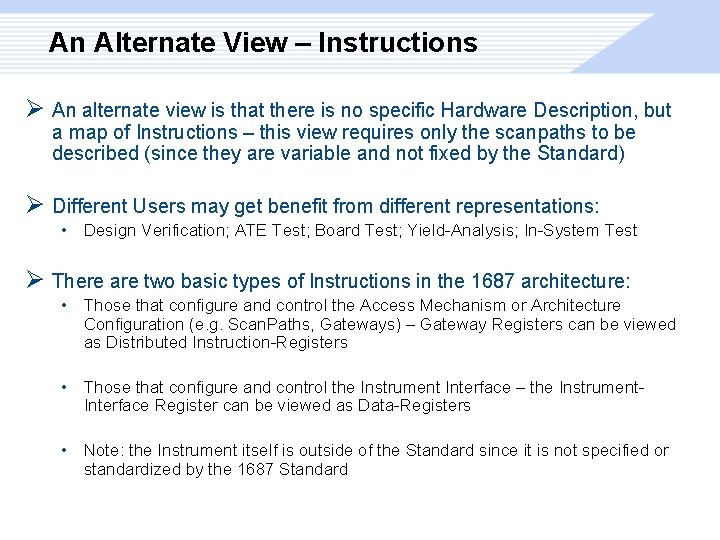

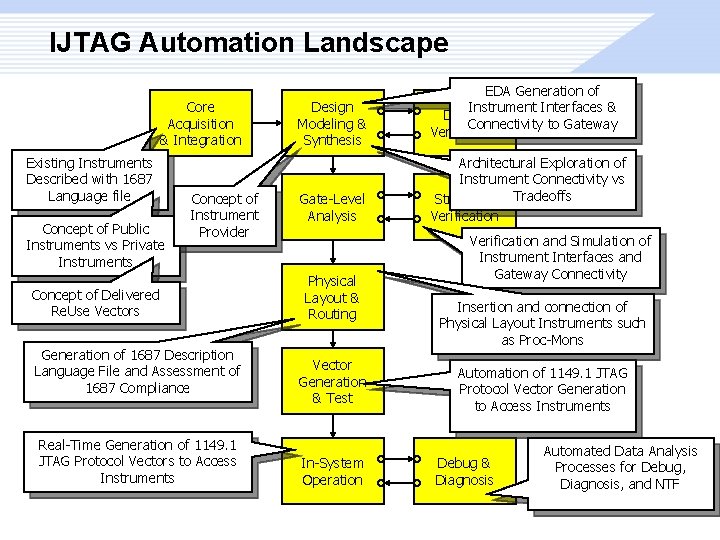

Triple-Point Diagram [PVTF] Temperature Cost Limits ATE Test to minimum PVTF points ATE Test Location Board Operation Location Frequency/Process Voltage Must correlate fails found at Board/System operation to ATE Test to avoid parametric NTF (No Trouble Found or Fail not Repeatable) Must give Silicon Provider fail information in context Silicon Provider must adjust Mfg Process or must adjust test to screen closer to Board/System operation point In a Disaggregated World: must trace Systematic Si problems back to ultimate provider – Si Library, EDA Tool, Core Provider, Chip-Stack, Die-Provider, Design Organization, Mask, Fab, Package…

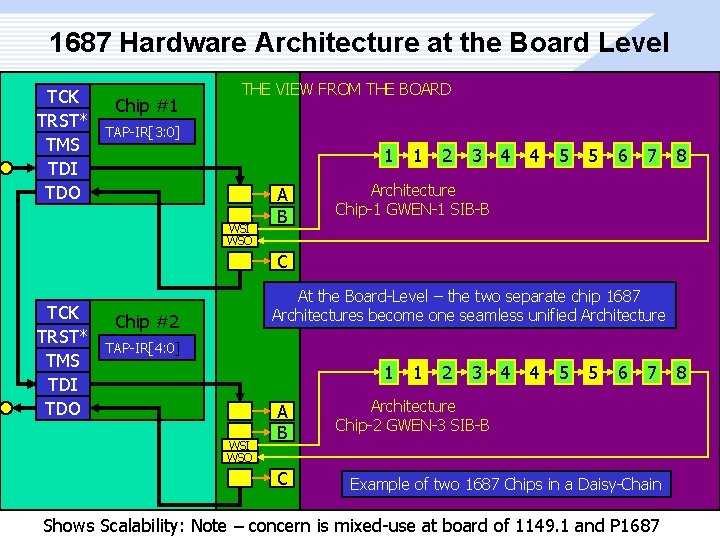

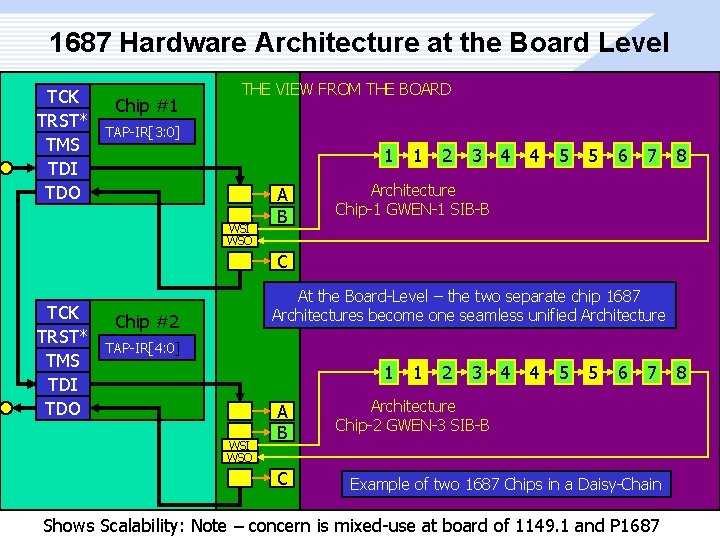

1687 Hardware Architecture at the Board Level TCK TRST* TMS TDI TDO Chip #1 THE VIEW FROM THE BOARD TAP-IR[3: 0] 1 WSI WSO A B 1 2 3 4 4 5 5 6 7 8 Architecture Chip-1 GWEN-1 SIB-B C TCK TRST* TMS TDI TDO At the Board-Level – the two separate chip 1687 Architectures become one seamless unified Architecture Chip #2 TAP-IR[4: 0] 1 WSI WSO A B C 1 2 3 4 4 5 5 6 7 Architecture Chip-2 GWEN-3 SIB-B Example of two 1687 Chips in a Daisy-Chain Shows Scalability: Note – concern is mixed-use at board of 1149. 1 and P 1687 8

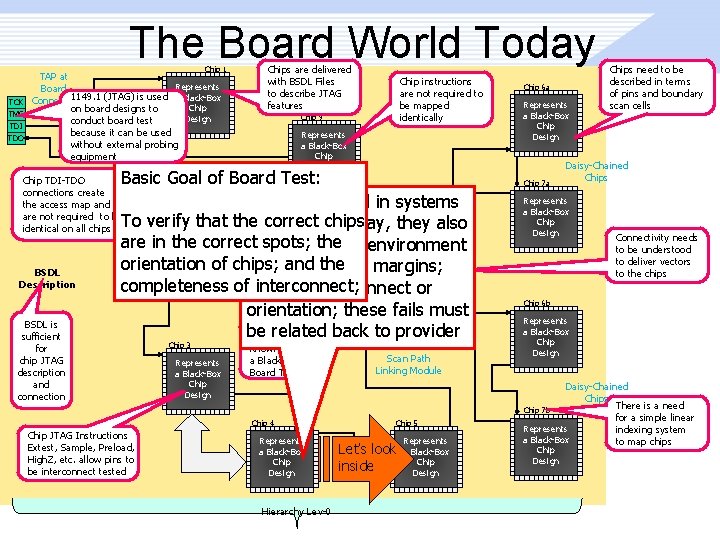

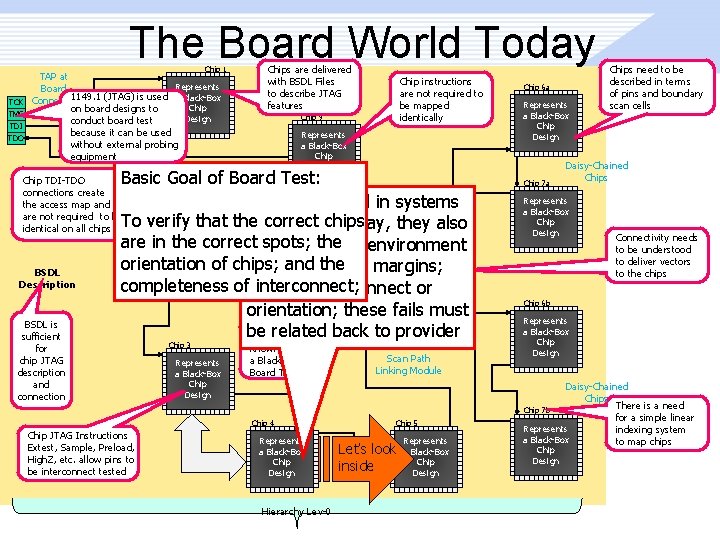

The Board World Today Chip 1 TCK TMS TDI TDO TAP at Represents Board 1149. 1 (JTAG) is used a Black-Box Connector Chip on board designs to Design conduct board test because it can be used without external probing equipment Chips are delivered with BSDL Files to describe JTAG features Chip instructions are not required to be mapped identically Chip 9 Represents a Black-Box Chip Design Basic Goal of Board Test: When Chips fail in systems To verify that the correct chips and boards today, they also Groupings or Chip 2 Chip 8 Star Connections are in the correct the of may failspots; because environment Represents impose a Black-Box mutual-exclusivity orientation and And parametric margins; Chip of chips; Chip the Design completeness ofnot interconnect; just interconnect or Mux 1 fails must orientation; these a Inside-the-Chip be related back to bprovider is generally not Chip TDI-TDO connections create the access map and are not required to be identical on all chips BSDL Description BSDL is sufficient for chip JTAG description and connection Chip 3 Represents a Black-Box Chip Design known and so is a Black-Box at Board Test Chip 4 Chip JTAG Instructions Extest, Sample, Preload, High. Z, etc. allow pins to be interconnect tested Represents a Black-Box Chip Design Hierarchy Lev-0 Scan Path Linking Module Chip 5 Let’s look inside Represents a Black-Box Chip Design Chip 6 a Represents a Black-Box Chip Design Chip 7 a Chips need to be described in terms of pins and boundary scan cells Daisy-Chained Chips Represents a Black-Box Chip Design Connectivity needs to be understood to deliver vectors to the chips Chip 6 b Represents a Black-Box Chip Design Daisy-Chained Chips There is a need Chip 7 b for a simple linear Represents indexing system a Black-Box to map chips Chip Design

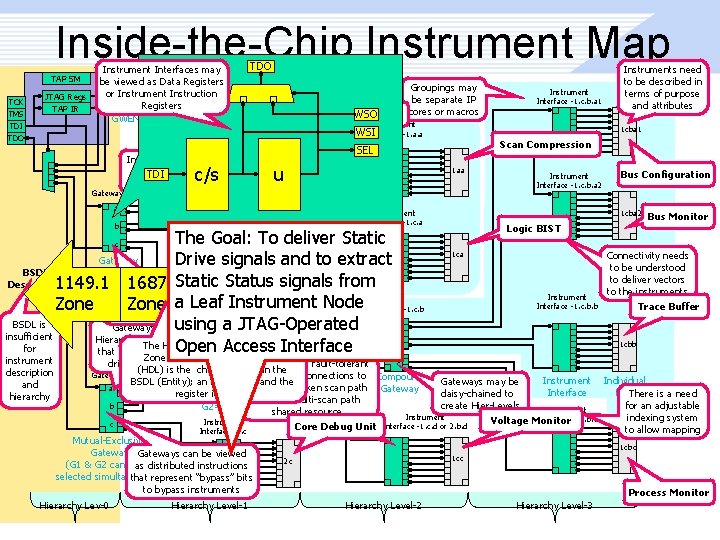

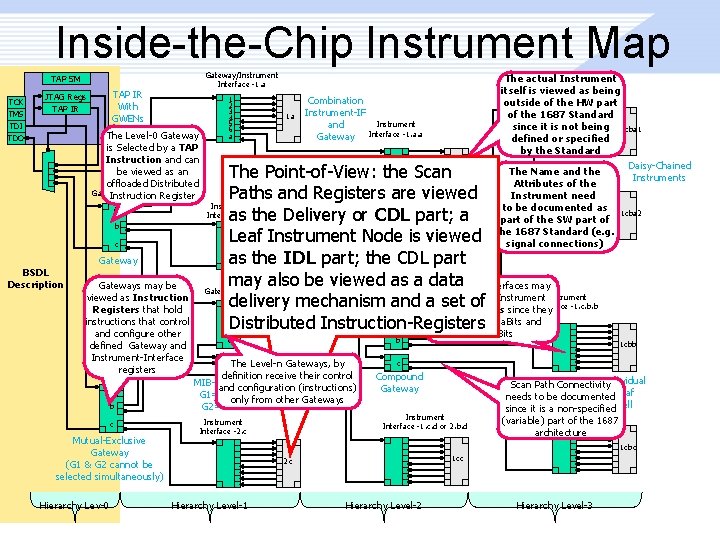

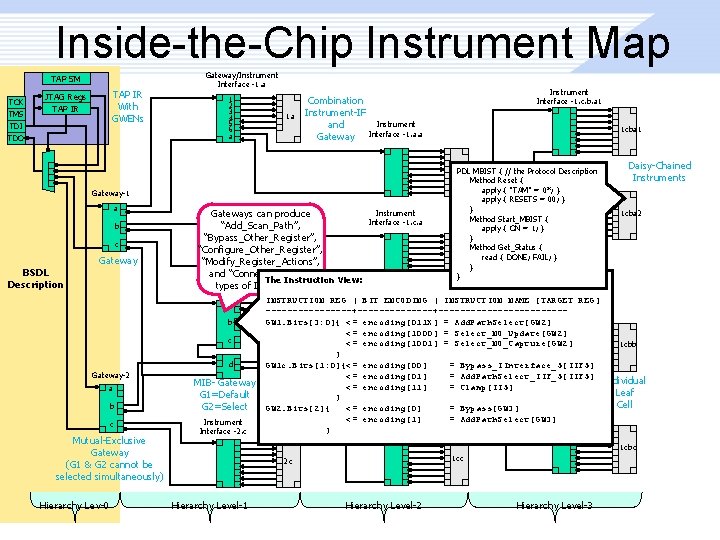

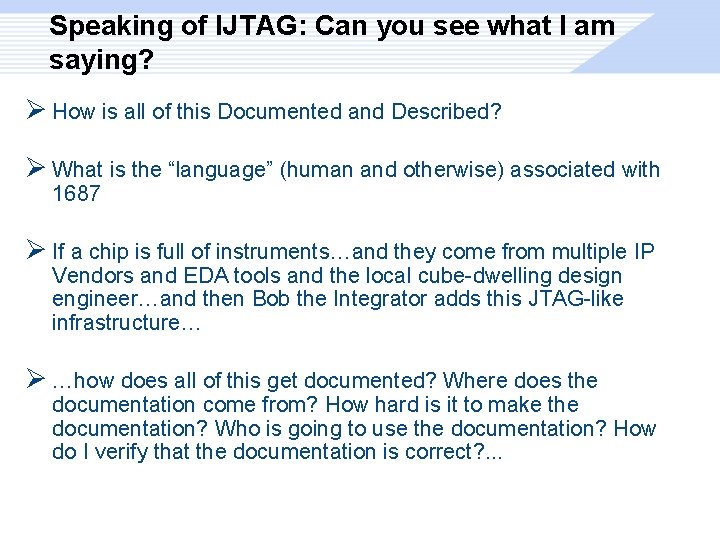

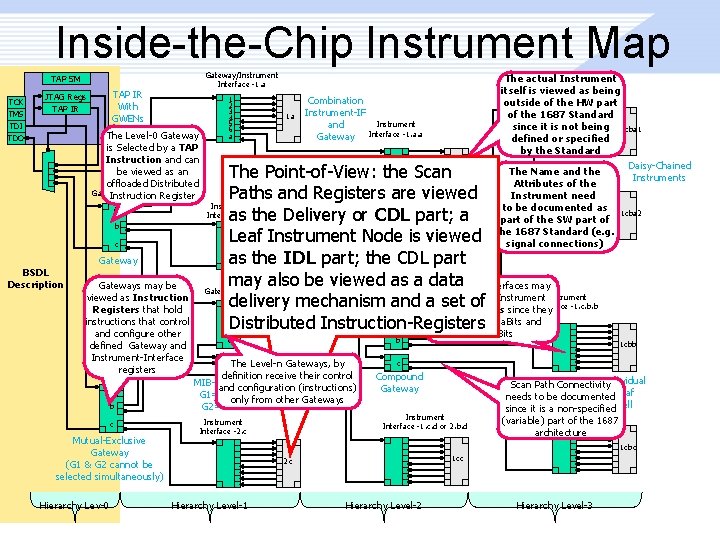

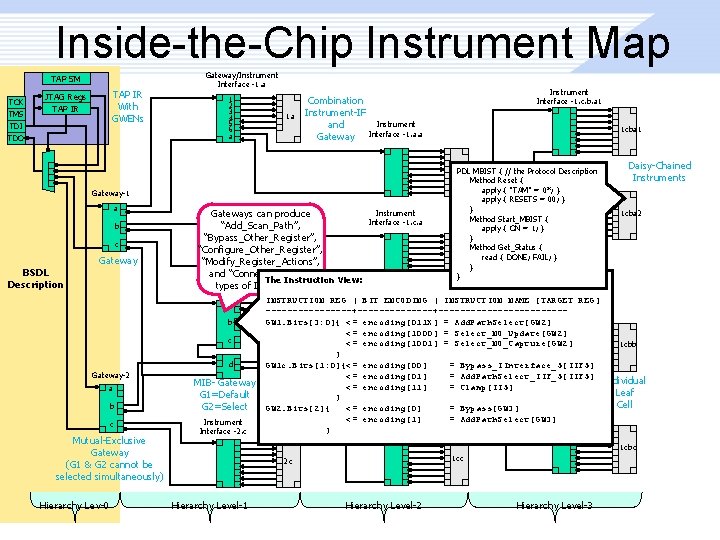

Inside-the-Chip Instrument Map TAP SM TCK TMS TDI JTAG Regs TAP IR TDO Instrument Interfaces may Gateway/Instrument be viewed as Data Registers Interface -1. a or. TAP Instrument Instruction 1 IR 2 With Registers 3 4 GWENs 5 6 a TDO Instrument Interfaces may include TDI SIBs and can be classed as Gateways c/s Gateway-1 a b Instrument Interface -1. b 1 a Groupings may be separate IP Combination cores or macros Instrument-IF Memory WSOBIST Instrument and Interface -1. a. a Gateway WSI SEL may u. Groupings be to align use 1 aa or align latency Instrument Interface -1. c. b. a 1 1 cba 1 Scan Compression Instrument Interface -1. c. b. a 2 Instrument Daisy-Chained Bus Configuration Instruments 1 cba 2 Interface -1. c. a MFG Scan Chains The Goal: To deliver Static 1 b Gateway Drive signals and to extract BSDL Gateways group Static Status. Instruments signalsarefrom Description 1149. 1 SIBs 1687 Gateway-1. c and SIBs are most-likely to be scan path a Leaf a. Instrument Node Gateway-1. c. b Zone dynamic Zone delivered “raw” management bits a with signal I/Fs BSDL is using ab JTAG-Operated Gateways enable insufficient b c Hierarchical Connections The Handoff between the BSDLInterface Open Access for that allow architectures Instruments need to be described in terms of purpose and attributes Logic BIST Bus Monitor c 1 ca Instrument Interface -1. c. b. b Connectivity needs to be understood to deliver vectors to the instruments Trace Buffer 1 cbb Zone and the 1687 description c d There may be fault-tolerant driven by tradeoffs (HDL) is the chip identifiier in the Gateway-2 multi-input connections to Compound Instrument Individual Gateways may be BSDL (Entity); MIBan instruction Gateway and the a minimize broken scan path Gateway Interface Leaf There is a need daisy-chained to register it selects G 1=Default risk – a multi-scan path Cell b for an adjustable create Hier-Levels G 2=Select Instrument shared resource Instrument indexing system Interface -1. c. b. c Voltage Monitor Instrument c Core Debug Unit Interface -1. c. d or 2. b. d to allow mapping Interface -2. c Mutual-Exclusive 1 cbc Gateways can be viewed 1 cc 2 c (G 1 & G 2 cannotasbe distributed instructions selected simultaneously) that represent “bypass” bits to bypass instruments Process Monitor Hierarchy Lev-0 Hierarchy Level-1 Hierarchy Level-2 Hierarchy Level-3 instrument description and hierarchy

Alfred L. Crouch Chief Technologist & Director of IJTAG R&D Vice-Chair IEEE P 1687 “IJTAG” Working Group P 1687 2008 Update: The Whole Story – Part 2 The IJTAG Features and Capabilities The Language and Description Portion BTW – Sept 2008 Crouch

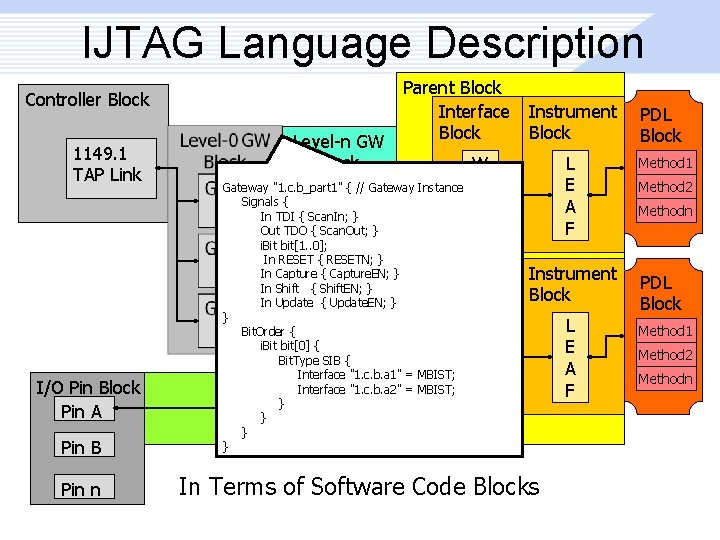

Part II: The Description Languages Ø This Section includes the description, documentation, development and file handoff of the 1687 Architecture

Speaking of IJTAG: Can you see what I am saying? Ø How is all of this Documented and Described? Ø What is the “language” (human and otherwise) associated with 1687 Ø If a chip is full of instruments…and they come from multiple IP Vendors and EDA tools and the local cube-dwelling design engineer…and then Bob the Integrator adds this JTAG-like infrastructure… Ø …how does all of this get documented? Where does the documentation come from? How hard is it to make the documentation? Who is going to use the documentation? How do I verify that the documentation is correct? . . .

Inside-the-Chip Instrument Map Gateway/Instrument Interface -1. a TAP SM TCK TMS TDI TAP IR With GWENs JTAG Regs TAP IR The Level-0 Gateway is Selected by a TAP Instruction and can be viewed as an offloaded Distributed Gateway-1 Instruction Register TDO a b c BSDL Description Gateways may be viewed as Instruction Registers that hold instructions that control and configure other defined Gateway and Instrument-Interface registers Gateway-2 a b c Mutual-Exclusive Gateway (G 1 & G 2 cannot be selected simultaneously) Hierarchy Lev-0 1 2 3 4 5 6 a 1 a The actual Instrument itself is viewed as being Instrument outside. Interface of the-1. c. b. a 1 HW part of the 1687 Standard since it is not being 1 cba 1 defined or specified by the Standard Combination Instrument-IF Instrument and Gateway Interface -1. a. a The Name and the The Point-of-View: the Scan 1 aa Instrument Attributes the Interfaceof -1. c. b. a 2 Instrument need Paths and Registers are viewed Instrument to be documented as Instrument Interface as-1. bthe Delivery or. Interface CDL part; a part of the SW part of -1. c. a Gateways can produce the 1687 Standard (e. g. Leaf Instrument Node is viewed signal connections) 1 b “Add_Scan_Path”, 1 ca “Bypass_Other_Register”, as the IDL part; the CDL part “Configure_Other_Register”, “Modify_Register_Actions”, may also be viewed as a data Instrument Interfaces may Gateway-1. c and “Connect_IO_Pins” viewed as Instrument adelivery mechanismtypes of Instructions and a beset of Interface -1. c. b. b Gateway-1. c. b Data Registers since they a b pass only Data. Bits and Distributed Instruction-Registers Status. Bits b c d. The Level-n Gateways, by definition receive their control MIB- Gateway and configuration (instructions) G 1=Default only from other Gateways G 2=Select Instrument Interface -2. c Daisy-Chained Instruments 1 cba 2 1 cbb c Compound Gateway Instrument Interface -1. c. d or 2. b. d Instrument Individual Scan Path Connectivity Interface needs to be documented. Leaf since it is Instrument a non-specified Cell Interface -1. c. b. c (variable) part of the 1687 architecture 1 cbc 1 cc 2 c Hierarchy Level-1 Hierarchy Level-2 Hierarchy Level-3

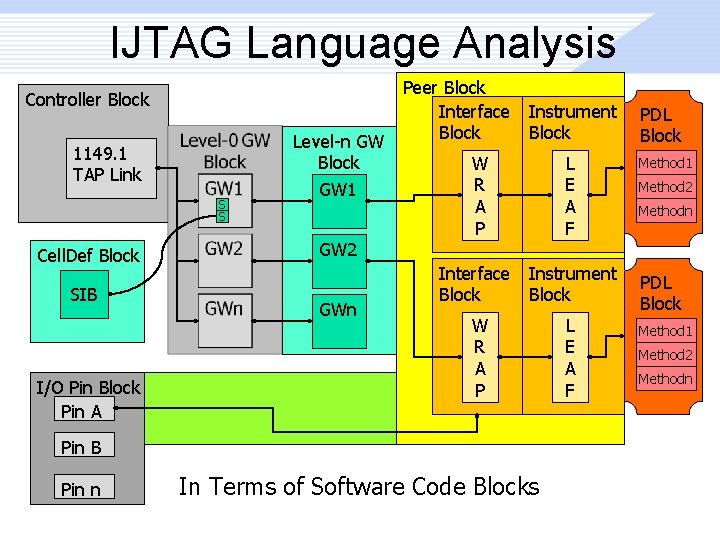

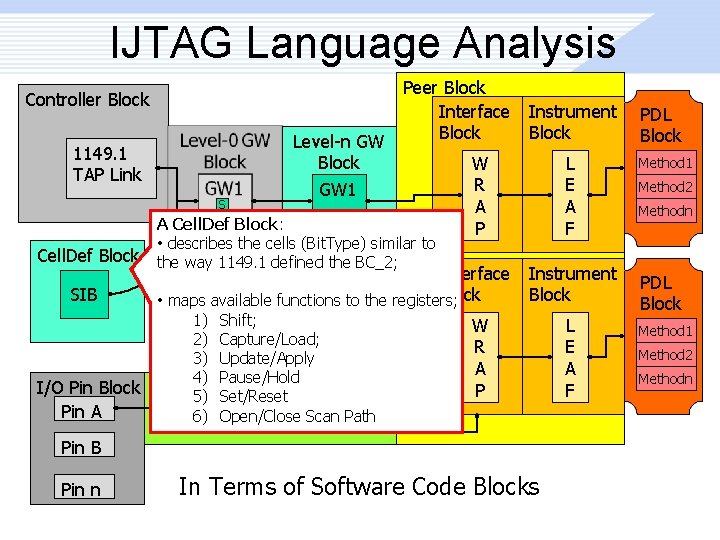

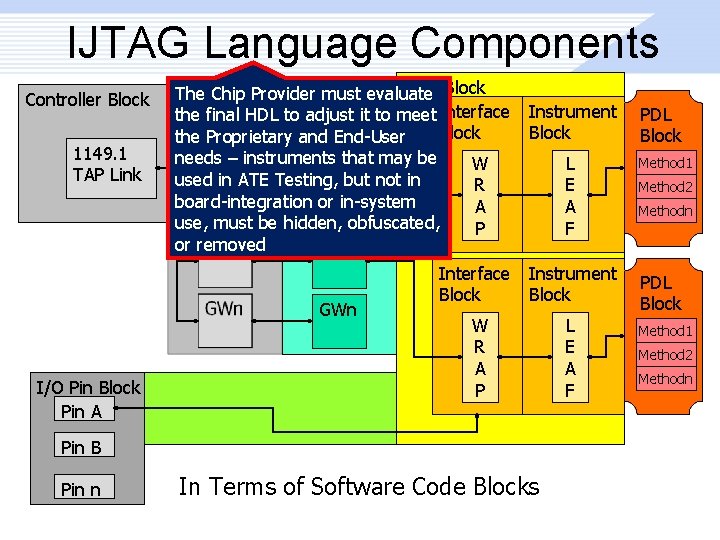

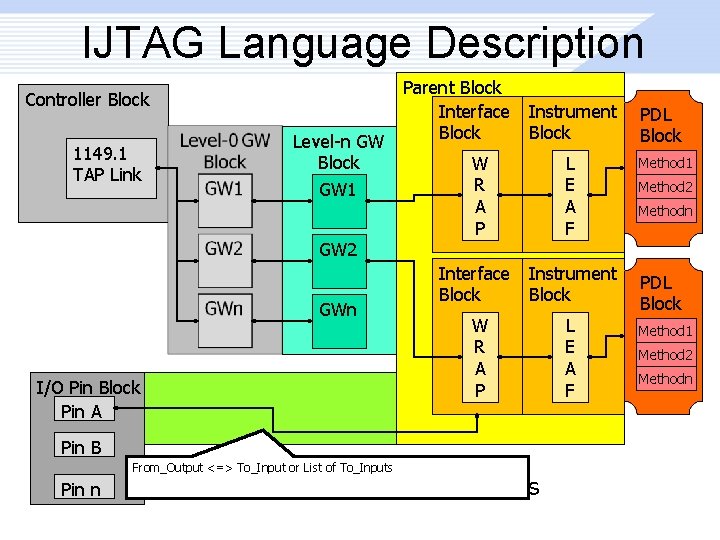

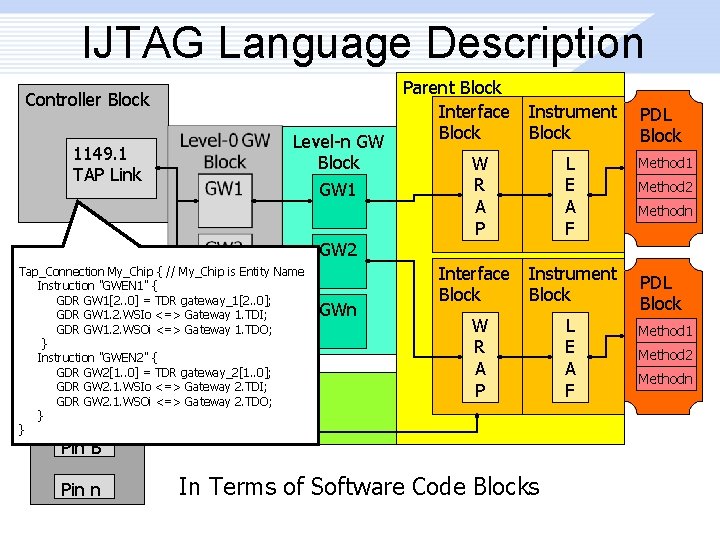

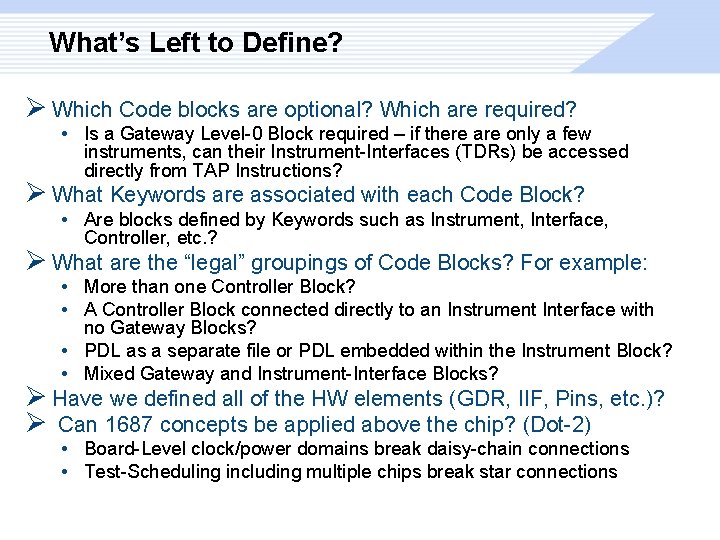

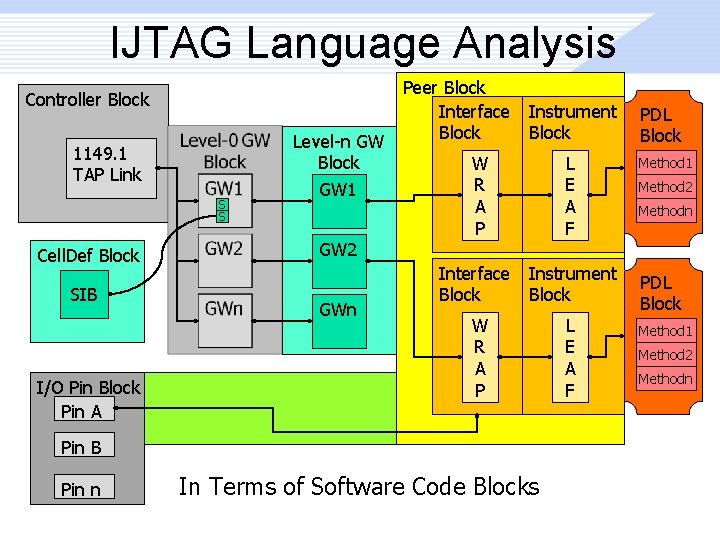

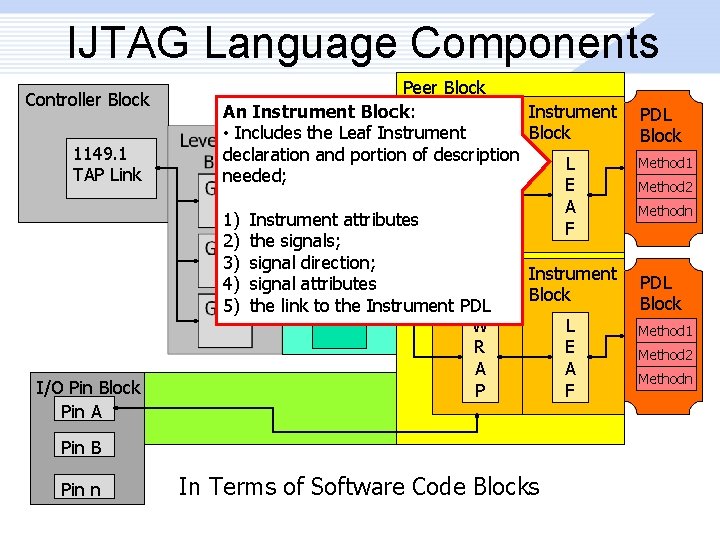

IJTAG Language Analysis Controller Block 1149. 1 TAP Link Cell. Def Block SIB I/O Pin Block Pin A Peer Block Interface Block Level-n GW Block W GW 1 stuff is changing. R Warning! This S A S we speak…meetings are being as P held…skids are being greased… GW 2 engineers are skulking around in Interface dark corners (uh, different ones Block than they usually GWnhang around)… W crayons are being brought to bear R …waitresses are being short-tipped A for all day meetings in restaurants… P Instrument Block L E A F Instrument Block Pin B Pin n In Terms of Software Code Blocks L E A F PDL Block Method 1 Method 2 Methodn

IJTAG Language Analysis Controller Block 1149. 1 TAP Link S S Cell. Def Block SIB I/O Pin Block Pin A Level-n GW Block GW 1 GW 2 GWn Peer Block Interface Block Instrument Block W R A P L E A F Pin B Pin n In Terms of Software Code Blocks PDL Block Method 1 Method 2 Methodn

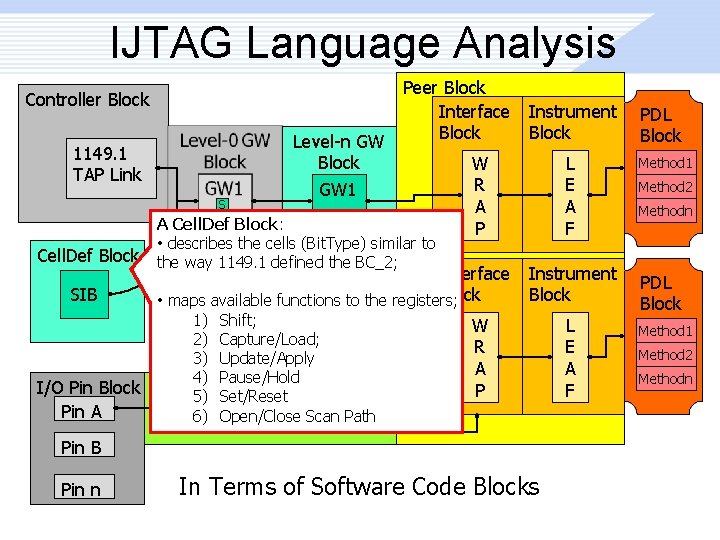

IJTAG Language Analysis Controller Block 1149. 1 TAP Link S S Cell. Def Block Level-n GW Block GW 1 Peer Block Interface Block A Cell. Def Block: • describes the cells (Bit. Type) GW 2 similar to the way 1149. 1 defined the BC_2; Instrument Block W R A P Interface SIB Block • maps available functions to the registers; GWn 1) Shift; W 2) Capture/Load; R 3) Update/Apply A 4) Pause/Hold I/O Pin Block P 5) Set/Reset Pin A 6) Open/Close Scan Path L E A F Instrument Block Pin B Pin n In Terms of Software Code Blocks L E A F PDL Block Method 1 Method 2 Methodn

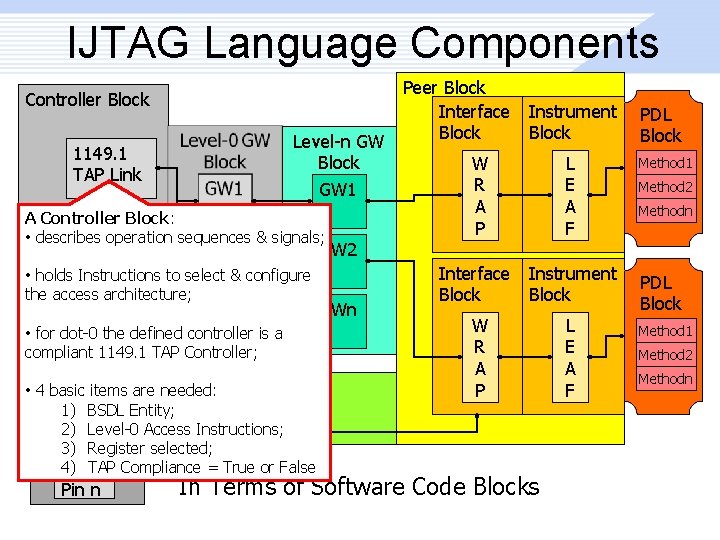

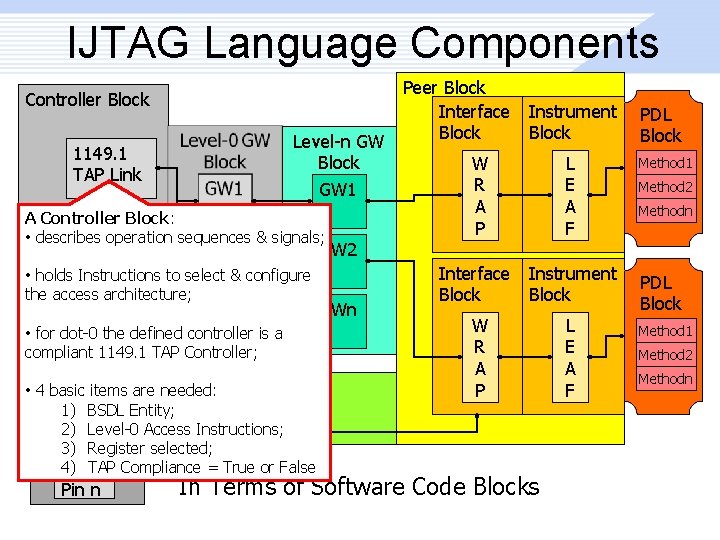

IJTAG Language Components Controller Block Level-n GW Block GW 1 1149. 1 TAP Link A Controller Block: • describes operation sequences & signals; GW 2 • holds Instructions to select & configure the access architecture; • for dot-0 the defined controller is a compliant 1149. 1 TAP Controller; Pinitems Blockare needed: • 4 I/O basic 1) Entity; Pin BSDL A 2) Level-0 Access Instructions; Pin Register B 3) selected; 4) TAP Compliance = True or False Pin n GWn Peer Block Interface Block Instrument Block W R A P L E A F In Terms of Software Code Blocks PDL Block Method 1 Method 2 Methodn

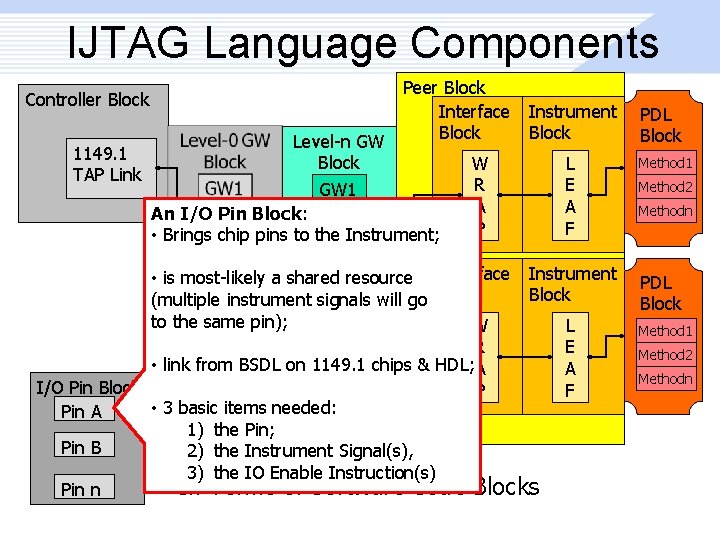

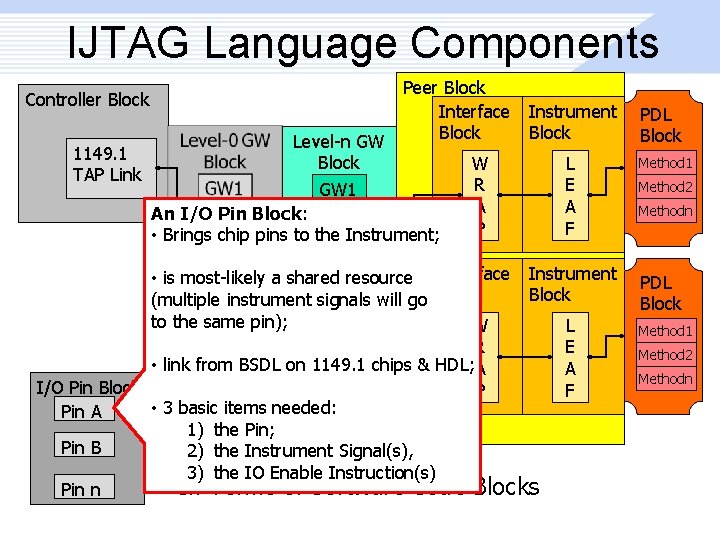

IJTAG Language Components Controller Block Peer Block Interface Block Instrument Block Level-n GW Block W L R E GW 1 A A An I/O Pin Block: P F • Brings chip pins to the Instrument; GW 2 • is most-likely a shared resource Interface Instrument Block (multiple instrument signals will go Block GWn to the same pin); W L R E • link from BSDL on 1149. 1 chips & HDL; A A I/O Pin Block P F • 3 basic items needed: Pin A 1) the Pin; Pin B 2) the Instrument Signal(s), 3) the IO Enable Instruction(s) In Terms of Software Code Blocks Pin n 1149. 1 TAP Link PDL Block Method 1 Method 2 Methodn

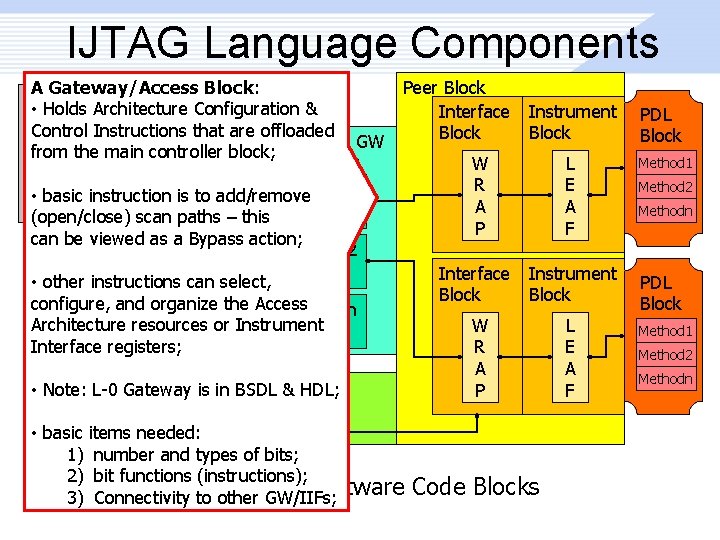

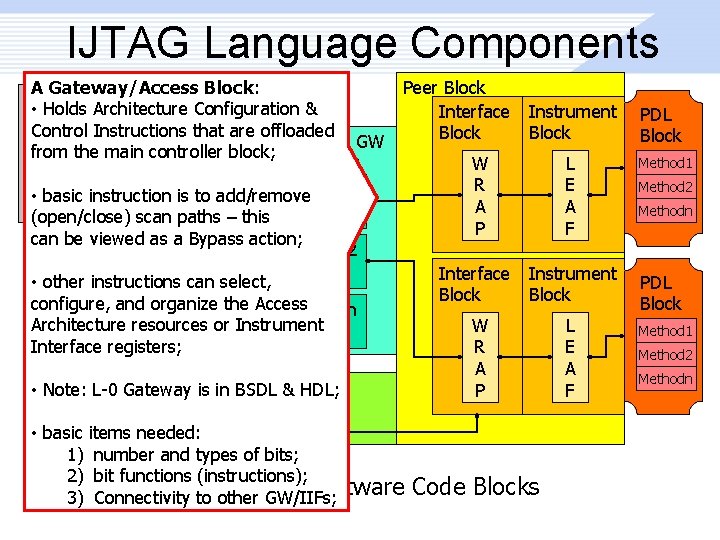

IJTAG Language Components A Gateway/Access Block: Controller Block • Holds Architecture Configuration & Control Instructions that are offloaded Level-n GW from 1149. 1 the main controller block; Block TAP Link • basic instruction is to add/remove GW 1 (open/close) scan paths – this can be viewed as a Bypass action; GW 2 Peer Block Interface Block • other instructions can select, configure, and organize the Access GWn Architecture resources or Instrument Interface registers; Pin. L-0 Block • I/O Note: Gateway is in BSDL & HDL; Pin A • basic items needed: Pin 1) Bnumber and types of bits; 2) bit functions (instructions); Into. Terms of Software Pin 3) n. Connectivity other GW/IIFs; Instrument Block W R A P L E A F Interface Block Instrument Block W R A P L E A F Code Blocks PDL Block Method 1 Method 2 Methodn

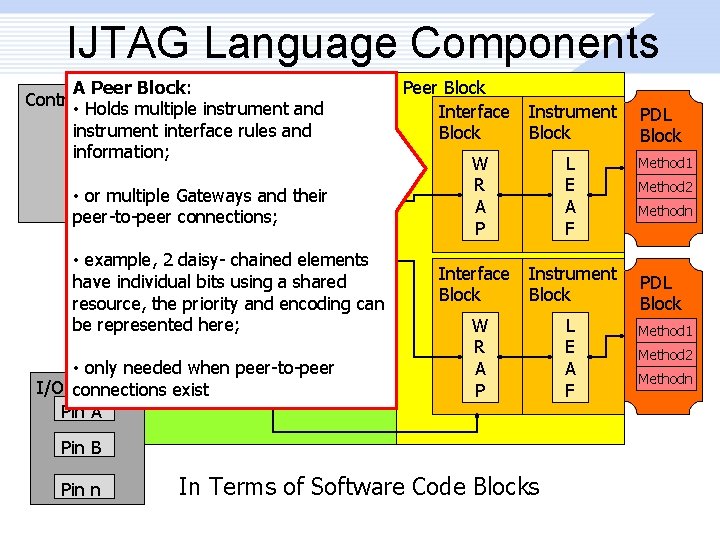

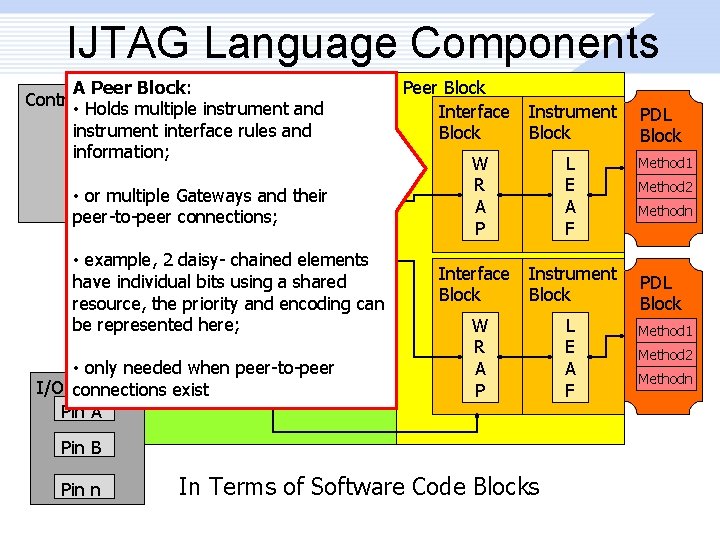

IJTAG Language Components A Peer Block: Controller Block • Holds multiple instrument and instrument interface rules and Level-n GW information; 1149. 1 Block TAP Link GW 1 • or multiple Gateways and their peer-to-peer connections; GW 2 • example, 2 daisy- chained elements have individual bits using a shared resource, the priority and encoding GWncan be represented here; • only needed when peer-to-peer I/O Pin Block connections exist Pin A Peer Block Interface Block Instrument Block W R A P L E A F Pin B Pin n In Terms of Software Code Blocks PDL Block Method 1 Method 2 Methodn

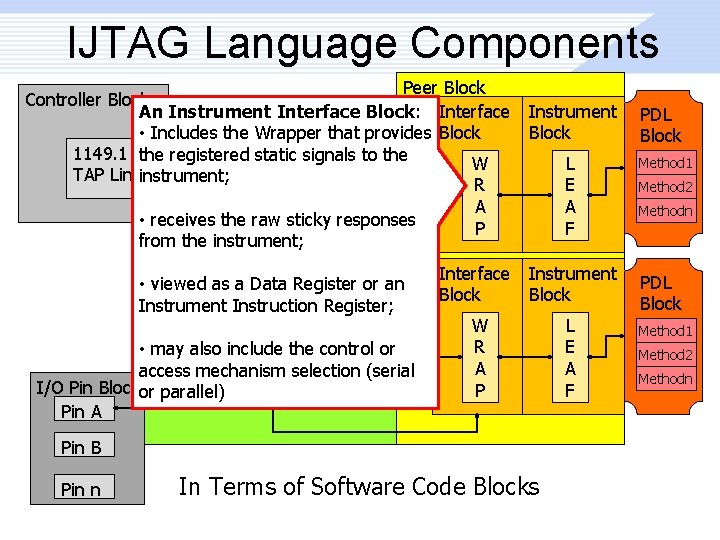

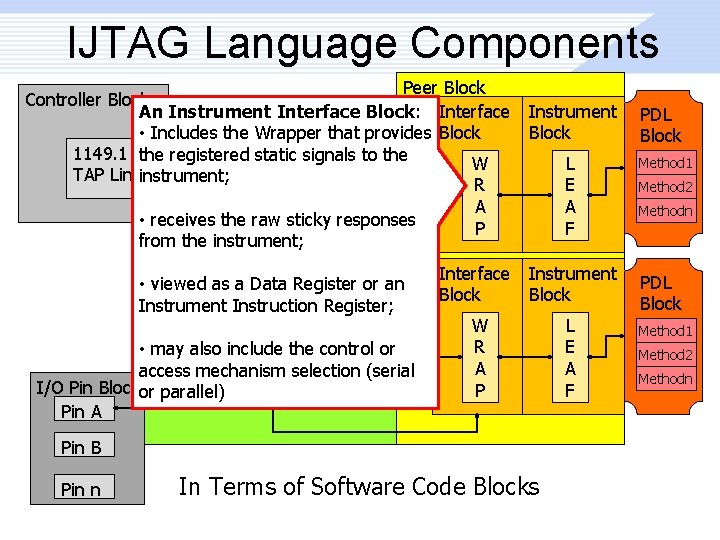

IJTAG Language Components Peer Block Controller Block An Instrument Interface Block: Interface • Includes the Wrapper that. GW provides Block Level-n 1149. 1 the registered static signals to the Block W TAP Linkinstrument; R GW 1 A • receives the raw sticky responses P from the instrument; GW 2 Interface • viewed as a Data Register or an Block Instrument Instruction GWn Register; W R • may also include the control or A access mechanism selection (serial I/O Pin Blockor parallel) P Pin A Instrument Block L E A F Instrument Block Pin B Pin n In Terms of Software Code Blocks L E A F PDL Block Method 1 Method 2 Methodn

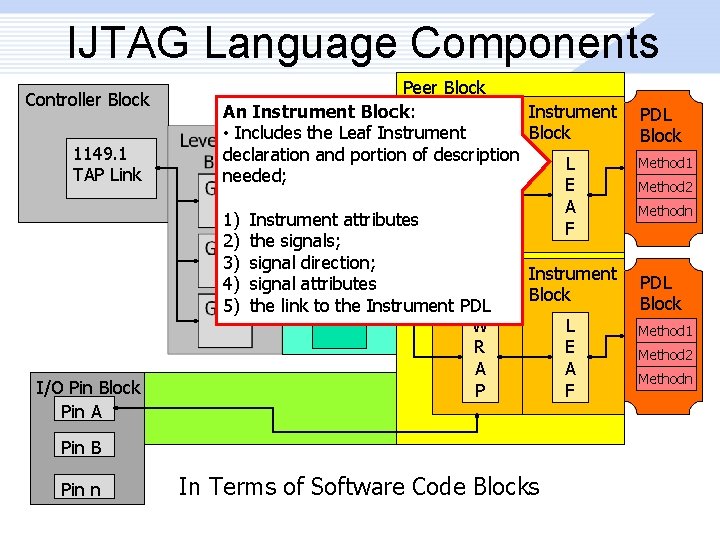

IJTAG Language Components Controller Block 1149. 1 TAP Link I/O Pin Block Pin A Peer Block An Instrument Block: Interface • Includes. Level-n the Leaf Block GWInstrument declaration and Blockportion of description W needed; R GW 1 A 1) Instrument attributes P 2) the signals; GW 2 3) signal direction; Interface 4) signal attributes Block 5) the link to the Instrument PDL GWn W R A P Instrument Block L E A F Instrument Block Pin B Pin n In Terms of Software Code Blocks L E A F PDL Block Method 1 Method 2 Methodn

IJTAG Language Components Controller Block 1149. 1 TAP Link I/O Pin Block Pin A Pin B Pin n A PDL Block: Peer Block Interface Instrument • Includes vector-based procedures or Block sequences to configure and Level-n GWrequired. Block operate Blockthe instrument; W L R E GW 1 • should be independent. A of the access A mechanism (associated Pto the raw F instrument GW 2 signal interface); Interface Instrument • PDL can be described Blockas Methods Block to GWnindividual configurations or conduct operations (primitives) W or complete. L R E tests (complex); A A F • Basic PDL is simply: P 1) Reads – Read<Instrument> 2) Writes – Write<Instrument> 3) Applies – Apply <R 1, R 2, W 1…> In Terms of Software Code Blocks PDL Block Method 1 Method 2 Methodn

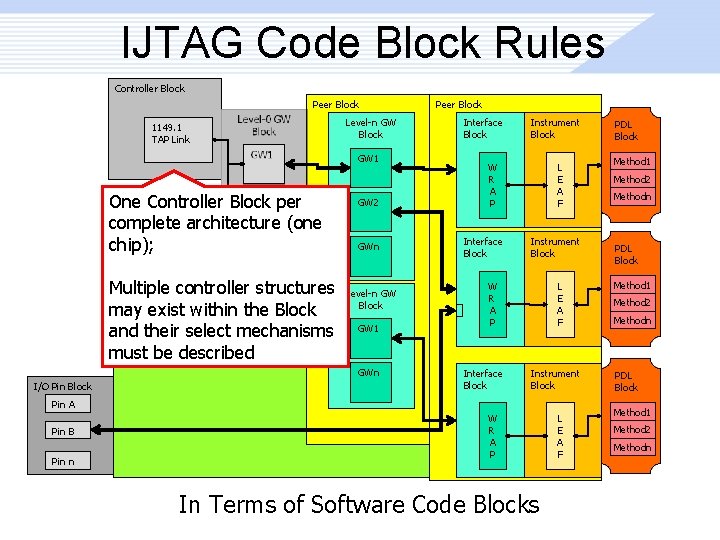

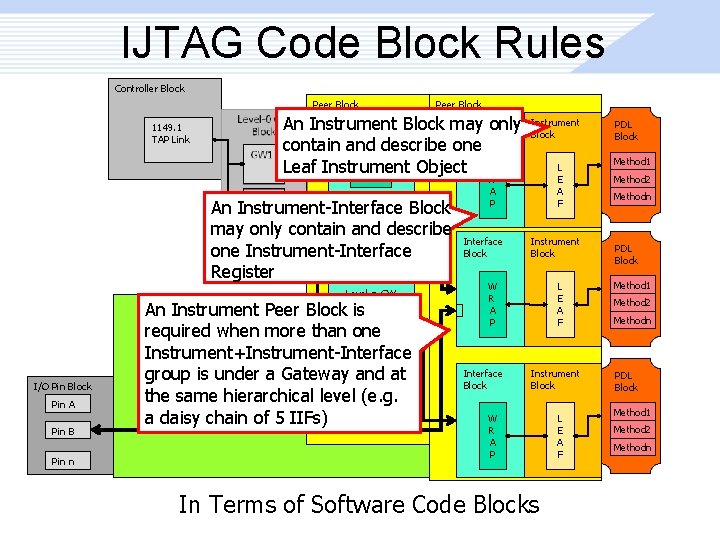

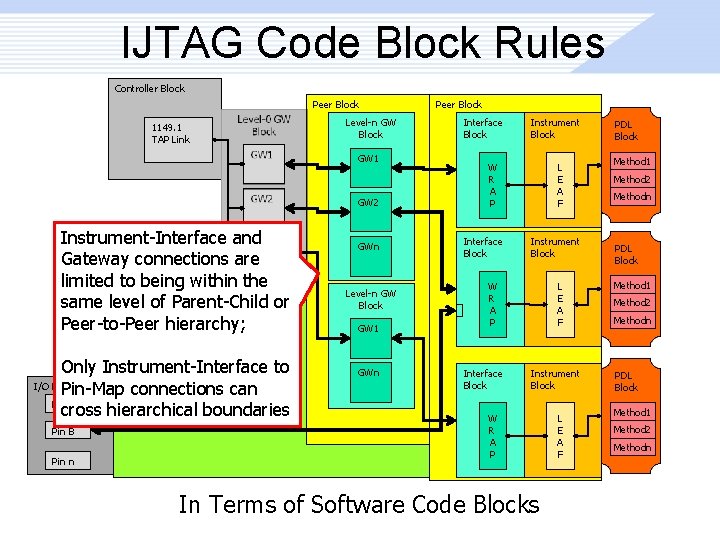

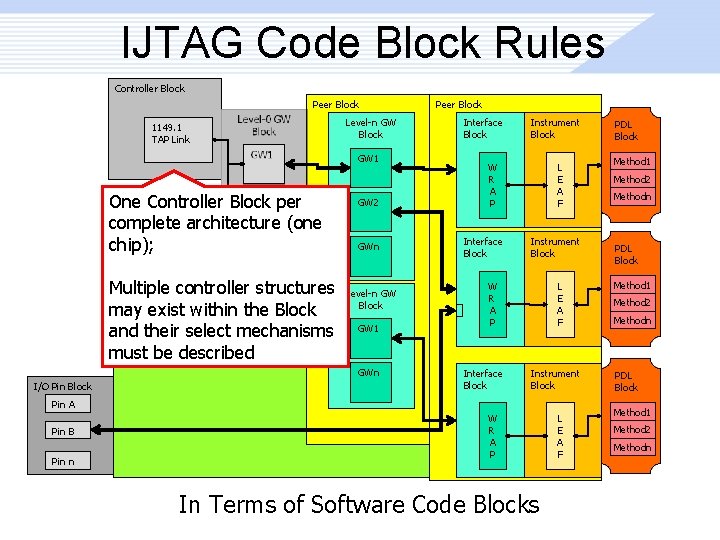

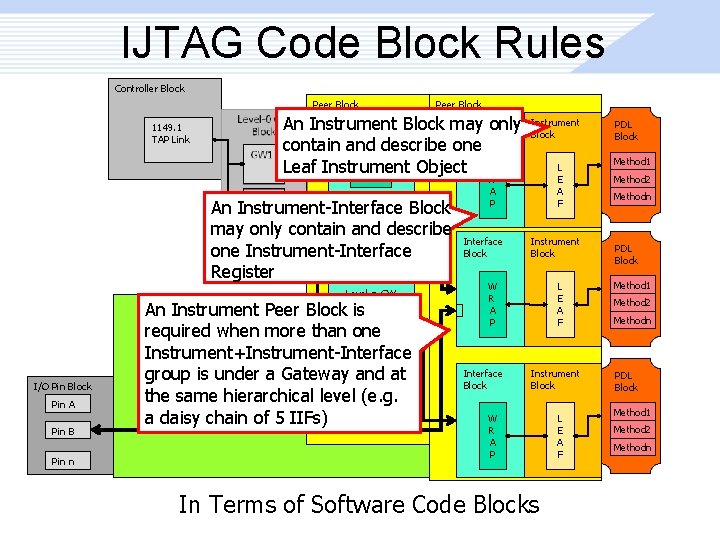

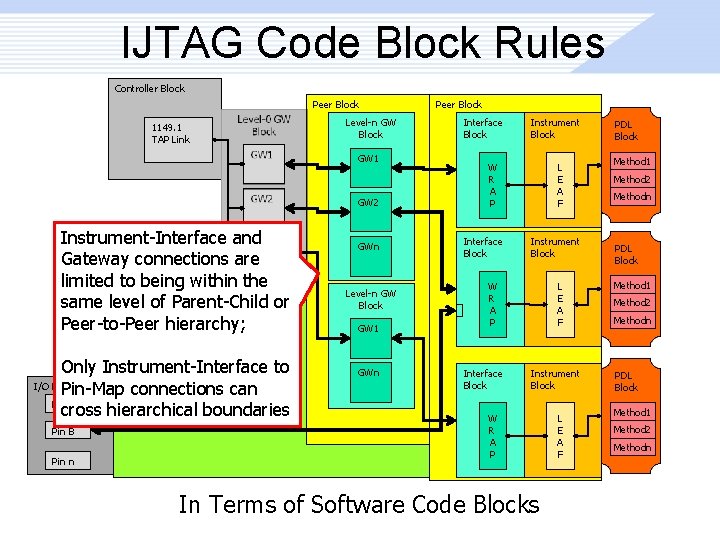

IJTAG Code Block Rules Controller Block Peer Block 1149. 1 TAP Link Level-n GW Block GW 1 One Controller Block per complete architecture (one chip); Multiple controller structures may exist within the Block and their select mechanisms must be described GW 2 GWn Level-n GW Block GW 1 GWn I/O Pin Block Peer Block Interface Block Instrument Block W R A P Interface Block L E A F Instrument Block Pin A Pin B Pin n W R A P In Terms of Software Code Blocks L E A F PDL Block Method 1 Method 2 Methodn

IJTAG Code Block Rules Controller Block Peer Block 1149. 1 TAP Link Peer Block Interface Level-n GW Block may An Instrument only Block contain and describe one GW 1 Leaf Instrument Object W GW 2 An Instrument-Interface Block may only contain and describe GWn one Instrument-Interface Register Level-n GW Block I/O Pin Block Pin A Pin B Pin n An Instrument Peer Block is GW 1 required when more than one Instrument+Instrument-Interface GWn at group is under a Gateway and the same hierarchical level (e. g. a daisy chain of 5 IIFs) Instrument Block L E A F R A P Interface Block Instrument Block W R A P Interface Block L E A F Instrument Block W R A P In Terms of Software Code Blocks L E A F PDL Block Method 1 Method 2 Methodn

IJTAG Code Block Rules Controller Block A Gateway Block is a Peer 1149. 1 TAP hold Link block in that it may several Gateway Registers at the same hierarchical level and their local connections Peer Block Level-n GW Block GW 1 GW 2 GWn Multiple Gateway Blocks (Level-0 or beyond) may exist per hierarchical level – if more than one block exists, then peer connections must I/O Pin Block be described Level-n GW Block GW 1 GWn Peer Block Interface Block Instrument Block W R A P Interface Block L E A F Instrument Block Pin A Pin B Pin n W R A P In Terms of Software Code Blocks L E A F PDL Block Method 1 Method 2 Methodn

IJTAG Code Block Rules Controller Block Peer Block 1149. 1 TAP Link Level-n GW Block GW 1 GW 2 Instrument-Interface and Gateway connections are limited to being within the same level of Parent-Child or Peer-to-Peer hierarchy; Only Instrument-Interface to I/O Pin-Map Block connections can Pin A cross hierarchical boundaries Pin B Pin n GWn Level-n GW Block GW 1 GWn Peer Block Interface Block Instrument Block W R A P Interface Block L E A F Instrument Block W R A P In Terms of Software Code Blocks L E A F PDL Block Method 1 Method 2 Methodn

Where Does HDL Come From? Ø The Chip Provider must supply HDL for end users of the chip… Ø …but as the HDL is being built, its sections come from several sources – the goal = reusable code sections

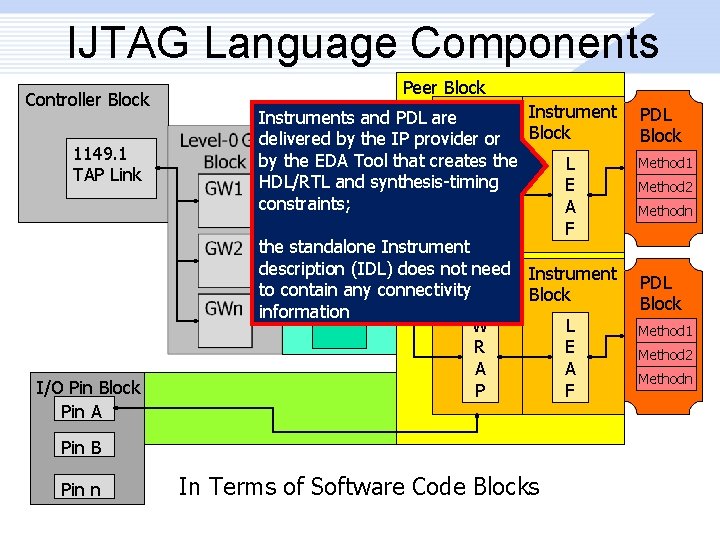

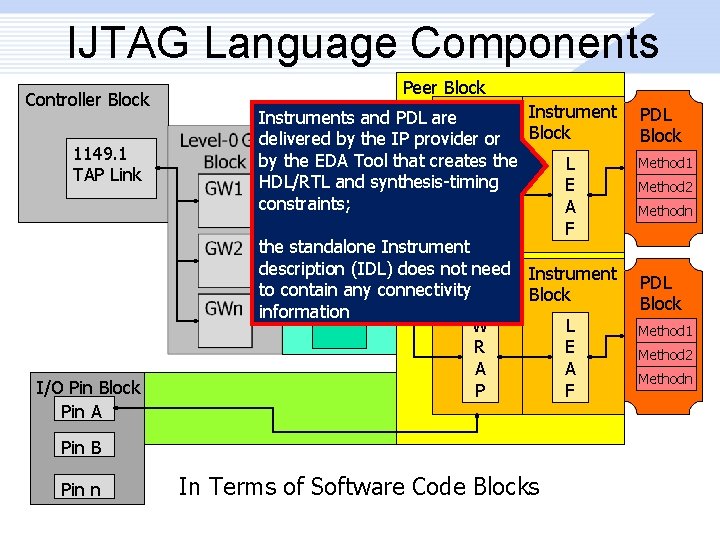

IJTAG Language Components Controller Block 1149. 1 TAP Link I/O Pin Block Pin A Peer Block Interface Instruments and PDL are Block or delivered by GW the IP provider Level-n by the EDA Block. Tool that creates W the HDL/RTL and synthesis-timing R GW 1 constraints; A P the standalone GW 2 Instrument description (IDL) does Interface not need to contain any connectivity Block GWn information W R A P Instrument Block L E A F Instrument Block Pin B Pin n In Terms of Software Code Blocks L E A F PDL Block Method 1 Method 2 Methodn

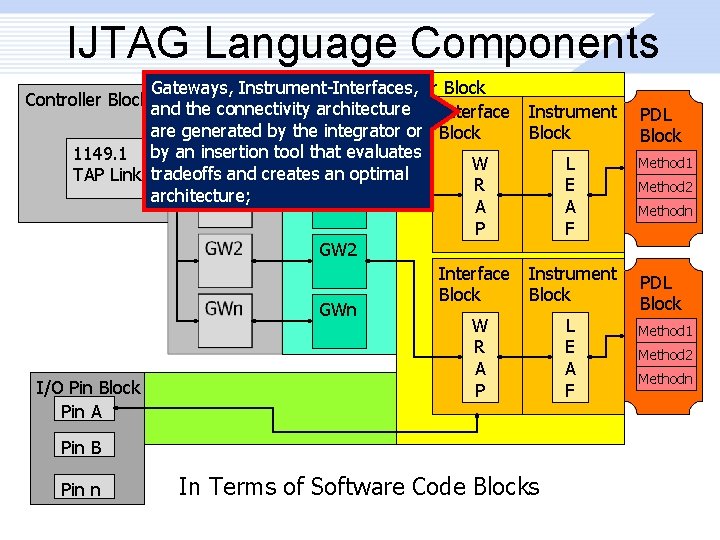

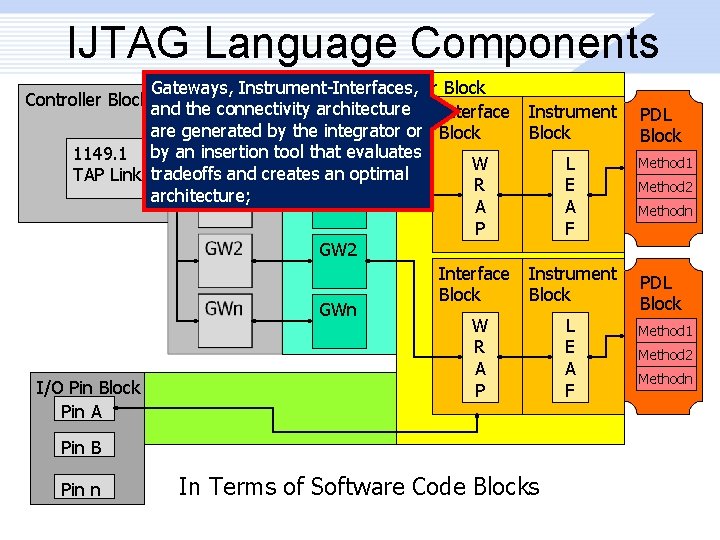

IJTAG Language Components Gateways, Instrument-Interfaces, Peer Block and the connectivity architecture Interface are generated by the integrator or Block Level-n GW 1149. 1 by an insertion tool that evaluates Block W TAP Link tradeoffs and creates an optimal R GW 1 architecture; A P GW 2 Interface Block GWn W R A I/O Pin Block P Pin A Controller Block Instrument Block L E A F Instrument Block Pin B Pin n In Terms of Software Code Blocks L E A F PDL Block Method 1 Method 2 Methodn

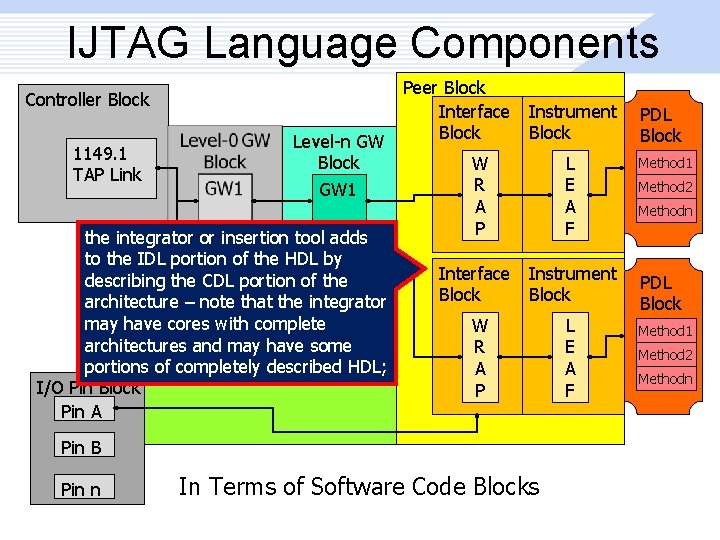

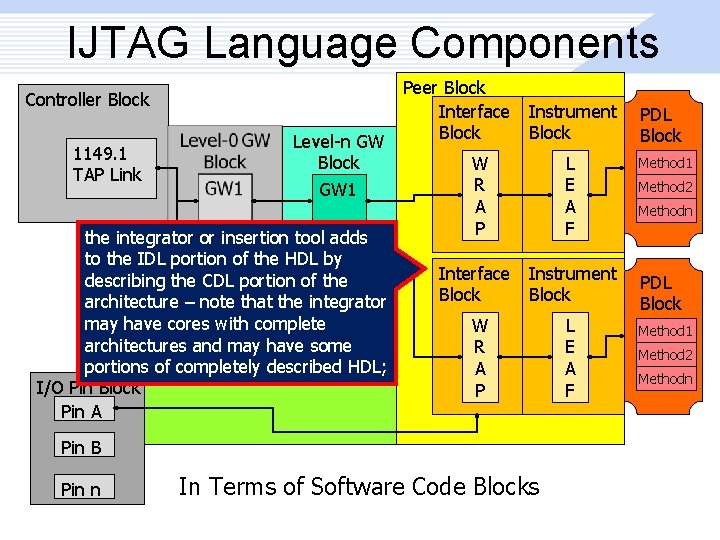

IJTAG Language Components Controller Block 1149. 1 TAP Link Level-n GW Block GW 1 the integrator or insertion tool adds GW 2 to the IDL portion of the HDL by describing the CDL portion of the architecture – note that the integrator GWn may have cores with complete architectures and may have some portions of completely described HDL; I/O Pin Block Pin A Peer Block Interface Block Instrument Block W R A P L E A F Pin B Pin n In Terms of Software Code Blocks PDL Block Method 1 Method 2 Methodn

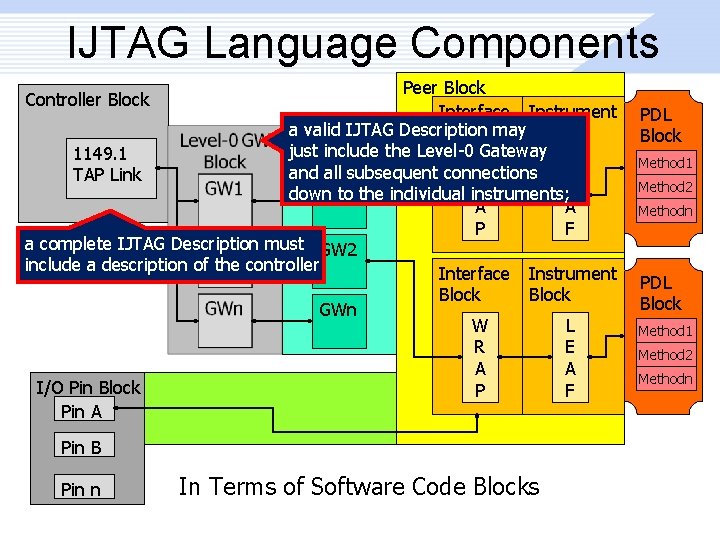

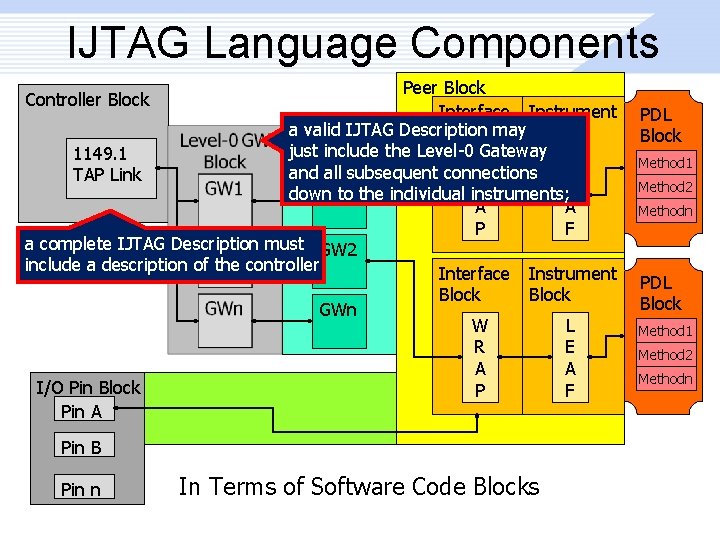

IJTAG Language Components Peer Block Interface Instrument a valid IJTAG Description Block may Block Level-n GW just include the Level-0 Gateway 1149. 1 Block W L and all subsequent connections TAP Link R E GW 1 down to the individual instruments; A A P F a complete IJTAG Description must GW 2 include a description of the controller Interface Instrument Block GWn W L R E A A I/O Pin Block P F Pin A Controller Block Pin B Pin n In Terms of Software Code Blocks PDL Block Method 1 Method 2 Methodn

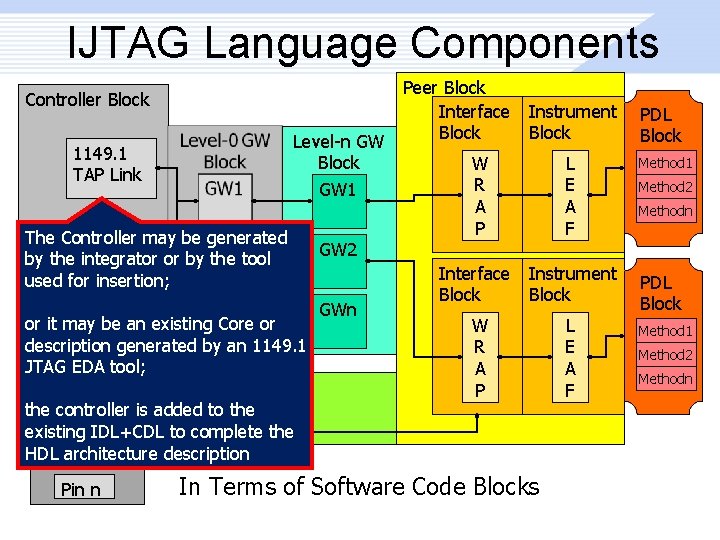

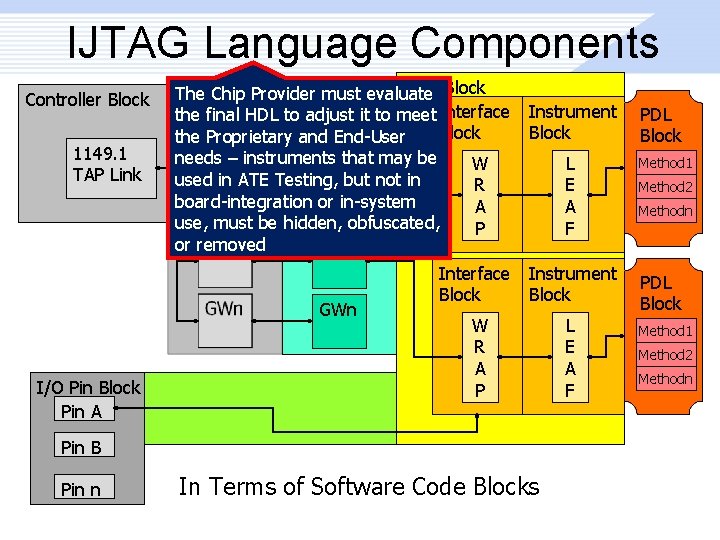

IJTAG Language Components Controller Block Level-n GW Block GW 1 1149. 1 TAP Link The Controller may be generated by the integrator or by the tool used for insertion; or it may be an existing Core or description generated by an 1149. 1 JTAG EDA tool; I/O Pin Block the controller is added to the Pin A existing IDL+CDL to complete the B HDL Pin architecture description Pin n GW 2 GWn Peer Block Interface Block Instrument Block W R A P L E A F In Terms of Software Code Blocks PDL Block Method 1 Method 2 Methodn

IJTAG Language Components Controller Block 1149. 1 TAP Link I/O Pin Block Pin A Peer Block The Chip Provider must evaluate the final HDL to adjust it to meet Interface Block the Proprietary. Level-n and End-User GW needs – instruments that may be Block W used in ATE Testing, but not in R GW 1 board-integration or in-system A use, must be hidden, obfuscated, P or removed GW 2 Interface Block GWn W R A P Instrument Block L E A F Instrument Block Pin B Pin n In Terms of Software Code Blocks L E A F PDL Block Method 1 Method 2 Methodn

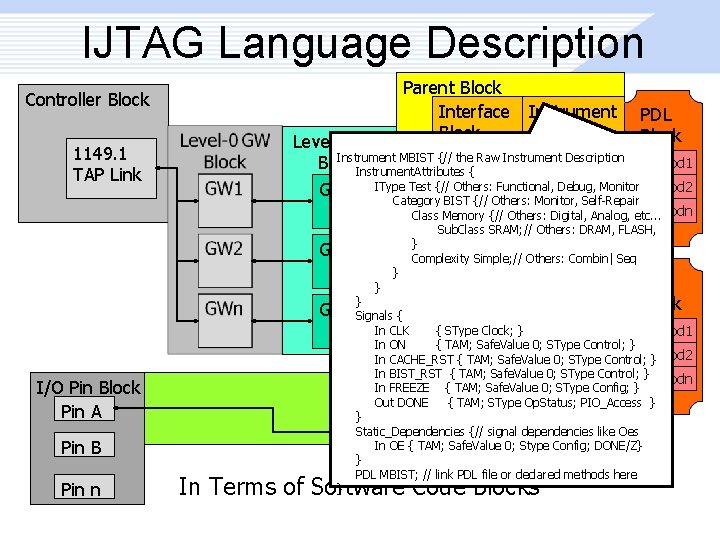

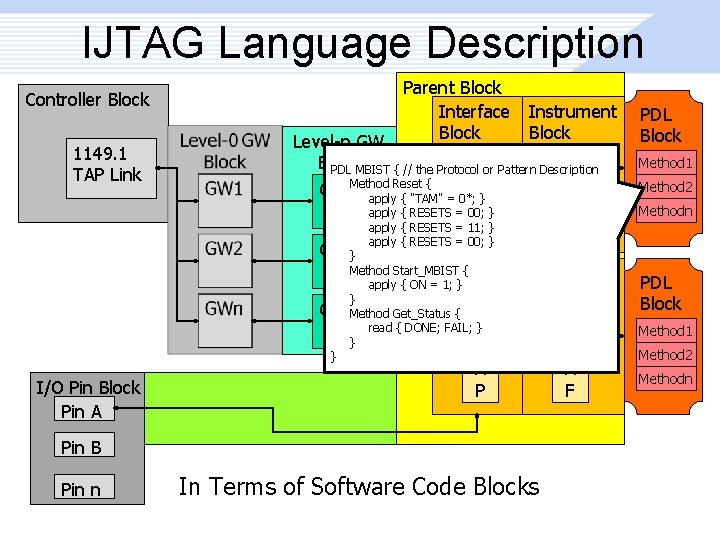

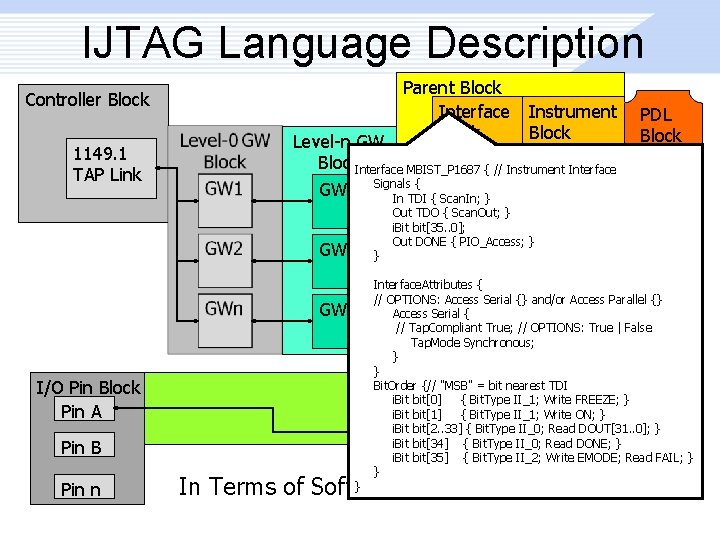

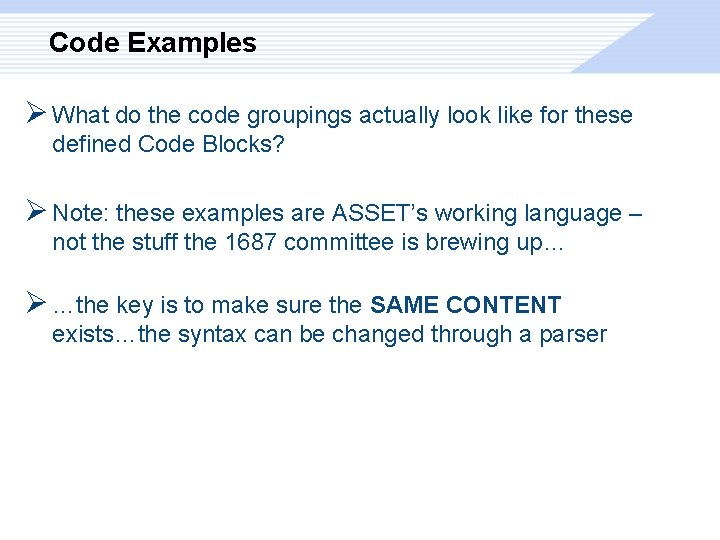

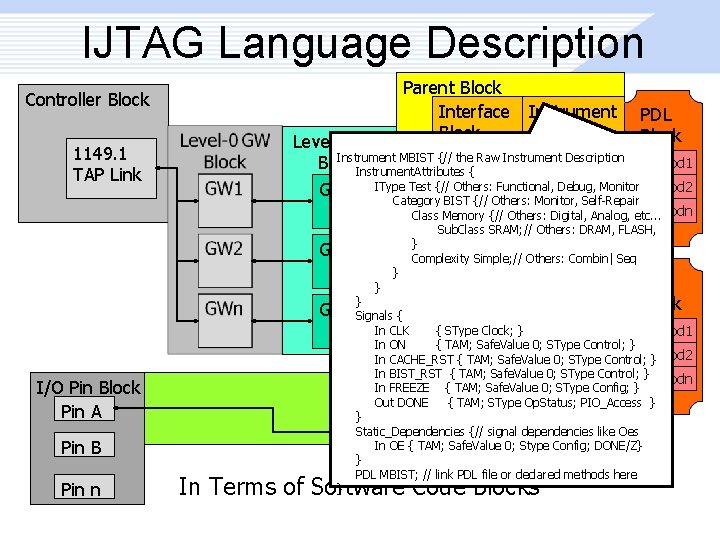

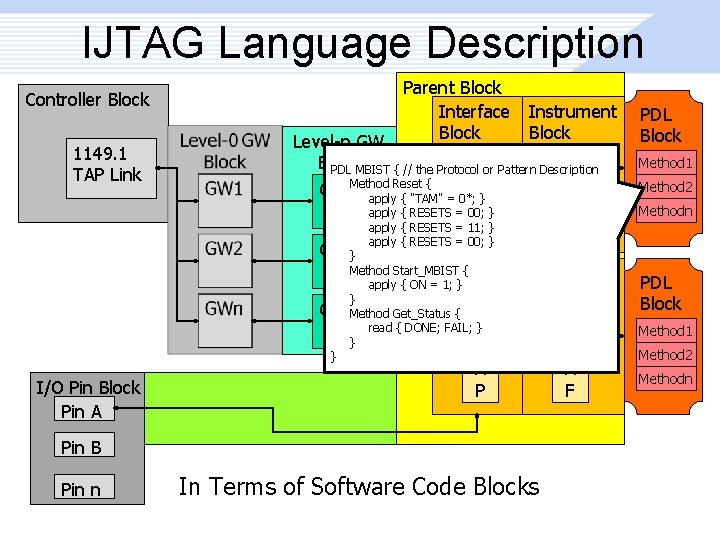

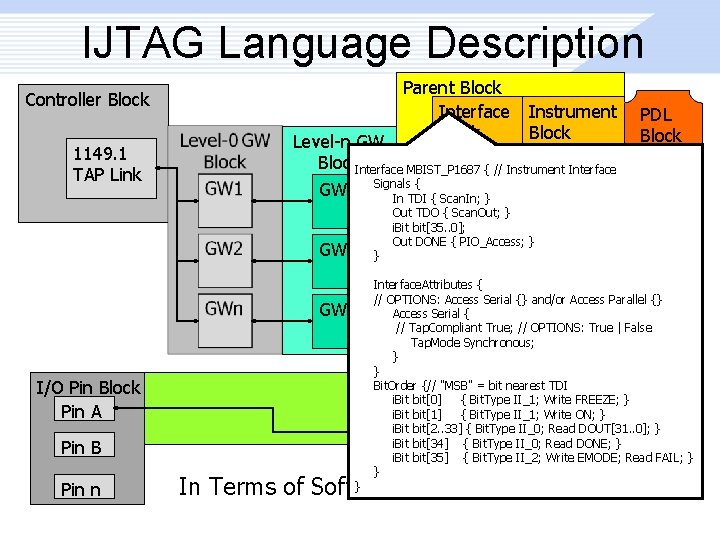

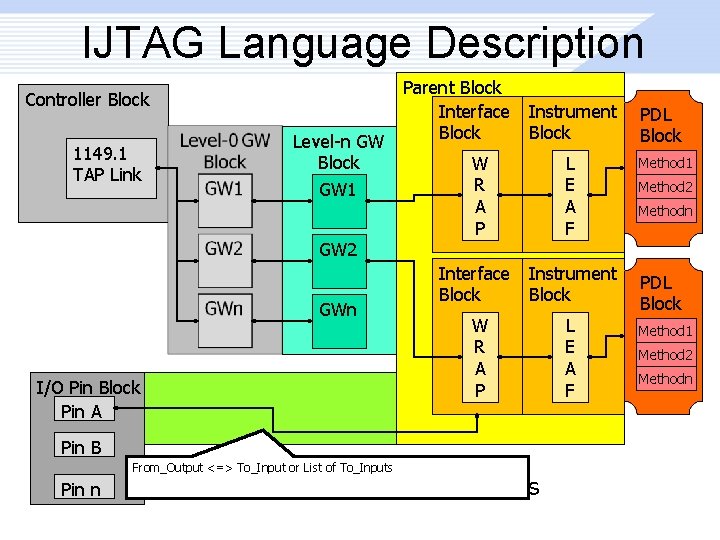

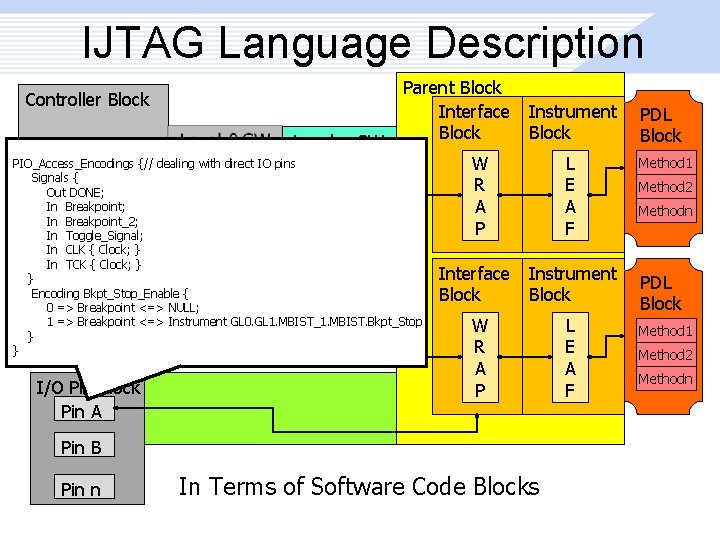

Code Examples Ø What do the code groupings actually look like for these defined Code Blocks? Ø Note: these examples are ASSET’s working language – not the stuff the 1687 committee is brewing up… Ø …the key is to make sure the SAME CONTENT exists…the syntax can be changed through a parser

IJTAG Language Description Controller Block 1149. 1 TAP Link I/O Pin Block Pin A Pin B Pin n Parent Block Interface Block Instrument Block PDL Block Level-n GW Instrument MBIST {// the Raw Instrument Description Method 1 Block W L Instrument. Attributes { R Functional, Debug, E Monitor. Method 2 GW 1 IType Test {// Others: Category BIST {// Others: Monitor, Self-Repair A A Methodn Class Memory {// Others: Digital, Analog, etc. . . Sub. Class P SRAM; // Others: F DRAM, FLASH, } GW 2 Complexity Simple; // Others: Combin| Seq } Interface Instrument PDL } Block GWn. Signals { WClock; } L In CLK { SType Method 1 In ON { TAM; R Safe. Value 0; SType E Control; } Method 2 In CACHE_RST { TAM; Safe. Value 0; SType Control; } A A In BIST_RST { TAM; Safe. Value 0; SType Control; Methodn } In FREEZE { TAM; P Safe. Value 0; SType F Config; } Out DONE { TAM; SType Op. Status; PIO_Access } } Static_Dependencies {// signal dependencies like Oes In OE { TAM; Safe. Value 0; Stype Config; DONE/Z} } PDL MBIST; // link PDL file or declared methods here } In Terms of Software Code Blocks

IJTAG Language Description Controller Block 1149. 1 TAP Link I/O Pin Block Pin A Parent Block Interface Block Instrument Block Level-n GW Block Wor Pattern Description L PDL MBIST { // the Protocol Reset { R E GW 1 Method apply { "TAM" = 0*; } A} A apply { RESETS = 00; apply { RESETS = 11; P} F apply { RESETS = 00; } GW 2} Method Start_MBIST { Interface Instrument apply { ON = 1; } Block } GWn. Method Get_Status { L read { DONE; FAIL; W } } R E } A A P F Pin B Pin n In Terms of Software Code Blocks PDL Block Method 1 Method 2 Methodn

IJTAG Language Description Parent Block Interface Block Controller Block 1149. 1 TAP Link I/O Pin Block Pin A PDL Block Level-n GW Block. Interface MBIST_P 1687 W{ // Instrument. LInterface Method 1 { R E Method 2 GW 1 Signals In TDI { Scan. In; } A Methodn Out TDO { Scan. Out; i. Bit bit[35. . 0]; P F Out DONE { PIO_Access; } GW 2 } Interface Instrument PDL Interface. Attributes { // OPTIONS: Block Access Serial {} Block and/or Access Parallel {} Block GWn Access Serial { WTrue; // OPTIONS: L True | False // Tap. Compliant Method 1 Tap. Mode Synchronous; R E Method 2 } A A } Methodn Bit. Order {// "MSB" = bit nearest TDI P F i. Bit bit[0] { Bit. Type II_1; Write FREEZE; } Pin B Pin n Instrument Block } i. Bit bit[1] { Bit. Type II_1; Write ON; } bit[2. . 33] { Bit. Type II_0; Read DOUT[31. . 0]; } bit[34] { Bit. Type II_0; Read DONE; } bit[35] { Bit. Type II_2; Write EMODE; Read FAIL; } In Terms of Software Code Blocks }

IJTAG Language Description Controller Block 1149. 1 TAP Link Level-n GW Block GW 1 GW 2 GWn I/O Pin Block Pin A Parent Block Interface Block Instrument Block W R A P L E A F Pin B From_Output <=> To_Input or List of To_Inputs Pin n In Terms of Software Code Blocks PDL Block Method 1 Method 2 Methodn

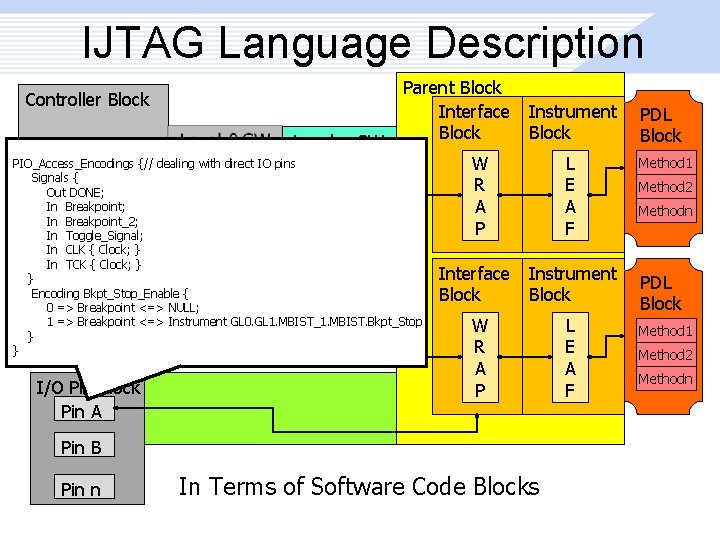

IJTAG Language Description Controller Block Level-n GW 1149. 1 PIO_Access_Encodings {// dealing with direct IO pins Block Signals {TAP Link GW 1 Out DONE; In In In } Breakpoint; Breakpoint_2; Toggle_Signal; CLK { Clock; } TCK { Clock; } Parent Block Interface Block GW 2 } Encoding Bkpt_Stop_Enable { 0 => Breakpoint <=> NULL; GWn 1 => Breakpoint <=> Instrument GL 0. GL 1. MBIST_1. MBIST. Bkpt_Stop } I/O Pin Block Pin A Instrument Block W R A P L E A F Interface Block Instrument Block W R A P L E A F Pin B Pin n In Terms of Software Code Blocks PDL Block Method 1 Method 2 Methodn

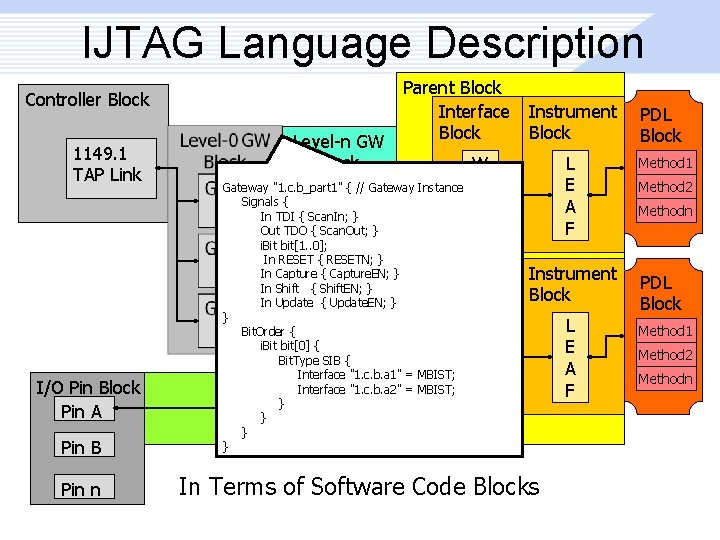

IJTAG Language Description Parent Block Interface Block Controller Block 1149. 1 TAP Link I/O Pin Block Pin A Pin B Pin n Level-n GW Block W Gateway "1. c. b_part 1" { // Gateway Instance R GW 1 Signals { A In TDI { Scan. In; } P Out TDO { Scan. Out; } i. Bit bit[1. . 0]; GW 2 In RESET { RESETN; } In Capture { Capture. EN; } Interface In Shift { Shift. EN; } Block In Update { Update. EN; } GWn } W Bit. Order { i. Bit bit[0] { R Bit. Type SIB { A Interface "1. c. b. a 1" = MBIST; Interface "1. c. b. a 2" = MBIST; P } } } Instrument Block L E A F Instrument Block } In Terms of Software Code Blocks L E A F PDL Block Method 1 Method 2 Methodn

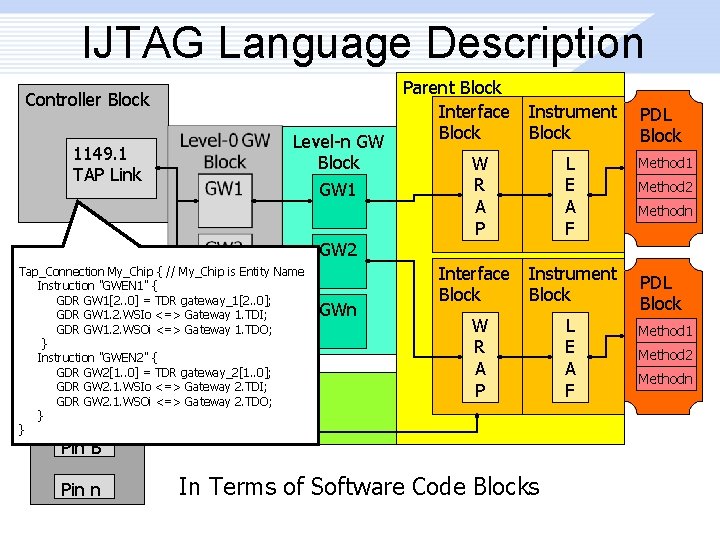

IJTAG Language Description Controller Block 1149. 1 TAP Link Level-n GW Block GW 1 GW 2 Tap_Connection My_Chip { // My_Chip is Entity Name Instruction "GWEN 1" { GDR GW 1[2. . 0] = TDR gateway_1[2. . 0]; GDR GW 1. 2. WSIo <=> Gateway 1. TDI; GDR GW 1. 2. WSOi <=> Gateway 1. TDO; } Instruction "GWEN 2" { GDR GW 2[1. . 0] = TDR gateway_2[1. . 0]; GW 2. 1. WSIo I/OGDR Pin Block <=> Gateway 2. TDI; GDR GW 2. 1. WSOi <=> Gateway 2. TDO; } Pin A } GWn Parent Block Interface Block Instrument Block W R A P L E A F Pin B Pin n In Terms of Software Code Blocks PDL Block Method 1 Method 2 Methodn

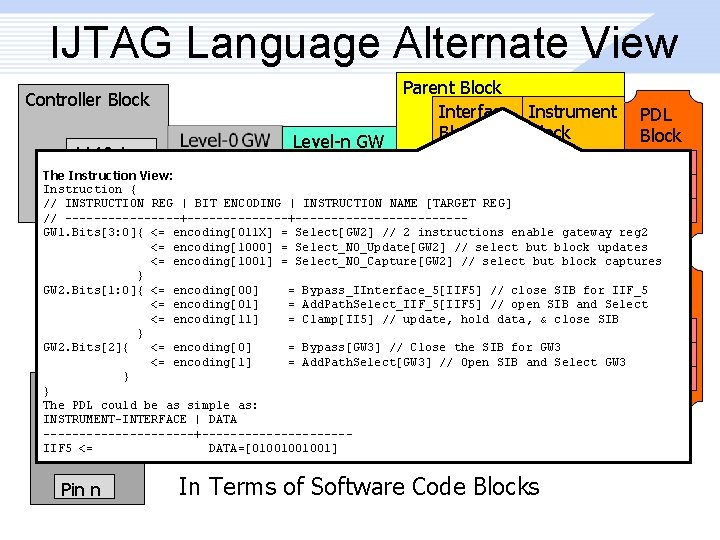

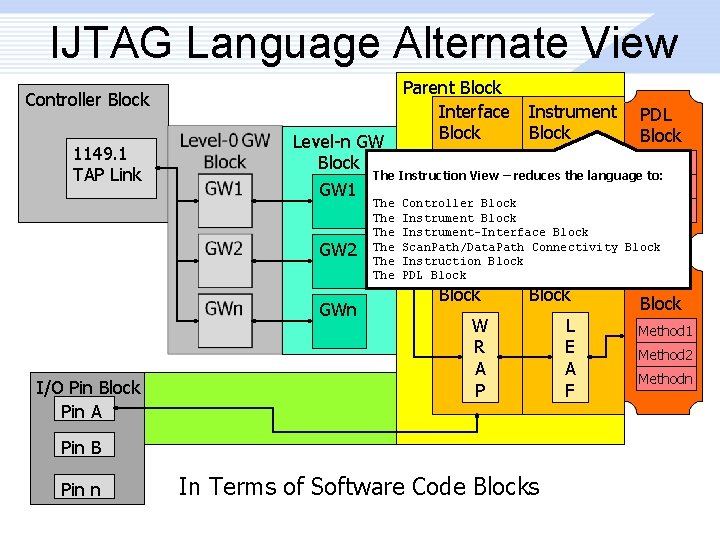

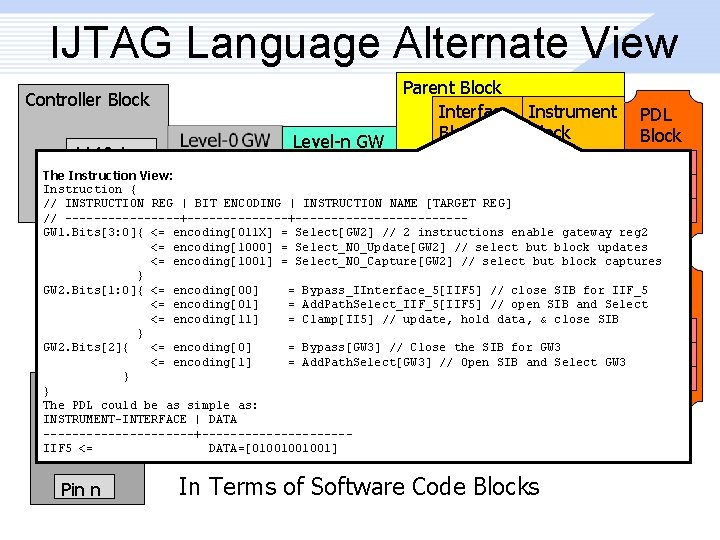

An Alternate View – Instructions Ø An alternate view is that there is no specific Hardware Description, but a map of Instructions – this view requires only the scanpaths to be described (since they are variable and not fixed by the Standard) Ø Different Users may get benefit from different representations: • Design Verification; ATE Test; Board Test; Yield-Analysis; In-System Test Ø There are two basic types of Instructions in the 1687 architecture: • Those that configure and control the Access Mechanism or Architecture Configuration (e. g. Scan. Paths, Gateways) – Gateway Registers can be viewed as Distributed Instruction-Registers • Those that configure and control the Instrument Interface – the Instrument. Interface Register can be viewed as Data-Registers • Note: the Instrument itself is outside of the Standard since it is not specified or standardized by the 1687 Standard

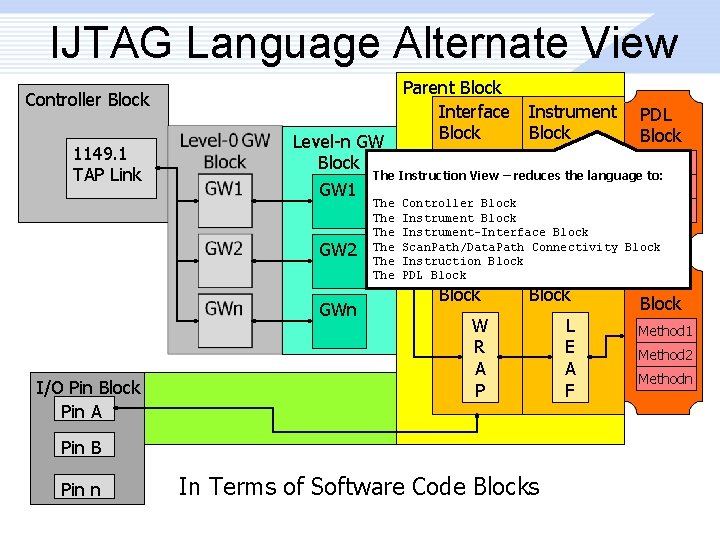

IJTAG Language Alternate View Controller Block 1149. 1 The Instruction TAP Link. View: Level-n GW Block GW 1 Parent Block Interface Block Instrument Block PDL Block Method 1 W L R E Method 2 Instruction { // INSTRUCTION REG | BIT ENCODING | INSTRUCTION NAME [TARGET REG] A A Methodn // --------+-------------------P F GW 1. Bits[3: 0]{ <= encoding[011 X] = Select[GW 2] // 2 instructions enable gateway reg 2 <= encoding[1000] = Select_NO_Update[GW 2] // select but block updates GW 2 <= encoding[1001] = Select_NO_Capture[GW 2] // select but block captures } Interface Instrument PDL GW 2. Bits[1: 0]{ <= encoding[00] = Bypass_IInterface_5[IIF 5] // close SIB for IIF_5 Block <= encoding[01] = Add. Path. Select_IIF_5[IIF 5] // open SIB and Select Block GWn <= encoding[11] = Clamp[II 5] // update, hold data, & close SIB W L Method 1 } GW 2. Bits[2]{ <= encoding[0] = Bypass[GW 3] // Close the SIB for GW 3 R E Method 2 <= encoding[1] = Add. Path. Select[GW 3] // Open SIB and Select GW 3 A A } Methodn I/O Pin Block } P F The PDL could be as simple as: Pin A INSTRUMENT-INTERFACE | DATA -----------+----------IIF 5 <= DATA=[01001001001] Pin B Pin n In Terms of Software Code Blocks

IJTAG Language Alternate View Controller Block 1149. 1 TAP Link I/O Pin Block Pin A Parent Block Interface Block Instrument Block Level-n GW Method 1 Block W L The Instruction View – reduces the language to: R E Method 2 GW 1 The Controller Block A A Methodn The Instrument Block P F The Instrument-Interface Block GW 2 The Scan. Path/Data. Path Connectivity Block The Instruction Block The PDL Block Interface Instrument PDL Block GWn W L Method 1 R E Method 2 A A Methodn P F Pin B Pin n PDL Block In Terms of Software Code Blocks

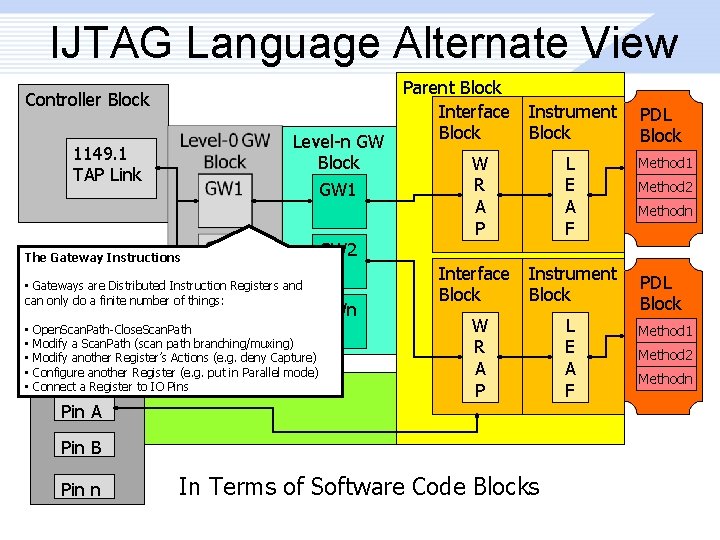

IJTAG Language Alternate View Controller Block Level-n GW Block GW 1 1149. 1 TAP Link The Gateway Instructions • Gateways are Distributed Instruction Registers and can only do a finite number of things: • Open. Scan. Path-Close. Scan. Path • Modify a Scan. Path (scan path branching/muxing) • Modify another Register’s Actions (e. g. deny Capture) • Configure another Register (e. g. put in Parallel mode) • Connect a Register I/O Pin Blockto IO Pins Pin A GW 2 GWn Parent Block Interface Block Instrument Block W R A P L E A F Pin B Pin n In Terms of Software Code Blocks PDL Block Method 1 Method 2 Methodn

We’re almost there… Ø Only a few hundred more slides to go… Just Kidding!

What’s Left to Define? Ø Which Code blocks are optional? Which are required? • Is a Gateway Level-0 Block required – if there are only a few instruments, can their Instrument-Interfaces (TDRs) be accessed directly from TAP Instructions? Ø What Keywords are associated with each Code Block? • Are blocks defined by Keywords such as Instrument, Interface, Controller, etc. ? Ø What are the “legal” groupings of Code Blocks? For example: • More than one Controller Block? • A Controller Block connected directly to an Instrument Interface with no Gateway Blocks? • PDL as a separate file or PDL embedded within the Instrument Block? • Mixed Gateway and Instrument-Interface Blocks? Ø Have we defined all of the HW elements (GDR, IIF, Pins, etc. )? Ø Can 1687 concepts be applied above the chip? (Dot-2) • Board-Level clock/power domains break daisy-chain connections • Test-Scheduling including multiple chips break star connections

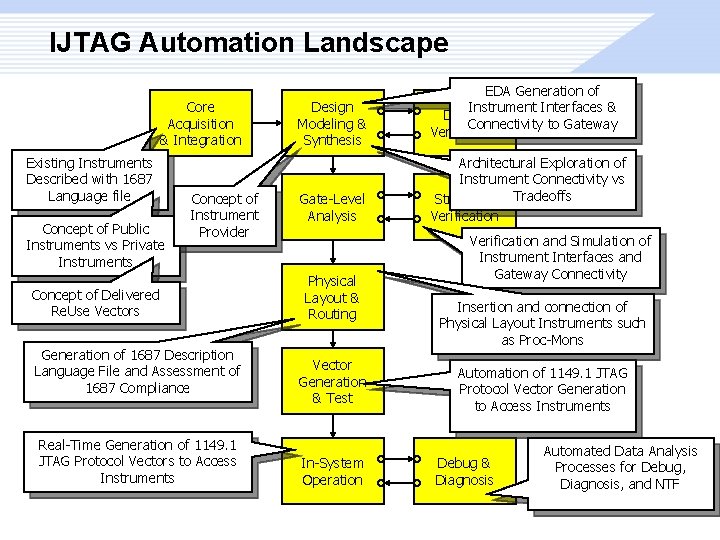

IJTAG Automation Landscape Core Acquisition & Integration Existing Instruments Described with 1687 Language file Concept of Public Instruments vs Private Instruments Concept of Instrument Provider Concept of Delivered Re. Use Vectors Generation of 1687 Description Language File and Assessment of 1687 Compliance Real-Time Generation of 1149. 1 JTAG Protocol Vectors to Access Instruments Design Modeling & Synthesis Gate-Level Analysis Physical Layout & Routing Vector Generation & Test In-System Operation EDA Generation of Instrument Interfaces & Design Connectivity to Gateway Verification Architectural Exploration of Instrument Connectivity vs Structural Tradeoffs Verification and Simulation of Instrument Interfaces and Gateway Connectivity Insertion and connection of Physical Layout Instruments such as Proc-Mons Automation of 1149. 1 JTAG Protocol Vector Generation to Access Instruments Debug & Diagnosis Automated Data Analysis Processes for Debug, Diagnosis, and NTF

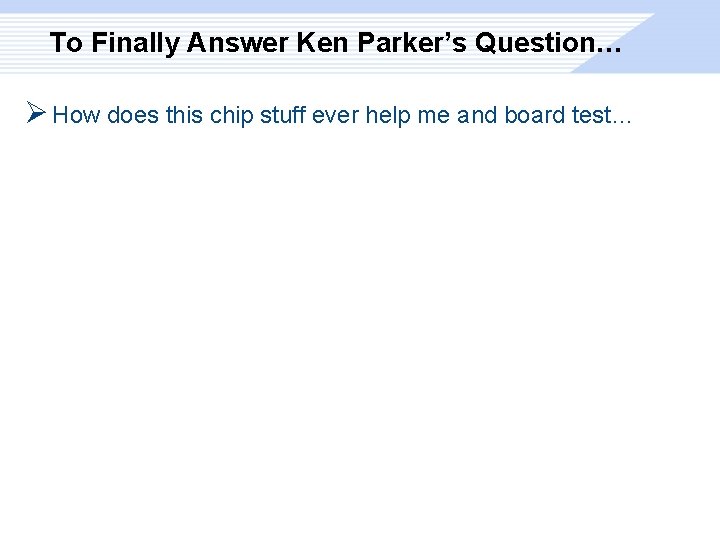

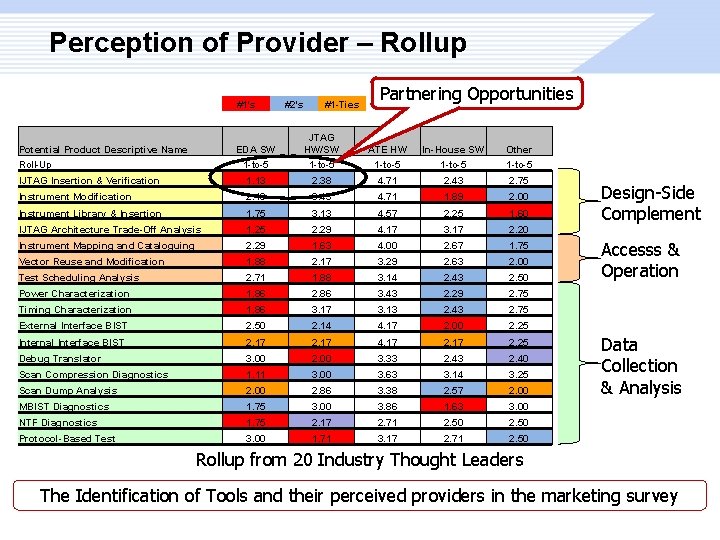

Perception of Provider – Rollup #1's #2's #1 -Ties Partnering Opportunities EDA SW JTAG HW/SW ATE HW In-House SW Other 1 -to-5 1 -to-5 IJTAG Insertion & Verification 1. 13 2. 38 4. 71 2. 43 2. 75 Instrument Modification 2. 13 3. 43 4. 71 1. 89 2. 00 Instrument Library & Insertion 1. 75 3. 13 4. 57 2. 25 1. 60 IJTAG Architecture Trade-Off Analysis 1. 25 2. 29 4. 17 3. 17 2. 20 Instrument Mapping and Cataloguing 2. 29 1. 63 4. 00 2. 67 1. 75 Vector Reuse and Modification 1. 88 2. 17 3. 29 2. 63 2. 00 Test Scheduling Analysis 2. 71 1. 88 3. 14 2. 43 2. 50 Power Characterization 1. 86 2. 86 3. 43 2. 29 2. 75 Timing Characterization 1. 86 3. 17 3. 13 2. 43 2. 75 External Interface BIST 2. 50 2. 14 4. 17 2. 00 2. 25 Internal Interface BIST 2. 17 4. 17 2. 25 Debug Translator 3. 00 2. 00 3. 33 2. 40 Scan Compression Diagnostics 1. 11 3. 00 3. 63 3. 14 3. 25 Scan Dump Analysis 2. 00 2. 86 3. 38 2. 57 2. 00 MBIST Diagnostics 1. 75 3. 00 3. 86 1. 63 3. 00 NTF Diagnostics 1. 75 2. 17 2. 71 2. 50 Protocol-Based Test 3. 00 1. 71 3. 17 2. 71 2. 50 Potential Product Descriptive Name Roll-Up Design-Side Complement Accesss & Operation Data Collection & Analysis Rollup from 20 Industry Thought Leaders The Identification of Tools and their perceived providers in the marketing survey

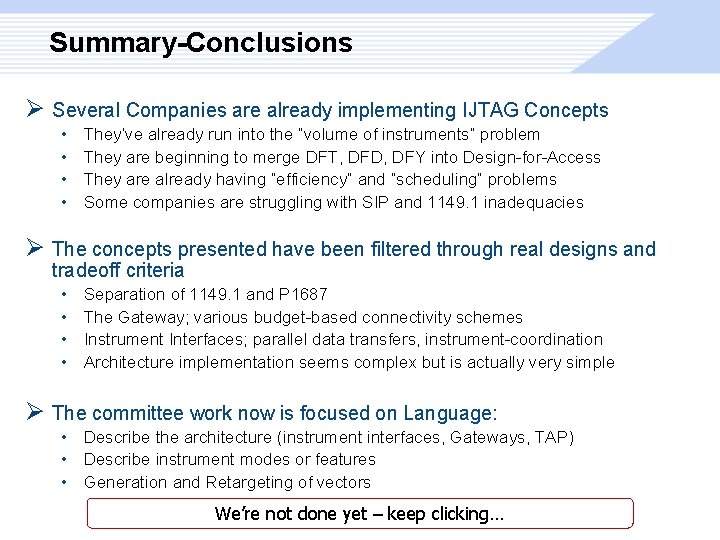

Summary-Conclusions Ø Several Companies are already implementing IJTAG Concepts • • They’ve already run into the “volume of instruments” problem They are beginning to merge DFT, DFD, DFY into Design-for-Access They are already having “efficiency” and “scheduling” problems Some companies are struggling with SIP and 1149. 1 inadequacies Ø The concepts presented have been filtered through real designs and tradeoff criteria • • Separation of 1149. 1 and P 1687 The Gateway; various budget-based connectivity schemes Instrument Interfaces; parallel data transfers, instrument-coordination Architecture implementation seems complex but is actually very simple Ø The committee work now is focused on Language: • Describe the architecture (instrument interfaces, Gateways, TAP) • Describe instrument modes or features • Generation and Retargeting of vectors We’re not done yet – keep clicking…

To Finally Answer Ken Parker’s Question… Ø How does this chip stuff ever help me and board test…

Inside-the-Chip Instrument Map TAP SM TCK TMS TDI TAP IR With GWENs JTAG Regs TAP IR TDO Gateway/Instrument Interface -1. a 1 2 3 4 5 6 a 1 a Gateway-1 a b c BSDL Description Gateway Instrument Gateways Interface -1. b can Instrument Interface -1. c. b. a 1 Combination Instrument-IF Instrument and Gateway Interface -1. a. a produce “Add_Scan_Path”, “Bypass_Other_Register”, 1 b “Configure_Other_Register”, “Modify_Register_Actions”, and “Connect_IO_Pins” The Instruction View: types of Instructions Gateway-1. c Instrument Interface -1. c. a 1 cba 1 1 aa PDL MBIST { // the Protocol Description Instrument Method Reset { Interface -1. c. b. a 2 apply { "TAM" = 0*; } apply { RESETS = 00; } } Method Start_MBIST { apply { ON = 1; } } Method Get_Status { 1 ca read { DONE; FAIL; } } } Daisy-Chained Instruments 1 cba 2 Instrument INSTRUCTION REG | BIT ENCODING | INSTRUCTION NAME [TARGET REG] Interface -1. c. b. b Gateway-1. c. b --------+-------------------a b GW 1. Bits[3: 0]{ <= encoding[011 X] = Add. Path. Select[GW 2] <= encoding[1000] = Select_NO_Update[GW 2] b c <= encoding[1001] = Select_NO_Capture[GW 2] 1 cbb } c d GW 1 c. Bits[1: 0]{<= encoding[00] = Bypass_IInterface_5[IIF 5] <= encoding[01] = Add. Path. Select_IIF_5[IIF 5] Compound Instrument Individual MIB- Gateway <= encoding[11] = Clamp[II 5] Gateway Interface Leaf G 1=Default } Cell G 2=Select GW 2. Bits[2]{ <= encoding[0] = Bypass[GW 3] Instrument <= encoding[1] = Add. Path. Select[GW 3] Interface -1. c. b. c Instrument Interface -1. c. d or 2. b. d } Interface -2. c a Gateway-2 a b c Mutual-Exclusive Gateway (G 1 & G 2 cannot be selected simultaneously) Hierarchy Lev-0 1 cbc 1 cc 2 c Hierarchy Level-1 Hierarchy Level-2 Hierarchy Level-3

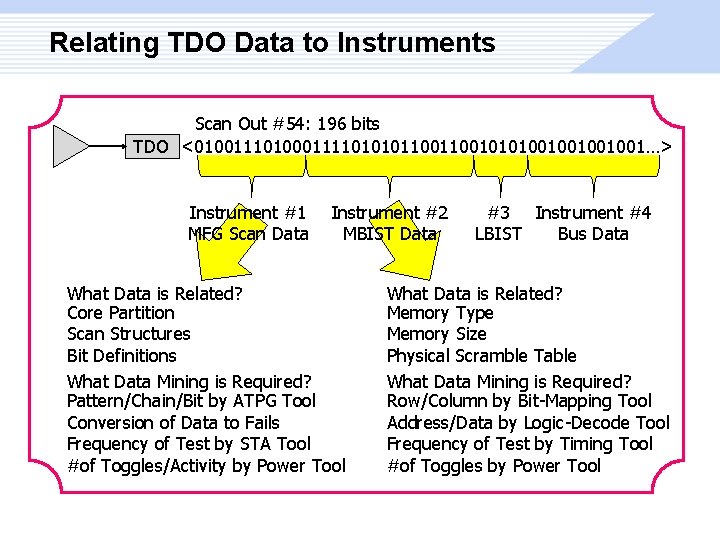

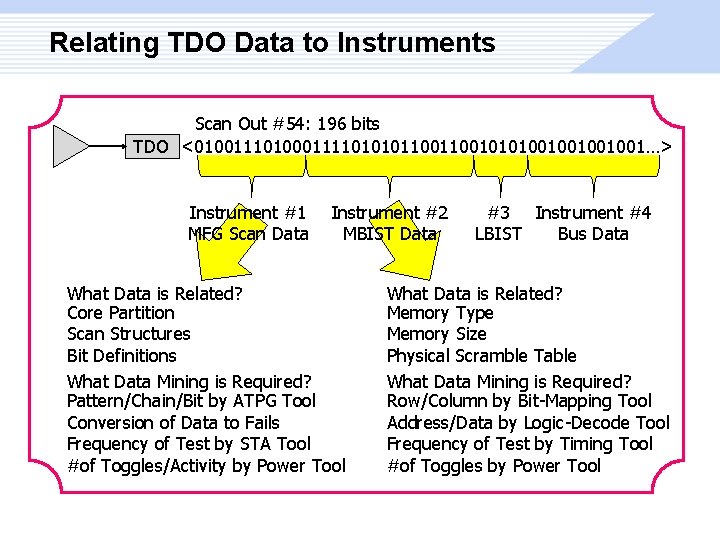

Relating TDO Data to Instruments Scan Out #54: 196 bits TDO <010011101000111101010110010101001001…> Instrument #1 MFG Scan Data Instrument #2 MBIST Data What Data is Related? Core Partition Scan Structures Bit Definitions What Data Mining is Required? Pattern/Chain/Bit by ATPG Tool Conversion of Data to Fails Frequency of Test by STA Tool #of Toggles/Activity by Power Tool #3 Instrument #4 LBIST Bus Data What Data is Related? Memory Type Memory Size Physical Scramble Table What Data Mining is Required? Row/Column by Bit-Mapping Tool Address/Data by Logic-Decode Tool Frequency of Test by Timing Tool #of Toggles by Power Tool

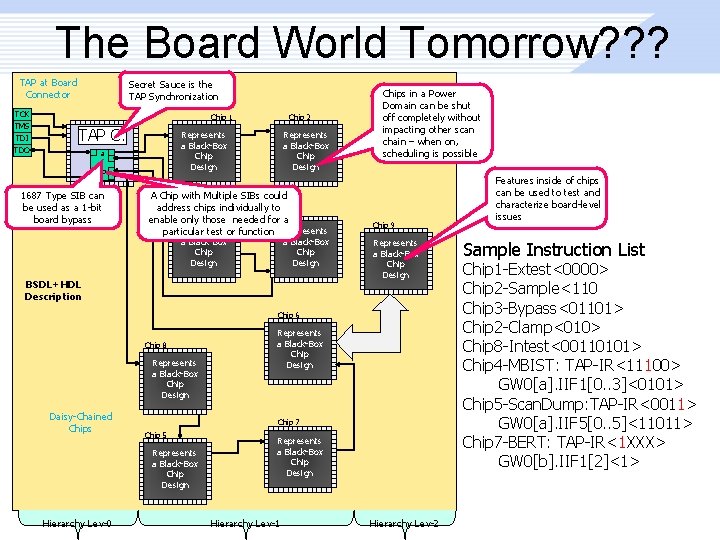

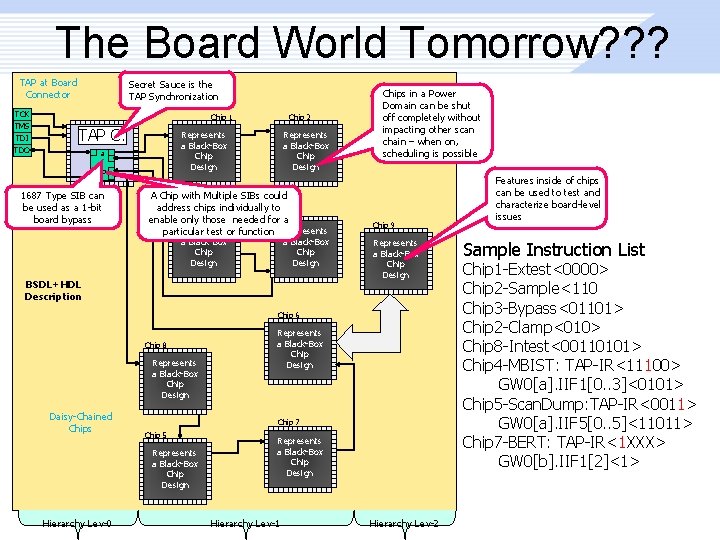

The Board World Tomorrow? ? ? TAP at Board Connector TCK TMS TDI TDO Secret Sauce is the TAP Synchronization Chip 1 TAP C. Represents a Black-Box Chip Design a b 1687 Type SIB can be used as a 1 -bit board bypass Chip 2 Represents a Black-Box Chip Design A Chip with Multiple SIBs could address chips individually to. Chip 4 Chip 3 enable only those needed for a Represents particular test or function Represents a Black-Box Chip Design BSDL+HDL Description Chips in a Power Domain can be shut off completely without impacting other scan chain – when on, scheduling is possible Chip 9 Represents a Black-Box Chip Design Chip 6 Chip 8 Represents a Black-Box Chip Design Daisy-Chained Chips Chip 7 Chip 5 Represents a Black-Box Chip Design Hierarchy Lev-0 Represents a Black-Box Chip Design Hierarchy Lev-1 Hierarchy Lev-2 Features inside of chips can be used to test and characterize board-level issues Sample Instruction List Chip 1 -Extest<0000> Chip 2 -Sample<110 Chip 3 -Bypass<01101> Chip 2 -Clamp<010> Chip 8 -Intest<00110101> Chip 4 -MBIST: TAP-IR<11100> GW 0[a]. IIF 1[0. . 3]<0101> Chip 5 -Scan. Dump: TAP-IR<0011> GW 0[a]. IIF 5[0. . 5]<11011> Chip 7 -BERT: TAP-IR<1 XXX> GW 0[b]. IIF 1[2]<1>