SRAM vs DRAM Transis Access per bit time

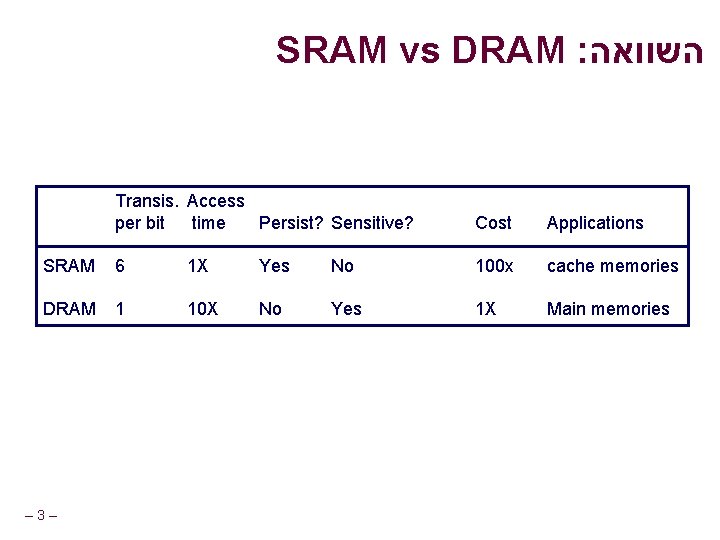

SRAM vs DRAM : השוואה Transis. Access per bit time Persist? Sensitive? Cost Applications SRAM 6 1 X Yes No 100 x cache memories DRAM 1 10 X No Yes 1 X Main memories – 3–

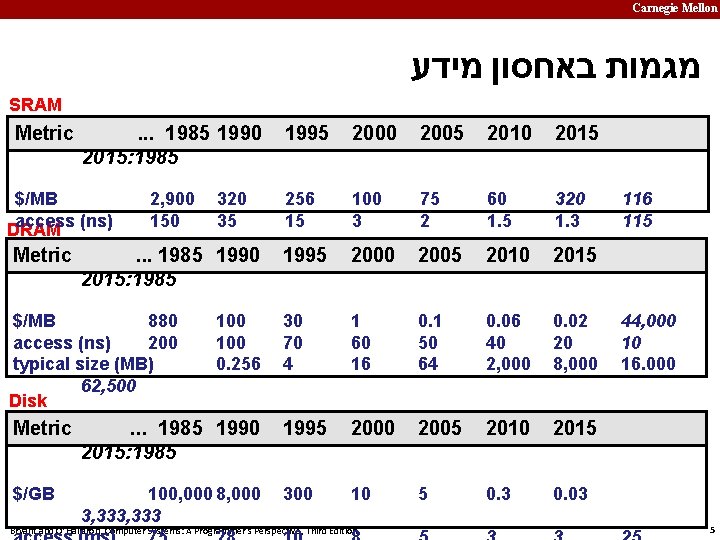

Carnegie Mellon מגמות באחסון מידע SRAM Metric . . . 1985 1990 2015: 1985 $/MB access (ns) DRAM Metric 2, 900 150 320 35 . . . 1985 1990 2015: 1985 $/MB 880 access (ns) 200 typical size (MB) 62, 500 Disk 100 0. 256 1995 2000 2005 2010 2015 256 15 100 3 75 2 60 1. 5 320 1. 3 1995 2000 2005 2010 2015 30 70 4 1 60 16 0. 1 50 64 0. 06 40 2, 000 0. 02 20 8, 000 Metric . . . 1985 1990 2015: 1985 1995 2000 2005 2010 2015 $/GB 100, 000 8, 000 3, 333 300 10 5 0. 3 0. 03 Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition 116 115 44, 000 10 16. 000 5

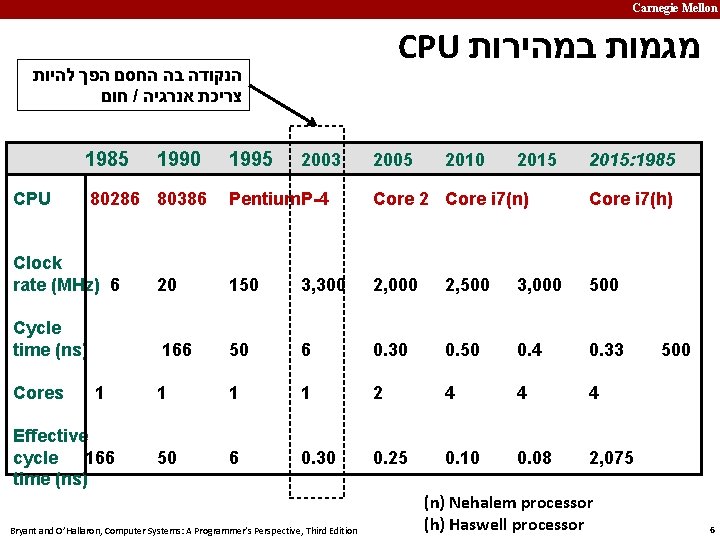

Carnegie Mellon CPU מגמות במהירות הנקודה בה החסם הפך להיות חום / צריכת אנרגיה 1985 CPU 1990 80286 80386 1995 2003 2005 2010 2015: 1985 Pentium. P-4 Core 2 Core i 7(n) Core i 7(h) Clock rate (MHz) 6 20 150 3, 300 2, 000 2, 500 3, 000 500 Cycle time (ns) 166 50 6 0. 30 0. 50 0. 4 0. 33 1 1 1 2 4 4 4 50 6 0. 30 0. 25 0. 10 0. 08 2, 075 Cores 1 Effective cycle 166 time (ns) Bryant and O’Hallaron, Computer Systems: A Programmer’s Perspective, Third Edition (n) Nehalem processor (h) Haswell processor 500 6

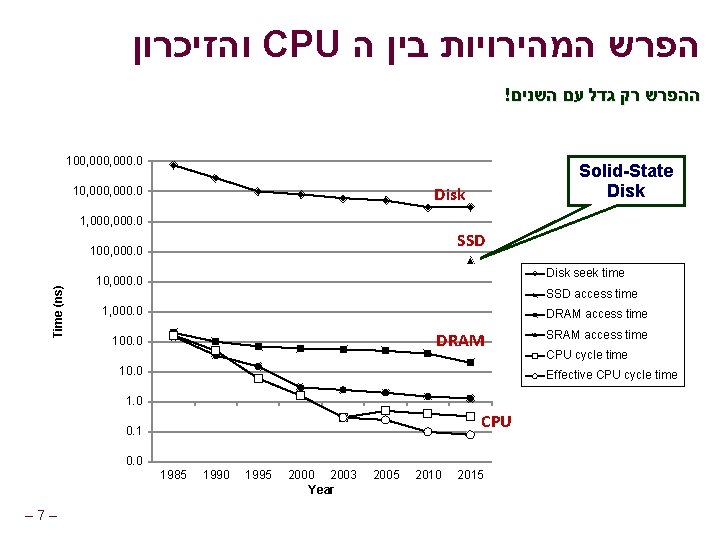

והזיכרון CPU הפרש המהירויות בין ה ! ההפרש רק גדל עם השנים 100, 000. 0 Solid-State Disk 10, 000. 0 1, 000. 0 SSD Time (ns) 100, 000. 0 Disk seek time 10, 000. 0 SSD access time 1, 000. 0 DRAM access time DRAM 100. 0 10. 0 CPU cycle time Effective CPU cycle time 1. 0 CPU 0. 1 0. 0 1985 – 7– SRAM access time 1990 1995 2000 2003 Year 2005 2010 2015

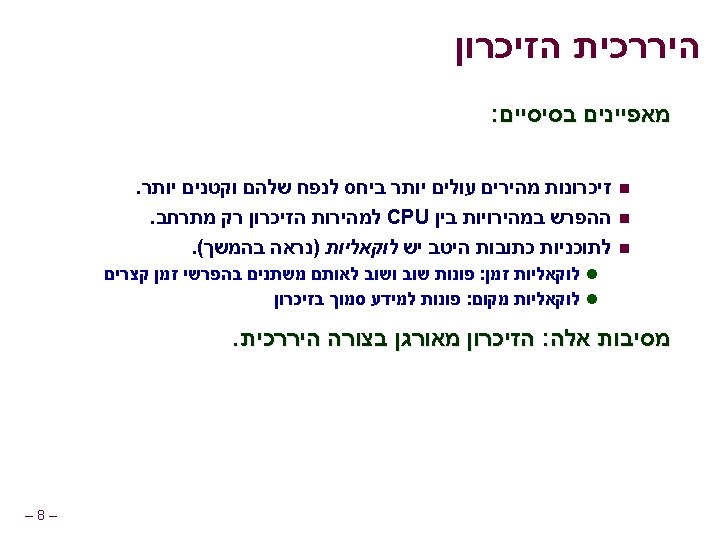

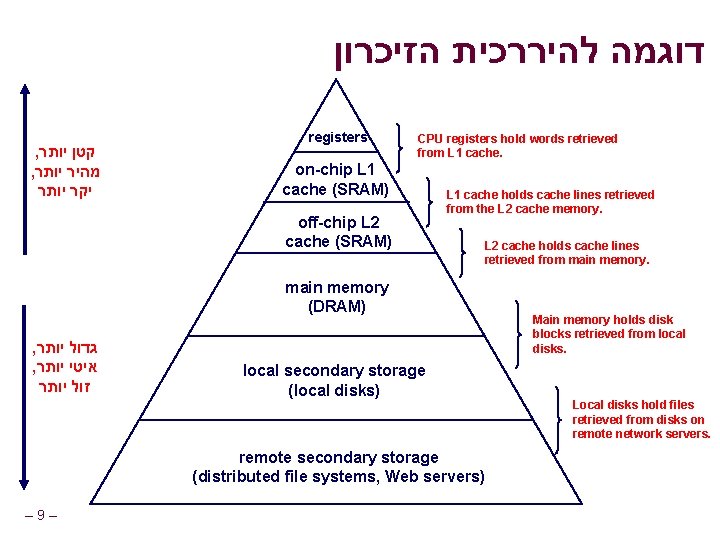

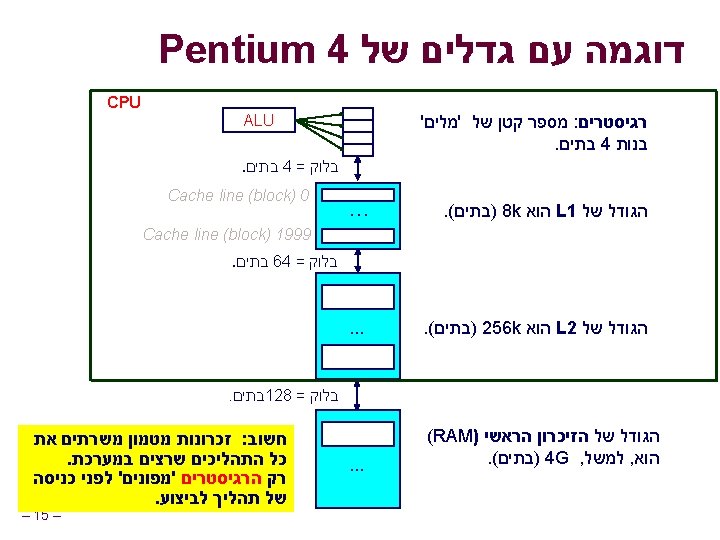

דוגמה להיררכית הזיכרון , קטן יותר , מהיר יותר יקר יותר registers CPU registers hold words retrieved from L 1 cache. on-chip L 1 cache (SRAM) off-chip L 2 cache (SRAM) L 1 cache holds cache lines retrieved from the L 2 cache memory. L 2 cache holds cache lines retrieved from main memory (DRAM) , גדול יותר , איטי יותר זול יותר local secondary storage (local disks) remote secondary storage (distributed file systems, Web servers) – 9– Main memory holds disk blocks retrieved from local disks. Local disks hold files retrieved from disks on remote network servers.

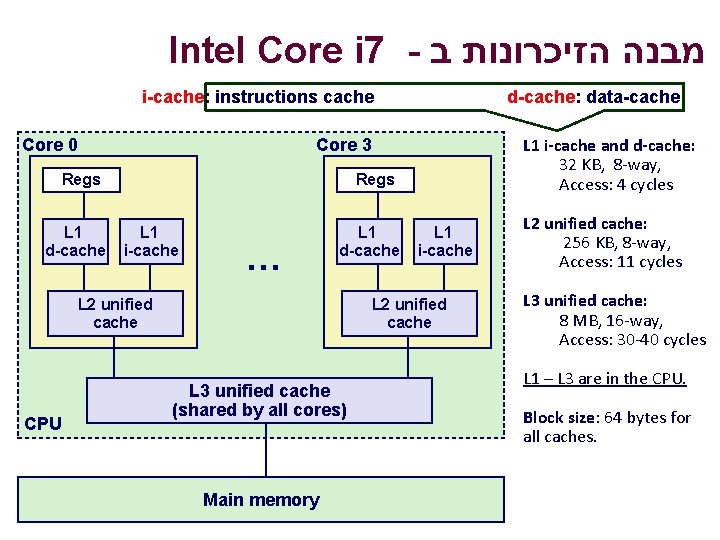

Intel Core i 7 - מבנה הזיכרונות ב i-cache: instructions cache Core 0 Regs L 1 i-cache … L 1 d-cache L 2 unified cache CPU – 16 – L 1 i-cache and d-cache: 32 KB, 8 -way, Access: 4 cycles Core 3 Regs L 1 d-cache: data-cache L 1 i-cache L 2 unified cache L 3 unified cache (shared by all cores) Main memory L 2 unified cache: 256 KB, 8 -way, Access: 11 cycles L 3 unified cache: 8 MB, 16 -way, Access: 30 -40 cycles L 1 – L 3 are in the CPU. Block size: 64 bytes for all caches.

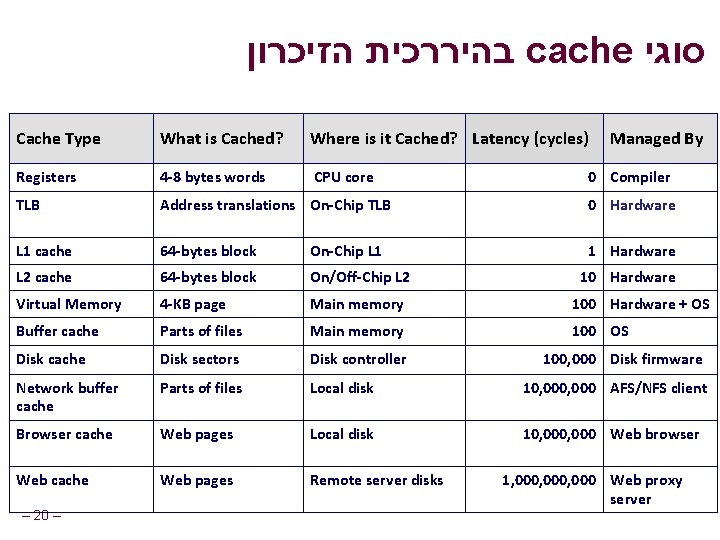

בהיררכית הזיכרון cache סוגי Cache Type What is Cached? Where is it Cached? Latency (cycles) Registers 4 -8 bytes words CPU core TLB Address translations On-Chip TLB 0 Hardware L 1 cache 64 -bytes block On-Chip L 1 1 Hardware L 2 cache 64 -bytes block On/Off-Chip L 2 Virtual Memory 4 -KB page Main memory 100 Hardware + OS Buffer cache Parts of files Main memory 100 OS Disk cache Disk sectors Disk controller Network buffer cache Parts of files Local disk 10, 000 AFS/NFS client Browser cache Web pages Local disk 10, 000 Web browser Web cache Web pages Remote server disks – 20 – Managed By 0 Compiler 10 Hardware 100, 000 Disk firmware 1, 000, 000 Web proxy server

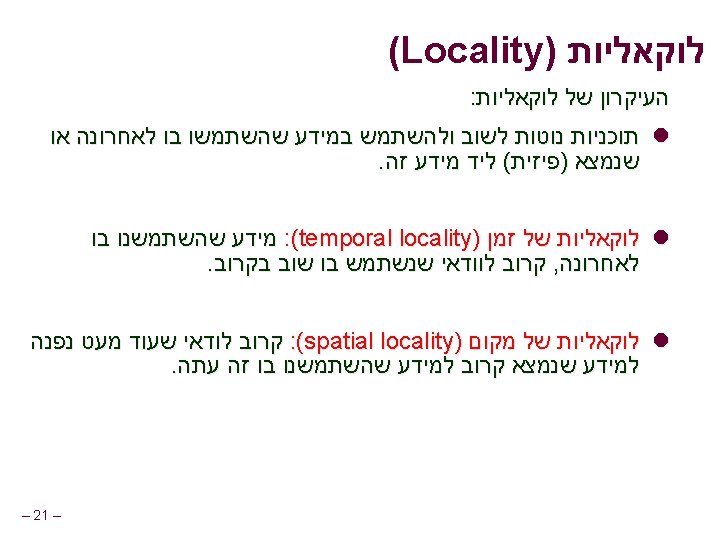

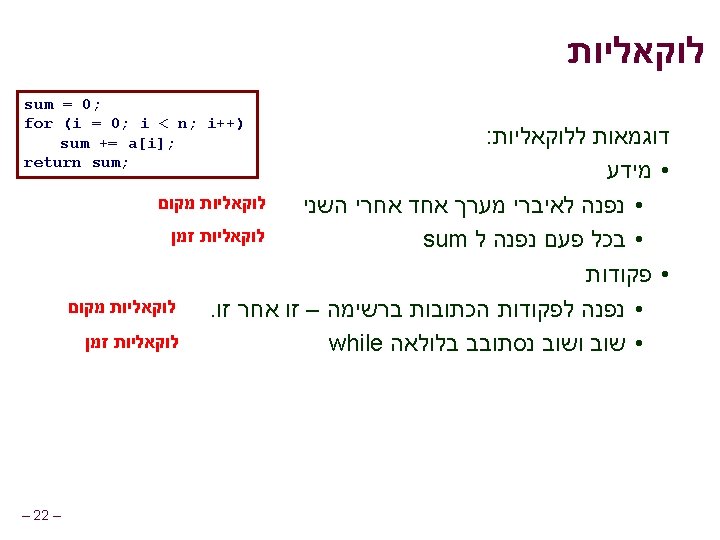

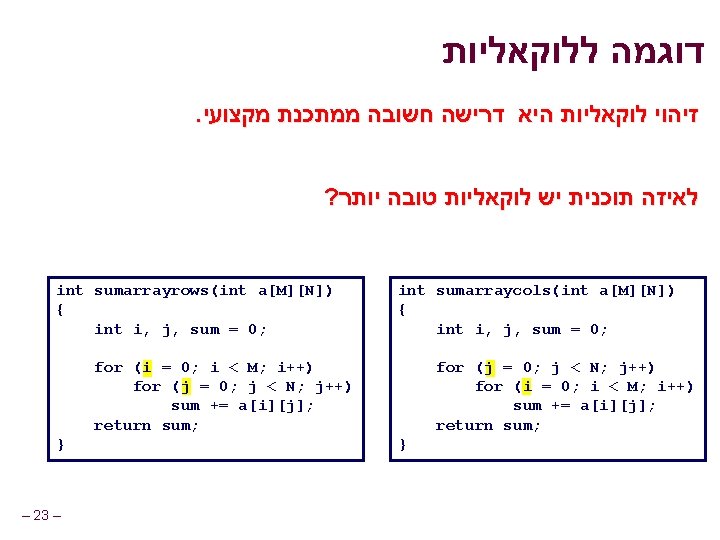

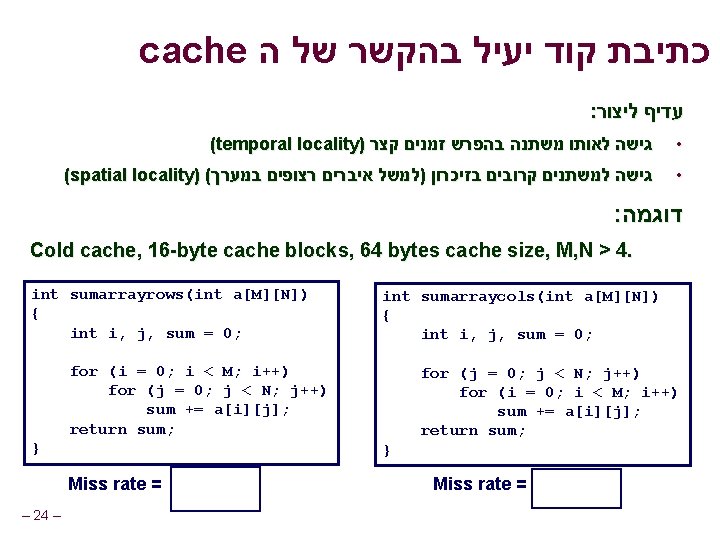

cache כתיבת קוד יעיל בהקשר של ה : עדיף ליצור (temporal locality) גישה לאותו משתנה בהפרש זמנים קצר • (spatial locality) ( גישה למשתנים קרובים בזיכרון )למשל איברים רצופים במערך • : דוגמה Cold cache, 16 -byte cache blocks, 64 bytes cache size, M, N > 4. int sumarrayrows(int a[M][N]) { int i, j, sum = 0; int sumarraycols(int a[M][N]) { int i, j, sum = 0; for (i = 0; i < M; i++) for (j = 0; j < N; j++) sum += a[i][j]; return sum; } } Miss rate = 1/4 = 25% – 24 – for (j = 0; j < N; j++) for (i = 0; i < M; i++) sum += a[i][j]; return sum; Miss rate = 100%

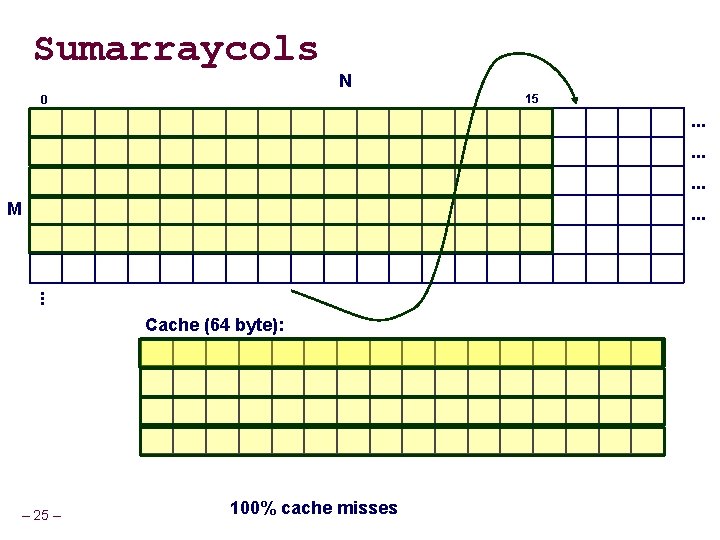

Sumarraycols N 15 0 . . M . . . Cache (64 byte): – 25 – 100% cache misses

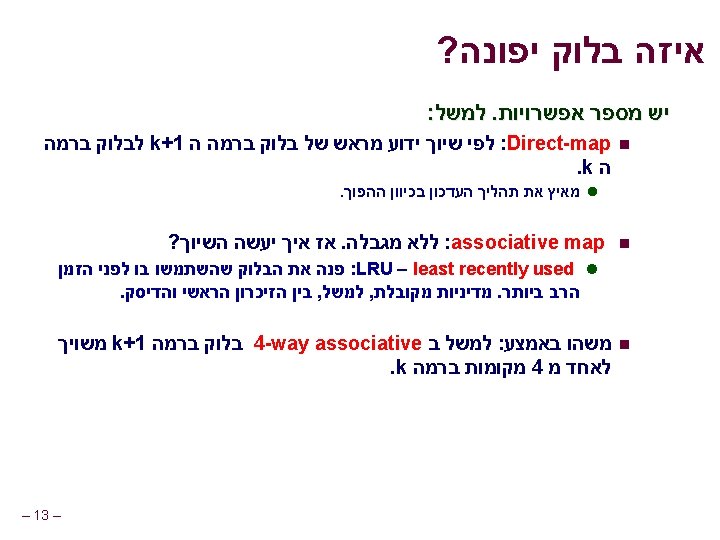

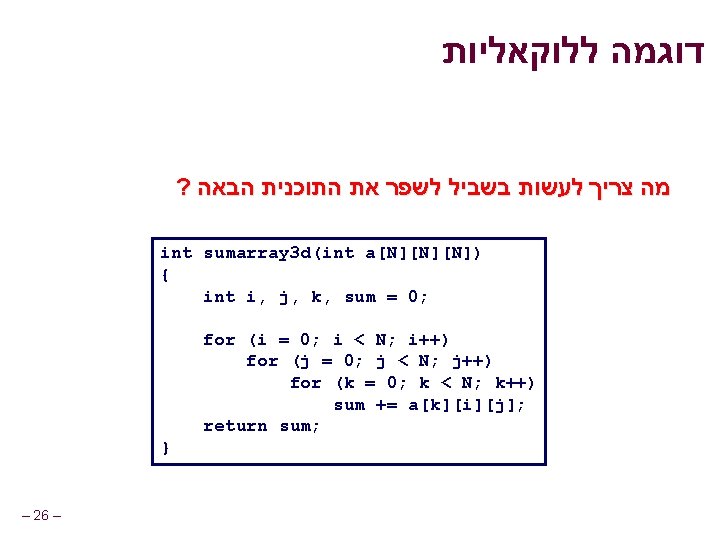

- Slides: 26