OnChip ECC for LowPower SRAM Design HsinI Liu

- Slides: 12

On-Chip ECC for Low-Power SRAM Design Hsin-I Liu EE 241 Project 5/9/2005

Outline n n Introduction to low-power SRAM Introduction on error correction code Analysis of data retention voltage in SRAM Simulations and results 5/9/2005 EE 241 Project

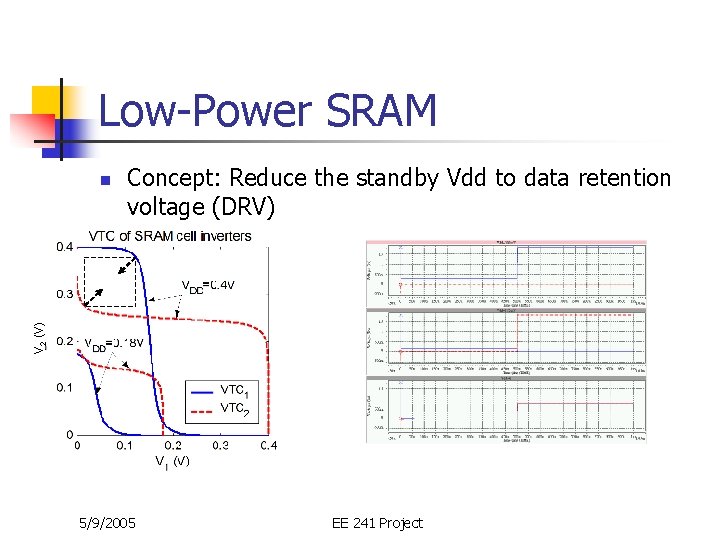

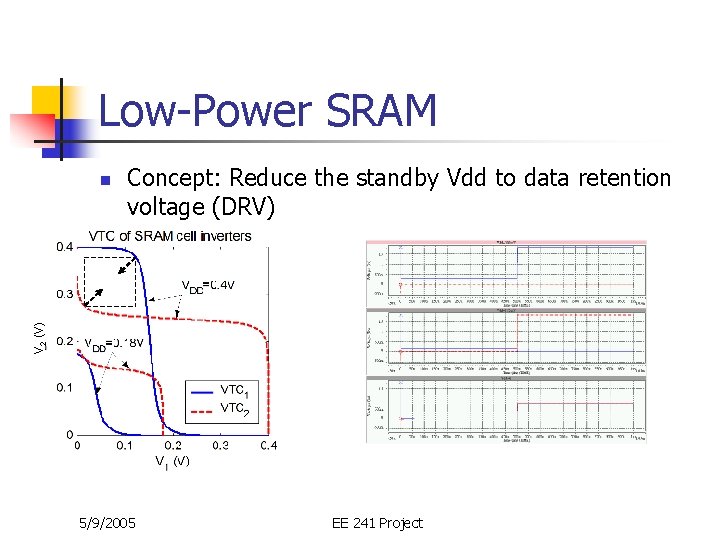

Low-Power SRAM Concept: Reduce the standby Vdd to data retention voltage (DRV) V 2 (V) n 5/9/2005 EE 241 Project

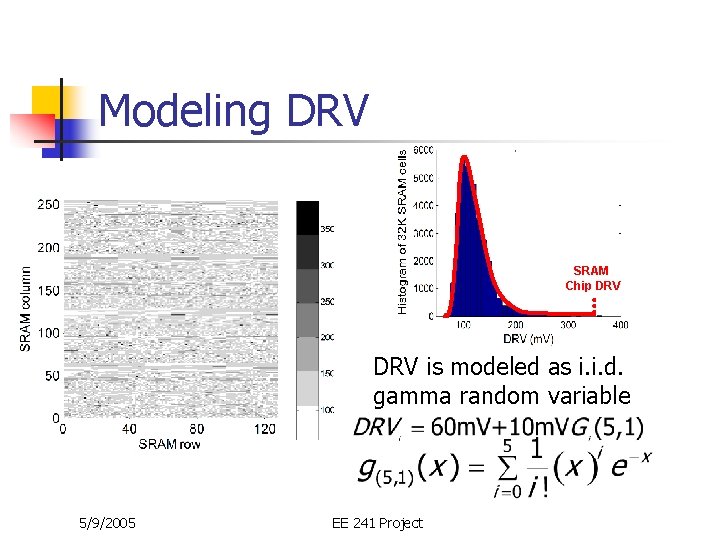

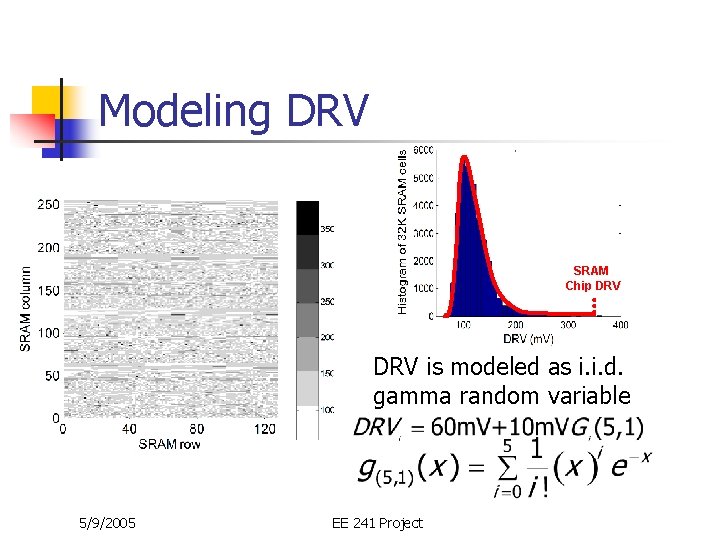

Modeling DRV SRAM Chip DRV is modeled as i. i. d. gamma random variable 5/9/2005 EE 241 Project

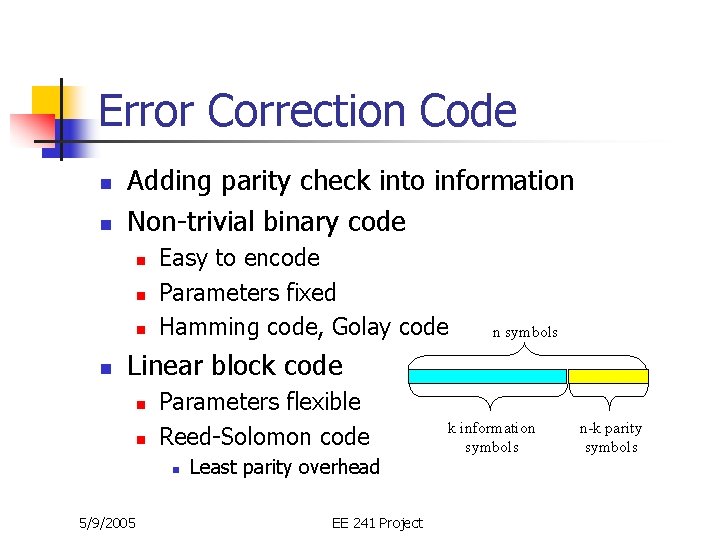

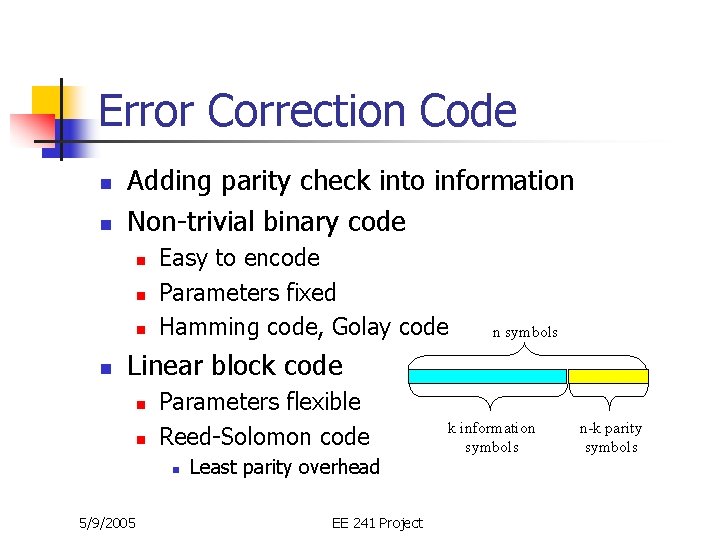

Error Correction Code n n Adding parity check into information Non-trivial binary code n n Easy to encode Parameters fixed Hamming code, Golay code n symbols Linear block code n n Parameters flexible Reed-Solomon code n 5/9/2005 Least parity overhead EE 241 Project k information symbols n-k parity symbols

Applying ECC to SRAM n Latency n n n 5/9/2005 In proportional to block size In this project: Hamming (15, 11), Golay(23, 12), and RS(15, 11) Implementation characteristics are wellknown EE 241 Project

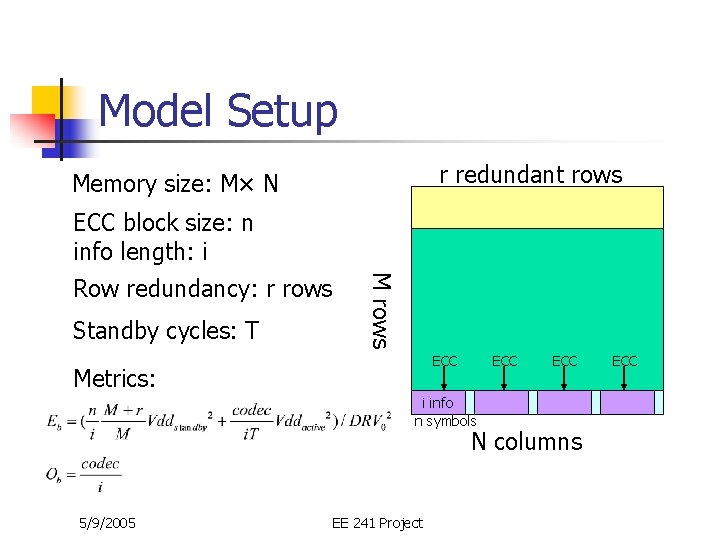

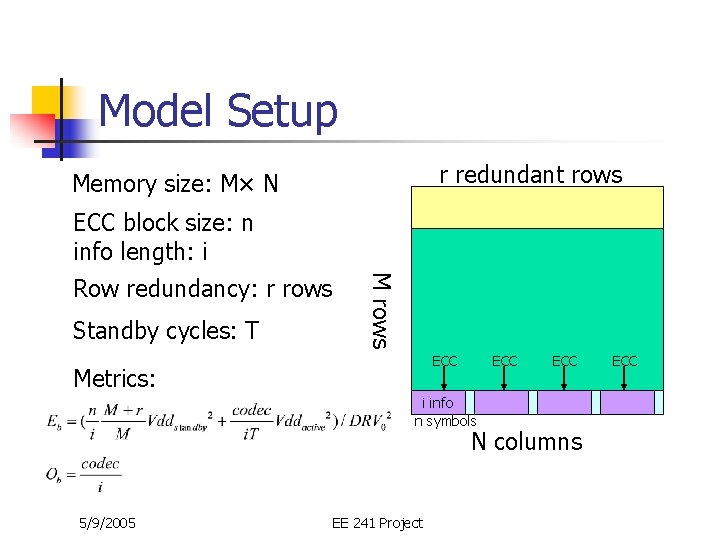

Model Setup r redundant rows Memory size: M× N ECC block size: n info length: i Standby cycles: T M rows Row redundancy: r rows ECC Metrics: ECC i info n symbols ECC N columns 5/9/2005 EE 241 Project ECC

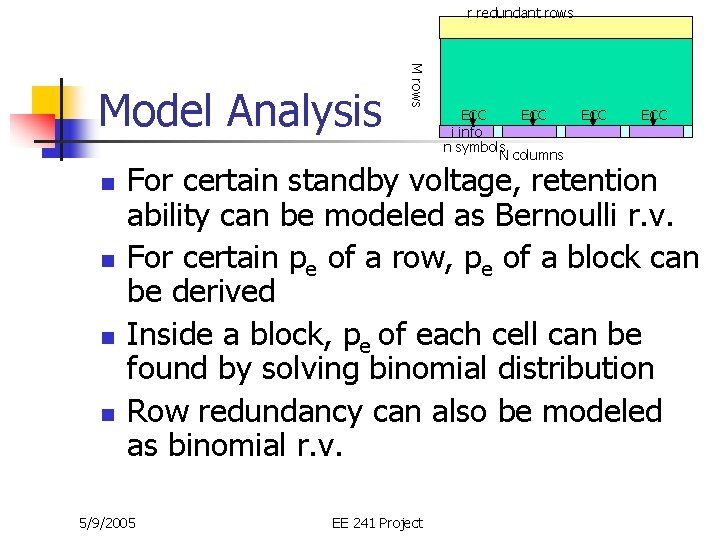

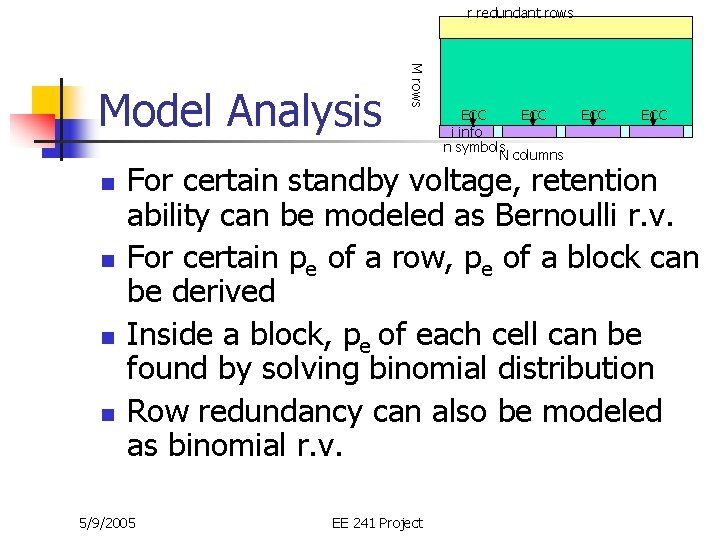

r redundant rows n n M rows Model Analysis ECC i info n symbols N columns ECC For certain standby voltage, retention ability can be modeled as Bernoulli r. v. For certain pe of a row, pe of a block can be derived Inside a block, pe of each cell can be found by solving binomial distribution Row redundancy can also be modeled as binomial r. v. 5/9/2005 EE 241 Project

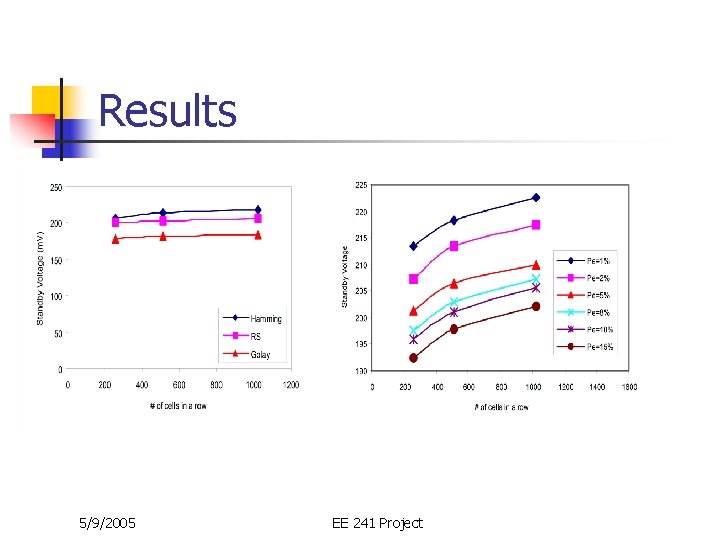

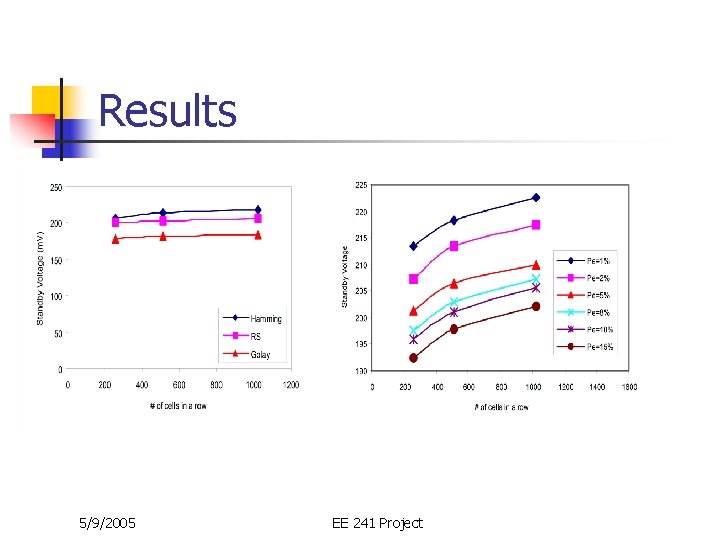

Results 5/9/2005 EE 241 Project

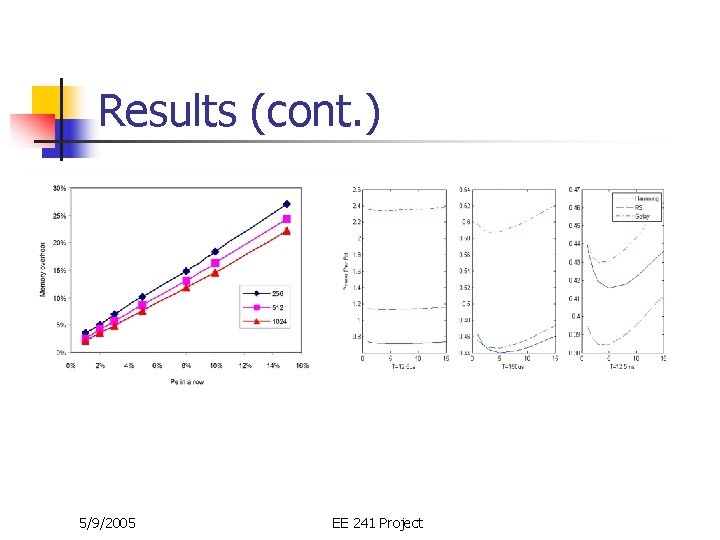

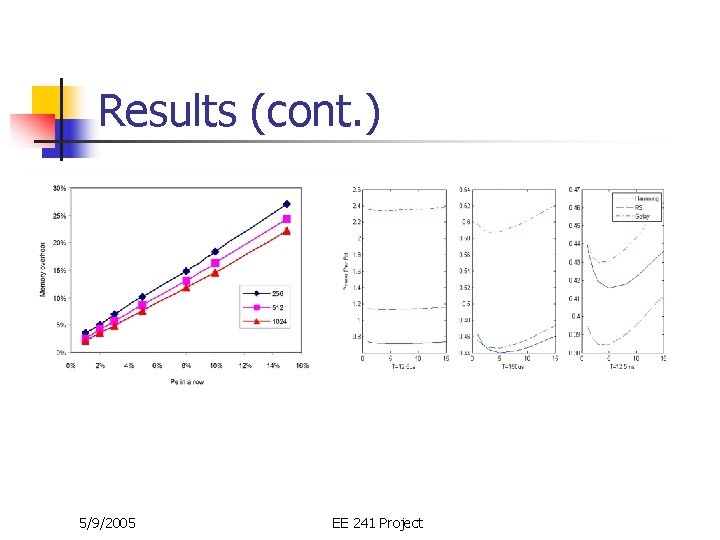

Results (cont. ) 5/9/2005 EE 241 Project

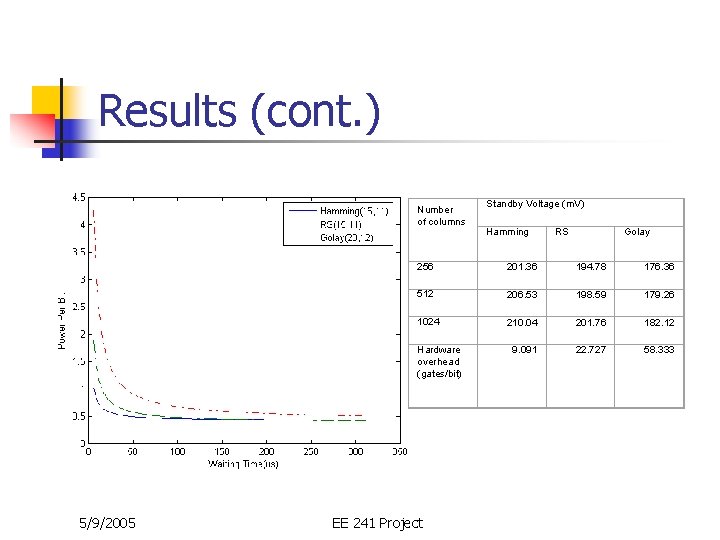

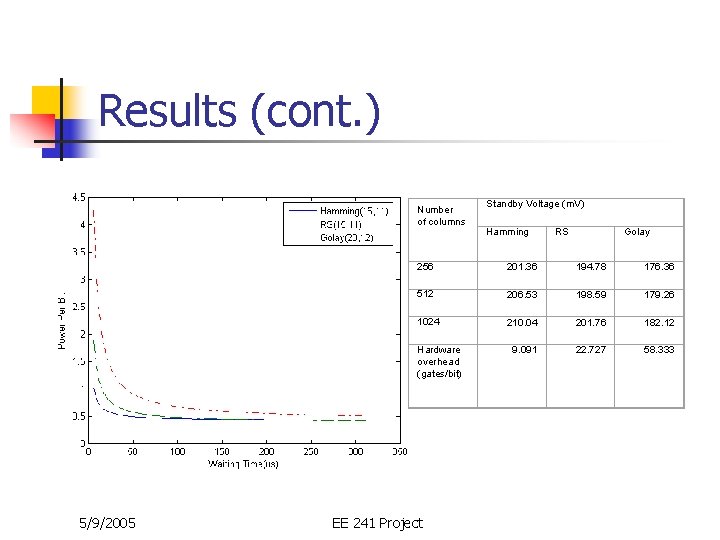

Results (cont. ) Number of columns Hamming RS Golay 256 201. 36 194. 78 176. 36 512 206. 53 198. 59 179. 26 1024 210. 04 201. 76 182. 12 9. 091 22. 727 58. 333 Hardware overhead (gates/bit) 5/9/2005 Standby Voltage (m. V) EE 241 Project

Conclusion n Hamming code introduces the least overhead For short waiting time, Hamming code can reduce Eb from 50% to 2 x As waiting time goes to infinity, Reed. Solomon saves the power by 3 x 5/9/2005 EE 241 Project