DRAM Hwansoo Han DRAM Organization Cell 1 bit

DRAM Hwansoo Han

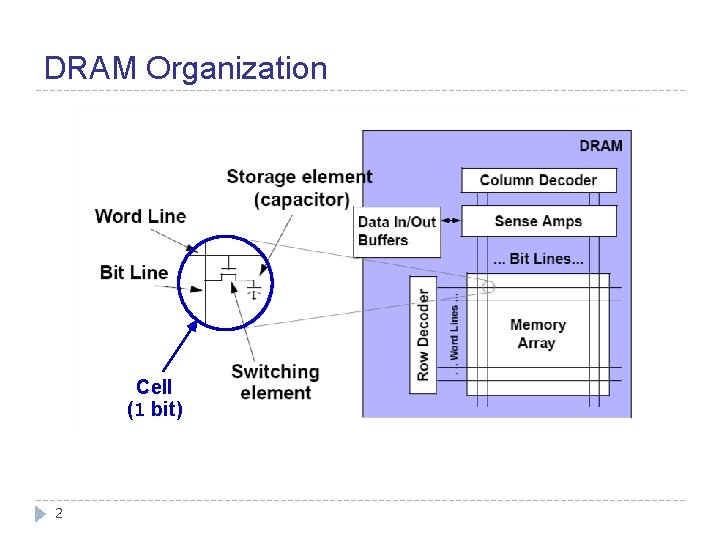

DRAM Organization Cell (1 bit) 2

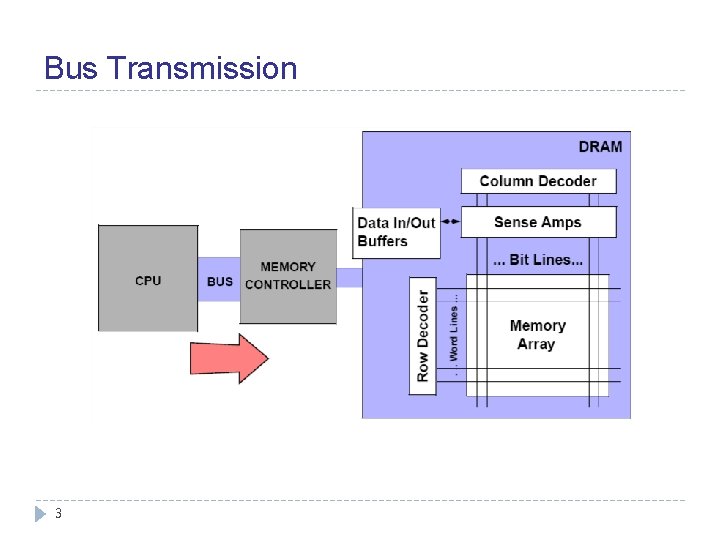

Bus Transmission 3

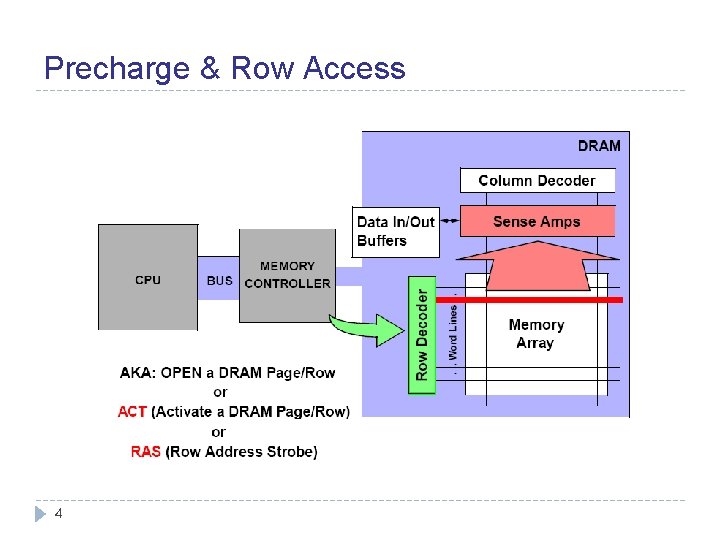

Precharge & Row Access 4

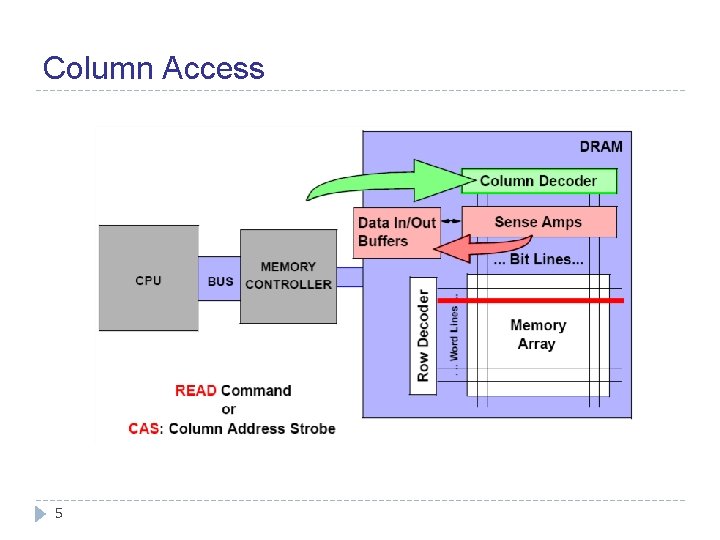

Column Access 5

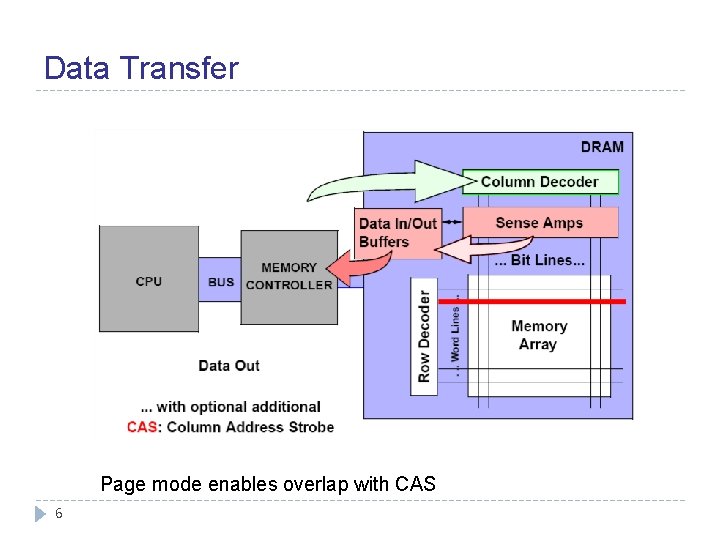

Data Transfer Page mode enables overlap with CAS 6

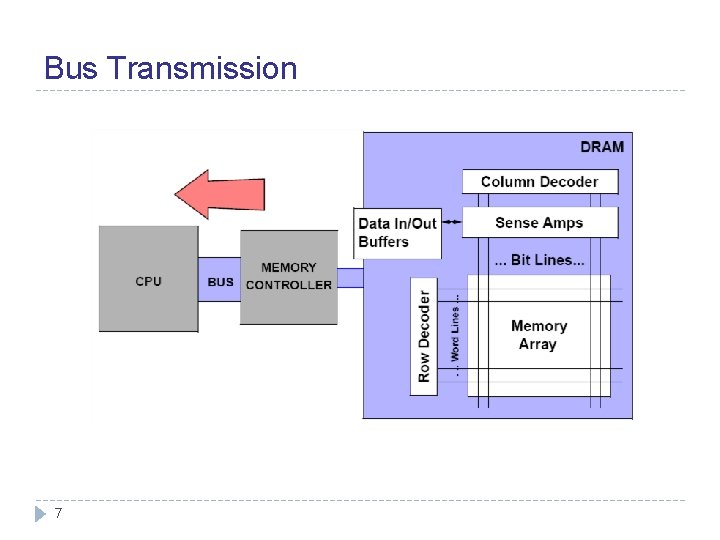

Bus Transmission 7

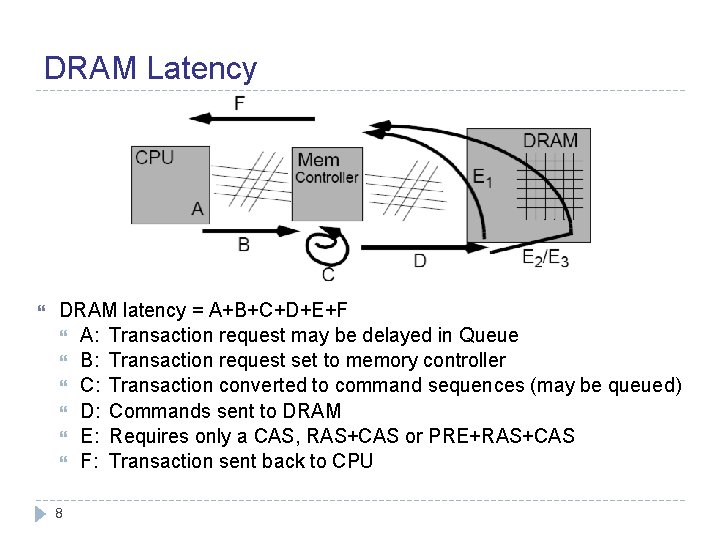

DRAM Latency DRAM latency = A+B+C+D+E+F A: Transaction request may be delayed in Queue B: Transaction request set to memory controller C: Transaction converted to command sequences (may be queued) D: Commands sent to DRAM E: Requires only a CAS, RAS+CAS or PRE+RAS+CAS F: Transaction sent back to CPU 8

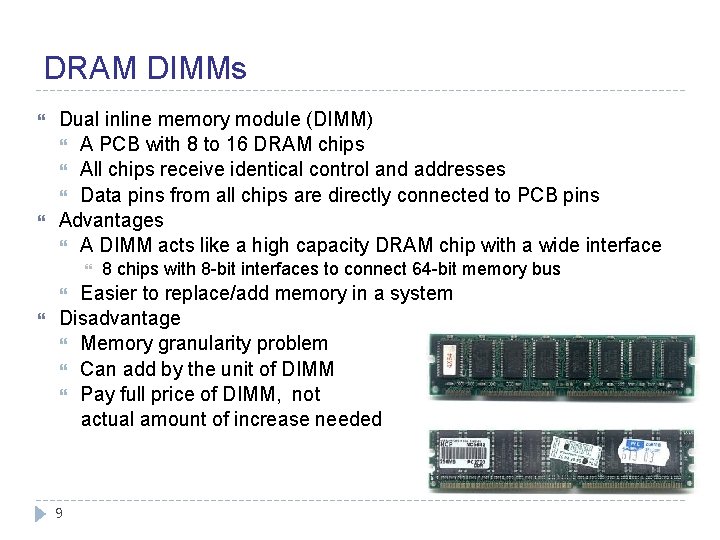

DRAM DIMMs Dual inline memory module (DIMM) A PCB with 8 to 16 DRAM chips All chips receive identical control and addresses Data pins from all chips are directly connected to PCB pins Advantages A DIMM acts like a high capacity DRAM chip with a wide interface Easier to replace/add memory in a system Disadvantage Memory granularity problem Can add by the unit of DIMM Pay full price of DIMM, not actual amount of increase needed 8 chips with 8 -bit interfaces to connect 64 -bit memory bus 9

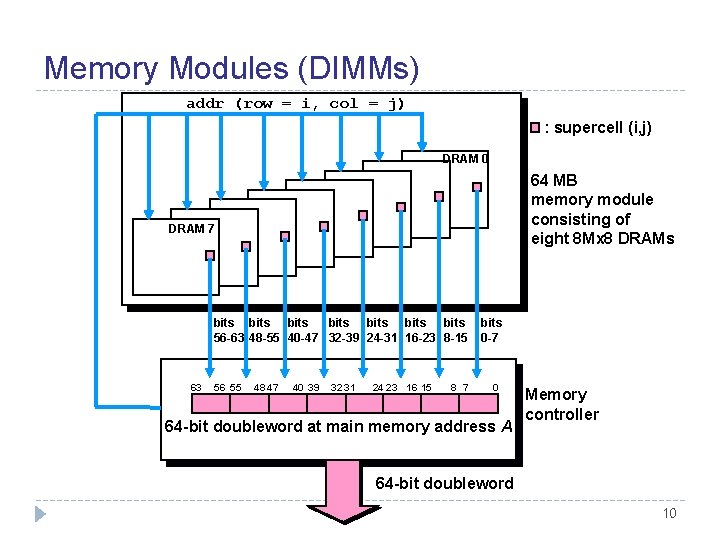

Memory Modules (DIMMs) addr (row = i, col = j) : supercell (i, j) DRAM 0 64 MB memory module consisting of eight 8 Mx 8 DRAMs DRAM 7 bits bits 56 -63 48 -55 40 -47 32 -39 24 -31 16 -23 8 -15 63 56 55 48 47 40 39 32 31 24 23 16 15 8 7 bits 0 -7 0 64 -bit doubleword at main memory address A Memory controller 64 -bit doubleword 10

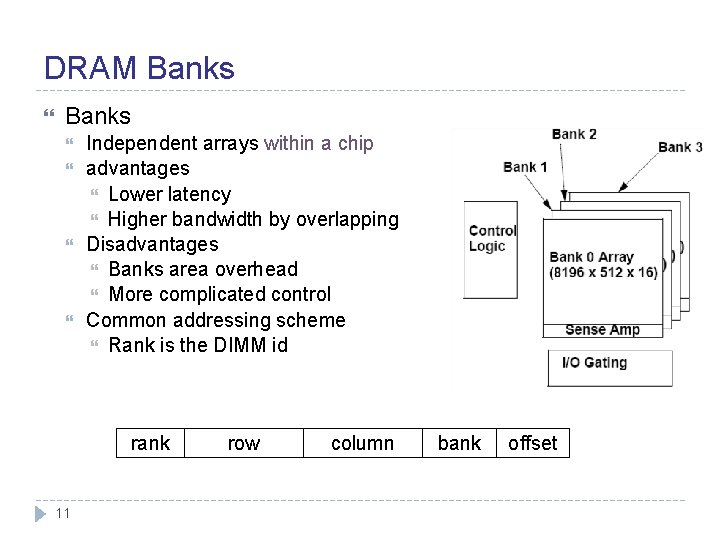

DRAM Banks Independent arrays within a chip advantages Lower latency Higher bandwidth by overlapping Disadvantages Banks area overhead More complicated control Common addressing scheme Rank is the DIMM id rank 11 row column bank offset

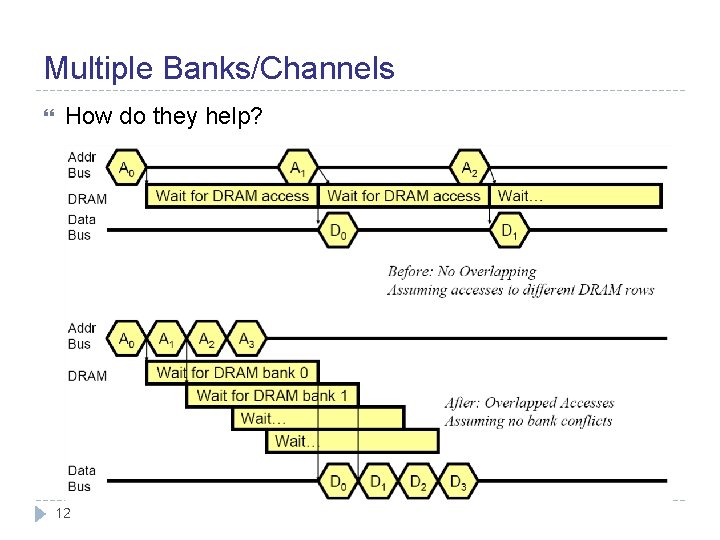

Multiple Banks/Channels How do they help? 12

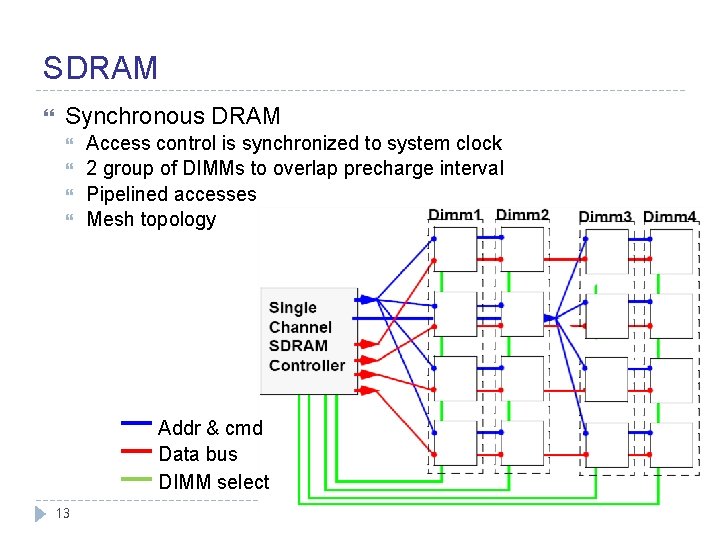

SDRAM Synchronous DRAM Access control is synchronized to system clock 2 group of DIMMs to overlap precharge interval Pipelined accesses Mesh topology Addr & cmd Data bus DIMM select 13

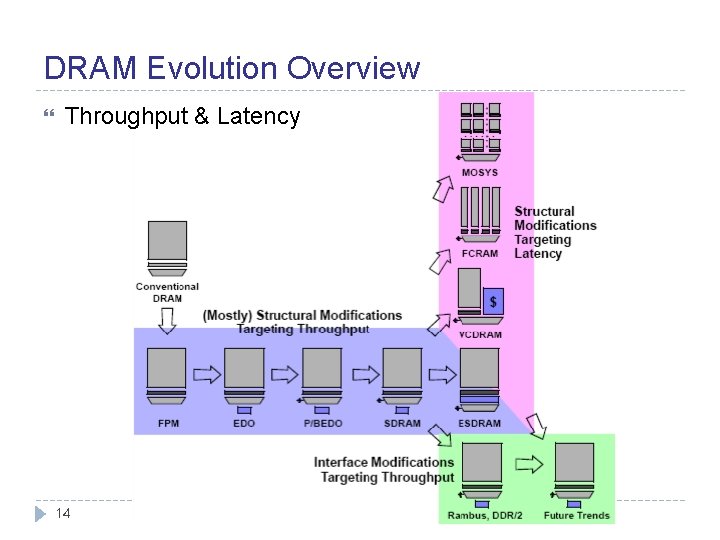

DRAM Evolution Overview Throughput & Latency 14

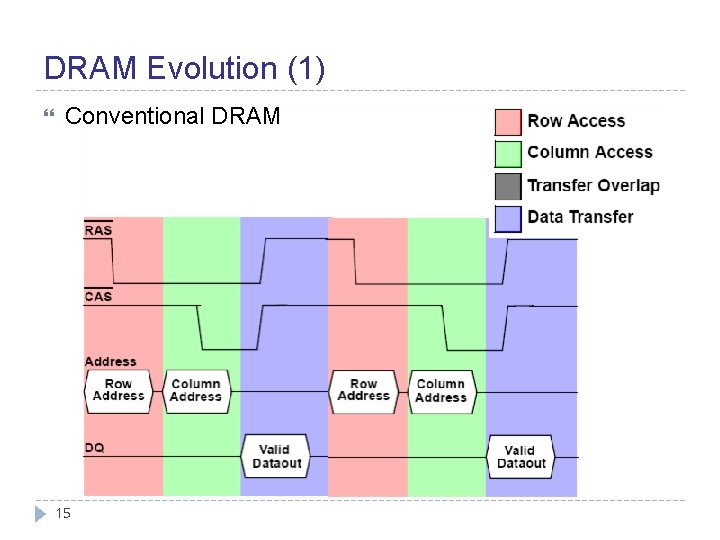

DRAM Evolution (1) Conventional DRAM 15

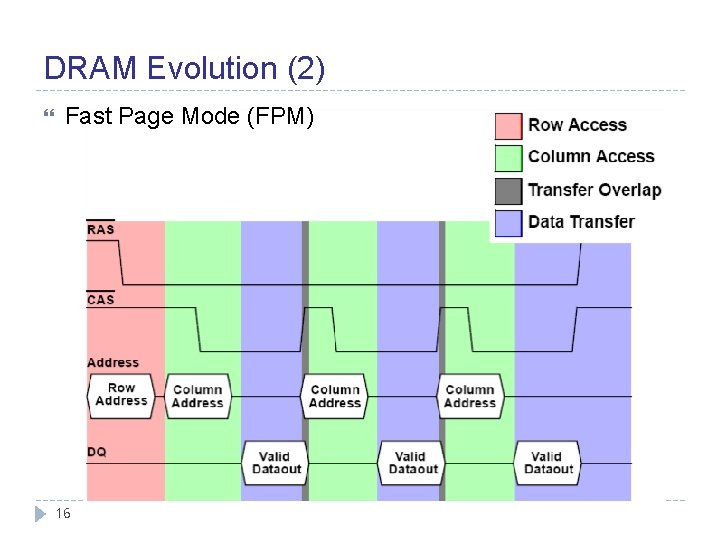

DRAM Evolution (2) Fast Page Mode (FPM) 16

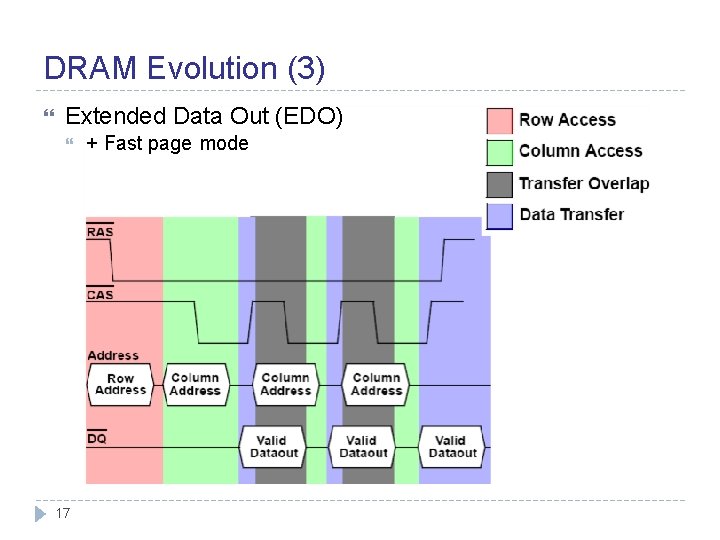

DRAM Evolution (3) Extended Data Out (EDO) 17 + Fast page mode

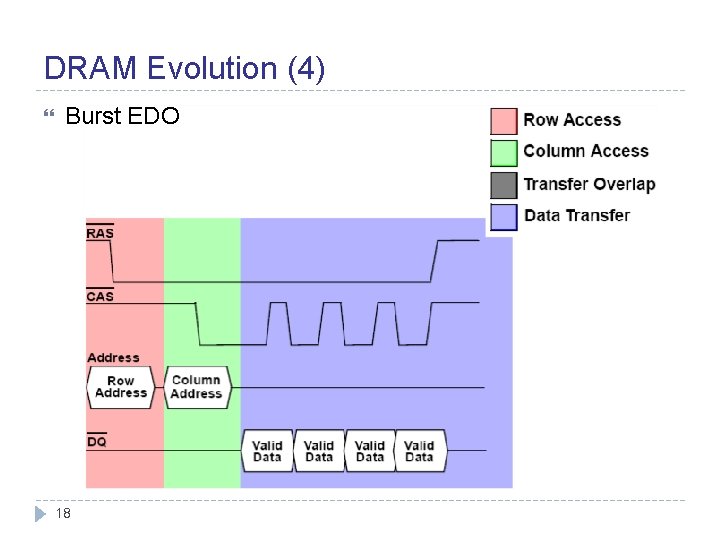

DRAM Evolution (4) Burst EDO 18

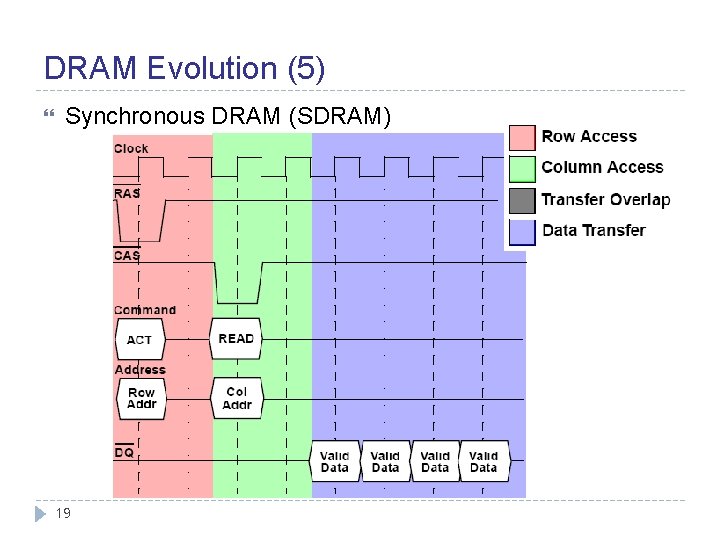

DRAM Evolution (5) Synchronous DRAM (SDRAM) 19

SDRAM Evolution ESDRAM DDR SDRAM Double data rate using both clock edges (double pumping) DDR 2 SDRAM with a row cache Allows starting next RAS to the same bank in parallel with current CAS Higher frequency FSB than DDR 100/133/166/200 MHz vs. 200/266/333/400 MHz Upto 3. 2 GB/s (PC-3200) vs. 6. 4 GB/s (PC 2 -6400) – 64 bit FSB Lower voltage DDR : 1. 8 v vs. 2. 5 v More banks (to operate at higher frequency than DDR) longer CAS delay (wider prefetch buffer than DDR, 4 -bit vs 2 -bit) DDR 3 20 400/533/667/800 Mhz FSB, 1. 5 v, 8 -bit prefetch buffer

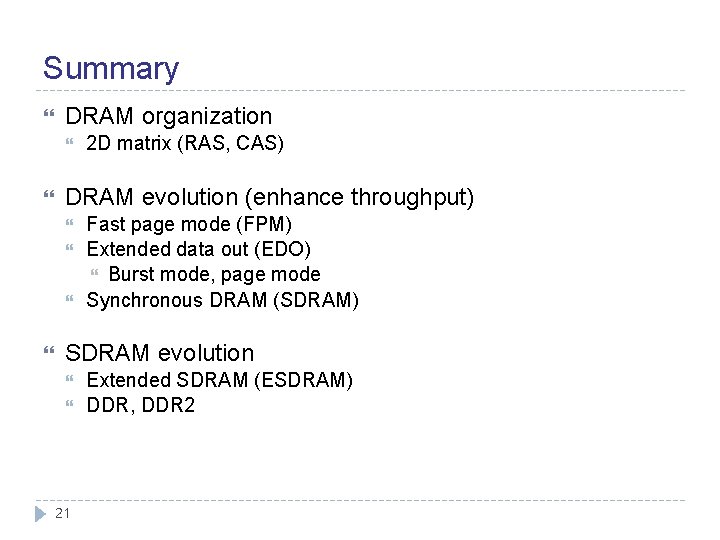

Summary DRAM organization DRAM evolution (enhance throughput) 2 D matrix (RAS, CAS) Fast page mode (FPM) Extended data out (EDO) Burst mode, page mode Synchronous DRAM (SDRAM) SDRAM evolution 21 Extended SDRAM (ESDRAM) DDR, DDR 2

- Slides: 21