CF Interface SRAM Tester Cyber Formosa link all

CF Interface SRAM Tester Cyber Formosa -link all together-

Worker Ownership • Chin-Hua Tsai CEO & Tester Programmer B 95902064 蔡青樺 • Ming-Hen Tsai COO& Interface Programmer B 95902028 蔡明亨 • Chia-Hua Ho CTO & Interface Programmer B 95902082 何家華 • Sang-Chang Hong CIO & Tester Programmer & Speakperson B 95902004 洪三權

WEB SITE • http: //peanuts. csie. ntu. edu. tw/~scan 33/ study/dsd/final/

Outline • Introduction • Why SRAM Tester? Market? Promising Future? • Technical Difficulty? • Technique • What is cf interface? • How to detect errors?

Outline • Introduction • Why SRAM Tester? Market? Promising Future? • Technical Difficulty? • Technique • What is cf interface? • How to detect errors?

What is SRAM Tester?

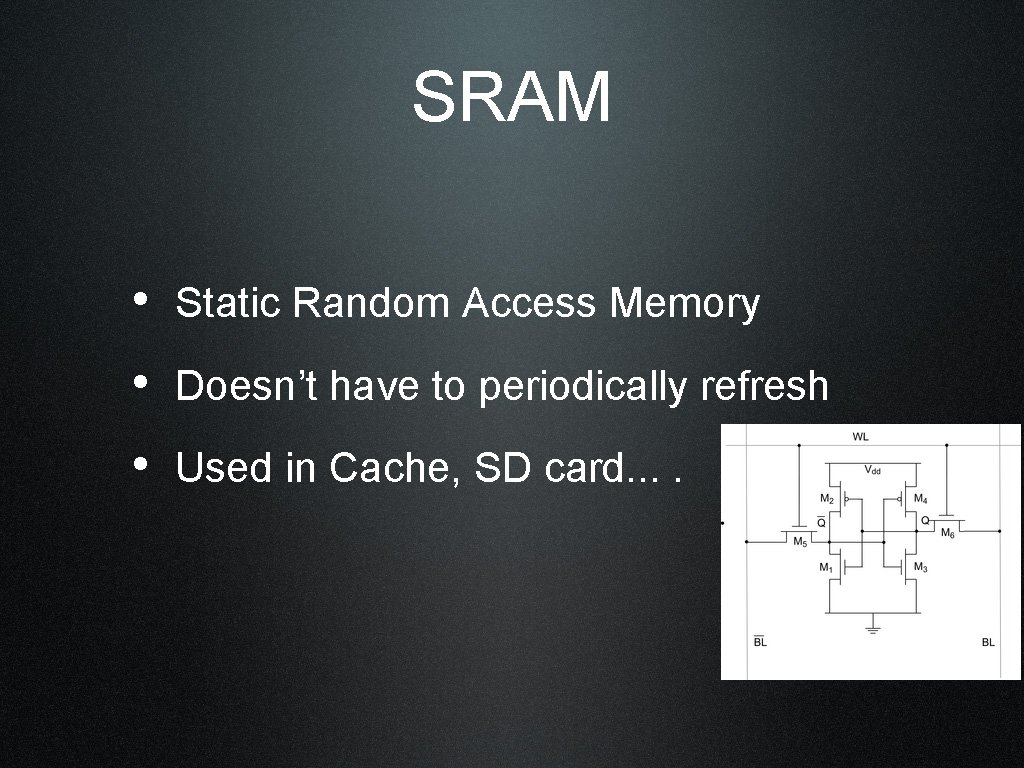

SRAM • Static Random Access Memory • Doesn’t have to periodically refresh • Used in Cache, SD card. .

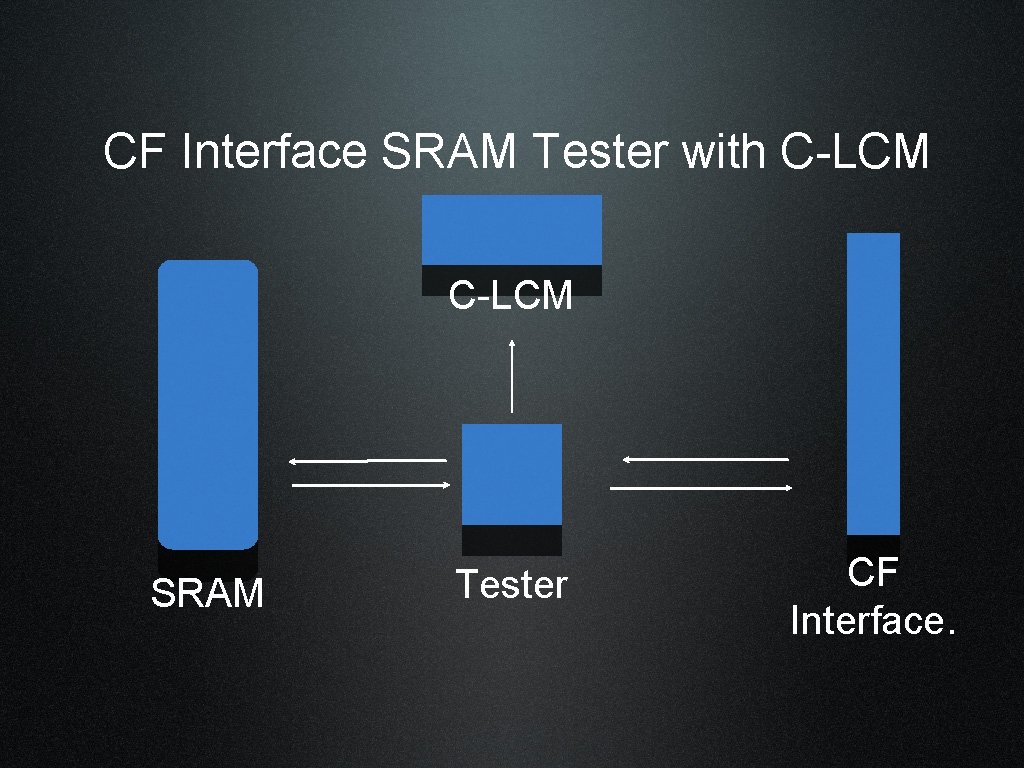

CF Interface SRAM Tester with C-LCM SRAM Tester CF Interface.

Multiple Applications Market • i-Ntelligent • Dram Tester

i-Ntelligent • Phone self-Repair • Test and Repair only one click!

i-Ntelligent • S: Useful, Safer. For Business! • W: Undeveloped User Pattern • O: A new World! Blue Ocean! • T: Need more capital.

DRAM Tester • Tester for DRAM

DRAM Tester • S: 力晶、茂德、南科、華邦 -> 20% Market Share Rate DRAM need newest Tech ! • W: DRAM Winter. . . • O: 12/16經濟部紓困方案 Windows 7 • T: Big Monster: Sam. Sung

Outline • Introduction • Why SRAM Tester? Market? Promising Future? • Technical Difficulty? • Technique • What is cf interface? • How to detect errors?

• 1981 年,微軟創辦人比爾.蓋茲(Bill Gates):「個人電腦記憶體需求將不會 超過 640 KB 」(Nobody would ever need more than 640 KB of memory on theirpersonal computer)

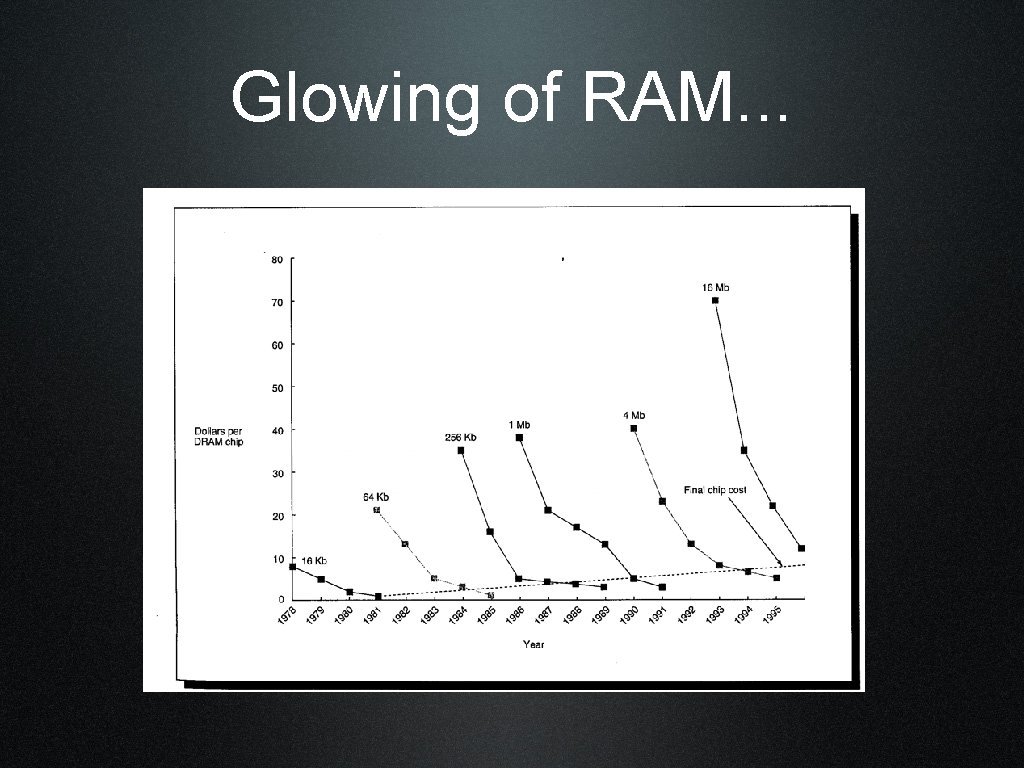

Diffculty of Testing • Ram become bigger and bigger EXPONENTIALLY! • Ram Fault become more complex • However, required testing time is same. . .

Memory Importance

Glowing of RAM. . .

Terrible Time Complexity 冏 From 商湯 to 21 th centry. . .

Outline • Introduction • Why SRAM Tester? Market? Promising Future? • Technical Difficulty? • Technique • What is cf interface? • How to detect errors?

What is CF Interface? • What is CF? • How does CF work? • How to use it? • What have we done?

What is CF Interface? • What is CF? • How does CF work? • How to use it? • What have we done?

Introduction (by SPEC): • CF/CF+ cards • Vendor-independent specification • CF Storage Cards provided the capability to easily transfer all types of digital information and software between a large variety of digital systems.

What is CF Interface? • What is CF? • How does CF work? • How to use it? • What have we done?

SPEC focus • Card Physical • Electrical Interface • Metaformat(Information structure) • Software Interface • Compact. Flash Adapters

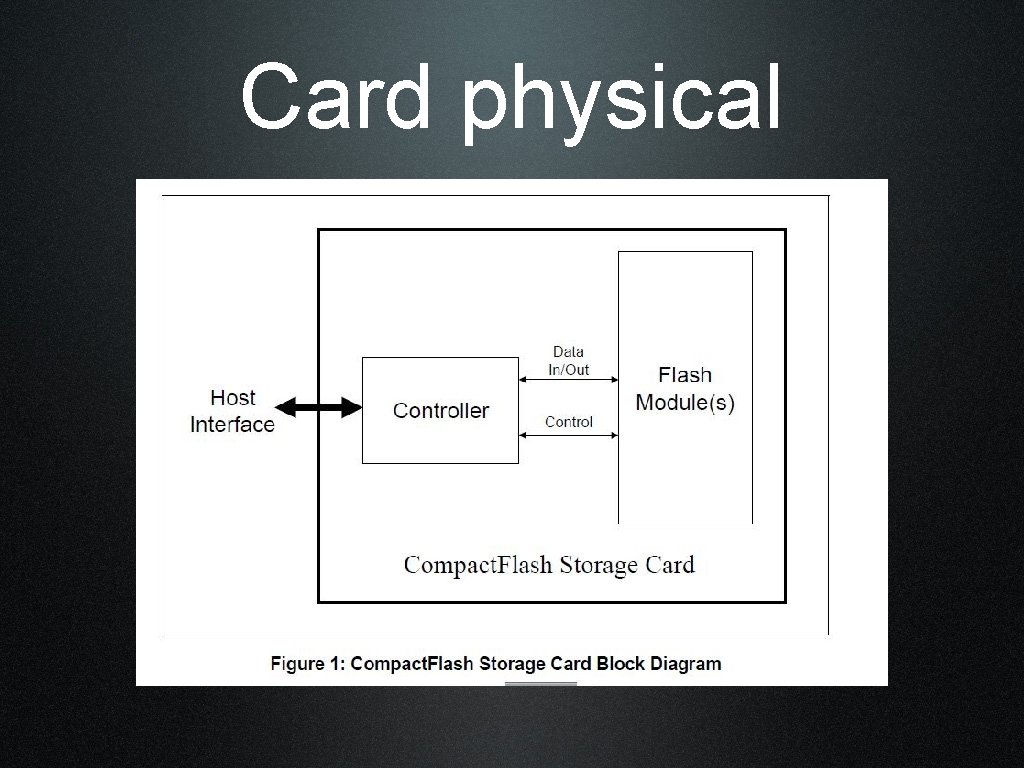

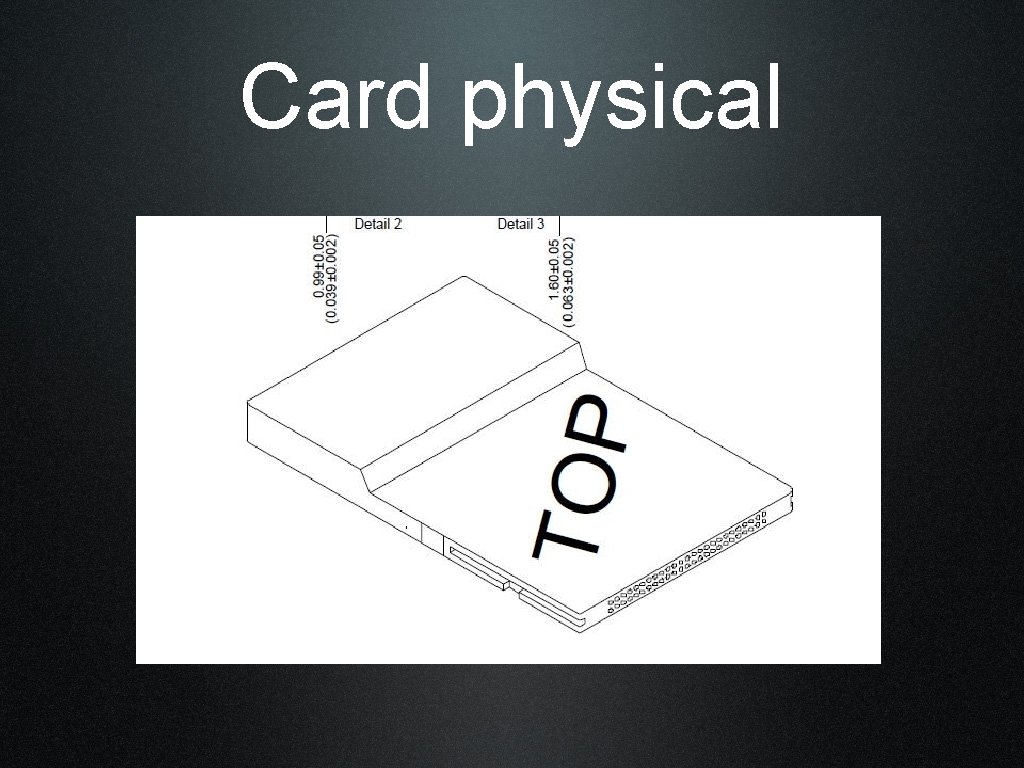

Card physical

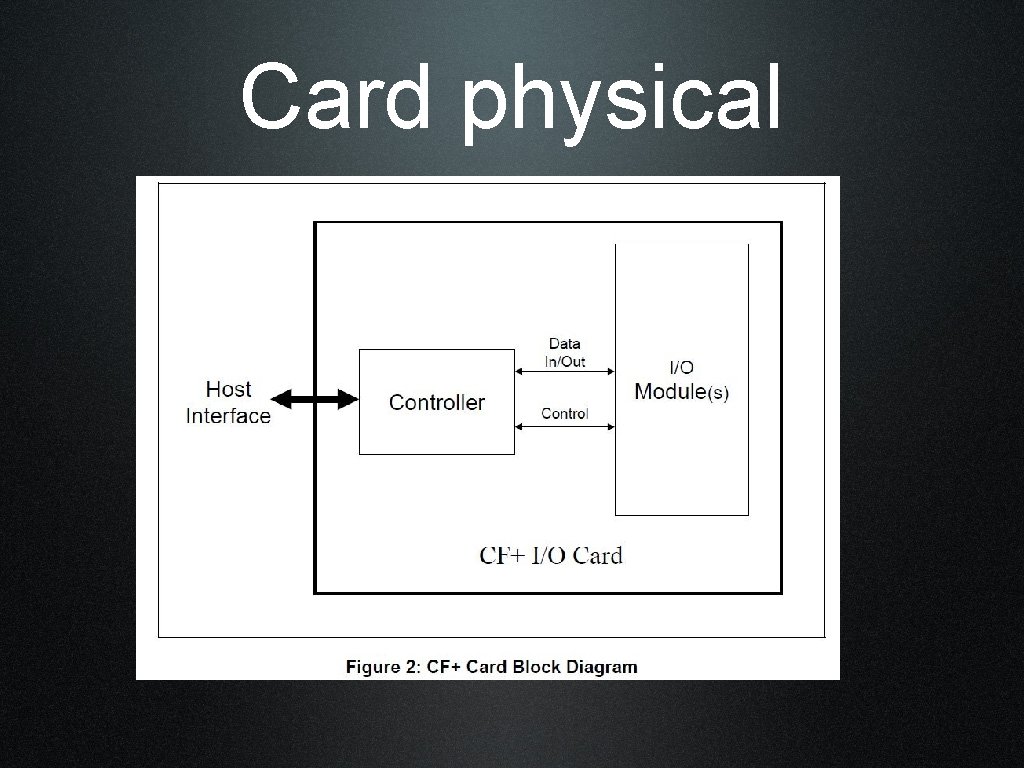

Card physical

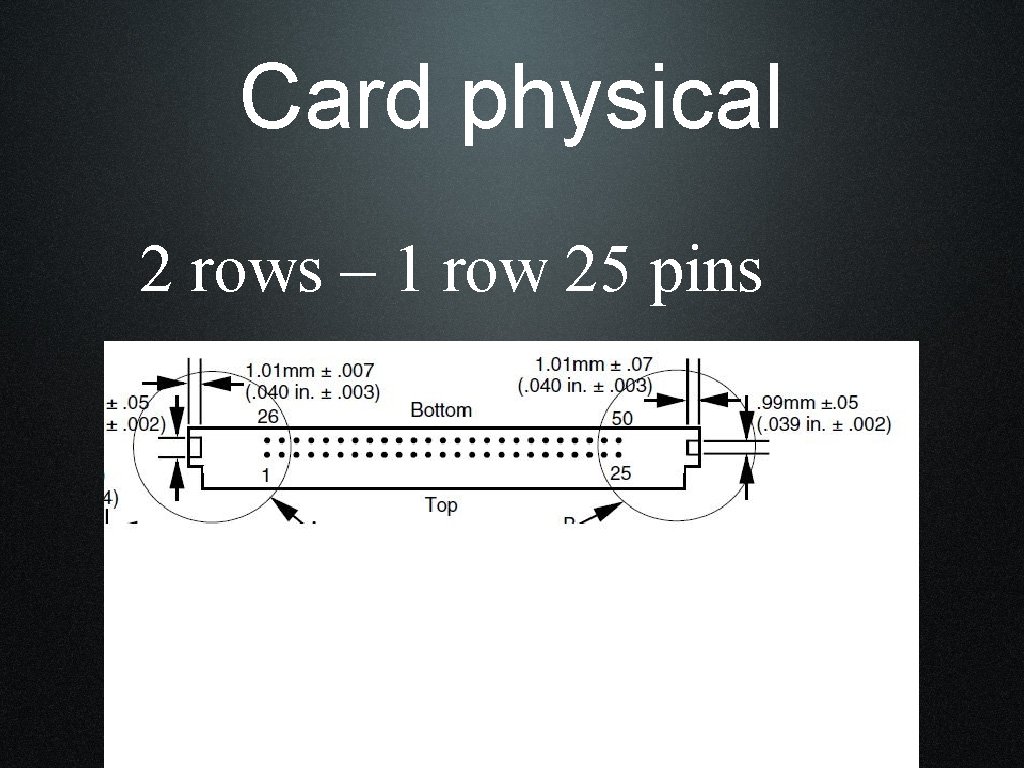

Card physical 2 rows – 1 row 25 pins

Card physical

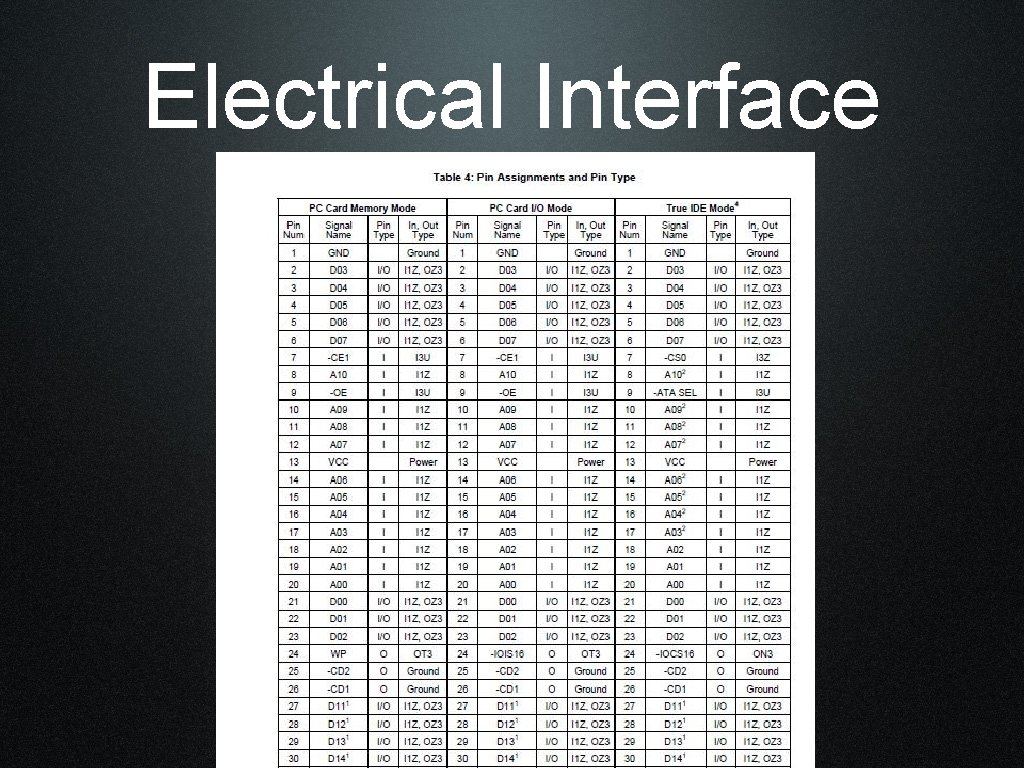

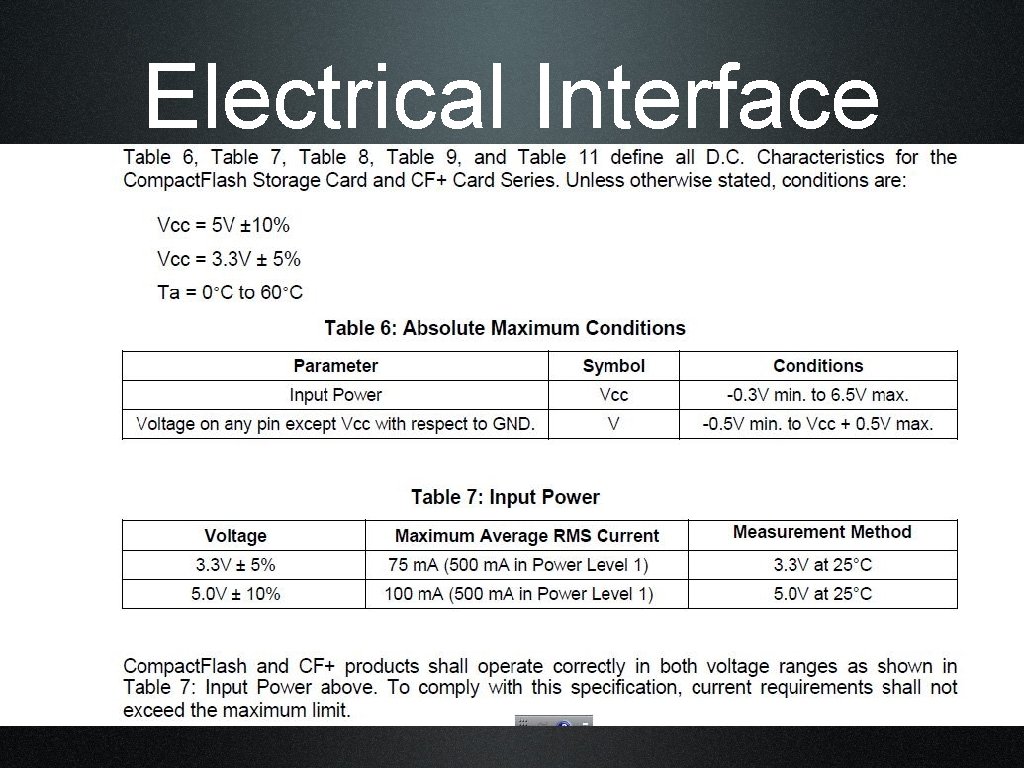

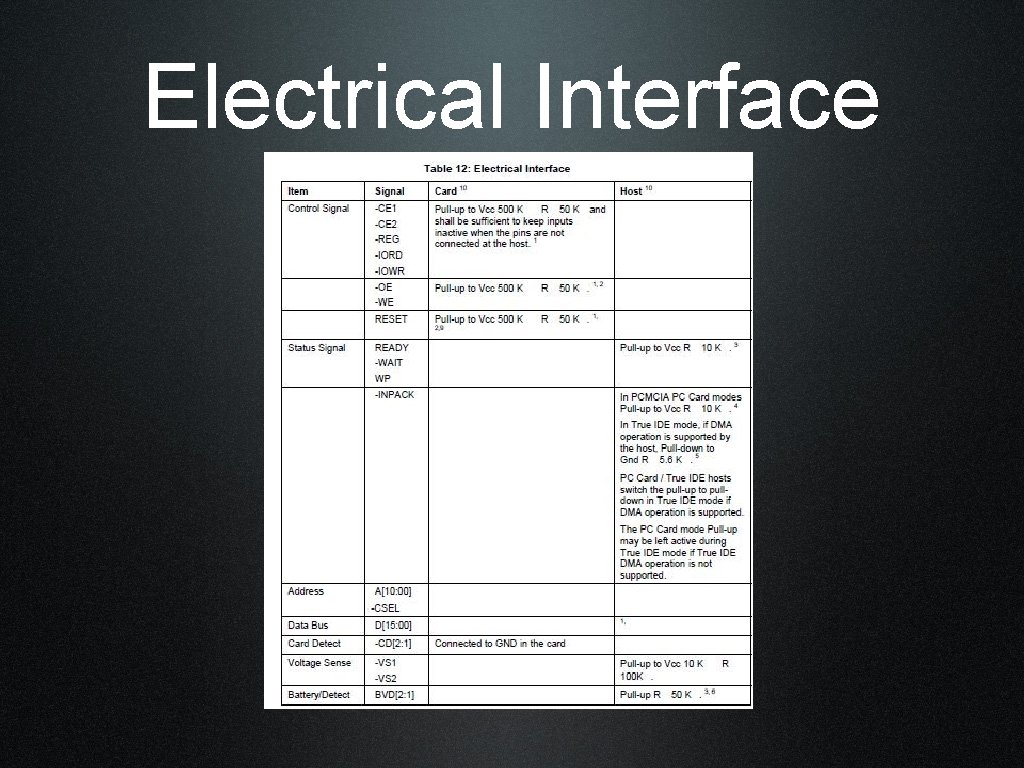

Electrical Interface

Electrical Interface

Electrical Interface

Software Interface • The standard PC-AT disk I/O address spaces 1 F 0 h-1 F 7 h, 3 F 6 h-3 F 7 h (primary) or 170 h-177 h, 376 h-377 h (secondary) with IRQ 14 (or other available IRQ). • Any system decoded 16 byte I/O block using any available IRQ. • Memory space.

Software Interface • Upon receipt of a Class 1 command, the Compact. Flash Storage Card sets BSY within 400 nsec. • Upon receipt of a Class 2 command, the Compact. Flash Storage Card sets BSY within 400 nsec, sets up the sector buffer for a write operation, sets DRQ within 700 μsec, and clears BSY within 400 nsec of setting DRQ. • Upon receipt of a Class 3 command, the Compact. Flash Storage Card sets BSY within 400 nsec, sets up the sector buffer for a write operation, sets DRQ within 20 msec (assuming no re-assignments), and clears BSY within 400 nsec of setting DRQ.

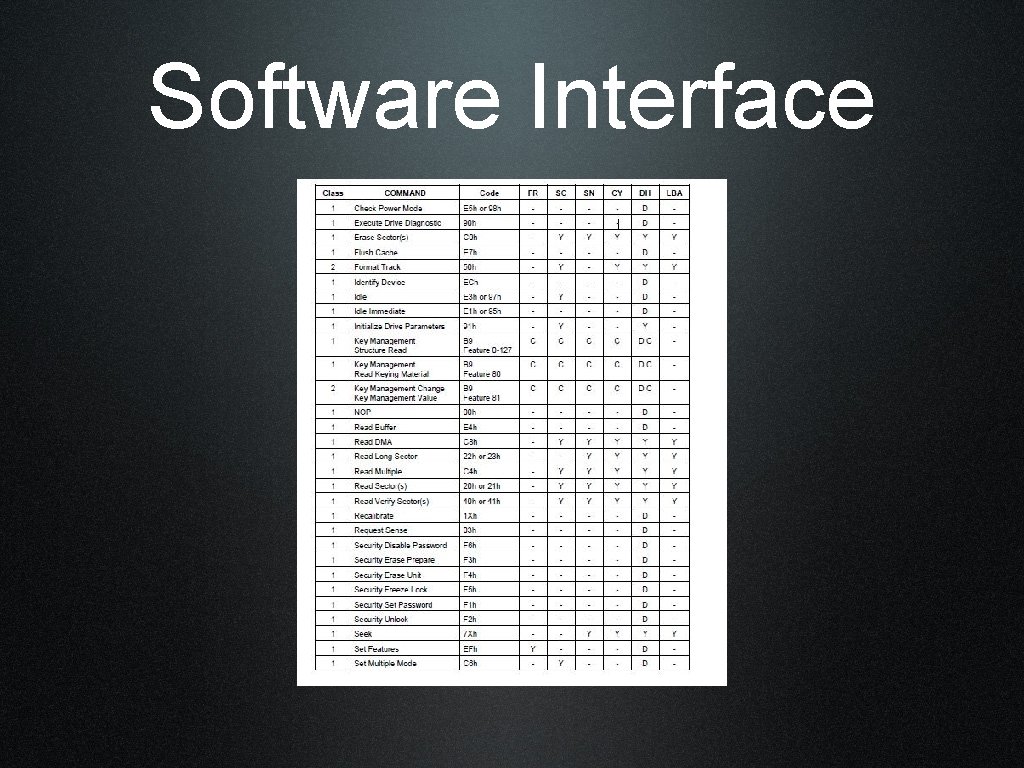

Software Interface

What is CF Interface? • What is CF? • How does CF work? • How to use it? • What have we done?

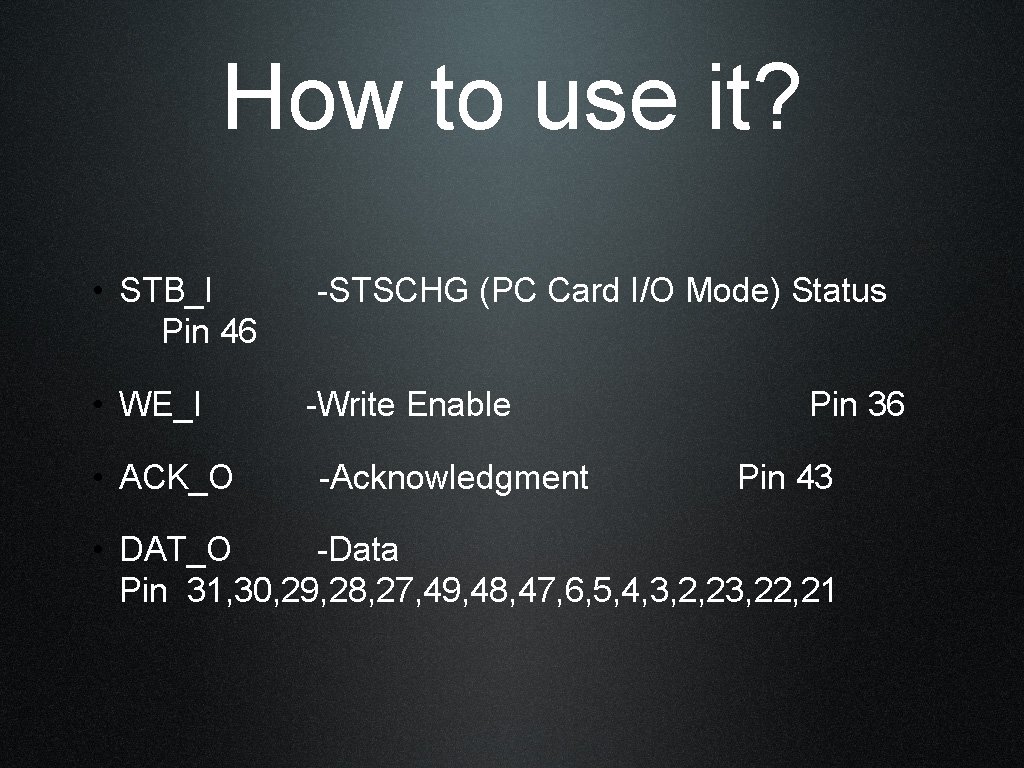

How to use it? • STB_I -STSCHG (PC Card I/O Mode) Status Pin 46 • WE_I -Write Enable • ACK_O -Acknowledgment Pin 36 Pin 43 • DAT_O -Data Pin 31, 30, 29, 28, 27, 49, 48, 47, 6, 5, 4, 3, 2, 23, 22, 21

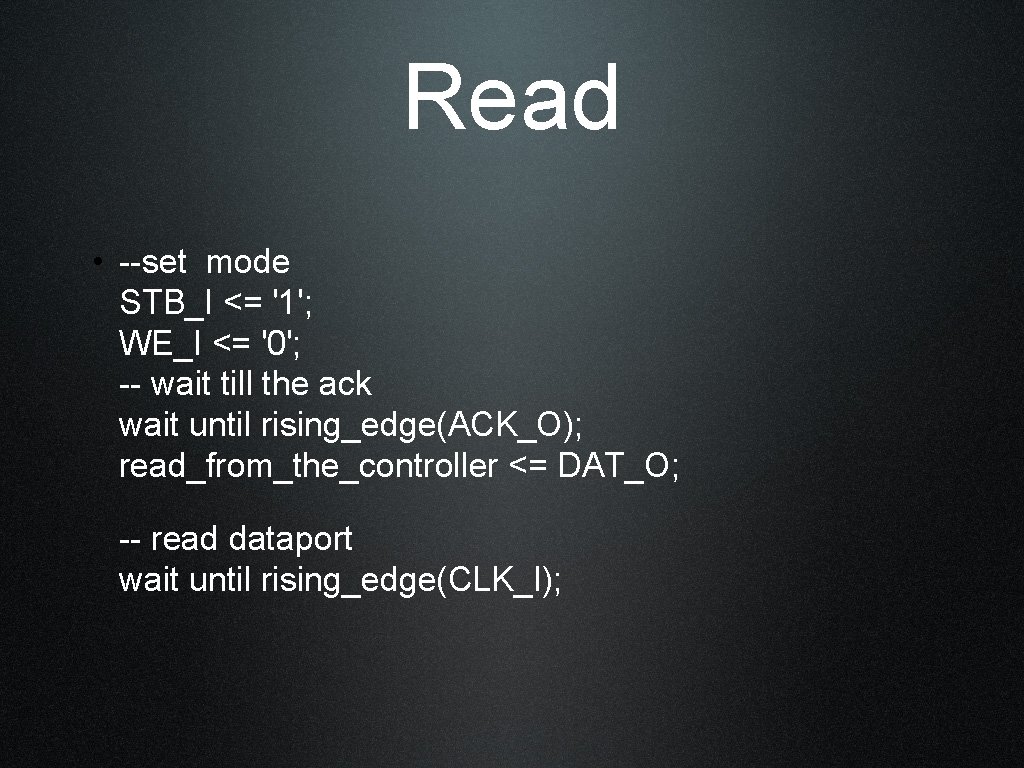

Read • --set mode STB_I <= '1'; WE_I <= '0'; -- wait till the ack wait until rising_edge(ACK_O); read_from_the_controller <= DAT_O; -- read dataport wait until rising_edge(CLK_I);

Write • STB_I <= '1'; WE_I <= '1'; --set mode DAT_O <= data_to_controller; --set data wait until rising_edge(ACK_O); -- operate synchronously wait until rising_edge(CLK_I);

What is CF Interface? • What is CF? • How does CF work? • How to use it? • What have we done?

Outline • Introduction • Why SRAM Tester? Market? Promising Future? • Technical Difficulty? • Technique • What is cf interface? • How to detect errors?

How to detect Errors? • Detection : All subtypes and All positions of subtype • Category of Faults • Detection Algorithm

What kinds of Errors? • AF ( Address Fault ) • SAF ( Stuck-at Fault ) • TF ( Transition Fault ) • SOp. F( Stuck-Open Fault ) • CF ( Coupling Faults ) • DRF( Data Retention Fault )

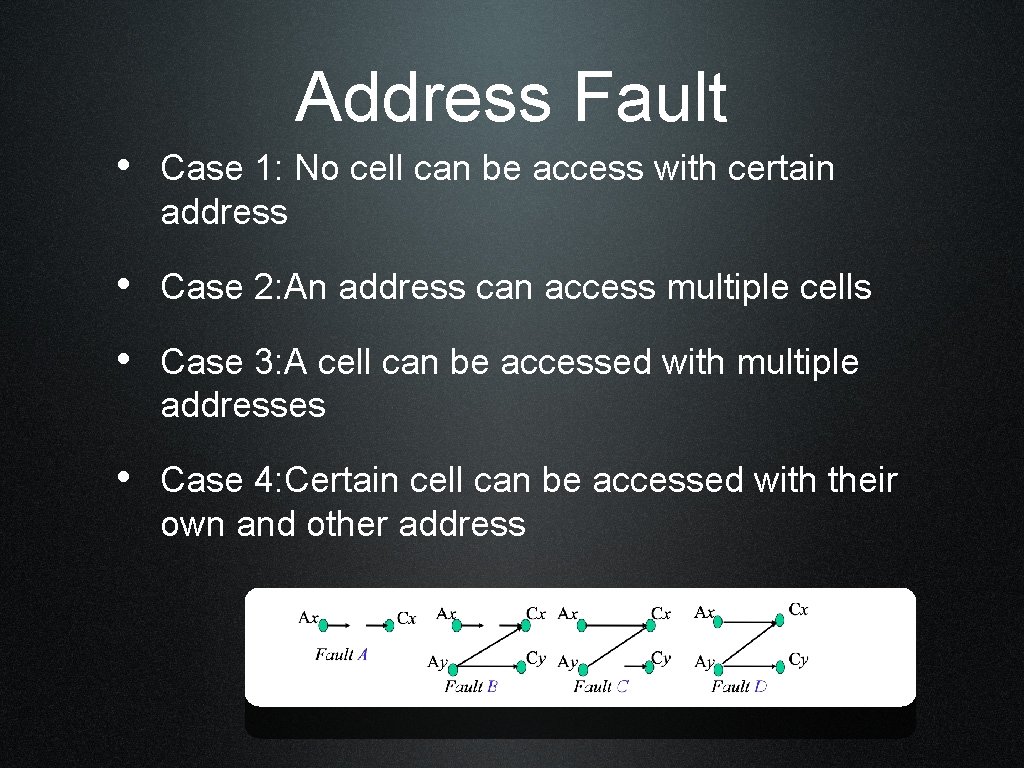

Address Fault • Case 1: No cell can be access with certain address • Case 2: An address can access multiple cells • Case 3: A cell can be accessed with multiple addresses • Case 4: Certain cell can be accessed with their own and other address

Stuck-at Fault

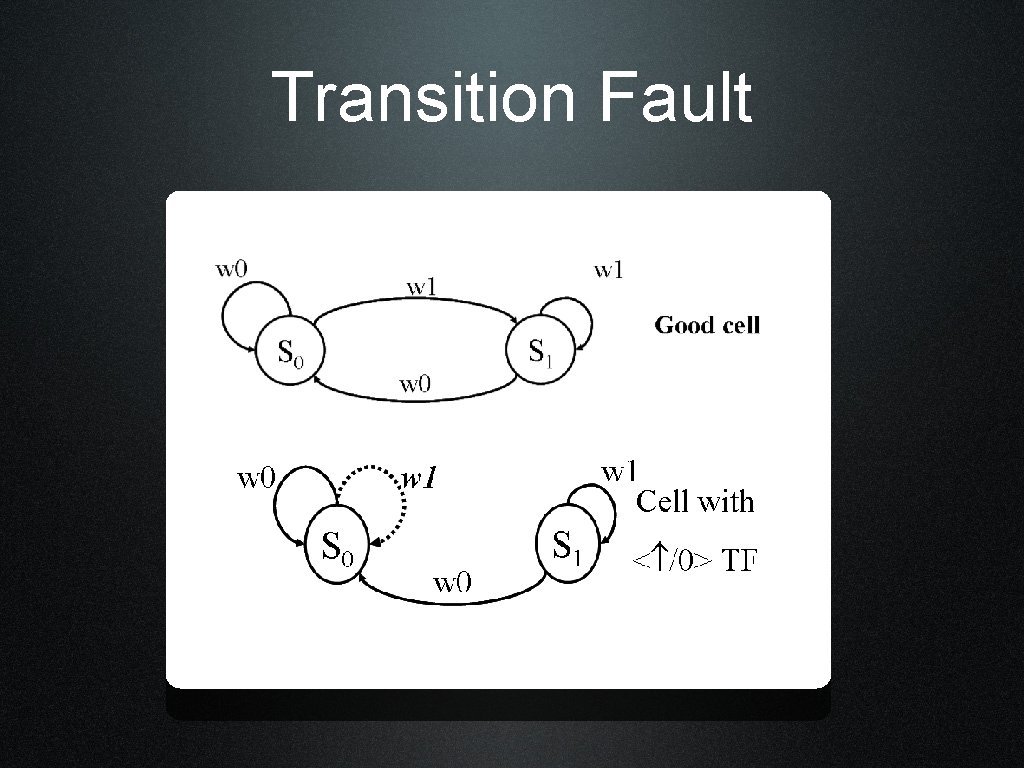

Transition Fault

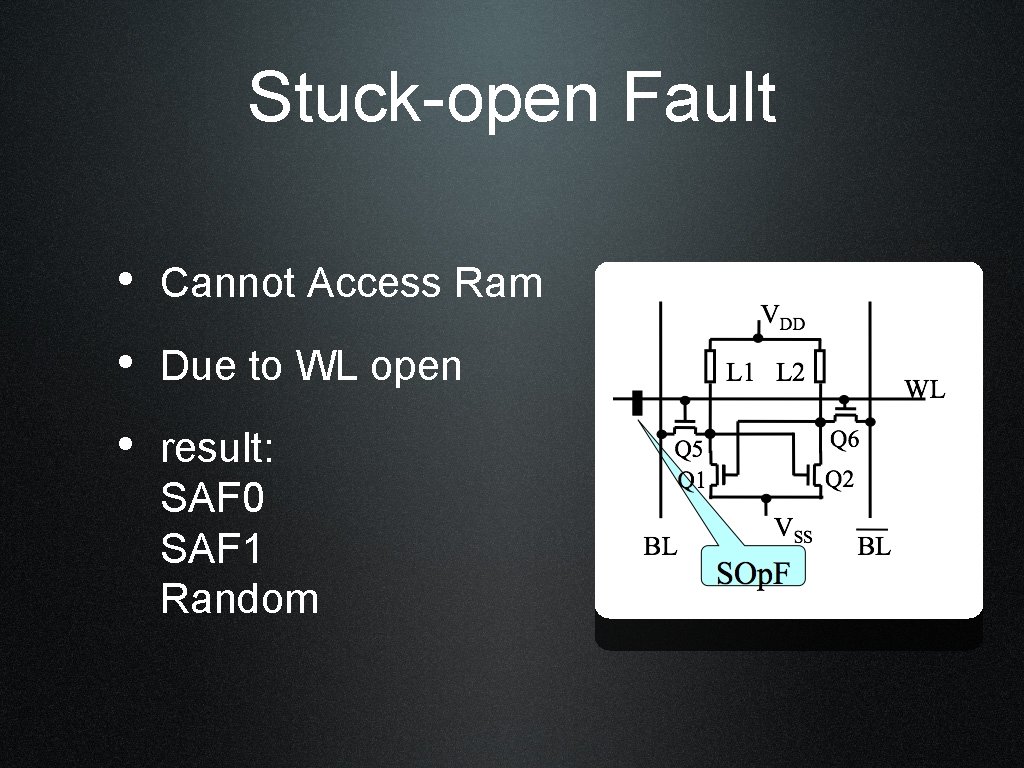

Stuck-open Fault • Cannot Access Ram • Due to WL open • result: SAF 0 SAF 1 Random

Coupling Fault • 當a-cell改變,V-cell就很衰的跟著變 • CFid e. g. <↑; 1> • CFst e. g. <0; 1> • CFin e. g. <0; x> (DRAM)

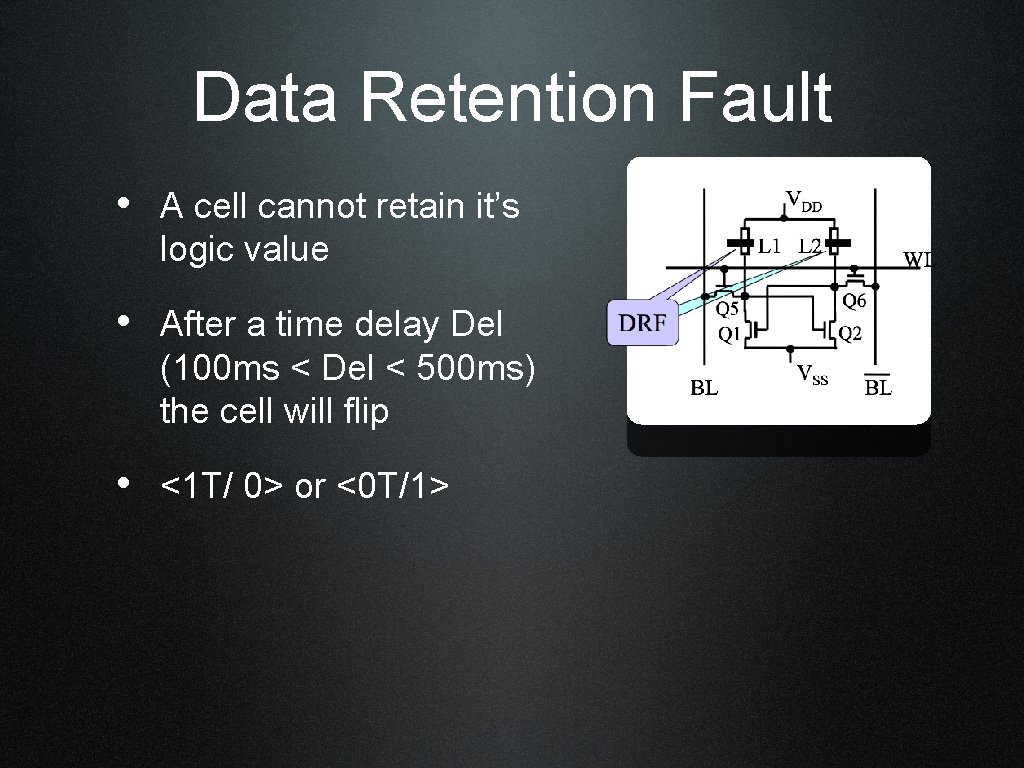

Data Retention Fault • A cell cannot retain it’s logic value • After a time delay Del (100 ms < Del < 500 ms) the cell will flip • <1 T/ 0> or <0 T/1>

Detection Algorithm • Scan ( Zero-One ) • Checker. Board • GALPAT • Walking 1/0 • March • Pseudo-Random Test

Scan( Zero-One ) Algorithm: Step 1: write 0 in all cells. Step 2: read all cells. Step 3: w Time Complexity: O(n)

Scan( Zero-One ) • Not all AFs will be detected • SAFs will be detected when it can be guaranteed that the address decoder is correct • Not all TFs are detected • Not all CFs will be detected

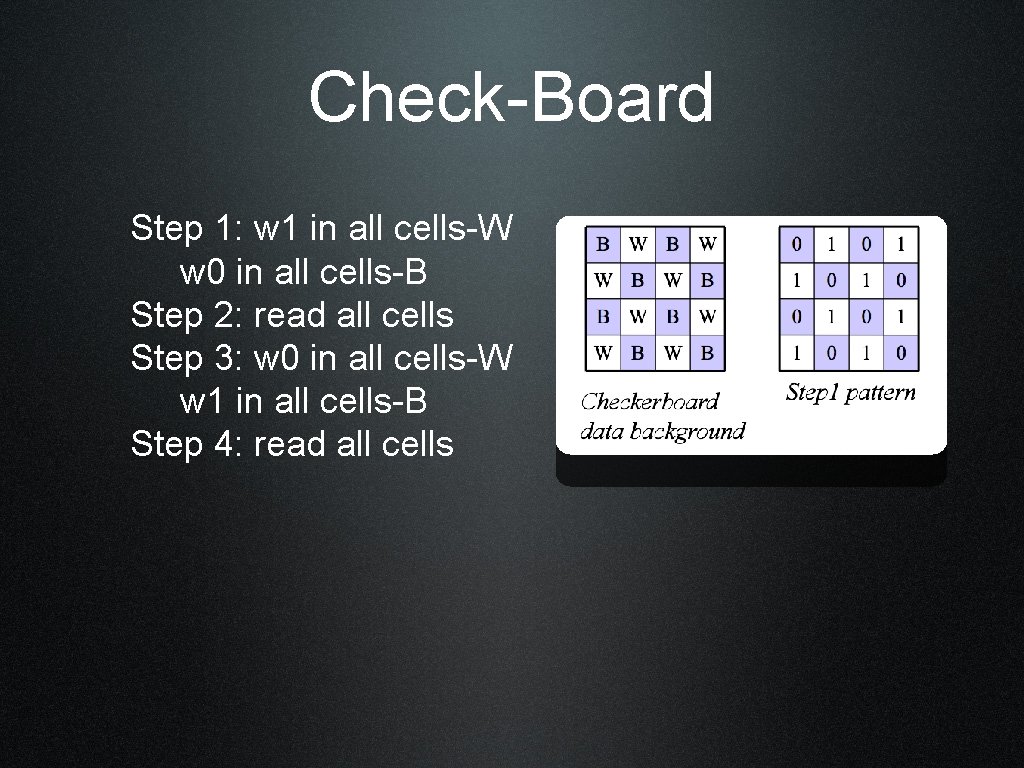

Check-Board Step 1: w 1 in all cells-W w 0 in all cells-B Step 2: read all cells Step 3: w 0 in all cells-W w 1 in all cells-B Step 4: read all cells

Check-Board • Not all AFs will be detected • SAFs will be detected when it can be guaranteed that the address decoder is correct • Not all TFs are detected • Not all CFs will be detected

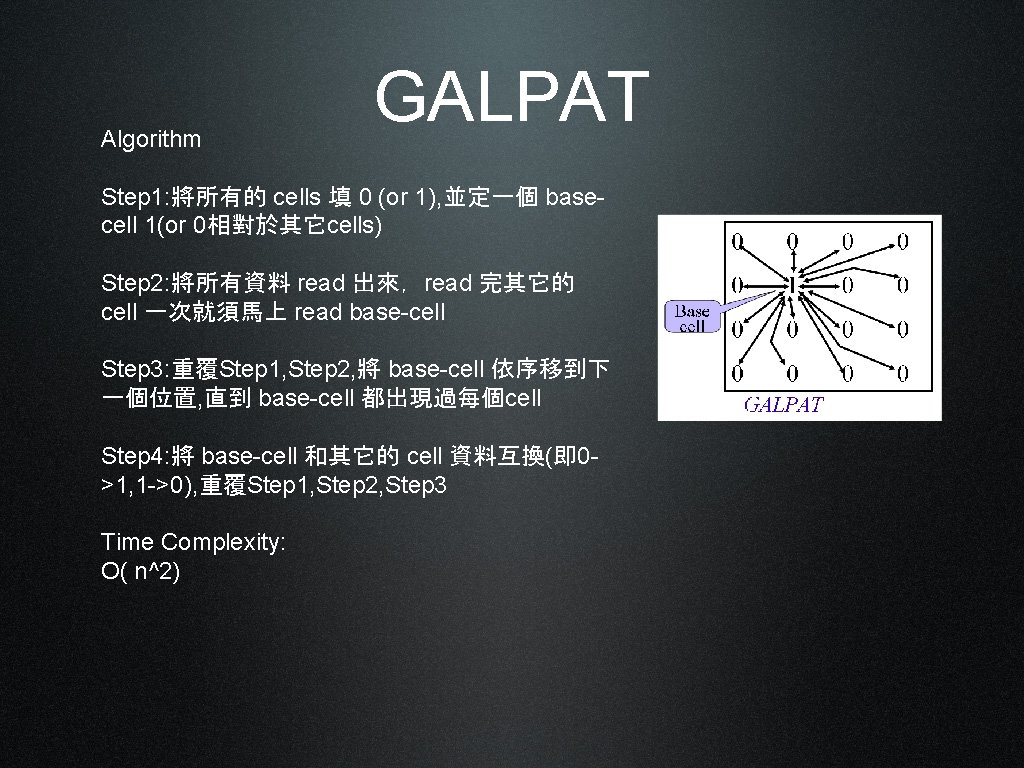

Algorithm GALPAT Step 1: 將所有的 cells 填 0 (or 1), 並定一個 basecell 1(or 0相對於其它cells) Step 2: 將所有資料 read 出來,read 完其它的 cell 一次就須馬上 read base-cell Step 3: 重覆Step 1, Step 2, 將 base-cell 依序移到下 一個位置, 直到 base-cell 都出現過每個cell Step 4: 將 base-cell 和其它的 cell 資料互換(即 0>1, 1 ->0), 重覆Step 1, Step 2, Step 3 Time Complexity: O( n^2)

GALPAT • All AFs are detected and located • All SAFs will be located • All TFs are located • All CFs are located

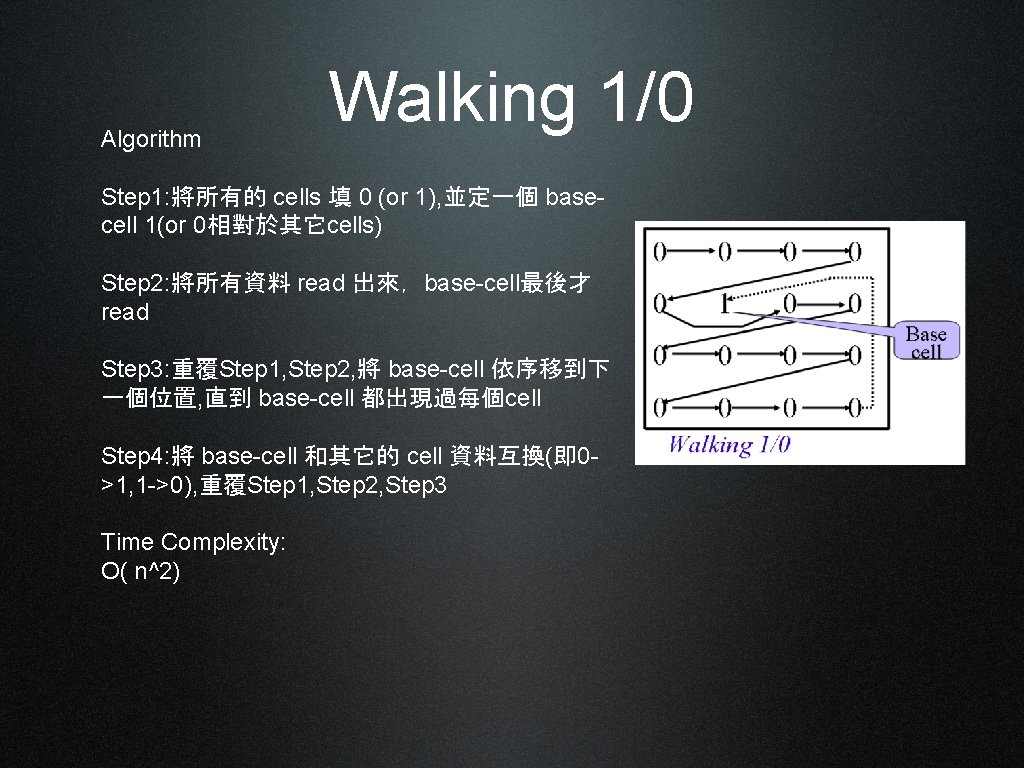

Algorithm Walking 1/0 Step 1: 將所有的 cells 填 0 (or 1), 並定一個 basecell 1(or 0相對於其它cells) Step 2: 將所有資料 read 出來,base-cell最後才 read Step 3: 重覆Step 1, Step 2, 將 base-cell 依序移到下 一個位置, 直到 base-cell 都出現過每個cell Step 4: 將 base-cell 和其它的 cell 資料互換(即 0>1, 1 ->0), 重覆Step 1, Step 2, Step 3 Time Complexity: O( n^2)

Walking 1/0 • All AFs are detected and located • All SAFs will be located • All TFs are located • All CFs are located

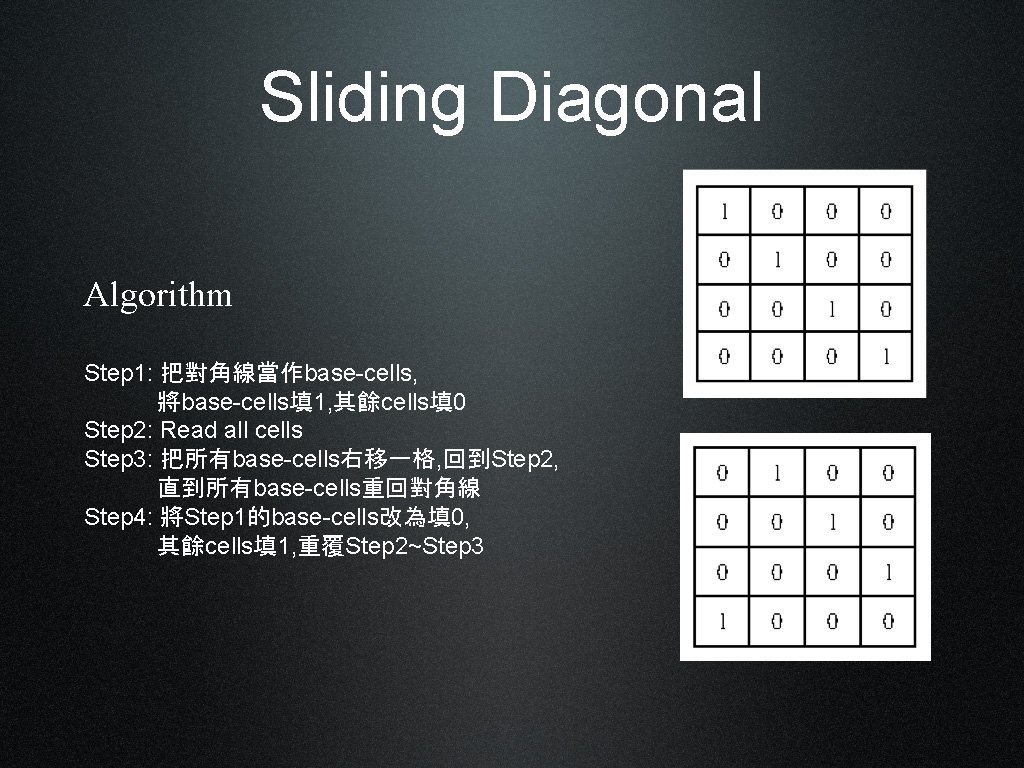

Sliding Diagonal Algorithm Step 1: 把對角線當作base-cells, 將base-cells填 1, 其餘cells填 0 Step 2: Read all cells Step 3: 把所有base-cells右移一格, 回到Step 2, 直到所有base-cells重回對角線 Step 4: 將Step 1的base-cells改為填 0, 其餘cells填 1, 重覆Step 2~Step 3

Sliding Diagonal • Time complexity = O(n 1. 5) • Not all AFs will be detected • All SAFs are detected and located • All TFs are detected and located • Not all CFs will be detected

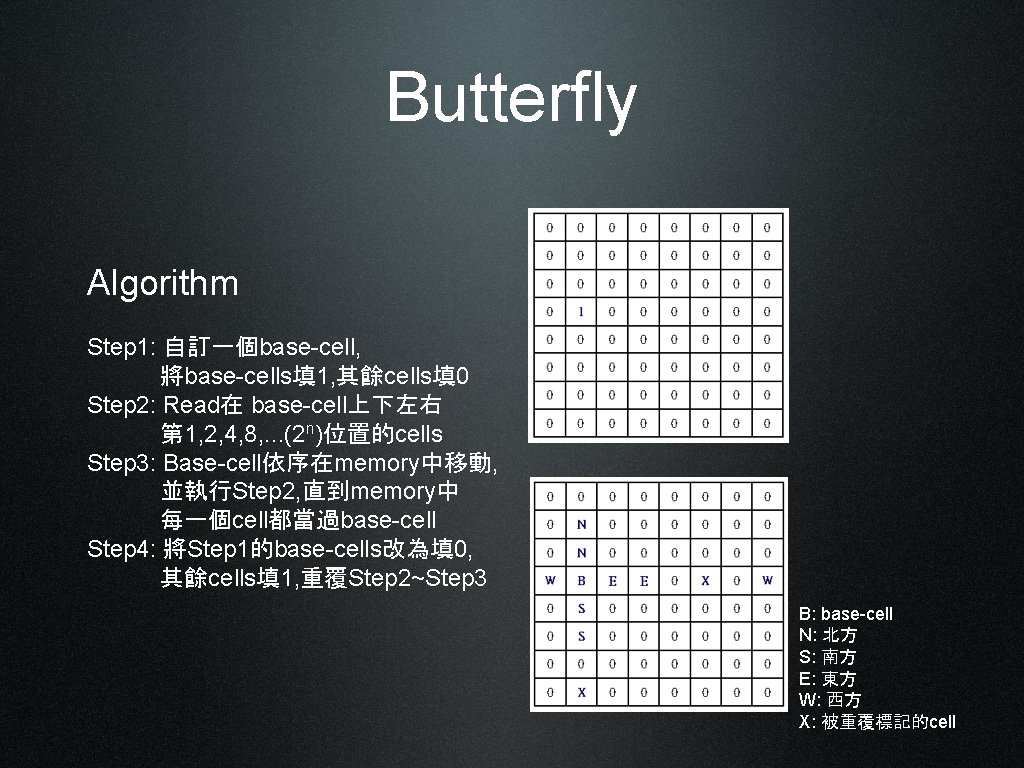

Butterfly Algorithm Step 1: 自訂一個base-cell, 將base-cells填 1, 其餘cells填 0 Step 2: Read在 base-cell上下左右 第 1, 2, 4, 8, . . . (2 n)位置的cells Step 3: Base-cell依序在memory中移動, 並執行Step 2, 直到memory中 每一個cell都當過base-cell Step 4: 將Step 1的base-cells改為填 0, 其餘cells填 1, 重覆Step 2~Step 3 B: base-cell N: 北方 S: 南方 E: 東方 W: 西方 X: 被重覆標記的cell

Butterfly Time complexity = O(n log 2 n) • Not all AFs will be detected • All SAFs are found

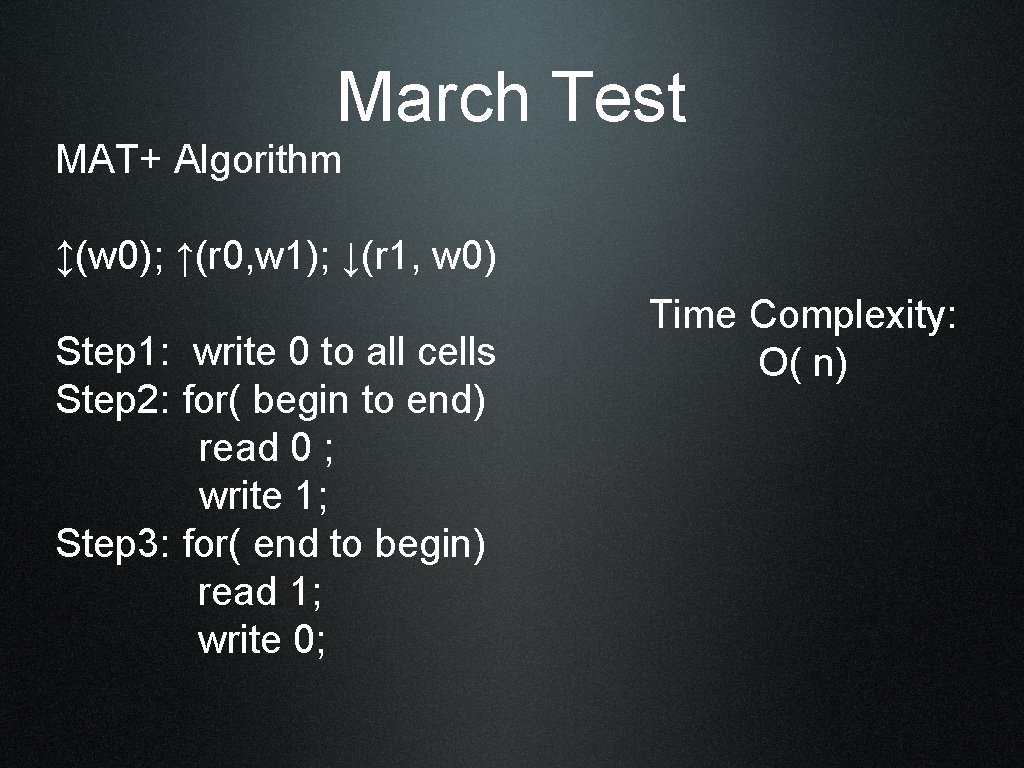

March Test MAT+ Algorithm ↕(w 0); ↑(r 0, w 1); ↓(r 1, w 0) Step 1: write 0 to all cells Step 2: for( begin to end) read 0 ; write 1; Step 3: for( end to begin) read 1; write 0; Time Complexity: O( n)

March Test • MAT+ • AF • SAF

March Test MATS : ↕(w 0); ↕(r 0, w 1); ↕(r 1) MATS+: ↕(w 0); ↑(r 0, w 1); ↓(r 1, w 0) Marching 1/0 : ↕(w 0); ↑(r 0, w 1, r 1); ↓(r 1, w 0, r 0); ↕(w 1); ↑(r 1, w 0, r 0); ↓(r 0, w 1, r 1); MATS++ : ↕ (w 0); ↑(r 0, w 1); ↓(r 1, w 0, r 0); MARCH X : ↕(w 0); ↑(r 0, w 1); ↓(r 1, w 0); ↕(r 0) MARCH C : ↕(w 0); ↑(r 0, w 1); ↑(r 1, w 0); ↕(r 0); ↓(r 0, w 1); ↓(r 1, w 0); ↕(r 0);

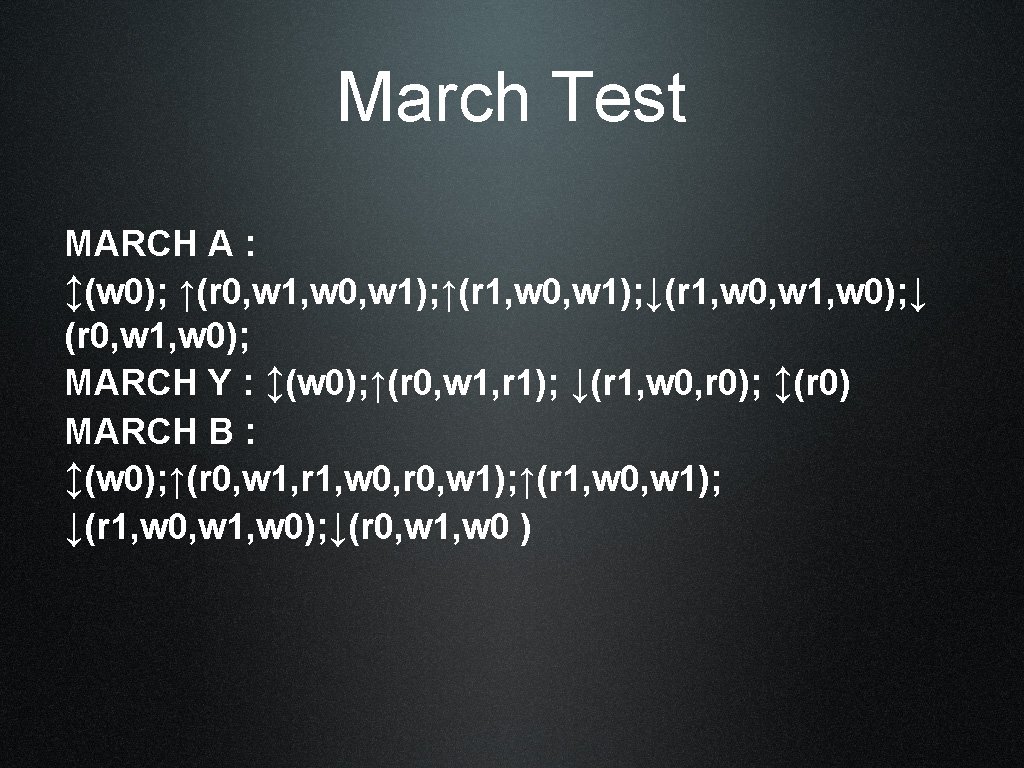

March Test MARCH A : ↕(w 0); ↑(r 0, w 1, w 0, w 1); ↑(r 1, w 0, w 1); ↓(r 1, w 0, w 1, w 0); ↓ (r 0, w 1, w 0); MARCH Y : ↕(w 0); ↑(r 0, w 1, r 1); ↓(r 1, w 0, r 0); ↕(r 0) MARCH B : ↕(w 0); ↑(r 0, w 1, r 1, w 0, r 0, w 1); ↑(r 1, w 0, w 1); ↓(r 1, w 0, w 1, w 0); ↓(r 0, w 1, w 0 )

March Test March Algorithm Test Lenth Fault MATS 4 n Some AFs, SAFs MATS+ 5 n AFs, SAFs Marching 1/0 14 n AFs, SAFs, TFs MATS++ 6 n AFs, SAFs, TFs March X 6 n AFs, SAFs, TFs, Some CFs March C- 10 n AFs, SAFs, TFs, Some CFs March A 15 n AFs, SAFs, TFs, Some CFs March Y 8 n AFs, SAFs, TFs, Some CFs March B 17 n AFs, SAFs, TFs, Some CFs

Pseudo-Random Test • complexity: O(kn) • k: # of iteration • it can be designed to detect different types of fault.

Pseudo-Random Test (cont. ) e: escape probability PD: probability of detecting fault PD = 1 – e we want to decrease the value of e

Pseudo-Random Test (cont. ) For example: we want to detect SA 0 fault based on Markov chain

Pseudo-Random Test (cont. ) S 0: state in which a 0 is stored S 1: state in which a 1 is stored SD 0: state in which SA 0 fault is detected (terminate state) p. Sx(t): probability of being in state Sx at iteration t p. I 1: probability of being in state 1 at first

Pseudo-Random Test (cont. ) initial condition: p. S 0(0) = 1 – p. I 1 p. S 1(0) = p. I 1 p. SD 0(0) = 0

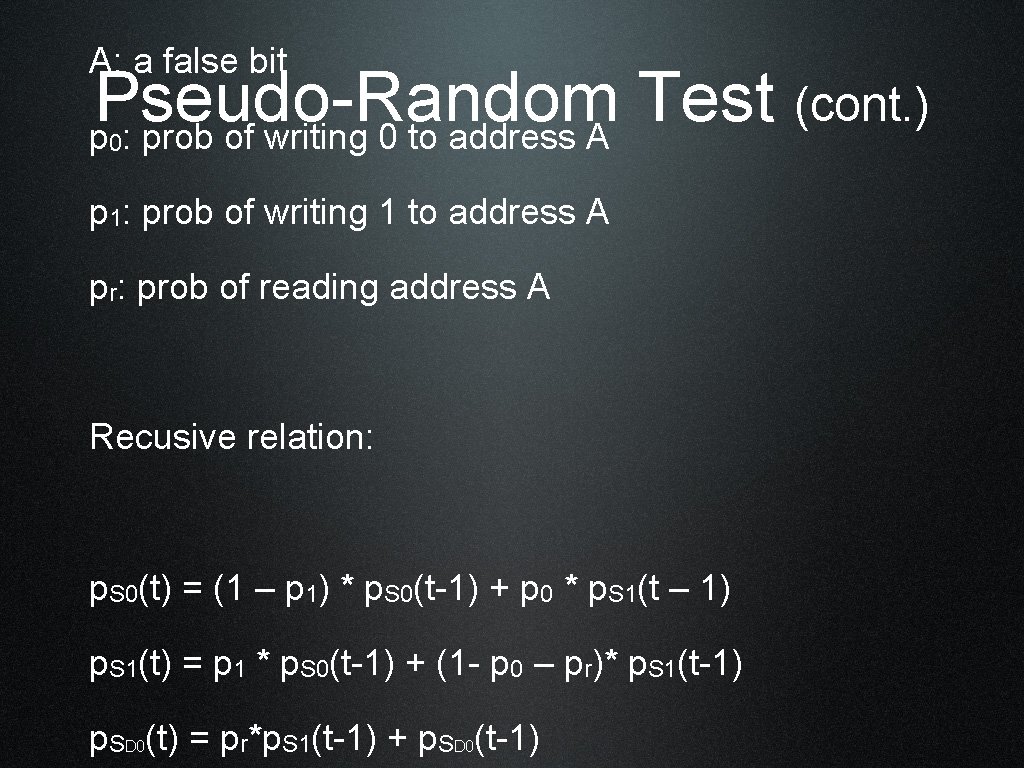

A: a false bit Pseudo-Random Test (cont. ) p : prob of writing 0 to address A 0 p 1: prob of writing 1 to address A pr: prob of reading address A Recusive relation: p. S 0(t) = (1 – p 1) * p. S 0(t-1) + p 0 * p. S 1(t – 1) p. S 1(t) = p 1 * p. S 0(t-1) + (1 - p 0 – pr)* p. S 1(t-1) p. SD 0(t) = pr*p. S 1(t-1) + p. SD 0(t-1)

Pseudo-Random Test (cont. ) We want to maximize p. SD 0(t) increase with iteration t given a escape probability, can we find t? (e ≥ 1 - p. SD 0(t))

Pseudo-Random Test (cont. ) What's the value of PSD 0(t) for any t? (so we can find t for every given e)

Pseudo-Random Test (cont. ) We can use generating function and solve the recursive relation. And blah. . .

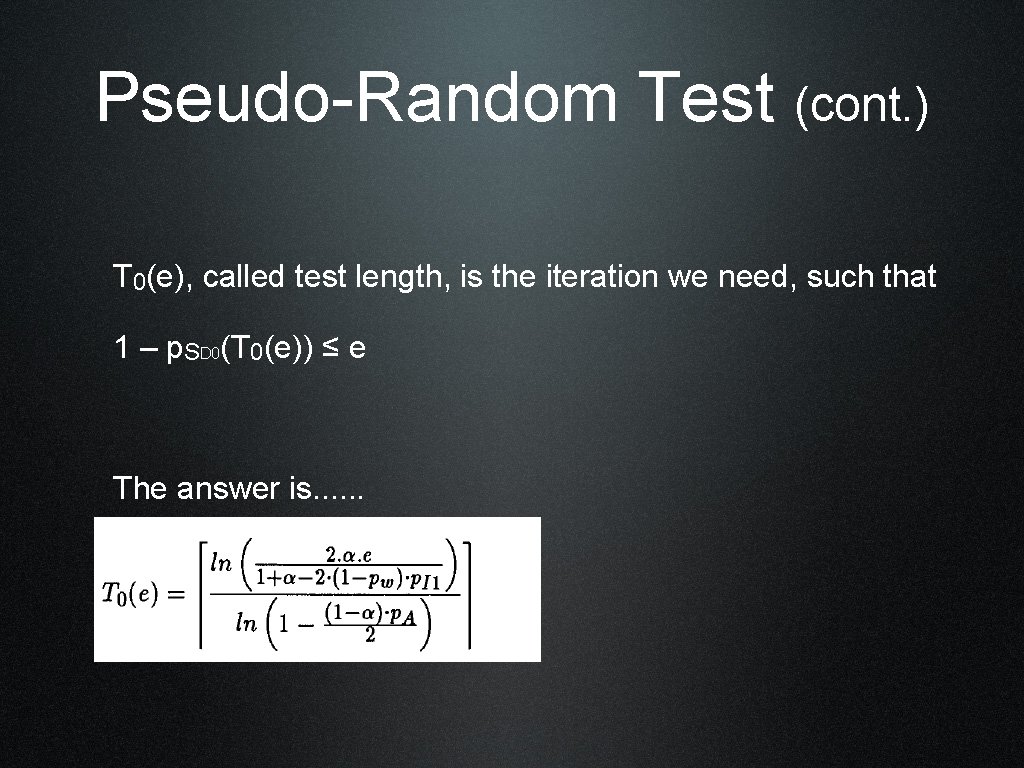

Pseudo-Random Test (cont. ) T 0(e), called test length, is the iteration we need, such that 1 – p. SD 0(T 0(e)) ≤ e The answer is. . .

- Slides: 78