COEN 180 SRAM SRAM n n n Highspeed

- Slides: 21

COEN 180 SRAM

SRAM n n n High-speed Low capacity Expensive n n n Large chip area. Continuous power use to maintain storage Technology used for making MM caches

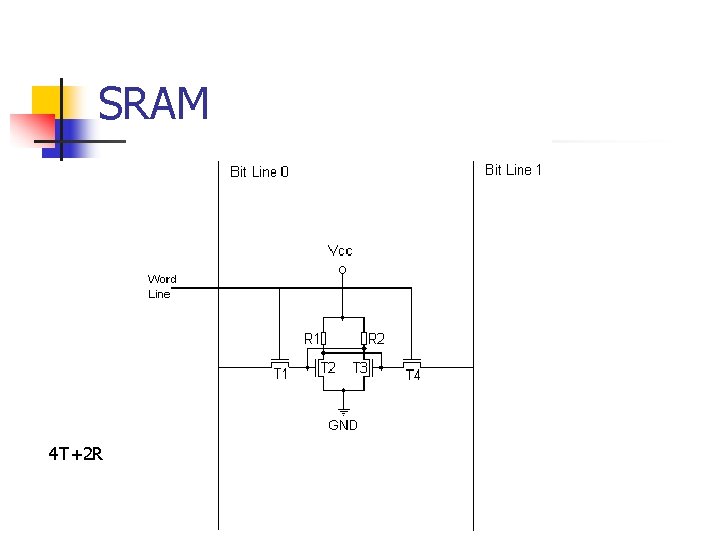

SRAM n n n Single cell stores single bit. 4 T+2 R design (old) 6 T design

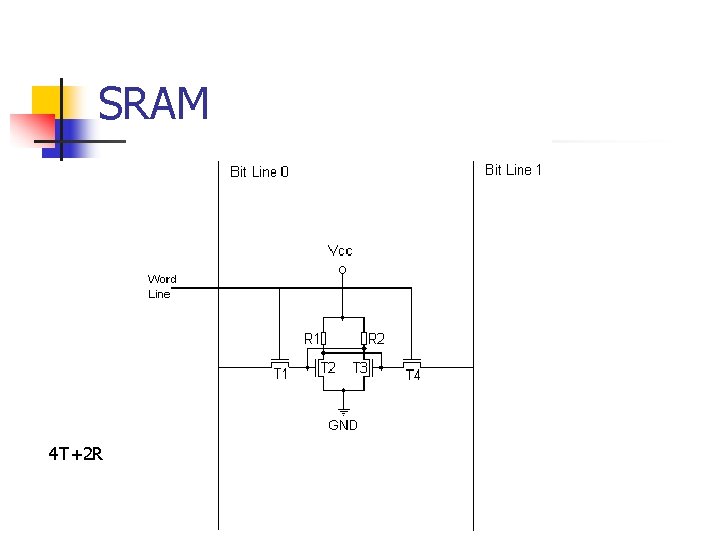

SRAM 4 T+2 R

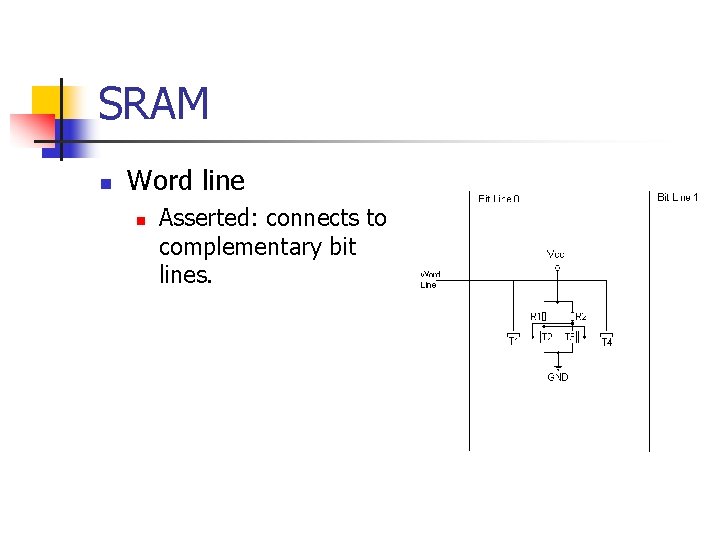

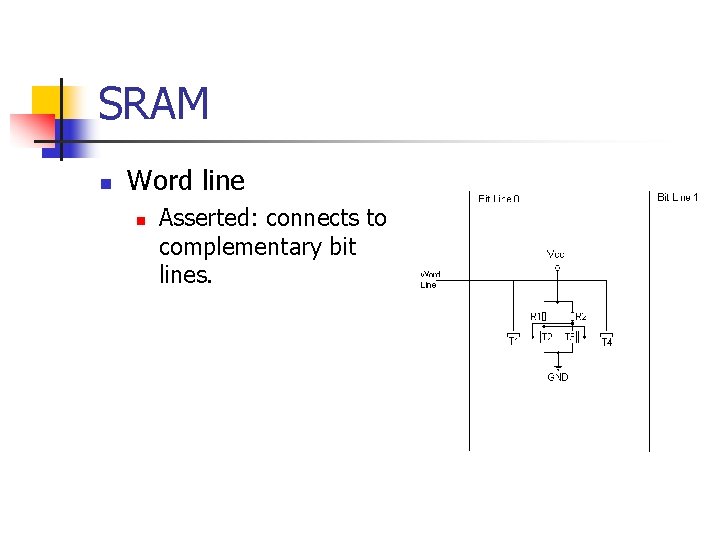

SRAM n Word line n Asserted: connects to complementary bit lines.

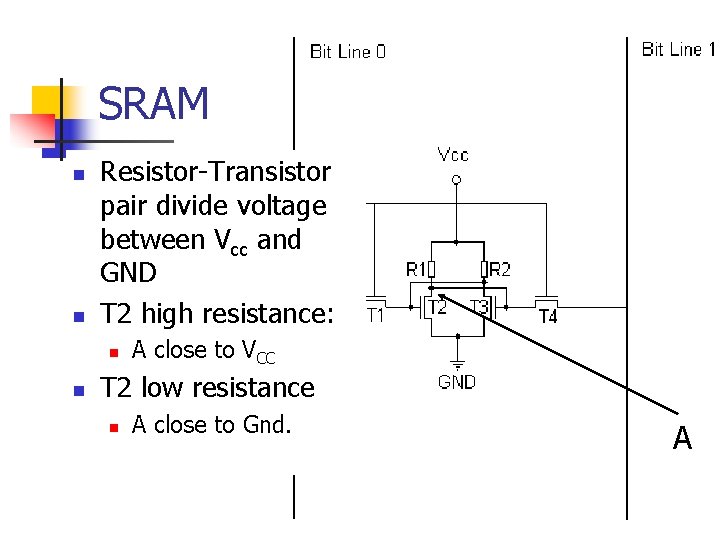

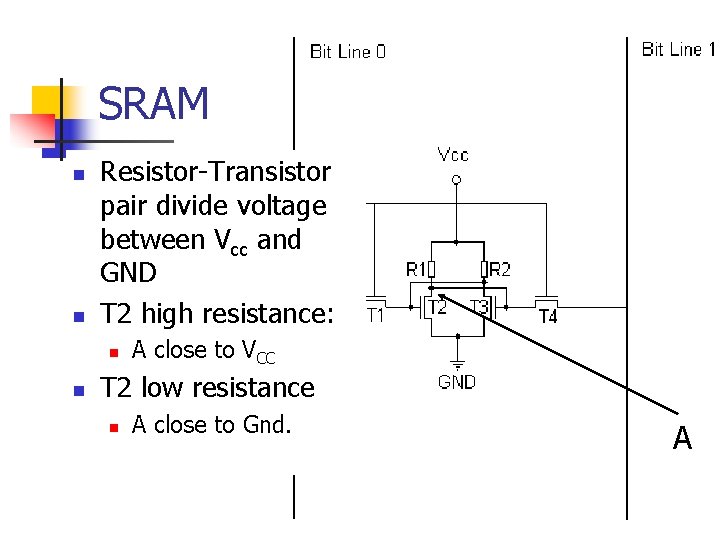

SRAM n n Resistor-Transistor pair divide voltage between Vcc and GND T 2 high resistance: n n A close to VCC T 2 low resistance n A close to Gnd. A

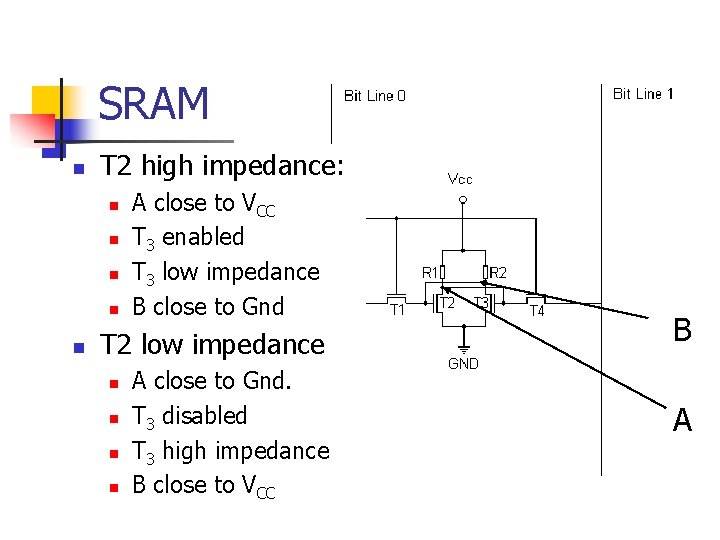

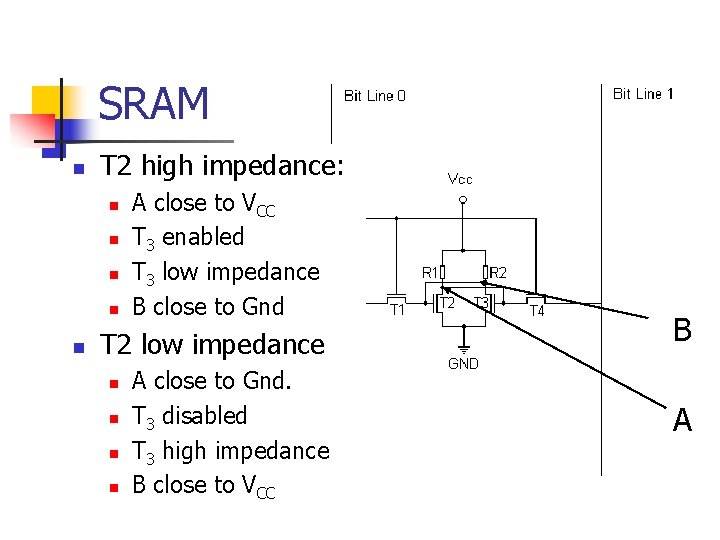

SRAM n T 2 high impedance: n n n A close to VCC T 3 enabled T 3 low impedance B close to Gnd T 2 low impedance n n A close to Gnd. T 3 disabled T 3 high impedance B close to VCC B A

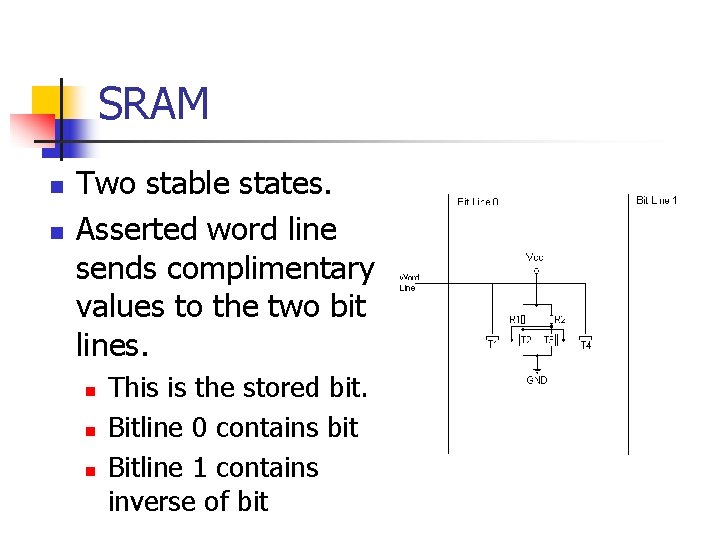

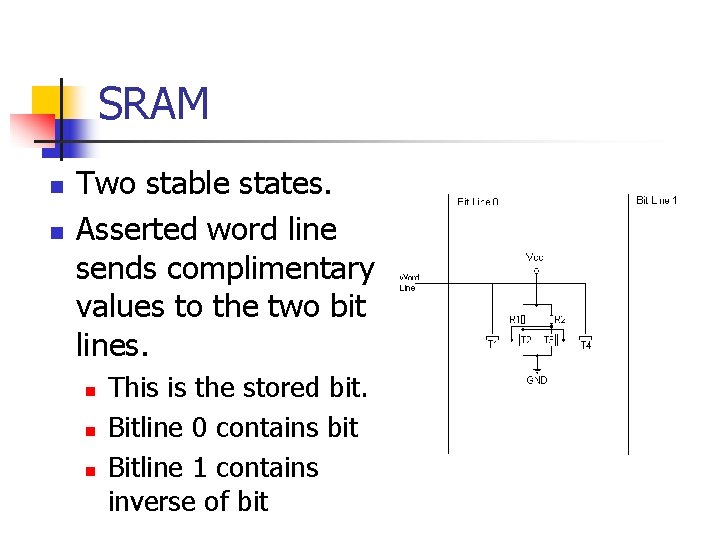

SRAM n n Two stable states. Asserted word line sends complimentary values to the two bit lines. n n n This is the stored bit. Bitline 0 contains bit Bitline 1 contains inverse of bit

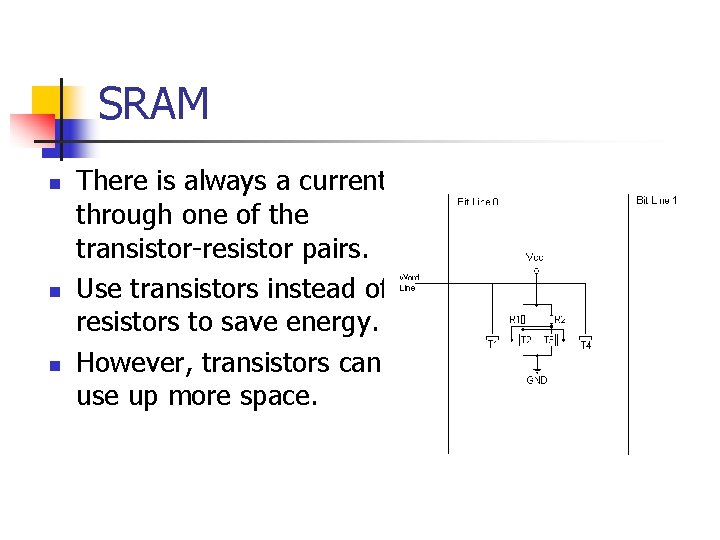

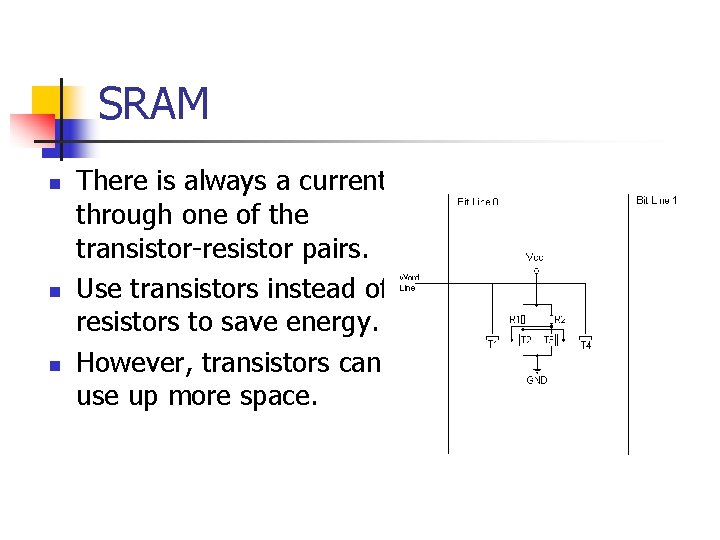

SRAM n n n There is always a current through one of the transistor-resistor pairs. Use transistors instead of resistors to save energy. However, transistors can use up more space.

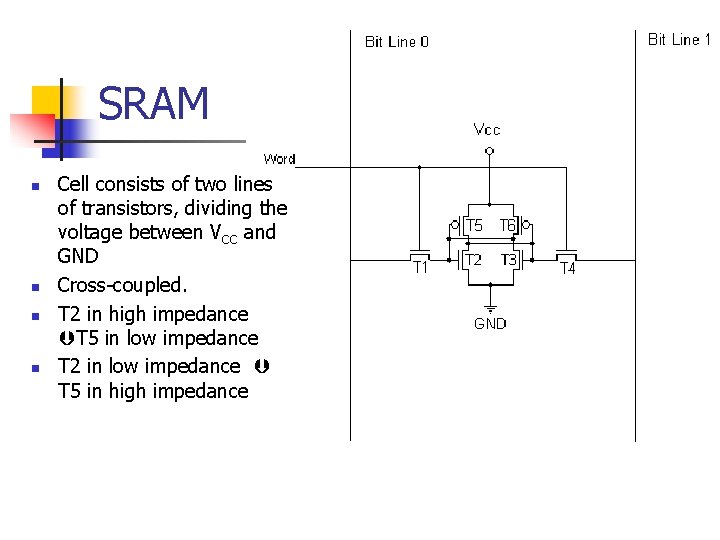

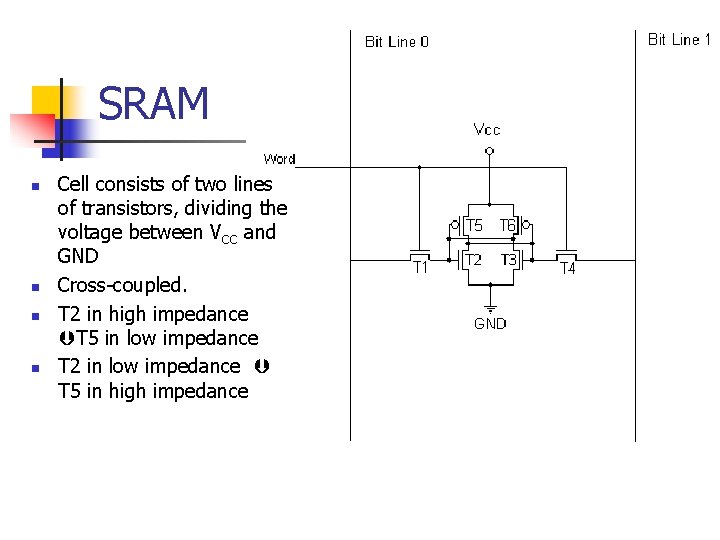

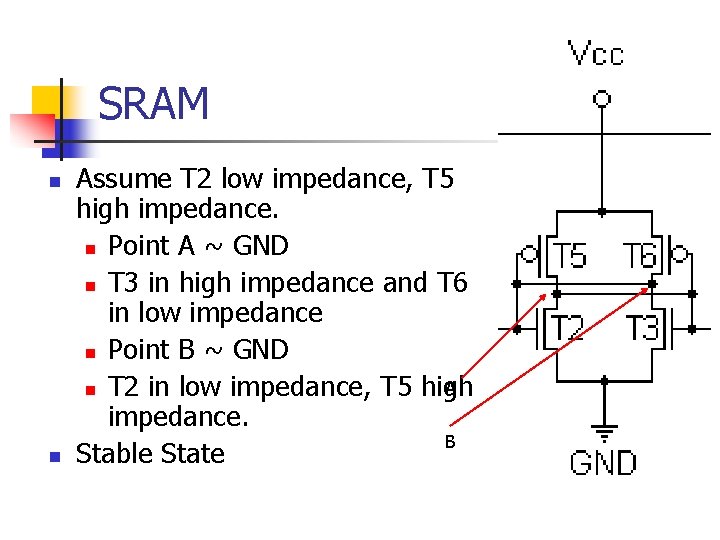

SRAM n n Cell consists of two lines of transistors, dividing the voltage between VCC and GND Cross-coupled. T 2 in high impedance T 5 in low impedance T 2 in low impedance T 5 in high impedance

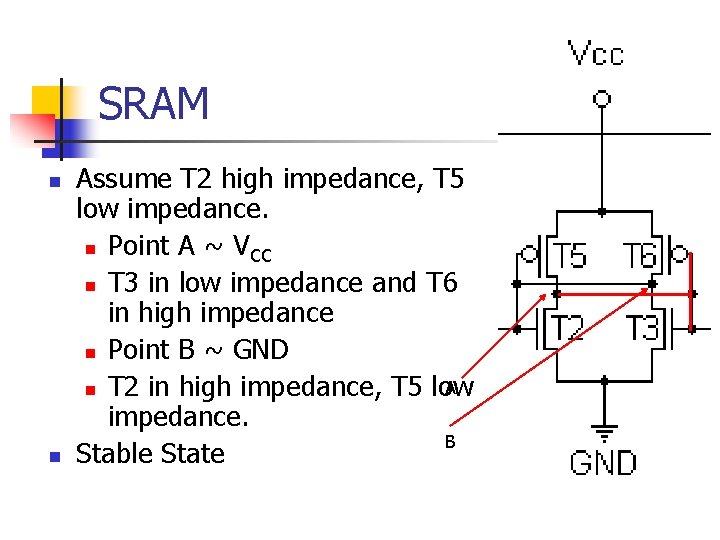

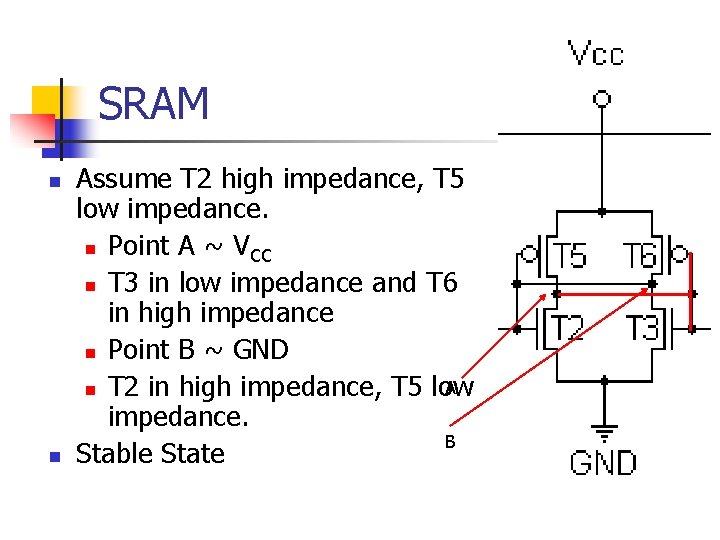

SRAM n n Assume T 2 high impedance, T 5 low impedance. n Point A ~ VCC n T 3 in low impedance and T 6 in high impedance n Point B ~ GND A n T 2 in high impedance, T 5 low impedance. B Stable State

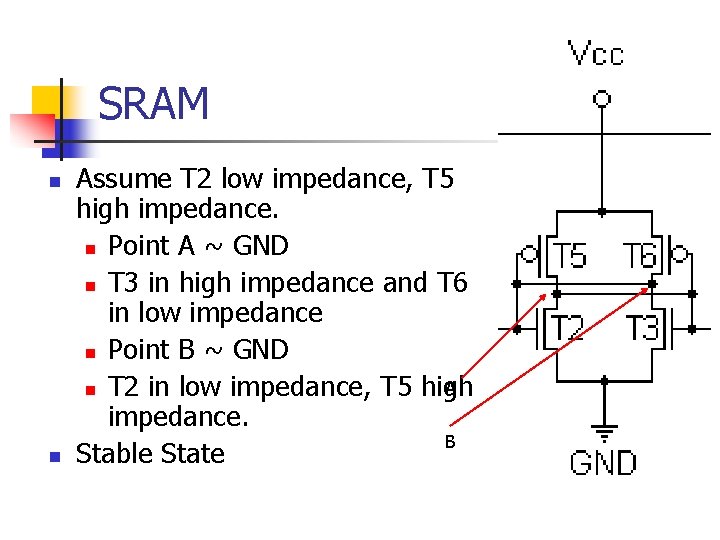

SRAM n n Assume T 2 low impedance, T 5 high impedance. n Point A ~ GND n T 3 in high impedance and T 6 in low impedance n Point B ~ GND A n T 2 in low impedance, T 5 high impedance. B Stable State

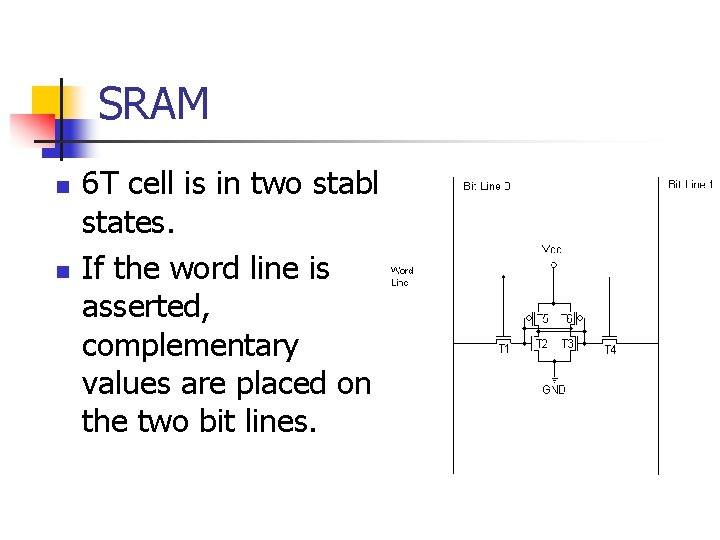

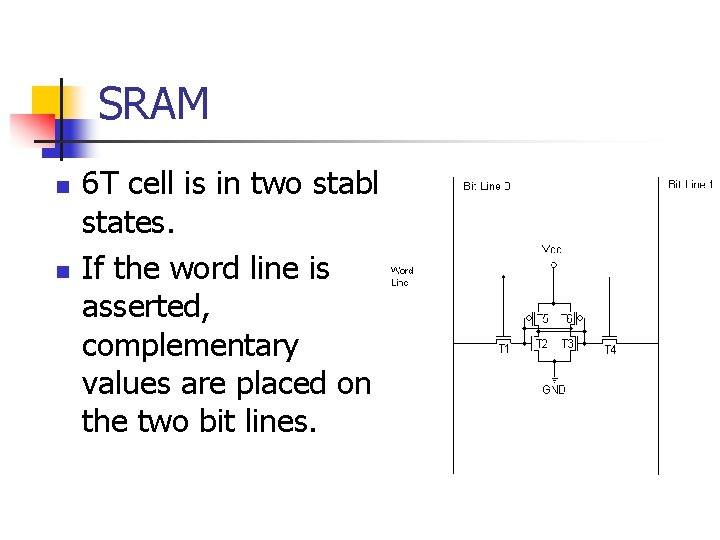

SRAM n n 6 T cell is in two stable states. If the word line is asserted, complementary values are placed on the two bit lines.

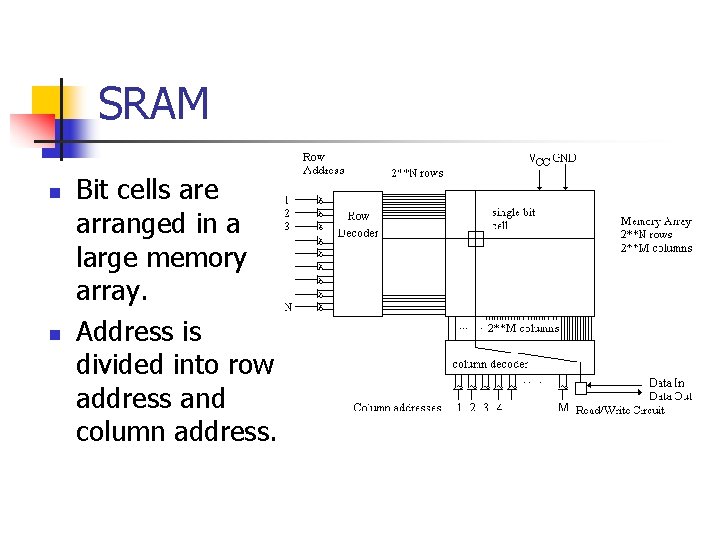

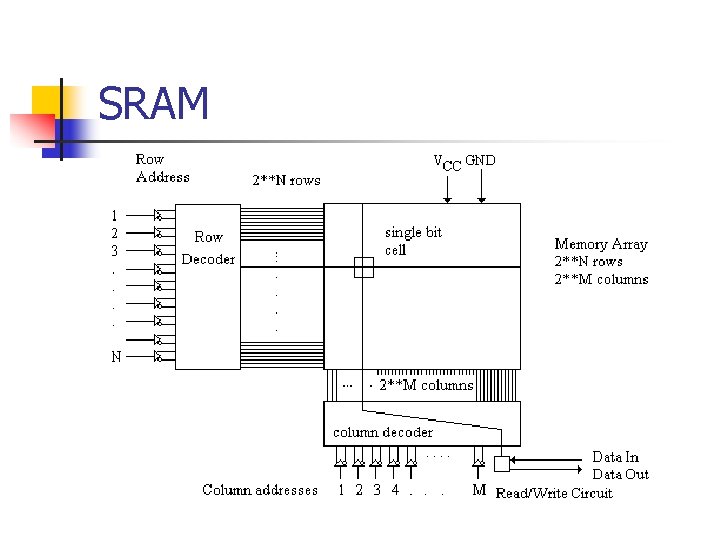

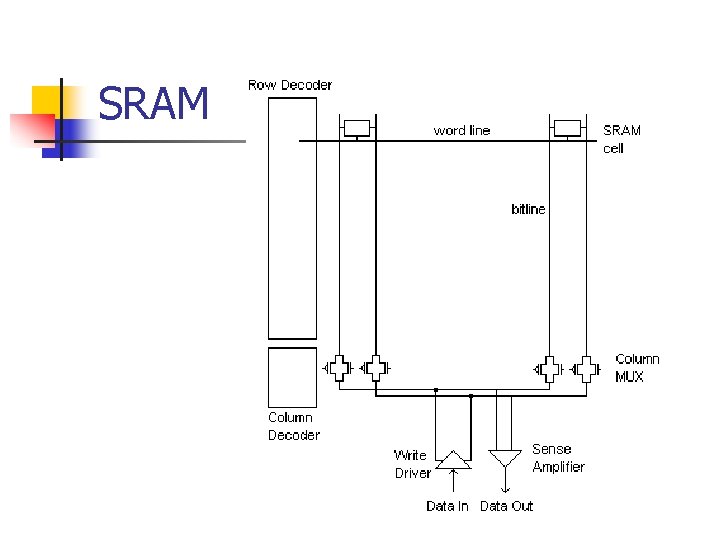

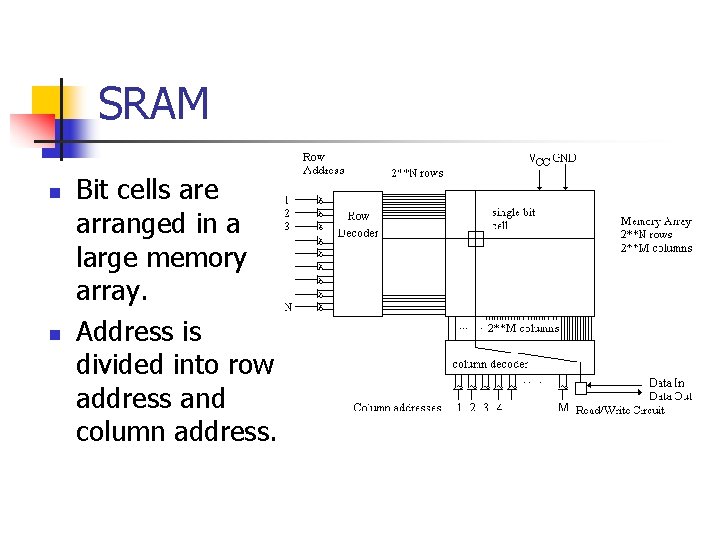

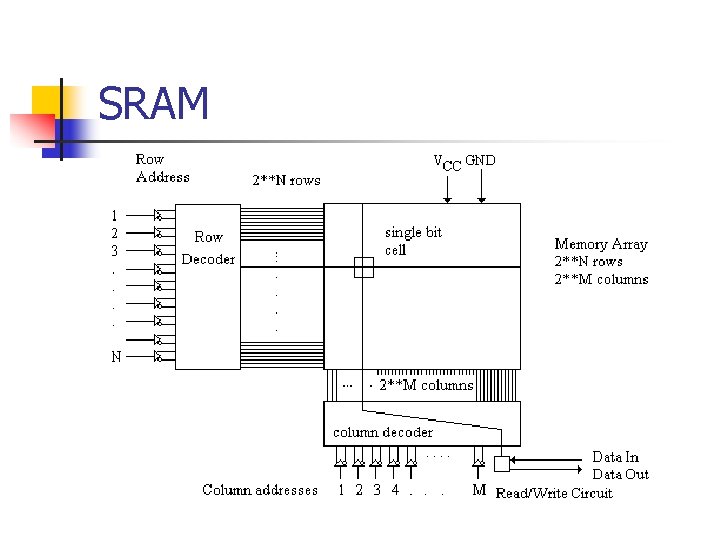

SRAM n n Bit cells are arranged in a large memory array. Address is divided into row address and column address.

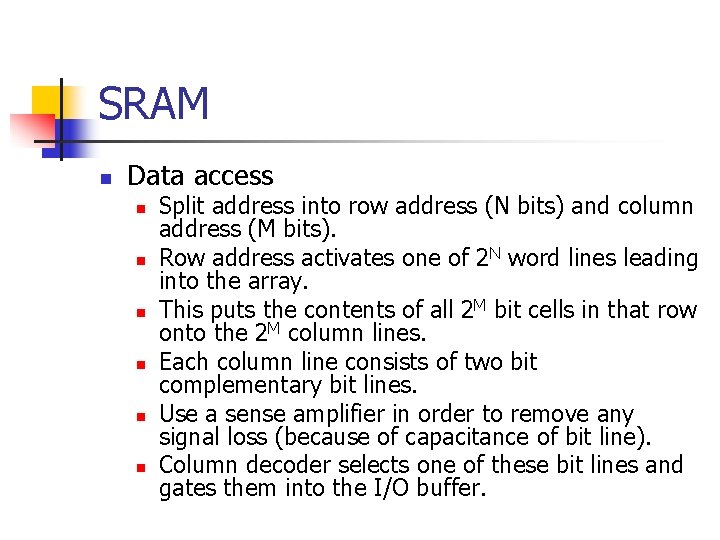

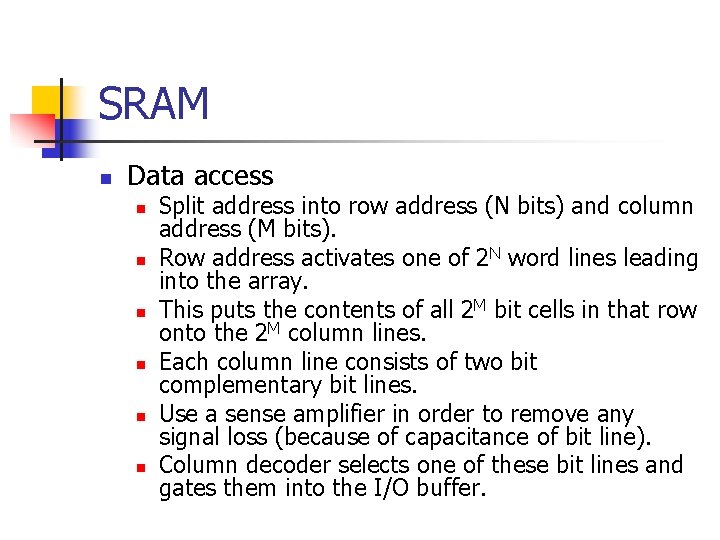

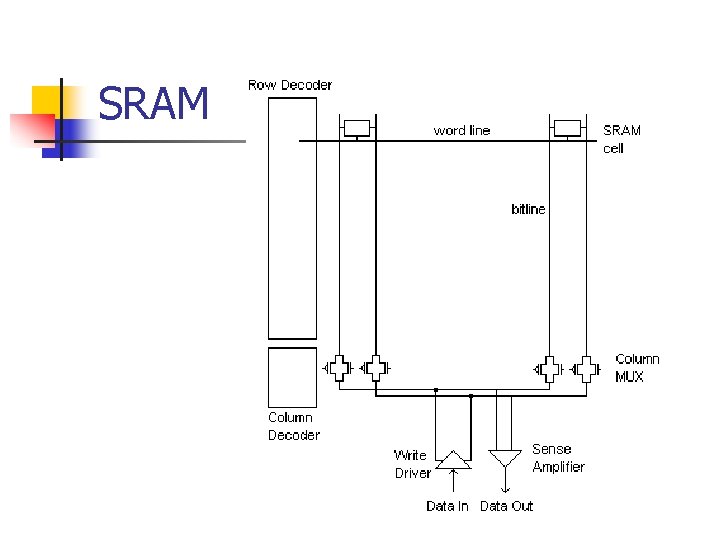

SRAM n Data access n n n Split address into row address (N bits) and column address (M bits). Row address activates one of 2 N word lines leading into the array. This puts the contents of all 2 M bit cells in that row onto the 2 M column lines. Each column line consists of two bit complementary bit lines. Use a sense amplifier in order to remove any signal loss (because of capacitance of bit line). Column decoder selects one of these bit lines and gates them into the I/O buffer.

SRAM

SRAM n Write access n n Everything as before. However: n Value in Read / Write Circuit overwhelms contents in the two bitlines. n This switches the state of the one selected bit cell.

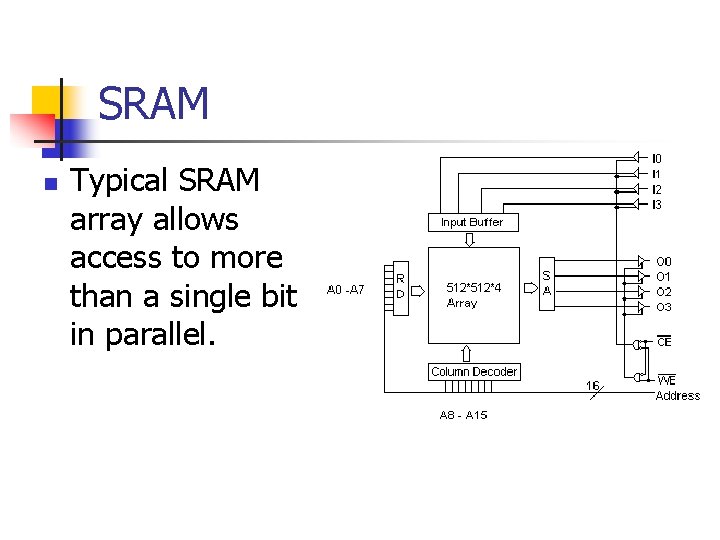

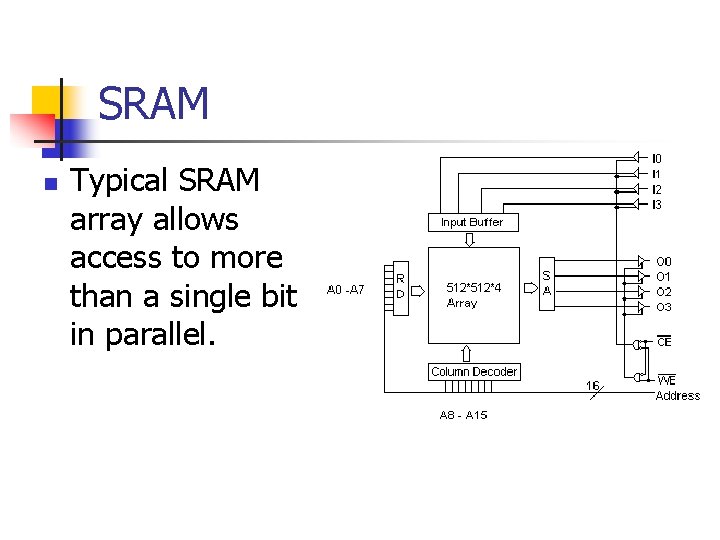

SRAM n Typical SRAM array allows access to more than a single bit in parallel.

SRAM

SRAM n Faster: n n n Faster chip technology Tighter chip technology Use different materials (Ga. As) Increase voltages Cool circuit Change pinout to cut input / output noise.

SRAM n Faster n n Can use input buffer to latch data. Access parameters: n Read-access time n n Propagation delay from the time when the address is presented at the chip to the time data is available at the output. Cycle time n Minimum time between initiation of a read operation and the initiation of another operation.