Lecture 11 Registers and Counters Registers can be

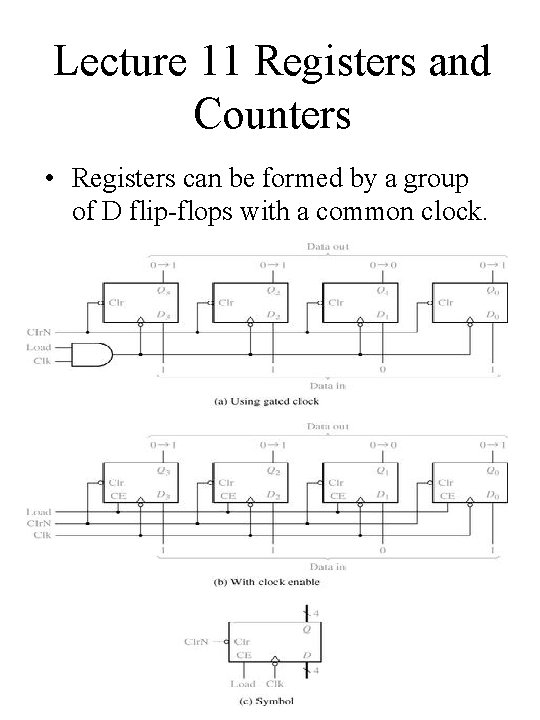

Lecture 11 Registers and Counters • Registers can be formed by a group of D flip-flops with a common clock. Chap 12 C H 1

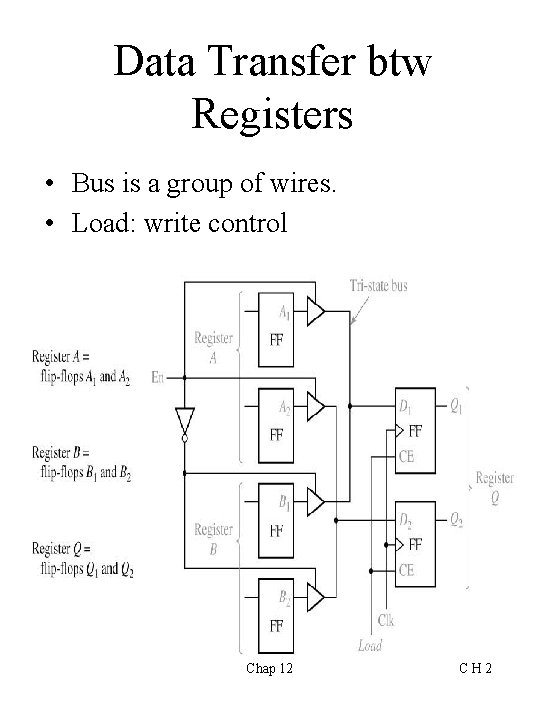

Data Transfer btw Registers • Bus is a group of wires. • Load: write control Chap 12 C H 2

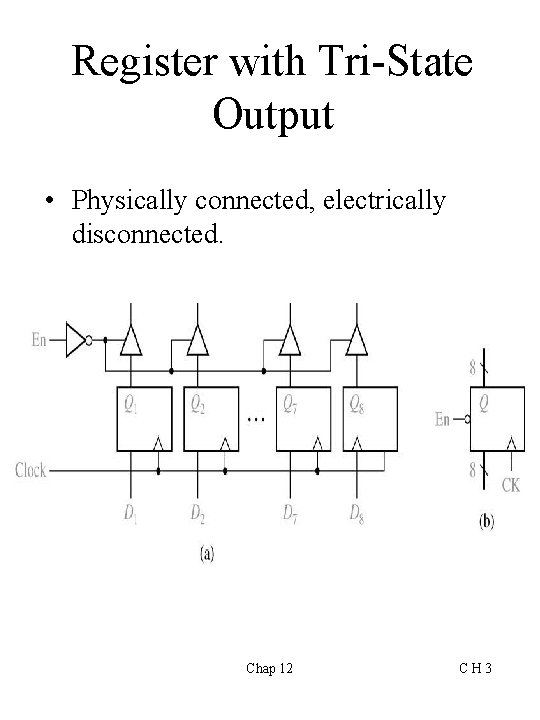

Register with Tri-State Output • Physically connected, electrically disconnected. Chap 12 C H 3

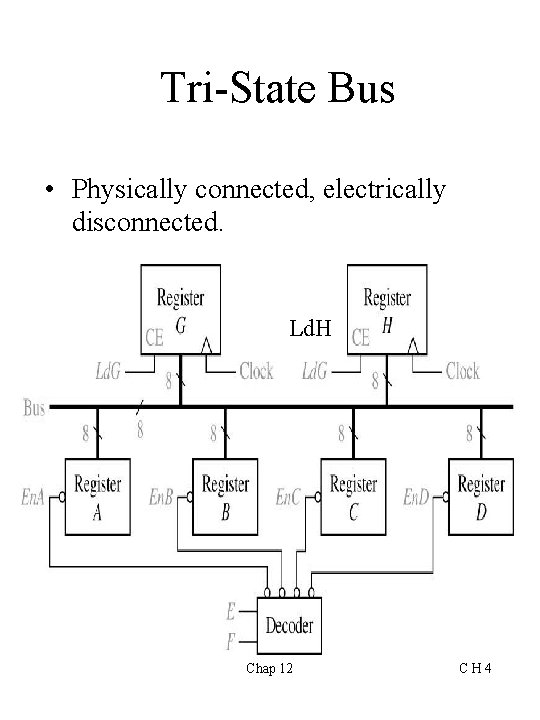

Tri-State Bus • Physically connected, electrically disconnected. Ld. H Chap 12 C H 4

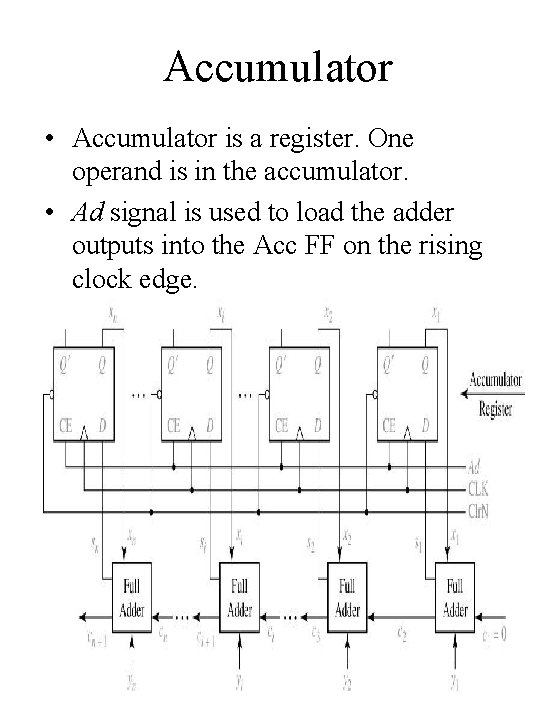

Accumulator • Accumulator is a register. One operand is in the accumulator. • Ad signal is used to load the adder outputs into the Acc FF on the rising clock edge. Chap 12 C H 5

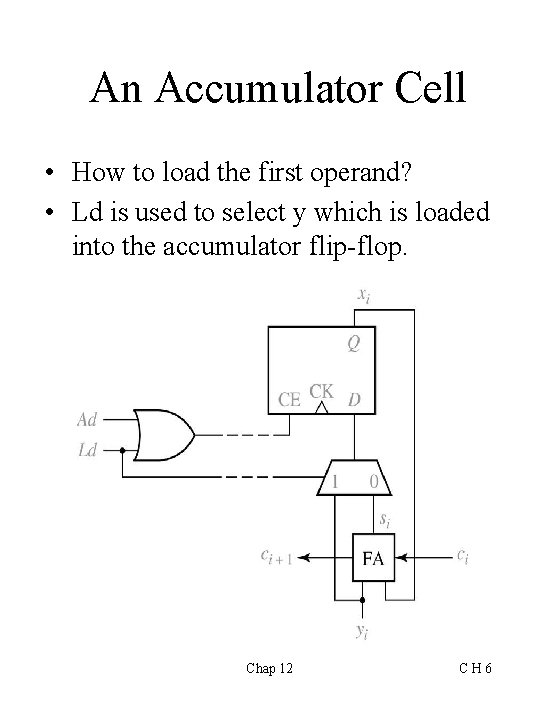

An Accumulator Cell • How to load the first operand? • Ld is used to select y which is loaded into the accumulator flip-flop. Chap 12 C H 6

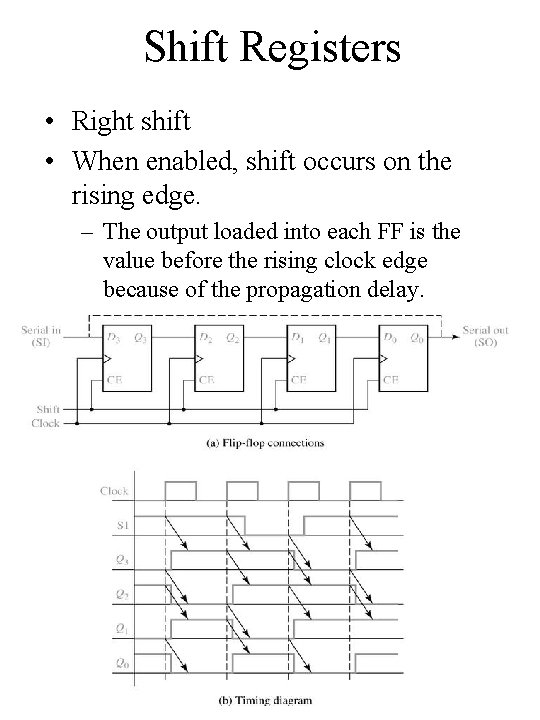

Shift Registers • Right shift • When enabled, shift occurs on the rising edge. – The output loaded into each FF is the value before the rising clock edge because of the propagation delay. Chap 12 C H 7

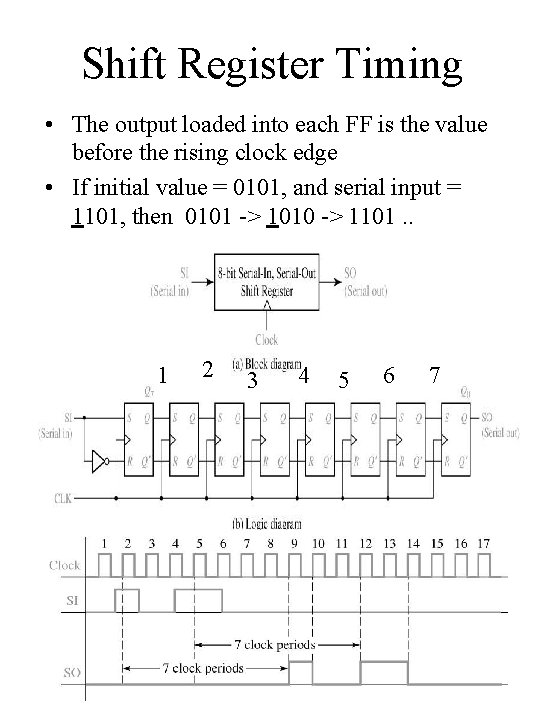

Shift Register Timing • The output loaded into each FF is the value before the rising clock edge • If initial value = 0101, and serial input = 1101, then 0101 -> 1010 -> 1101. . 1 2 3 Chap 12 4 5 6 7 C H 8

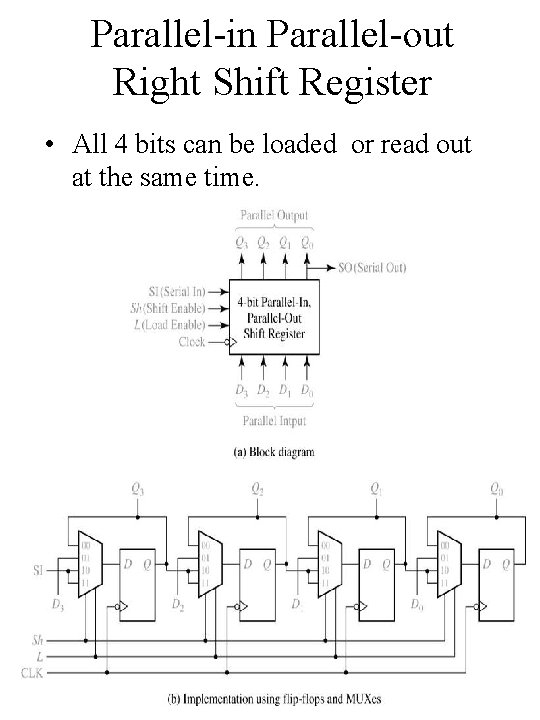

Parallel-in Parallel-out Right Shift Register • All 4 bits can be loaded or read out at the same time. Chap 12 C H 9

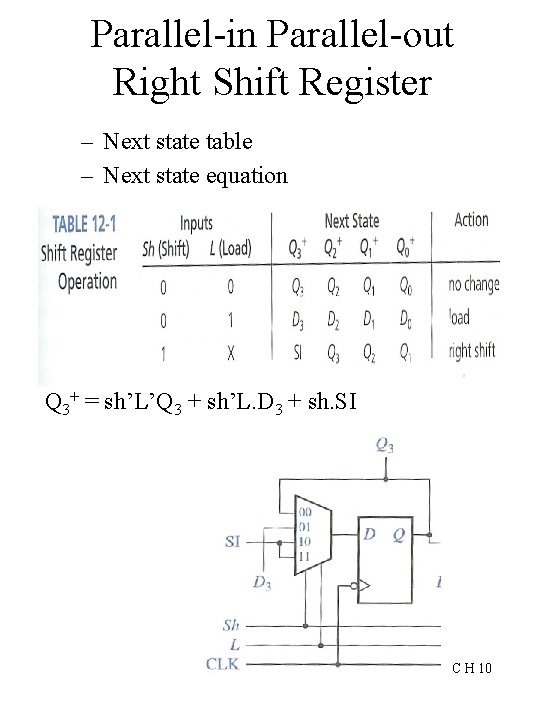

Parallel-in Parallel-out Right Shift Register – Next state table – Next state equation Q 3+ = sh’L’Q 3 + sh’L. D 3 + sh. SI Chap 12 C H 10

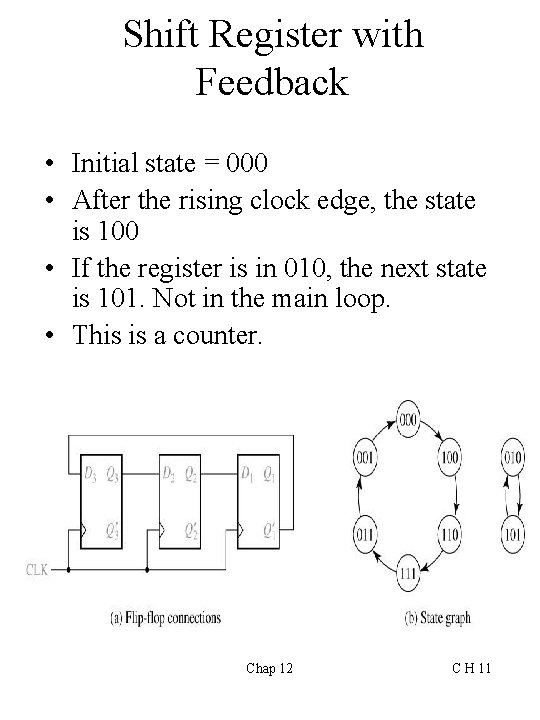

Shift Register with Feedback • Initial state = 000 • After the rising clock edge, the state is 100 • If the register is in 010, the next state is 101. Not in the main loop. • This is a counter. Chap 12 C H 11

Synchronous Counter • Synchronous counter – FFs are synchronized by a common input pulse. • Example: Construct a binary counter using three T FF to count pulses. – 000, 001, 010, 011, 100, 101, 110, 111, 000 …. . Chap 12 C H 12

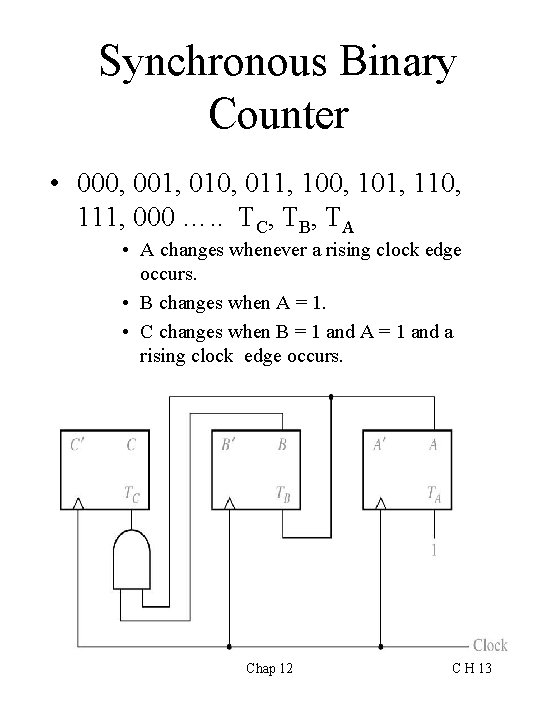

Synchronous Binary Counter • 000, 001, 010, 011, 100, 101, 110, 111, 000 …. . TC, TB, TA • A changes whenever a rising clock edge occurs. • B changes when A = 1. • C changes when B = 1 and A = 1 and a rising clock edge occurs. Chap 12 C H 13

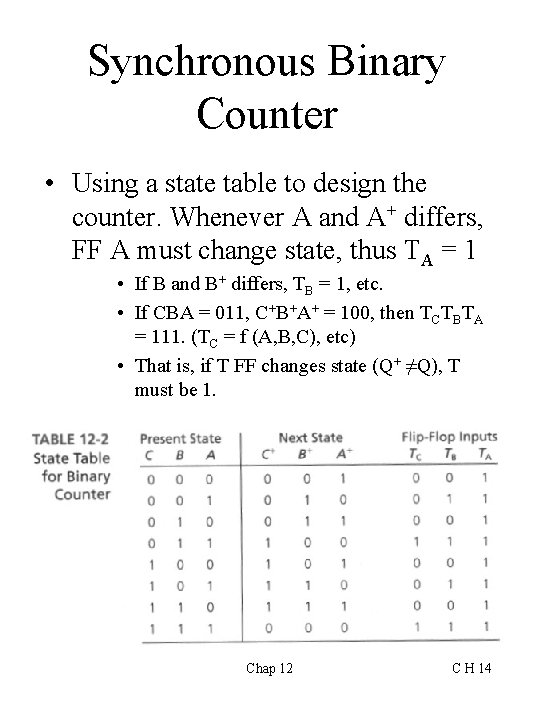

Synchronous Binary Counter • Using a state table to design the counter. Whenever A and A+ differs, FF A must change state, thus TA = 1 • If B and B+ differs, TB = 1, etc. • If CBA = 011, C+B+A+ = 100, then TCTBTA = 111. (TC = f (A, B, C), etc) • That is, if T FF changes state (Q+ ≠Q), T must be 1. Chap 12 C H 14

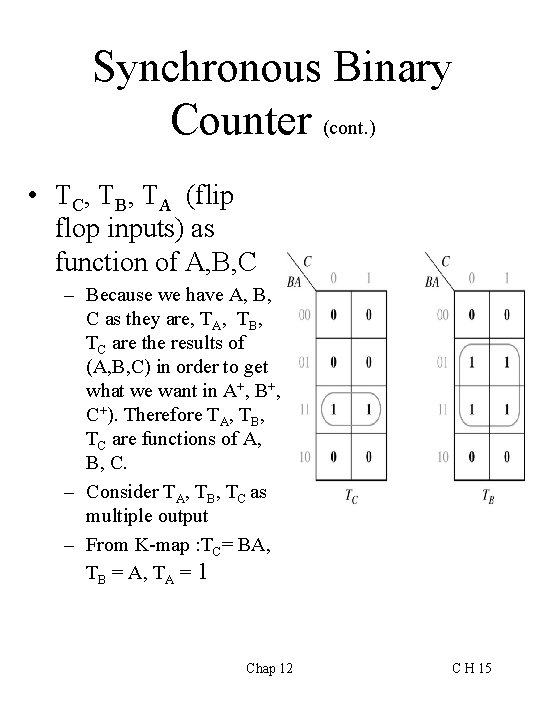

Synchronous Binary Counter (cont. ) • TC, TB, TA (flip flop inputs) as function of A, B, C – Because we have A, B, C as they are, TA, TB, TC are the results of (A, B, C) in order to get what we want in A+, B+, C+). Therefore TA, TB, TC are functions of A, B, C. – Consider TA, TB, TC as multiple output – From K-map : TC= BA, TB = A, TA = 1 Chap 12 C H 15

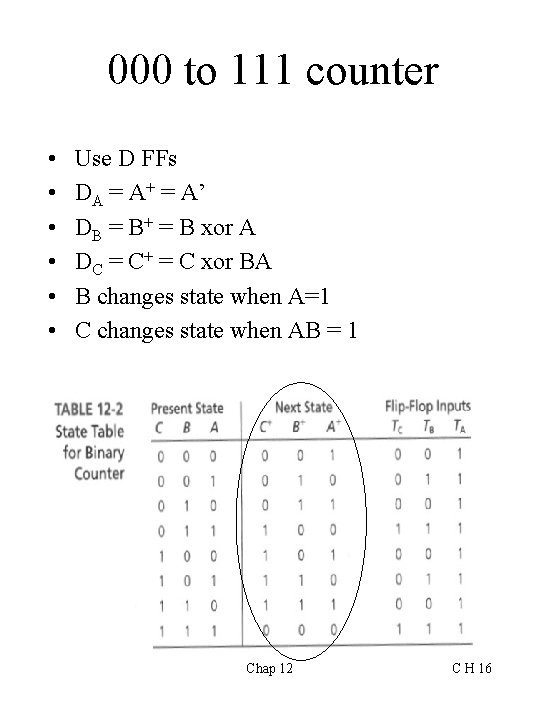

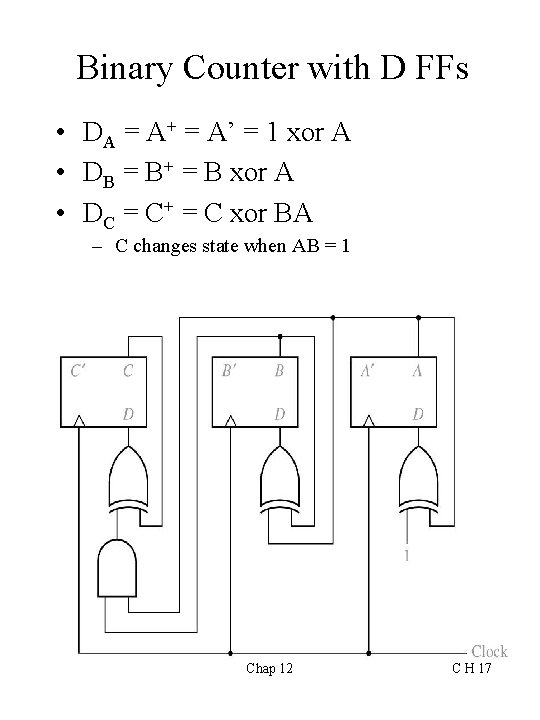

000 to 111 counter • • • Use D FFs DA = A+ = A’ DB = B+ = B xor A DC = C+ = C xor BA B changes state when A=1 C changes state when AB = 1 Chap 12 C H 16

Binary Counter with D FFs • DA = A+ = A’ = 1 xor A • DB = B+ = B xor A • DC = C+ = C xor BA – C changes state when AB = 1 Chap 12 C H 17

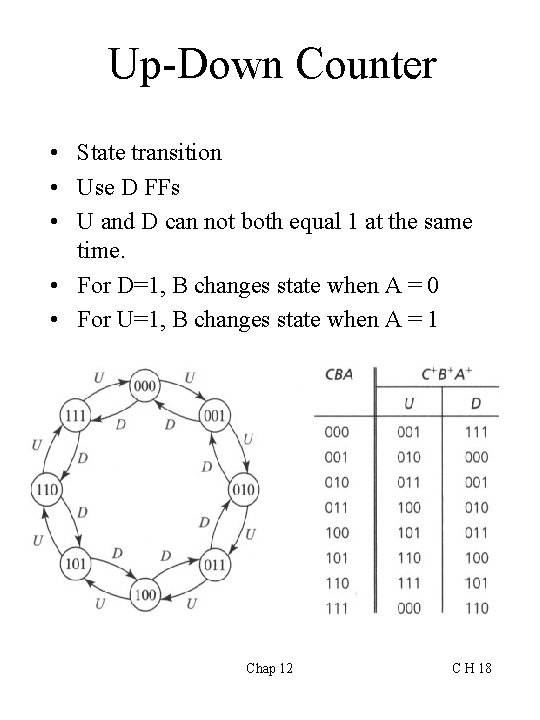

Up-Down Counter • State transition • Use D FFs • U and D can not both equal 1 at the same time. • For D=1, B changes state when A = 0 • For U=1, B changes state when A = 1 Chap 12 C H 18

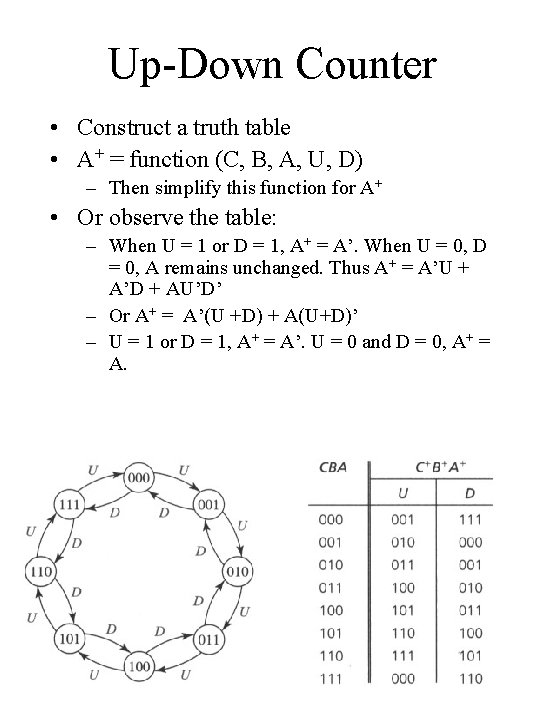

Up-Down Counter • Construct a truth table • A+ = function (C, B, A, U, D) – Then simplify this function for A+ • Or observe the table: – When U = 1 or D = 1, A+ = A’. When U = 0, D = 0, A remains unchanged. Thus A+ = A’U + A’D + AU’D’ – Or A+ = A’(U +D) + A(U+D)’ – U = 1 or D = 1, A+ = A’. U = 0 and D = 0, A+ = A. Chap 12 C H 19

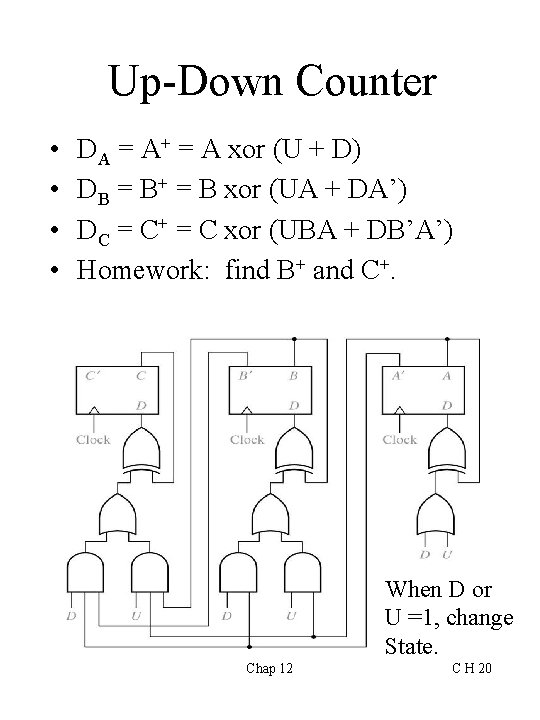

Up-Down Counter • • DA = A+ = A xor (U + D) DB = B+ = B xor (UA + DA’) DC = C+ = C xor (UBA + DB’A’) Homework: find B+ and C+. When D or U =1, change State. Chap 12 C H 20

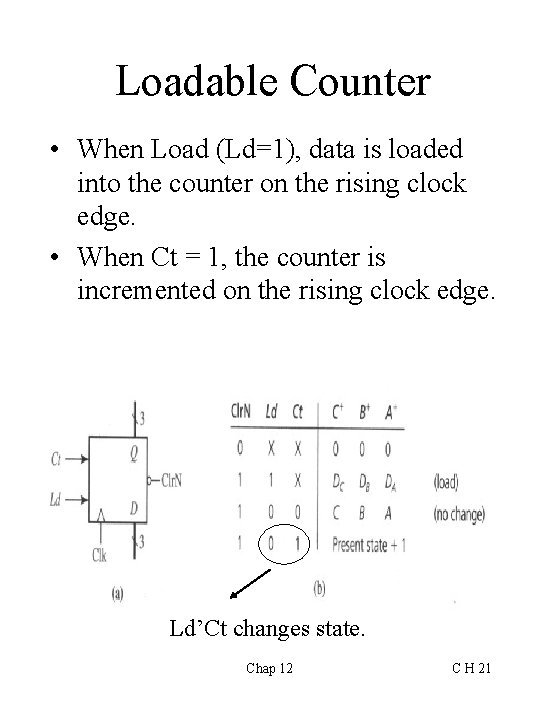

Loadable Counter • When Load (Ld=1), data is loaded into the counter on the rising clock edge. • When Ct = 1, the counter is incremented on the rising clock edge. Ld’Ct changes state. Chap 12 C H 21

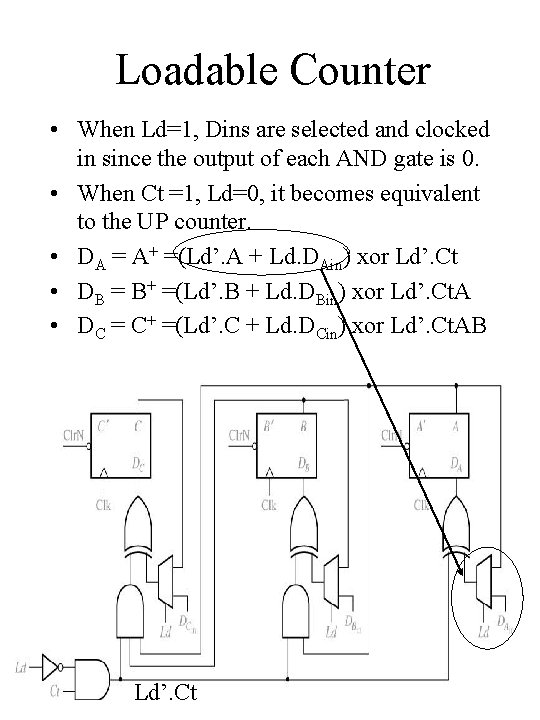

Loadable Counter • When Ld=1, Dins are selected and clocked in since the output of each AND gate is 0. • When Ct =1, Ld=0, it becomes equivalent to the UP counter. • DA = A+ =(Ld’. A + Ld. DAin) xor Ld’. Ct • DB = B+ =(Ld’. B + Ld. DBin) xor Ld’. Ct. A • DC = C+ =(Ld’. C + Ld. DCin) xor Ld’. Ct. AB Chap 12 Ld’. Ct C H 22

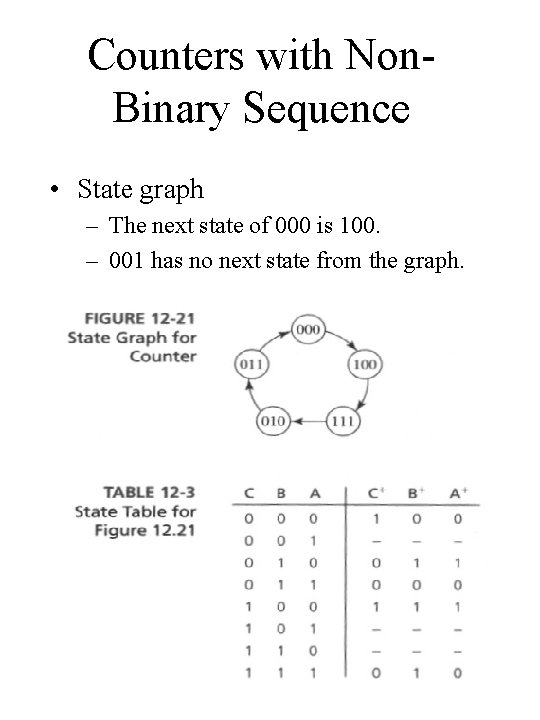

Counters with Non. Binary Sequence • State graph – The next state of 000 is 100. – 001 has no next state from the graph. Chap 12 C H 23

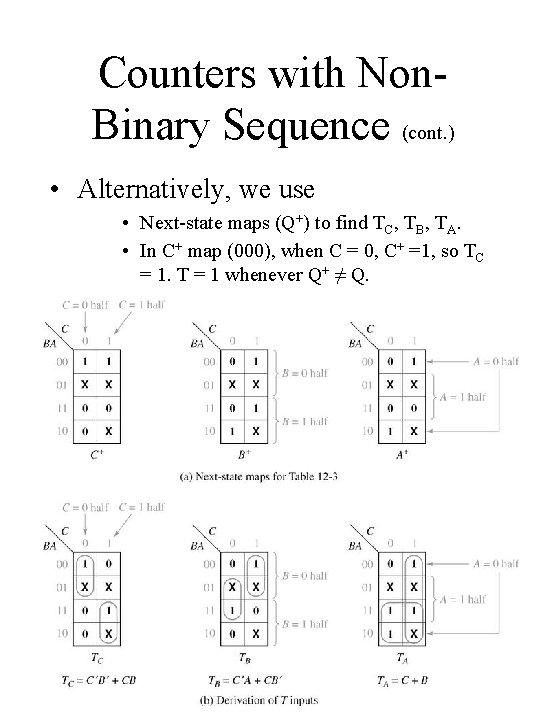

Counters with Non. Binary Sequence (cont. ) • Alternatively, we use • Next-state maps (Q+) to find TC, TB, TA. • In C+ map (000), when C = 0, C+ =1, so TC = 1. T = 1 whenever Q+ ≠ Q. Chap 12 C H 24

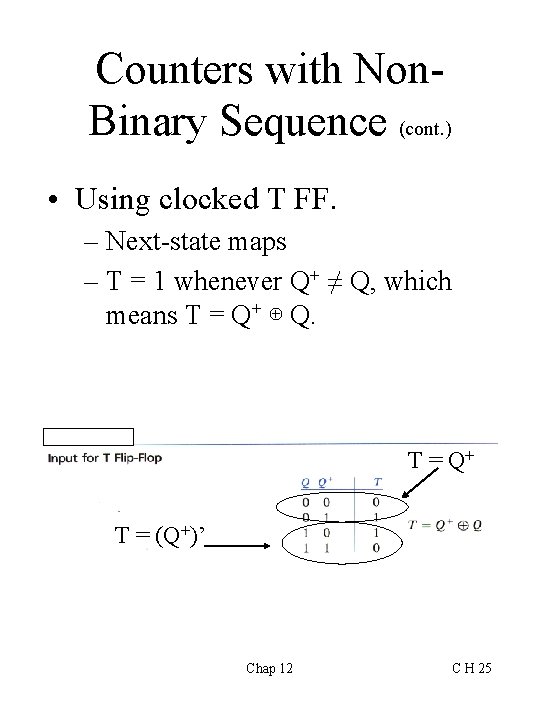

Counters with Non. Binary Sequence (cont. ) • Using clocked T FF. – Next-state maps – T = 1 whenever Q+ ≠ Q, which means T = Q+ ⊕ Q. T = Q+ T = (Q+)’ Chap 12 C H 25

Counters with Non-Binary Sequence (cont. ) • The resultant circuit and timing diagram. Chap 12 C H 26

Counters with Non-Binary Sequence (cont. ) • Summary of procedure – Form a state table of Q and Q+ – Plot Q+ map with respect to Q. – Plot T map w. r. t Q. TQ map is formed from the Q+ map by complementing the Q = 1 entries and leaving Q = 0 entries unchanged. – Find input equation of each T using the TQ map. Chap 12 C H 27

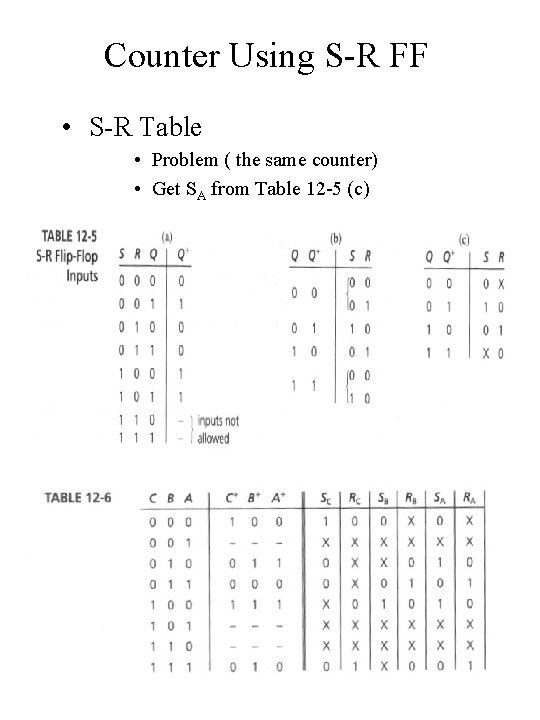

Counter Using S-R FF • S-R Table • Problem ( the same counter) • Get SA from Table 12 -5 (c) Chap 12 C H 28

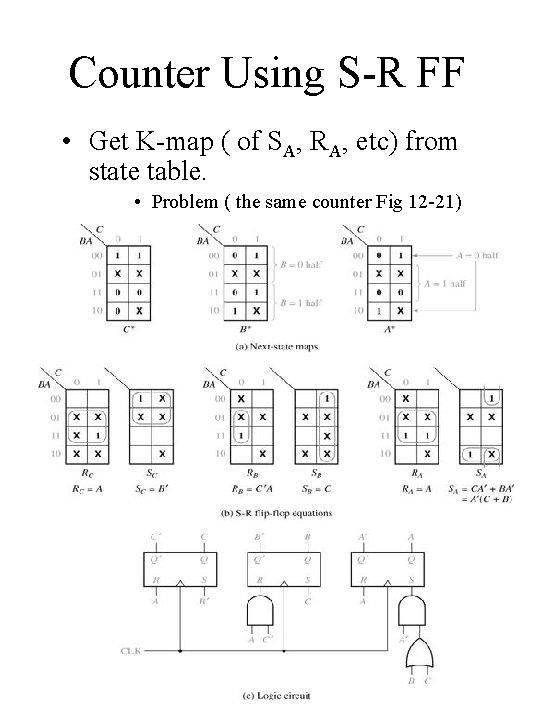

Counter Using S-R FF • Get K-map ( of SA, RA, etc) from state table. • Problem ( the same counter Fig 12 -21) Chap 12 C H 29

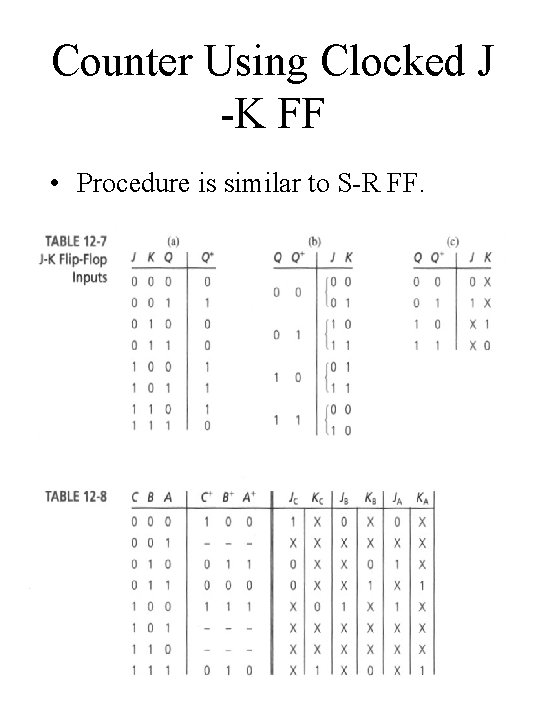

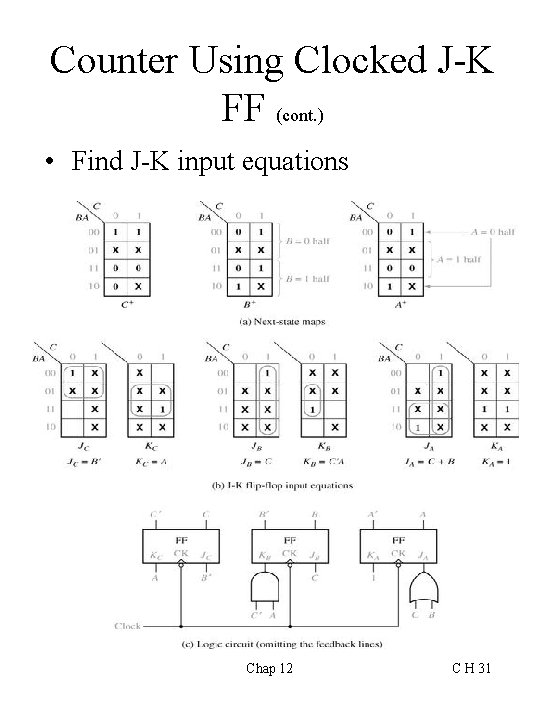

Counter Using Clocked J -K FF • Procedure is similar to S-R FF. Chap 12 C H 30

Counter Using Clocked J-K FF (cont. ) • Find J-K input equations Chap 12 C H 31

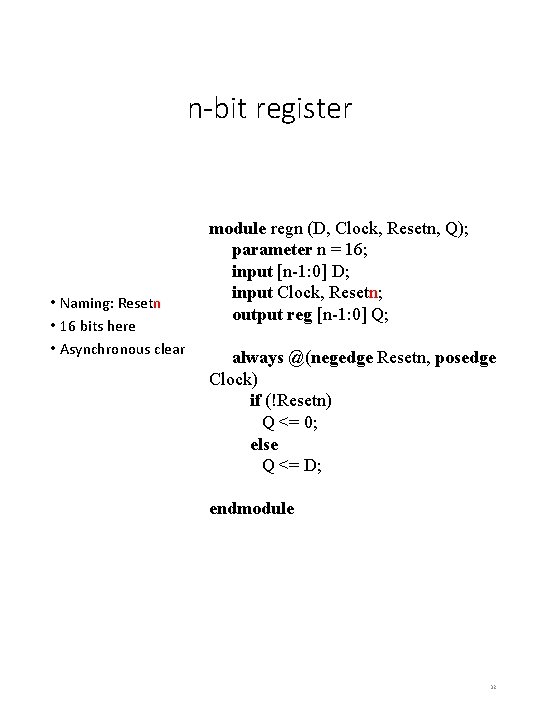

n-bit register • Naming: Resetn • 16 bits here • Asynchronous clear module regn (D, Clock, Resetn, Q); parameter n = 16; input [n-1: 0] D; input Clock, Resetn; output reg [n-1: 0] Q; always @(negedge Resetn, posedge Clock) if (!Resetn) Q <= 0; else Q <= D; endmodule 32

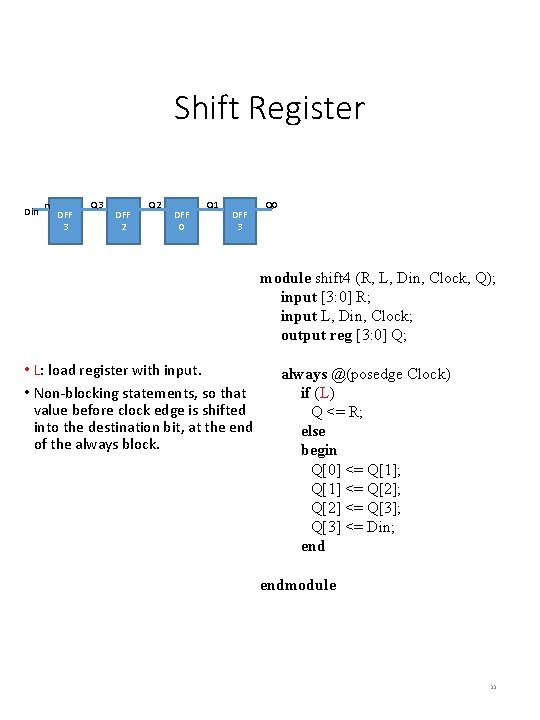

Shift Register Din D DFF 3 Q 3 DFF 2 Q 2 DFF 0 Q 1 DFF 3 Q 0 module shift 4 (R, L, Din, Clock, Q); input [3: 0] R; input L, Din, Clock; output reg [3: 0] Q; • L: load register with input. always @(posedge Clock) if (L) • Non-blocking statements, so that value before clock edge is shifted Q <= R; into the destination bit, at the end else of the always block. begin Q[0] <= Q[1]; Q[1] <= Q[2]; Q[2] <= Q[3]; Q[3] <= Din; endmodule 33

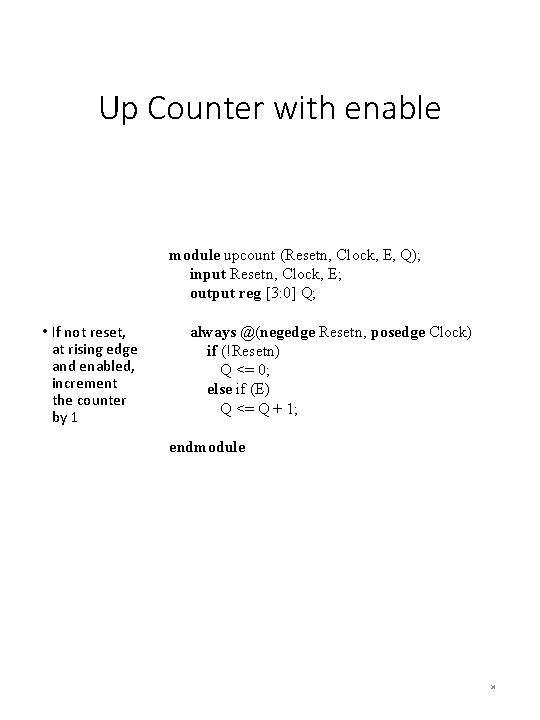

Up Counter with enable • If not reset, at rising edge and enabled, increment the counter by 1 module upcount (Resetn, Clock, E, Q); input Resetn, Clock, E; output reg [3: 0] Q; always @(negedge Resetn, posedge Clock) if (!Resetn) Q <= 0; else if (E) Q <= Q + 1; endmodule 34

Up/down Counter with enable • Q <= Q+1 • Q <= Q-1 module UDcount (R, Clock, L, E, up_down, Q); parameter n = 8; input [n-1: 0] R; input Clock, L, E, up_down; output reg [n-1: 0] Q; always @(posedge Clock) if (L) Q <= R; else if (E) Q <= Q + (up_down ? 1 : -1); endmodule 35

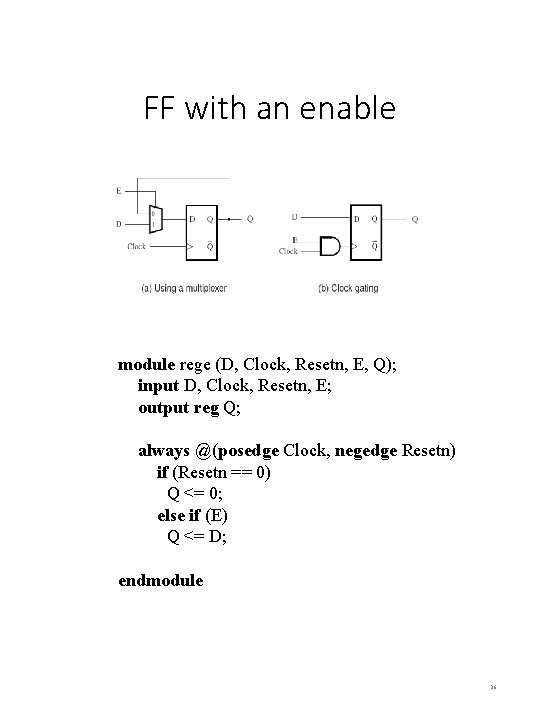

FF with an enable module rege (D, Clock, Resetn, E, Q); input D, Clock, Resetn, E; output reg Q; always @(posedge Clock, negedge Resetn) if (Resetn == 0) Q <= 0; else if (E) Q <= D; endmodule 36

- Slides: 36