Registers and Counters Registers n n n n

- Slides: 33

Registers and Counters

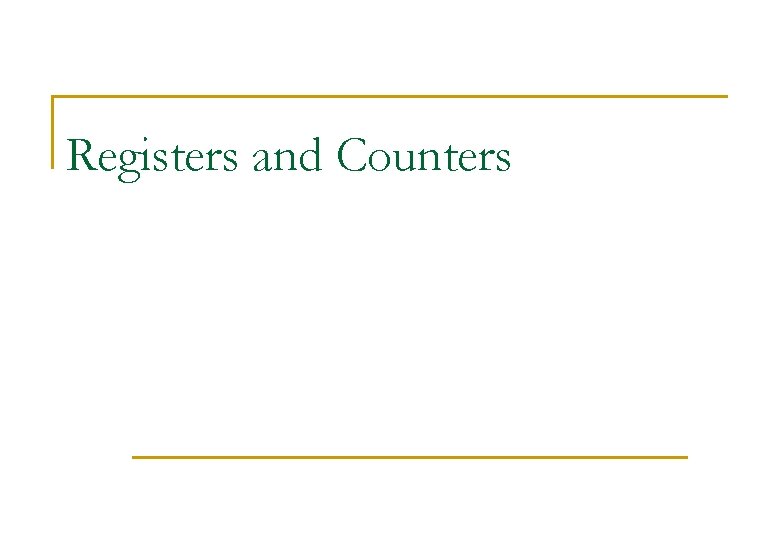

Registers n n n n Register is very important building blocks. A data register is often used to store binary information. A register might be used to accept input data from an alphanumeric keyboard and the present this data to the circuitry used to display on the CRT screen. Register is a group of flip flops that can be used to store a binary number. n-bit register has n flip flops and each FF stores one bit. Two basic functions: data storage and data movement. A binary register also performs very important arithmetic operations such as complementation, multiplication, and division.

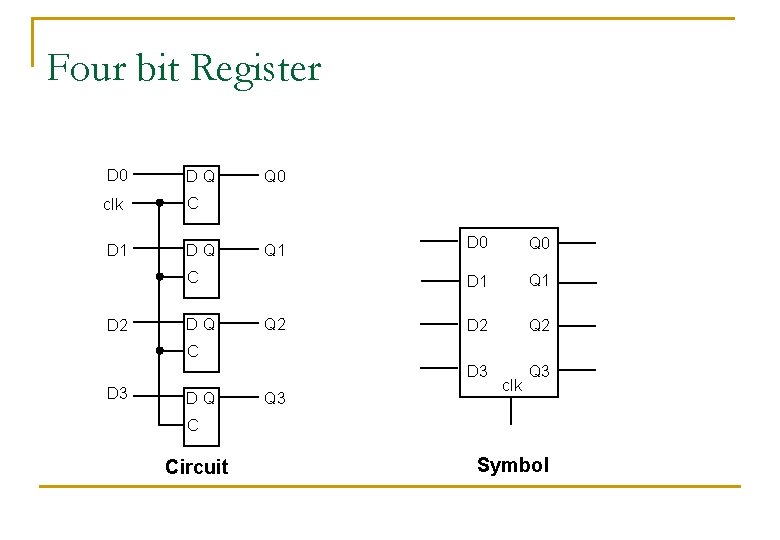

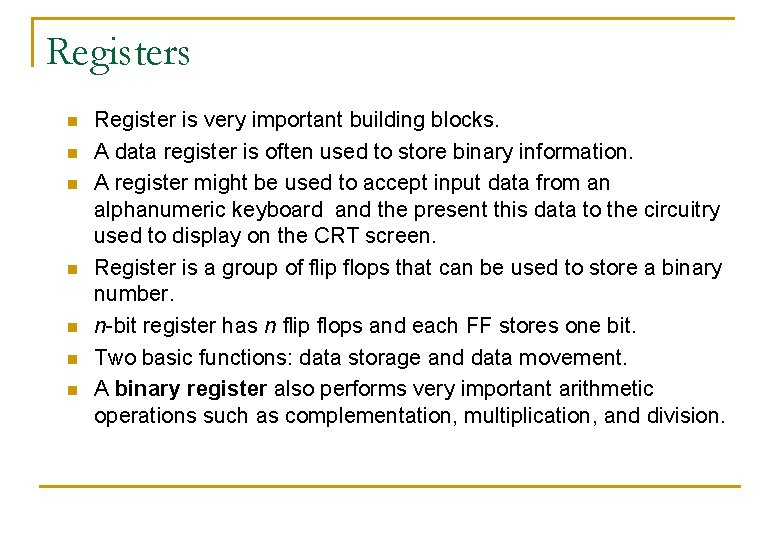

Four bit Register D 0 DQ clk C D 1 DQ Q 0 Q 1 C D 2 DQ Q 2 D 0 Q 0 D 1 Q 1 D 2 Q 2 C D 3 DQ Q 3 clk Q 3 C Circuit Symbol

Shift Registers n n A shift register can also be connected to form a number of different types of counters (count the clock pulses). The FF must be connected such that the binary number can be entered (shifted in) into the register and possibly shifted out. A group of flip flops connected to provide either shifted in or shifted out or both of these functions is called a shift register. In the shift register, binary number can be moved from one place to another in either of two ways: 1. Shifting the data 1 bit at a time in a serial fashion either from LSB or MSB. This technique is referred to as serial shifting. 2. Shifting all the data bits simultaneously which is referred to as parallel shifting.

Shift Registers n n Shift registers are a type of sequential logic circuit, mainly for storage of digital data. They are a group of flip-flops connected in a chain so that the output from one flip-flop becomes the input of the next flip-flop. All the flip-flops are driven by a common clock, and all are set or reset simultaneously. A shift register is a digital memory circuit found in calculators, computers, and data-processing system.

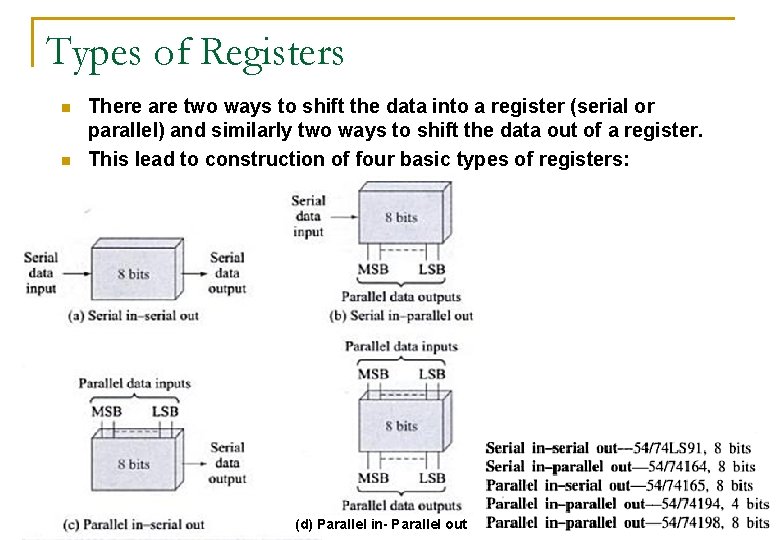

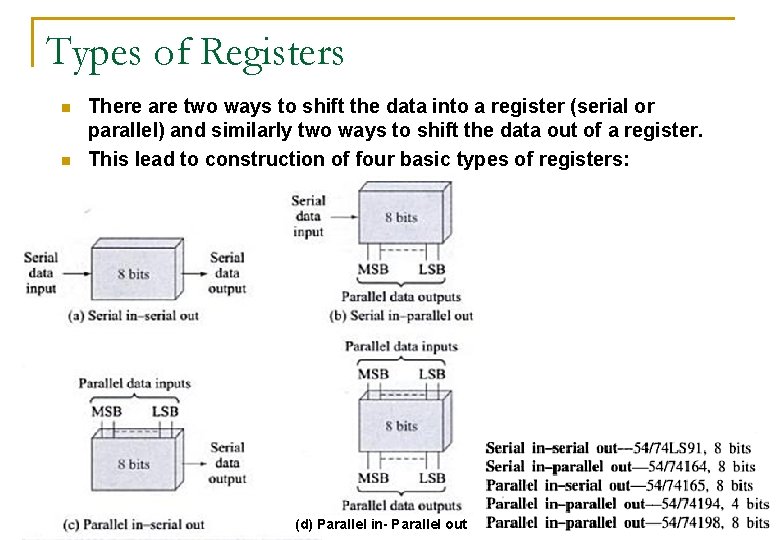

Types of Registers n n There are two ways to shift the data into a register (serial or parallel) and similarly two ways to shift the data out of a register. This lead to construction of four basic types of registers: (d) Parallel in- Parallel out

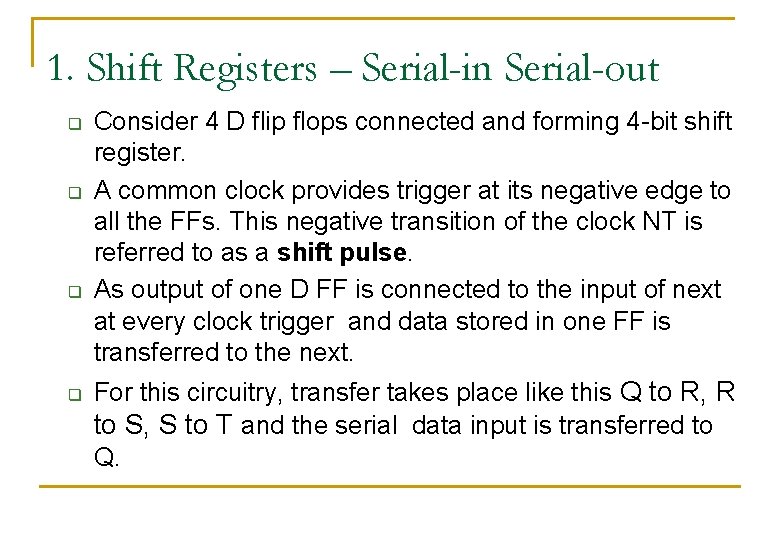

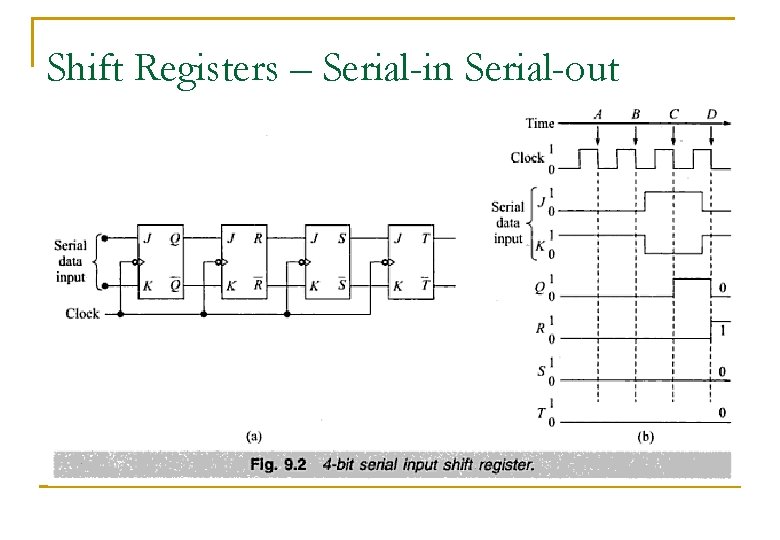

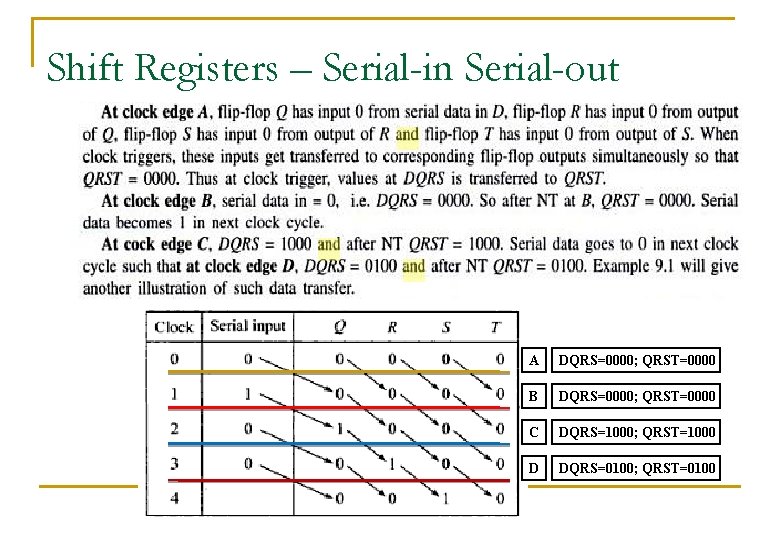

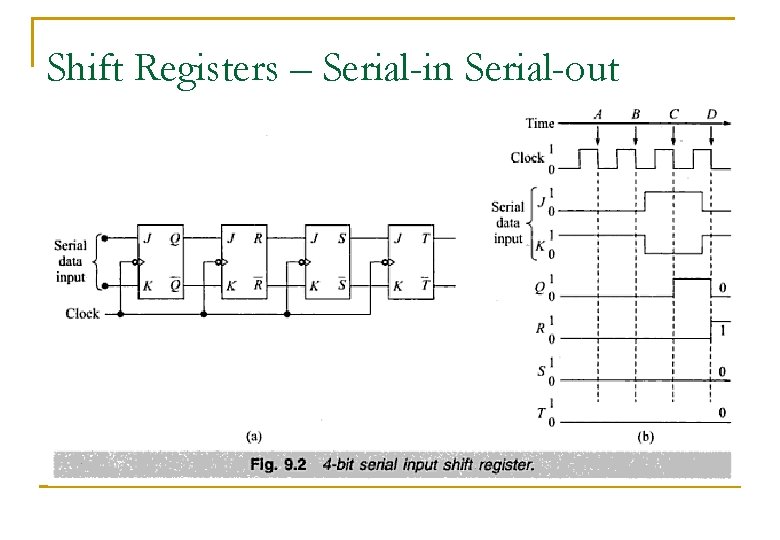

1. Shift Registers – Serial-in Serial-out q q Consider 4 D flip flops connected and forming 4 -bit shift register. A common clock provides trigger at its negative edge to all the FFs. This negative transition of the clock NT is referred to as a shift pulse. As output of one D FF is connected to the input of next at every clock trigger and data stored in one FF is transferred to the next. For this circuitry, transfer takes place like this Q to R, R to S, S to T and the serial data input is transferred to Q.

Shift Registers – Serial-in Serial-out

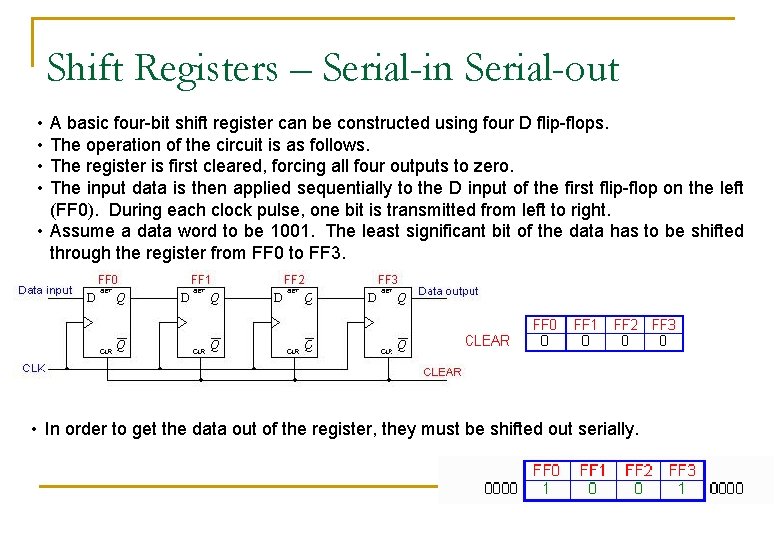

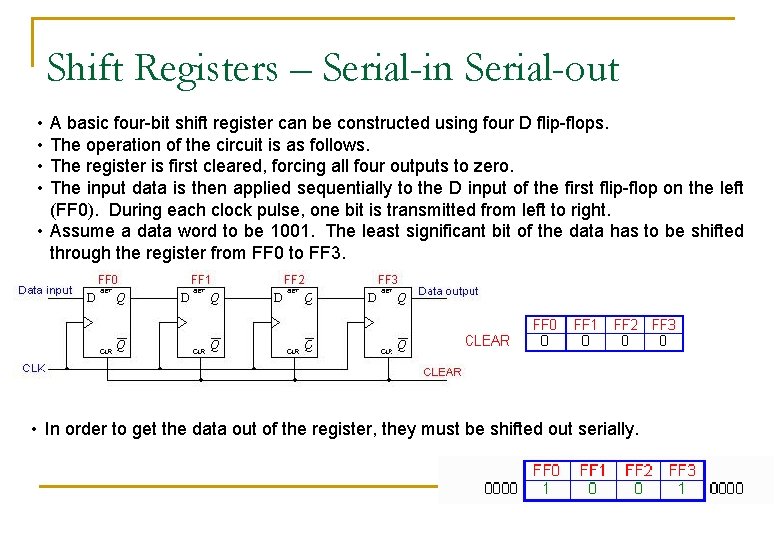

Shift Registers – Serial-in Serial-out • • A basic four-bit shift register can be constructed using four D flip-flops. The operation of the circuit is as follows. The register is first cleared, forcing all four outputs to zero. The input data is then applied sequentially to the D input of the first flip-flop on the left (FF 0). During each clock pulse, one bit is transmitted from left to right. • Assume a data word to be 1001. The least significant bit of the data has to be shifted through the register from FF 0 to FF 3. • In order to get the data out of the register, they must be shifted out serially.

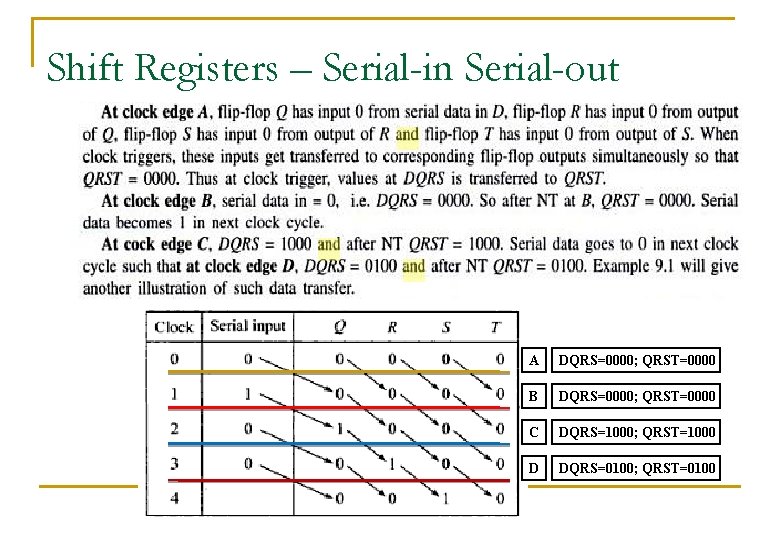

Shift Registers – Serial-in Serial-out A DQRS=0000; QRST=0000 B DQRS=0000; QRST=0000 C DQRS=1000; QRST=1000 D DQRS=0100; QRST=0100

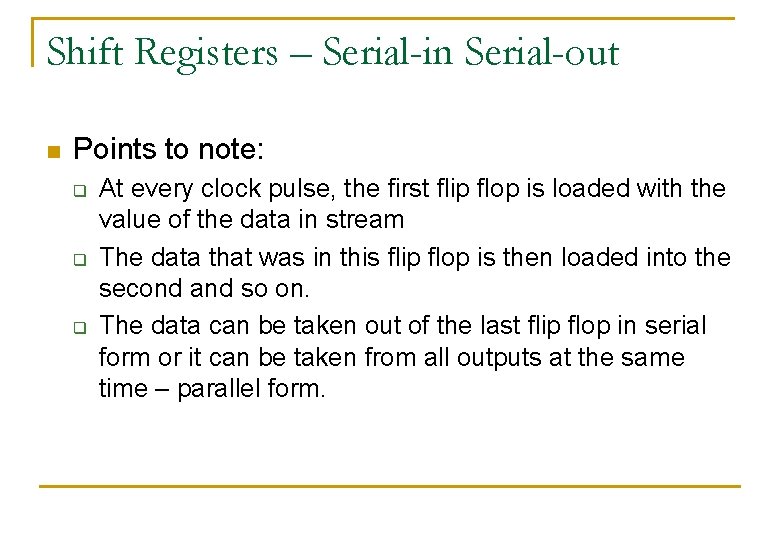

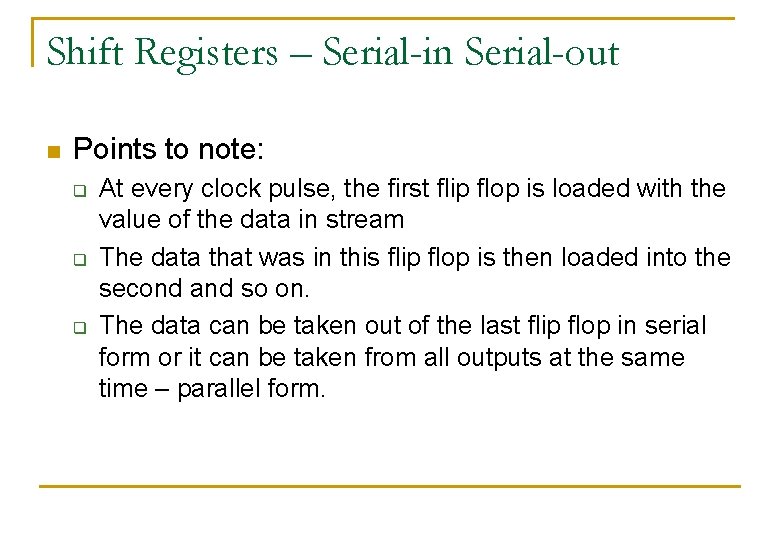

Shift Registers – Serial-in Serial-out n Points to note: q q q At every clock pulse, the first flip flop is loaded with the value of the data in stream The data that was in this flip flop is then loaded into the second and so on. The data can be taken out of the last flip flop in serial form or it can be taken from all outputs at the same time – parallel form.

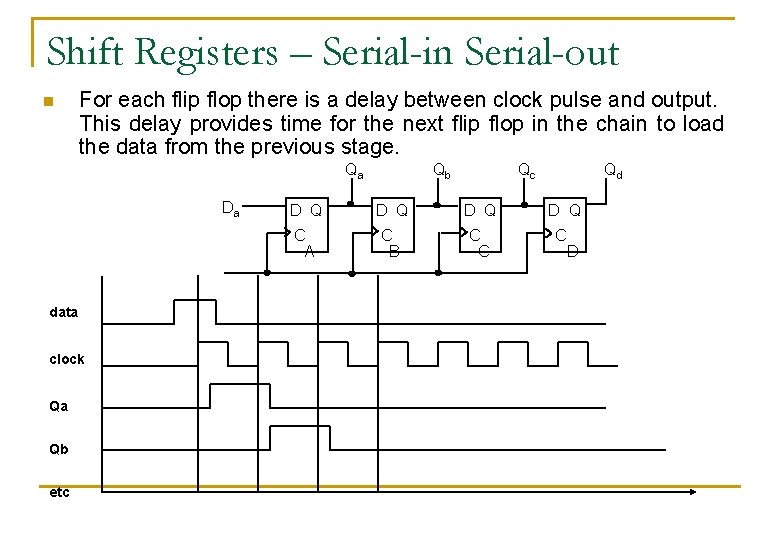

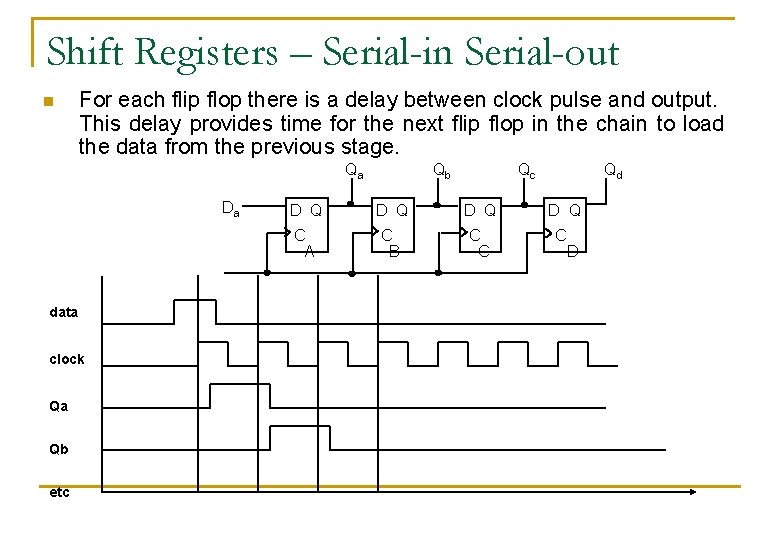

Shift Registers – Serial-in Serial-out n For each flip flop there is a delay between clock pulse and output. This delay provides time for the next flip flop in the chain to load the data from the previous stage. Qa Da data clock Qa Qb etc Qb Qc Qd D Q D Q C A C B C C C D

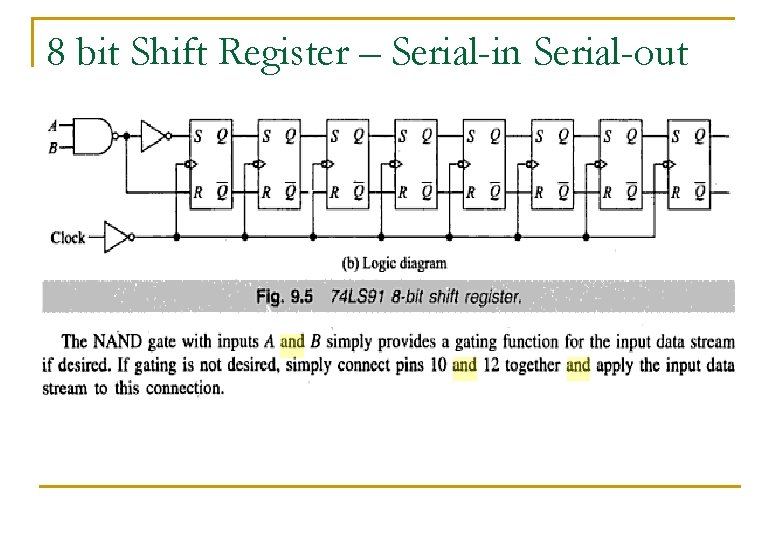

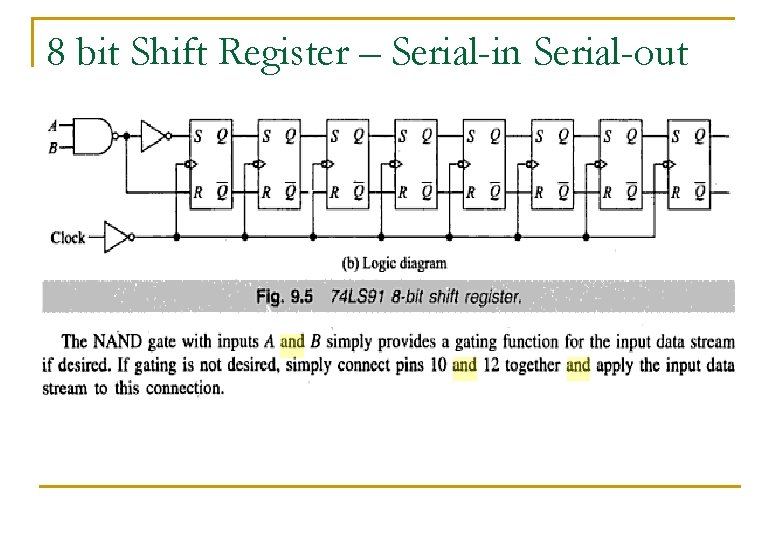

8 bit Shift Register – Serial-in Serial-out

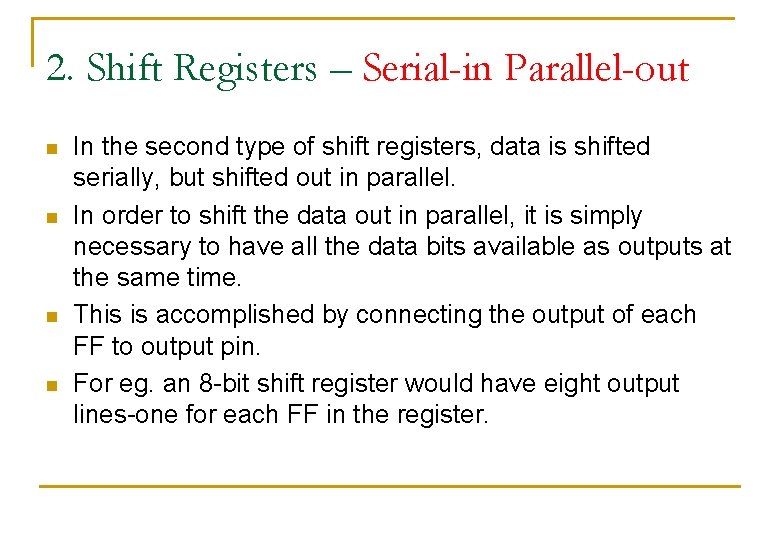

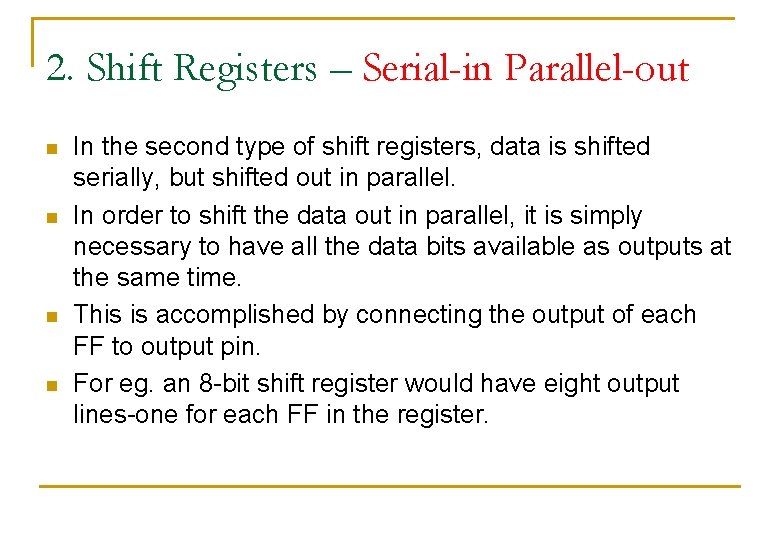

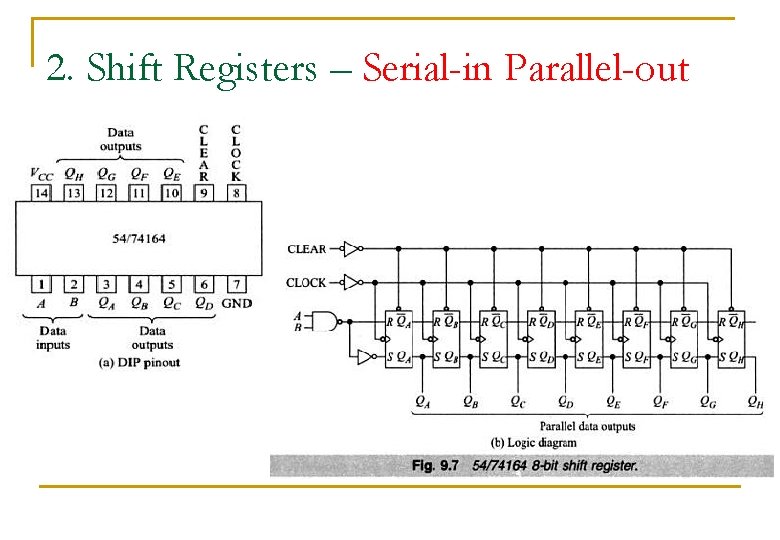

2. Shift Registers – Serial-in Parallel-out n n In the second type of shift registers, data is shifted serially, but shifted out in parallel. In order to shift the data out in parallel, it is simply necessary to have all the data bits available as outputs at the same time. This is accomplished by connecting the output of each FF to output pin. For eg. an 8 -bit shift register would have eight output lines-one for each FF in the register.

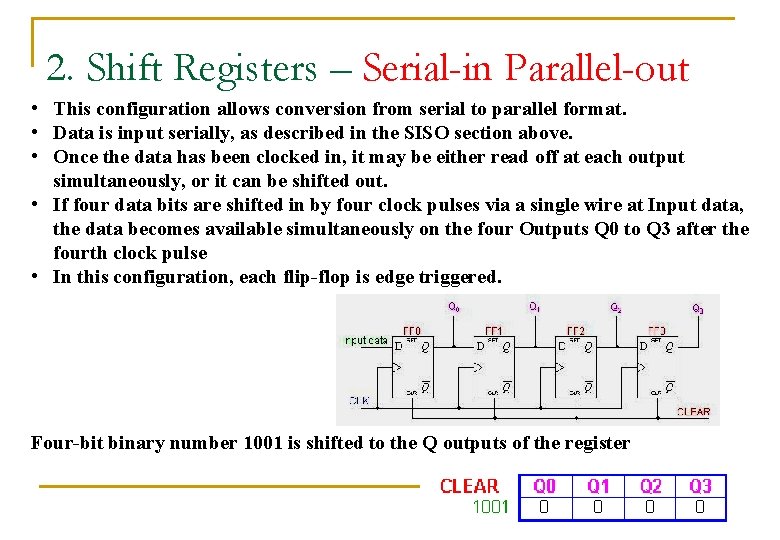

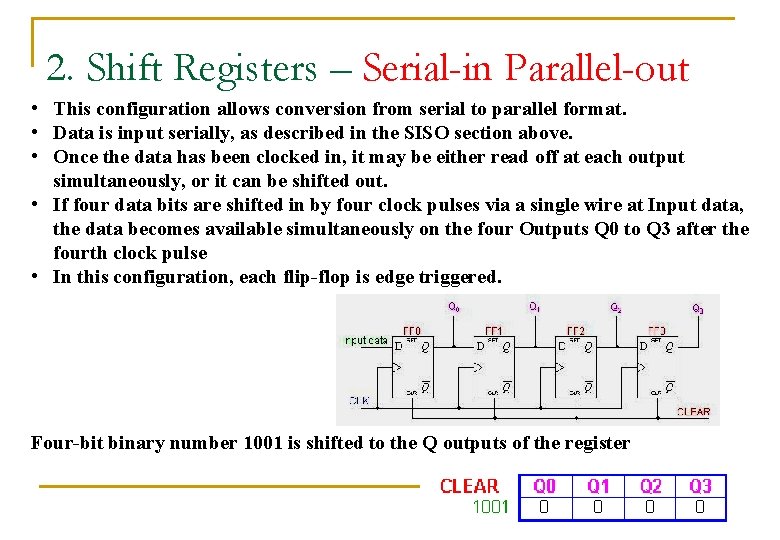

2. Shift Registers – Serial-in Parallel-out • This configuration allows conversion from serial to parallel format. • Data is input serially, as described in the SISO section above. • Once the data has been clocked in, it may be either read off at each output simultaneously, or it can be shifted out. • If four data bits are shifted in by four clock pulses via a single wire at Input data, the data becomes available simultaneously on the four Outputs Q 0 to Q 3 after the fourth clock pulse • In this configuration, each flip-flop is edge triggered. Four-bit binary number 1001 is shifted to the Q outputs of the register

2. Shift Registers – Serial-in Parallel-out

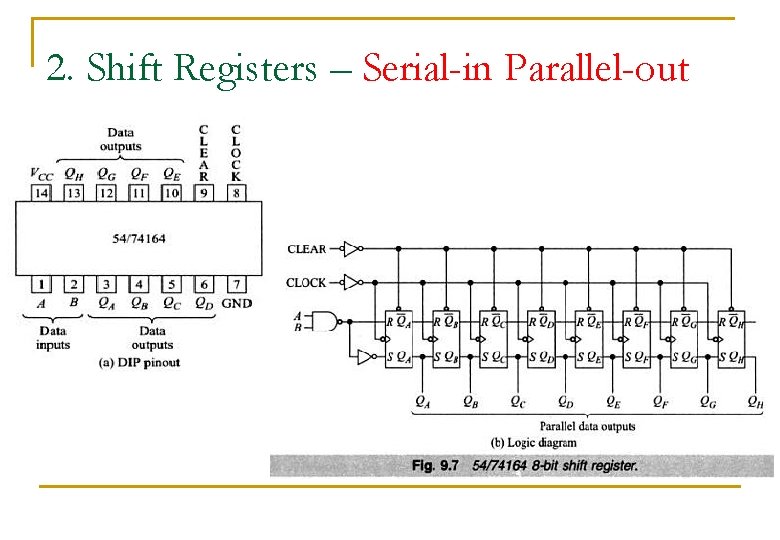

2. Shift Registers – Serial-in Parallel-out n n The Shift register 74 LS 91 is exactly similar to 54/74164 8 -bit register with 2 exceptions: Each FF is available as an output – all 8 bits of any number stored in the register are available simultaneously as an output (parallel data output). Each FF has an asynchronous clear input. Thus it is applied through amplifier and will reset (clear) every FF. Since It is an asynchronous signal, it can be applied at any time without regard to the clock waveform and this signal is level sensitive.

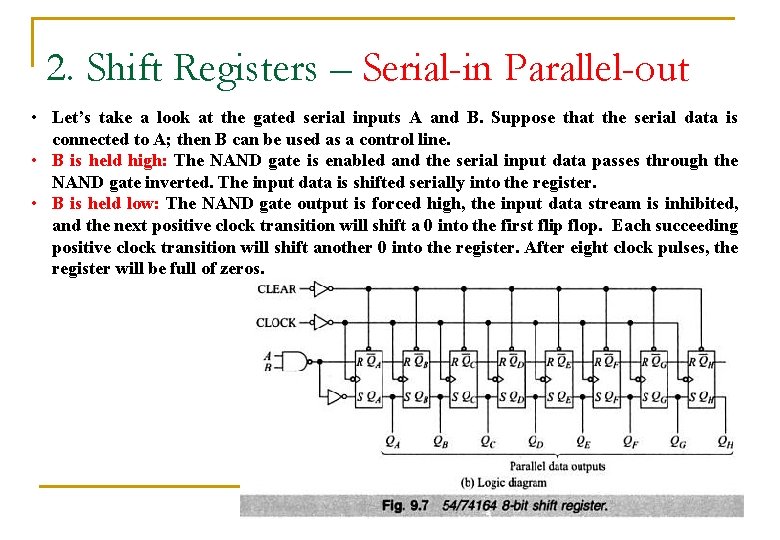

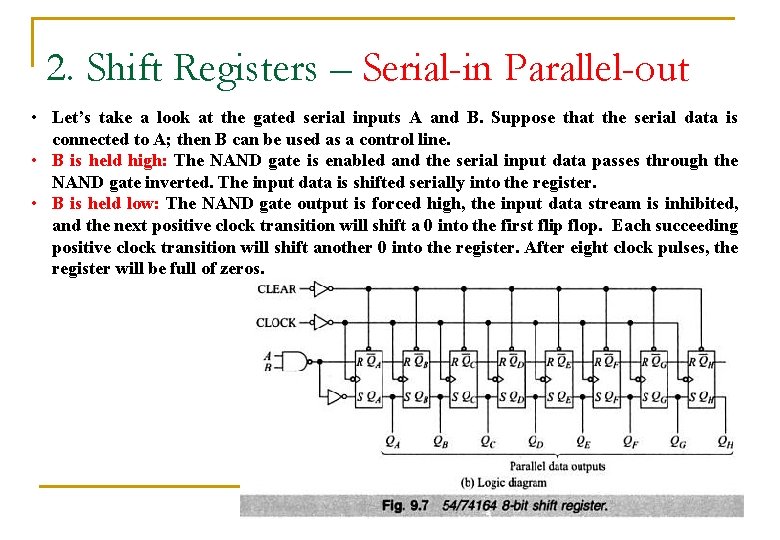

2. Shift Registers – Serial-in Parallel-out • Let’s take a look at the gated serial inputs A and B. Suppose that the serial data is connected to A; then B can be used as a control line. • B is held high: The NAND gate is enabled and the serial input data passes through the NAND gate inverted. The input data is shifted serially into the register. • B is held low: The NAND gate output is forced high, the input data stream is inhibited, and the next positive clock transition will shift a 0 into the first flip flop. Each succeeding positive clock transition will shift another 0 into the register. After eight clock pulses, the register will be full of zeros.

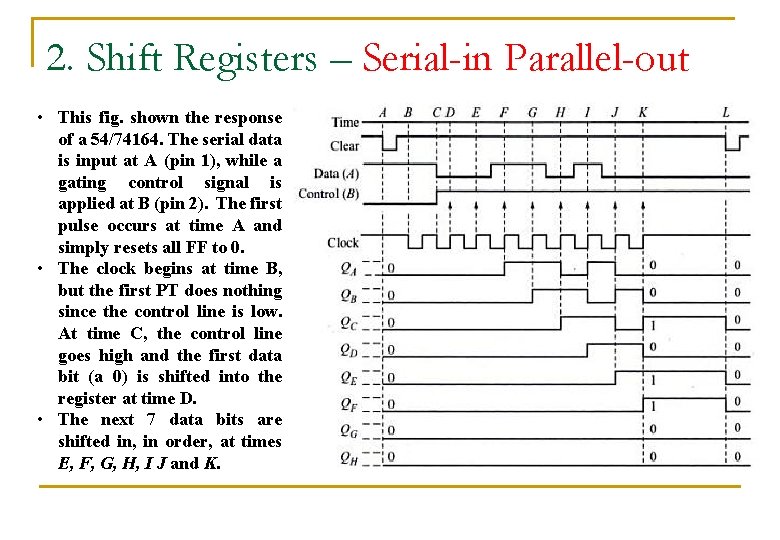

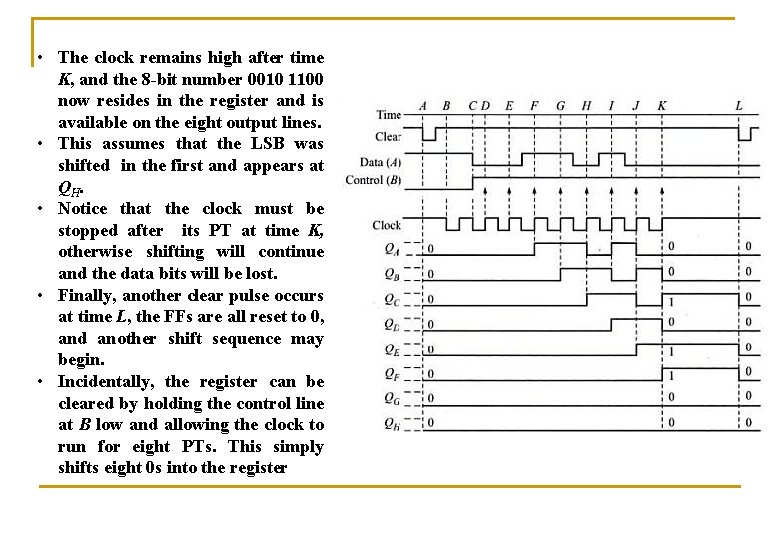

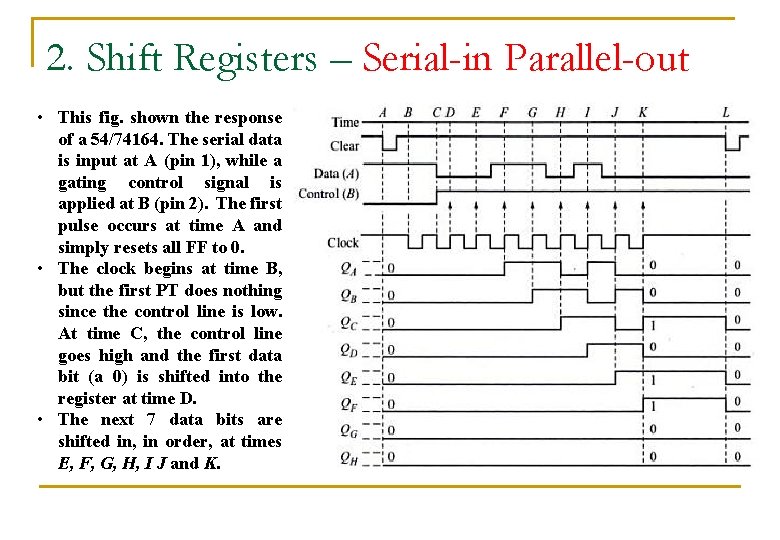

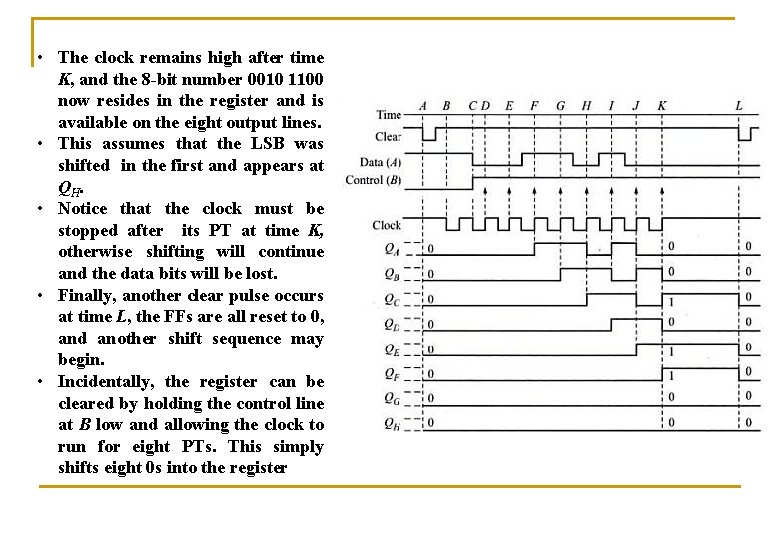

2. Shift Registers – Serial-in Parallel-out • This fig. shown the response of a 54/74164. The serial data is input at A (pin 1), while a gating control signal is applied at B (pin 2). The first pulse occurs at time A and simply resets all FF to 0. • The clock begins at time B, but the first PT does nothing since the control line is low. At time C, the control line goes high and the first data bit (a 0) is shifted into the register at time D. • The next 7 data bits are shifted in, in order, at times E, F, G, H, I J and K.

• The clock remains high after time K, and the 8 -bit number 0010 1100 now resides in the register and is available on the eight output lines. • This assumes that the LSB was shifted in the first and appears at QH. • Notice that the clock must be stopped after its PT at time K, otherwise shifting will continue and the data bits will be lost. • Finally, another clear pulse occurs at time L, the FFs are all reset to 0, and another shift sequence may begin. • Incidentally, the register can be cleared by holding the control line at B low and allowing the clock to run for eight PTs. This simply shifts eight 0 s into the register

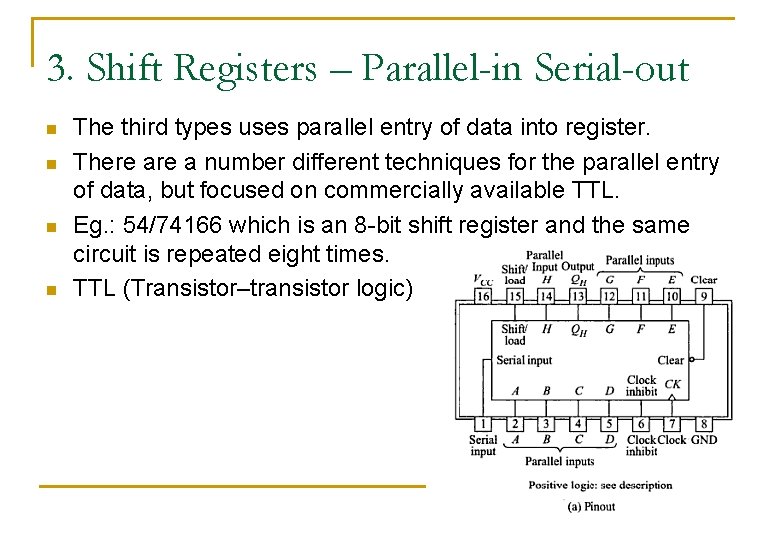

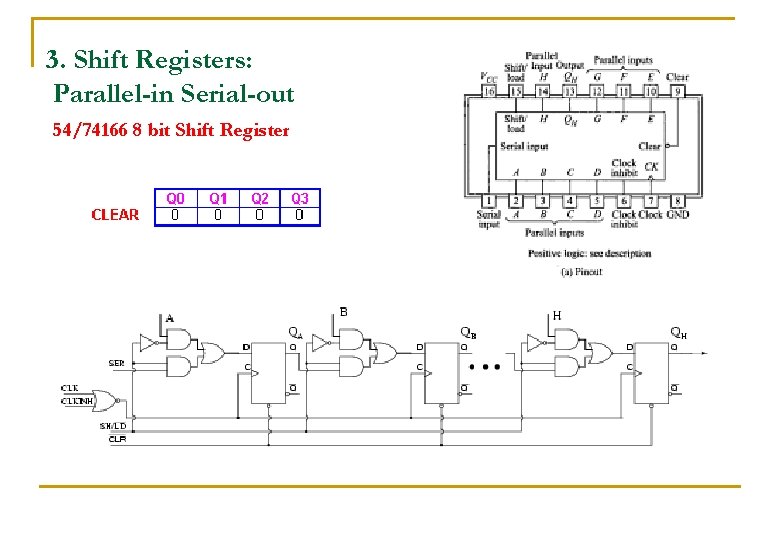

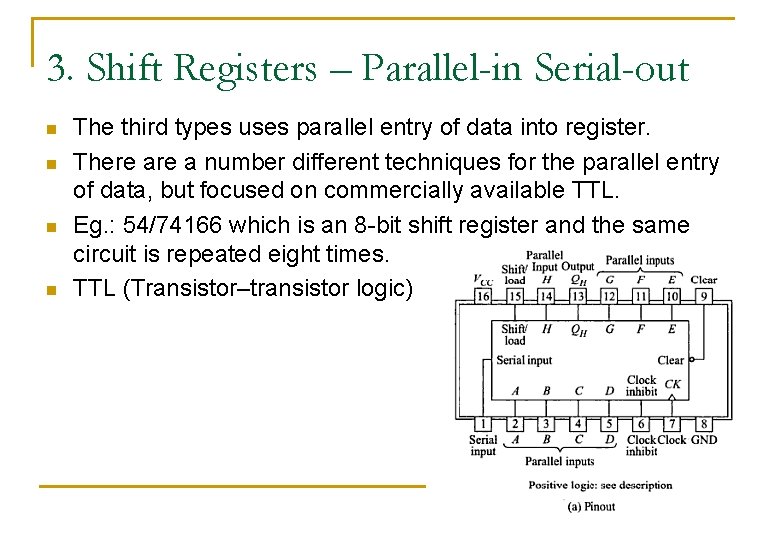

3. Shift Registers – Parallel-in Serial-out n n The third types uses parallel entry of data into register. There a number different techniques for the parallel entry of data, but focused on commercially available TTL. Eg. : 54/74166 which is an 8 -bit shift register and the same circuit is repeated eight times. TTL (Transistor–transistor logic)

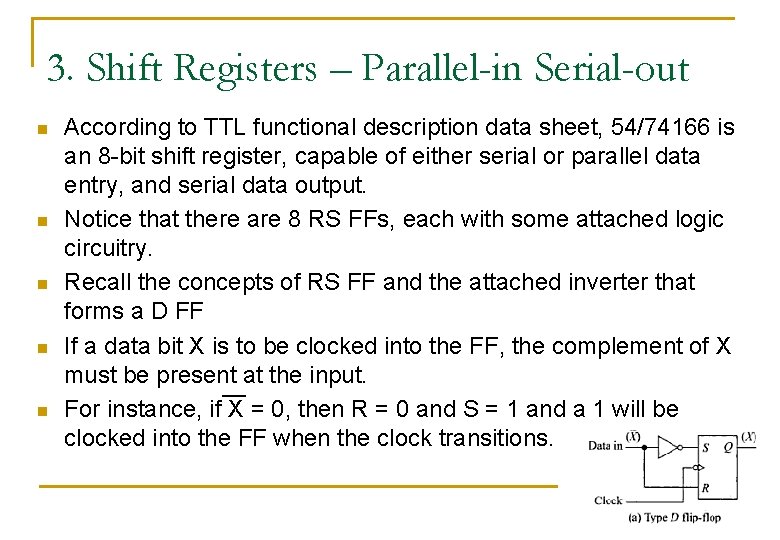

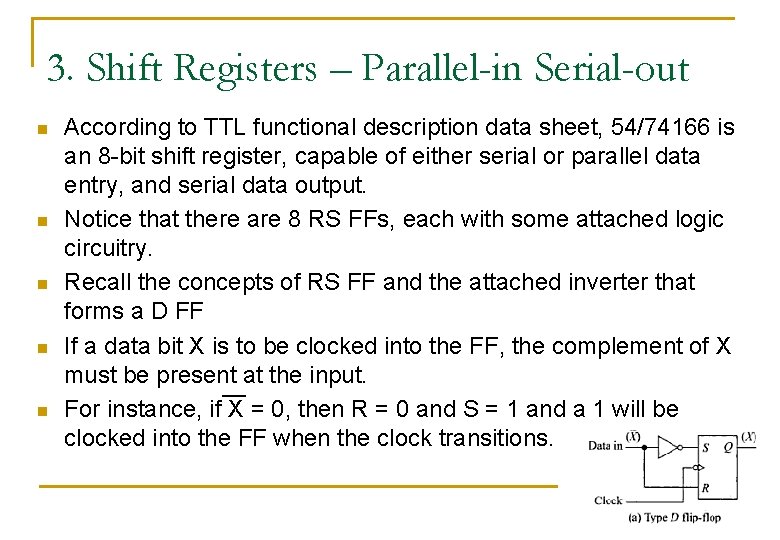

3. Shift Registers – Parallel-in Serial-out n n n According to TTL functional description data sheet, 54/74166 is an 8 -bit shift register, capable of either serial or parallel data entry, and serial data output. Notice that there are 8 RS FFs, each with some attached logic circuitry. Recall the concepts of RS FF and the attached inverter that forms a D FF If a data bit X is to be clocked into the FF, the complement of X must be present at the input. For instance, if X = 0, then R = 0 and S = 1 and a 1 will be clocked into the FF when the clock transitions.

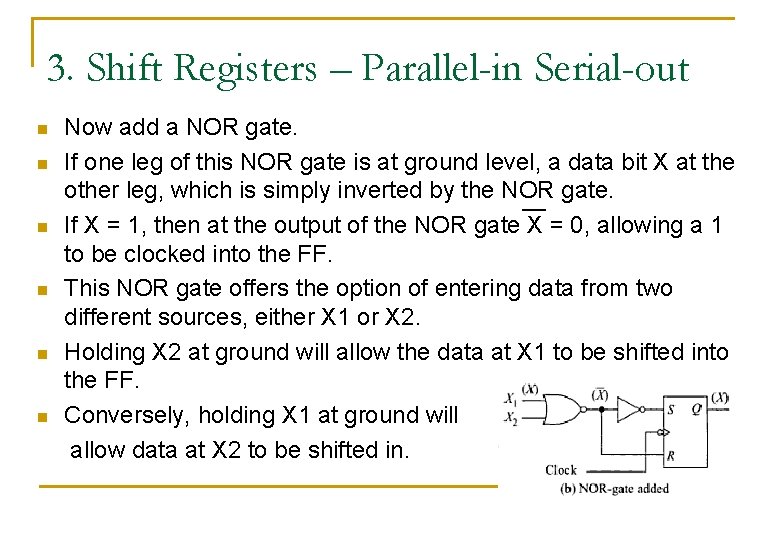

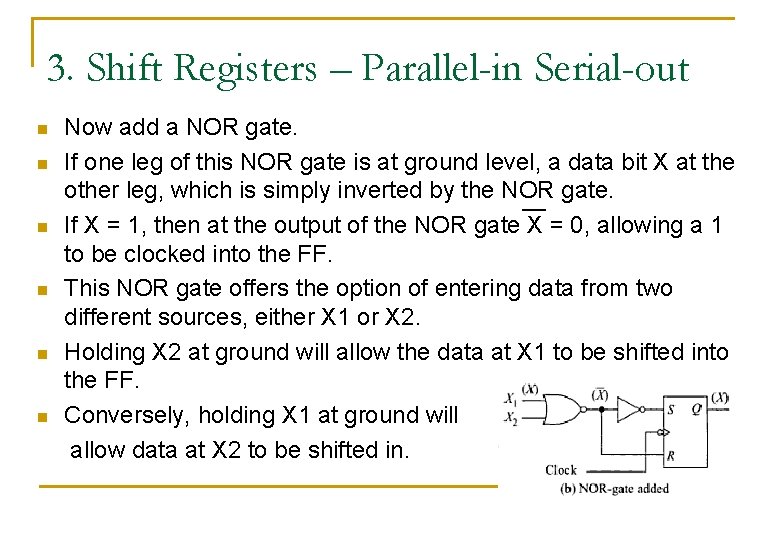

3. Shift Registers – Parallel-in Serial-out n n n Now add a NOR gate. If one leg of this NOR gate is at ground level, a data bit X at the other leg, which is simply inverted by the NOR gate. If X = 1, then at the output of the NOR gate X = 0, allowing a 1 to be clocked into the FF. This NOR gate offers the option of entering data from two different sources, either X 1 or X 2. Holding X 2 at ground will allow the data at X 1 to be shifted into the FF. Conversely, holding X 1 at ground will allow data at X 2 to be shifted in.

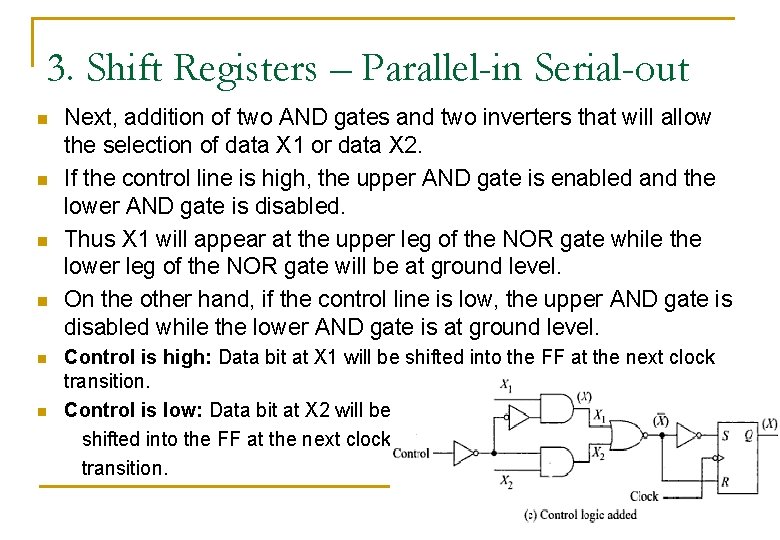

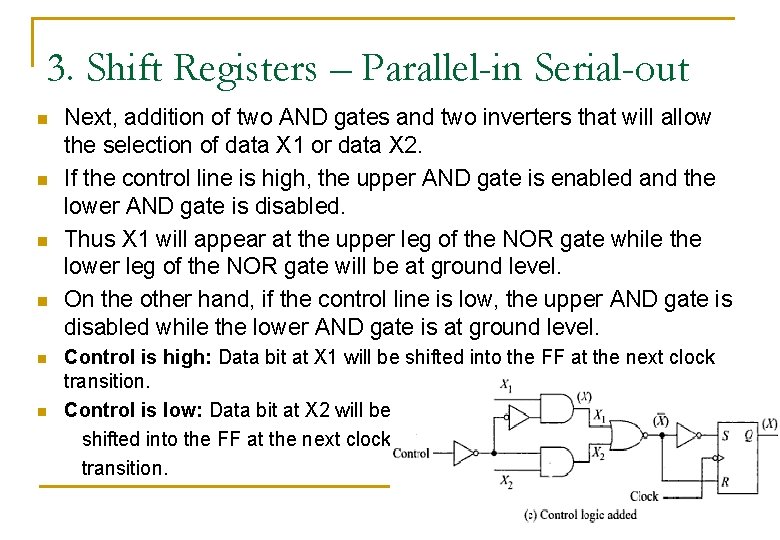

3. Shift Registers – Parallel-in Serial-out n n n Next, addition of two AND gates and two inverters that will allow the selection of data X 1 or data X 2. If the control line is high, the upper AND gate is enabled and the lower AND gate is disabled. Thus X 1 will appear at the upper leg of the NOR gate while the lower leg of the NOR gate will be at ground level. On the other hand, if the control line is low, the upper AND gate is disabled while the lower AND gate is at ground level. Control is high: Data bit at X 1 will be shifted into the FF at the next clock transition. Control is low: Data bit at X 2 will be shifted into the FF at the next clock transition.

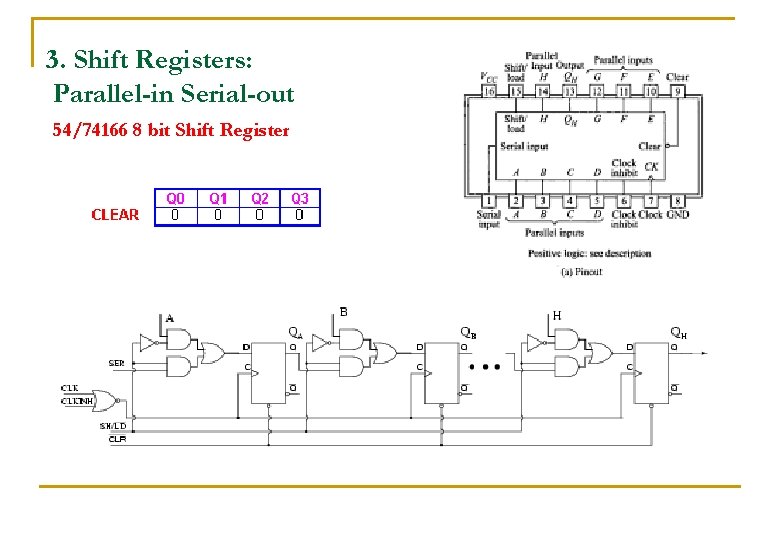

3. Shift Registers: Parallel-in Serial-out 54/74166 8 bit Shift Register

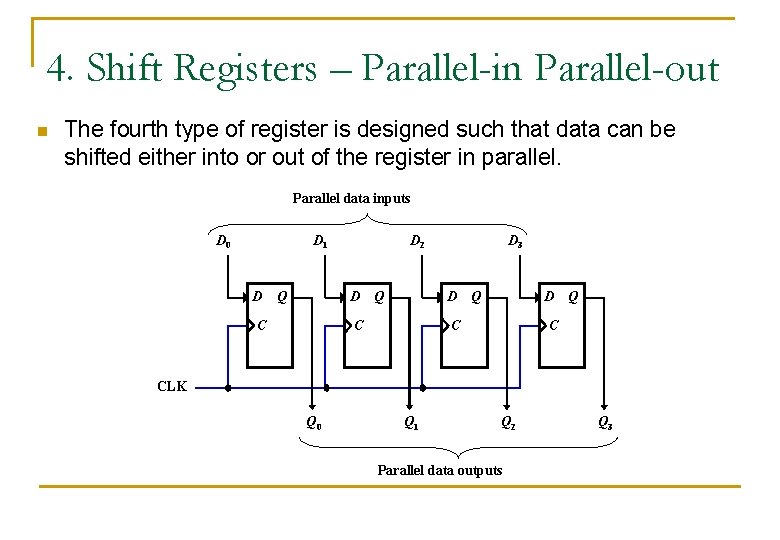

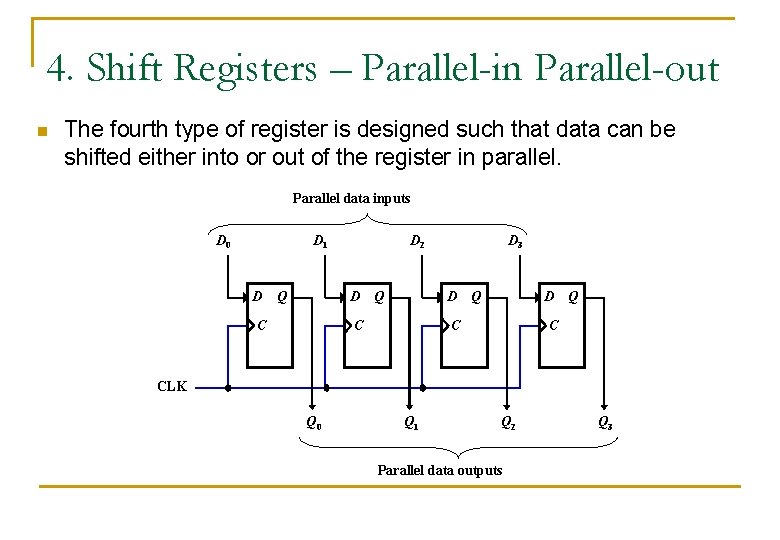

4. Shift Registers – Parallel-in Parallel-out n The fourth type of register is designed such that data can be shifted either into or out of the register in parallel. Parallel data inputs D 0 D 1 D D 2 D Q C D 3 D Q C Q C CLK Q 0 Q 1 Q 2 Parallel data outputs Q 3

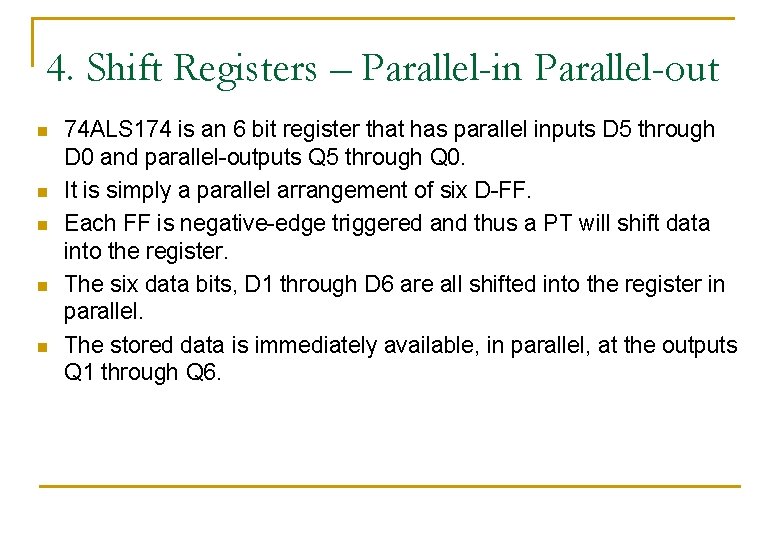

4. Shift Registers – Parallel-in Parallel-out n n n 74 ALS 174 is an 6 bit register that has parallel inputs D 5 through D 0 and parallel-outputs Q 5 through Q 0. It is simply a parallel arrangement of six D-FF. Each FF is negative-edge triggered and thus a PT will shift data into the register. The six data bits, D 1 through D 6 are all shifted into the register in parallel. The stored data is immediately available, in parallel, at the outputs Q 1 through Q 6.

4. Shift Registers – Parallel-in Parallel-out

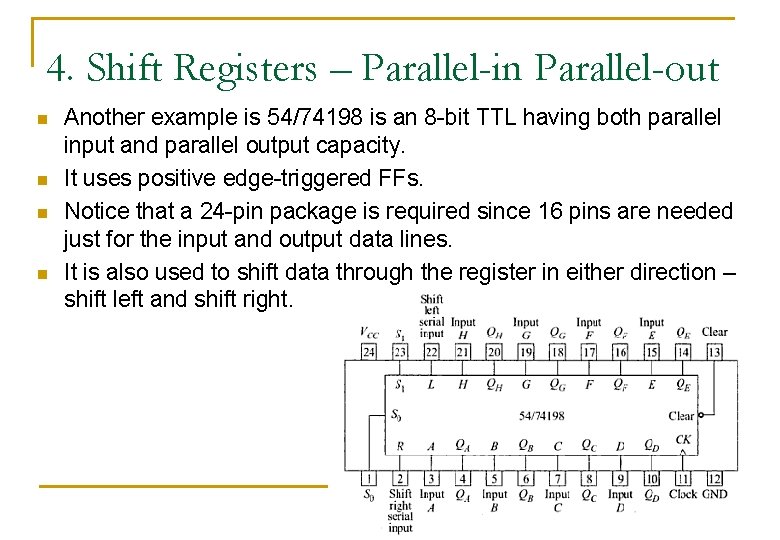

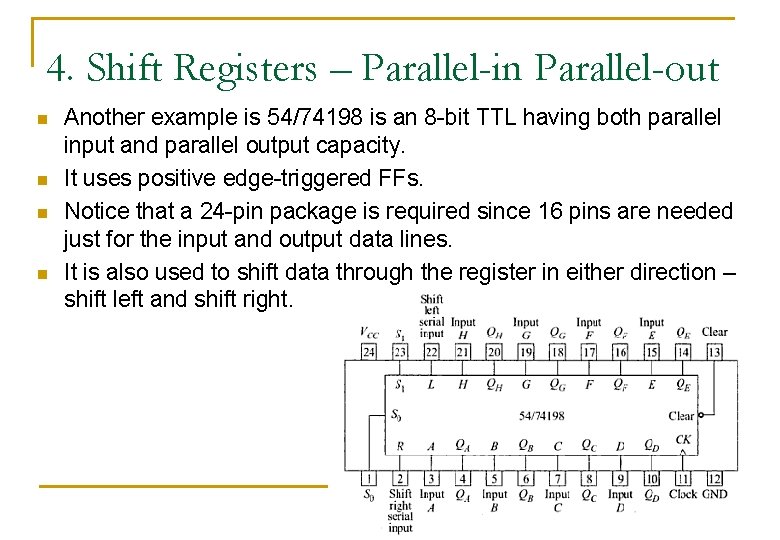

4. Shift Registers – Parallel-in Parallel-out n n Another example is 54/74198 is an 8 -bit TTL having both parallel input and parallel output capacity. It uses positive edge-triggered FFs. Notice that a 24 -pin package is required since 16 pins are needed just for the input and output data lines. It is also used to shift data through the register in either direction – shift left and shift right.

4. Shift Registers – Parallel-in Parallel-out n n Since this register is used to store the data, it is referred to as data register or data latch. Notice that it is not possible to shift stored data either to the right or to the left. A low level at the clear input will immediately reset all FFs low. The clear input is asynchronous – it can be done at any time and it takes precedence over all other inputs.

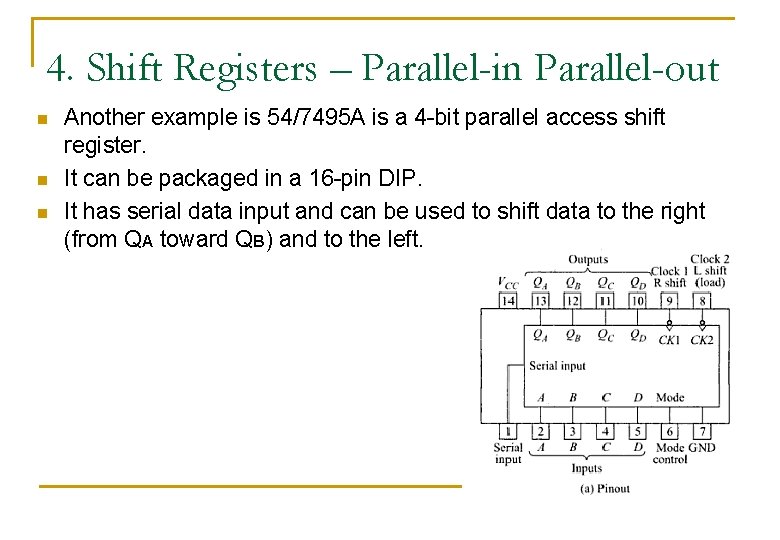

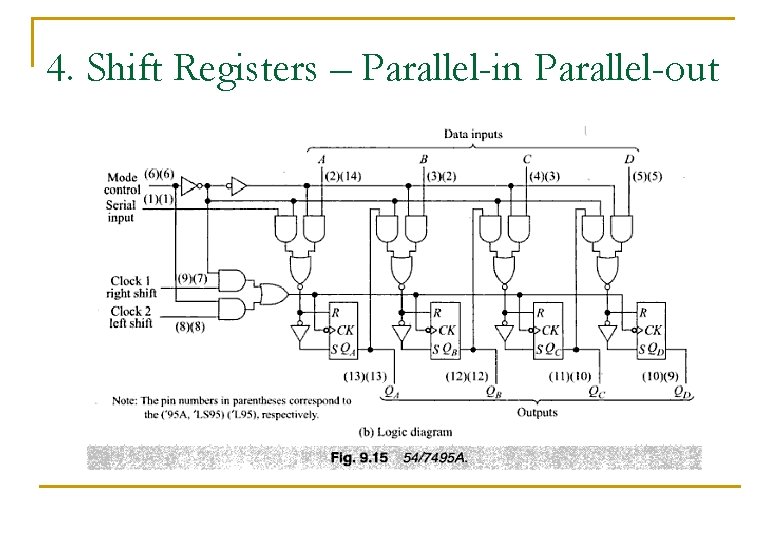

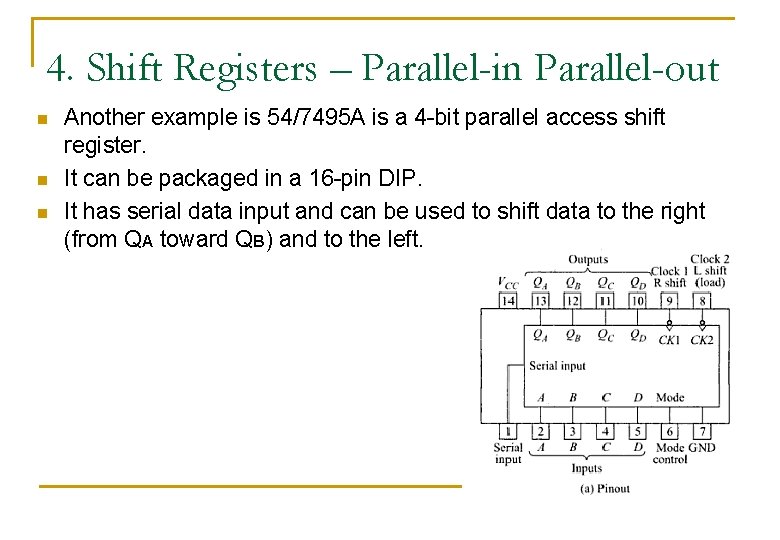

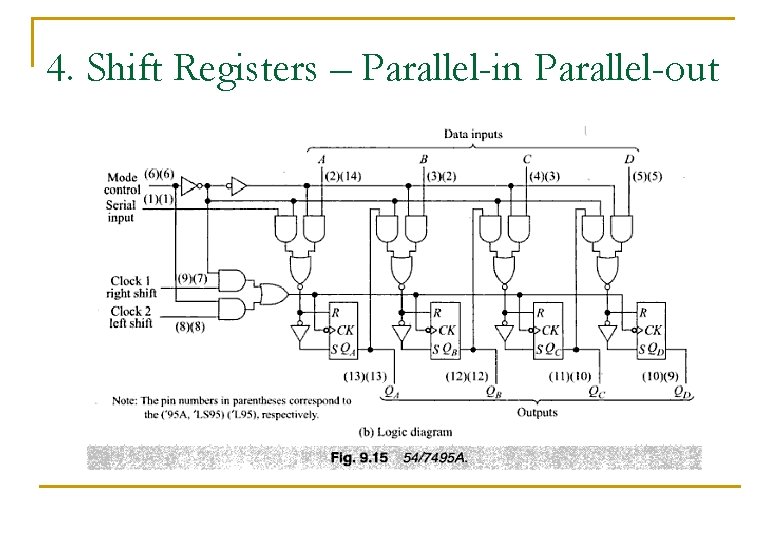

4. Shift Registers – Parallel-in Parallel-out n n n Another example is 54/7495 A is a 4 -bit parallel access shift register. It can be packaged in a 16 -pin DIP. It has serial data input and can be used to shift data to the right (from QA toward QB) and to the left.

4. Shift Registers – Parallel-in Parallel-out

Registers/Shift registers n Summary q Registers consist of a group of D-type latches or flip-flops which are clocked simultaneously to store a binary word n q set-up and hold times must be observed Shift registers allow data to be moved from one bit position to another n used for parallel «serial conversion and some types of arithmetic operations