Chapter 6 Registers and Counters Registers Register and

- Slides: 28

Chapter 6 Registers and Counters

Registers • Register and counter logic circuits contain flipflops • A “register” is a group of flip-flops , each one is capable of storing “ 1 bit” of information • A n-bit register consists of a group of n flipflops capable of storing n bits of binary information. • A “counter” is a register that goes through a sequence of binary states

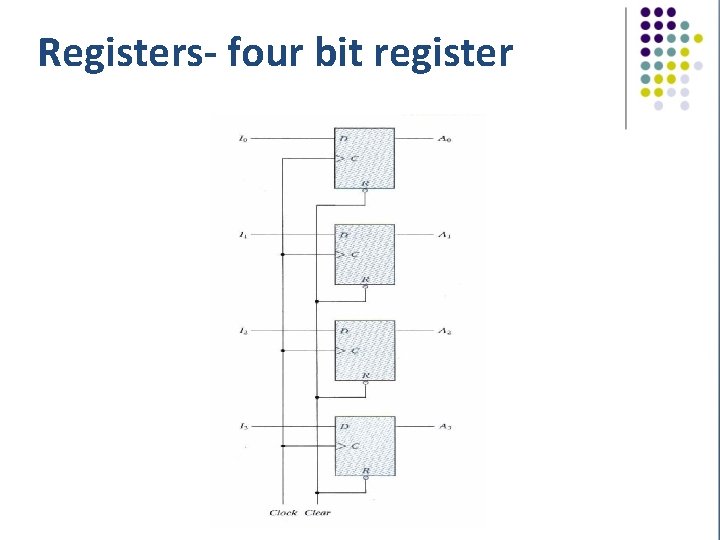

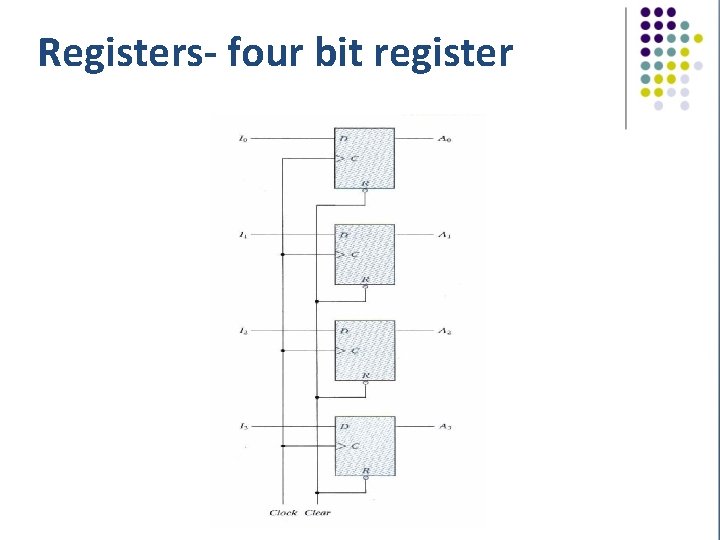

Registers- four bit register

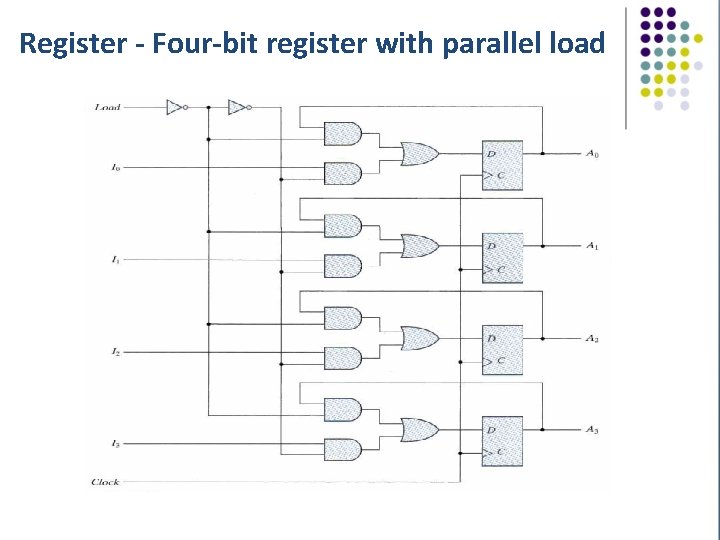

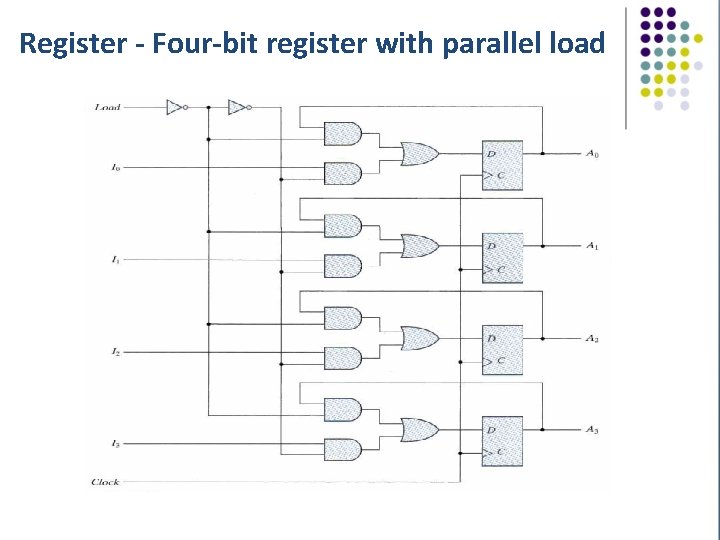

Register - Four-bit register with parallel load • Additional gates implement 2 -channel mux • Data is always transfer at positive clock pulse • When “Load-input” is “ 1” , the data from inputs transfer to registers • When “Load-input” is “ 0” , the flip-flop output (present state) transfer to register and implement “no change” condition

Register - Four-bit register with parallel load

Shift registers • Shifting of binary information from one cell to its neighboring cell , is called “shift register” • The output of one flip-flop is connected to input of next flip-flop • All flip-flop receive common clock pulses, which shift the data from one stage to the next

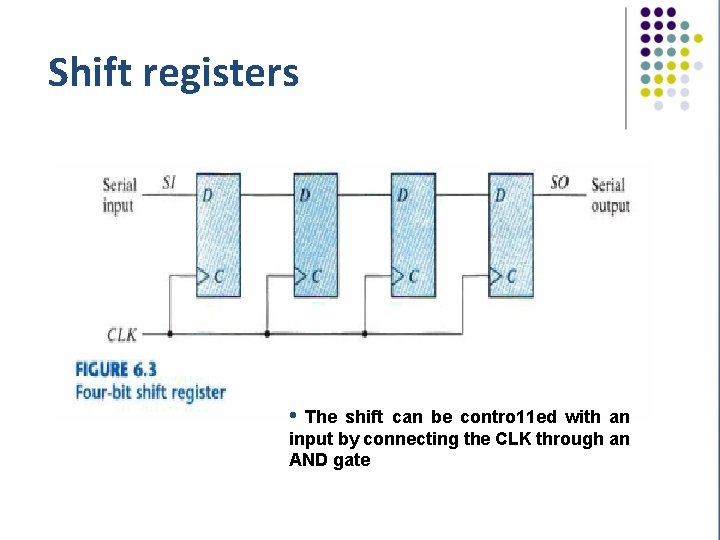

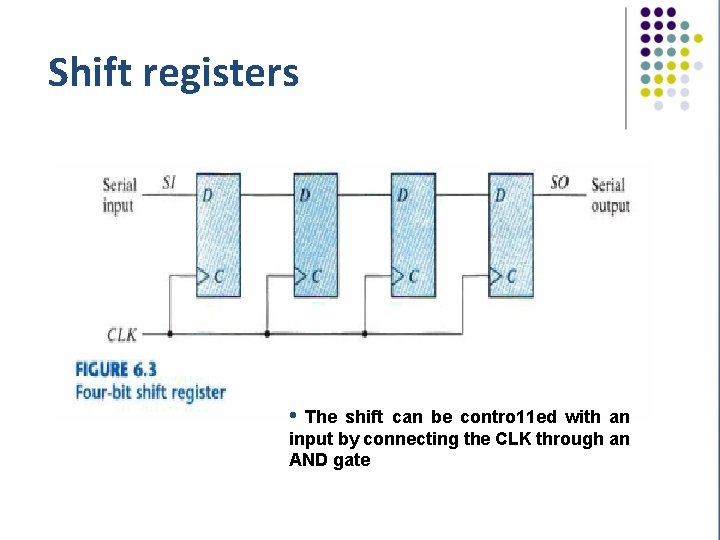

Shift registers • The shift can be contro 11 ed with an input by connecting the CLK through an AND gate

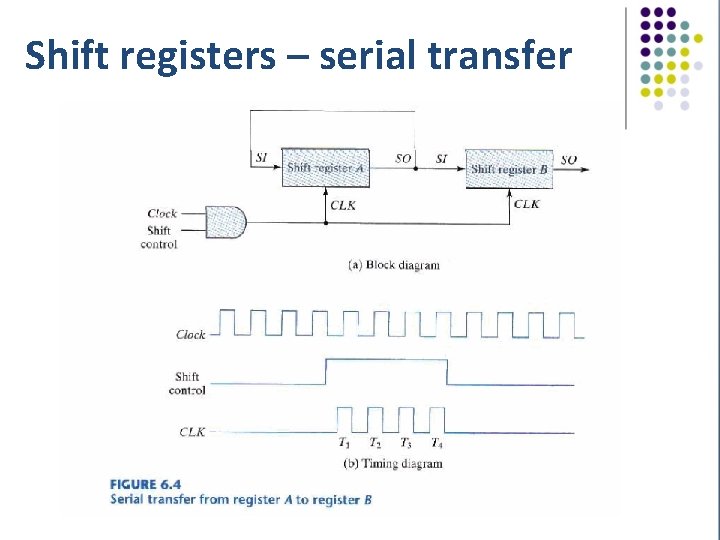

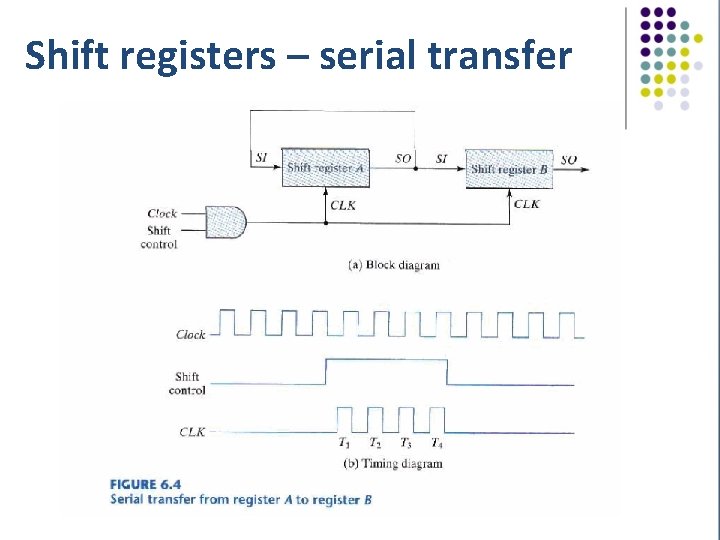

Shift registers – serial transfer • The “serial - mode”, transfer and manipulate one bit information at a time • The “parallel – mode”, information is available from all bits of a register and all bits can be transferred simultaneously during one clock pulse

Shift registers – serial transfer

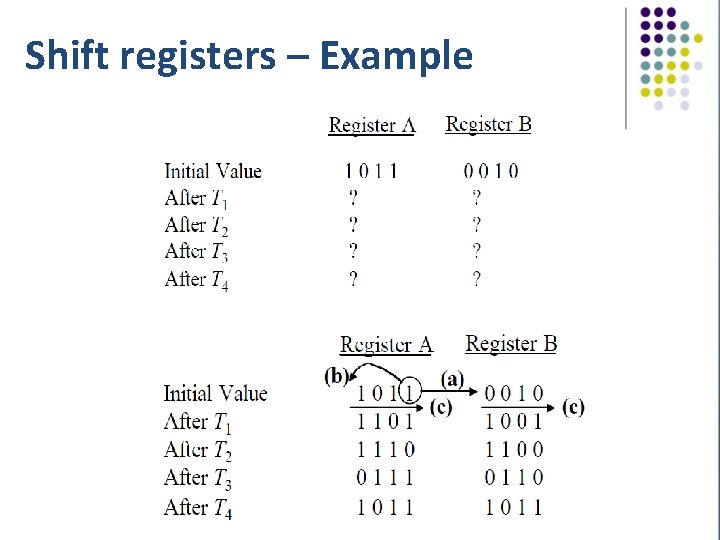

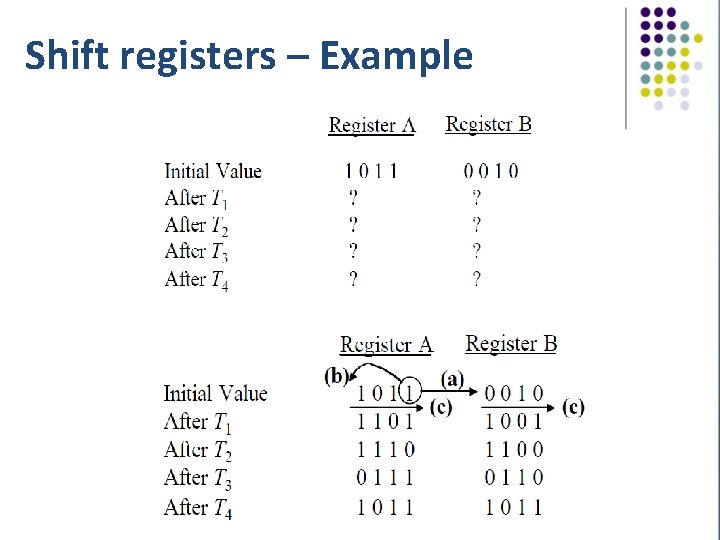

Shift registers – Example

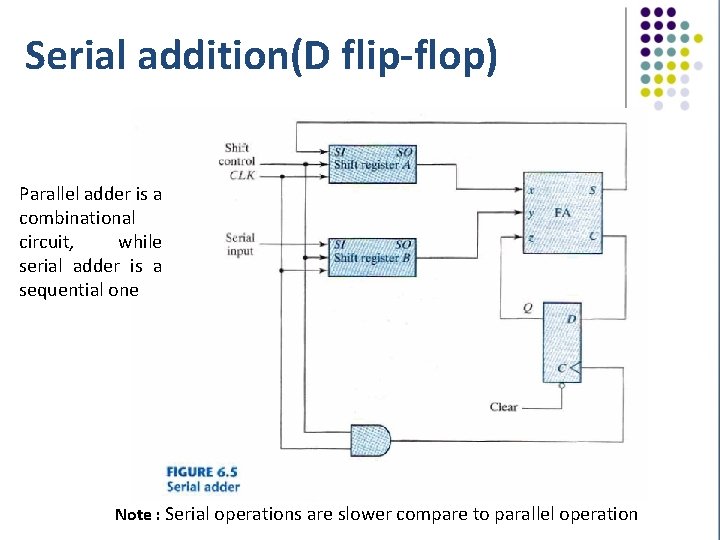

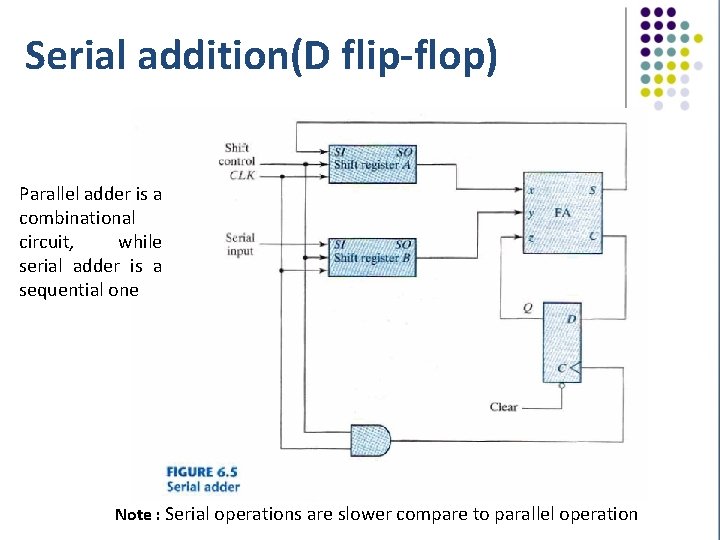

Serial addition(D flip-flop) Parallel adder is a combinational circuit, while serial adder is a sequential one Note : Serial operations are slower compare to parallel operation

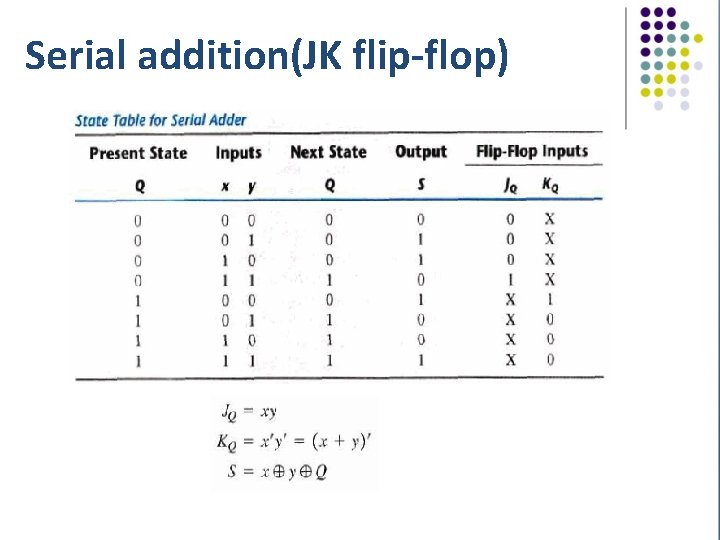

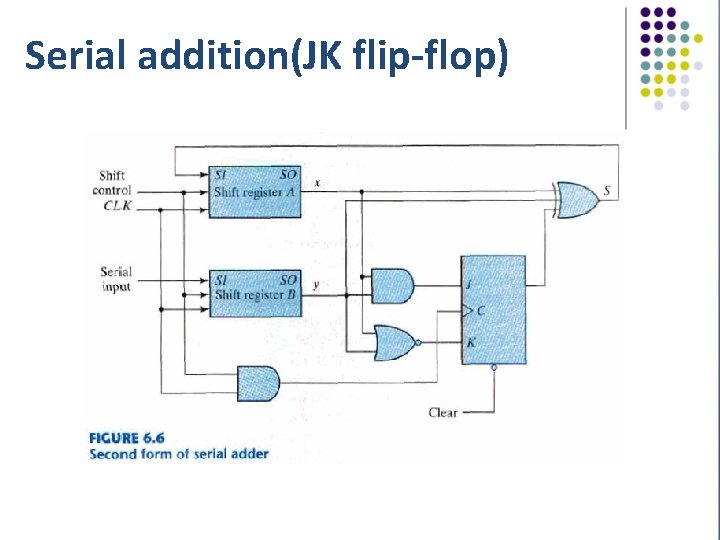

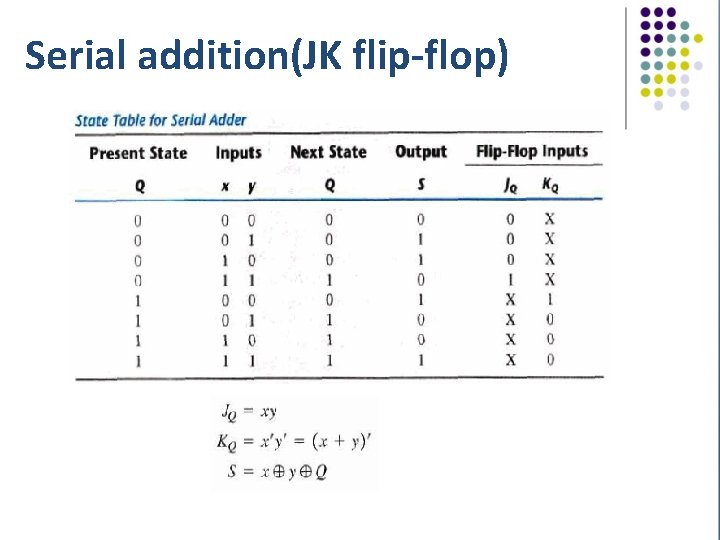

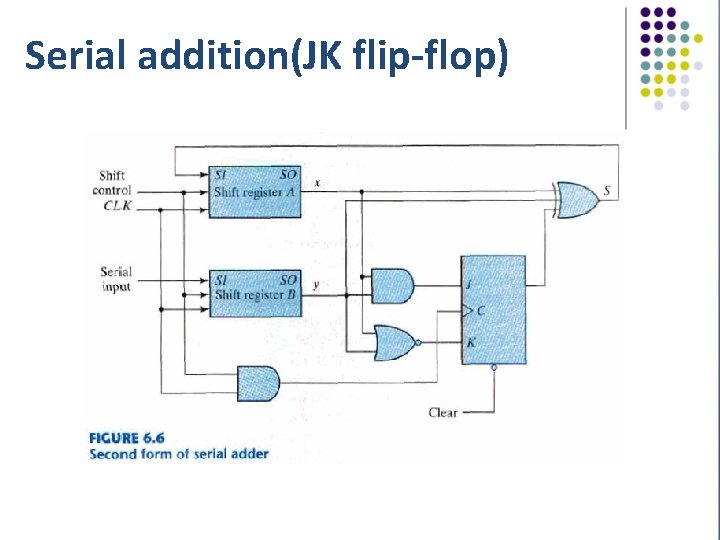

Serial addition(JK flip-flop)

Serial addition(JK flip-flop)

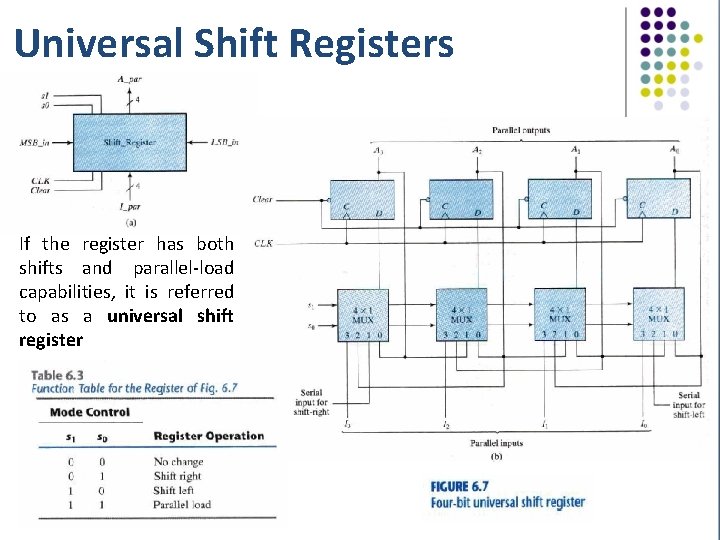

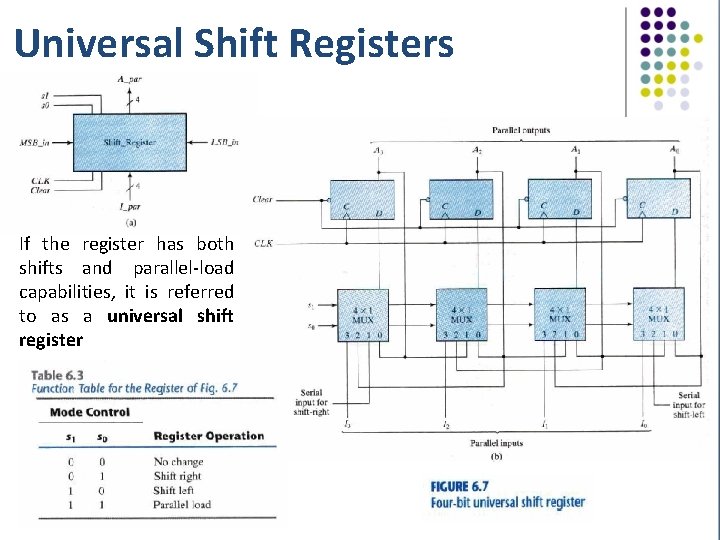

Universal Shift Registers The general shift registers have following capabilities: • A clear control to clear the register to 0 • A clock input to synchronize the operation • A shift-right control to enable the shift-right operation • A shift-left control to enable the shift-left operation • A parallel-load control enable, n-input lines associated with the parallel transfer • n parallel output lines • A control state , that leaves the information unchanged

Universal Shift Registers If the register has both shifts and parallel-load capabilities, it is referred to as a universal shift register

Ripple Counters • A register that goes through sequence of states upon application of input pulses is called a “Counter” • A counter that follows the binary number sequence is called a binary counter • A n-bit binary counter consists of n flipflops and counts from 0 through 2ⁿ -1 • Counter are divided into two categories, • Ripple counters • Synchronous counters

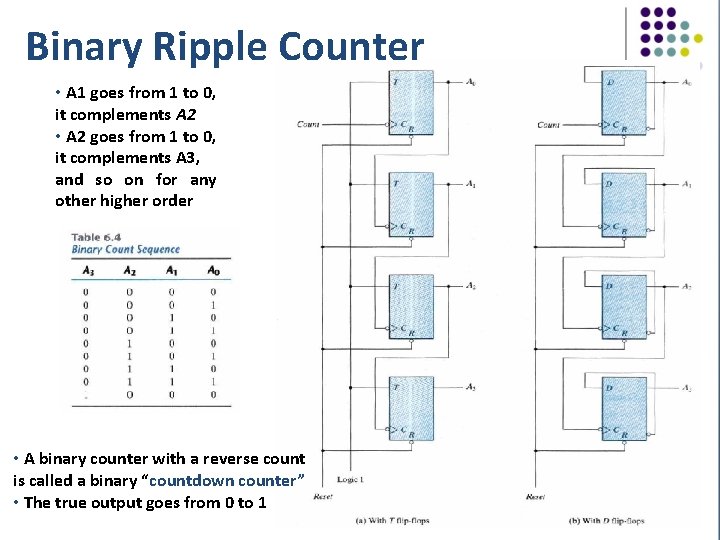

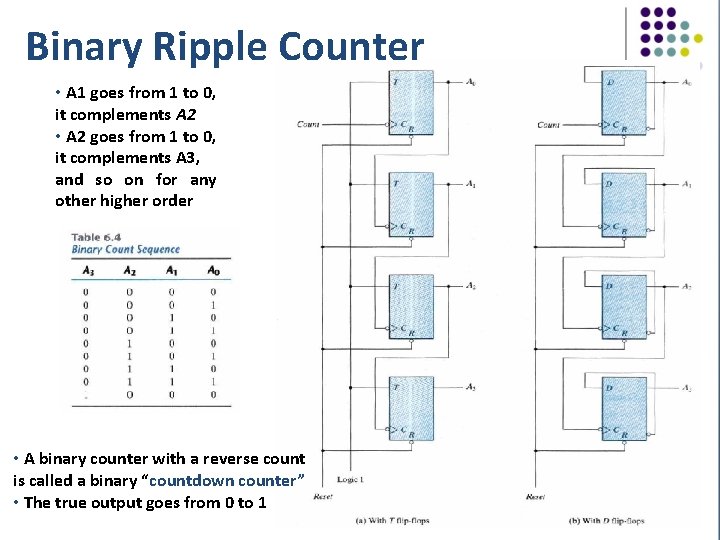

Binary Ripple Counter • A 1 goes from 1 to 0, it complements A 2 • A 2 goes from 1 to 0, it complements A 3, and so on for any other higher order • A binary counter with a reverse count is called a binary “countdown counter” • The true output goes from 0 to 1

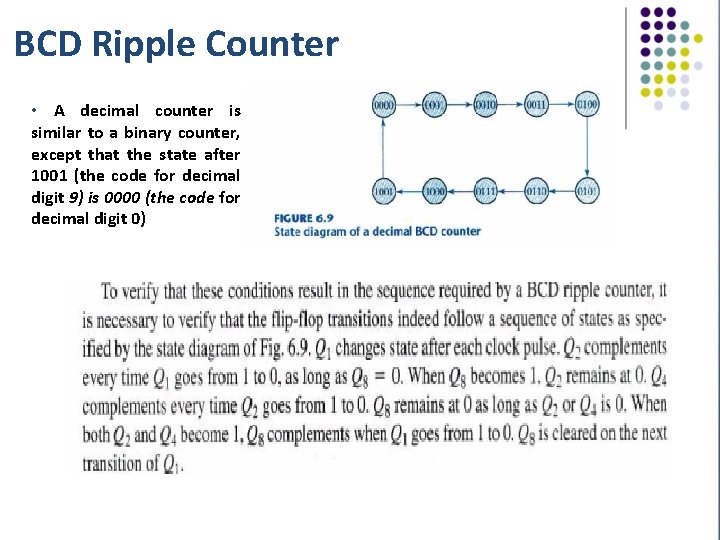

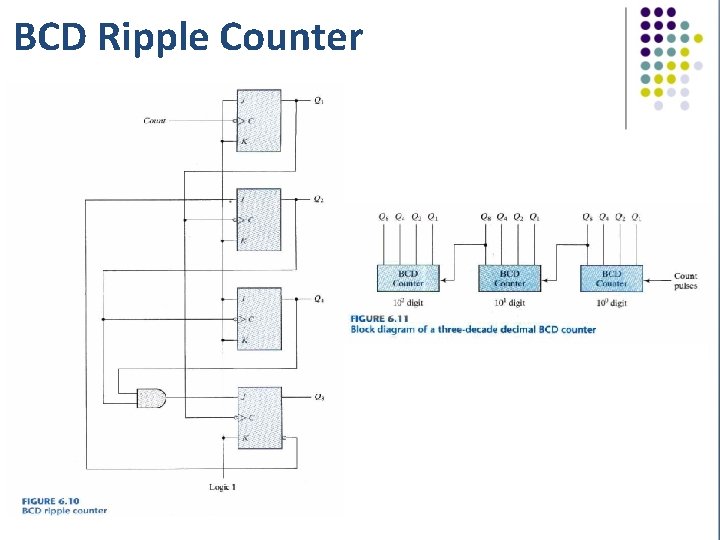

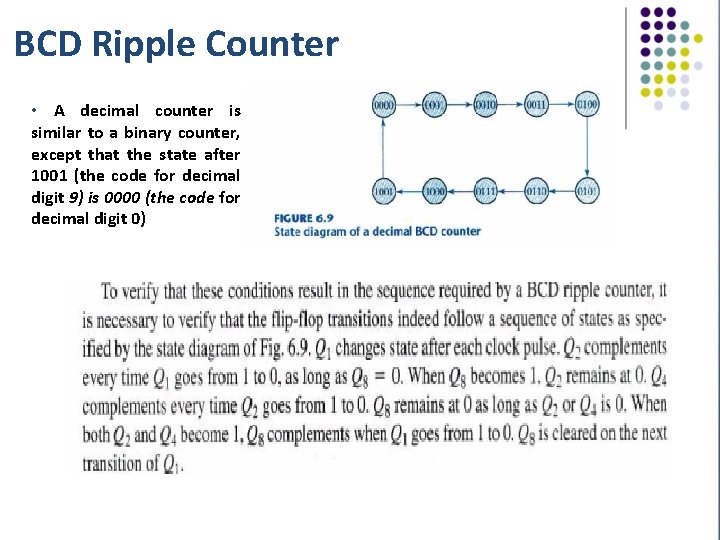

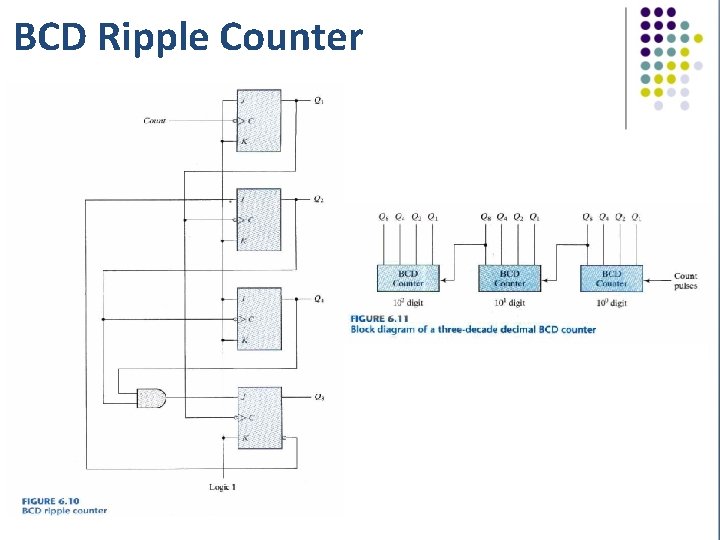

BCD Ripple Counter • A decimal counter is similar to a binary counter, except that the state after 1001 (the code for decimal digit 9) is 0000 (the code for decimal digit 0)

BCD Ripple Counter

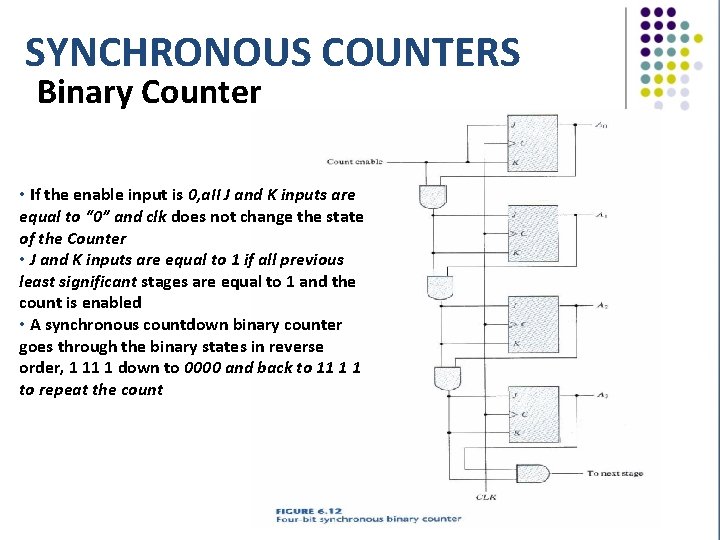

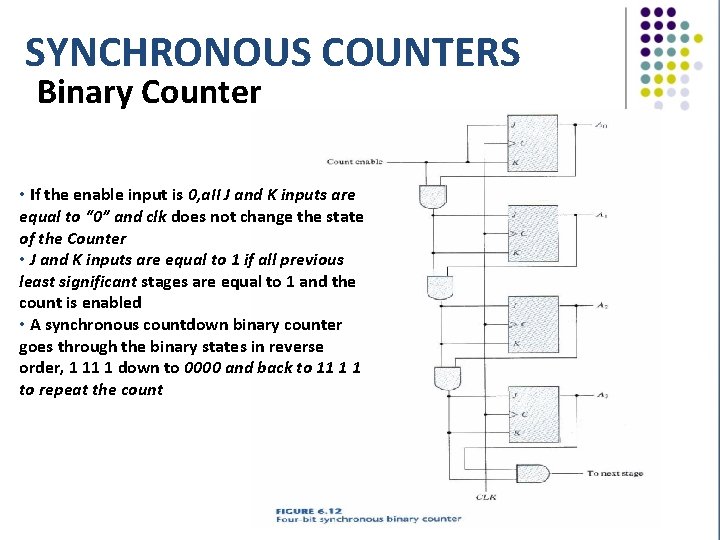

SYNCHRONOUS COUNTERS Binary Counter • If the enable input is 0, a. II J and K inputs are equal to “ 0” and clk does not change the state of the Counter • J and K inputs are equal to 1 if all previous least significant stages are equal to 1 and the count is enabled • A synchronous countdown binary counter goes through the binary states in reverse order, 1 11 1 down to 0000 and back to 11 1 1 to repeat the count

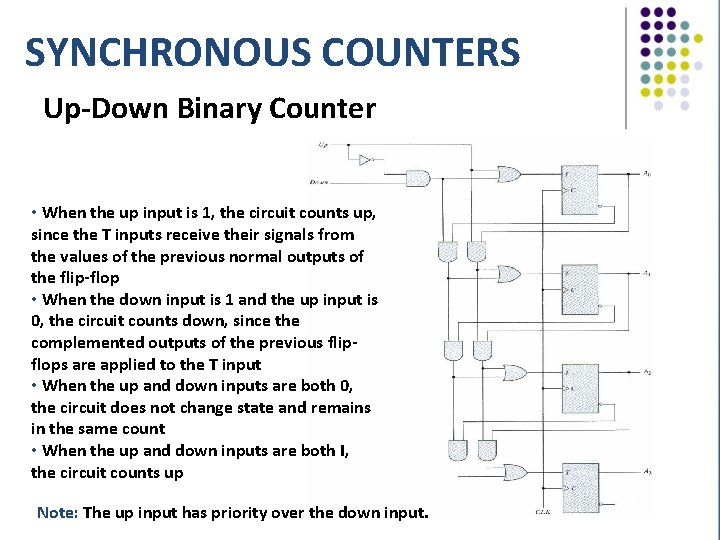

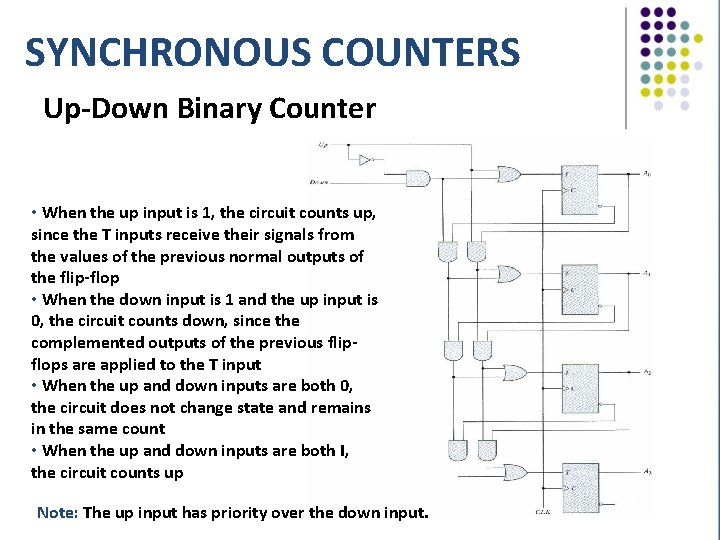

SYNCHRONOUS COUNTERS Up-Down Binary Counter • When the up input is 1, the circuit counts up, since the T inputs receive their signals from the values of the previous normal outputs of the flip-flop • When the down input is 1 and the up input is 0, the circuit counts down, since the complemented outputs of the previous flipflops are applied to the T input • When the up and down inputs are both 0, the circuit does not change state and remains in the same count • When the up and down inputs are both I, the circuit counts up Note: The up input has priority over the down input.

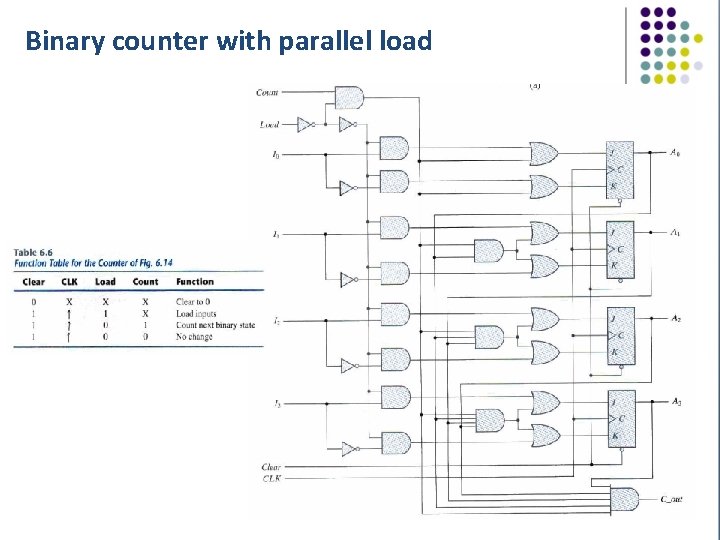

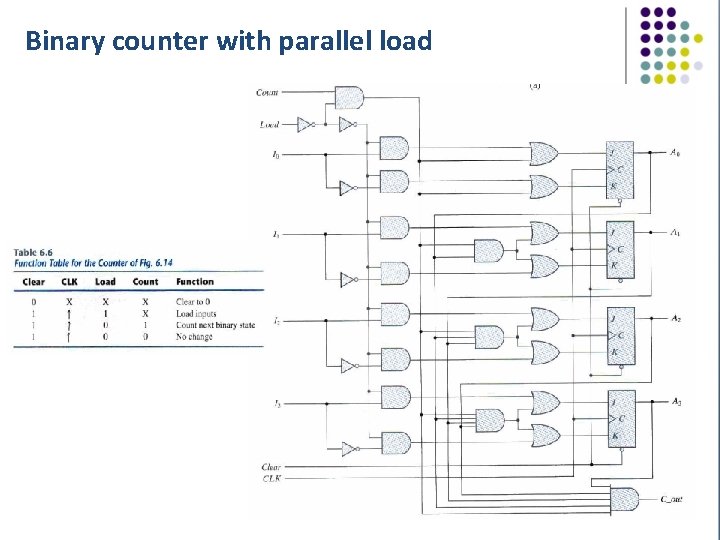

Binary counter with parallel load

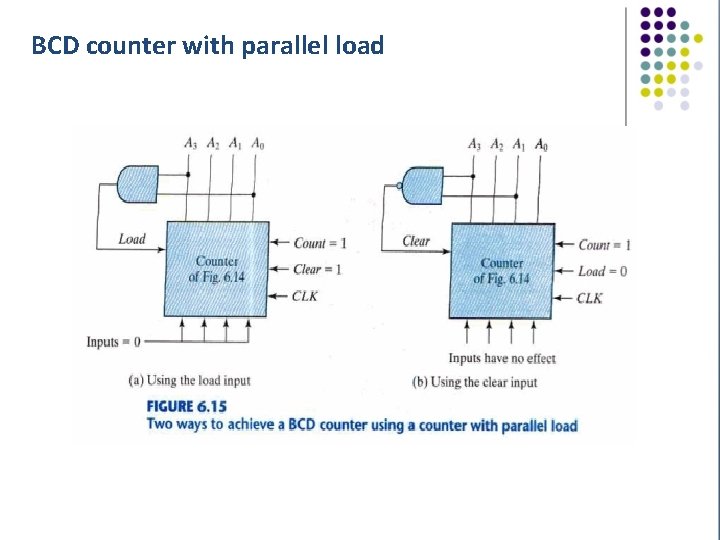

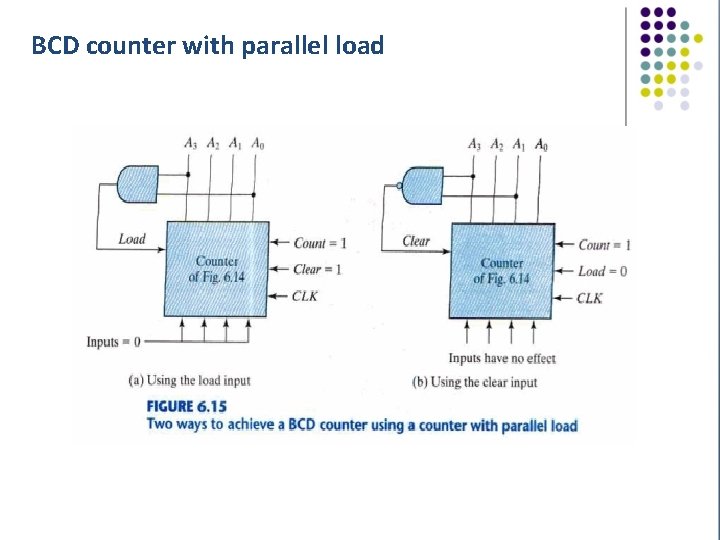

BCD counter with parallel load

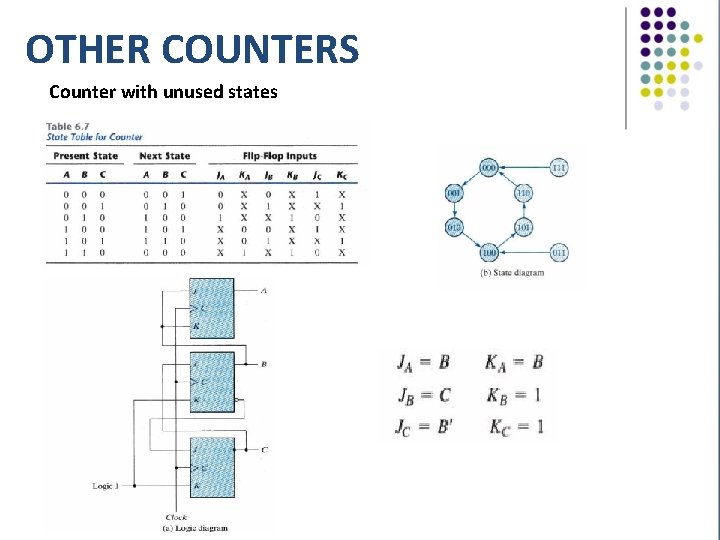

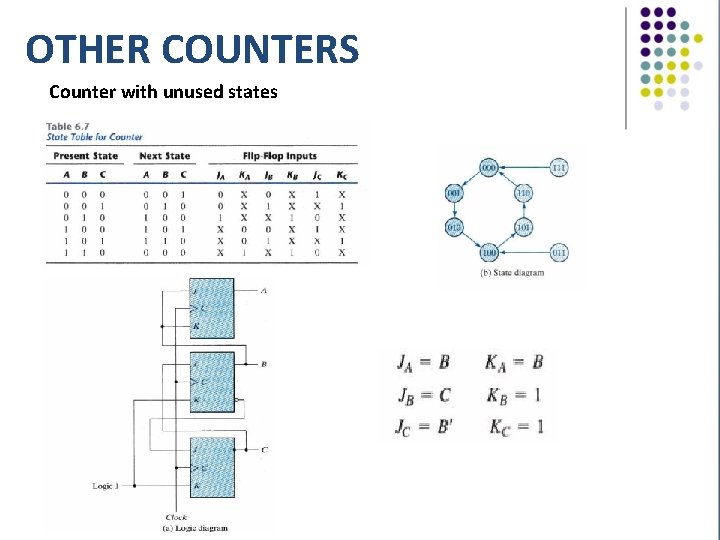

OTHER COUNTERS Counter with unused states

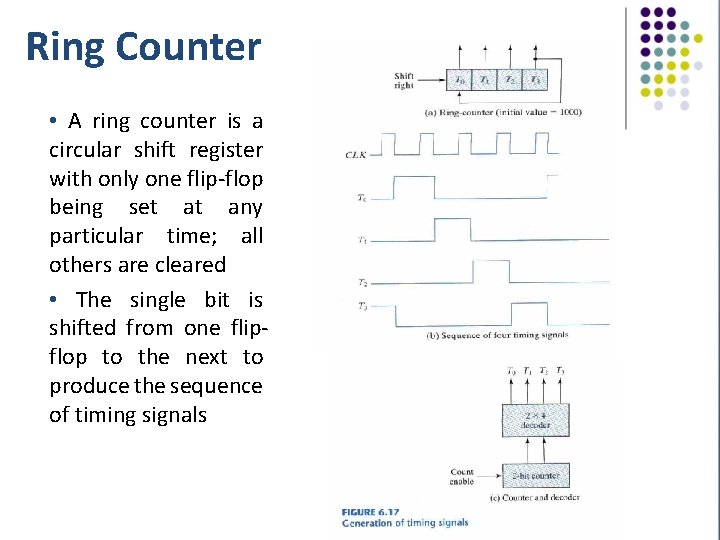

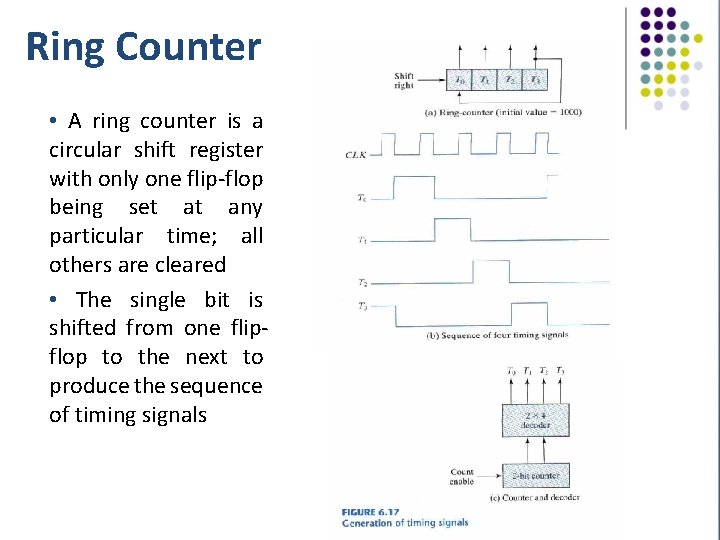

Ring Counter • A ring counter is a circular shift register with only one flip-flop being set at any particular time; all others are cleared • The single bit is shifted from one flipflop to the next to produce the sequence of timing signals

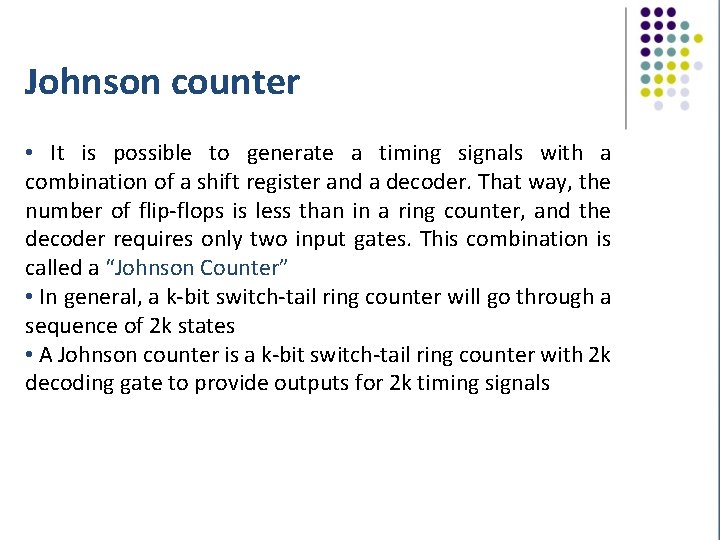

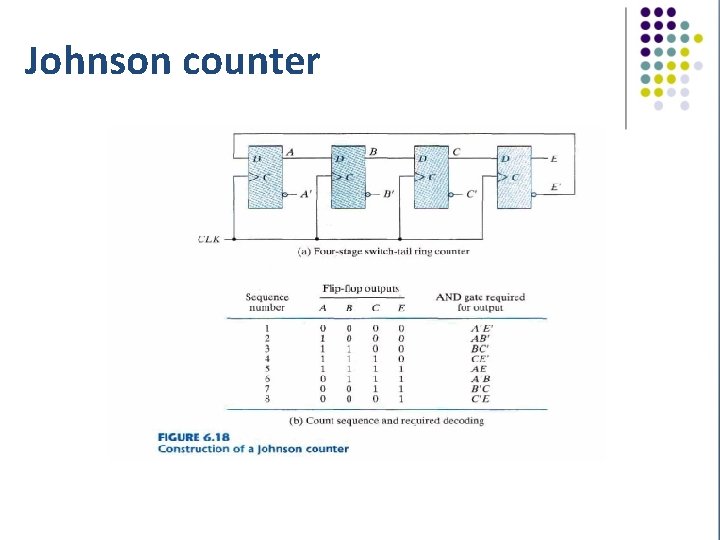

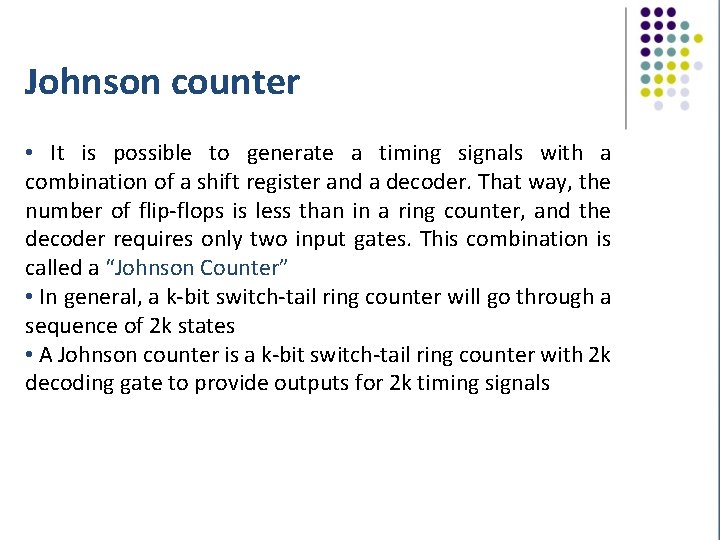

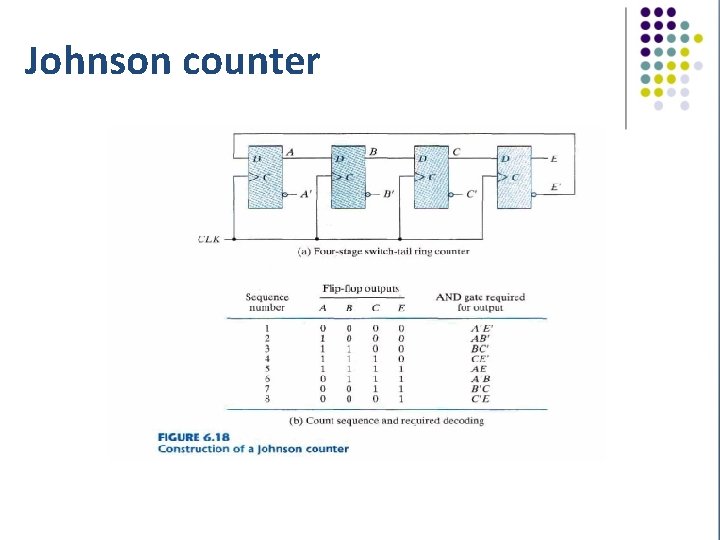

Johnson counter • It is possible to generate a timing signals with a combination of a shift register and a decoder. That way, the number of flip-flops is less than in a ring counter, and the decoder requires only two input gates. This combination is called a “Johnson Counter” • In general, a k-bit switch-tail ring counter will go through a sequence of 2 k states • A Johnson counter is a k-bit switch-tail ring counter with 2 k decoding gate to provide outputs for 2 k timing signals

Johnson counter

Home work 6. 2, 6. 4, 6. 6, 6. 7, 6. 8, 6. 9, 6. 11, 6. 12, 6. 13, 6. 14, 6. 16, 6. 17, 6. 18, 6. 19, 6. 20, 6. 24, 6. 25, 6. 27, 6. 28, 6. 29, 6. 30