Graduate Institute of Electronics Engineering NTU 98 1

- Slides: 47

Graduate Institute of Electronics Engineering, NTU 98 -1 Under-Graduate Project Synthesis of Combinational Logic Speaker: 蔡朝陽 Adviser: Prof. An-Yeu Wu Date: 2010/10/19 ACCESS IC LAB

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Outline v What is synthesis? v Behavior Description for Synthesis v Write Efficient HDL Code P. 2

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU What is logic synthesis v Logic synthesis is the process of converting a highlevel description of design into an optimized gatelevel representation v Logic synthesis uses standard cell library which have simple cells, such as basic logic gates like and, or, and nor, or macro cells, such as adder, muxes, memory, and special flip-flops v The designer would first understand the architectural description. Then he/she would consider design constraints such as timing, area, testability, and power P. 3

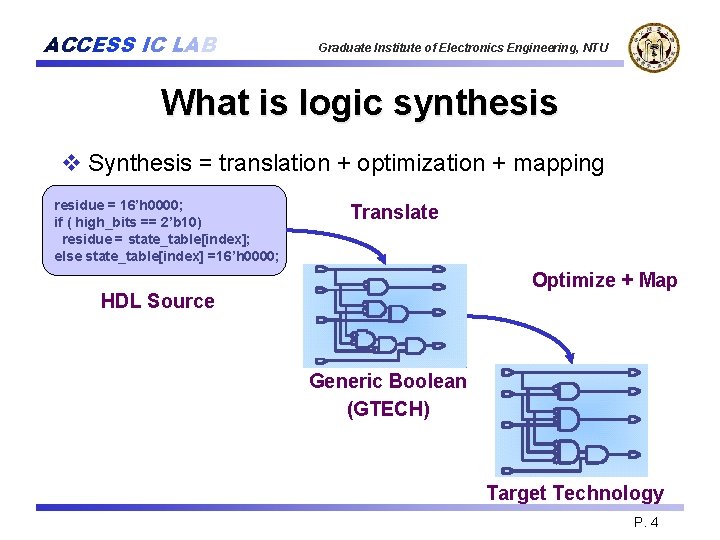

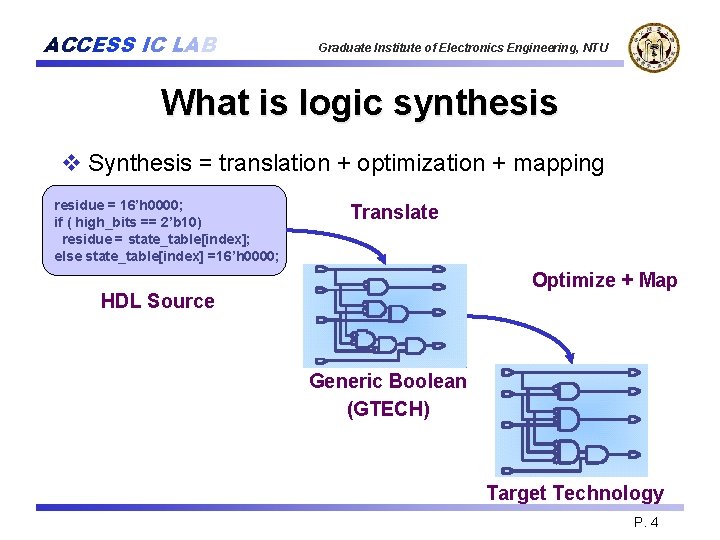

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU What is logic synthesis v Synthesis = translation + optimization + mapping residue = 16’h 0000; if ( high_bits == 2’b 10) residue = state_table[index]; else state_table[index] =16’h 0000; Translate Optimize + Map HDL Source Generic Boolean (GTECH) Target Technology P. 4

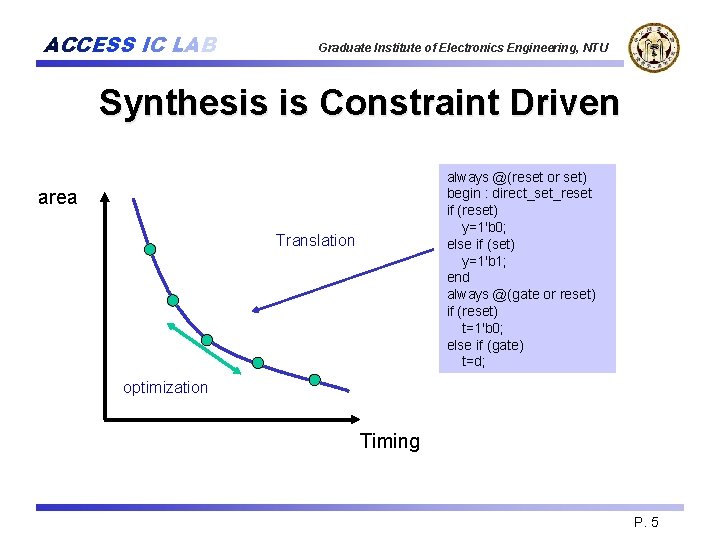

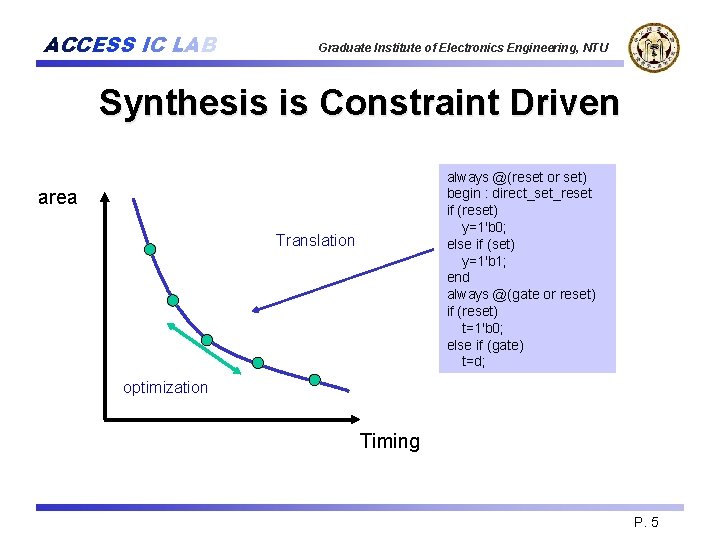

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Synthesis is Constraint Driven always @(reset or set) begin : direct_set_reset if (reset) y=1'b 0; else if (set) y=1'b 1; end always @(gate or reset) if (reset) t=1'b 0; else if (gate) t=d; area Translation optimization Timing P. 5

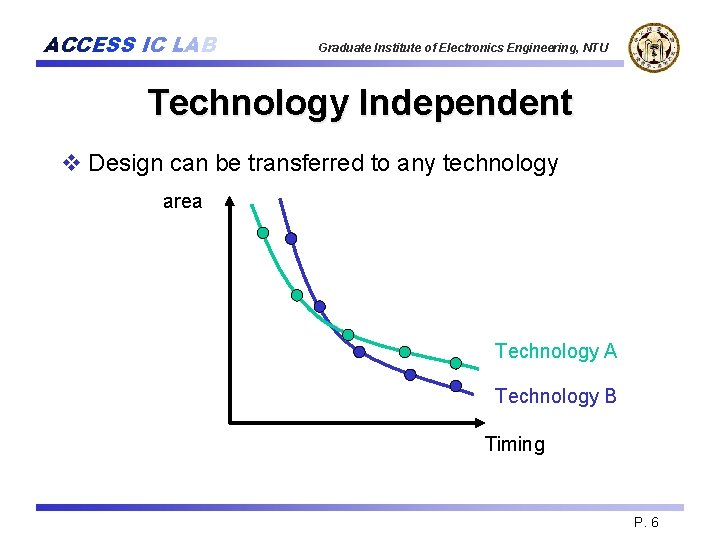

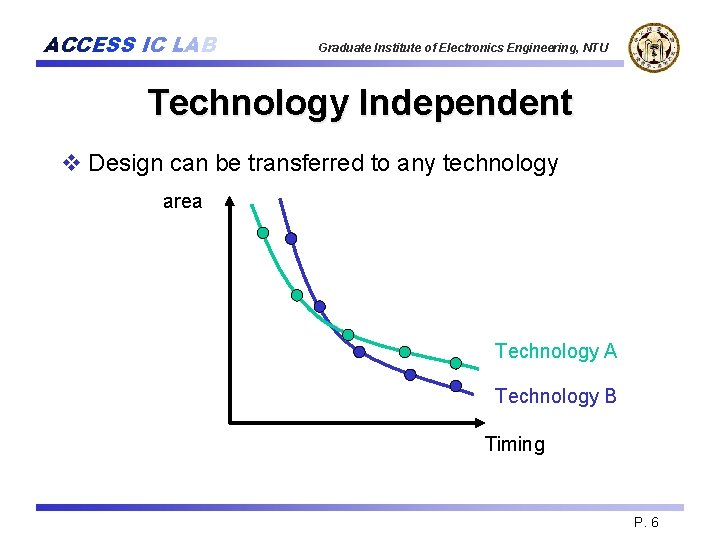

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Technology Independent v Design can be transferred to any technology area Technology A Technology B Timing P. 6

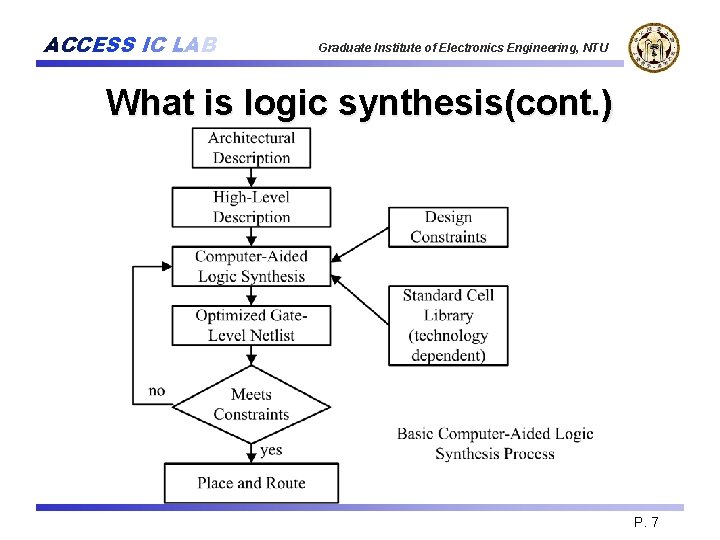

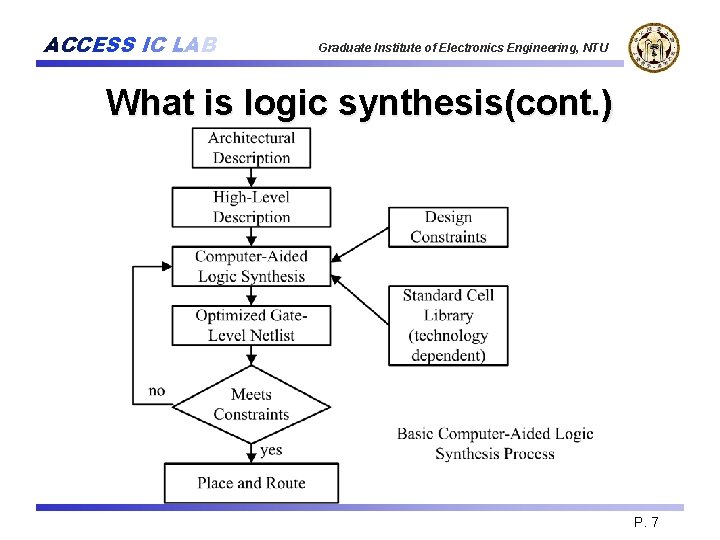

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU What is logic synthesis(cont. ) P. 7

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Impact of Logic Synthesis v Limitation on manual design v For large designs, manual conversion was prone human error, such as a small gate missed somewhere v The designer could never be sure that the design constraints were going to be met until the gate-level implementation is complete and tested v A significant portion of the design cycle was dominated by the time taken to convert a high-level design into gates v Design reuse was not possible v Each designer would implement design blocks differently. For large designs, this could mean that smaller blocks were optimized but the overall design was not optimal P. 8

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Impact of Logic Synthesis(cont. ) v Automated Logic synthesis tools addressed these problems as follows v High-level design is less prone to human error because designs are described at a higher level of abstraction v High-level design is done without significant concern about design constraints v Conversion from high-level design to gates is fast v Logic synthesis tools optimize the design as a whole. This removes the problem with varied designer styles for the different blocks in the design and suboptimal designs v Logic synthesis tools allow technology-independent design v Design reuse is possible for technology-independent descriptions. P. 9

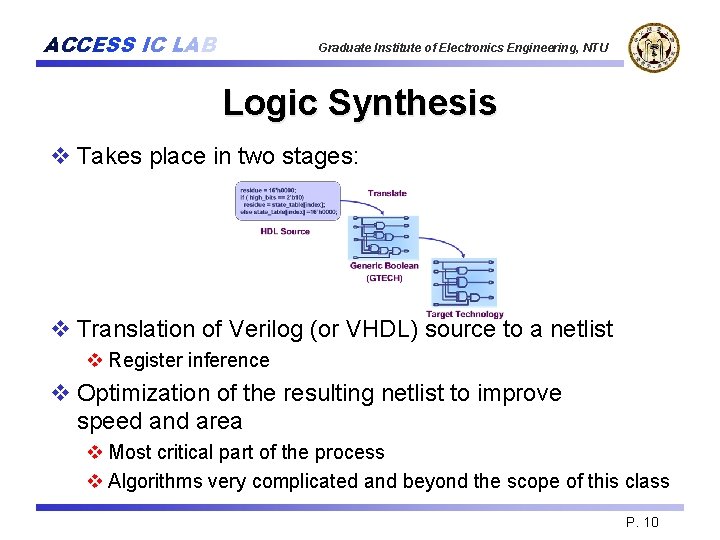

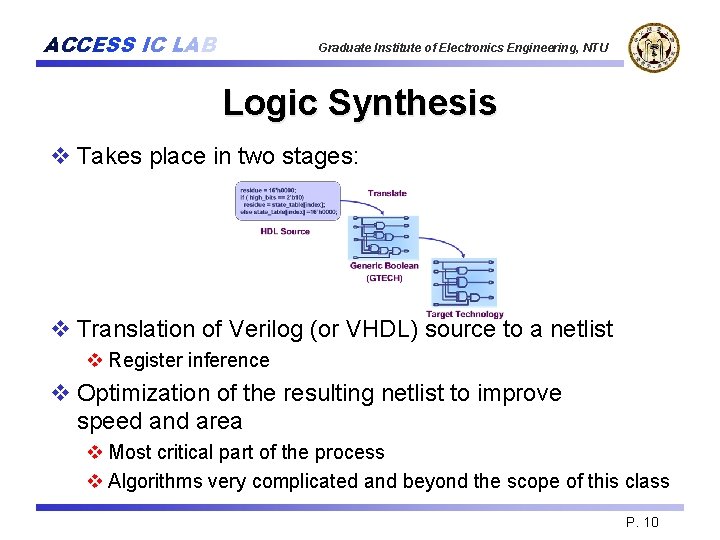

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Logic Synthesis v Takes place in two stages: v Translation of Verilog (or VHDL) source to a netlist v Register inference v Optimization of the resulting netlist to improve speed and area v Most critical part of the process v Algorithms very complicated and beyond the scope of this class P. 10

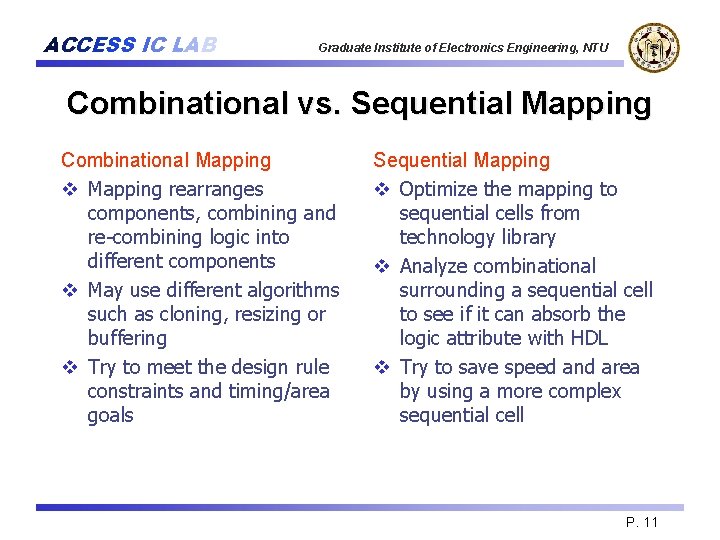

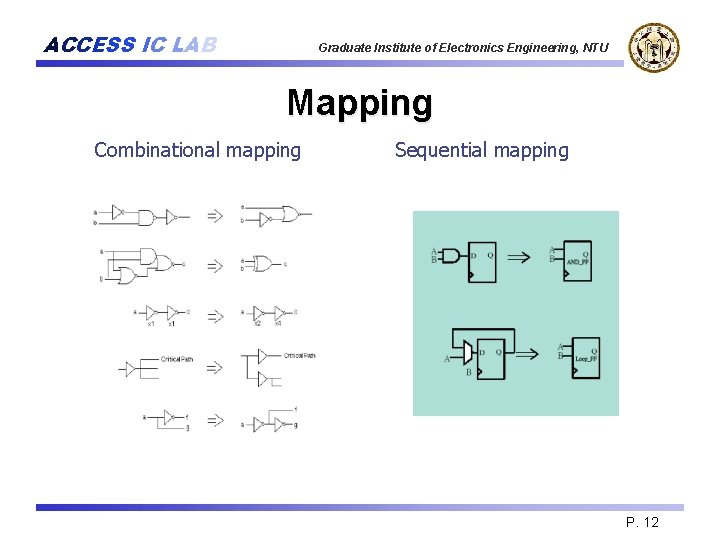

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Combinational vs. Sequential Mapping Combinational Mapping v Mapping rearranges components, combining and re-combining logic into different components v May use different algorithms such as cloning, resizing or buffering v Try to meet the design rule constraints and timing/area goals Sequential Mapping v Optimize the mapping to sequential cells from technology library v Analyze combinational surrounding a sequential cell to see if it can absorb the logic attribute with HDL v Try to save speed and area by using a more complex sequential cell P. 11

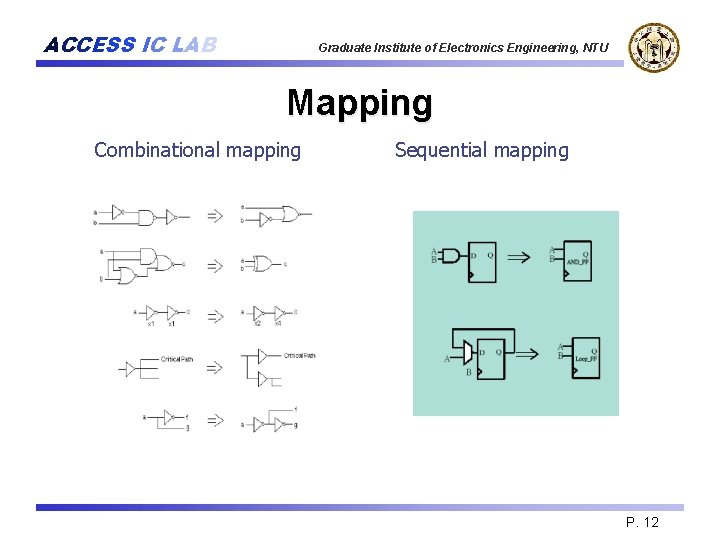

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Mapping Combinational mapping Sequential mapping P. 12

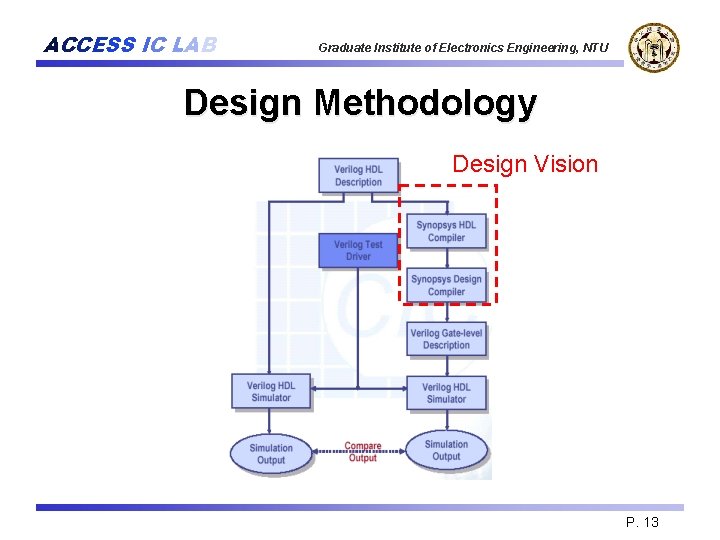

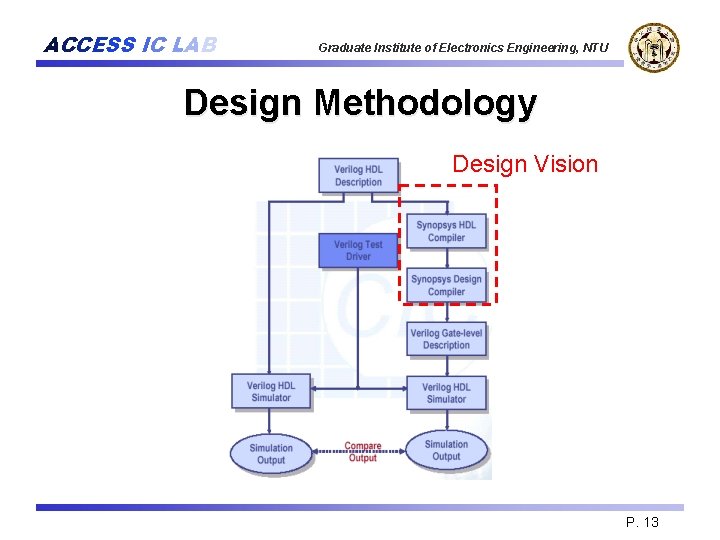

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Design Methodology Design Vision P. 13

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Verilog and Logic Synthesis v Verilog is used in two ways v. Model for discrete-event simulation v. Specification for a logic synthesis system v Logic synthesis converts a subset of the Verilog language into an efficient netlist v One of the major breakthroughs in designing logic chips in the last 20 years v Most chips are designed using at least some logic synthesis P. 14

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Verilog Primitive Cell v Verilog primitive cells build basic combinational circuit v Synthesizable Verilog primitives cells vand, nand, or, nor, xnor, not vbufif 0, bufif 1, notif 0, notif 1 P. 15

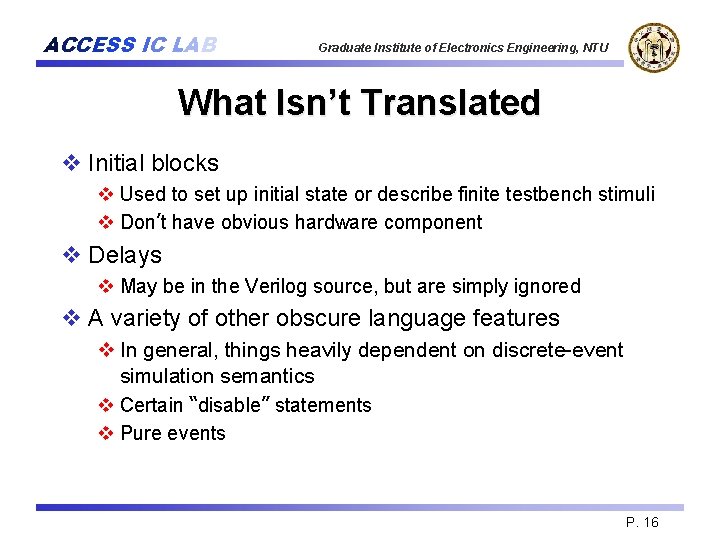

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU What Isn’t Translated v Initial blocks v Used to set up initial state or describe finite testbench stimuli v Don’t have obvious hardware component v Delays v May be in the Verilog source, but are simply ignored v A variety of other obscure language features v In general, things heavily dependent on discrete-event simulation semantics v Certain “disable” statements v Pure events P. 16

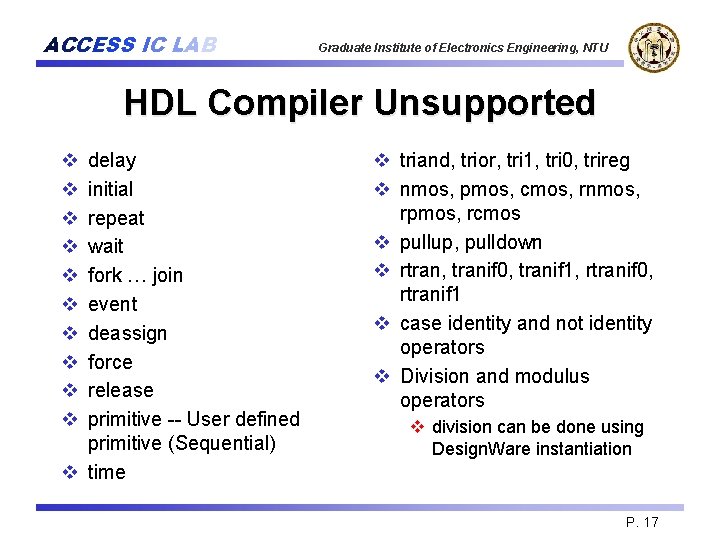

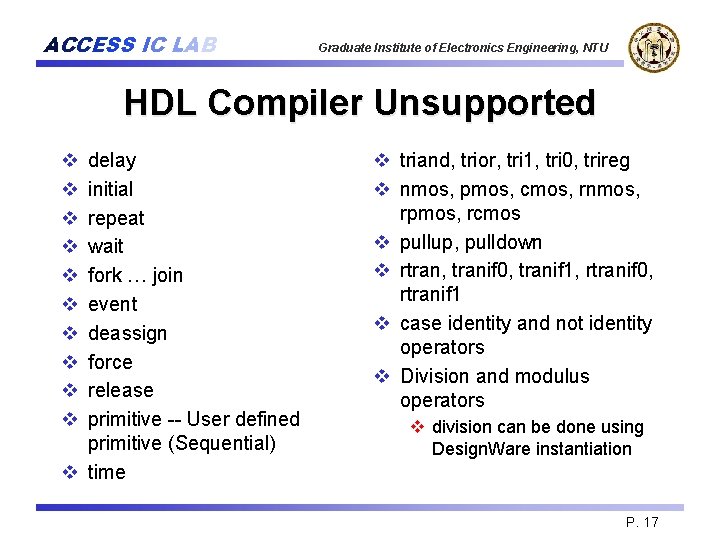

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU HDL Compiler Unsupported v v v v v delay initial repeat wait fork … join event deassign force release primitive -- User defined primitive (Sequential) v time v triand, trior, tri 1, tri 0, trireg v nmos, pmos, cmos, rnmos, rpmos, rcmos v pullup, pulldown v rtran, tranif 0, tranif 1, rtranif 0, rtranif 1 v case identity and not identity operators v Division and modulus operators v division can be done using Design. Ware instantiation P. 17

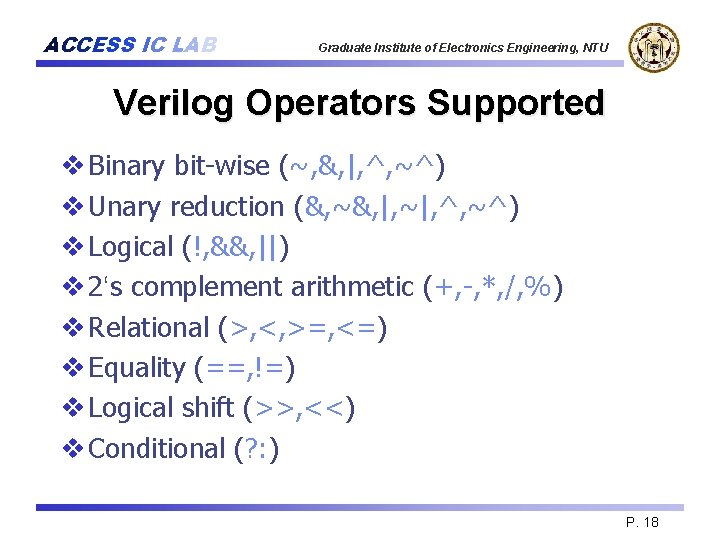

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Verilog Operators Supported v Binary bit-wise (~, &, |, ^, ~^) v Unary reduction (&, ~&, |, ~|, ^, ~^) v Logical (!, &&, ||) v 2‘s complement arithmetic (+, -, *, /, %) v Relational (>, <, >=, <=) v Equality (==, !=) v Logical shift (>>, <<) v Conditional (? : ) P. 18

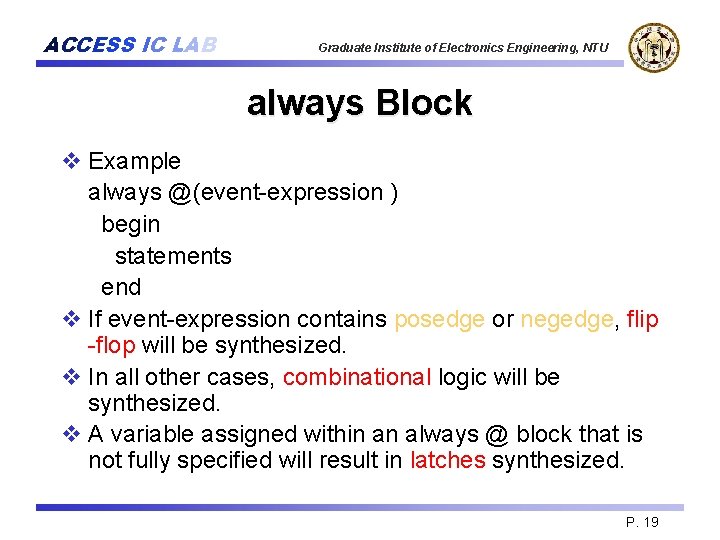

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU always Block v Example always @(event-expression ) begin statements end v If event-expression contains posedge or negedge, flip -flop will be synthesized. v In all other cases, combinational logic will be synthesized. v A variable assigned within an always @ block that is not fully specified will result in latches synthesized. P. 19

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Latch Inference v A variable assigned within an always block that is not fully specified. v If a case statement is not a full case, it will infer a latch. P. 20

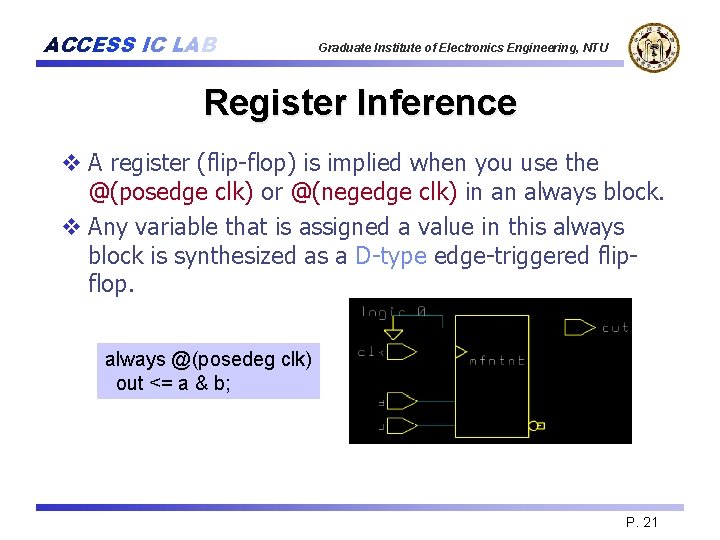

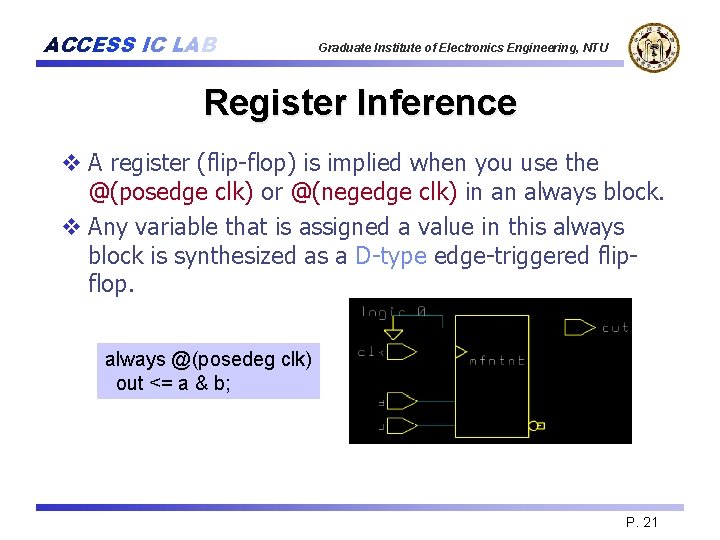

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Register Inference v A register (flip-flop) is implied when you use the @(posedge clk) or @(negedge clk) in an always block. v Any variable that is assigned a value in this always block is synthesized as a D-type edge-triggered flipflop. always @(posedeg clk) out <= a & b; P. 21

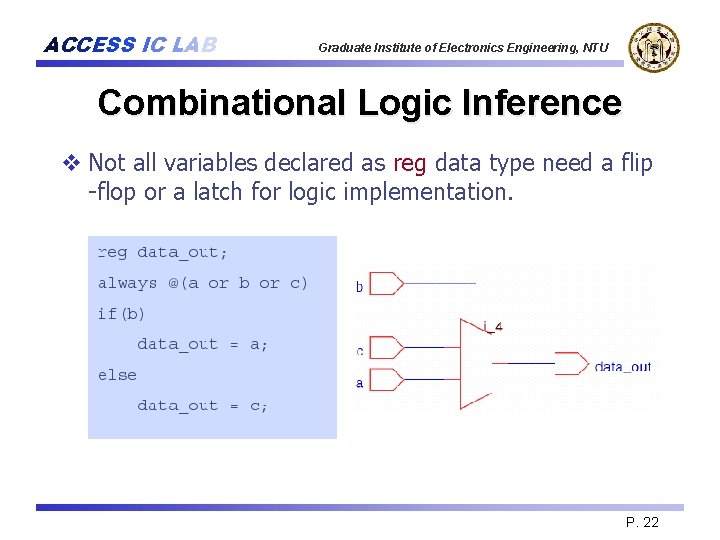

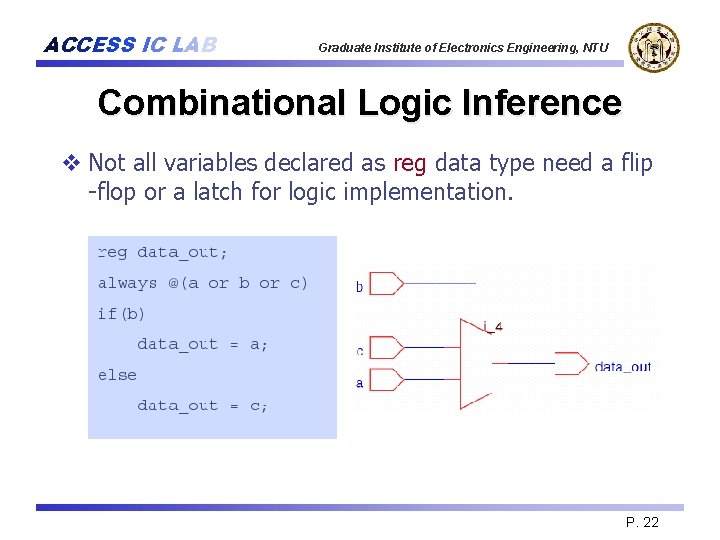

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Combinational Logic Inference v Not all variables declared as reg data type need a flip -flop or a latch for logic implementation. P. 22

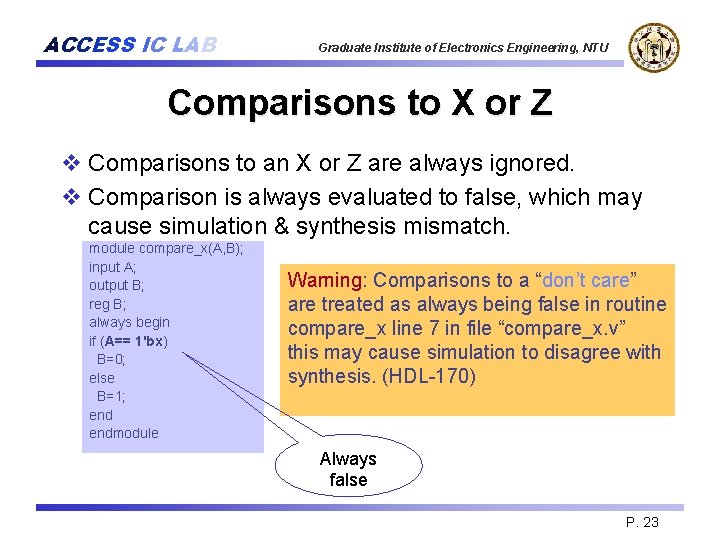

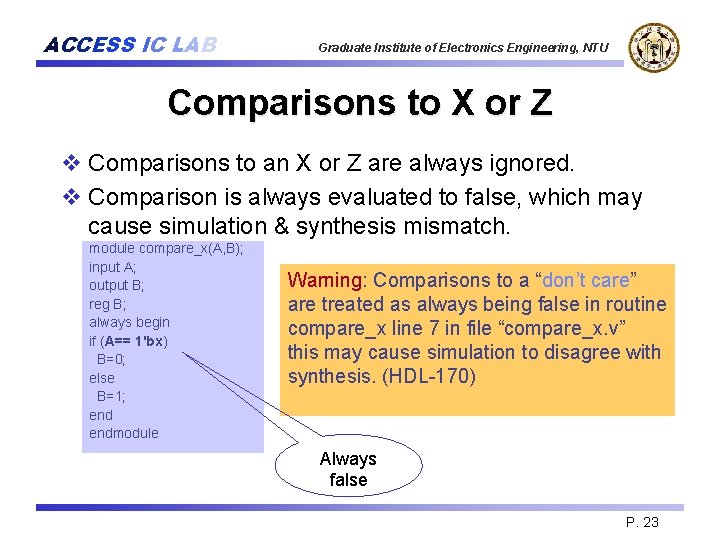

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Comparisons to X or Z v Comparisons to an X or Z are always ignored. v Comparison is always evaluated to false, which may cause simulation & synthesis mismatch. module compare_x(A, B); input A; output B; reg B; always begin if (A== 1'bx) B=0; else B=1; endmodule Warning: Comparisons to a “don’t care” are treated as always being false in routine compare_x line 7 in file “compare_x. v” this may cause simulation to disagree with synthesis. (HDL-170) Always false P. 23

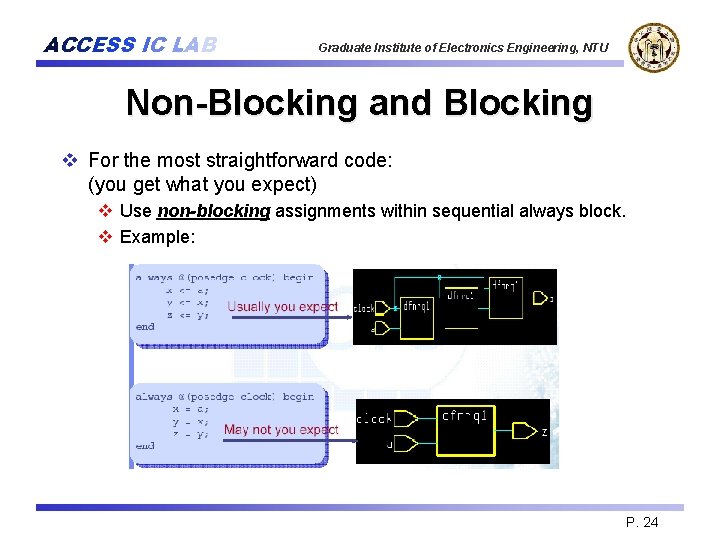

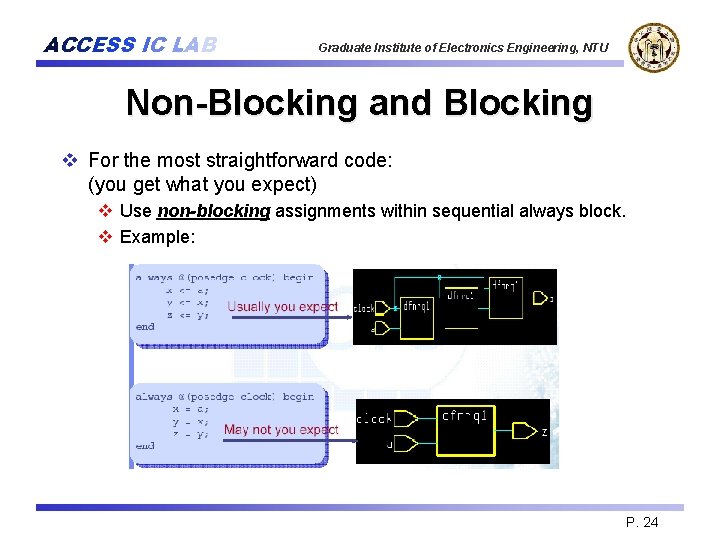

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Non-Blocking and Blocking v For the most straightforward code: (you get what you expect) v Use non-blocking assignments within sequential always block. v Example: P. 24

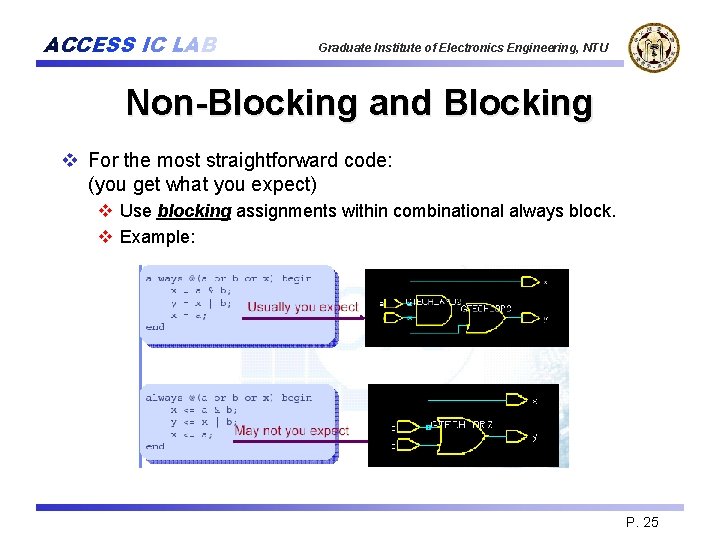

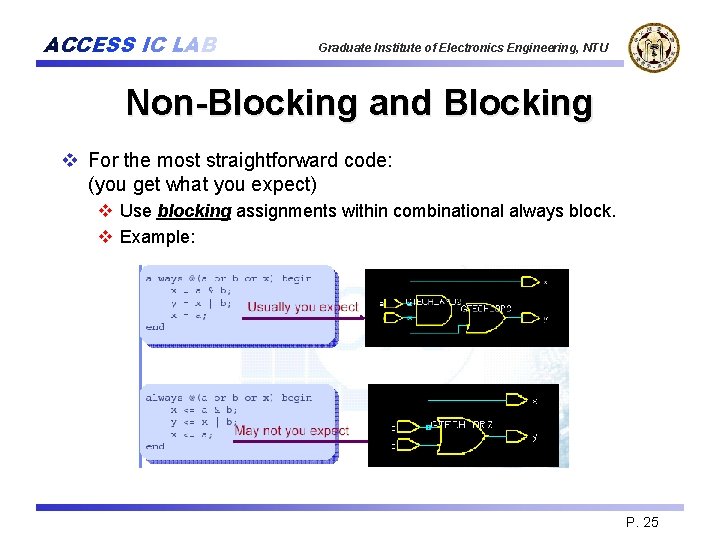

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Non-Blocking and Blocking v For the most straightforward code: (you get what you expect) v Use blocking assignments within combinational always block. v Example: P. 25

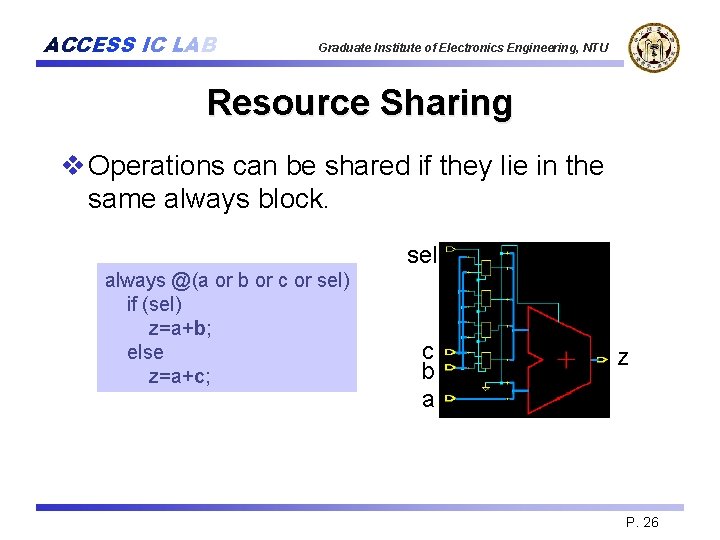

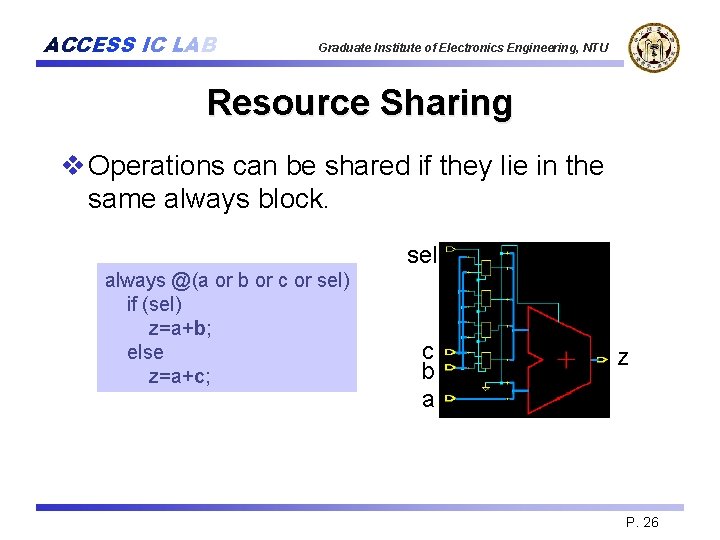

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Resource Sharing v Operations can be shared if they lie in the same always block. sel always @(a or b or c or sel) if (sel) z=a+b; else z=a+c; c b a z P. 26

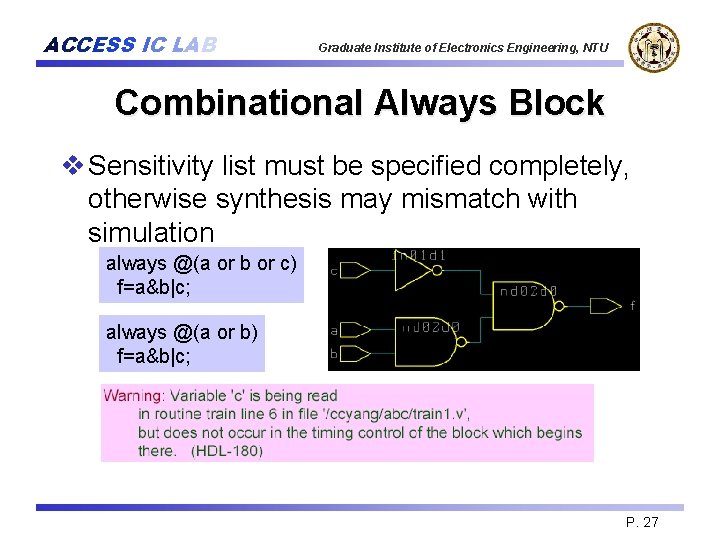

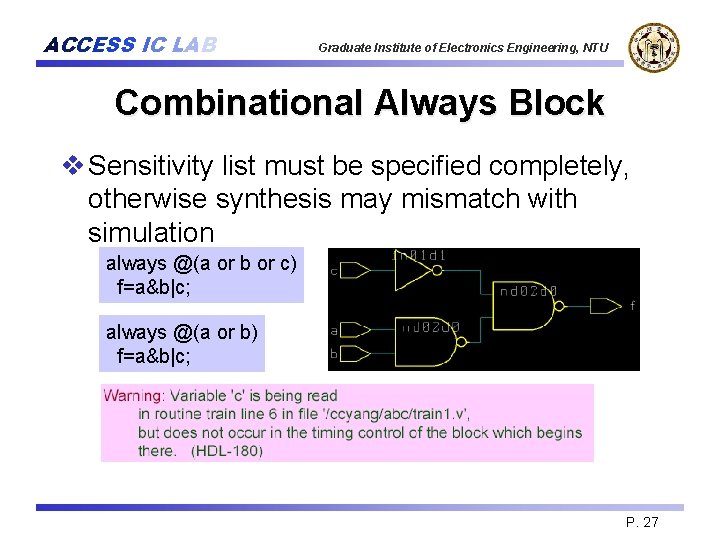

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Combinational Always Block v Sensitivity list must be specified completely, otherwise synthesis may mismatch with simulation always @(a or b or c) f=a&b|c; always @(a or b) f=a&b|c; P. 27

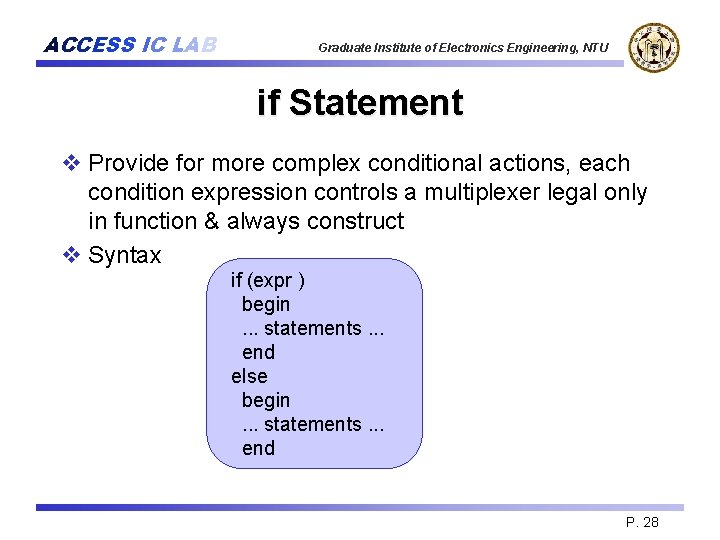

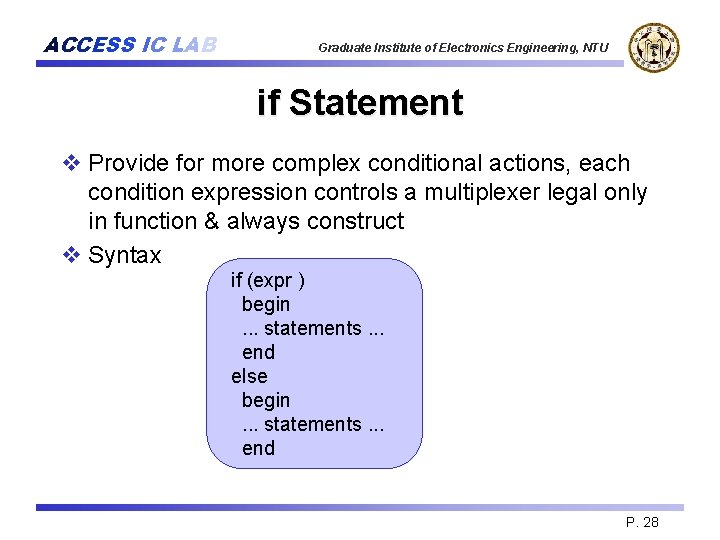

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU if Statement v Provide for more complex conditional actions, each condition expression controls a multiplexer legal only in function & always construct v Syntax if (expr ) begin. . . statements. . . end else begin. . . statements. . . end P. 28

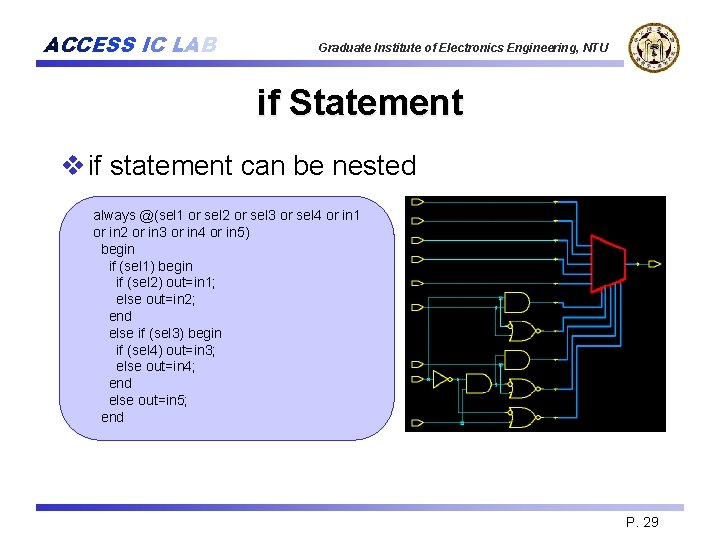

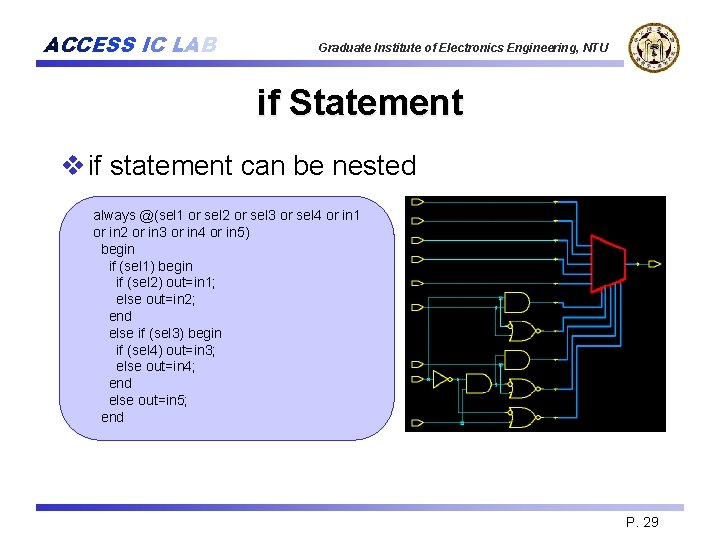

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU if Statement v if statement can be nested always @(sel 1 or sel 2 or sel 3 or sel 4 or in 1 or in 2 or in 3 or in 4 or in 5) begin if (sel 1) begin if (sel 2) out=in 1; else out=in 2; end else if (sel 3) begin if (sel 4) out=in 3; else out=in 4; end else out=in 5; end P. 29

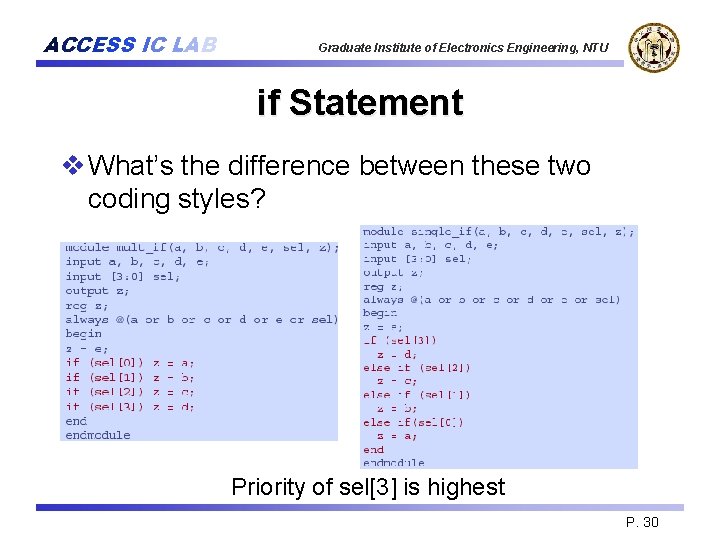

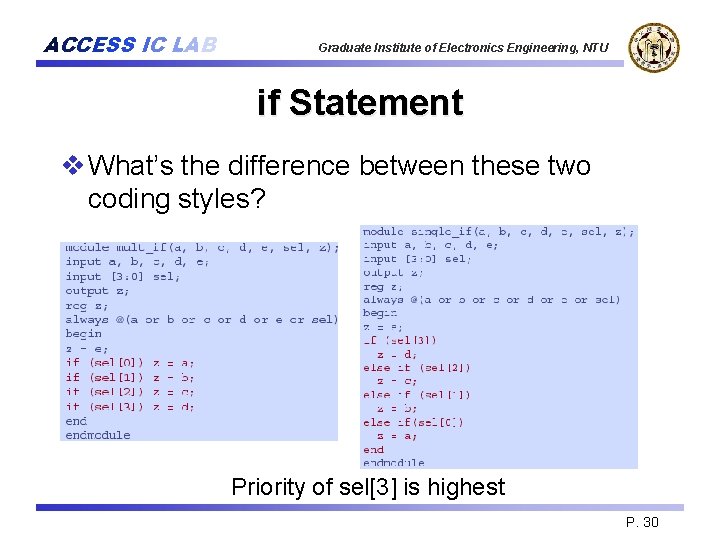

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU if Statement v What’s the difference between these two coding styles? Priority of sel[3] is highest P. 30

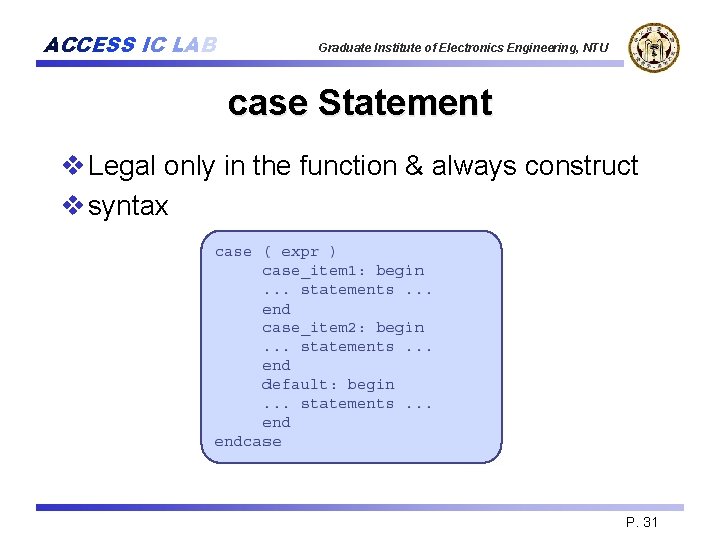

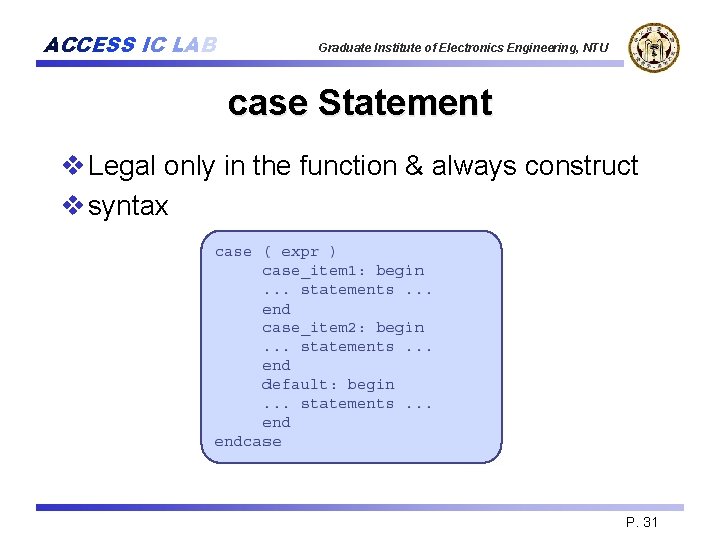

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU case Statement v Legal only in the function & always construct v syntax P. 31

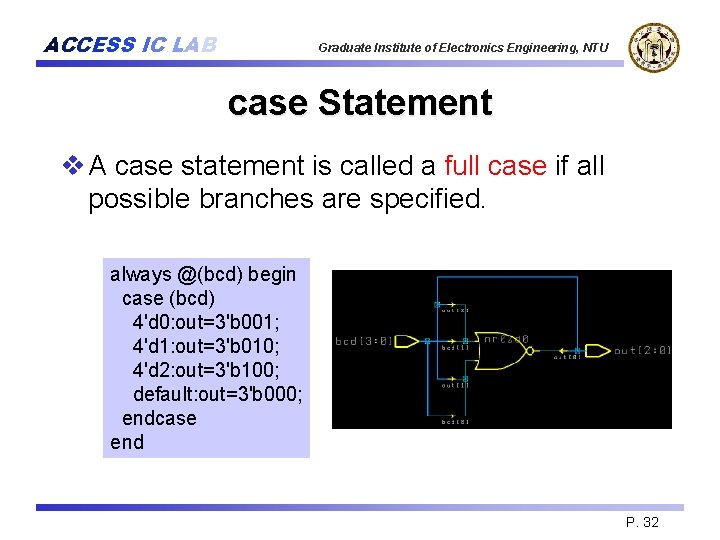

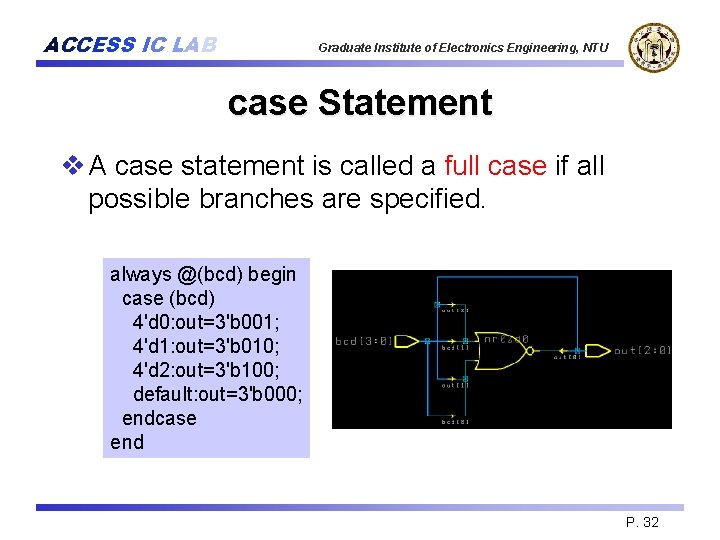

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU case Statement v A case statement is called a full case if all possible branches are specified. always @(bcd) begin case (bcd) 4'd 0: out=3'b 001; 4'd 1: out=3'b 010; 4'd 2: out=3'b 100; default: out=3'b 000; endcase end P. 32

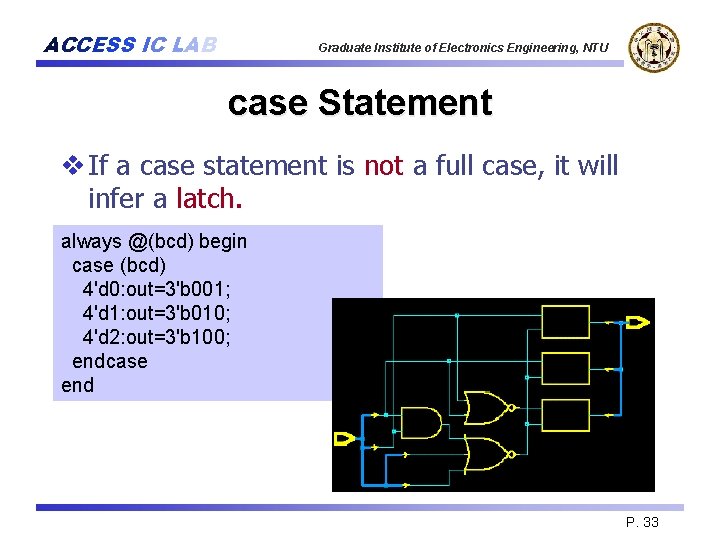

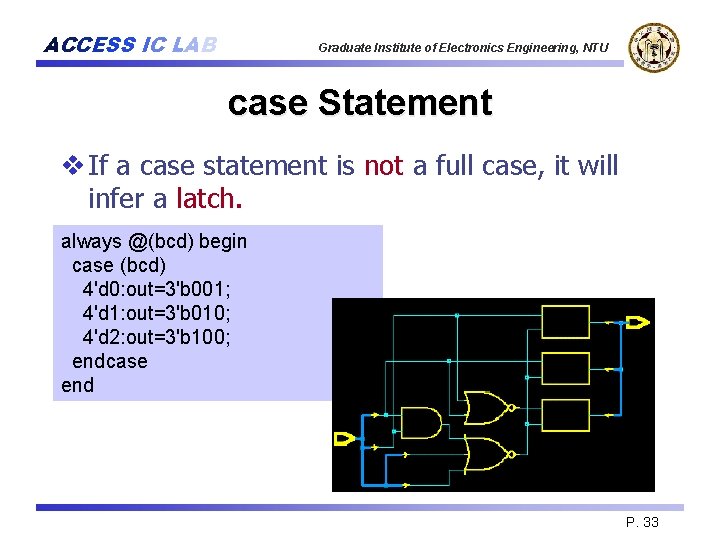

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU case Statement v If a case statement is not a full case, it will infer a latch. always @(bcd) begin case (bcd) 4'd 0: out=3'b 001; 4'd 1: out=3'b 010; 4'd 2: out=3'b 100; endcase end P. 33

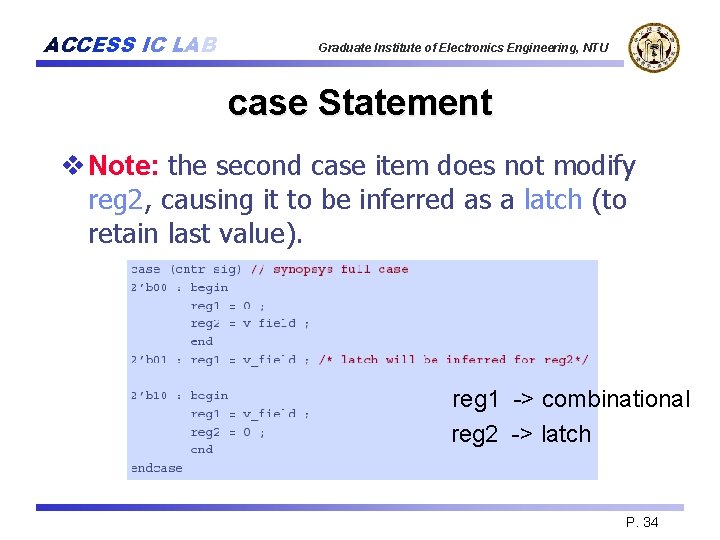

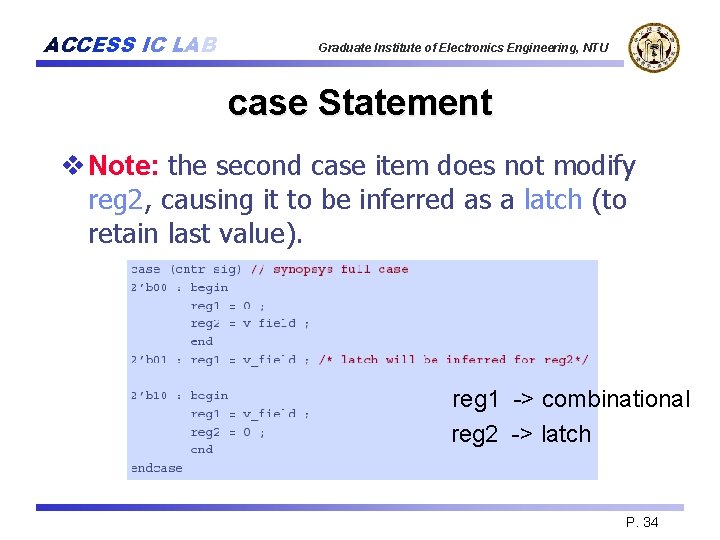

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU case Statement v Note: the second case item does not modify reg 2, causing it to be inferred as a latch (to retain last value). reg 1 -> combinational reg 2 -> latch P. 34

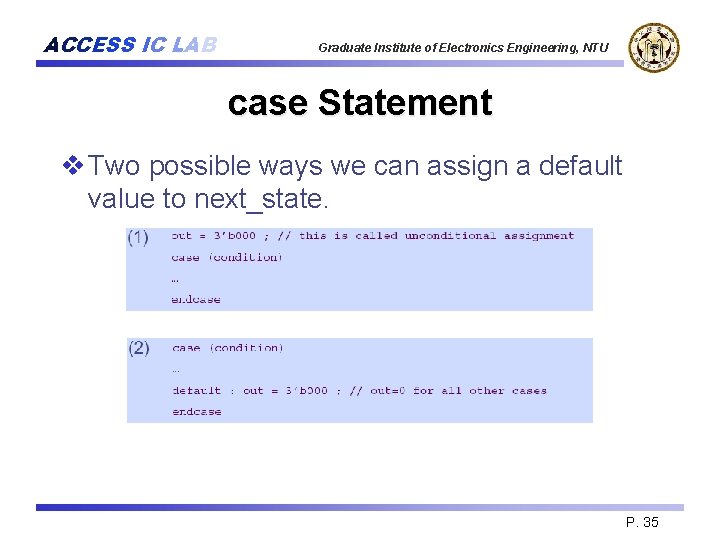

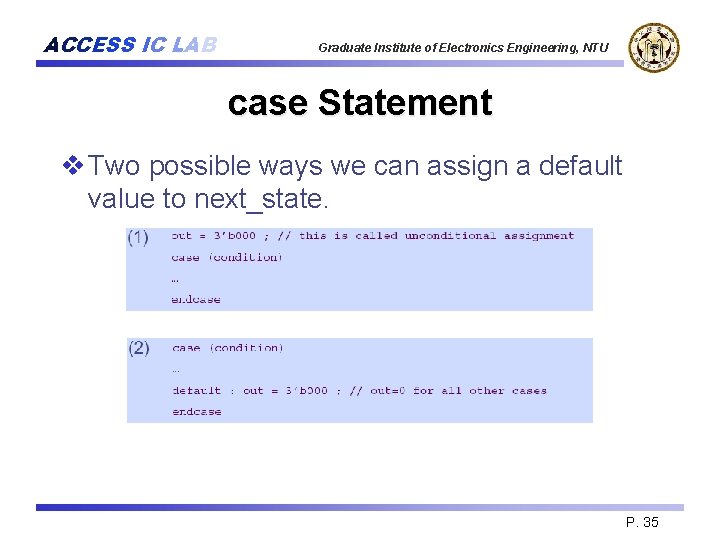

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU case Statement v Two possible ways we can assign a default value to next_state. P. 35

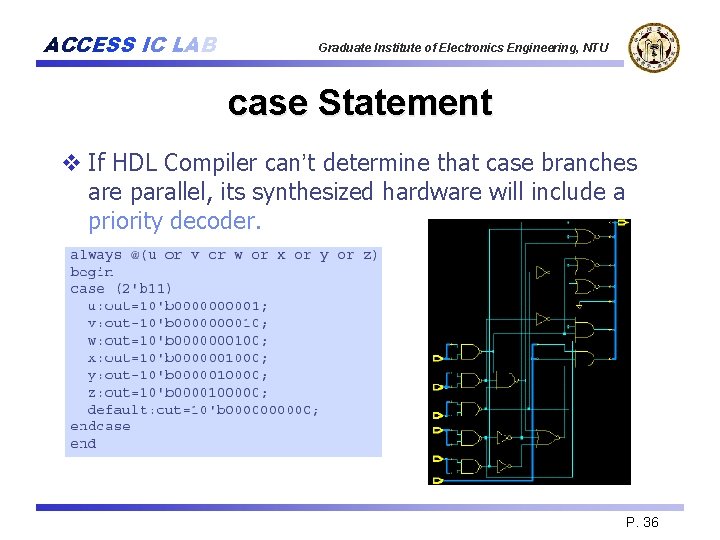

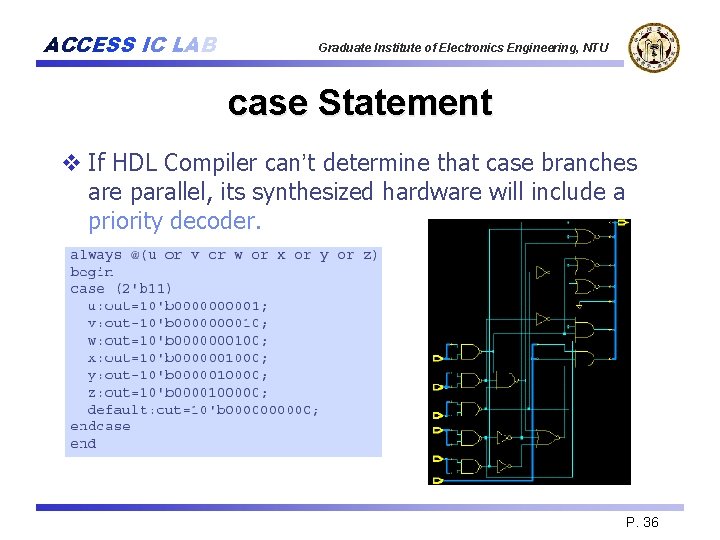

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU case Statement v If HDL Compiler can’t determine that case branches are parallel, its synthesized hardware will include a priority decoder. P. 36

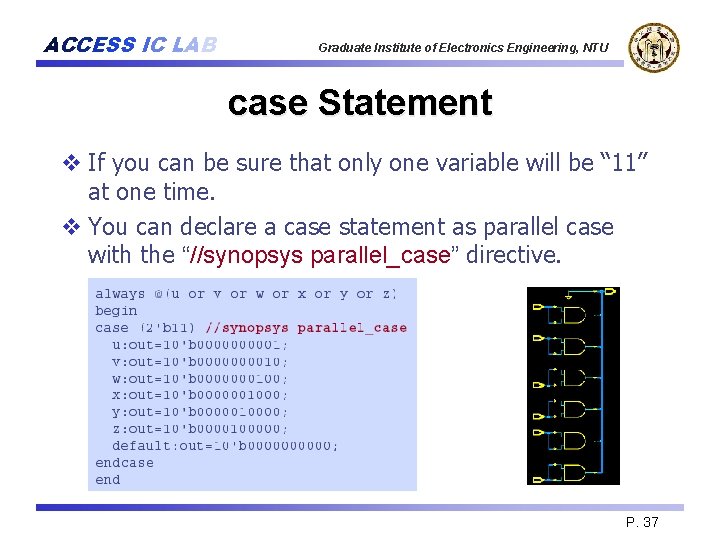

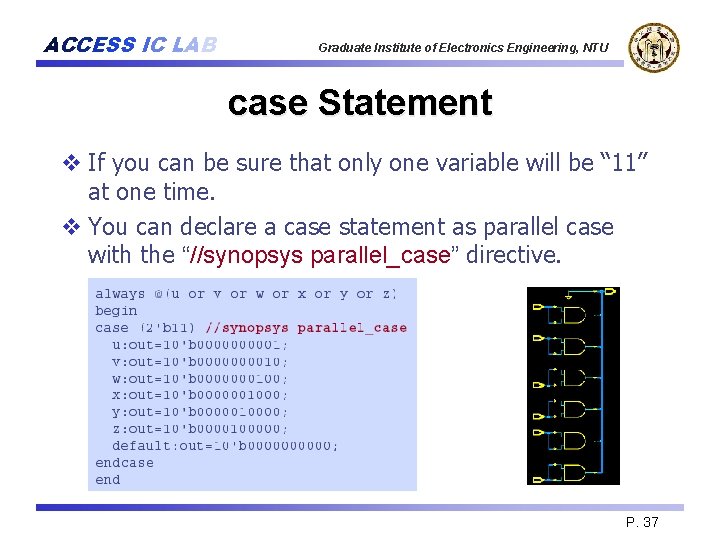

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU case Statement v If you can be sure that only one variable will be “ 11” at one time. v You can declare a case statement as parallel case with the “//synopsys parallel_case” directive. P. 37

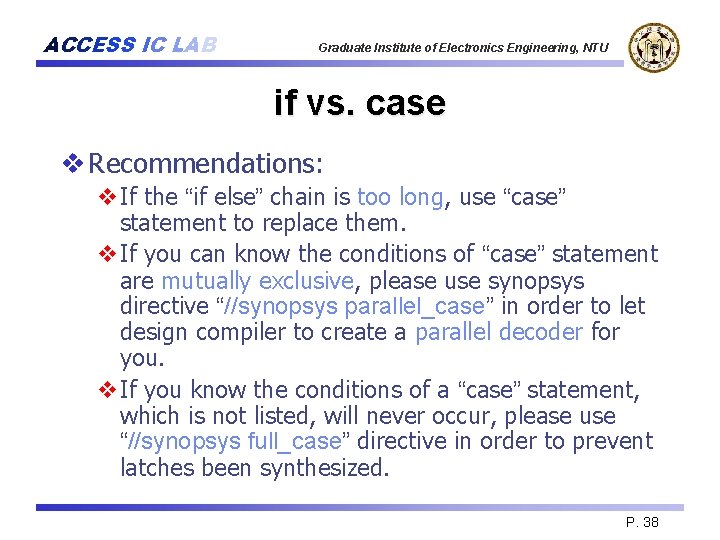

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU if vs. case v Recommendations: v. If the “if else” chain is too long, use “case” statement to replace them. v. If you can know the conditions of “case” statement are mutually exclusive, please use synopsys directive “//synopsys parallel_case” in order to let design compiler to create a parallel decoder for you. v. If you know the conditions of a “case” statement, which is not listed, will never occur, please use “//synopsys full_case” directive in order to prevent latches been synthesized. P. 38

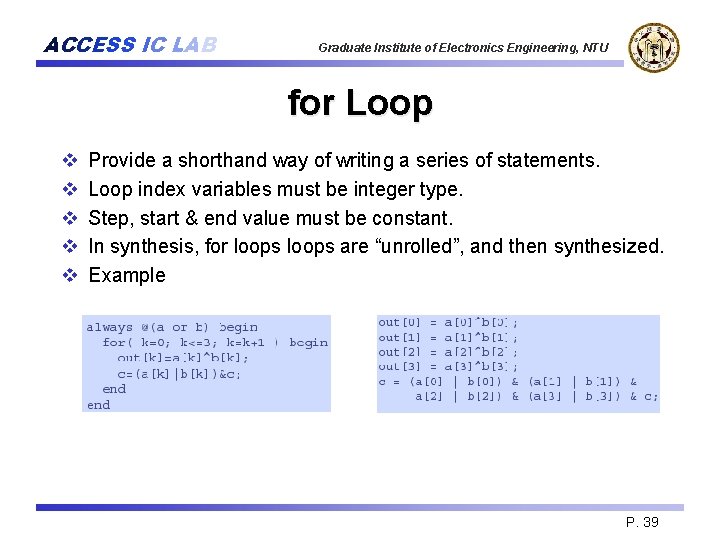

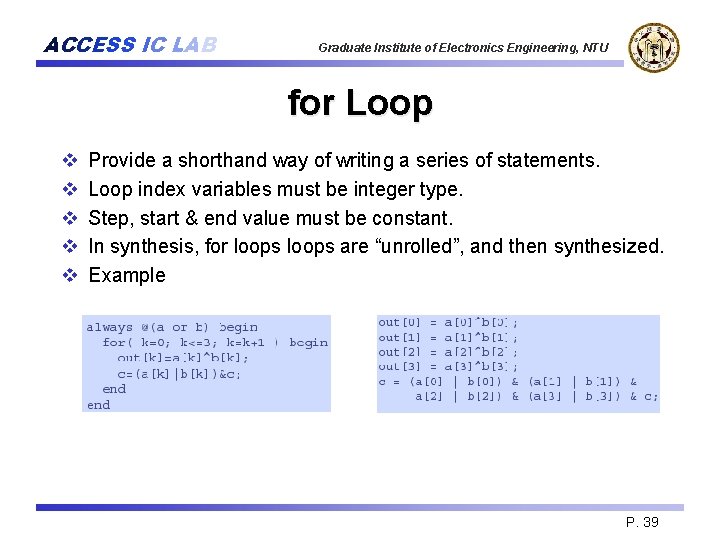

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU for Loop v v v Provide a shorthand way of writing a series of statements. Loop index variables must be integer type. Step, start & end value must be constant. In synthesis, for loops are “unrolled”, and then synthesized. Example P. 39

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Write Efficient HDL Code v Use parentheses control complex structure of a design. v Use operator bit-width efficiently. v Data-path Duplication v Operator in “if” statement P. 40

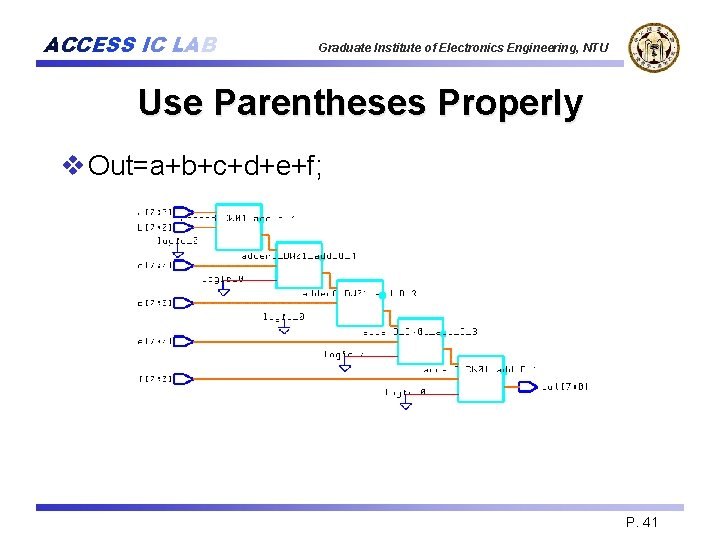

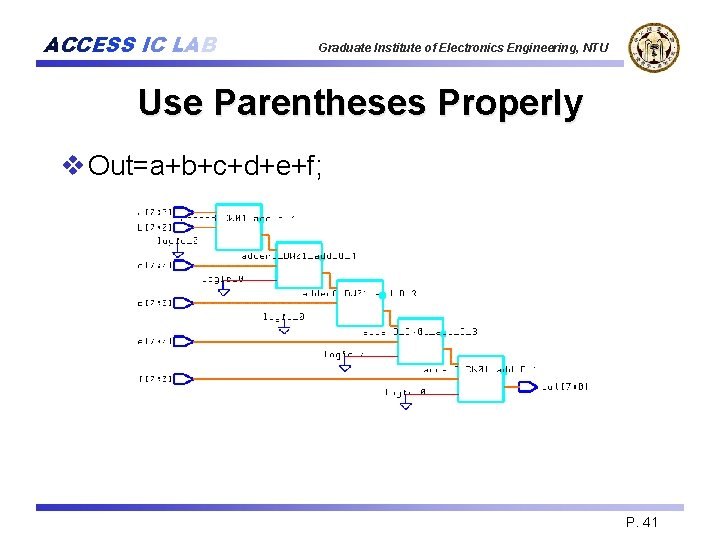

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Use Parentheses Properly v Out=a+b+c+d+e+f; P. 41

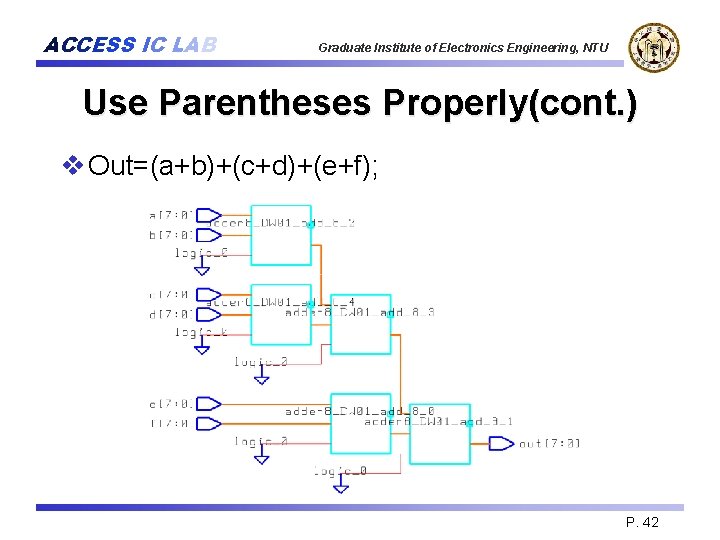

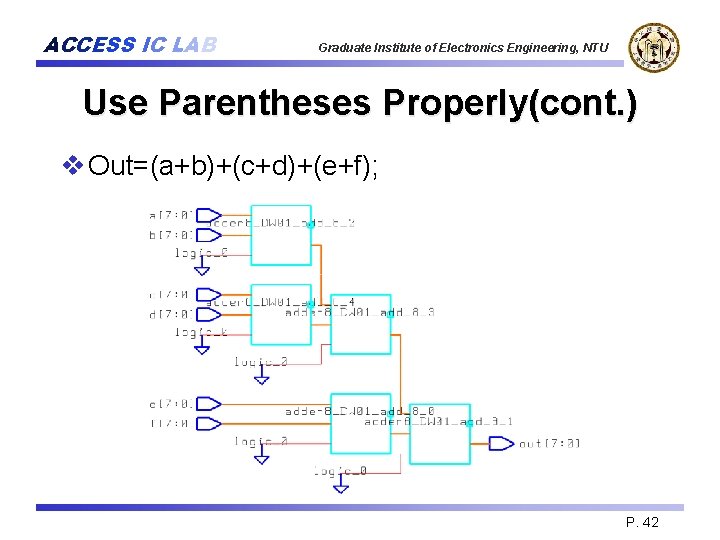

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Use Parentheses Properly(cont. ) v Out=(a+b)+(c+d)+(e+f); P. 42

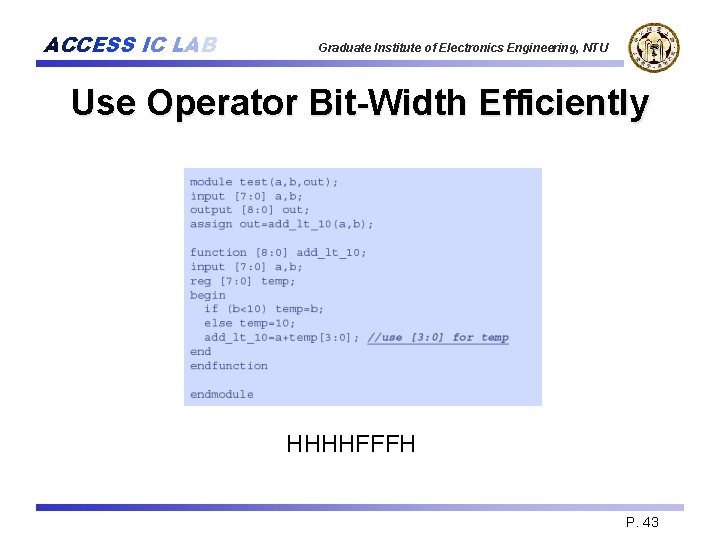

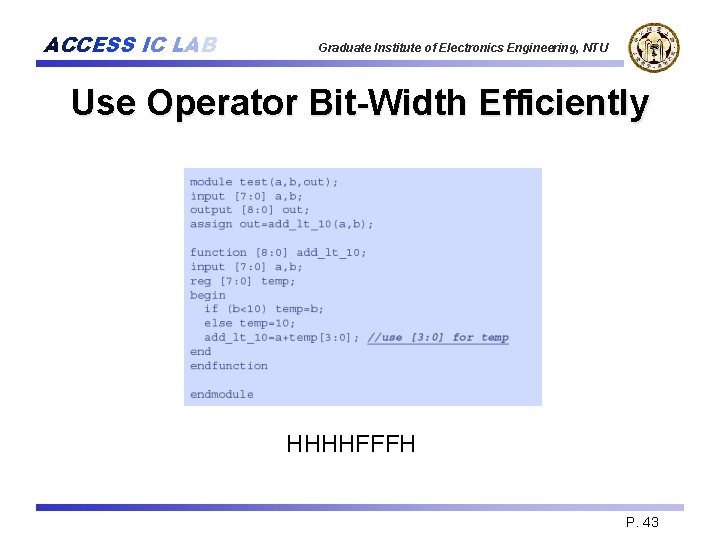

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Use Operator Bit-Width Efficiently HHHHFFFH P. 43

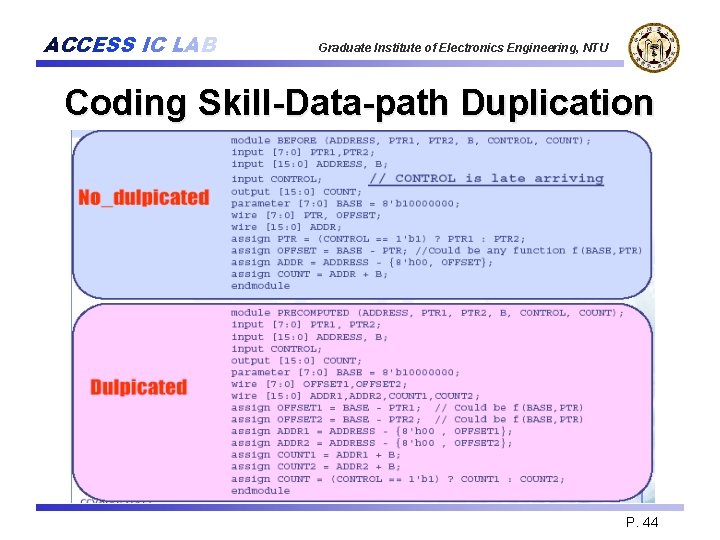

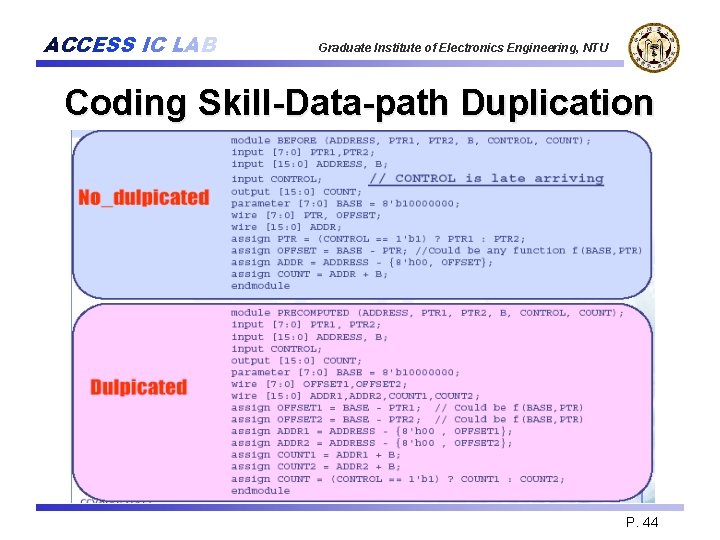

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Coding Skill-Data-path Duplication P. 44

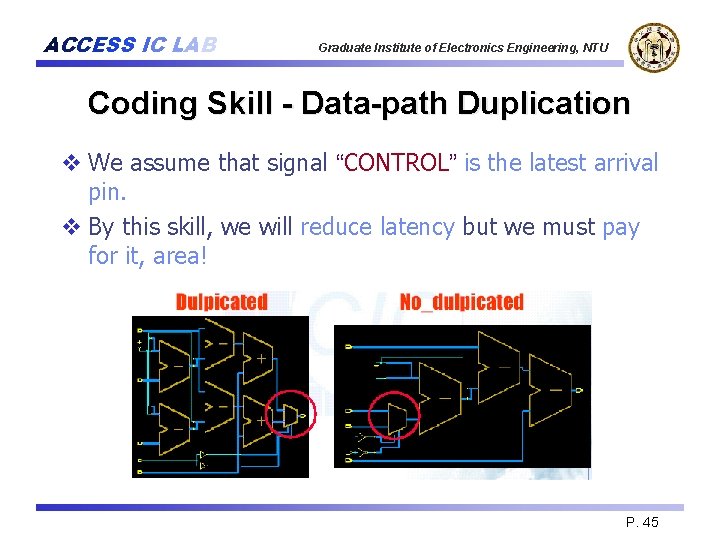

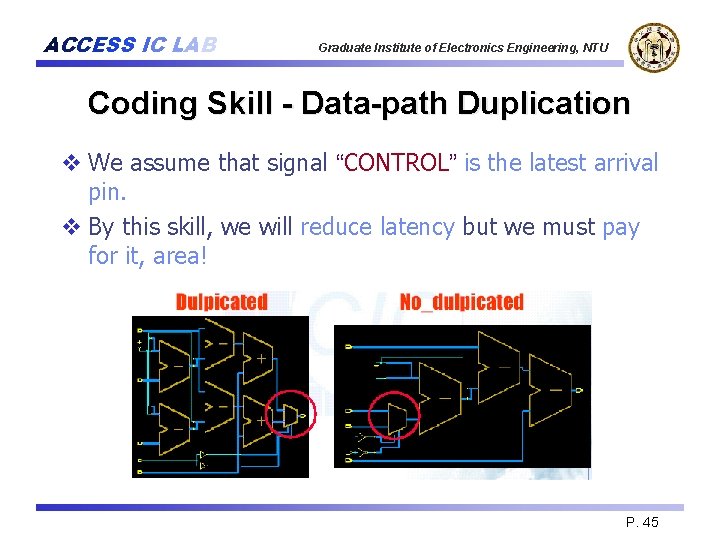

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Coding Skill - Data-path Duplication v We assume that signal “CONTROL” is the latest arrival pin. v By this skill, we will reduce latency but we must pay for it, area! P. 45

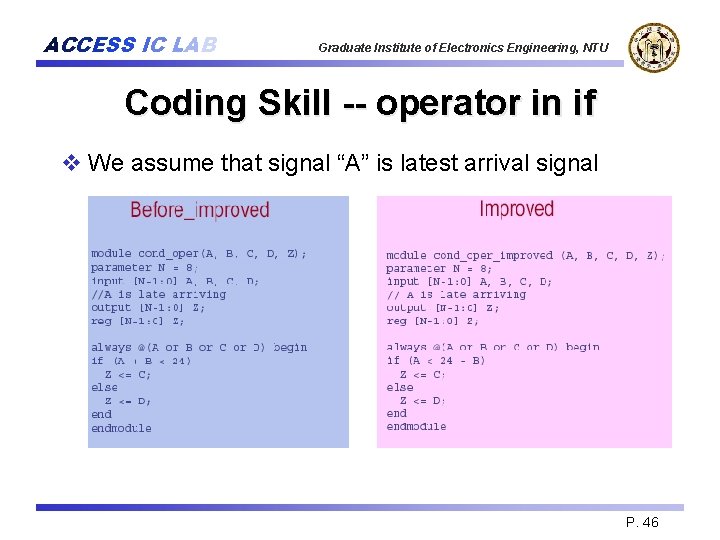

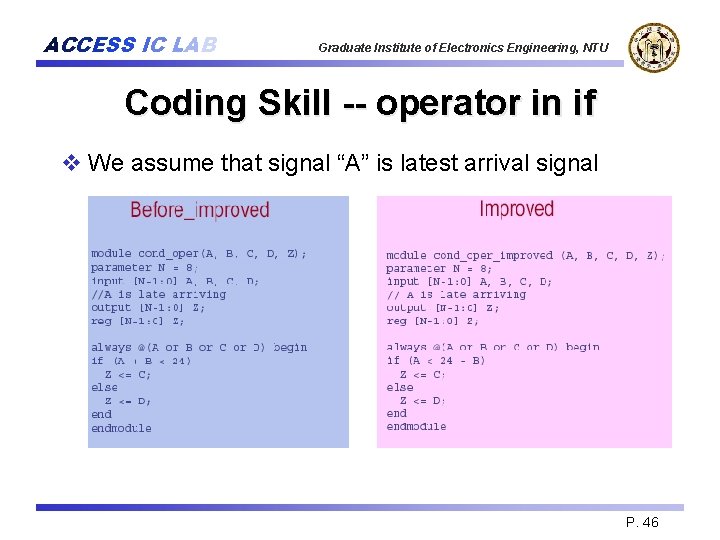

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Coding Skill -- operator in if v We assume that signal “A” is latest arrival signal P. 46

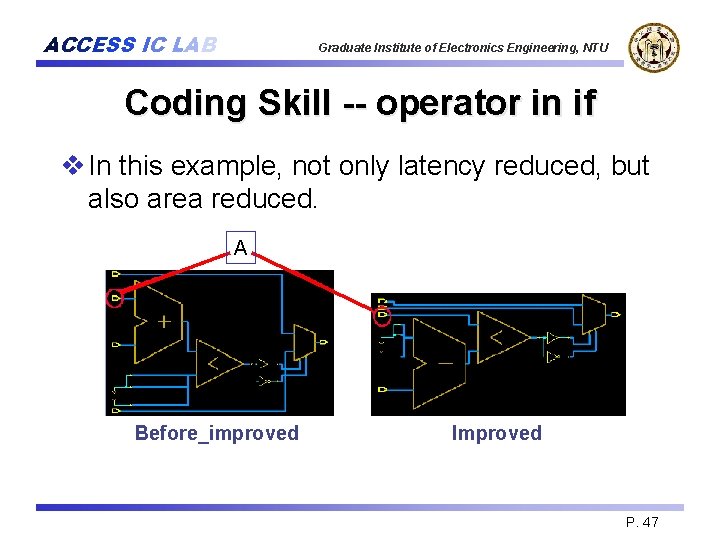

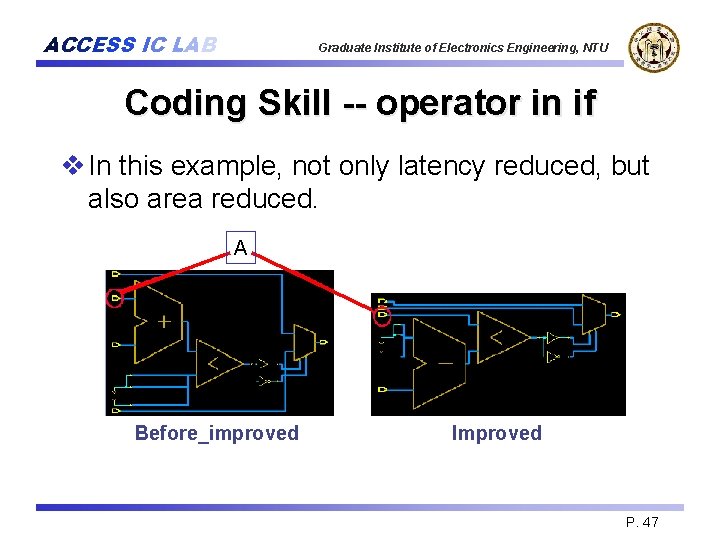

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Coding Skill -- operator in if v In this example, not only latency reduced, but also area reduced. A Before_improved Improved P. 47