Graduate Institute of Electronics Engineering NTU LowPower CMOS

- Slides: 47

Graduate Institute of Electronics Engineering, NTU Low-Power CMOS Design For Advanced VLSI Design and VLSI Signal Processing Courses 12 -04 -2002 台大電機系 吳安宇 教授 ACCESS IC LAB

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Data Source v “Low-power Circuit Design Basics, ” by Prof. Jan M. Rabaey, UC Berkerly, in tutorial of ISCAS, London, 1994. v “Can we simultaneously achieve High Speed and Low Power in IC Design? ” by Prof. Wentai Liu in 7 th VLSI/CAD Symposium, 1996. v Chapter 17 of Textbook. 台灣大學 吳安宇 教授 2

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Low Power Design – An Emerging Discipline v Historical figure of merit for VLSI design – performance (circuit speed) and chip area (circuit density/cost). But v Power dissipation is now an important metric in VLSI design. v No single major source for power savings across all design levels – Required a new way of THINKING!!! v Companies lack the basic power-conscious culture and designers need to be educated in this respect. v Overall Goal – To reduce power dissipations but maintaining adequate throughput rate. 台灣大學 吳安宇 教授 3

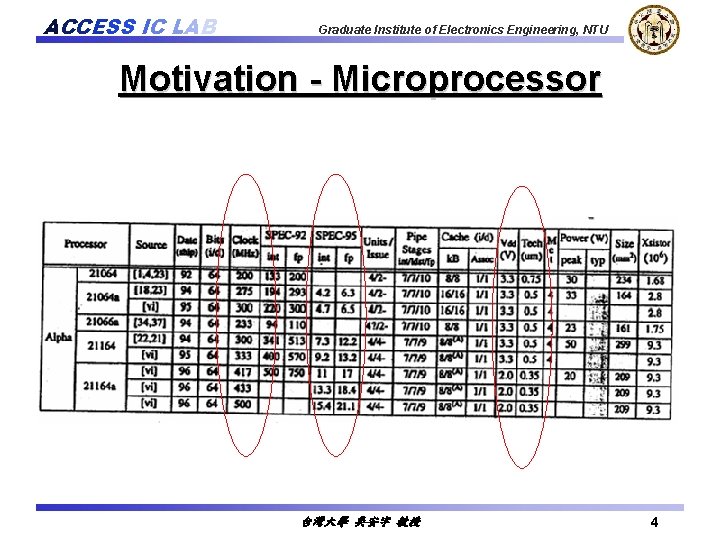

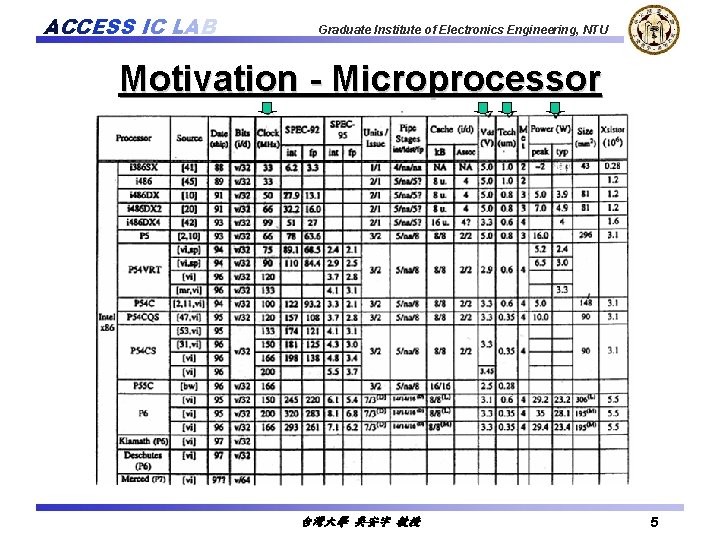

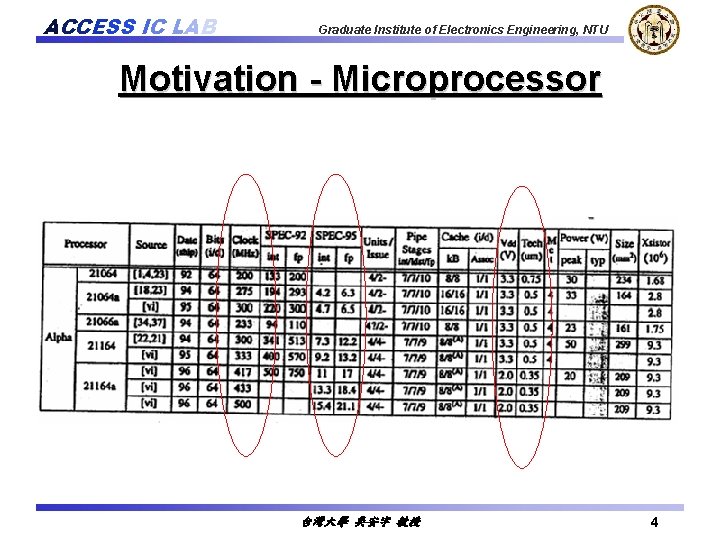

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Motivation - Microprocessor 台灣大學 吳安宇 教授 4

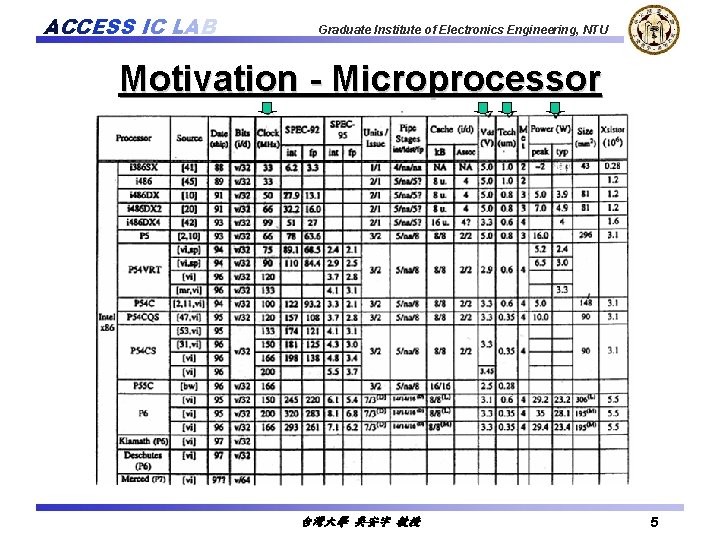

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Motivation - Microprocessor 台灣大學 吳安宇 教授 5

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Competitive Reasons – Low Power v Battery Powered Systems – Extended Battery Life and reduce weight and size. v High-Performance Systems v Cost Ø Package (chip carrier, heat sink, card slots, plenum, …) Ø Power Systems (supplies, distribution, regulators, …) Ø Fans (noise, power, reliability, area, …) Ø Operating cost to customer – Energy Star issue. v Reliability Ø Failure rate increase by 4 X for Tj @ 110 C vs 70 C Ø Mission critical operation at 100 C v Size and Weight – Product footprint (office and deskspace) 台灣大學 吳安宇 教授 6

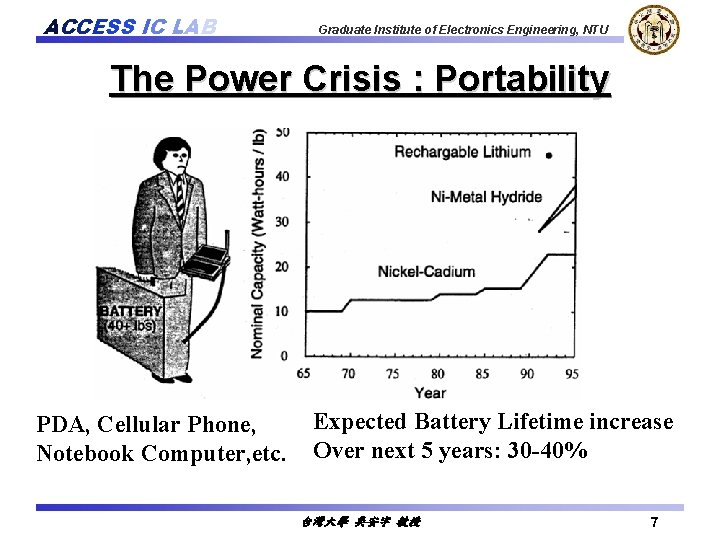

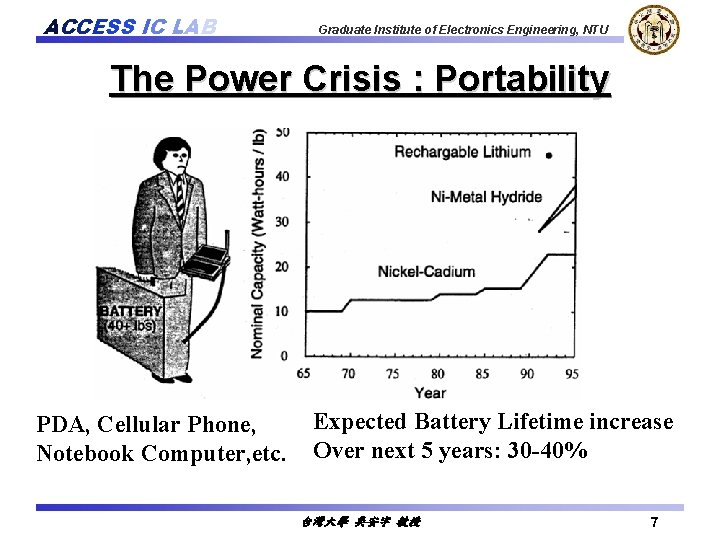

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU The Power Crisis : Portability PDA, Cellular Phone, Notebook Computer, etc. Expected Battery Lifetime increase Over next 5 years: 30 -40% 台灣大學 吳安宇 教授 7

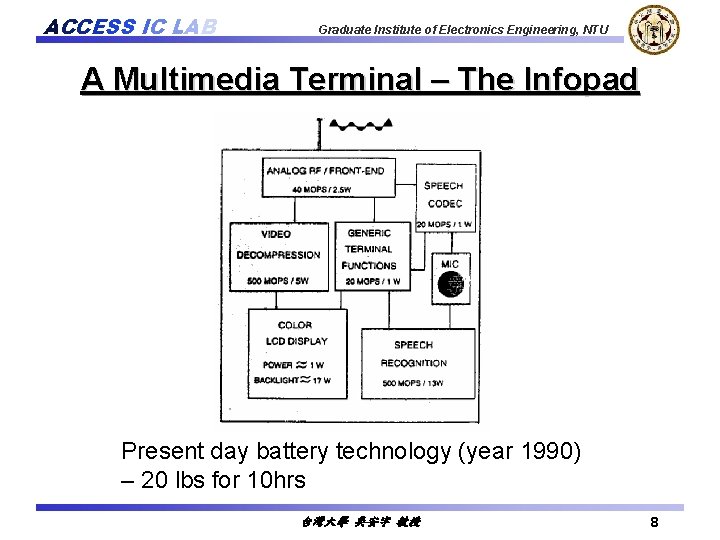

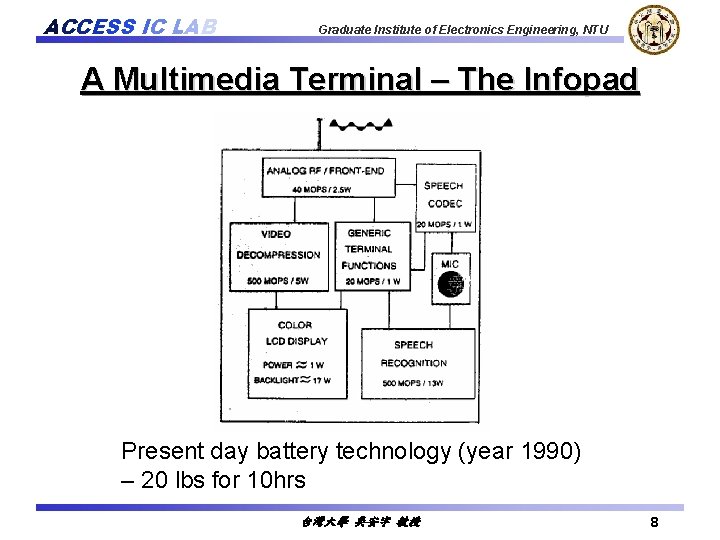

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU A Multimedia Terminal – The Infopad Present day battery technology (year 1990) – 20 lbs for 10 hrs 台灣大學 吳安宇 教授 8

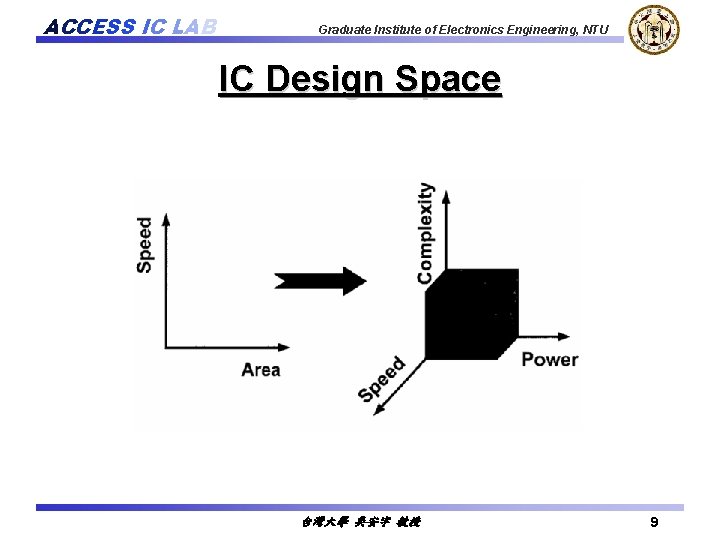

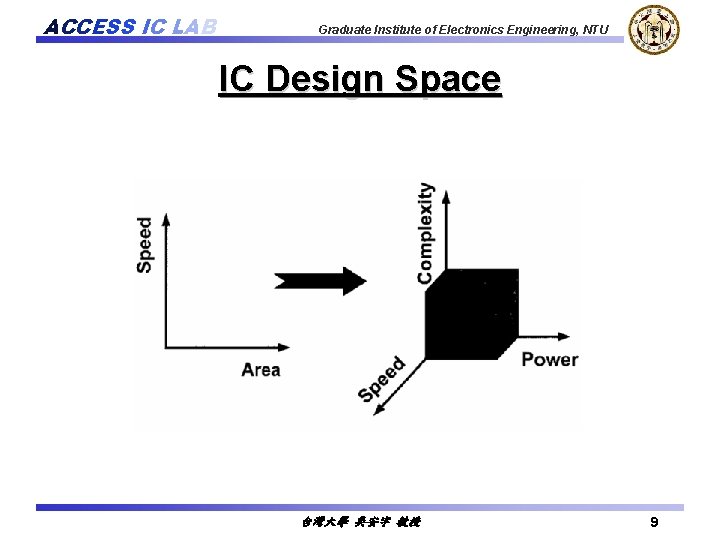

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU IC Design Space 台灣大學 吳安宇 教授 9

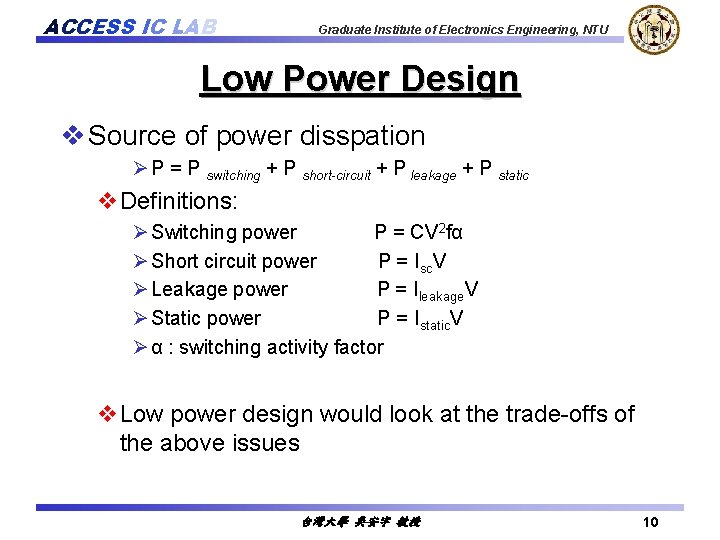

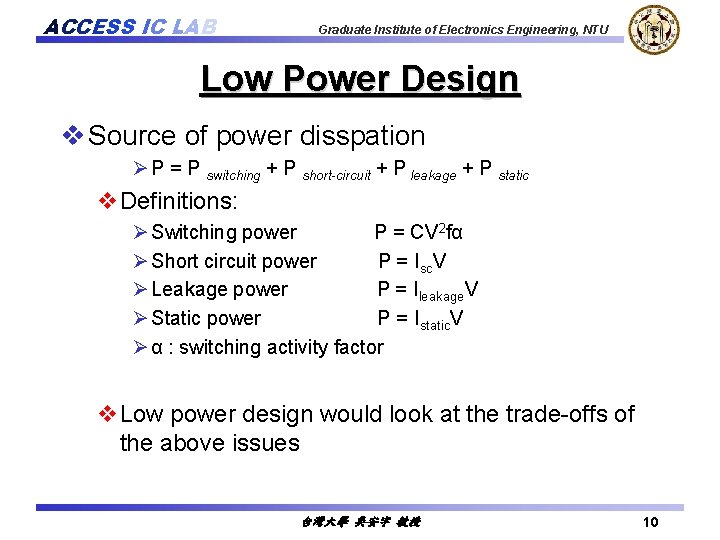

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Low Power Design v Source of power disspation Ø P = P switching + P short-circuit + P leakage + P static v. Definitions: Ø Switching power P = CV 2 fα Ø Short circuit power P = Isc. V Ø Leakage power P = Ileakage. V Ø Static power P = Istatic. V Ø α : switching activity factor v. Low power design would look at the trade-offs of the above issues 台灣大學 吳安宇 教授 10

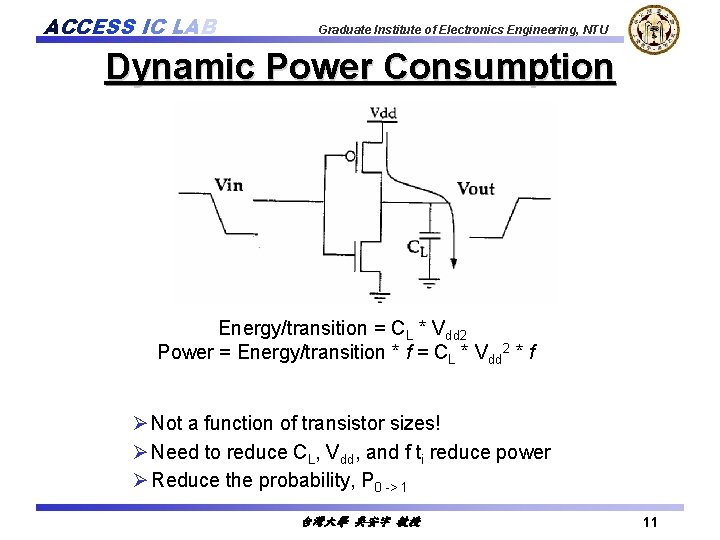

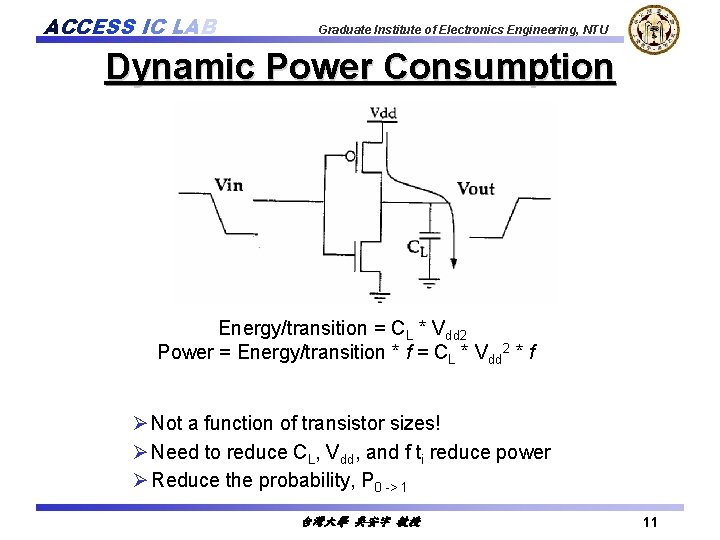

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Dynamic Power Consumption Energy/transition = CL * Vdd 2 Power = Energy/transition * f = CL * Vdd 2 * f Ø Not a function of transistor sizes! Ø Need to reduce CL, Vdd, and f ti reduce power Ø Reduce the probability, P 0 -> 1 台灣大學 吳安宇 教授 11

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Dynamic Power Consumption Extended v Power = Energy/transition * transition rate = CL * Vdd 2 * f 0 ->1 = CL * Vdd 2 * P 0 ->1 * f = CEFF * Vdd 2 * f v Power Dissipation is Data Dependent Function of Switching Activity v. CEFF = Effective Capacitance = CL * P 0 ->1 台灣大學 吳安宇 教授 12

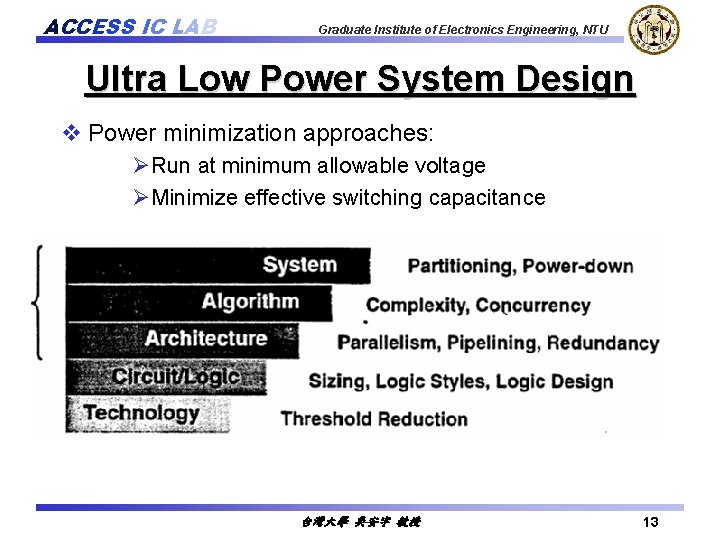

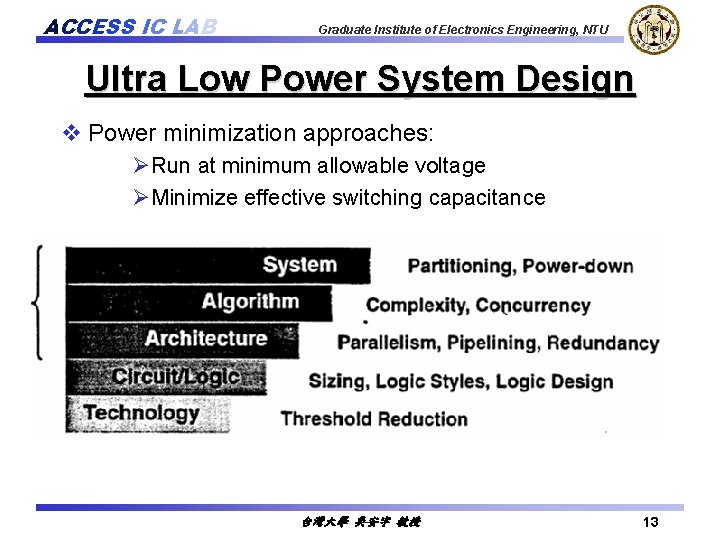

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Ultra Low Power System Design v Power minimization approaches: ØRun at minimum allowable voltage ØMinimize effective switching capacitance 台灣大學 吳安宇 教授 13

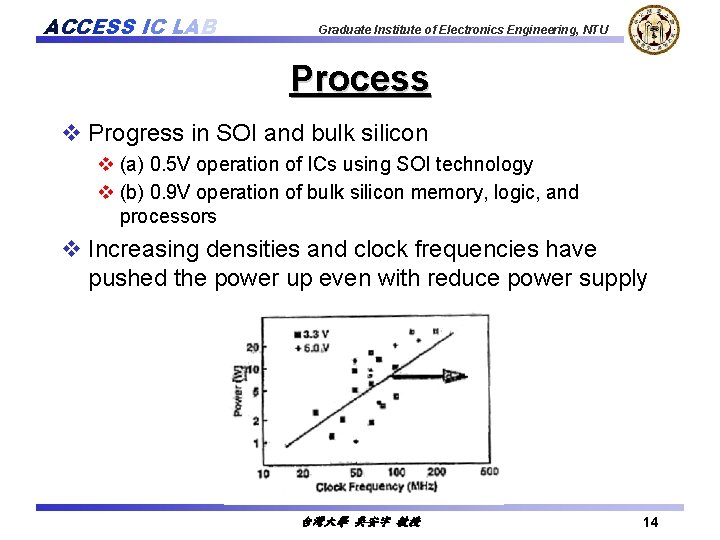

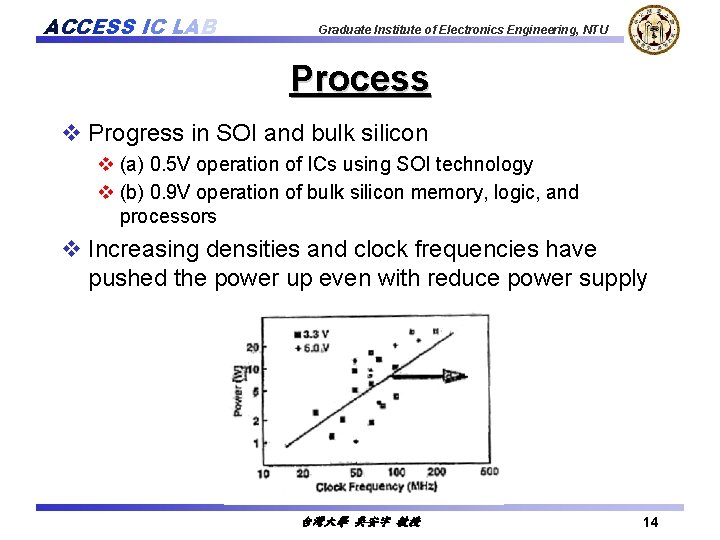

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Process v Progress in SOI and bulk silicon v (a) 0. 5 V operation of ICs using SOI technology v (b) 0. 9 V operation of bulk silicon memory, logic, and processors v Increasing densities and clock frequencies have pushed the power up even with reduce power supply 台灣大學 吳安宇 教授 14

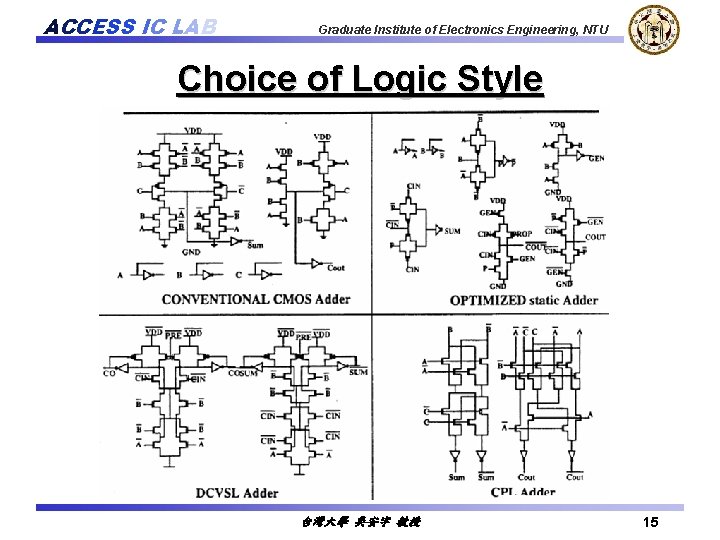

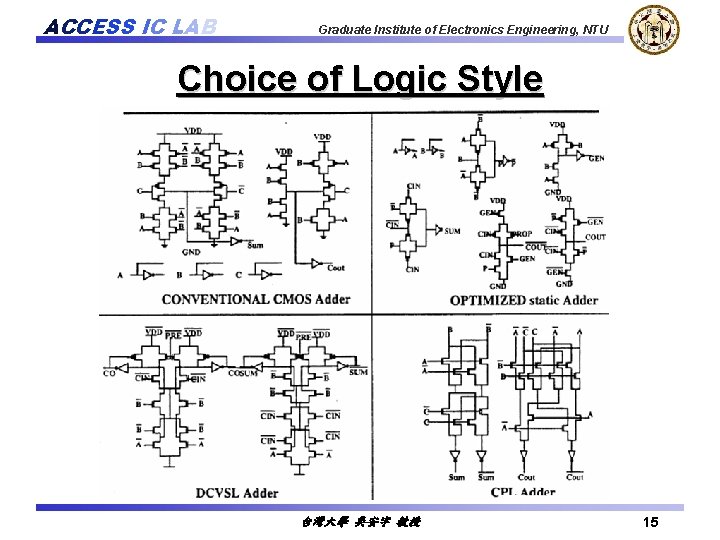

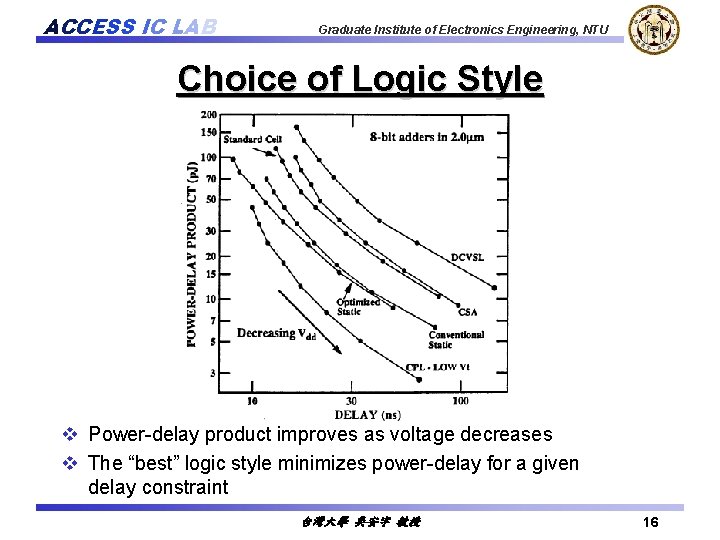

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Choice of Logic Style 台灣大學 吳安宇 教授 15

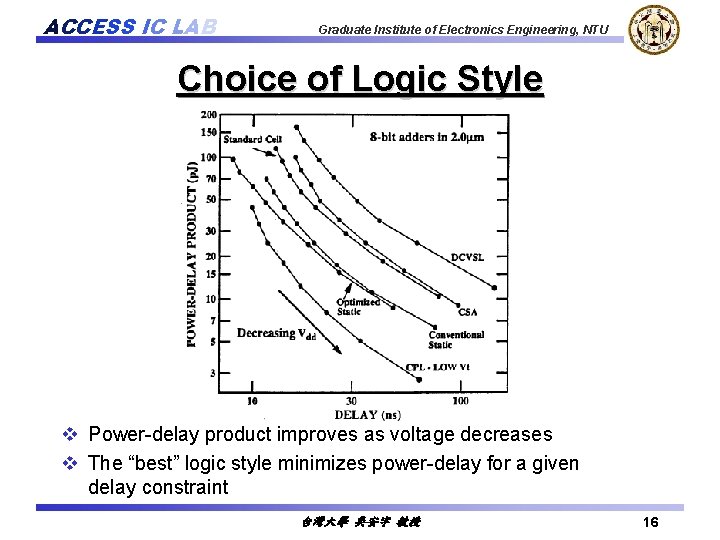

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Choice of Logic Style v Power-delay product improves as voltage decreases v The “best” logic style minimizes power-delay for a given delay constraint 台灣大學 吳安宇 教授 16

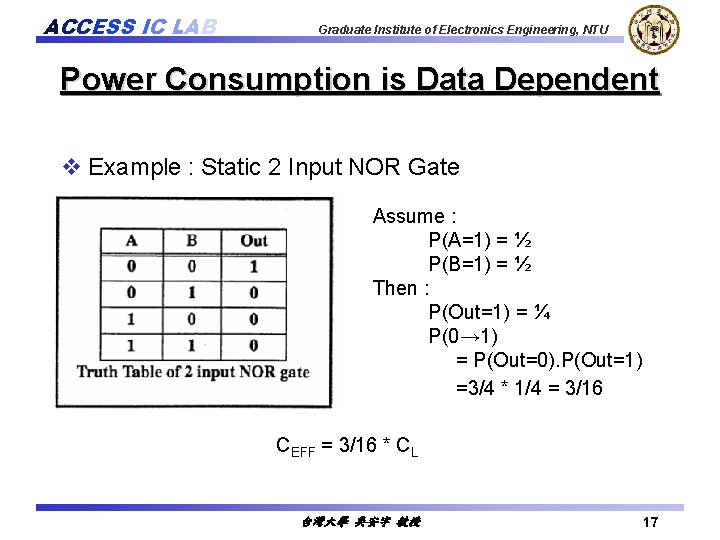

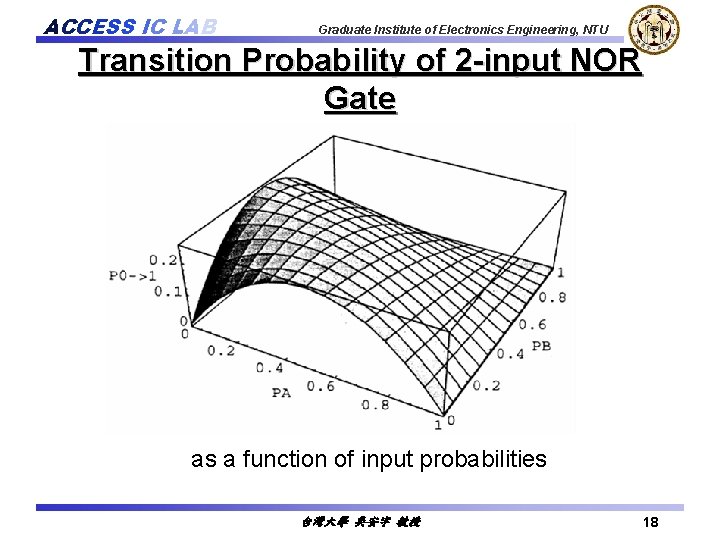

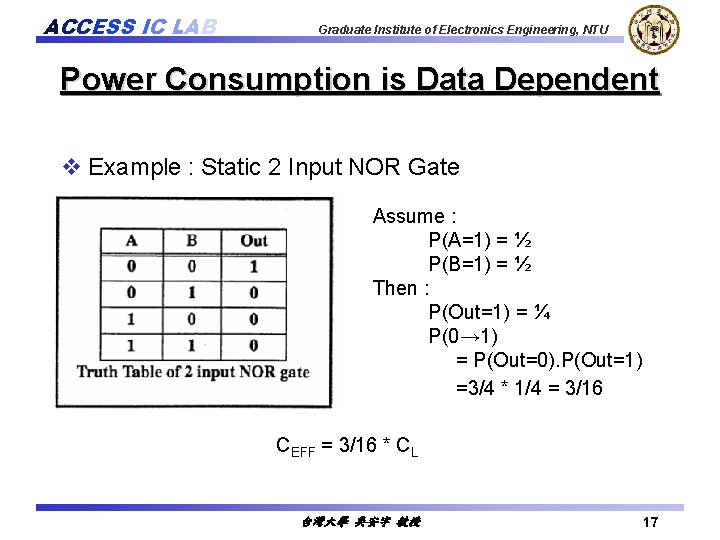

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Power Consumption is Data Dependent v Example : Static 2 Input NOR Gate Assume : P(A=1) = ½ P(B=1) = ½ Then : P(Out=1) = ¼ P(0→ 1) = P(Out=0). P(Out=1) =3/4 * 1/4 = 3/16 CEFF = 3/16 * CL 台灣大學 吳安宇 教授 17

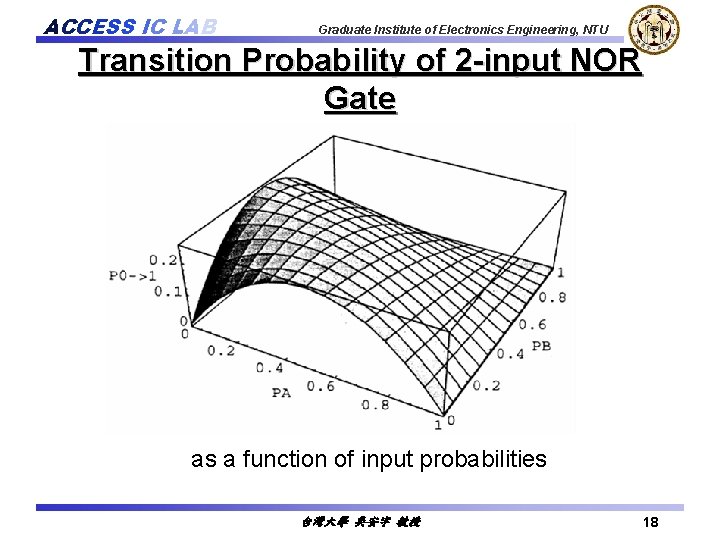

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Transition Probability of 2 -input NOR Gate as a function of input probabilities 台灣大學 吳安宇 教授 18

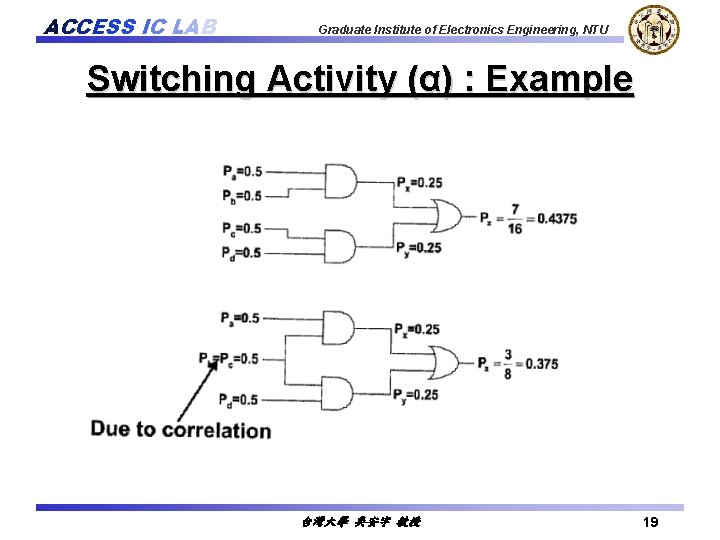

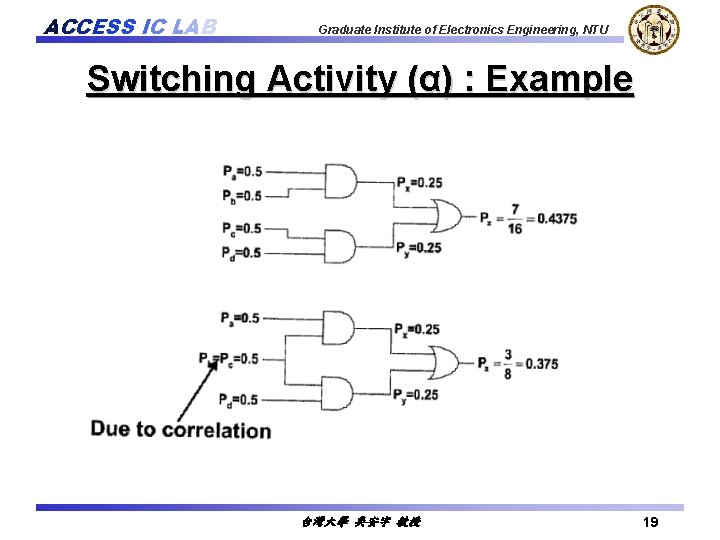

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Switching Activity (α) : Example 台灣大學 吳安宇 教授 19

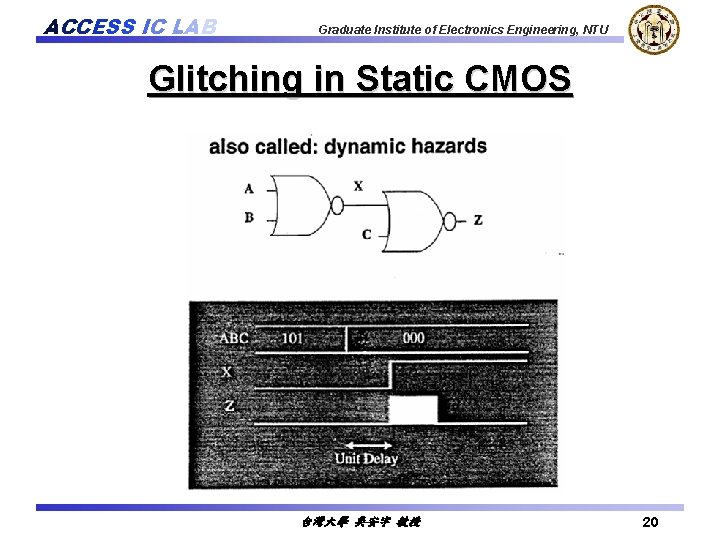

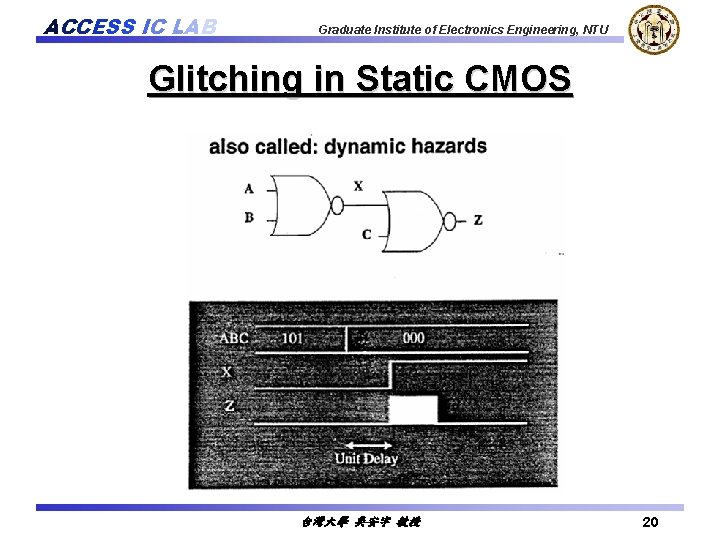

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Glitching in Static CMOS 台灣大學 吳安宇 教授 20

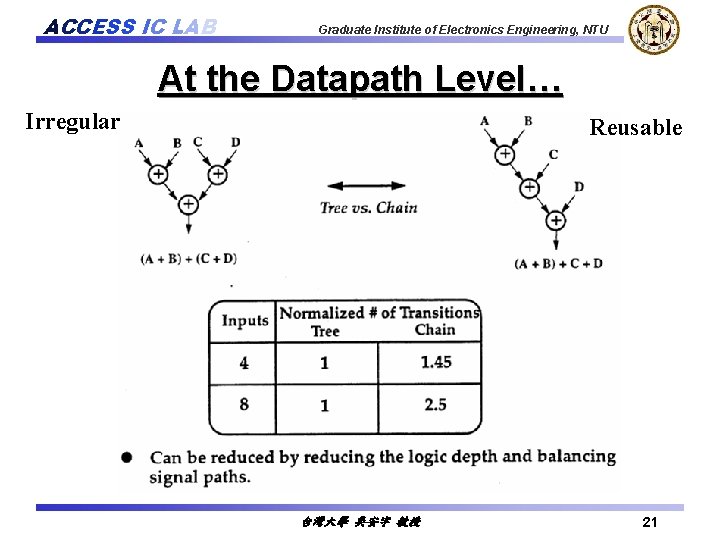

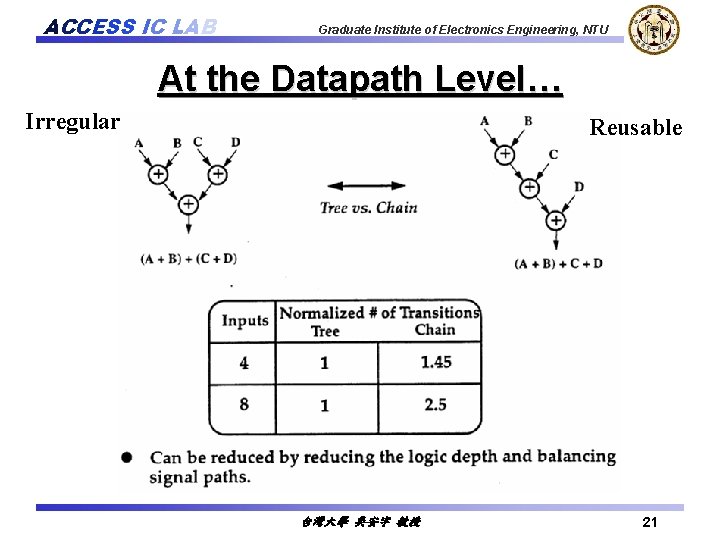

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU At the Datapath Level… Irregular Reusable 台灣大學 吳安宇 教授 21

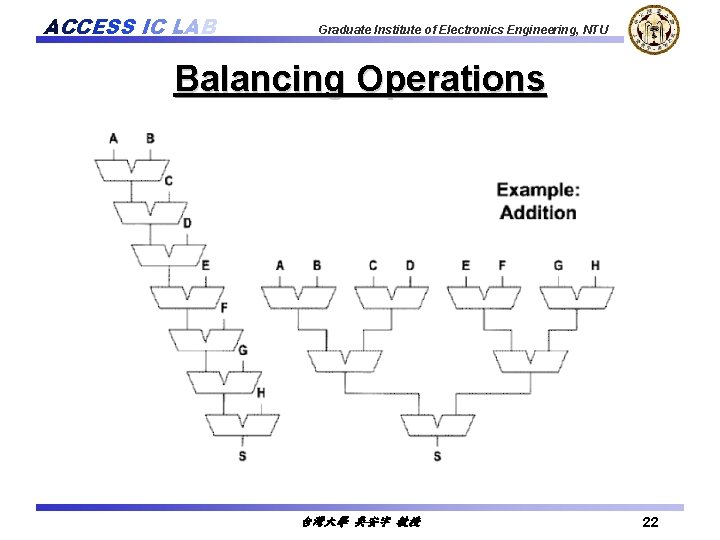

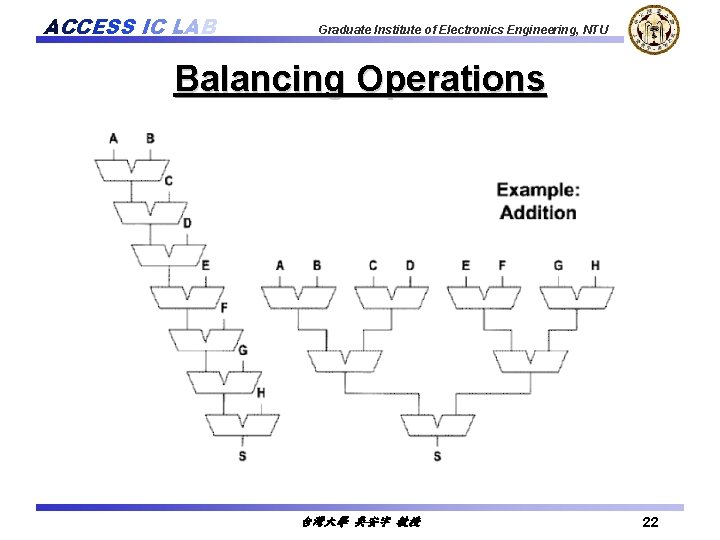

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Balancing Operations 台灣大學 吳安宇 教授 22

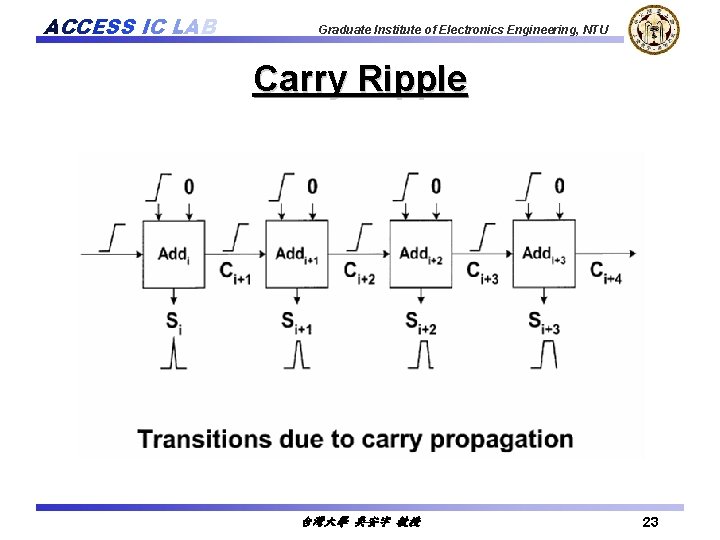

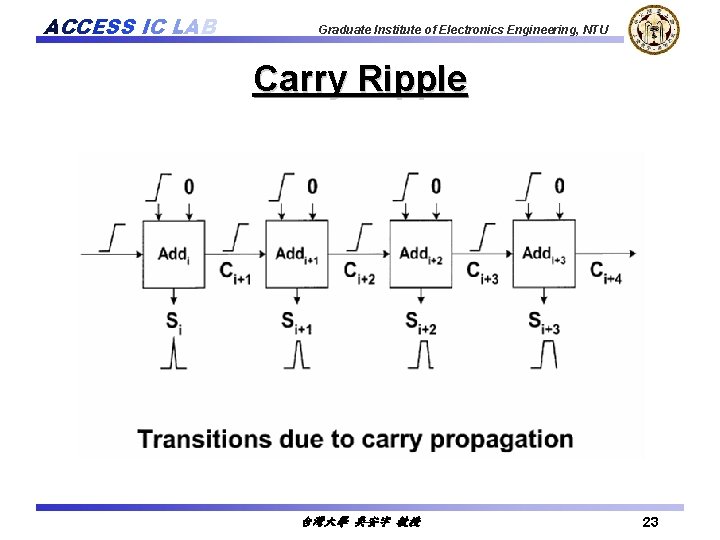

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Carry Ripple 台灣大學 吳安宇 教授 23

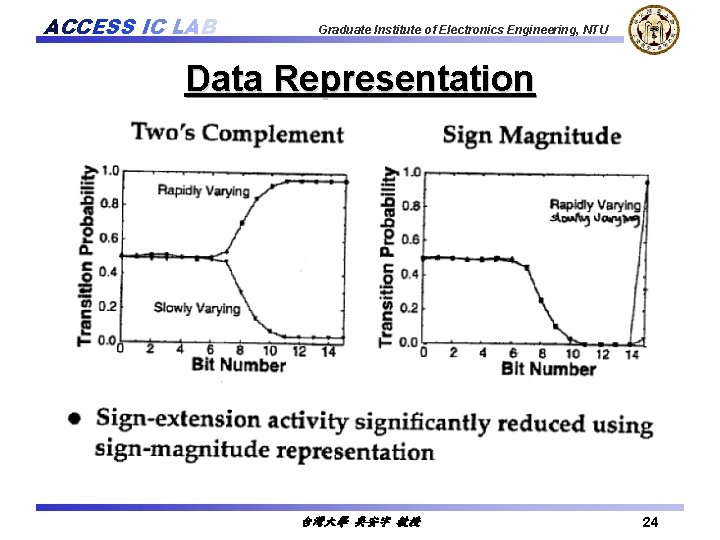

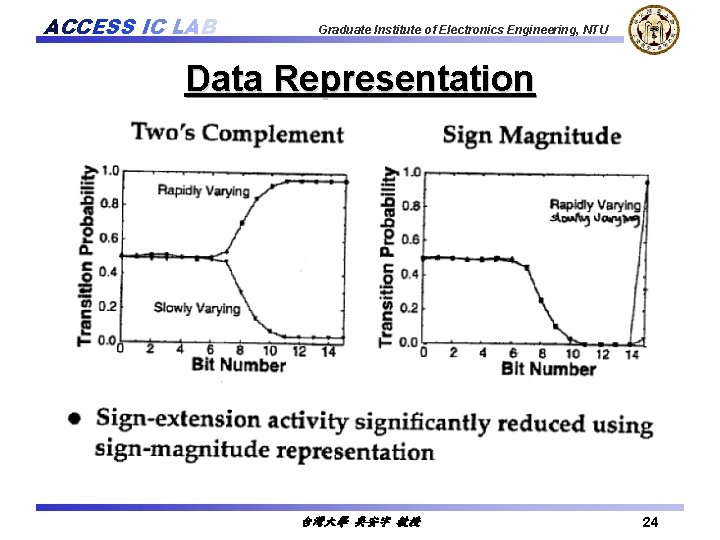

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Data Representation 台灣大學 吳安宇 教授 24

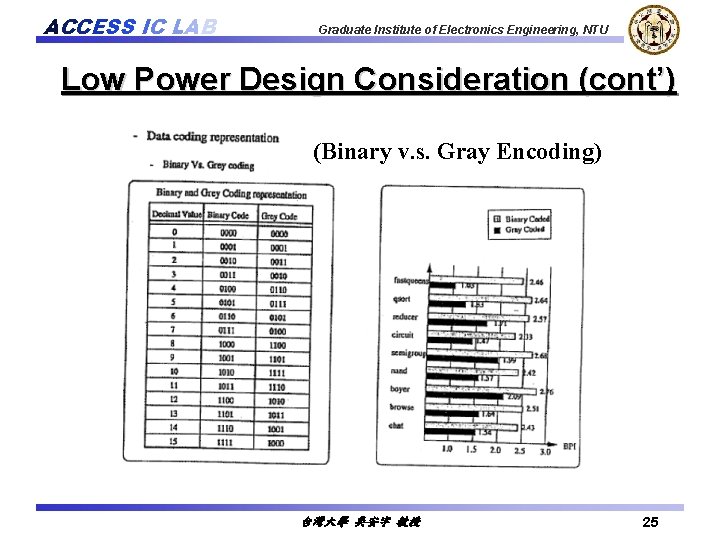

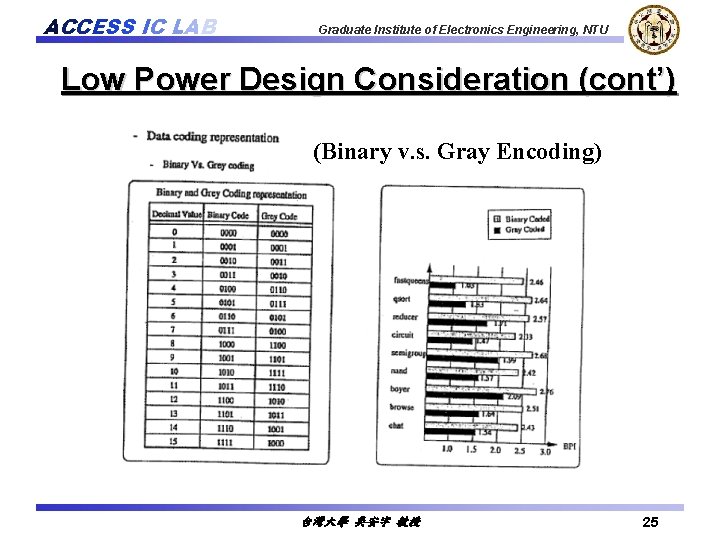

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Low Power Design Consideration (cont’) (Binary v. s. Gray Encoding) 台灣大學 吳安宇 教授 25

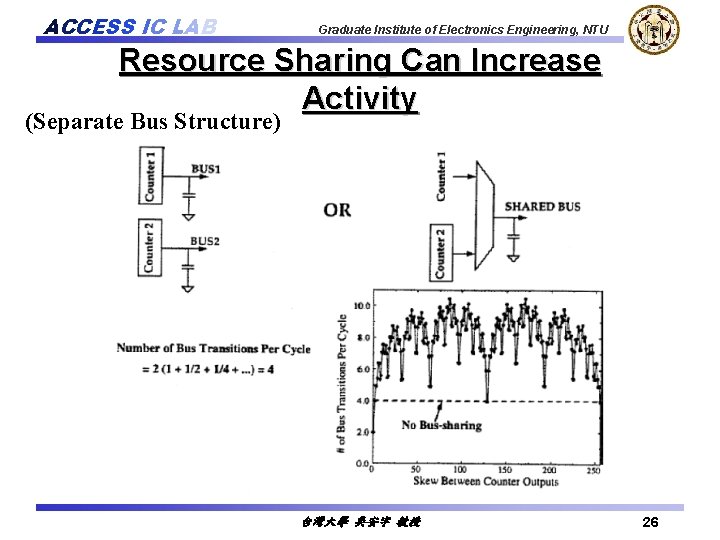

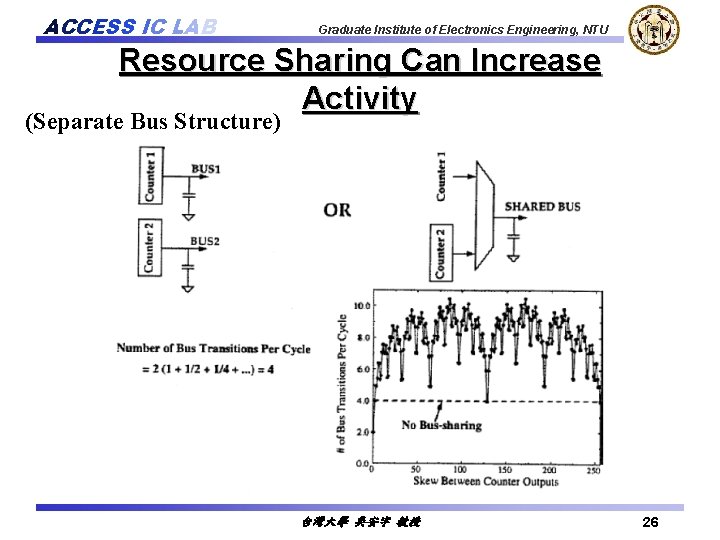

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Resource Sharing Can Increase Activity (Separate Bus Structure) 台灣大學 吳安宇 教授 26

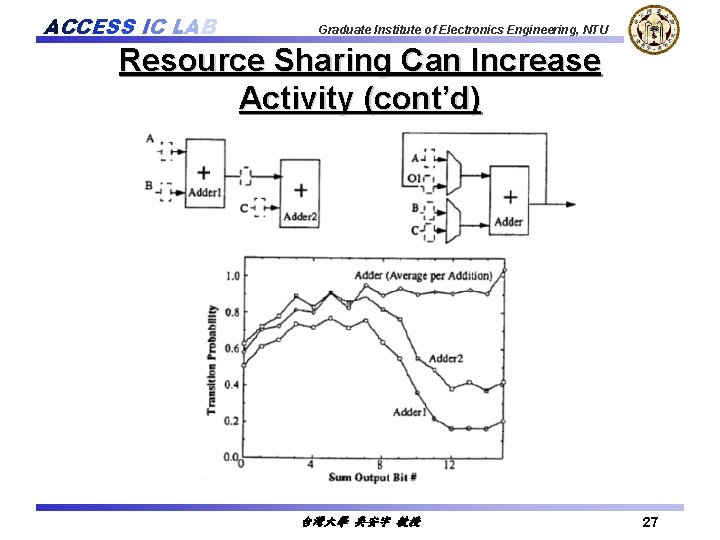

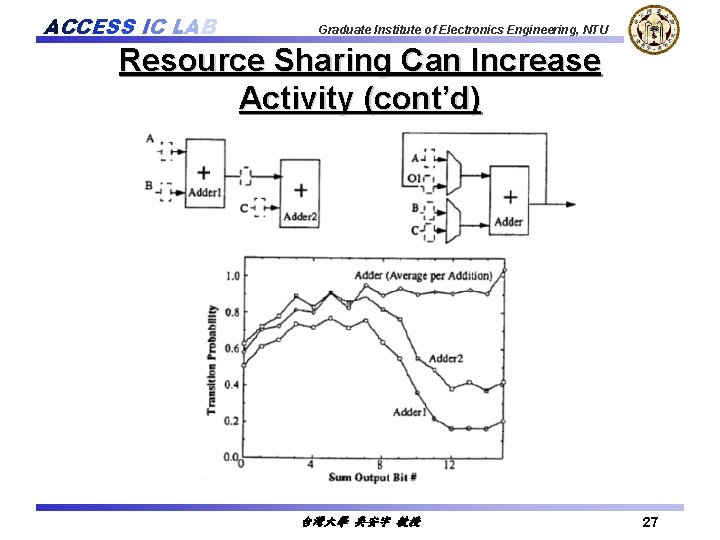

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Resource Sharing Can Increase Activity (cont’d) 台灣大學 吳安宇 教授 27

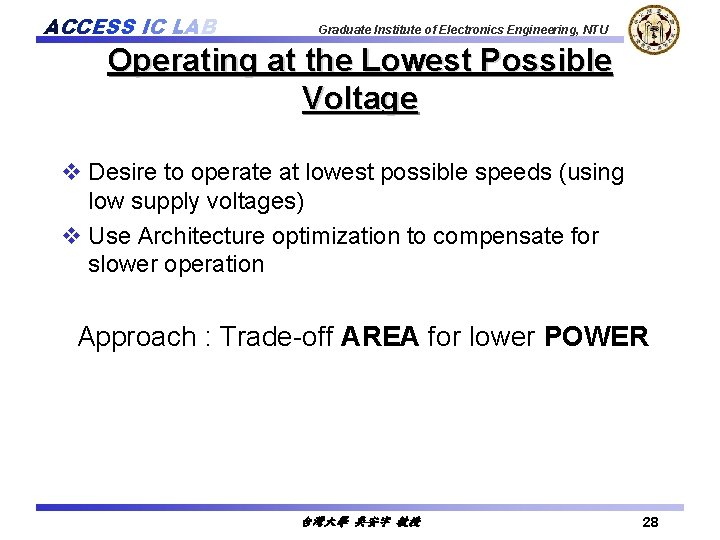

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Operating at the Lowest Possible Voltage v Desire to operate at lowest possible speeds (using low supply voltages) v Use Architecture optimization to compensate for slower operation Approach : Trade-off AREA for lower POWER 台灣大學 吳安宇 教授 28

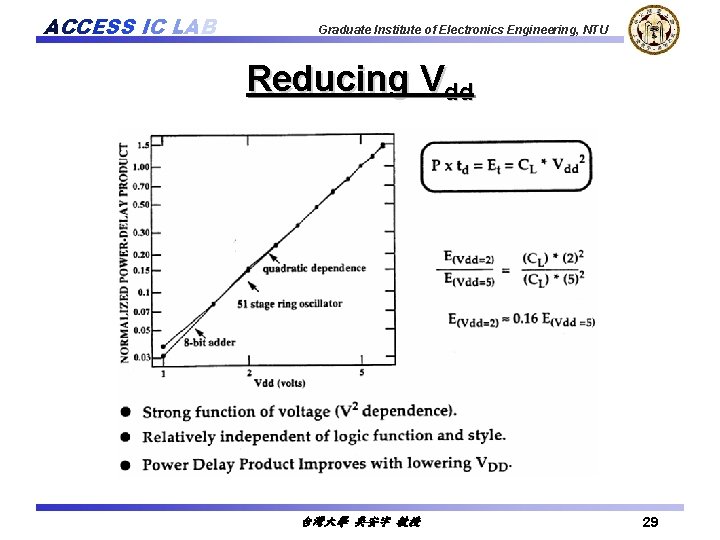

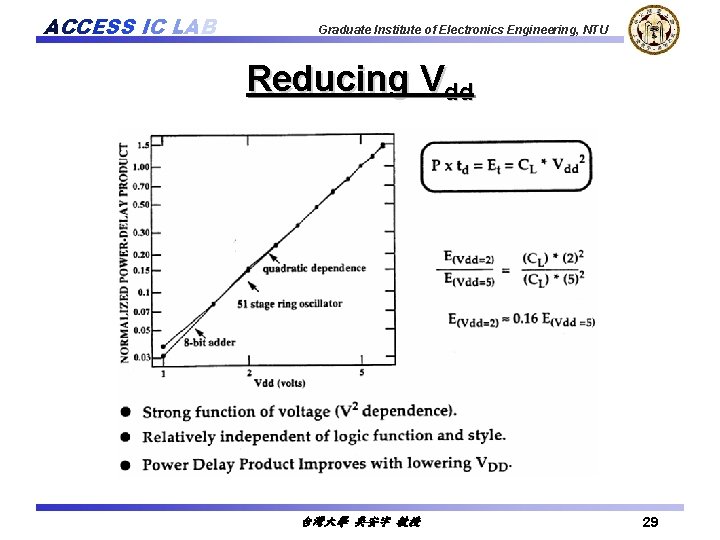

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Reducing Vdd 台灣大學 吳安宇 教授 29

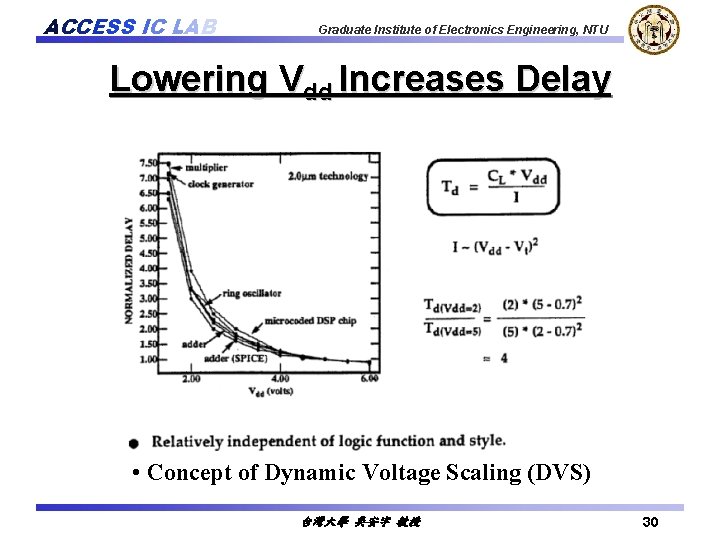

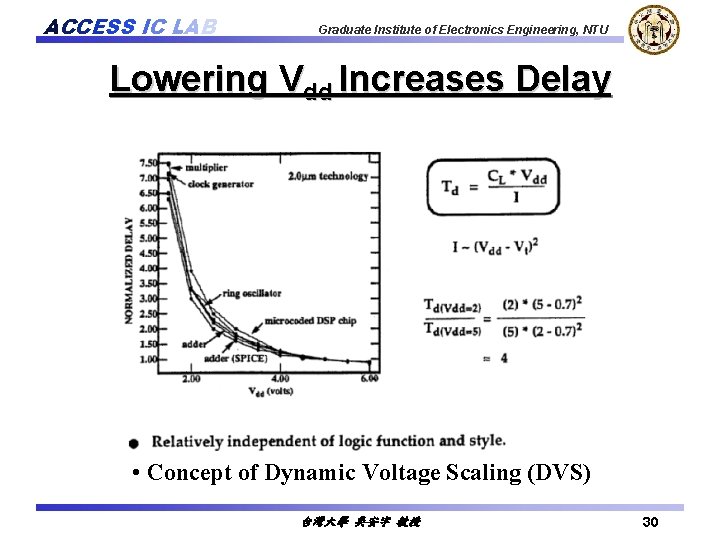

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Lowering Vdd Increases Delay • Concept of Dynamic Voltage Scaling (DVS) 台灣大學 吳安宇 教授 30

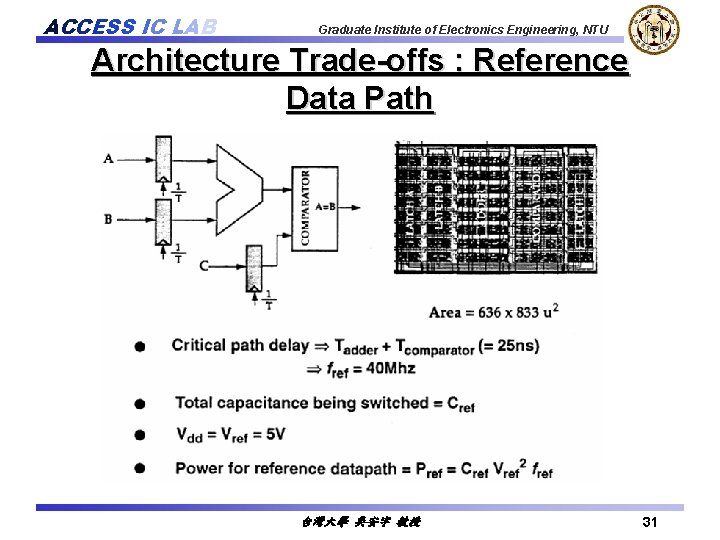

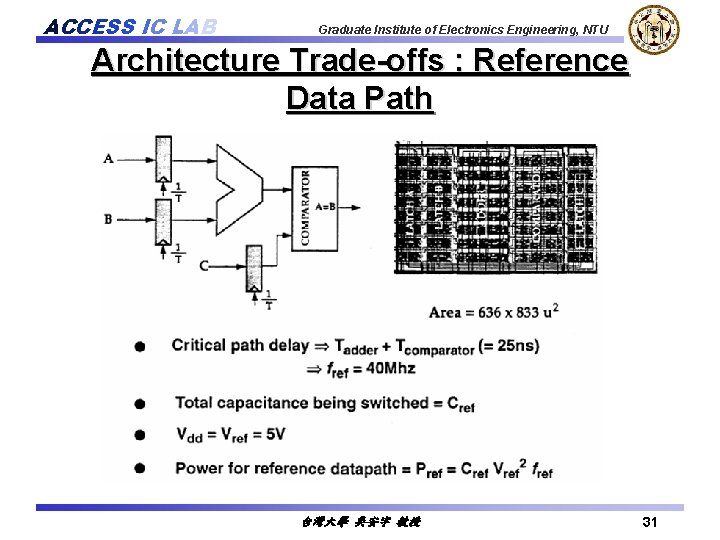

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Architecture Trade-offs : Reference Data Path 台灣大學 吳安宇 教授 31

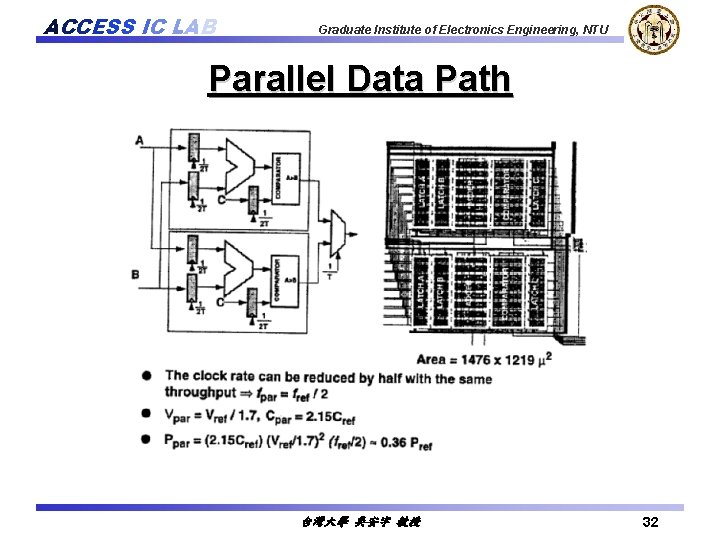

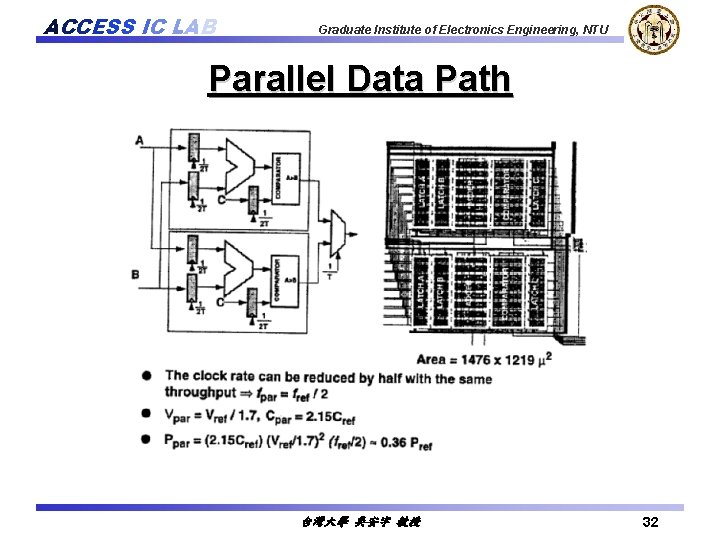

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Parallel Data Path 台灣大學 吳安宇 教授 32

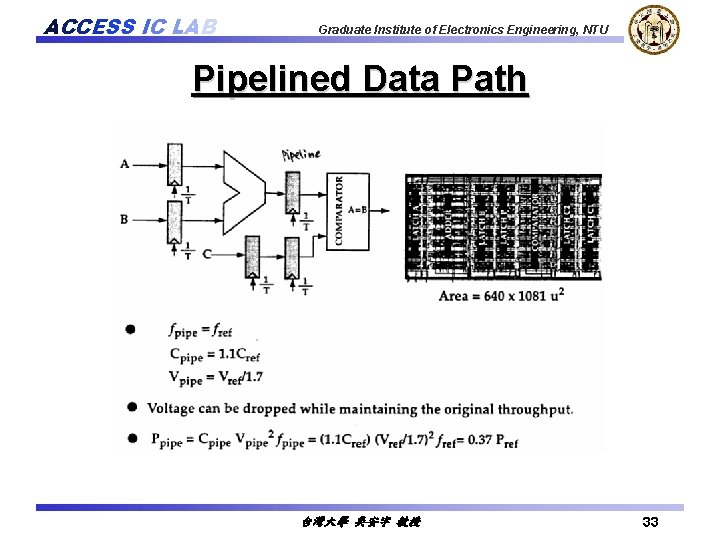

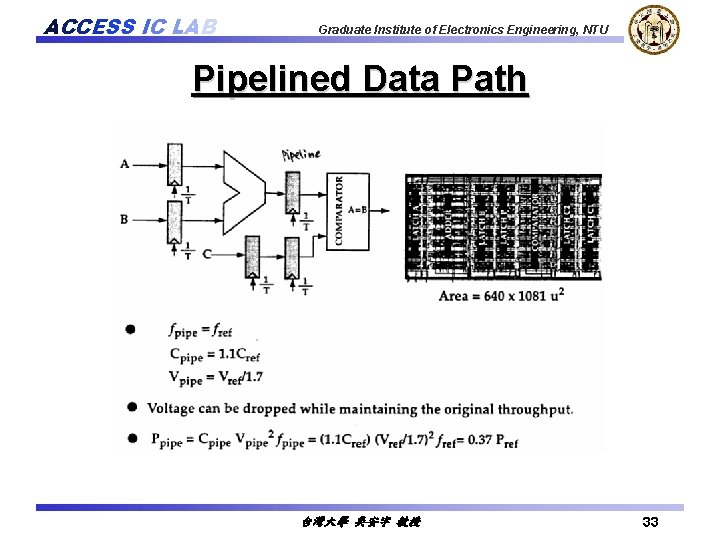

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Pipelined Data Path 台灣大學 吳安宇 教授 33

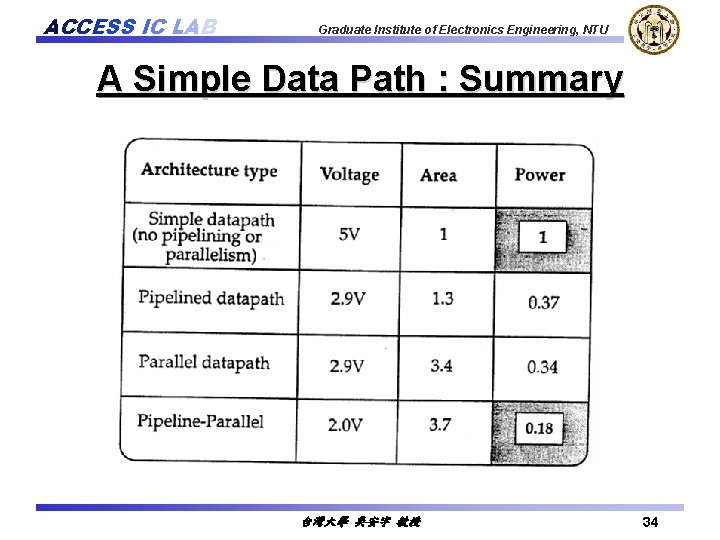

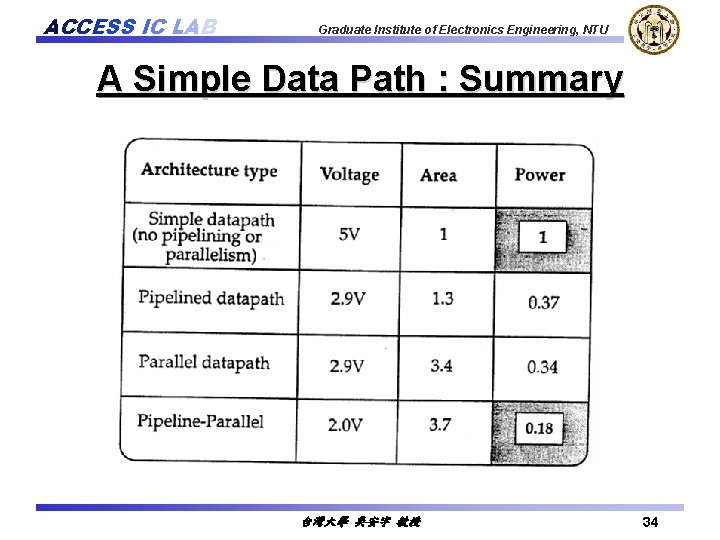

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU A Simple Data Path : Summary 台灣大學 吳安宇 教授 34

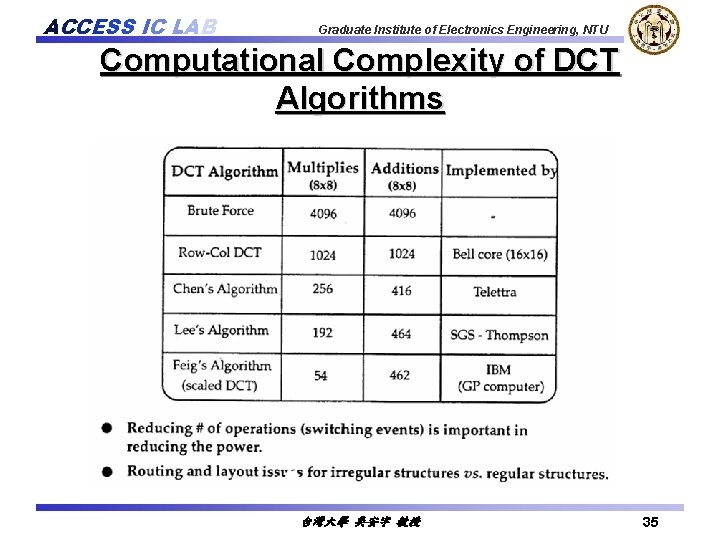

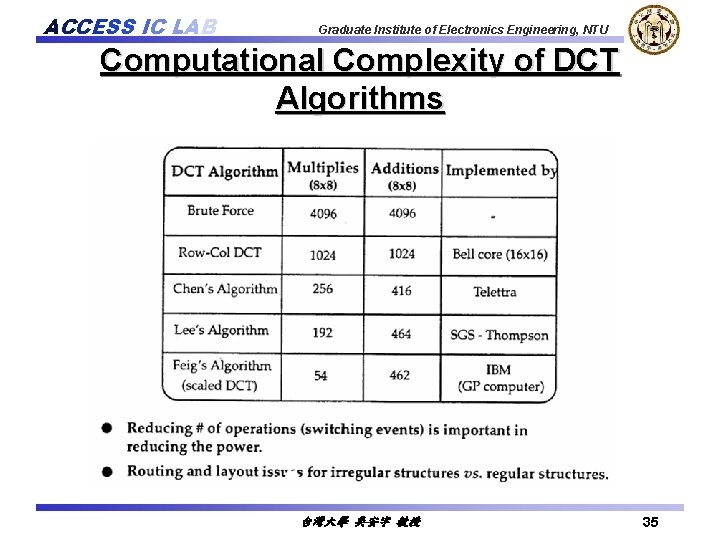

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Computational Complexity of DCT Algorithms 台灣大學 吳安宇 教授 35

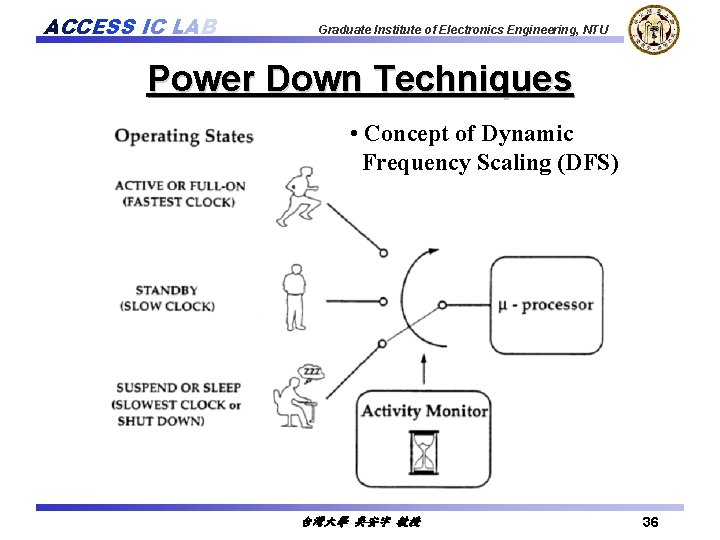

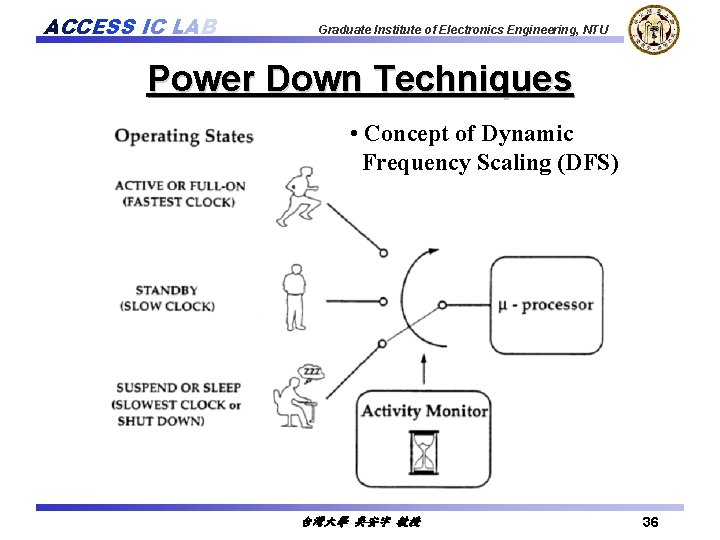

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Power Down Techniques • Concept of Dynamic Frequency Scaling (DFS) 台灣大學 吳安宇 教授 36

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Energy-efficient Software Coding v Potential for power reduction via software modification is relatively unexploited. v Code size and algorithmic efficiency can significantly affect energy dissipation v Pipelining at software level- VLIW coding style v Examples - 台灣大學 吳安宇 教授 37

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Power Hunger – Clock Network (Always Ticking) v H-Tree – design deficiencies based on Elmore delay model v PLL – every designer (digital or analog) should have the knowledge of PLL Ø Multiple frequencies in chips/systems – by PLL Ø Low main frequency, But Ø Jitter and Noise, Gain and Bandwidth, Pull-in and Lock Time, Stability … v Local time zone v Self-Timed v Asynchronous => Use Gated Clocks, Sleep Mode 台灣大學 吳安宇 教授 38

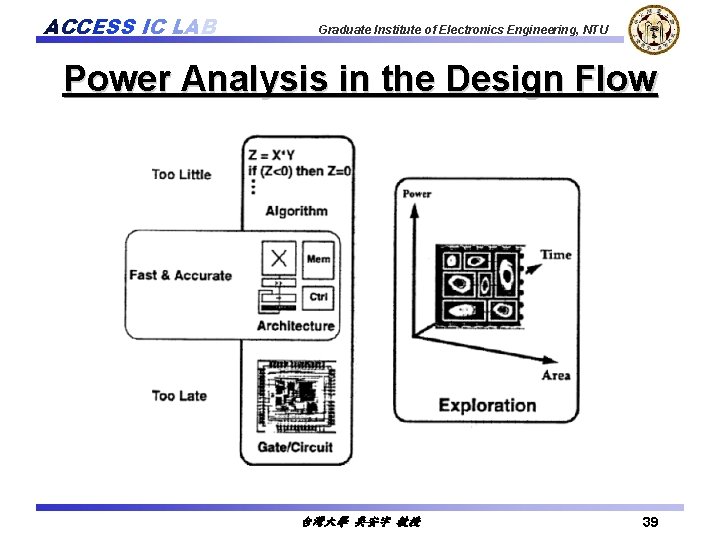

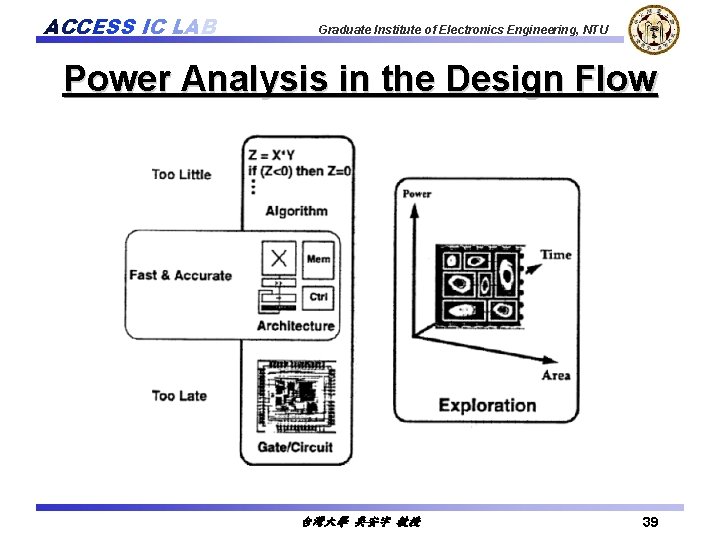

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Power Analysis in the Design Flow 台灣大學 吳安宇 教授 39

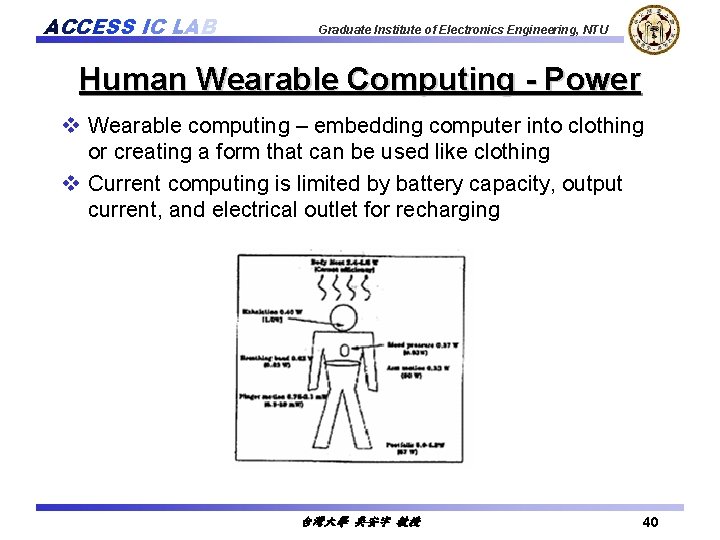

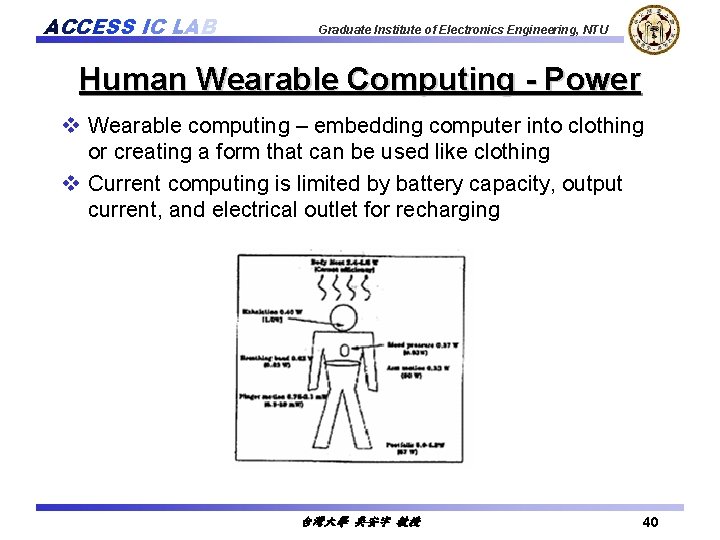

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Human Wearable Computing - Power v Wearable computing – embedding computer into clothing or creating a form that can be used like clothing v Current computing is limited by battery capacity, output current, and electrical outlet for recharging 台灣大學 吳安宇 教授 40

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Conclusions v High-speed design is a requirement for many applications v Low-power design is also a requirement for IC designers. v A new way of THINKING to simultaneously achieve both!!! v Low power impacts in the cost, size, weight, performance, and reliability. v Variable Vdd and Vt is a trend v CAD tools high level power estimation and management v Don’t just work on VLSI, pay attention to MEMS – lot of problems and potential is great. 台灣大學 吳安宇 教授 41

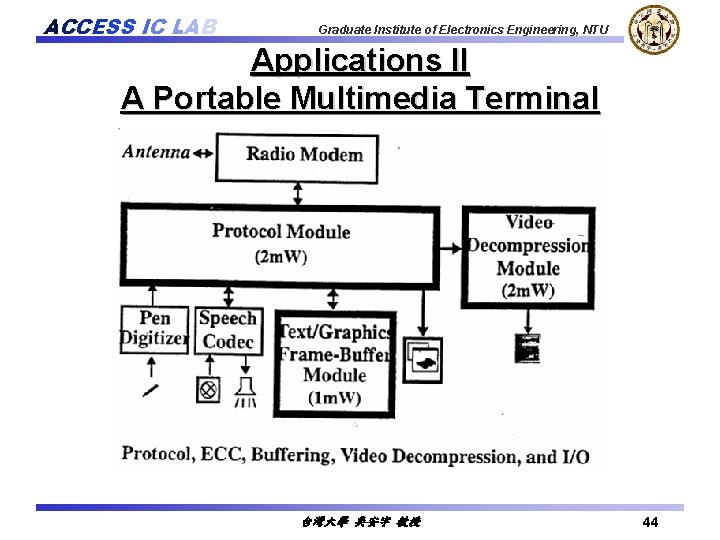

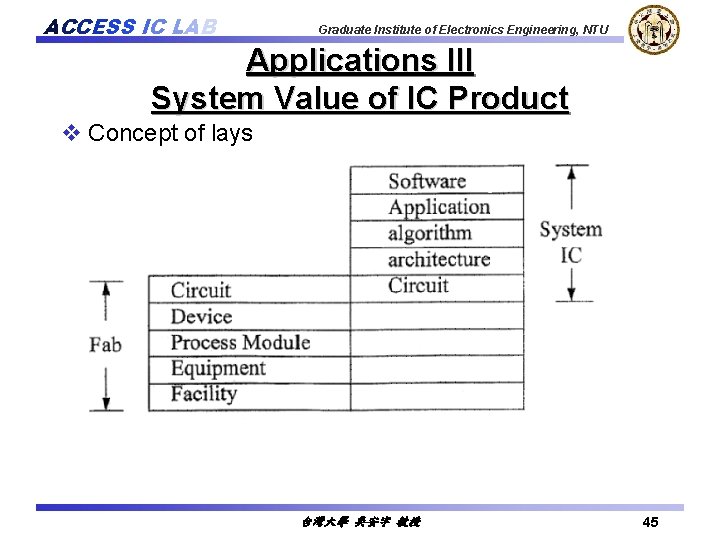

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Applications v Portable Multimedia Terminal v Wireless C&C v System on Chip (From Dr. Yang of Windbond) 台灣大學 吳安宇 教授 42

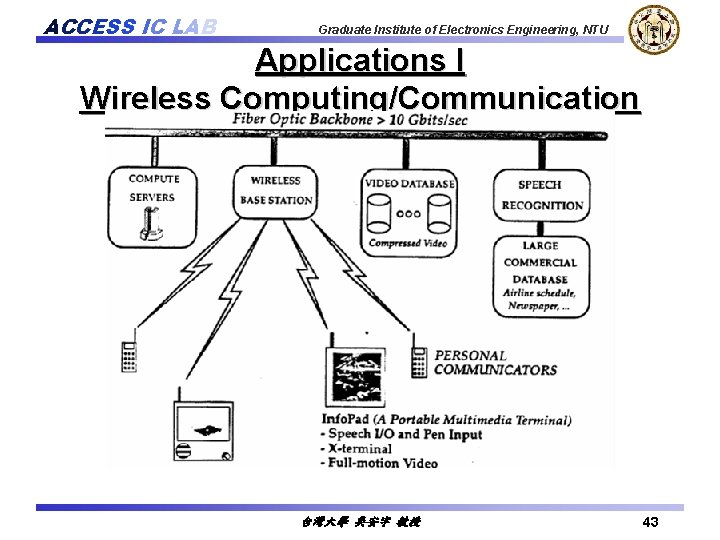

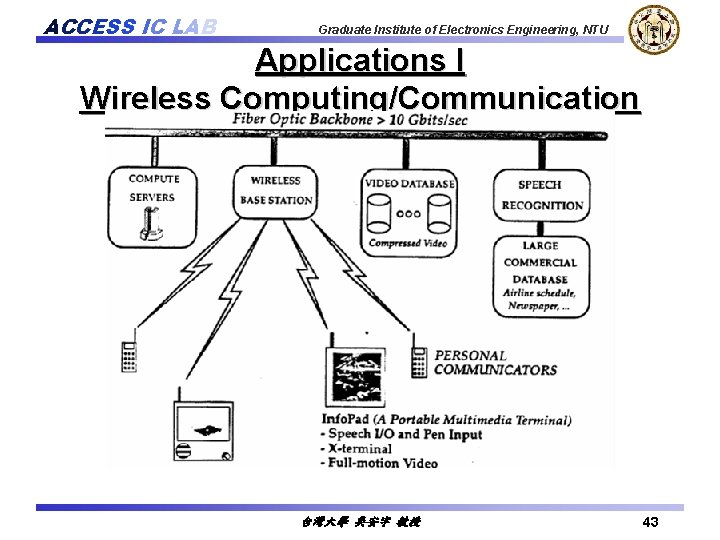

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Applications I Wireless Computing/Communication 台灣大學 吳安宇 教授 43

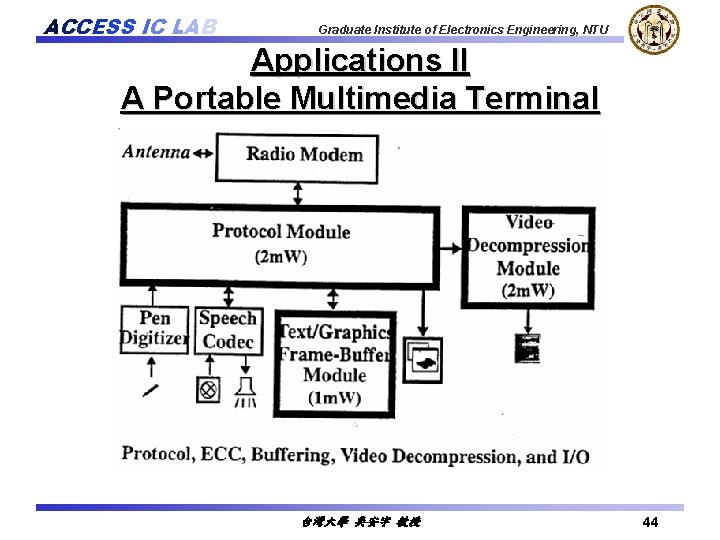

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Applications II A Portable Multimedia Terminal 台灣大學 吳安宇 教授 44

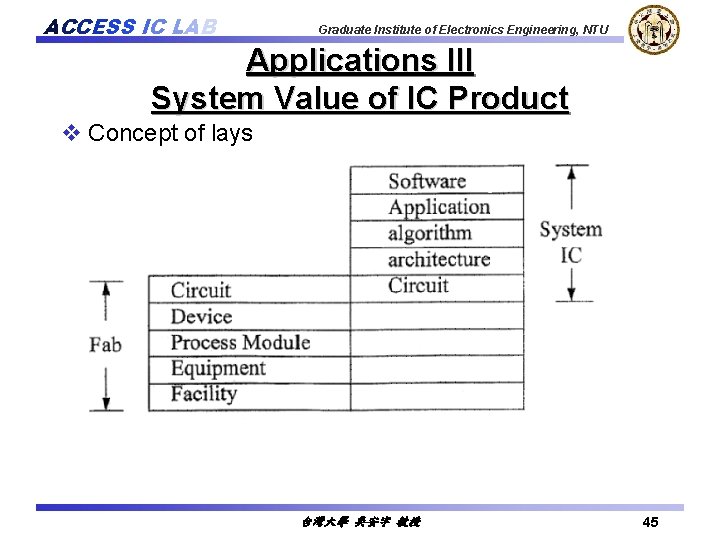

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Applications III System Value of IC Product v Concept of lays 台灣大學 吳安宇 教授 45

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Applications IV System on Chip v Entire system function Ø Logic + Memory Ø More than two types of devices v Allow more freedom in architecture v Const/Performance trade-off 台灣大學 吳安宇 教授 46

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Applications V New Opportunity for Taiwan IC Industry v PAST v. Digital IC vµ P v. IBM Compatible + MD-DOS v FUTURE v. System On Chip Ø Reduce head-on competition on standard products Ø Technology will be available Ø Manufacturing Service available Ø Same starting point as other countries Ø Can have more R/D focus 台灣大學 吳安宇 教授 47