Graduate Institute of Electronics Engineering NTU 102 1

- Slides: 41

Graduate Institute of Electronics Engineering, NTU 102 -1 Under-Graduate Project Verilog Speaker: 黃乃珊 Adviser: Prof. An-Yeu Wu Date: 2013/9/26 ACCESS IC LAB

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Outline v Basic Concept of Verilog HDL v Gate Level Modeling v Simulation & Verification v Summary P. 2

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU What is Verilog HDL ? v Hardware Description Language v Mixed level modeling v Behavioral Ø Algorithmic ( like high level language) Ø Register transfer (Synthesizable) v Register Transfer Level (RTL) Ø Describing a system by the flow of data and control signals within and between functional blocks Ø Define the model in terms of cycles, based on a defined clock v Structural Ø Gate (AND, OR ……) Ø Switch (PMOS, NOMS, JFET ……) P. 3

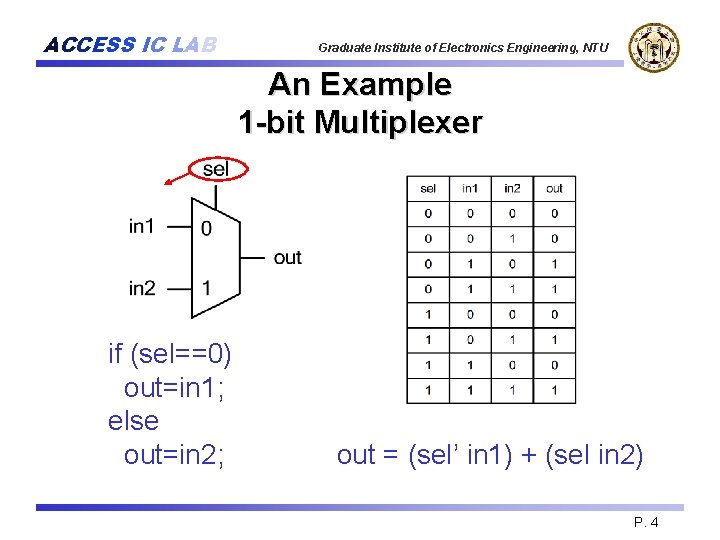

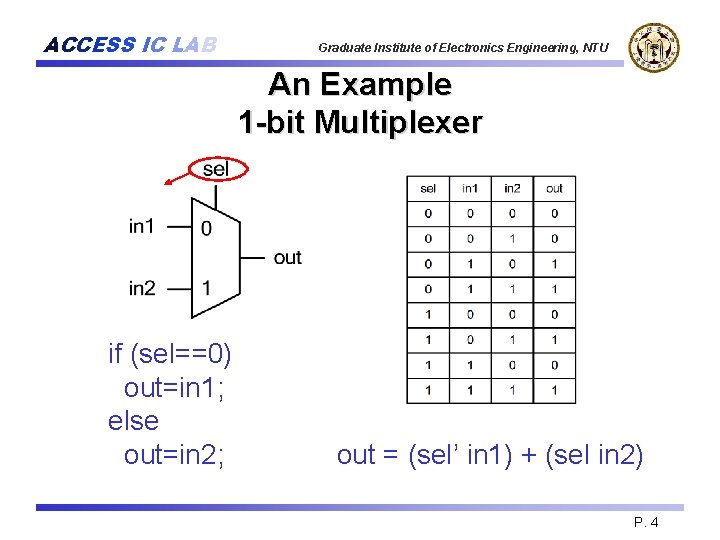

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU An Example 1 -bit Multiplexer if (sel==0) out=in 1; else out=in 2; out = (sel’ in 1) + (sel in 2) P. 4

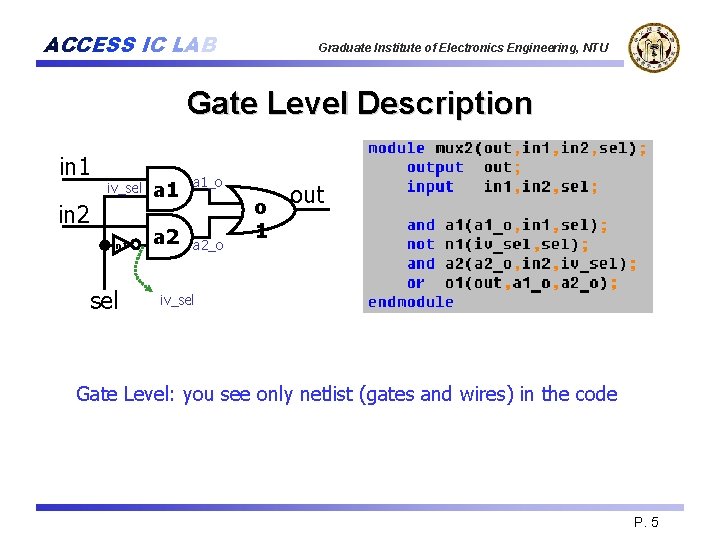

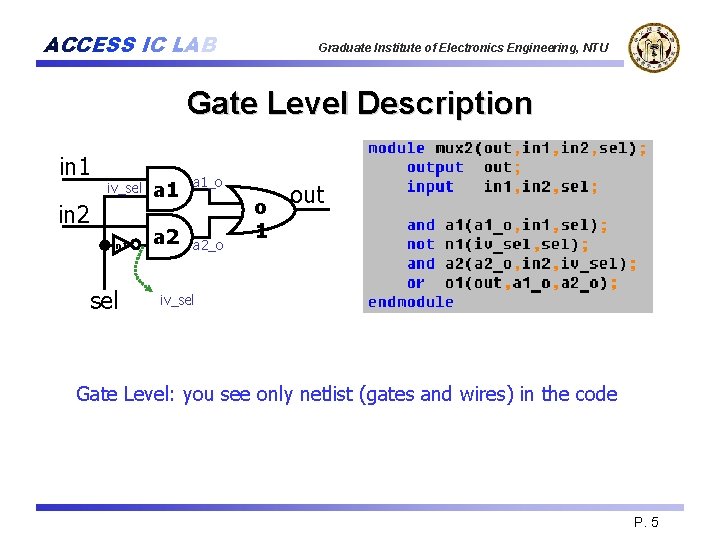

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Gate Level Description in 1 iv_sel in 2 n 1 sel a 1 a 2 a 1_o a 2_o o 1 out iv_sel Gate Level: you see only netlist (gates and wires) in the code P. 5

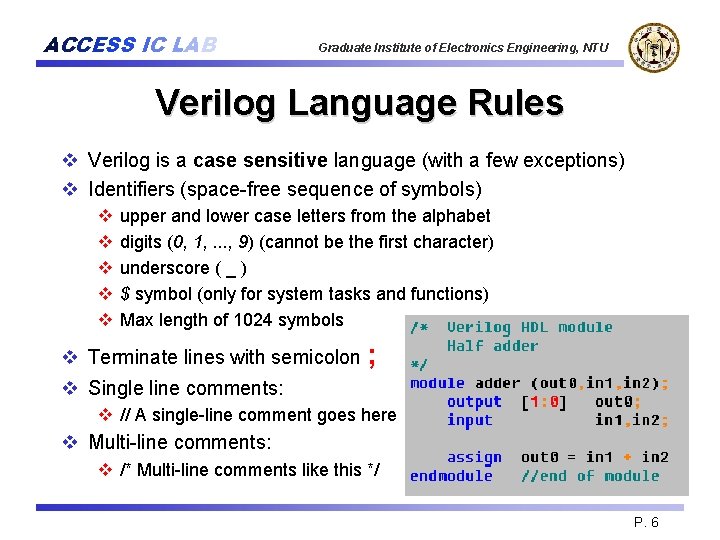

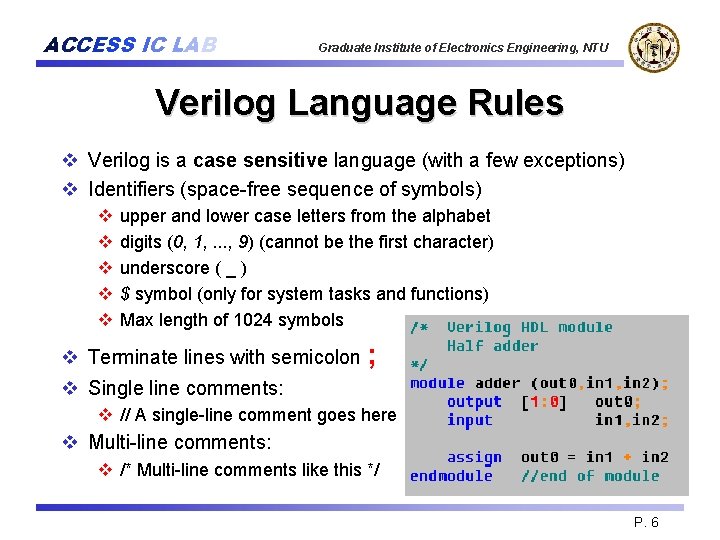

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Verilog Language Rules v Verilog is a case sensitive language (with a few exceptions) v Identifiers (space-free sequence of symbols) v v v upper and lower case letters from the alphabet digits (0, 1, . . . , 9) (cannot be the first character) underscore ( _ ) $ symbol (only for system tasks and functions) Max length of 1024 symbols v Terminate lines with semicolon ; v Single line comments: v // A single-line comment goes here v Multi-line comments: v /* Multi-line comments like this */ P. 6

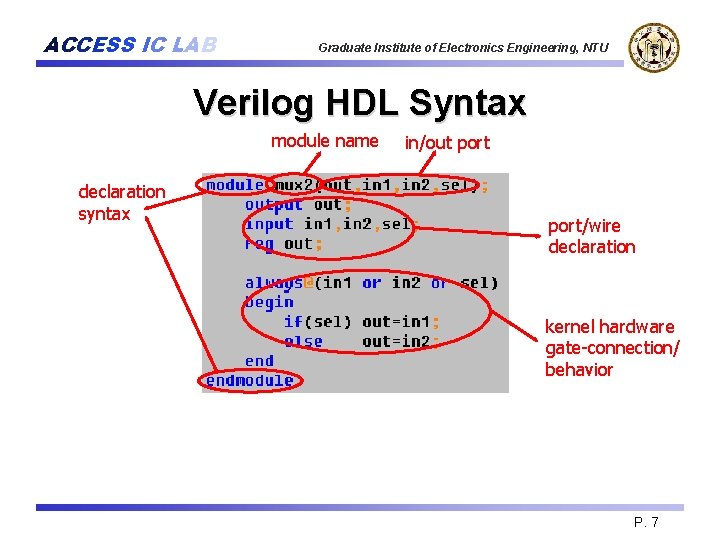

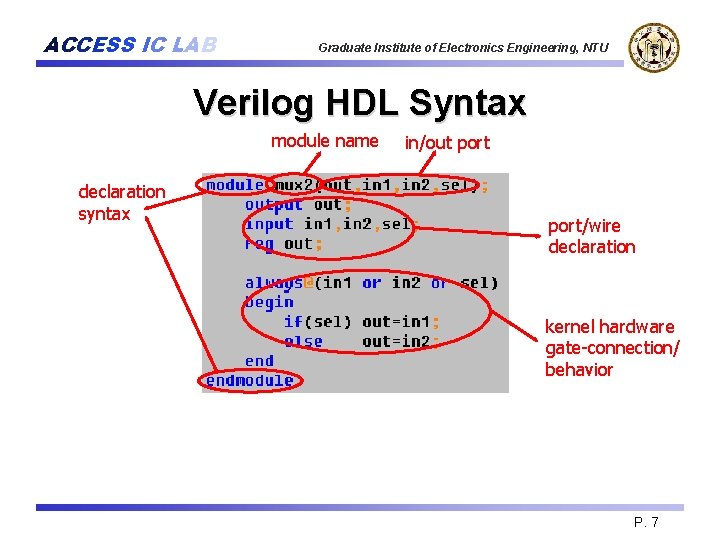

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Verilog HDL Syntax module name declaration syntax in/out port/wire declaration kernel hardware gate-connection/ behavior P. 7

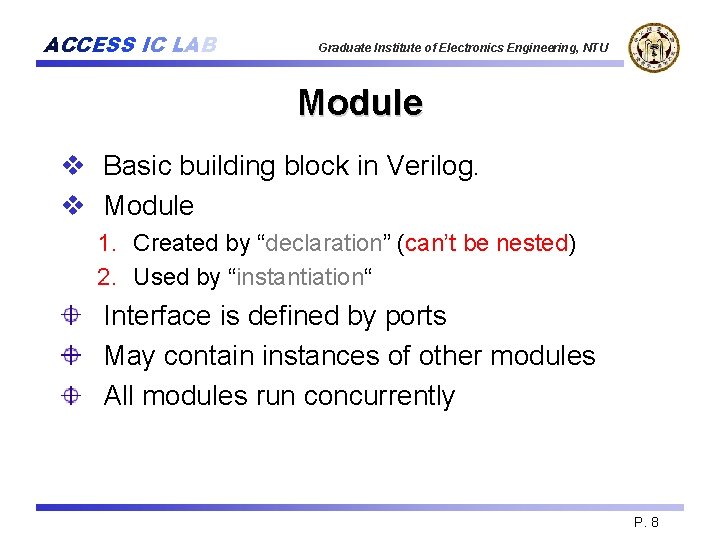

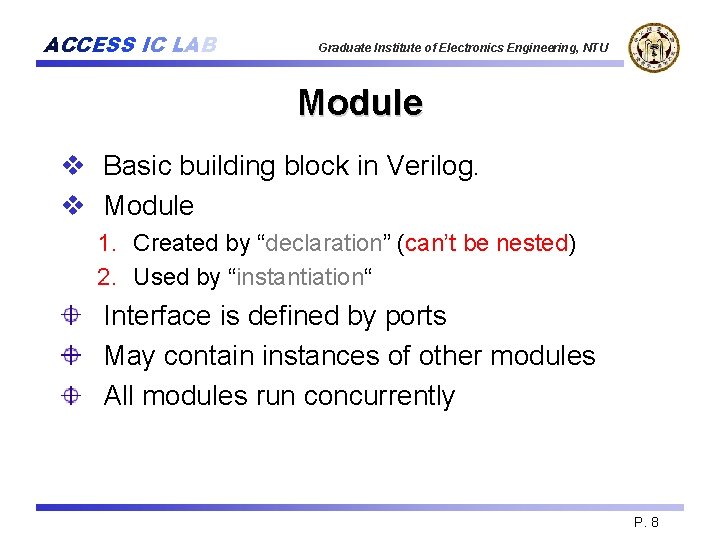

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Module v Basic building block in Verilog. v Module 1. Created by “declaration” (can’t be nested) 2. Used by “instantiation“ Interface is defined by ports May contain instances of other modules All modules run concurrently P. 8

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Instances v A module provides a template from which you can create actual objects. v When a module is invoked, Verilog creates a unique object from the template. v Each object has its own name, variables, parameters and I/O interface. P. 9

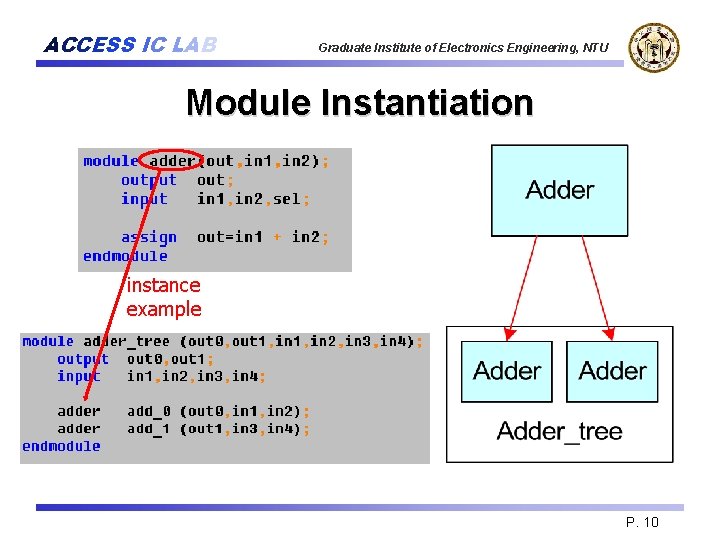

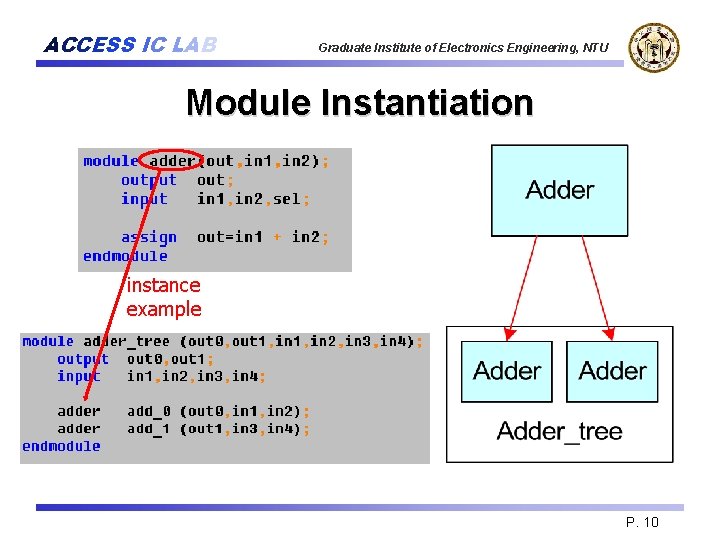

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Module Instantiation instance example P. 10

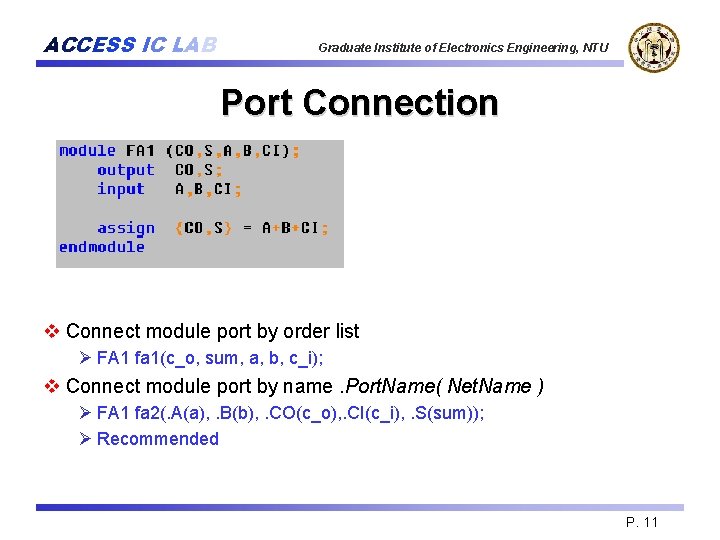

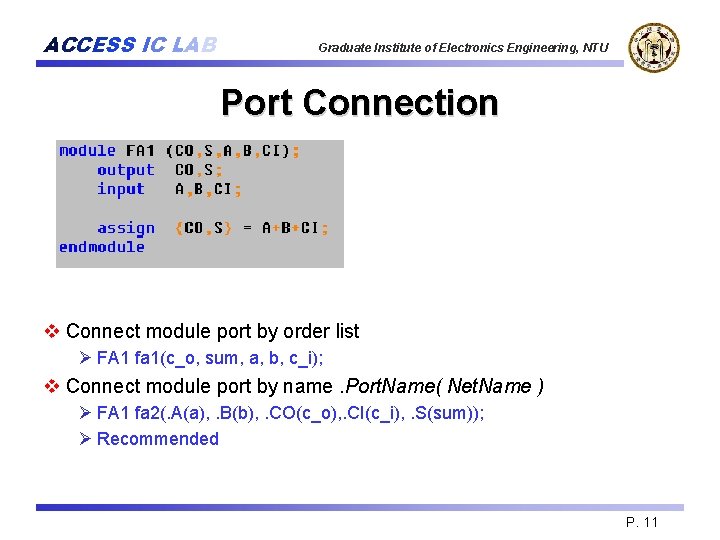

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Port Connection v Connect module port by order list Ø FA 1 fa 1(c_o, sum, a, b, c_i); v Connect module port by name. Port. Name( Net. Name ) Ø FA 1 fa 2(. A(a), . B(b), . CO(c_o), . CI(c_i), . S(sum)); Ø Recommended P. 11

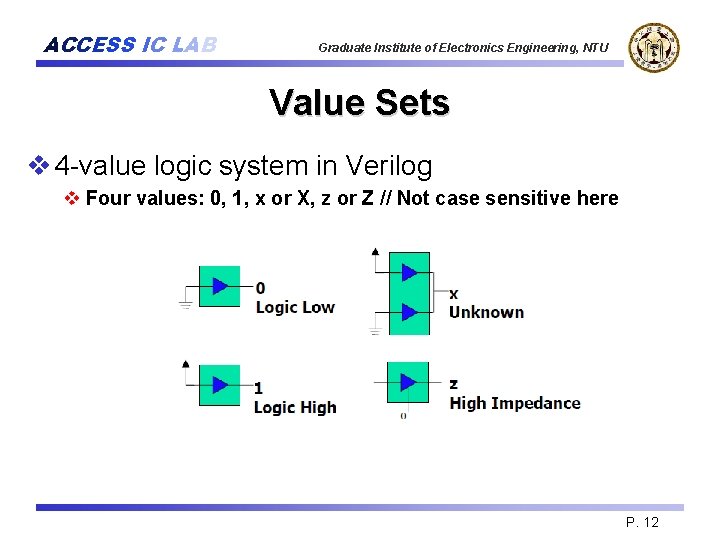

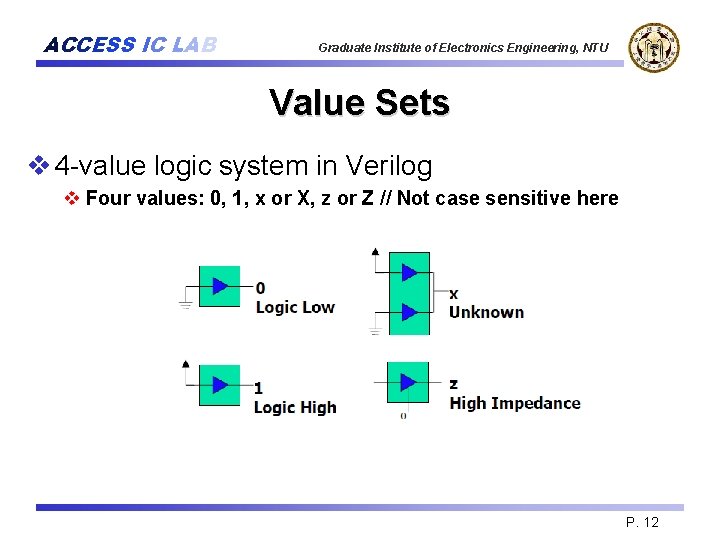

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Value Sets v 4 -value logic system in Verilog v Four values: 0, 1, x or X, z or Z // Not case sensitive here P. 12

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Register and Net v Registers v Keyword : reg, integer, time, real v Event-driven modeling v Storage element (modeling sequential circuit) v Assignment in “always” block v Default value is X v Nets v Keyword : wire, wand, wor, triand, trior, supply 0, supply 1 v Doesn’t store value, just a connection v input, output, inout are default “wire” v Can’t appear in “always” block assignment v Default value is Z P. 13

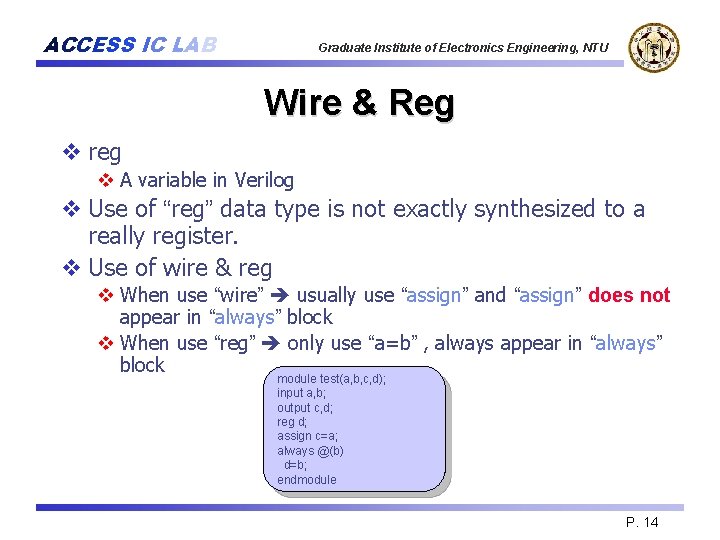

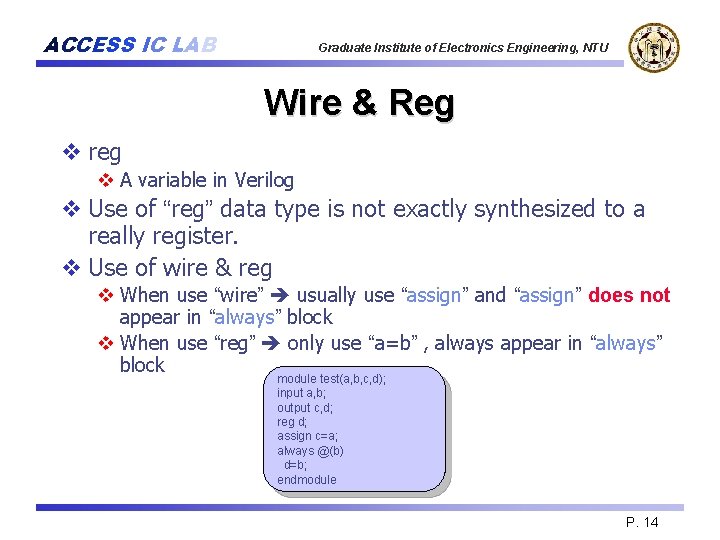

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Wire & Reg v reg v A variable in Verilog v Use of “reg” data type is not exactly synthesized to a really register. v Use of wire & reg v When use “wire” usually use “assign” and “assign” does not appear in “always” block v When use “reg” only use “a=b” , always appear in “always” block module test(a, b, c, d); input a, b; output c, d; reg d; assign c=a; always @(b) d=b; endmodule P. 14

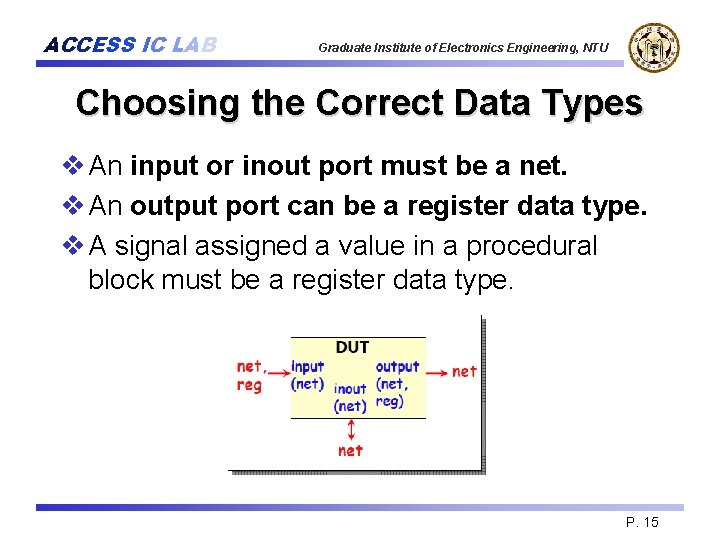

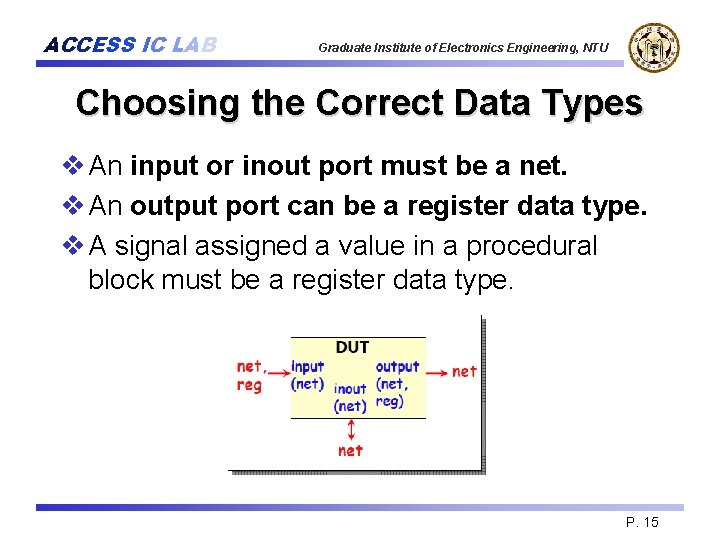

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Choosing the Correct Data Types v An input or inout port must be a net. v An output port can be a register data type. v A signal assigned a value in a procedural block must be a register data type. P. 15

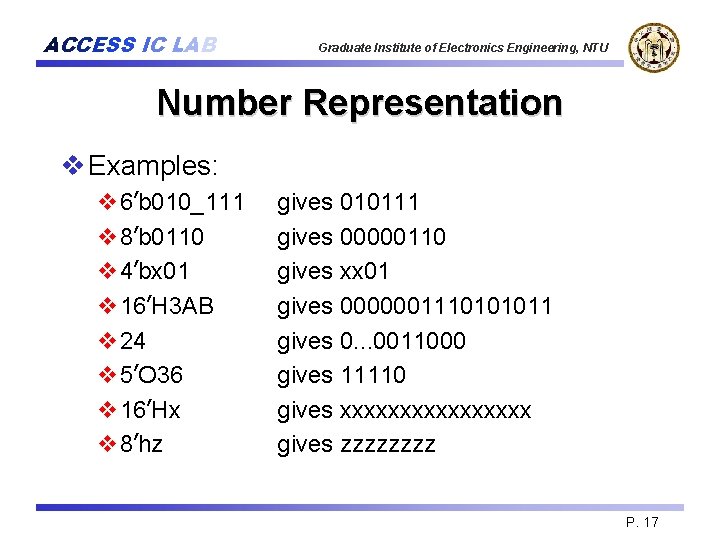

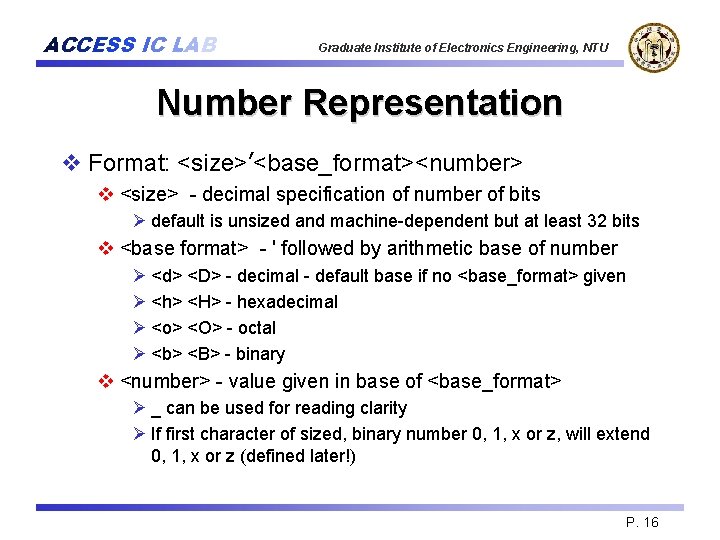

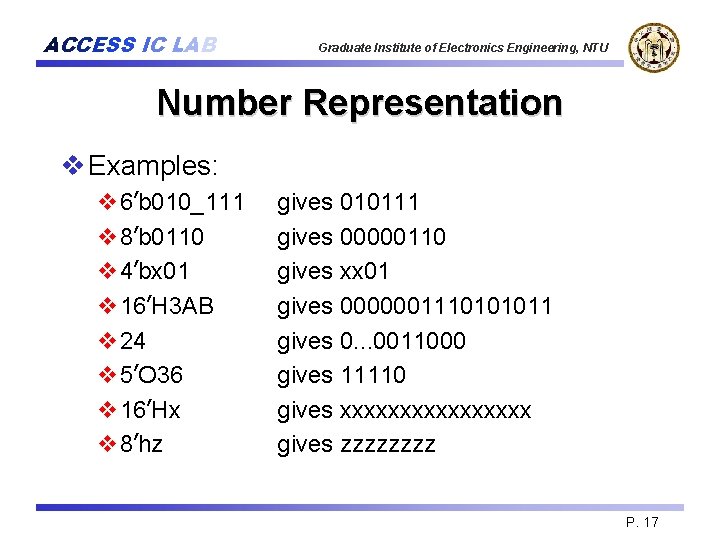

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Number Representation v Format: <size>’<base_format><number> v <size> - decimal specification of number of bits Ø default is unsized and machine-dependent but at least 32 bits v <base format> - ' followed by arithmetic base of number Ø <d> <D> - decimal - default base if no <base_format> given Ø <h> <H> - hexadecimal Ø <o> <O> - octal Ø <b> <B> - binary v <number> - value given in base of <base_format> Ø _ can be used for reading clarity Ø If first character of sized, binary number 0, 1, x or z, will extend 0, 1, x or z (defined later!) P. 16

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Number Representation v Examples: v 6’b 010_111 v 8’b 0110 v 4’bx 01 v 16’H 3 AB v 24 v 5’O 36 v 16’Hx v 8’hz gives 010111 gives 00000110 gives xx 01 gives 0000001110101011 gives 0… 0011000 gives 11110 gives xxxxxxxx gives zzzz P. 17

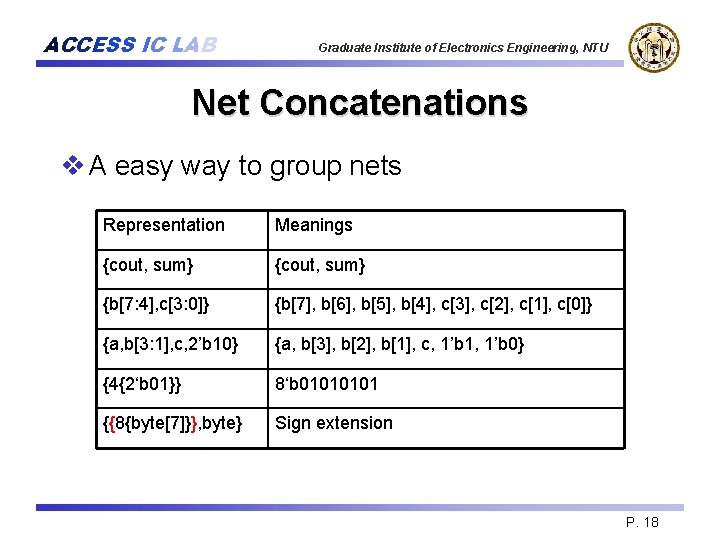

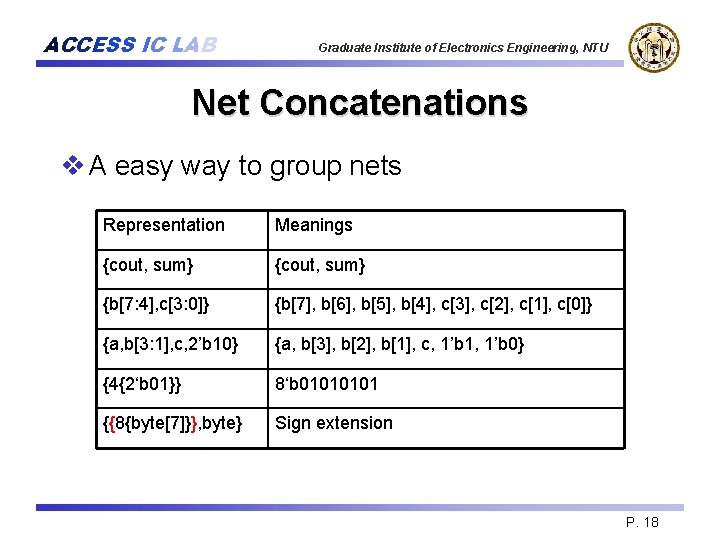

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Net Concatenations v A easy way to group nets Representation Meanings {cout, sum} {b[7: 4], c[3: 0]} {b[7], b[6], b[5], b[4], c[3], c[2], c[1], c[0]} {a, b[3: 1], c, 2’b 10} {a, b[3], b[2], b[1], c, 1’b 1, 1’b 0} {4{2‘b 01}} 8‘b 0101 {{8{byte[7]}}, byte} Sign extension P. 18

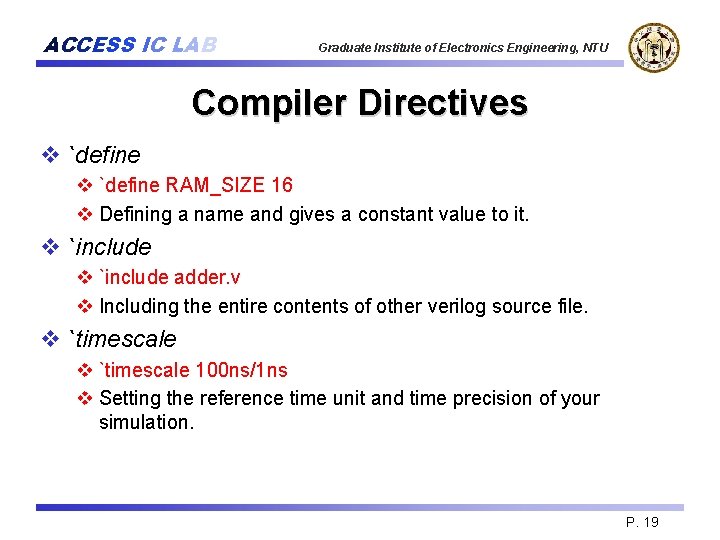

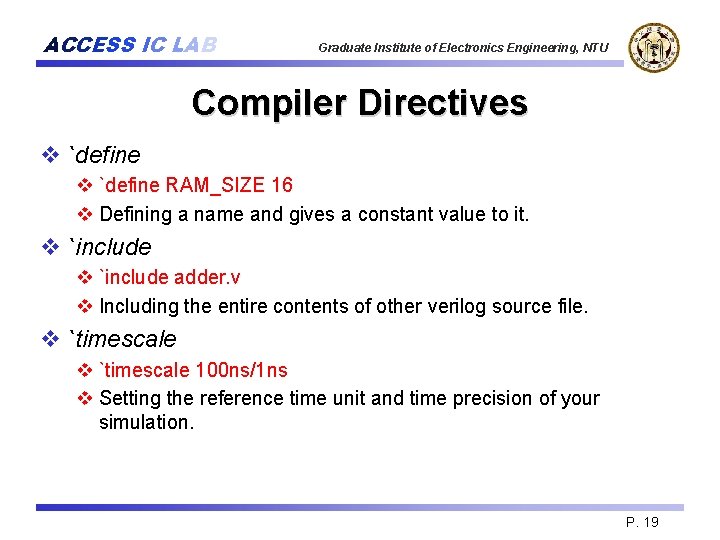

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Compiler Directives v `define RAM_SIZE 16 v Defining a name and gives a constant value to it. v `include adder. v v Including the entire contents of other verilog source file. v `timescale 100 ns/1 ns v Setting the reference time unit and time precision of your simulation. P. 19

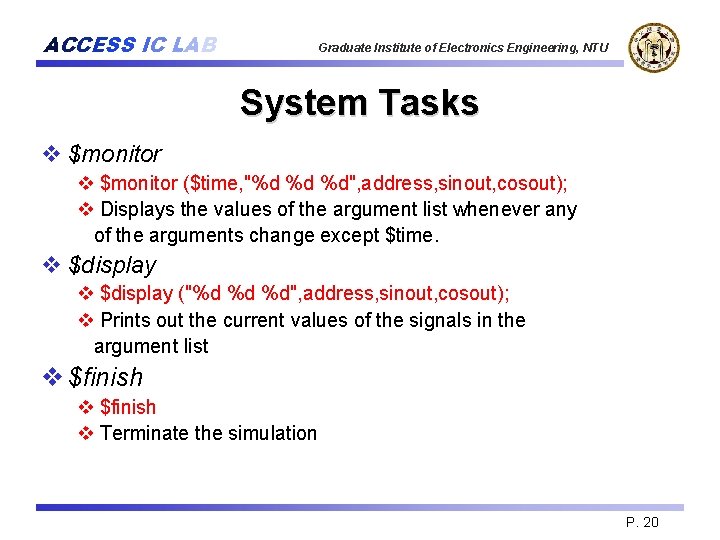

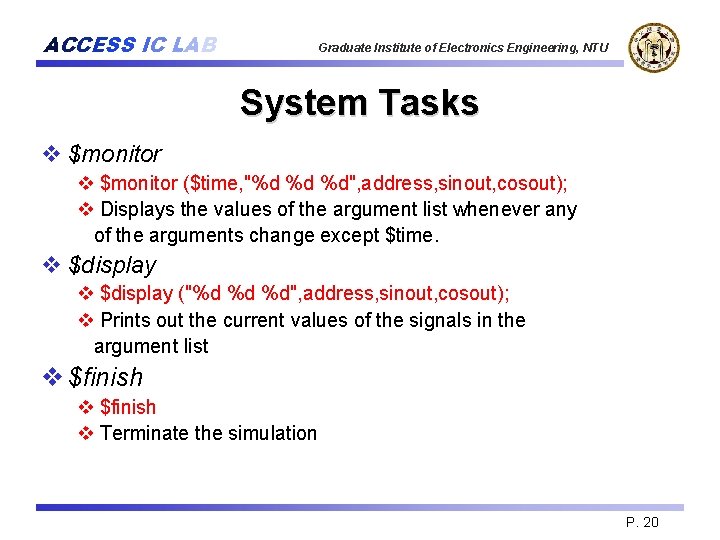

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU System Tasks v $monitor ($time, "%d %d %d", address, sinout, cosout); v Displays the values of the argument list whenever any of the arguments change except $time. v $display ("%d %d %d", address, sinout, cosout); v Prints out the current values of the signals in the argument list v $finish v Terminate the simulation P. 20

Graduate Institute of Electronics Engineering, NTU Gate Level Modeling ACCESS IC LAB

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Gate Level Modeling v Steps v. Develop the boolean function of output v. Draw the circuit with logic gates/primitives v. Connect gates/primitives with net (usually wire) v HDL: Hardware Description Language v. Figure out architecture first, then write code. P. 22

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Primitives v Primitives are modules ready to be instanced v Smallest modeling block for simulator v Verilog build-in primitive gate vand, or, not, buf, xor, nand, nor, xnor vprim_name inst_name( output, in 0, in 1, . . ); ØEX. and g 0(a, b, c); v User defined primitive (UDP) vbuilding block defined by designer P. 23

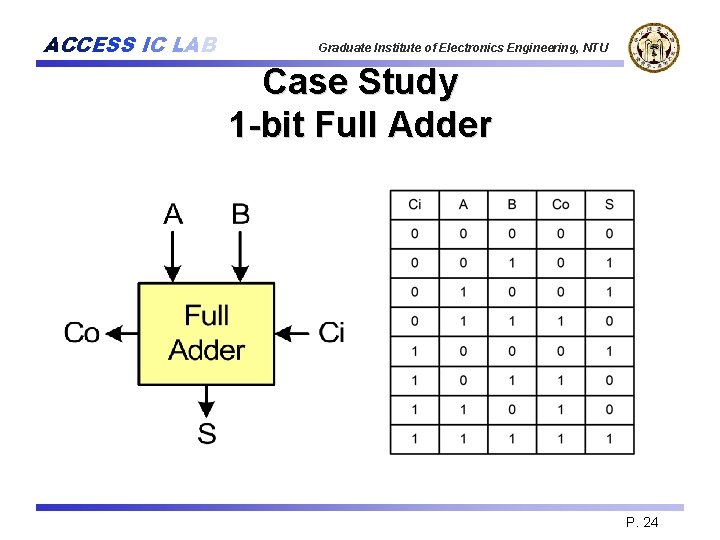

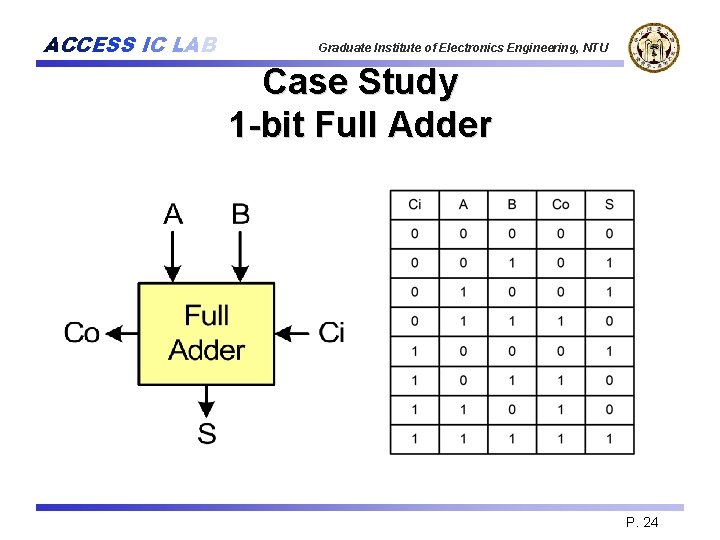

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Case Study 1 -bit Full Adder P. 24

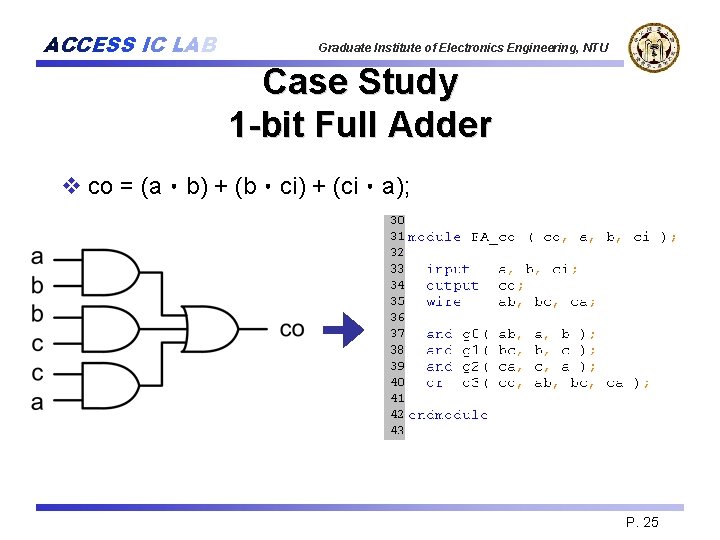

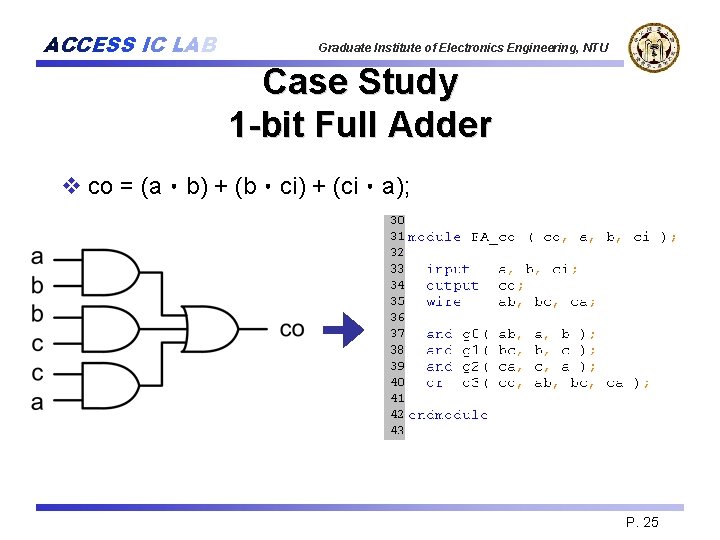

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Case Study 1 -bit Full Adder v co = (a‧b) + (b‧ci) + (ci‧a); P. 25

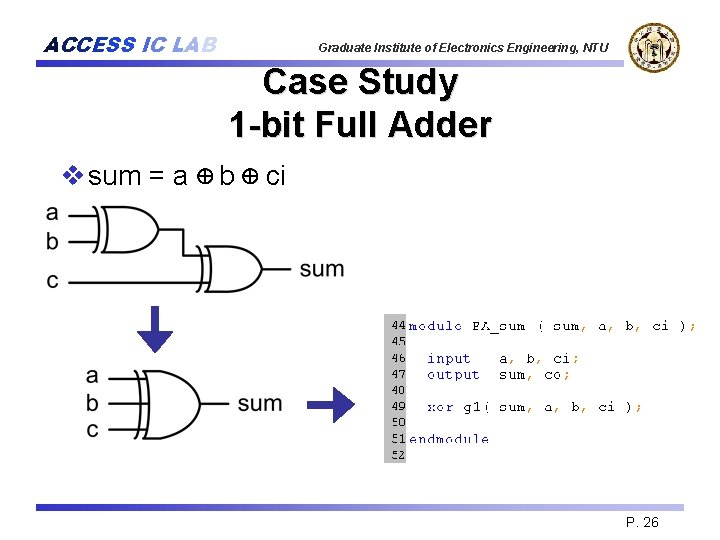

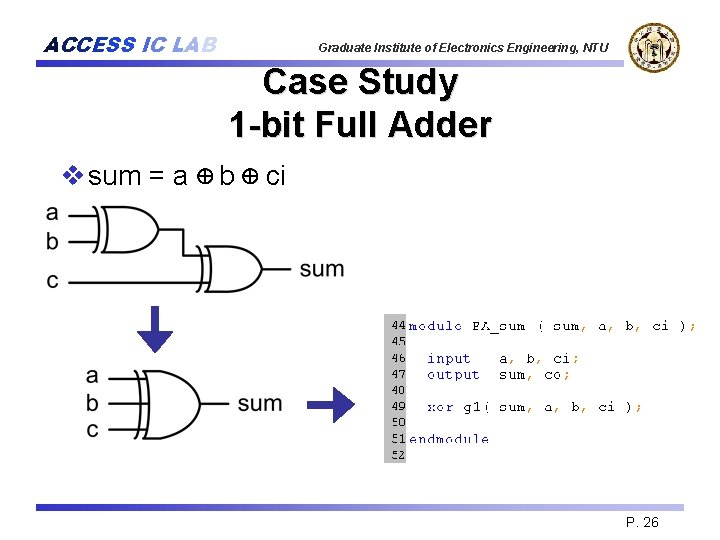

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Case Study 1 -bit Full Adder v sum = a b ci P. 26

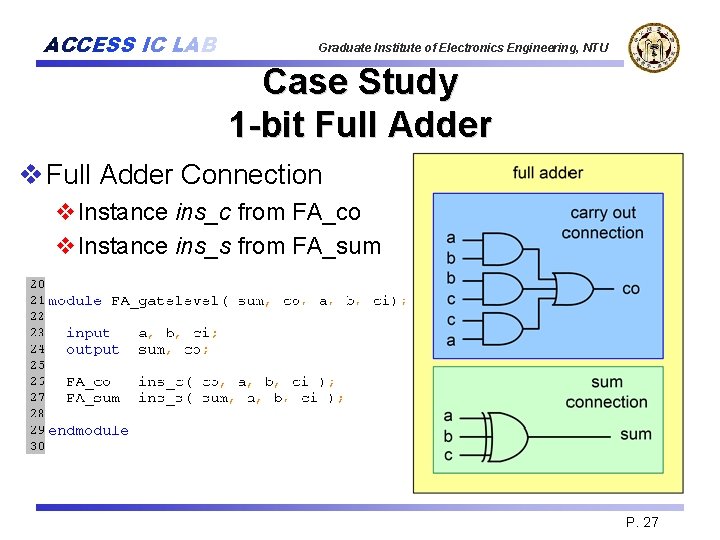

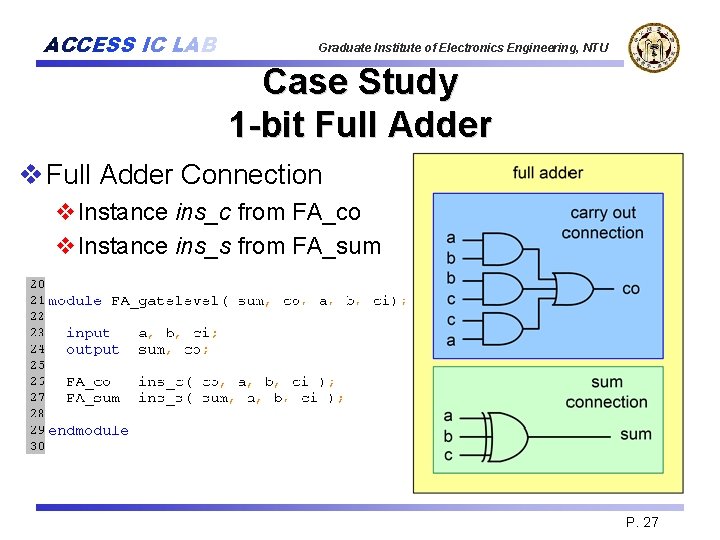

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Case Study 1 -bit Full Adder v Full Adder Connection v. Instance ins_c from FA_co v. Instance ins_s from FA_sum P. 27

Graduate Institute of Electronics Engineering, NTU Timing and Delays ACCESS IC LAB

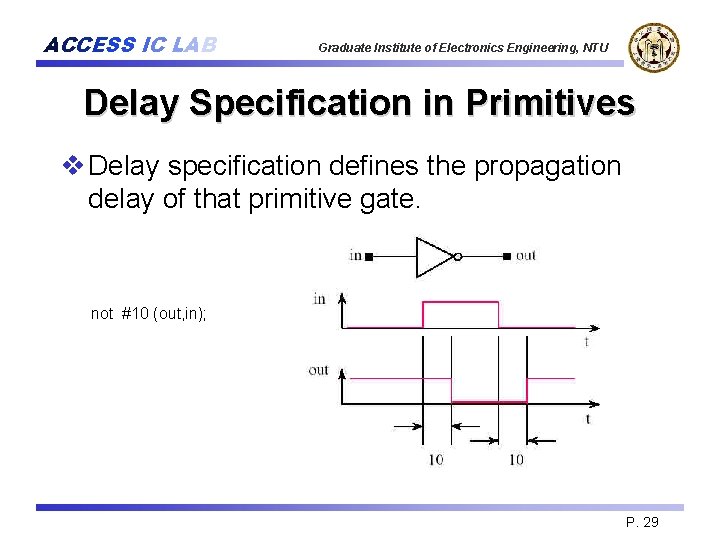

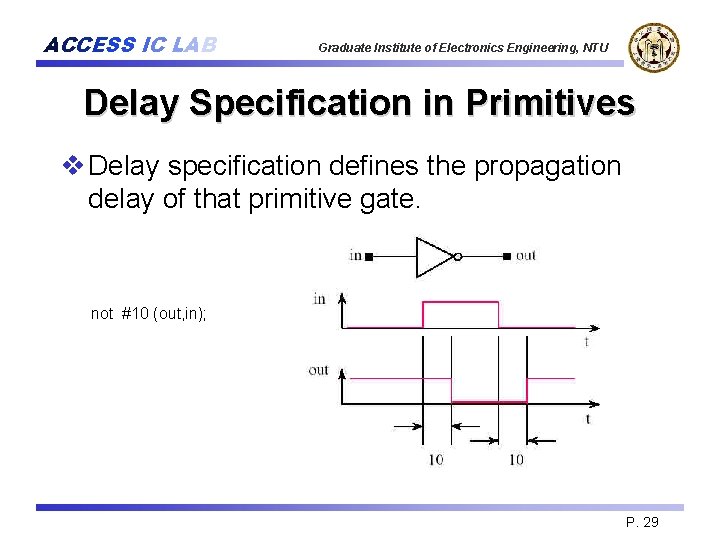

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Delay Specification in Primitives v Delay specification defines the propagation delay of that primitive gate. not #10 (out, in); P. 29

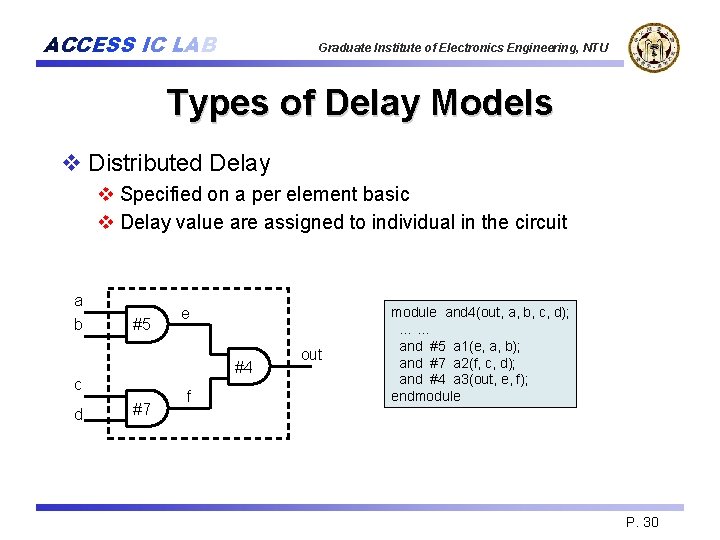

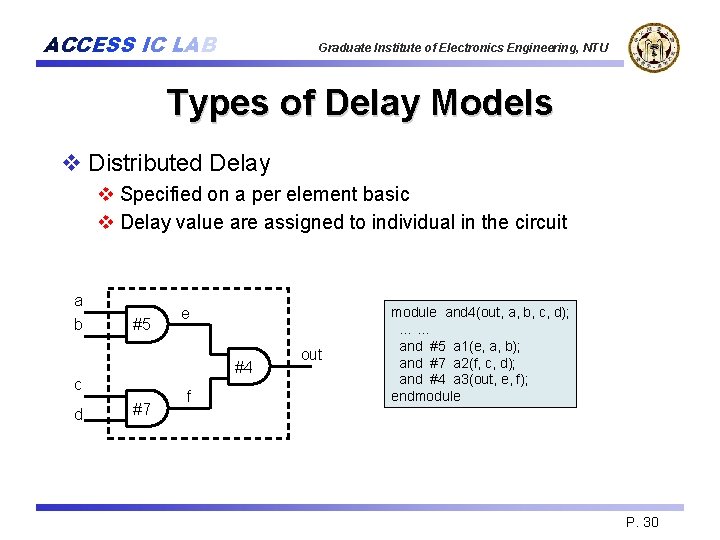

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Types of Delay Models v Distributed Delay v Specified on a per element basic v Delay value are assigned to individual in the circuit a b #5 #4 c d e #7 f out module and 4(out, a, b, c, d); …… and #5 a 1(e, a, b); and #7 a 2(f, c, d); and #4 a 3(out, e, f); endmodule P. 30

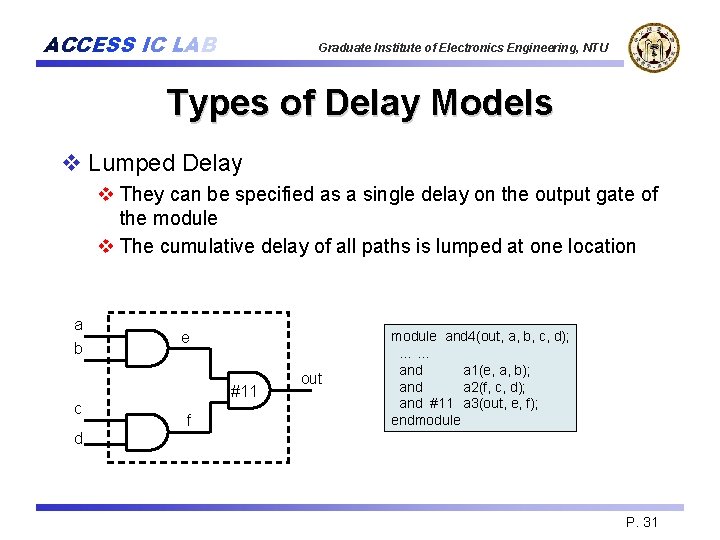

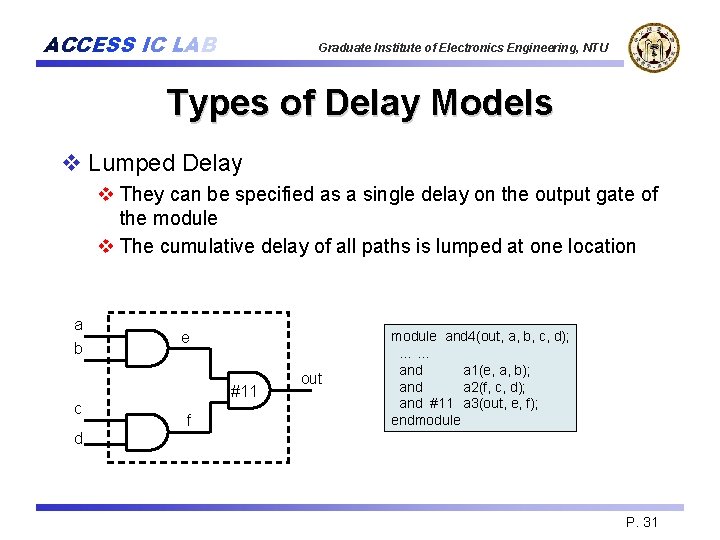

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Types of Delay Models v Lumped Delay v They can be specified as a single delay on the output gate of the module v The cumulative delay of all paths is lumped at one location a b c e #11 f out module and 4(out, a, b, c, d); …… and a 1(e, a, b); and a 2(f, c, d); and #11 a 3(out, e, f); endmodule d P. 31

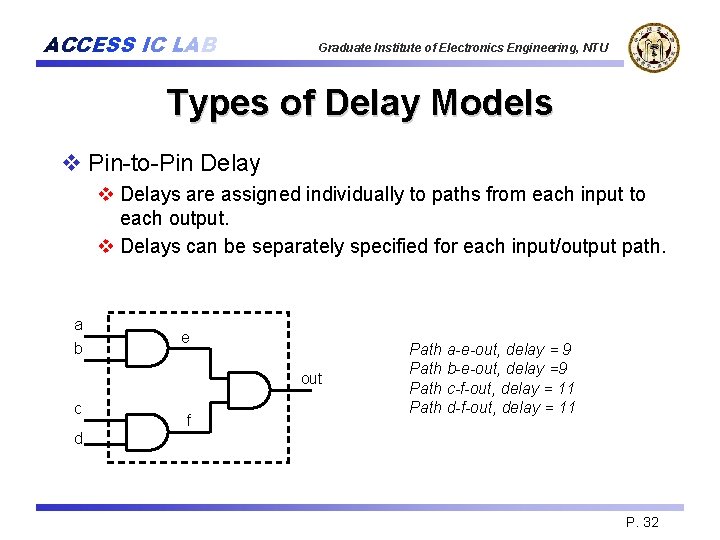

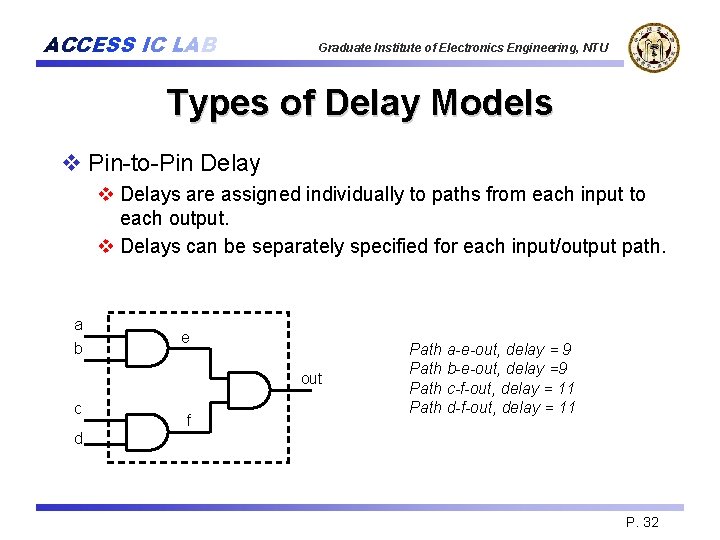

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Types of Delay Models v Pin-to-Pin Delay v Delays are assigned individually to paths from each input to each output. v Delays can be separately specified for each input/output path. a b e out c f Path a-e-out, delay = 9 Path b-e-out, delay =9 Path c-f-out, delay = 11 Path d-f-out, delay = 11 d P. 32

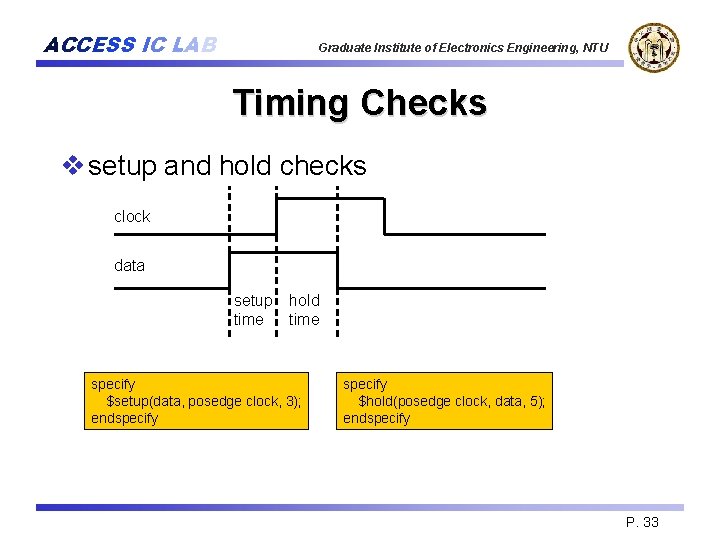

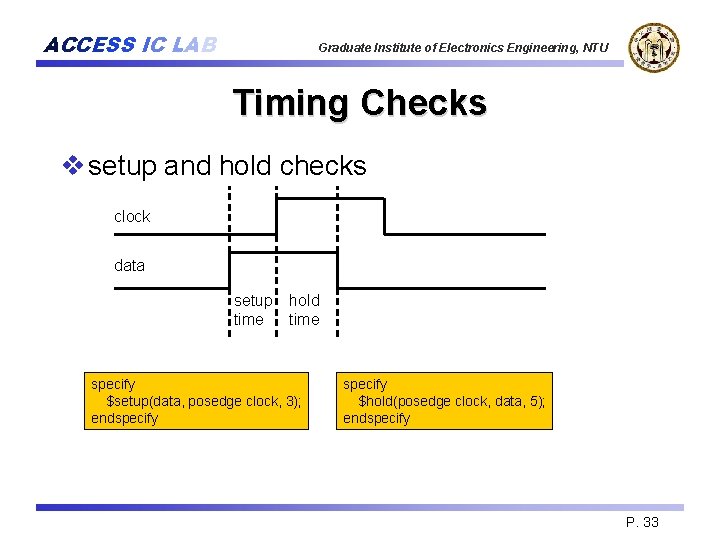

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Timing Checks v setup and hold checks clock data setup time hold time specify $setup(data, posedge clock, 3); endspecify $hold(posedge clock, data, 5); endspecify P. 33

Graduate Institute of Electronics Engineering, NTU Simulation & Verification ACCESS IC LAB

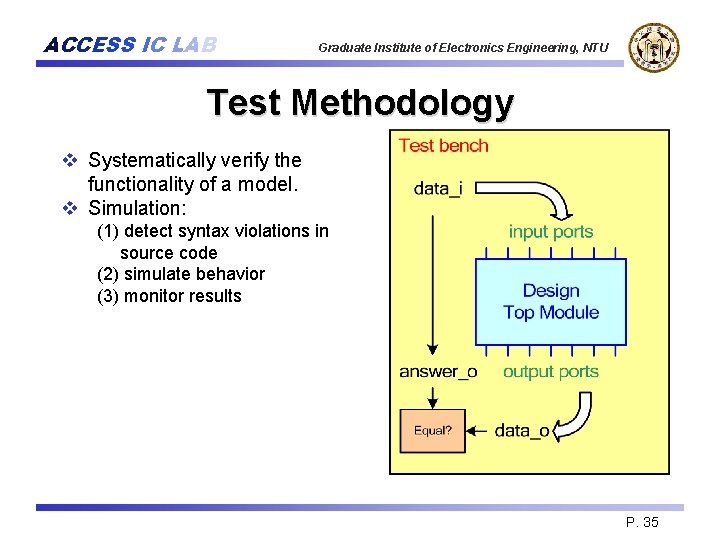

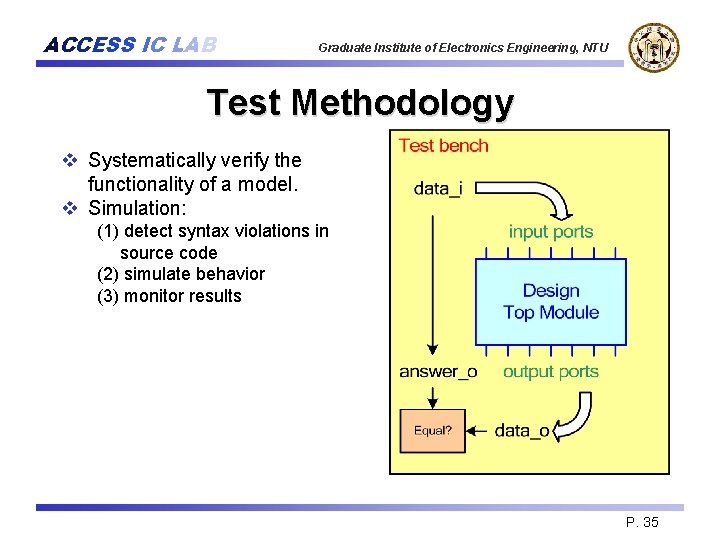

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Test Methodology v Systematically verify the functionality of a model. v Simulation: (1) detect syntax violations in source code (2) simulate behavior (3) monitor results P. 35

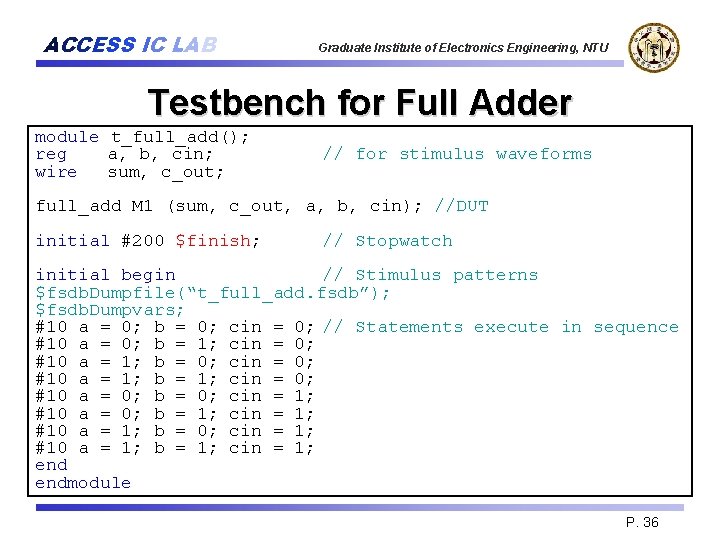

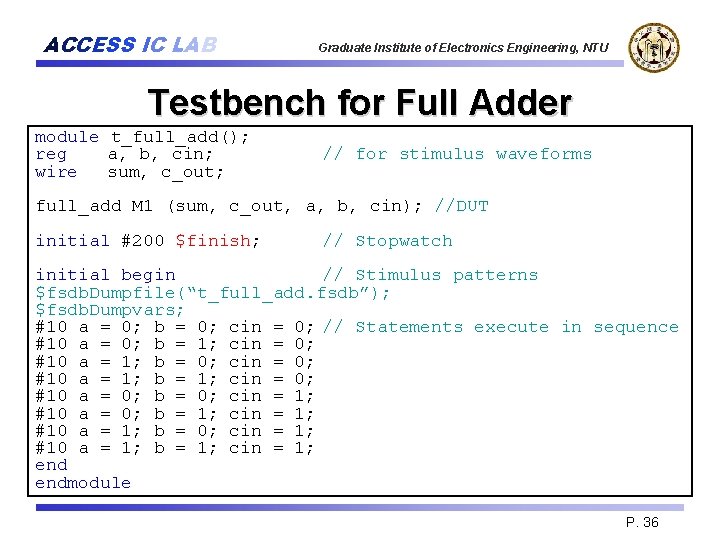

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Testbench for Full Adder module t_full_add(); reg a, b, cin; wire sum, c_out; // for stimulus waveforms full_add M 1 (sum, c_out, a, b, cin); //DUT initial #200 $finish; // Stopwatch initial begin // Stimulus patterns $fsdb. Dumpfile(“t_full_add. fsdb”); $fsdb. Dumpvars; #10 a = 0; b = 0; cin = 0; // Statements execute in sequence #10 a = 0; b = 1; cin = 0; #10 a = 1; b = 0; cin = 0; #10 a = 1; b = 1; cin = 0; #10 a = 0; b = 0; cin = 1; #10 a = 0; b = 1; cin = 1; #10 a = 1; b = 0; cin = 1; #10 a = 1; b = 1; cin = 1; endmodule P. 36

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Simulation Results P. 37

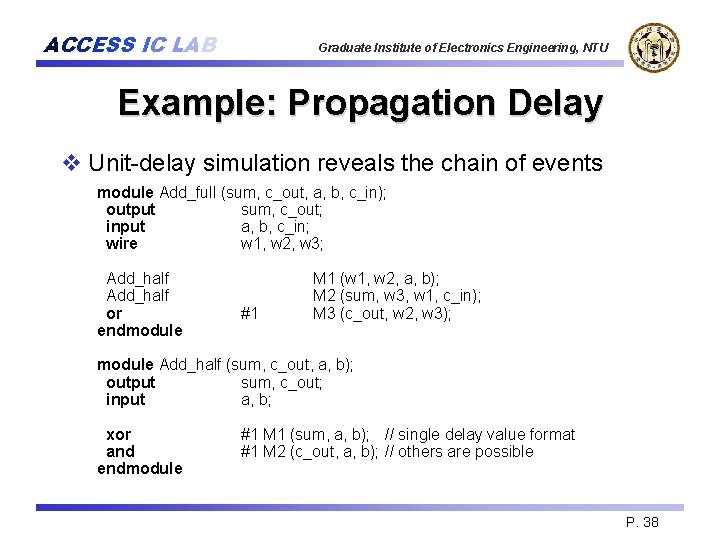

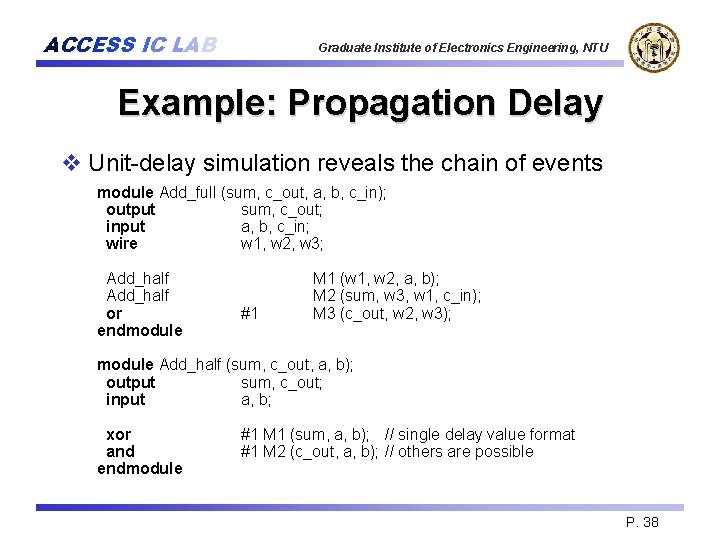

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Example: Propagation Delay v Unit-delay simulation reveals the chain of events module Add_full (sum, c_out, a, b, c_in); output sum, c_out; input a, b, c_in; wire w 1, w 2, w 3; Add_half M 1 (w 1, w 2, a, b); Add_half M 2 (sum, w 3, w 1, c_in); or #1 M 3 (c_out, w 2, w 3); endmodule Add_half (sum, c_out, a, b); output sum, c_out; input a, b; xor #1 M 1 (sum, a, b); // single delay value format and #1 M 2 (c_out, a, b); // others are possible endmodule P. 38

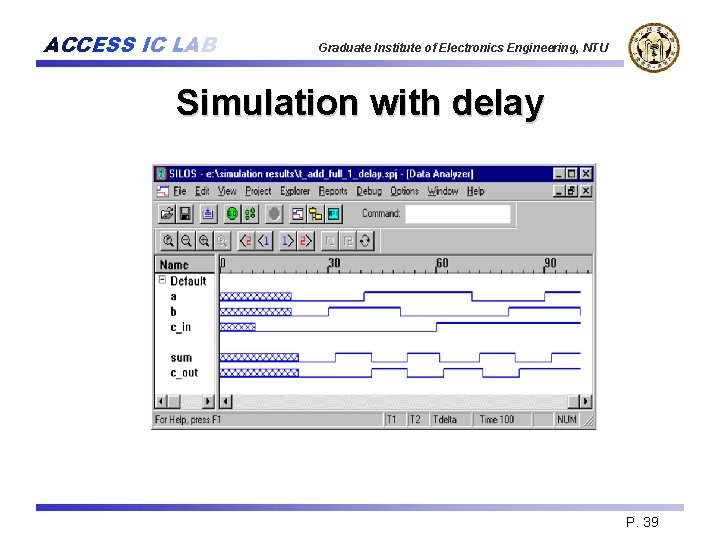

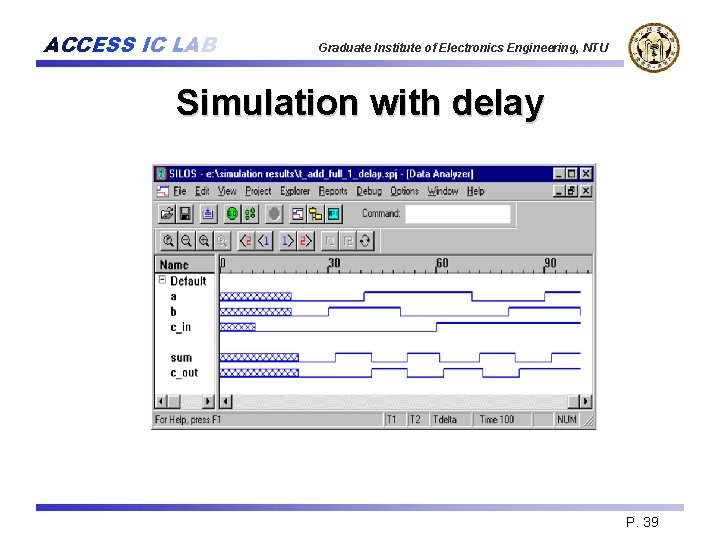

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Simulation with delay P. 39

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Summary v Design module v Gate-level or RT-level v Real hardware Ø Instance of modules exist all the time v Each module has architecture figure Ø Plot architecture figures before you write verilog codes v Test bench v Feed input data and compare output values versus time v Usually behavior level v Not real hardware, just like C/C++ P. 40

ACCESS IC LAB v Verilog is a platform Graduate Institute of Electronics Engineering, NTU Note Ø Support hardware design (design module) Ø Also support C/C++ like coding (test bench) v How to write verilog well Ø Know basic concepts and syntax Ø Get a good reference (a person or some code files) Ø Form a good coding habit Naming rule, comments, format partition (assign or always block) v Hardware Ø Combinational circuits 畫圖(architecture), then 連連看(coding) Ø Sequential circuits register: element to store data P. 41