Graduate Institute of Electronics Engineering NTU 102 1

- Slides: 15

Graduate Institute of Electronics Engineering, NTU 102 -1 Under-Graduate Project FFT Speaker: 林祐民 (Yumin) Adviser: Prof. An-Yeu Wu Date: 2013/9/17 ACCESS IC LAB

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Access Lab Profile/Overview v Location: EE building II (Rm. 232, 14坪) v Manpower: v 6 Ph. D. students v 13 MS students v Equipment: v 3 Sun Blade 2000 Workstations v 2 Sun Ultra 60 Workstations v 24 PC and 6 Notebooks for students P 2

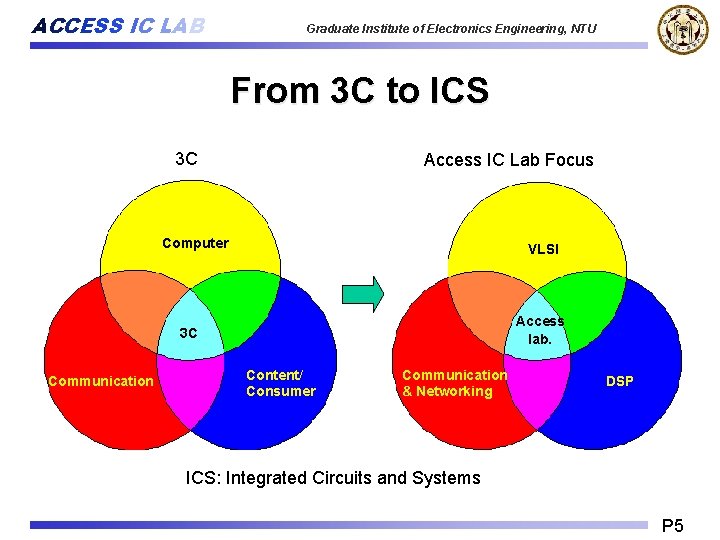

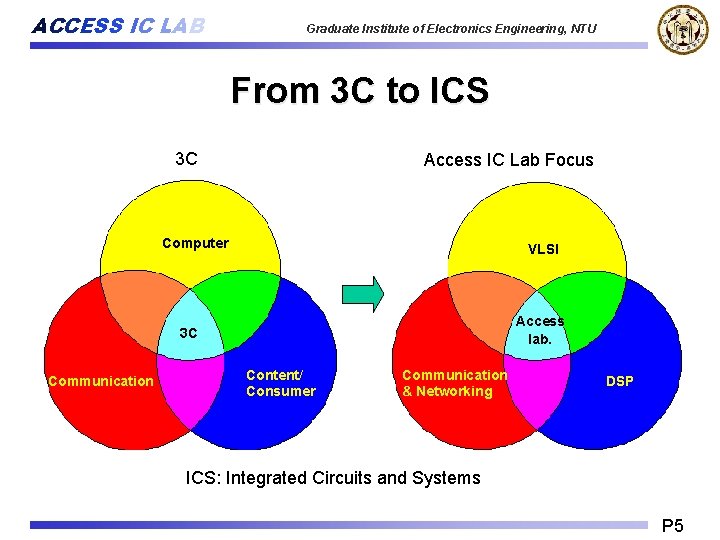

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU From 3 C to ICS 3 C Access IC Lab Focus Computer VLSI Access lab. 3 C Communication Content/ Consumer Communication & Networking DSP ICS: Integrated Circuits and Systems P 5

Graduate Institute of Electronics Engineering, NTU Project Topics for Undergraduate Members ACCESS IC LAB

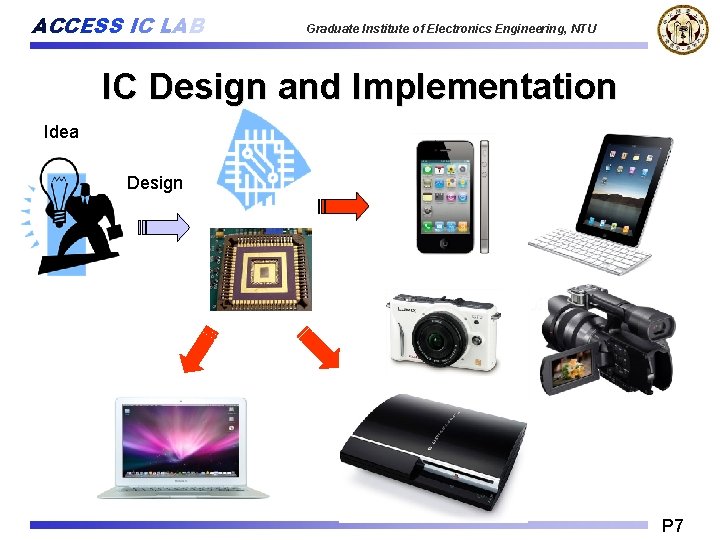

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU IC Design and Implementation Idea Design P 7

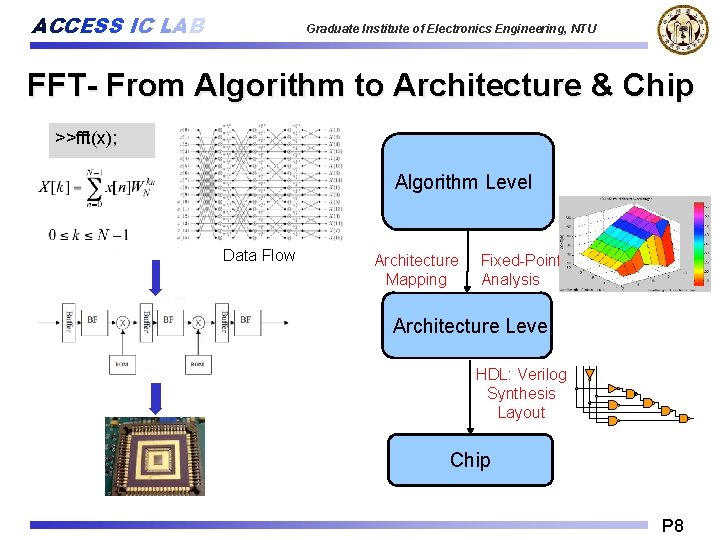

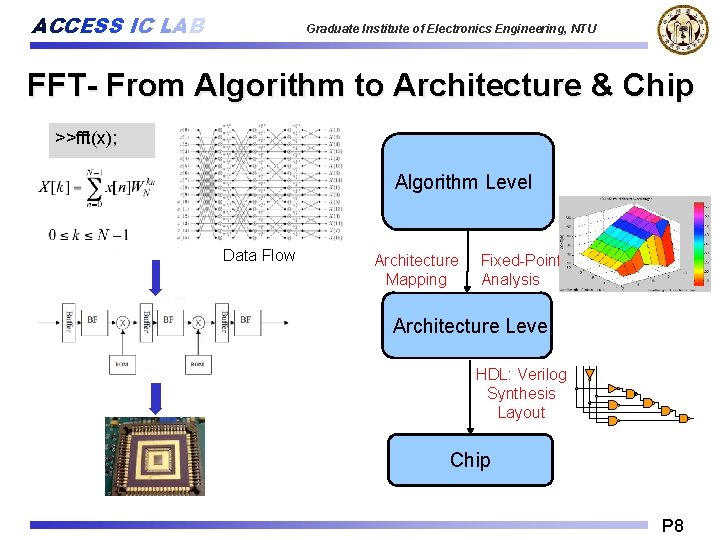

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU FFT- From Algorithm to Architecture & Chip >>fft(x); Algorithm Level Data Flow Architecture Mapping Fixed-Point Analysis Architecture Level HDL: Verilog Synthesis Layout Chip P 8

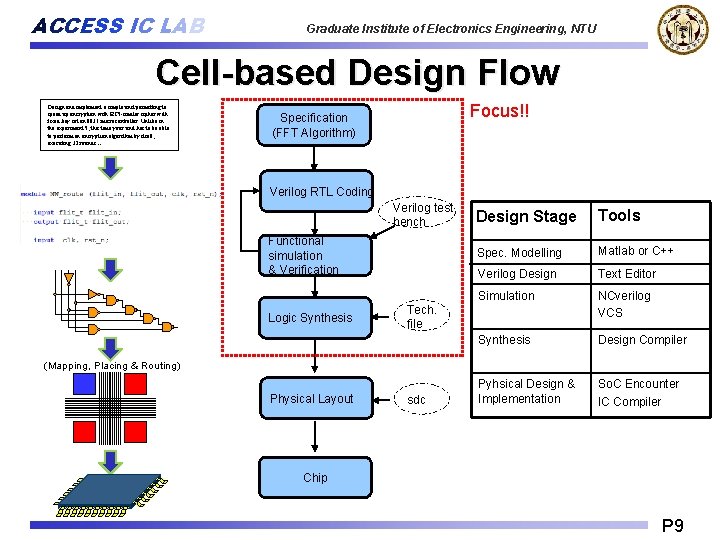

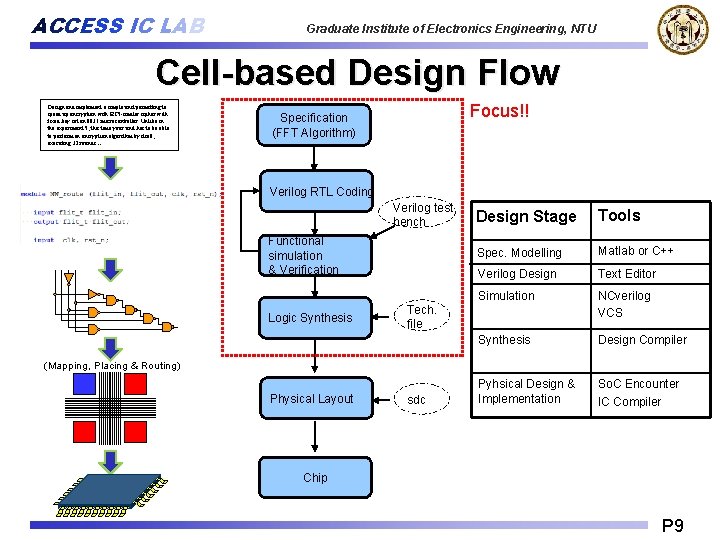

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Cell-based Design Flow Design and implement a simple unit permitting to speed up encryption with RC 5 -similar cipher with fixed key set on 8031 microcontroller. Unlike in the experiment 5, this time your unit has to be able to perform an encryption algorithm by itself, executing 32 rounds…. . Focus!! Specification (FFT Algorithm) Verilog RTL Coding Verilog test bench Functional simulation & Verification Logic Synthesis Design Stage Tools Spec. Modelling Matlab or C++ Verilog Design Text Editor Simulation NCverilog VCS Synthesis Design Compiler Pyhsical Design & Implementation So. C Encounter IC Compiler Tech. file (Mapping, Placing & Routing) Physical Layout sdc Chip P 9

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Verilog HDL v HDL – Hardware Description Language v Why use an HDL v Hardware is becoming very difficult to design directly v HDL is easier and cheaper to explore different design options v Reduce design time and cost v Goal v HDL has high-level programming language constructs and constructs to describe the connectivity of your circuit. v Ability to mix different levels of abstraction freely v One language for all aspects of design, test, and verification P 10

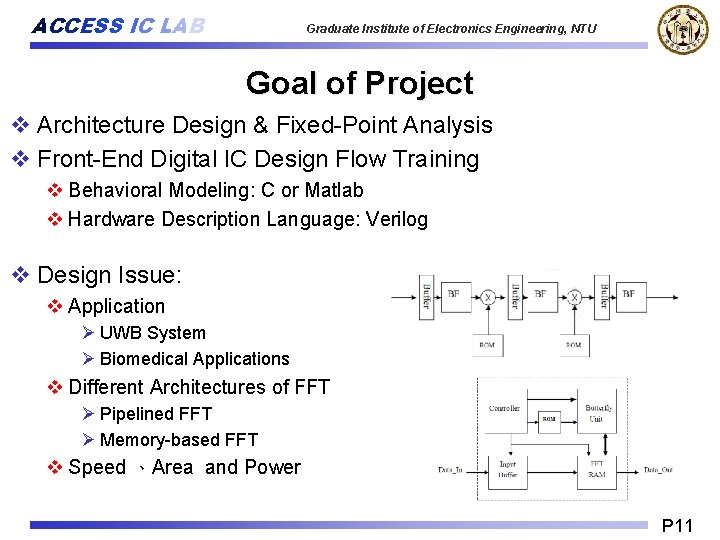

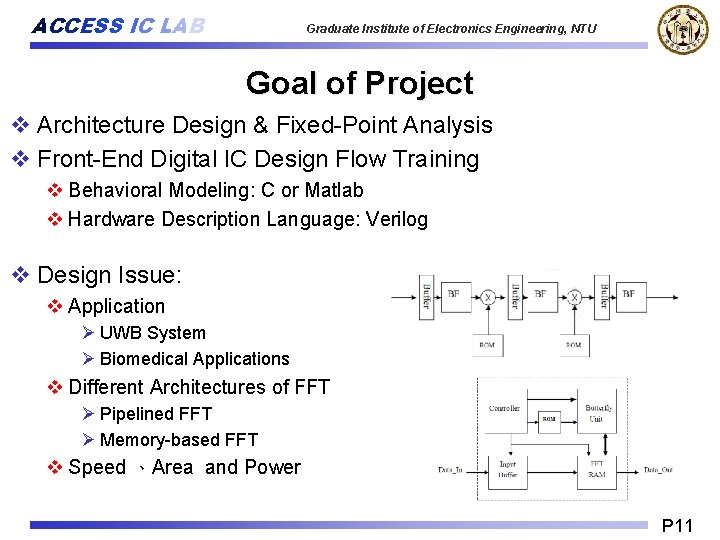

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Goal of Project v Architecture Design & Fixed-Point Analysis v Front-End Digital IC Design Flow Training v Behavioral Modeling: C or Matlab v Hardware Description Language: Verilog v Design Issue: v Application Ø UWB System Ø Biomedical Applications v Different Architectures of FFT Ø Pipelined FFT Ø Memory-based FFT v Speed 、Area and Power P 11

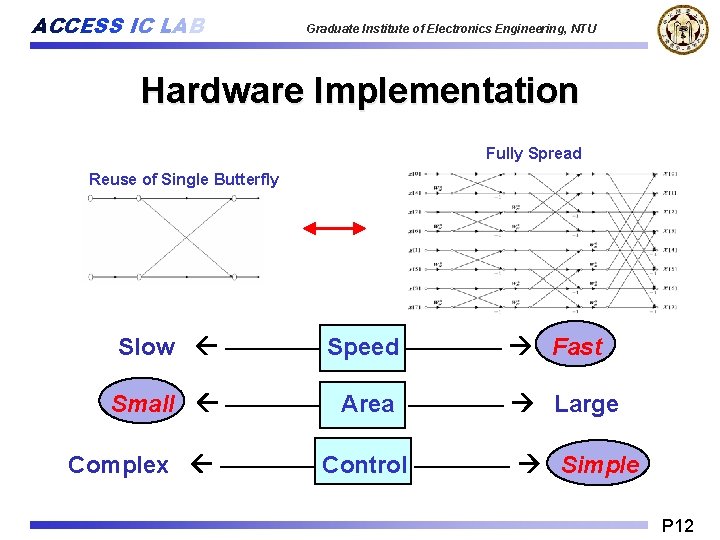

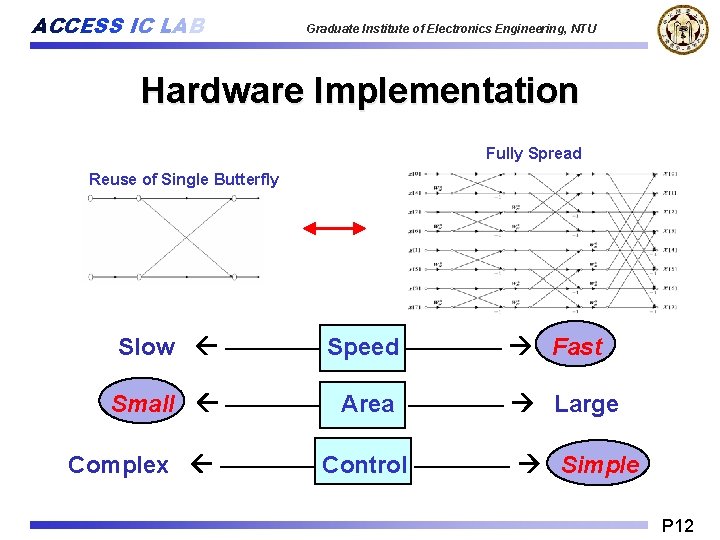

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Hardware Implementation Fully Spread Reuse of Single Butterfly Slow ———— Speed ———— Fast Small ———— Area ———— Large Complex ———— Control ———— Simple P 12

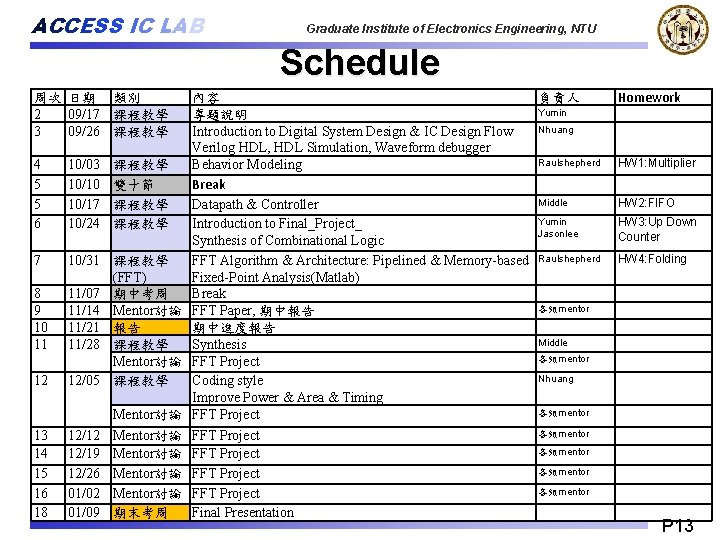

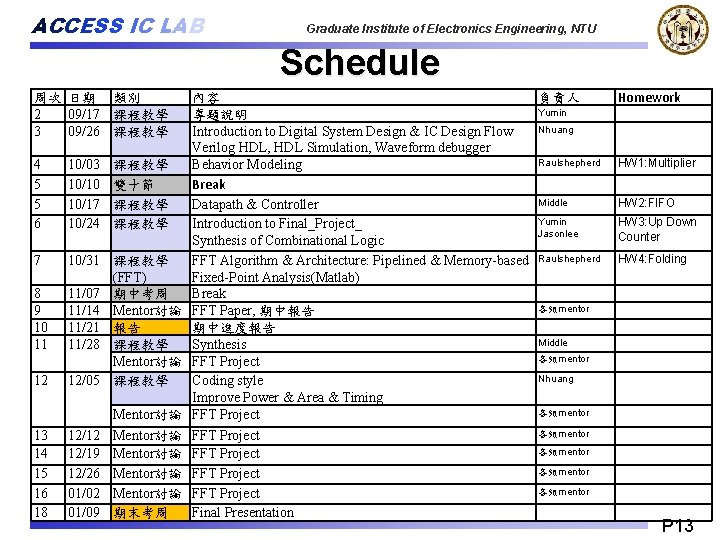

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Schedule 周次 日期 類別 2 09/17 課程教學 3 09/26 課程教學 Homework 4 5 5 6 HW 1: Multiplier 7 8 9 10 11 12 13 14 15 16 18 內容 負責人 Yumin 專題說明 Nhuang Introduction to Digital System Design & IC Design Flow Verilog HDL, HDL Simulation, Waveform debugger Raulshepherd 10/03 課程教學 Behavior Modeling Break 10/10 雙十節 Middle 10/17 課程教學 Datapath & Controller Yumin 10/24 課程教學 Introduction to Final_Project_ Jasonlee Synthesis of Combinational Logic 10/31 課程教學 FFT Algorithm & Architecture: Pipelined & Memory-based Raulshepherd (FFT) Fixed-Point Analysis(Matlab) 11/07 期中考周 Break 各組mentor 11/14 Mentor討論 FFT Paper, 期中報告 期中進度報告 11/21 報告 Middle 11/28 課程教學 Synthesis 各組mentor Mentor討論 FFT Project Nhuang 12/05 課程教學 Coding style Improve Power & Area & Timing 各組mentor Mentor討論 FFT Project 12/12 12/19 12/26 01/02 01/09 Mentor討論 期末考周 FFT Project Final Presentation HW 2: FIFO HW 3: Up Down Counter HW 4: Folding 各組mentor P 13

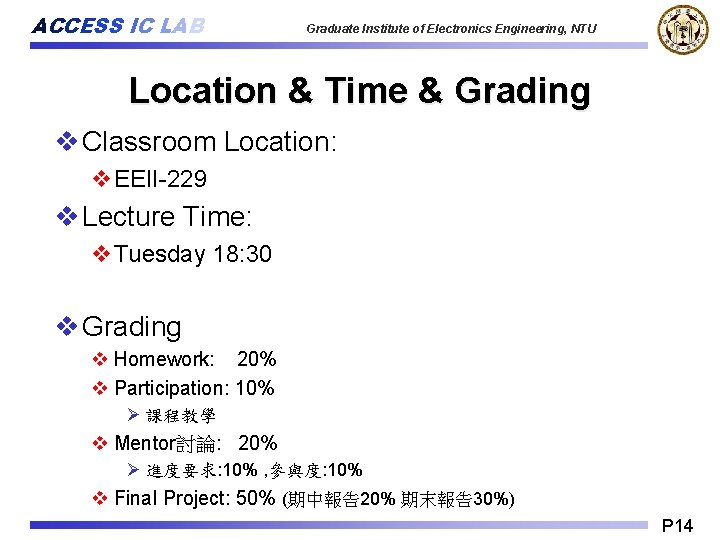

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Location & Time & Grading v Classroom Location: v. EEII-229 v Lecture Time: v. Tuesday 18: 30 v Grading v Homework: 20% v Participation: 10% Ø 課程教學 v Mentor討論: 20% Ø 進度要求: 10% , 參與度: 10% v Final Project: 50% (期中報告20% 期末報告30%) P 14

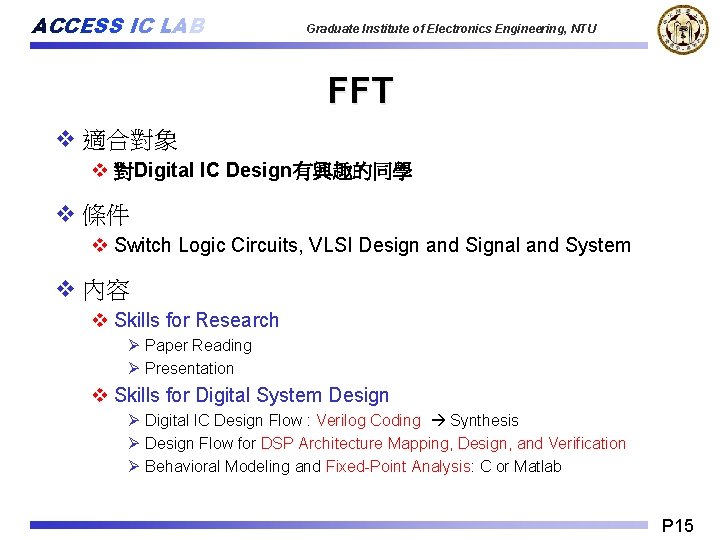

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU FFT v 適合對象 v 對Digital IC Design有興趣的同學 v 條件 v Switch Logic Circuits, VLSI Design and Signal and System v 內容 v Skills for Research Ø Paper Reading Ø Presentation v Skills for Digital System Design Ø Digital IC Design Flow : Verilog Coding Synthesis Ø Design Flow for DSP Architecture Mapping, Design, and Verification Ø Behavioral Modeling and Fixed-Point Analysis: C or Matlab P 15