Graduate Institute of Electronics Engineering NTU Multirate Processing

- Slides: 30

Graduate Institute of Electronics Engineering, NTU Multirate Processing of Digital Signals: Fundamentals VLSI Signal Processing 台灣大學電機系 吳安宇 ACCESS IC LAB

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Outline Introduction Sampling Rate Conversion Multistage Implementation Practice Structure Polyphase Implementation

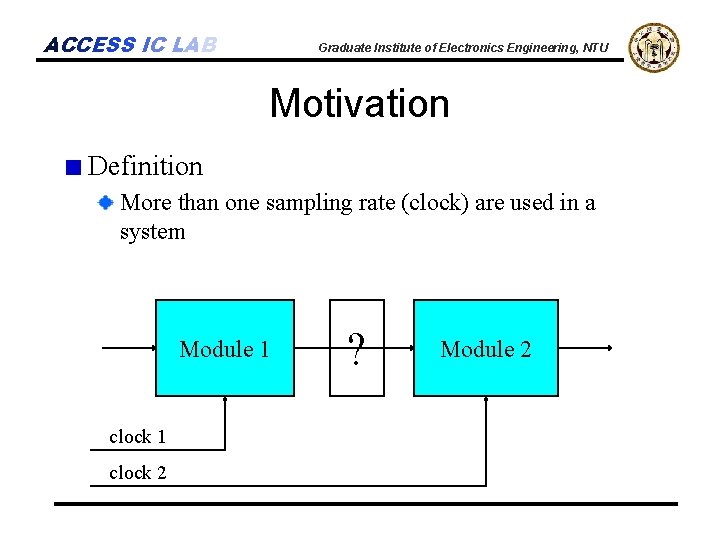

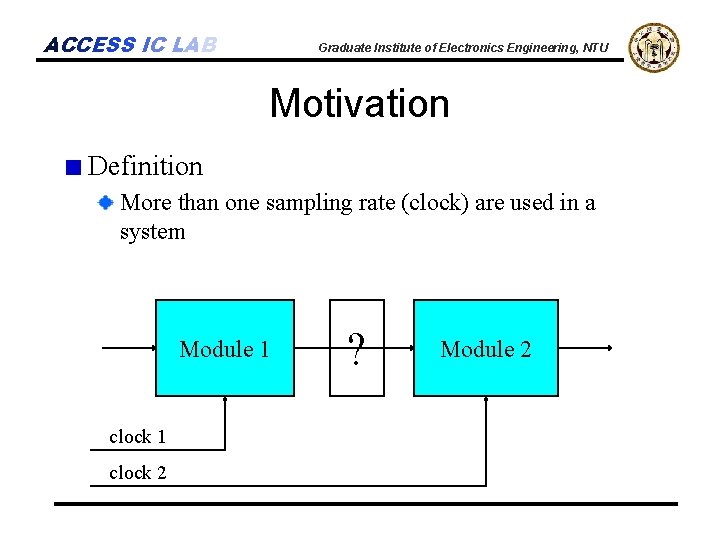

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Motivation Definition More than one sampling rate (clock) are used in a system Module 1 clock 2 ? Module 2

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Conversion Approach Analog approach Digital approach (multirate DSP system)

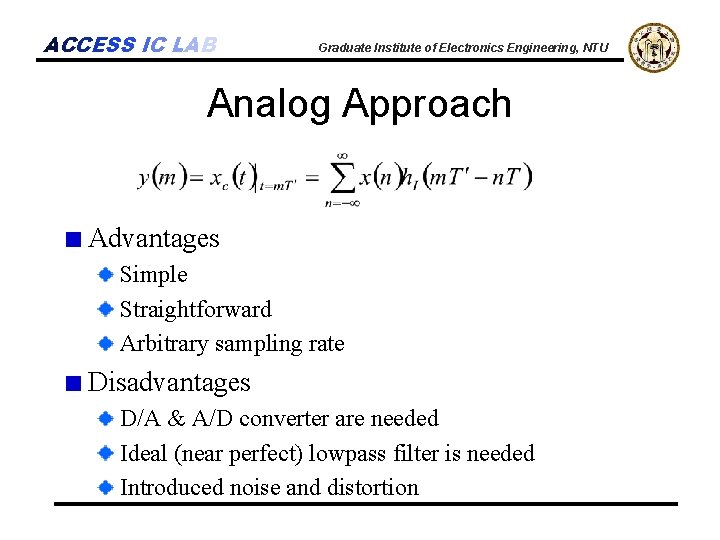

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Analog Approach Advantages Simple Straightforward Arbitrary sampling rate Disadvantages D/A & A/D converter are needed Ideal (near perfect) lowpass filter is needed Introduced noise and distortion

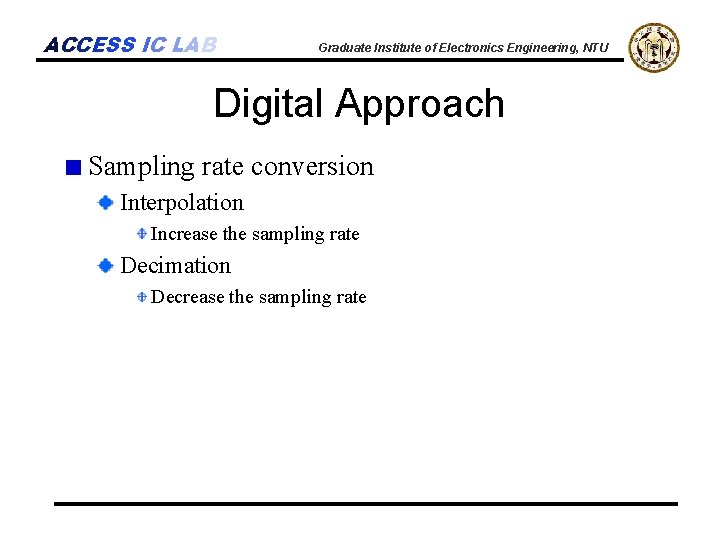

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Digital Approach Sampling rate conversion Interpolation Increase the sampling rate Decimation Decrease the sampling rate

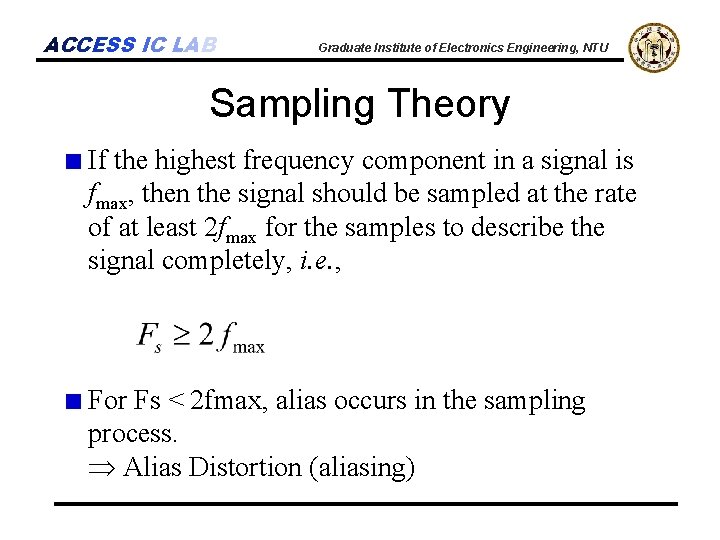

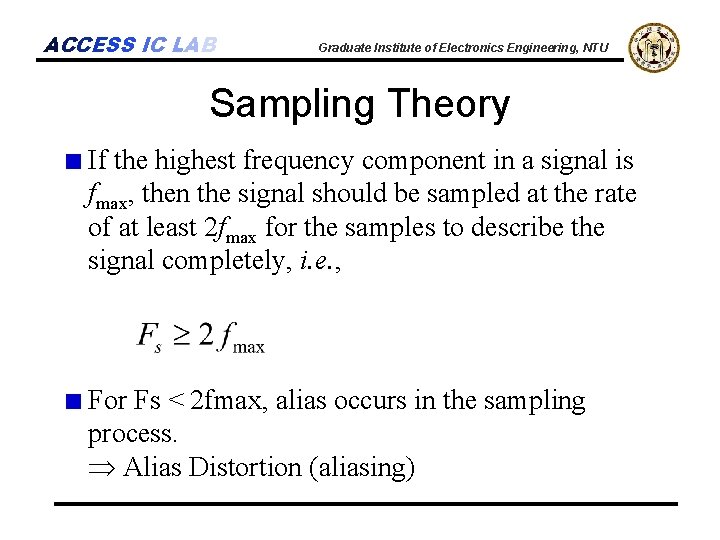

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Sampling Theory If the highest frequency component in a signal is fmax, then the signal should be sampled at the rate of at least 2 fmax for the samples to describe the signal completely, i. e. , For Fs < 2 fmax, alias occurs in the sampling process. Alias Distortion (aliasing)

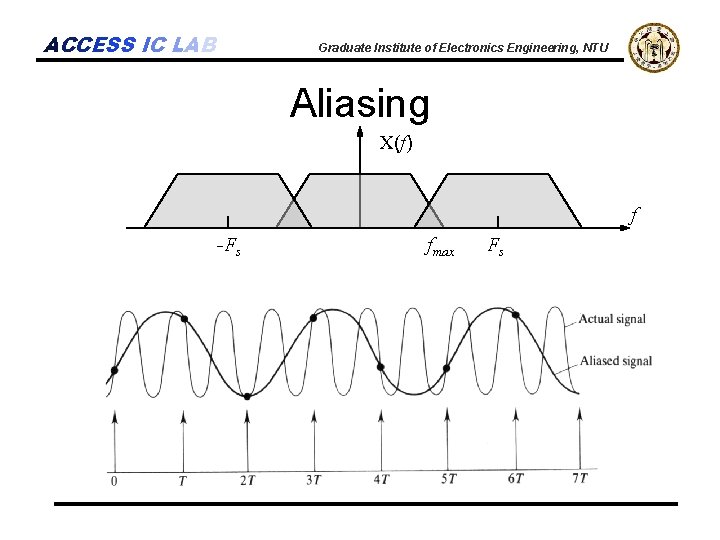

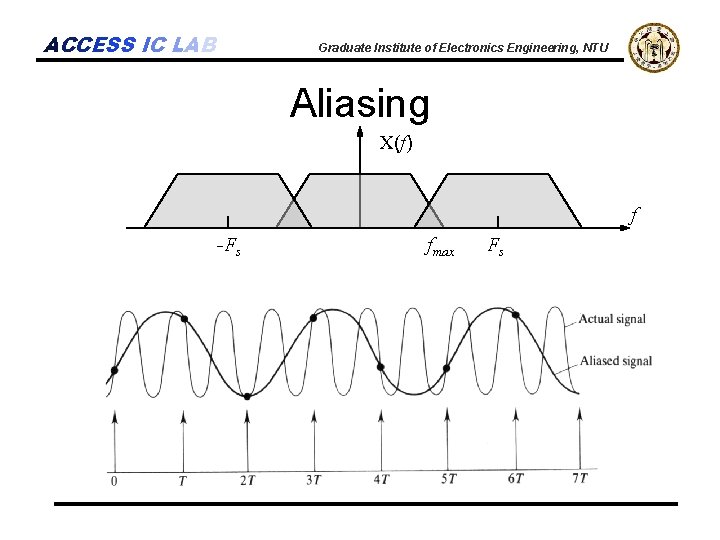

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Aliasing X(f) f -Fs fmax Fs

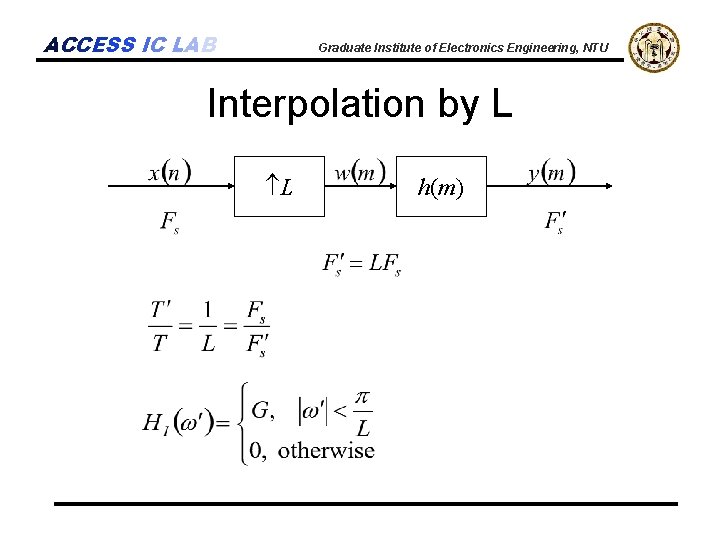

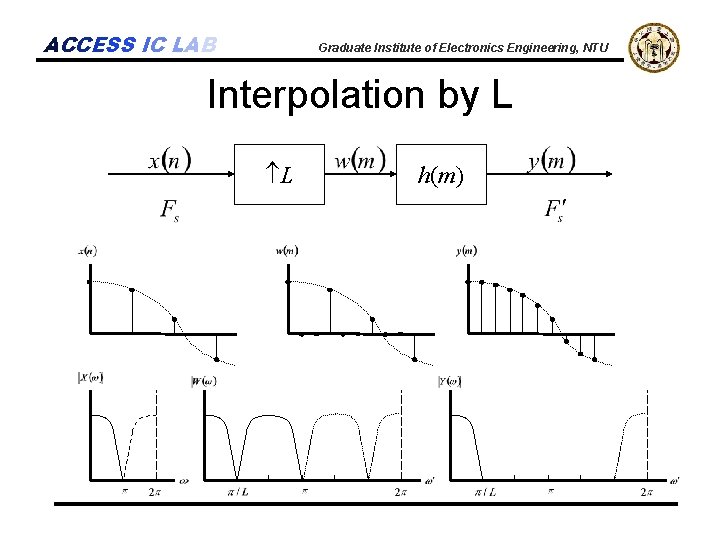

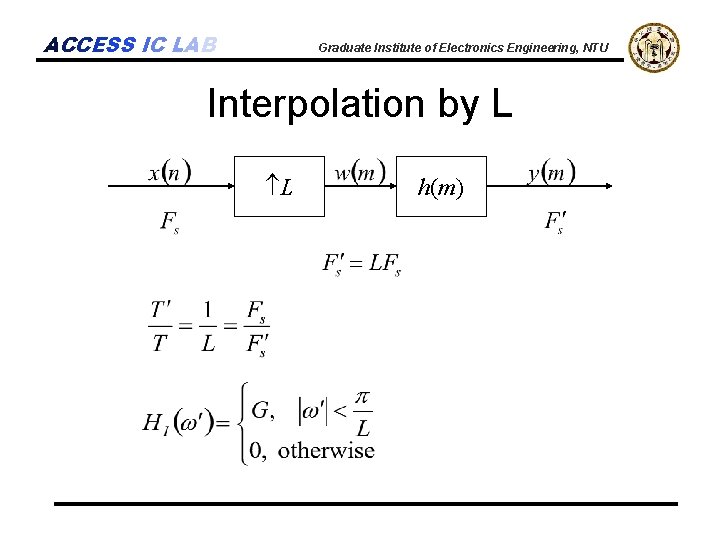

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Interpolation by L L h(m)

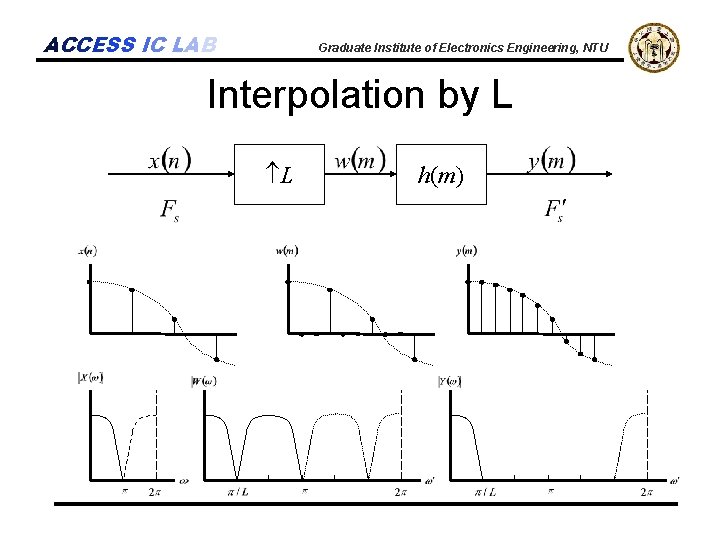

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Interpolation by L L h(m)

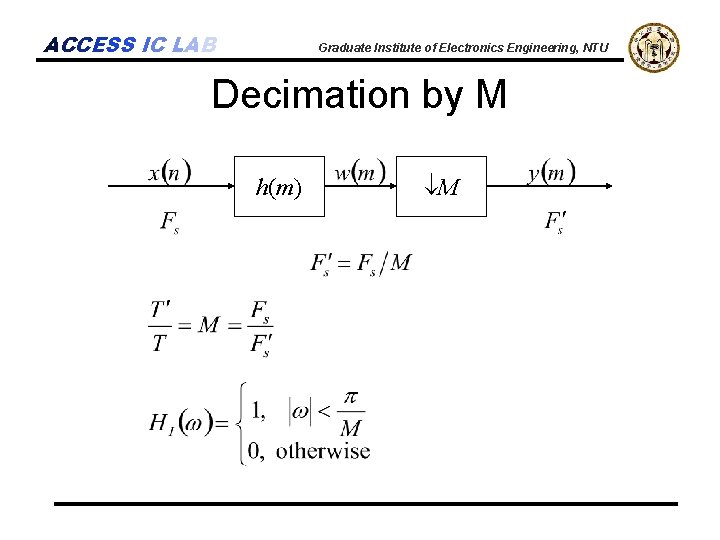

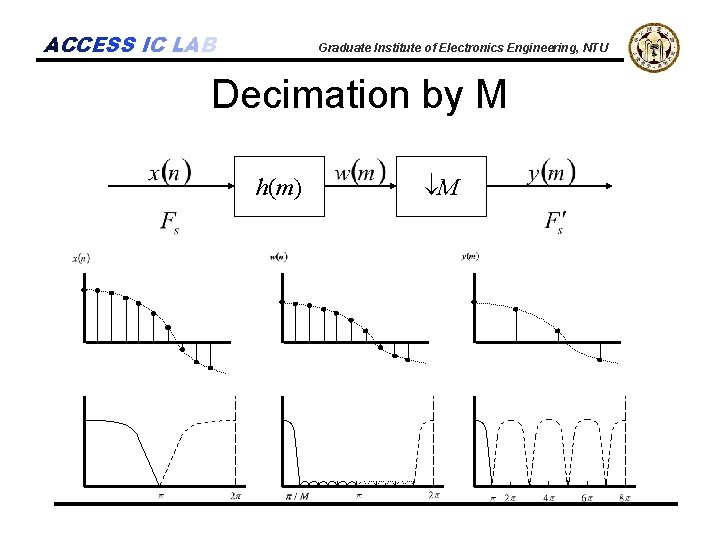

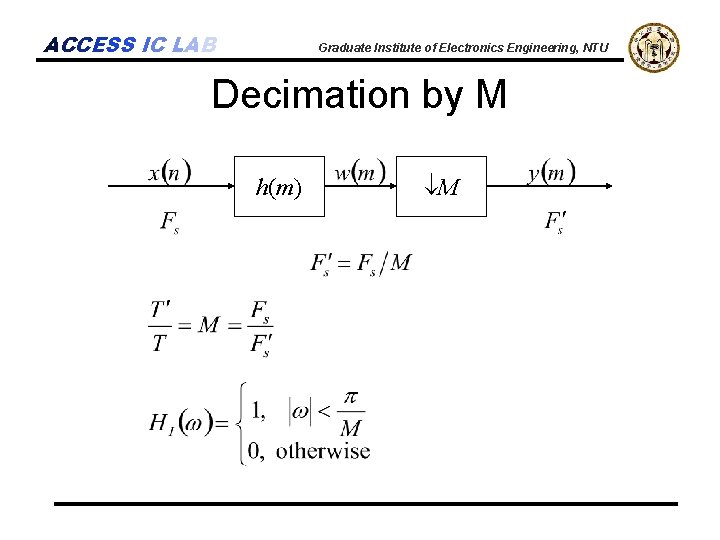

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Decimation by M h(m) M

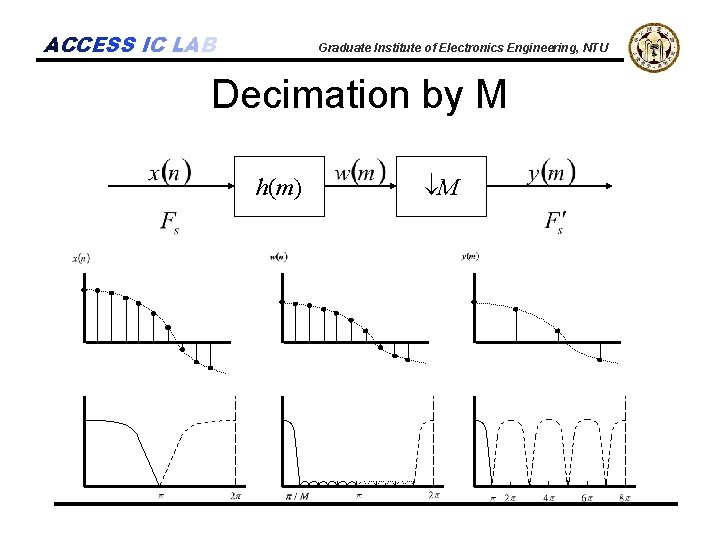

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Decimation by M h(m) M

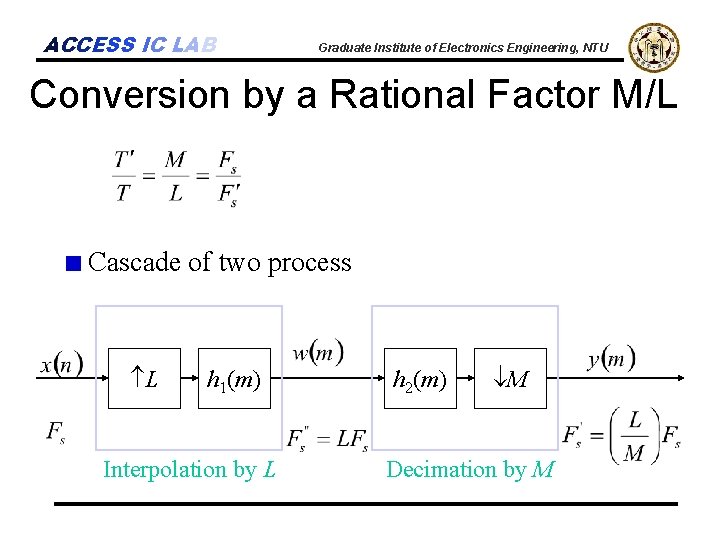

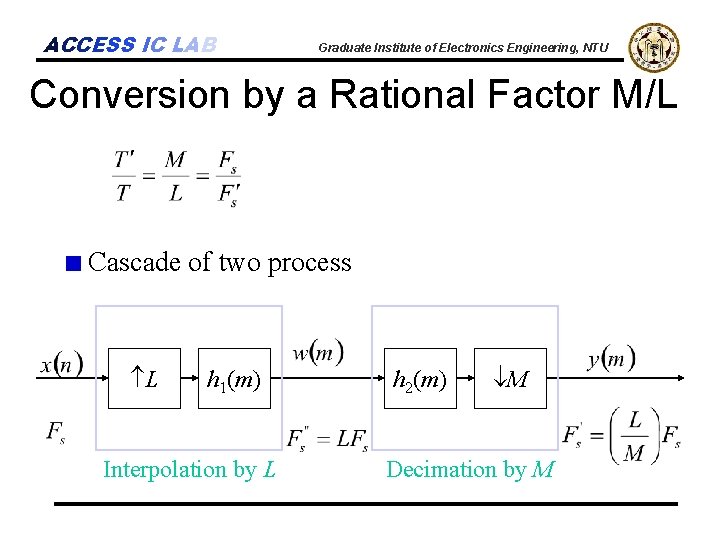

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Conversion by a Rational Factor M/L Cascade of two process L h 1(m) Interpolation by L h 2(m) M Decimation by M

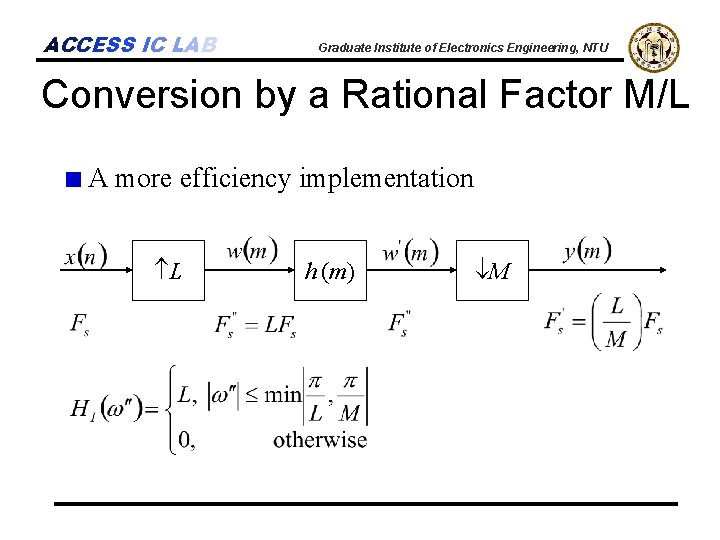

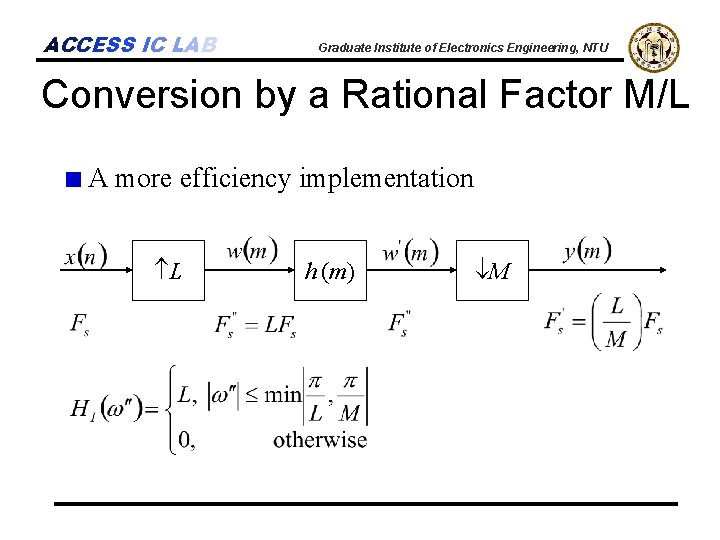

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Conversion by a Rational Factor M/L A more efficiency implementation L h (m) M

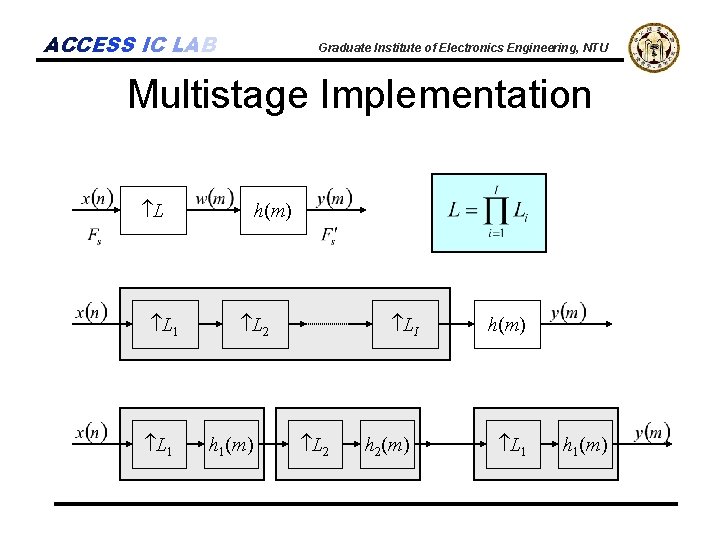

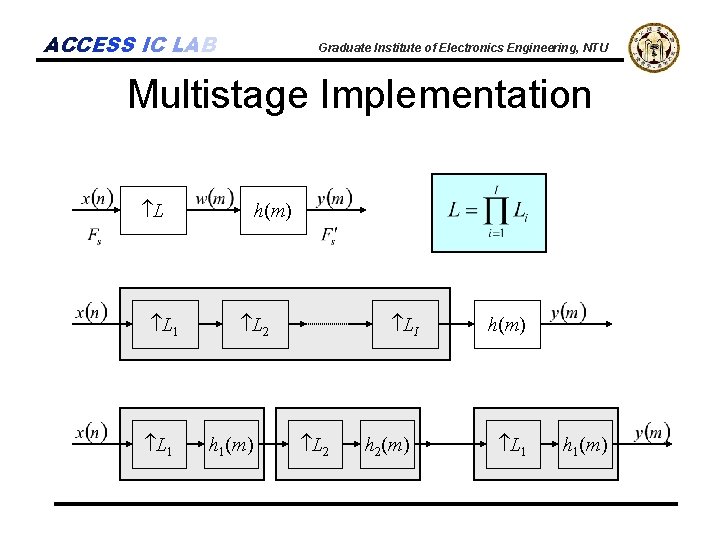

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Multistage Implementation L L 1 h(m) L 2 h 1(m) LI L 2 h 2(m) h(m) L 1 h 1(m)

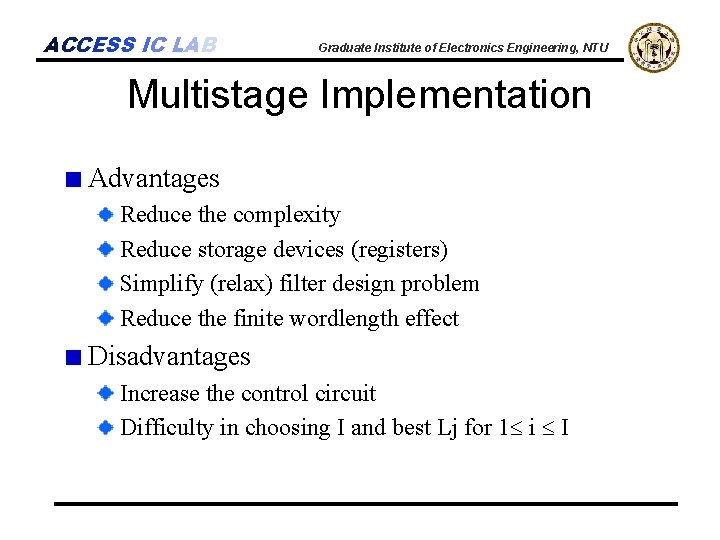

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Multistage Implementation Advantages Reduce the complexity Reduce storage devices (registers) Simplify (relax) filter design problem Reduce the finite wordlength effect Disadvantages Increase the control circuit Difficulty in choosing I and best Lj for 1 i I

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Interpolated FIR (IFIR) Approach Nothing to do with interpolation and decimation Conceptually similar Suitable for narrowband FIR filter design LPF HPF BPF

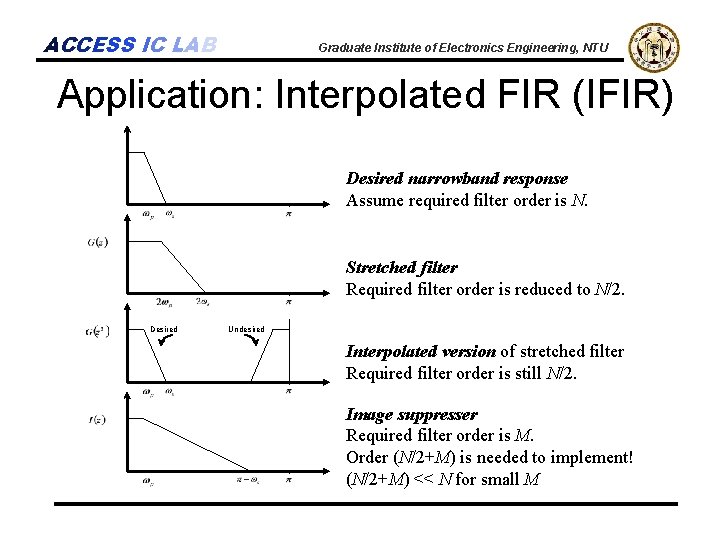

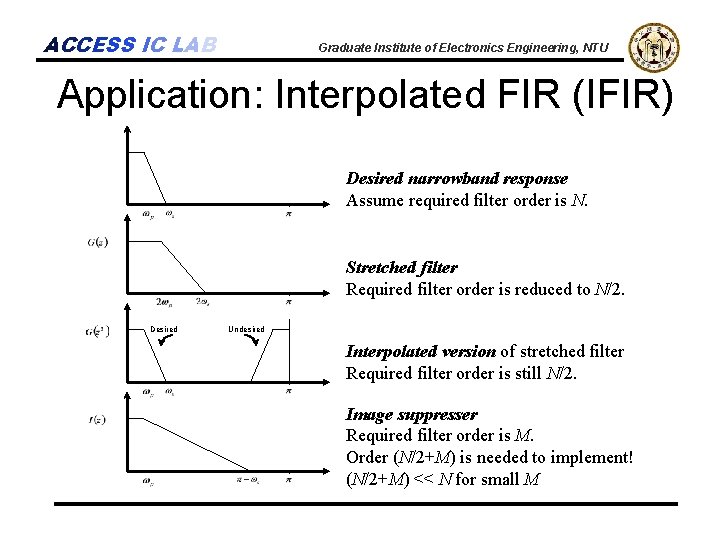

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Application: Interpolated FIR (IFIR) Desired narrowband response Assume required filter order is N. Stretched filter Required filter order is reduced to N/2. Desired Undesired Interpolated version of stretched filter Required filter order is still N/2. Image suppresser Required filter order is M. Order (N/2+M) is needed to implement! (N/2+M) << N for small M

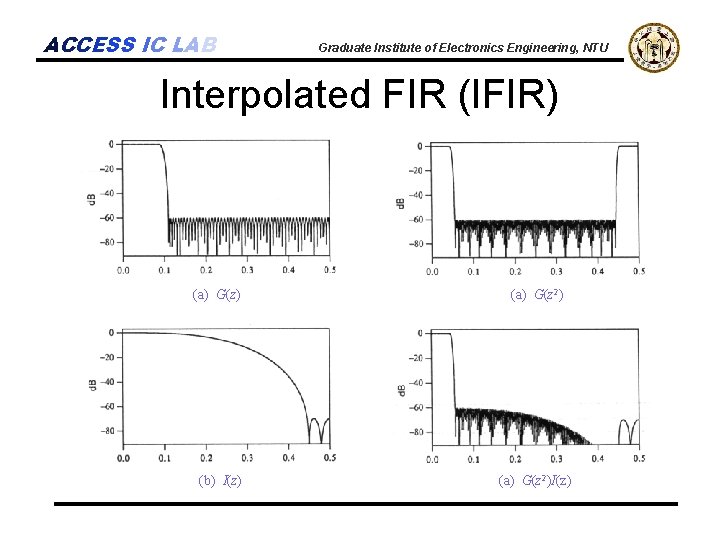

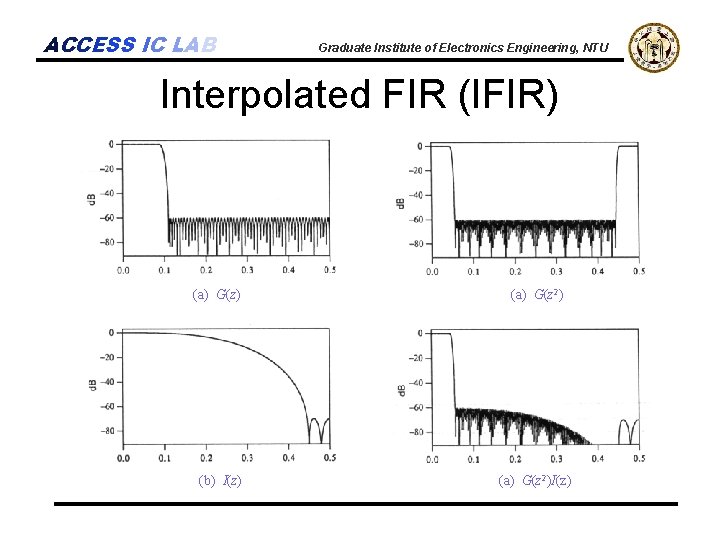

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Interpolated FIR (IFIR) (a) G(z 2) (b) I(z) (a) G(z 2)I(z)

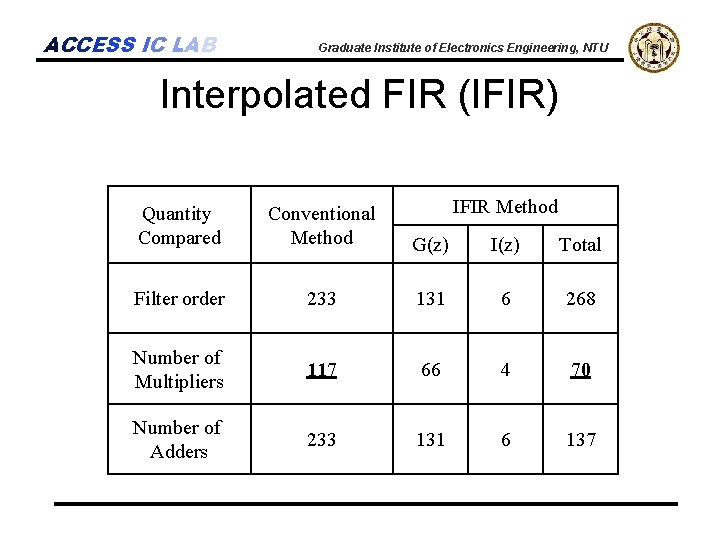

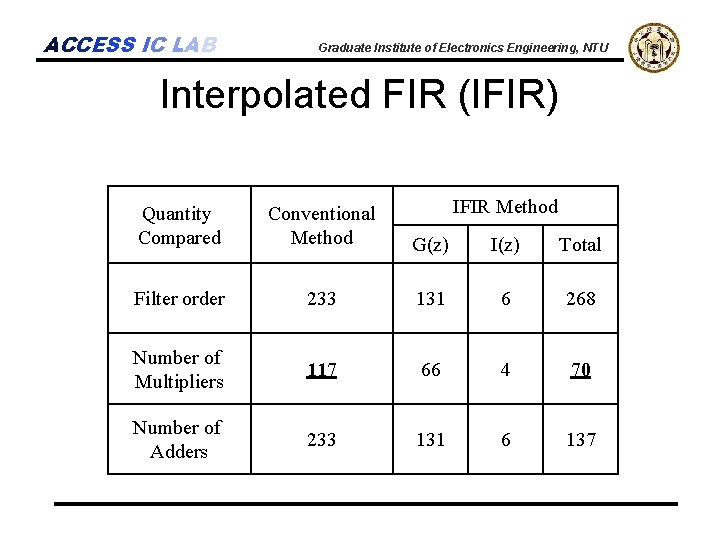

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Interpolated FIR (IFIR) IFIR Method Quantity Compared Conventional Method G(z) I(z) Total Filter order 233 131 6 268 Number of Multipliers 117 66 4 70 Number of Adders 233 131 6 137

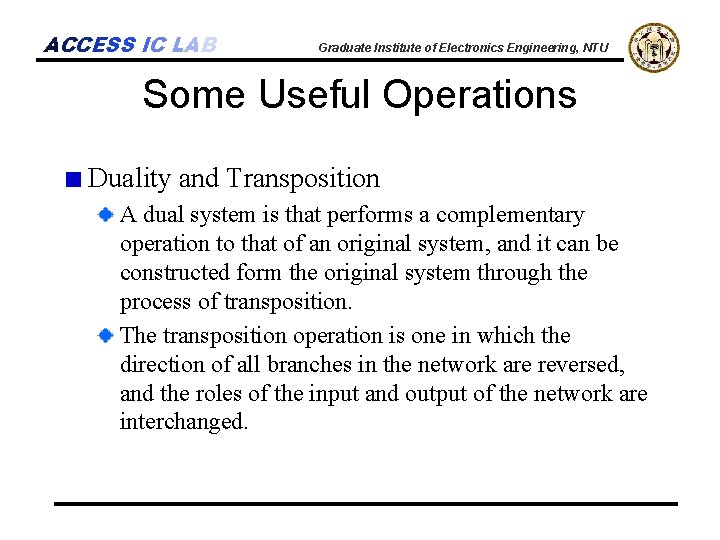

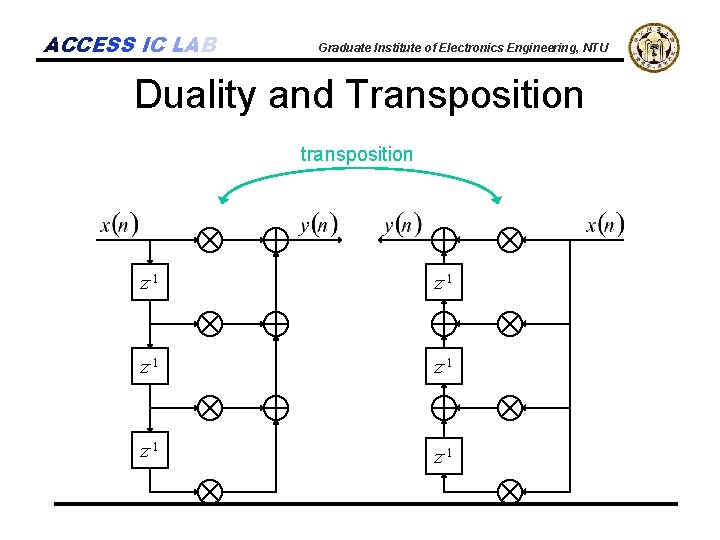

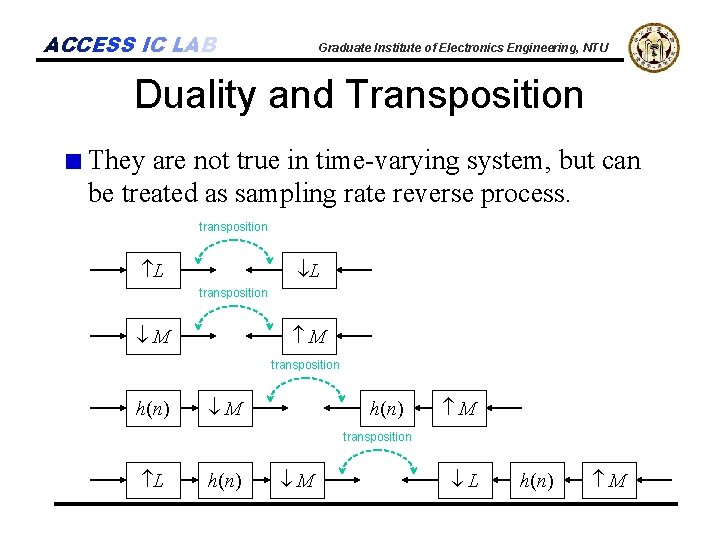

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Some Useful Operations Duality and Transposition A dual system is that performs a complementary operation to that of an original system, and it can be constructed form the original system through the process of transposition. The transposition operation is one in which the direction of all branches in the network are reversed, and the roles of the input and output of the network are interchanged.

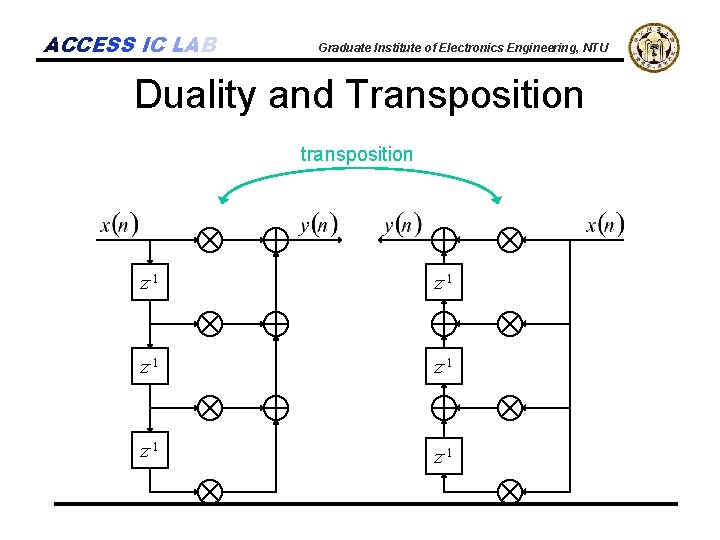

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Duality and Transposition transposition z-1 z-1 z-1

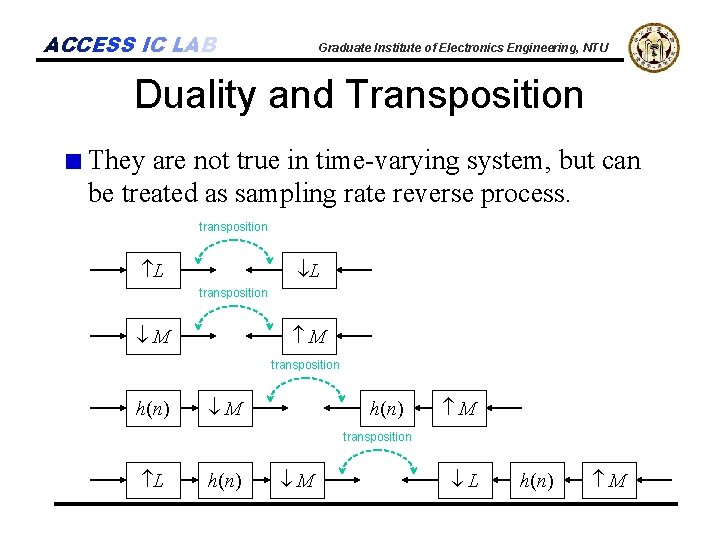

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Duality and Transposition They are not true in time-varying system, but can be treated as sampling rate reverse process. transposition L L transposition M M transposition h(n) M transposition L h(n) M

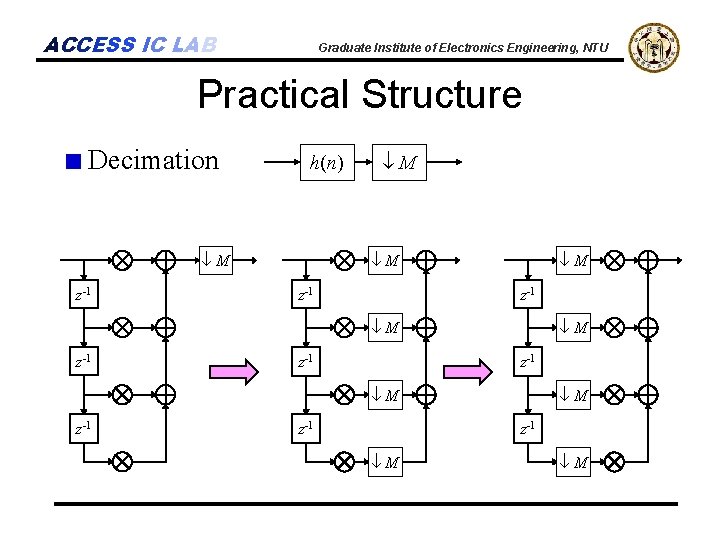

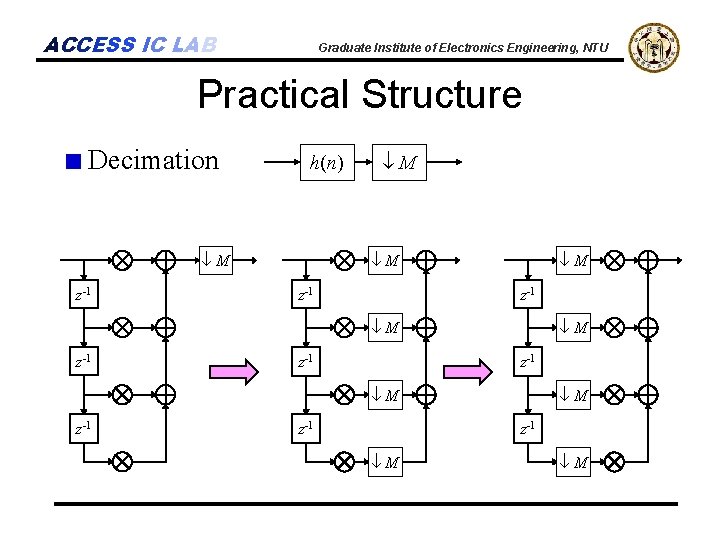

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Practical Structure Decimation h(n) M z-1 M z-1 M z-1 M M

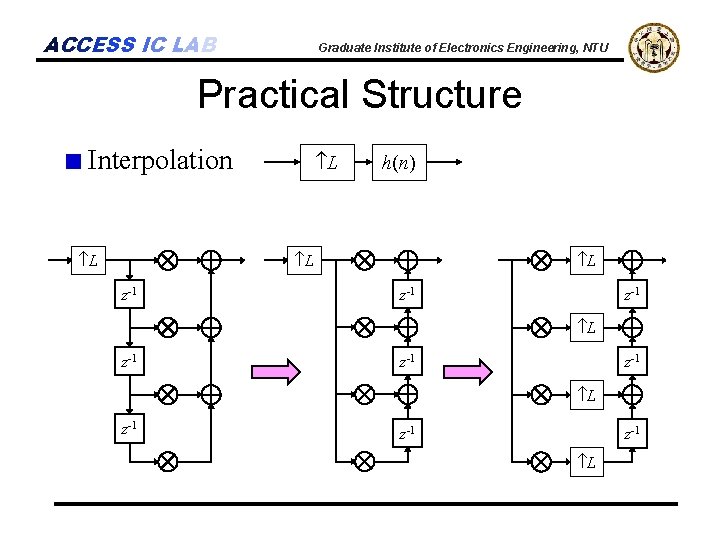

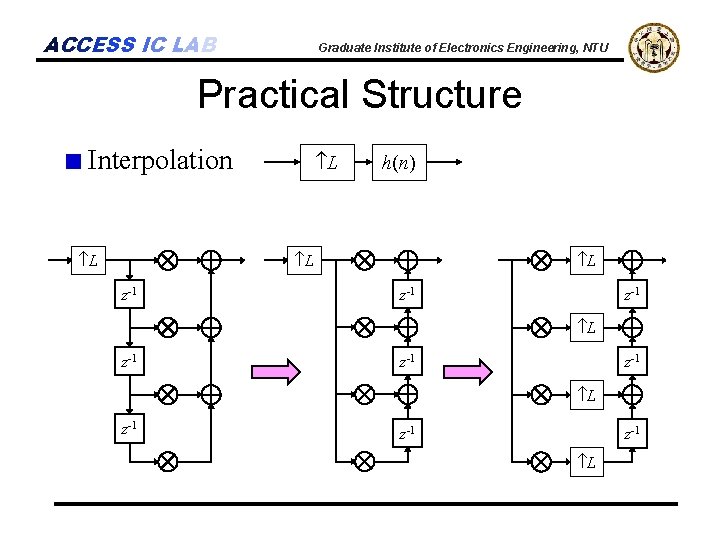

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Practical Structure Interpolation L h(n) L L z-1 z-1 z-1 L

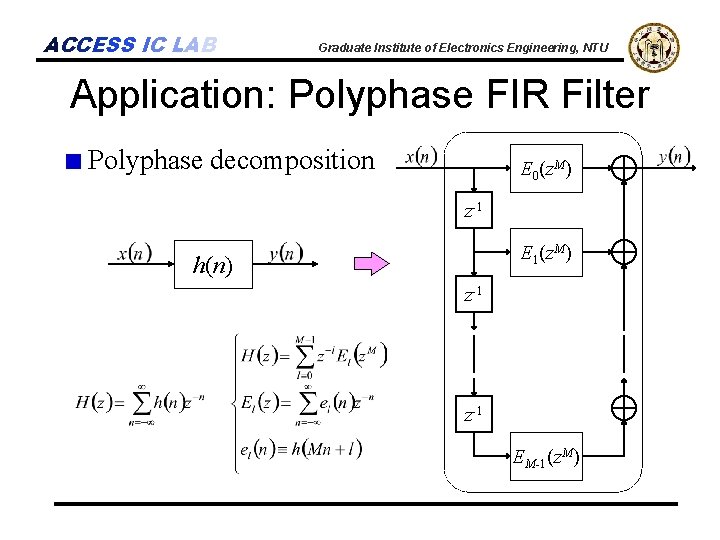

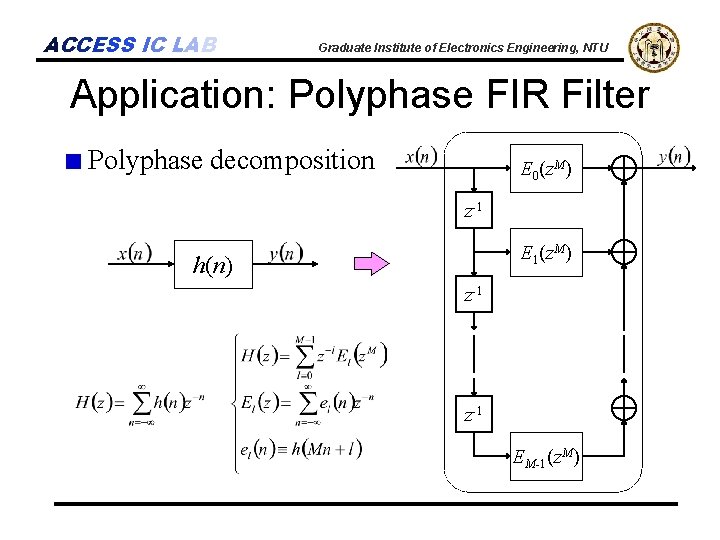

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Application: Polyphase FIR Filter Polyphase decomposition E 0(z. M) z-1 E 1(z. M) h(n) z-1 EM-1(z. M)

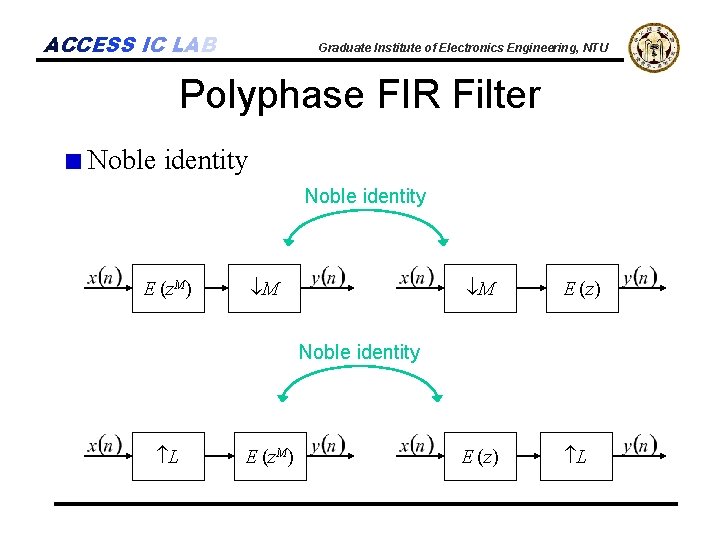

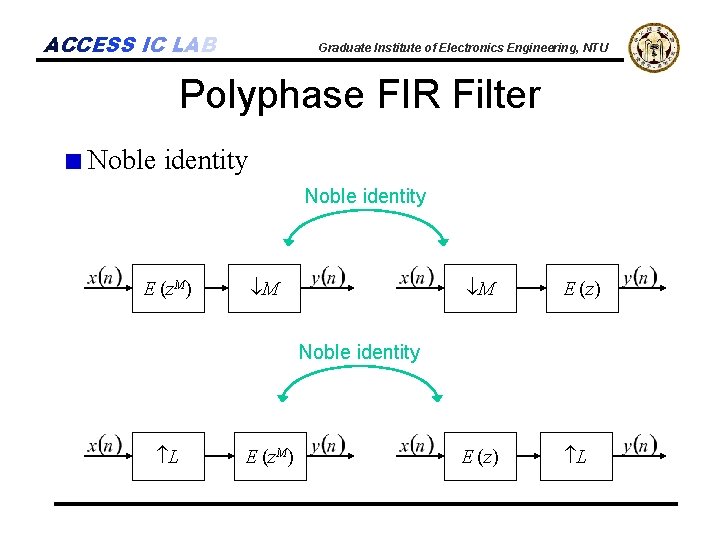

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Polyphase FIR Filter Noble identity E (z. M) M M E (z) L Noble identity L E (z. M)

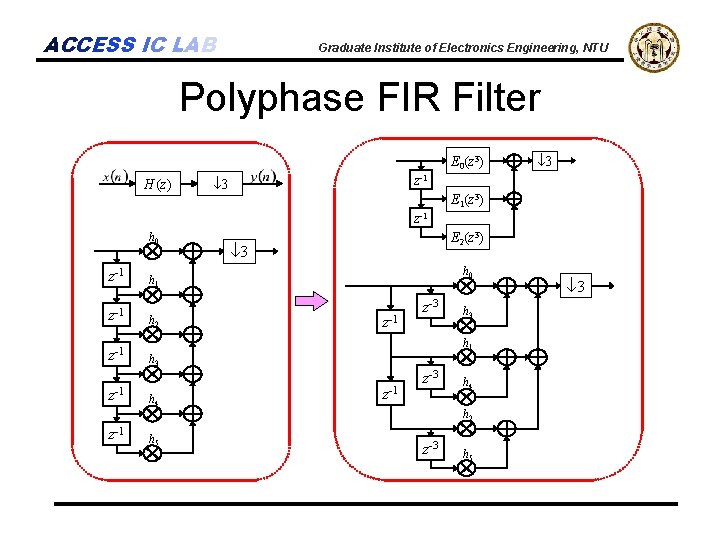

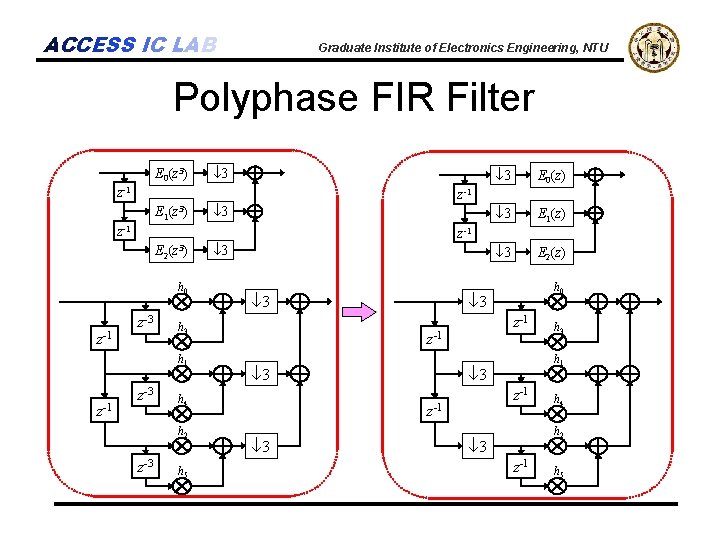

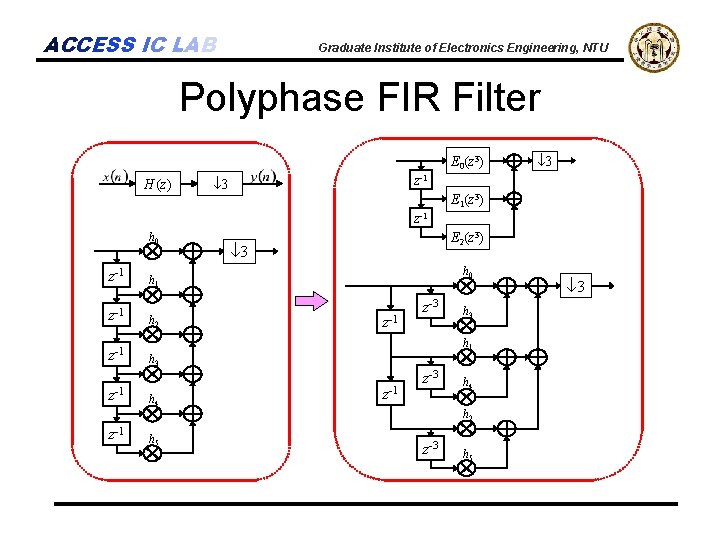

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Polyphase FIR Filter E 0(z 3) H (z) 3 z-1 3 E 1(z 3) z-1 h 0 z-1 z-1 z-1 E 2(z 3) 3 h 0 h 1 h 2 z-1 z-3 h 1 h 3 h 4 h 5 z-1 z-3 h 4 h 2 z-3 h 5 3

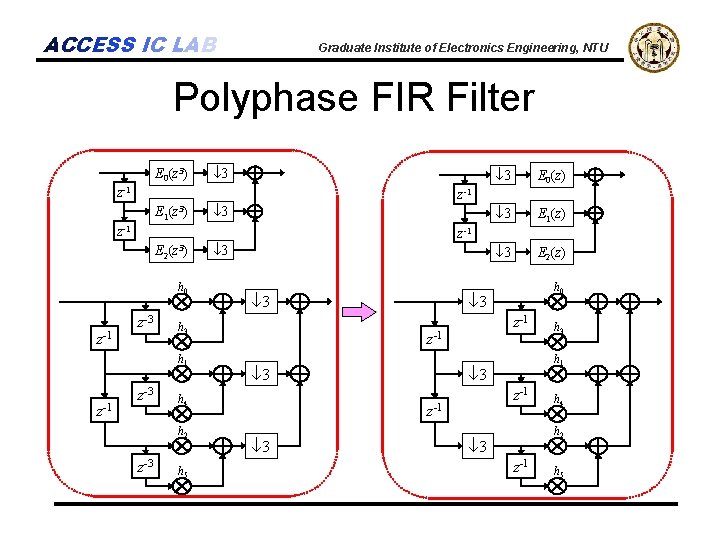

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Polyphase FIR Filter E 0(z 3) 3 z-1 3 E 1(z) 3 E 2(z) z-1 E 2(z 3) h 0 z-3 3 3 h 5 z-1 h 3 h 1 3 z-1 3 h 0 3 z-1 h 4 h 2 z-3 3 h 1 z-1 E 0(z) z-1 E 1(z 3) z-1 3 h 4 h 2 3 z-1 h 5

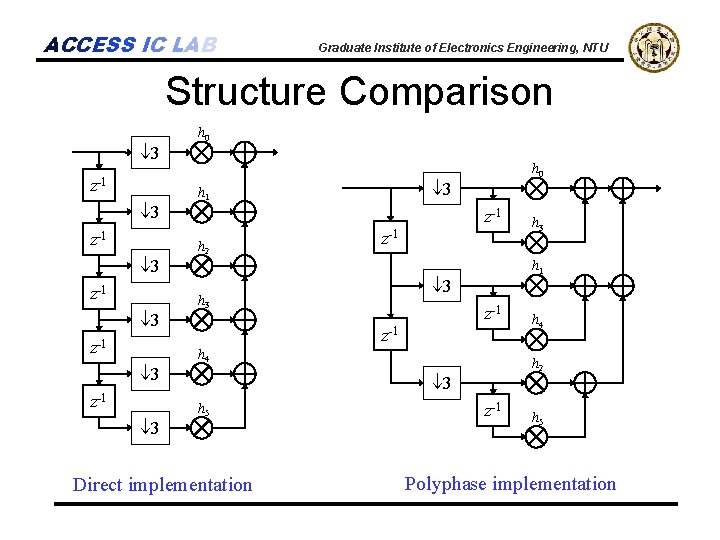

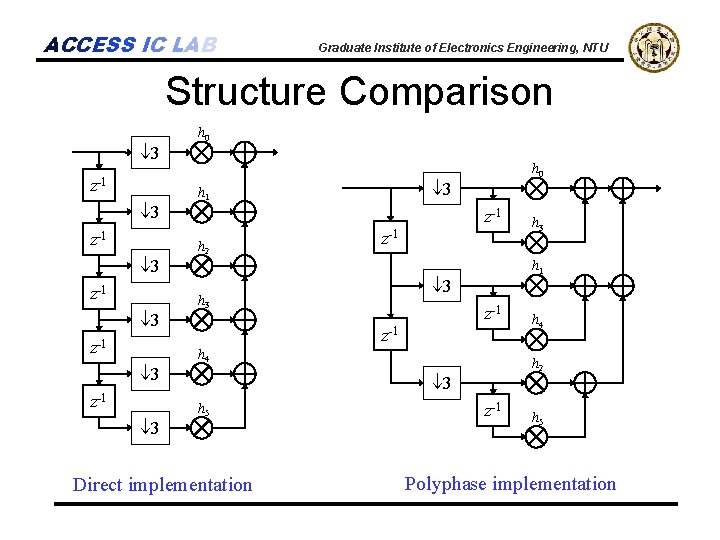

ACCESS IC LAB Graduate Institute of Electronics Engineering, NTU Structure Comparison 3 z-1 3 z-1 3 h 0 3 h 1 z-1 h 2 z-1 h 1 3 h 3 z-1 h 4 Direct implementation h 4 h 2 3 h 5 h 3 z-1 h 5 Polyphase implementation