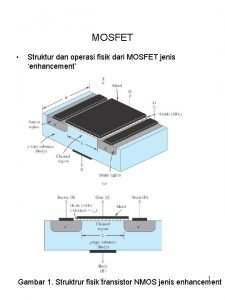

Feldeffekttransistoren MOSFET Aufbau und Funktionsweise nKanalEnhancementFET Feldeffekttransistoren MOSFET

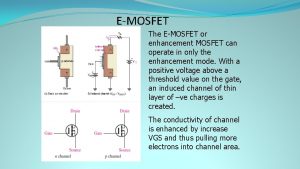

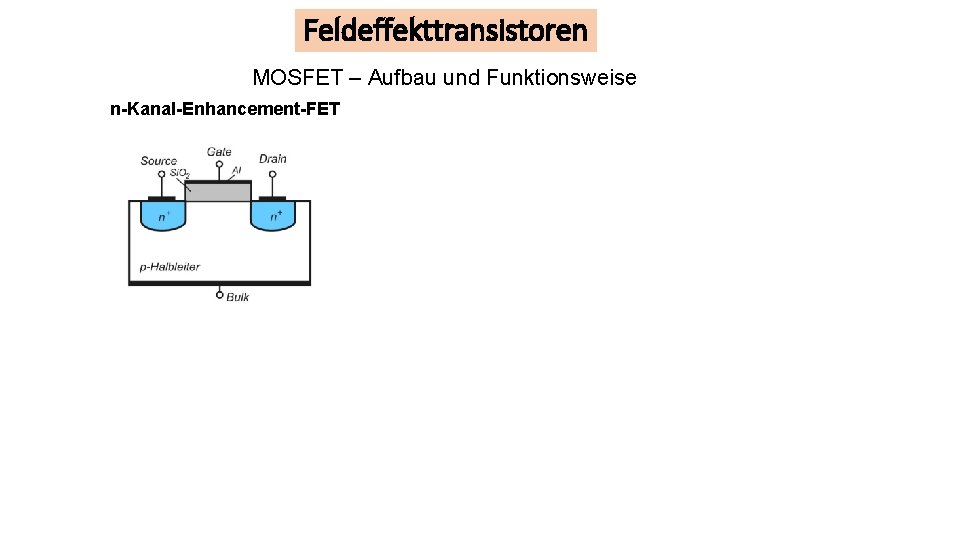

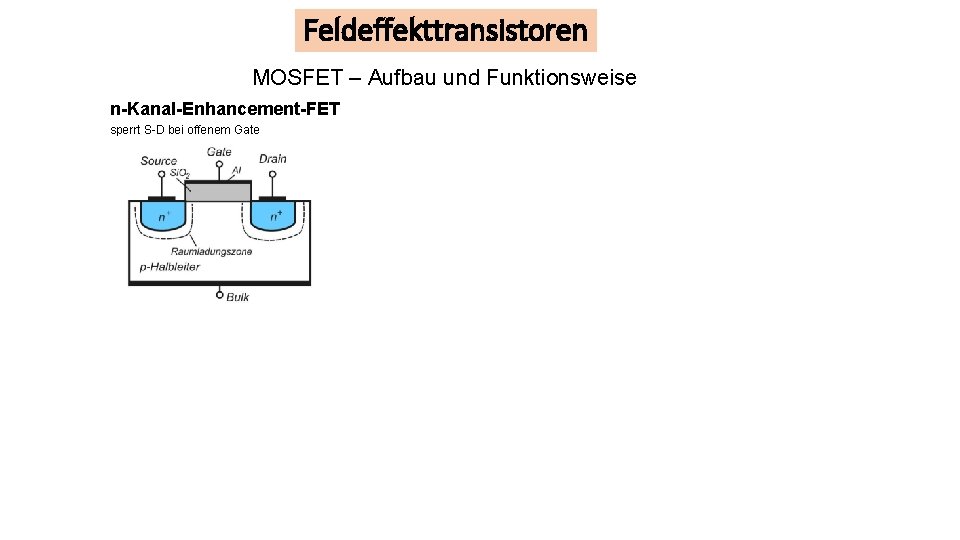

Feldeffekttransistoren MOSFET – Aufbau und Funktionsweise n-Kanal-Enhancement-FET

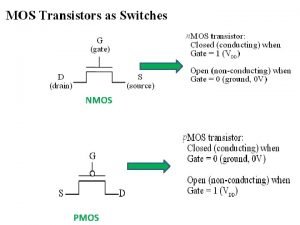

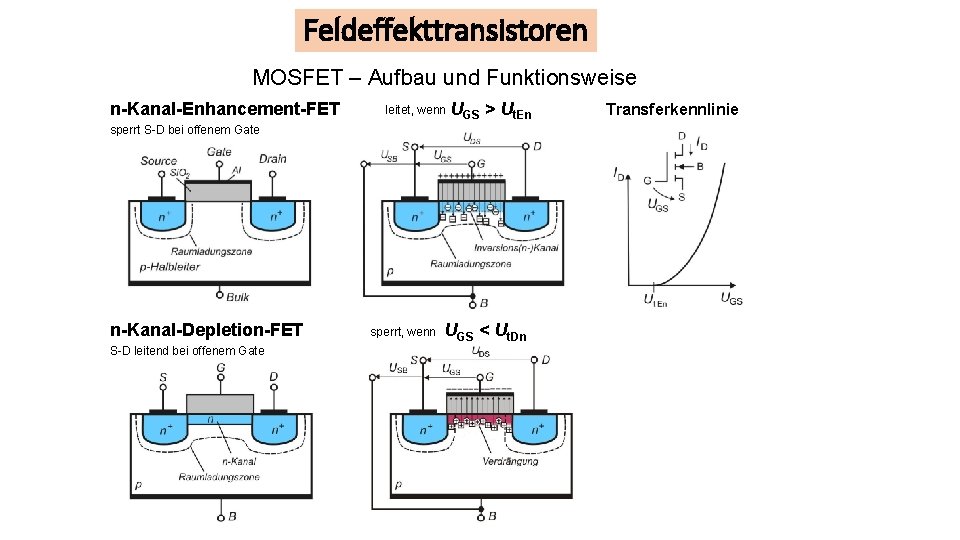

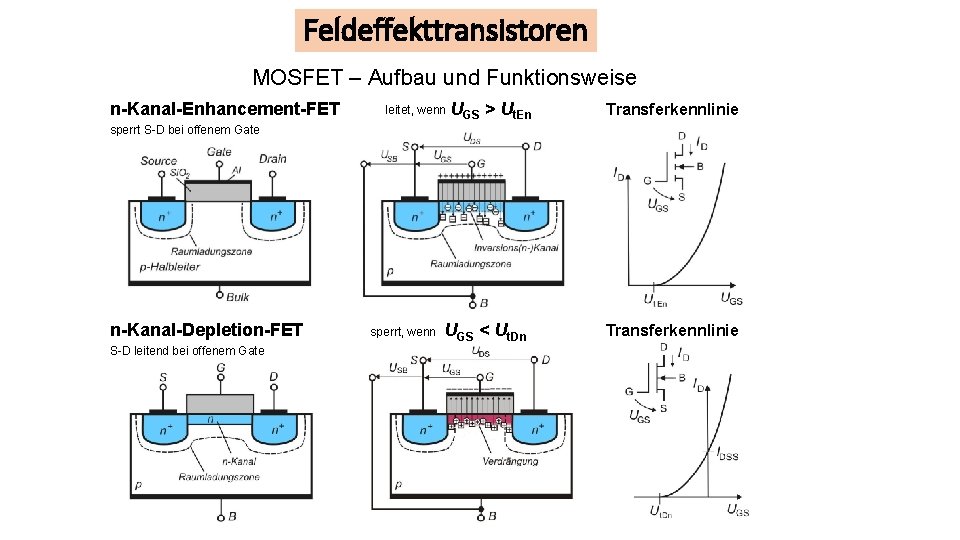

Feldeffekttransistoren MOSFET – Aufbau und Funktionsweise n-Kanal-Enhancement-FET sperrt S-D bei offenem Gate

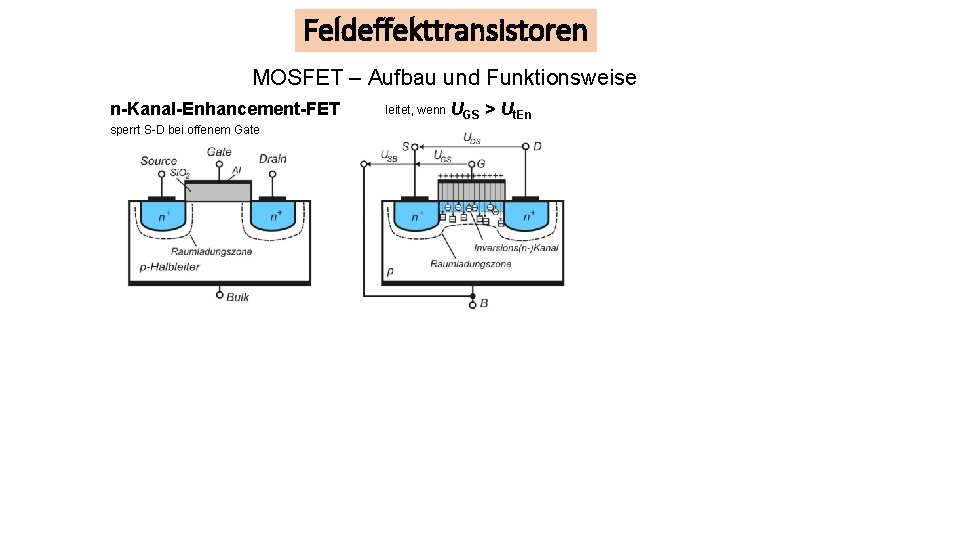

Feldeffekttransistoren MOSFET – Aufbau und Funktionsweise n-Kanal-Enhancement-FET sperrt S-D bei offenem Gate leitet, wenn UGS > Ut. En

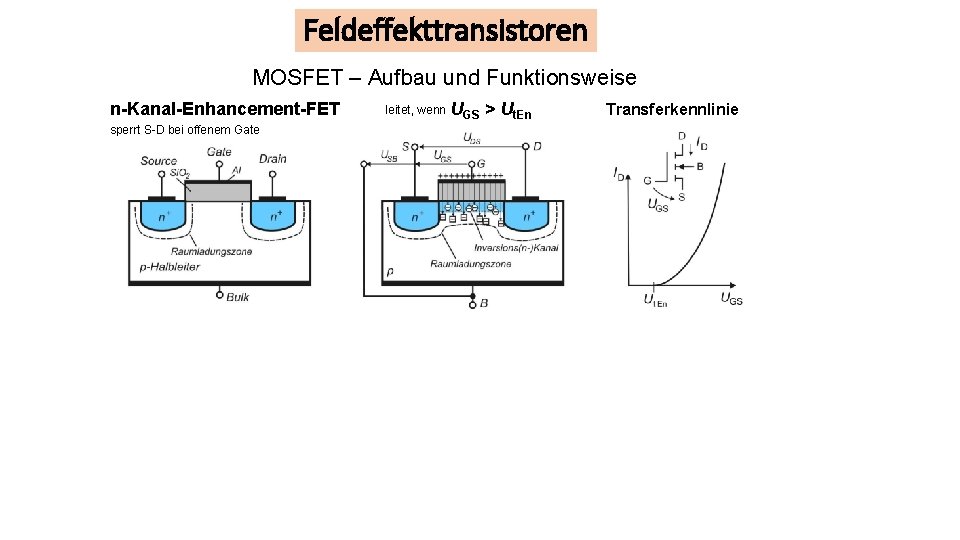

Feldeffekttransistoren MOSFET – Aufbau und Funktionsweise n-Kanal-Enhancement-FET sperrt S-D bei offenem Gate leitet, wenn UGS > Ut. En Transferkennlinie

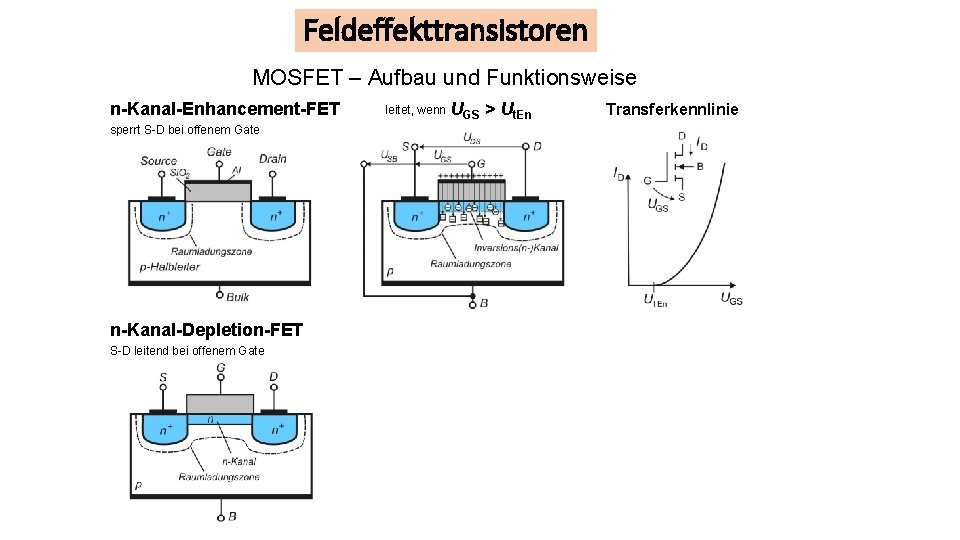

Feldeffekttransistoren MOSFET – Aufbau und Funktionsweise n-Kanal-Enhancement-FET sperrt S-D bei offenem Gate n-Kanal-Depletion-FET S-D leitend bei offenem Gate leitet, wenn UGS > Ut. En Transferkennlinie

Feldeffekttransistoren MOSFET – Aufbau und Funktionsweise n-Kanal-Enhancement-FET leitet, wenn UGS > Ut. En sperrt S-D bei offenem Gate n-Kanal-Depletion-FET S-D leitend bei offenem Gate sperrt, wenn UGS < Ut. Dn Transferkennlinie

Feldeffekttransistoren MOSFET – Aufbau und Funktionsweise n-Kanal-Enhancement-FET leitet, wenn UGS > Ut. En Transferkennlinie sperrt S-D bei offenem Gate n-Kanal-Depletion-FET S-D leitend bei offenem Gate sperrt, wenn UGS < Ut. Dn Transferkennlinie

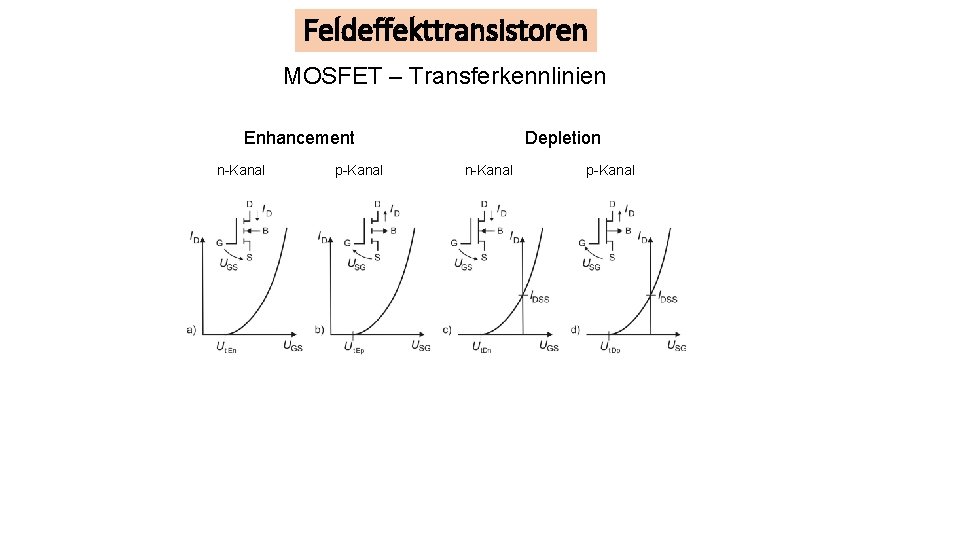

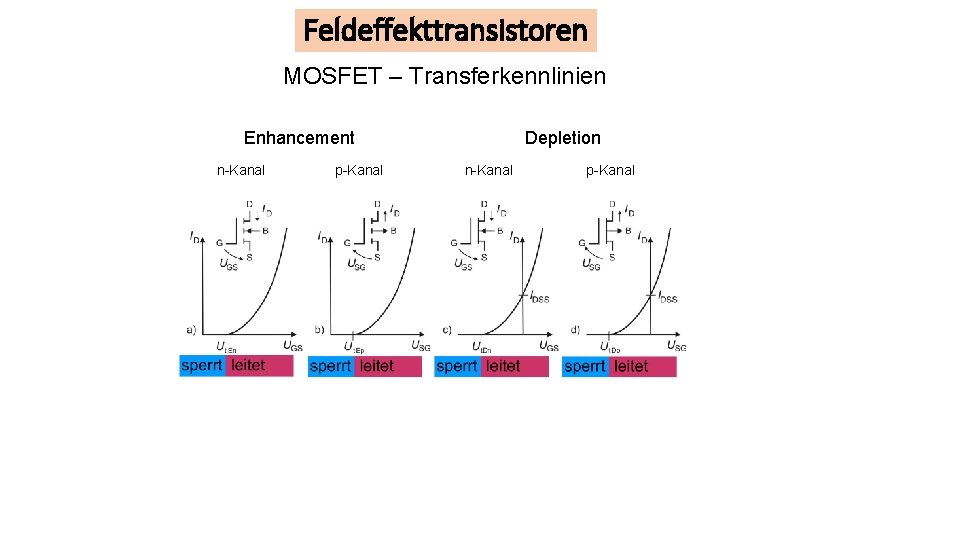

Feldeffekttransistoren MOSFET – Transferkennlinien Enhancement n-Kanal p-Kanal Depletion n-Kanal p-Kanal

Feldeffekttransistoren MOSFET – Transferkennlinien Enhancement n-Kanal p-Kanal Depletion n-Kanal p-Kanal

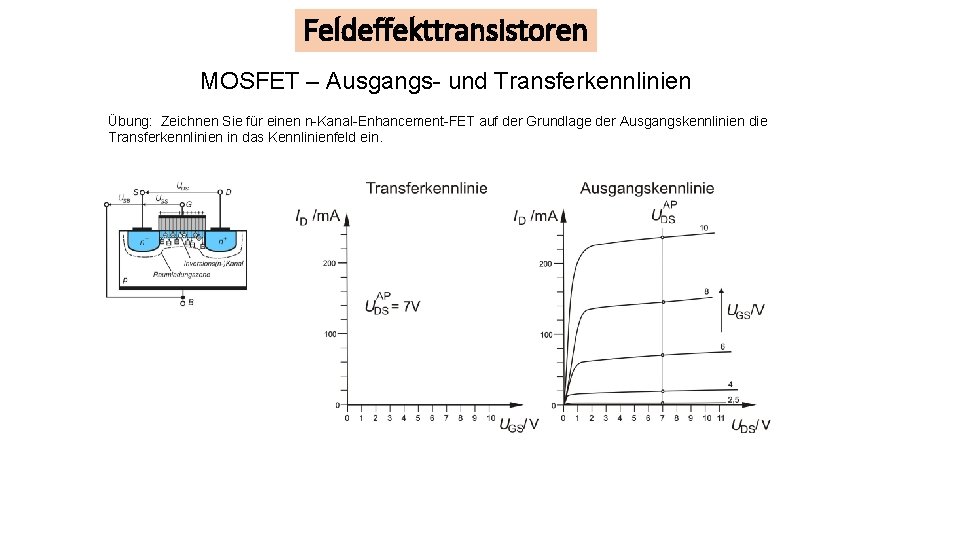

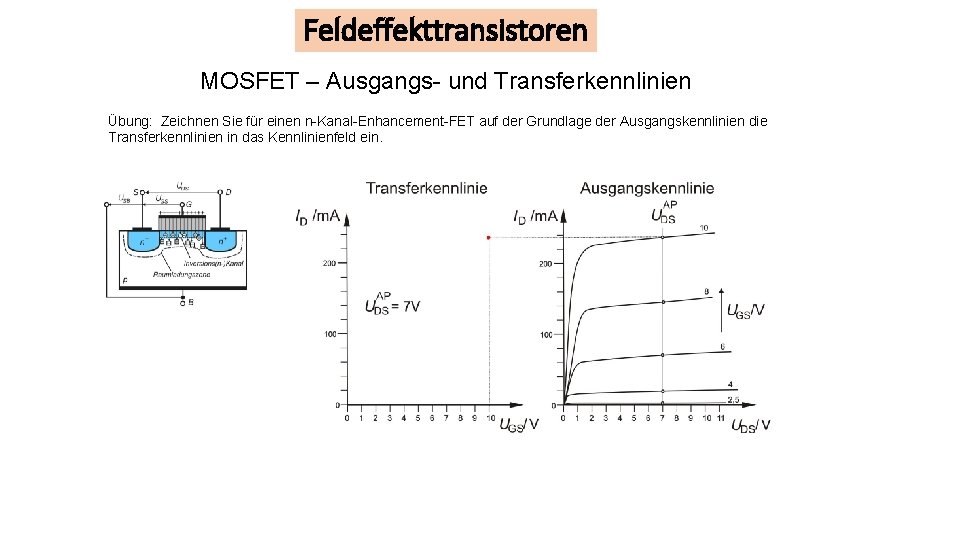

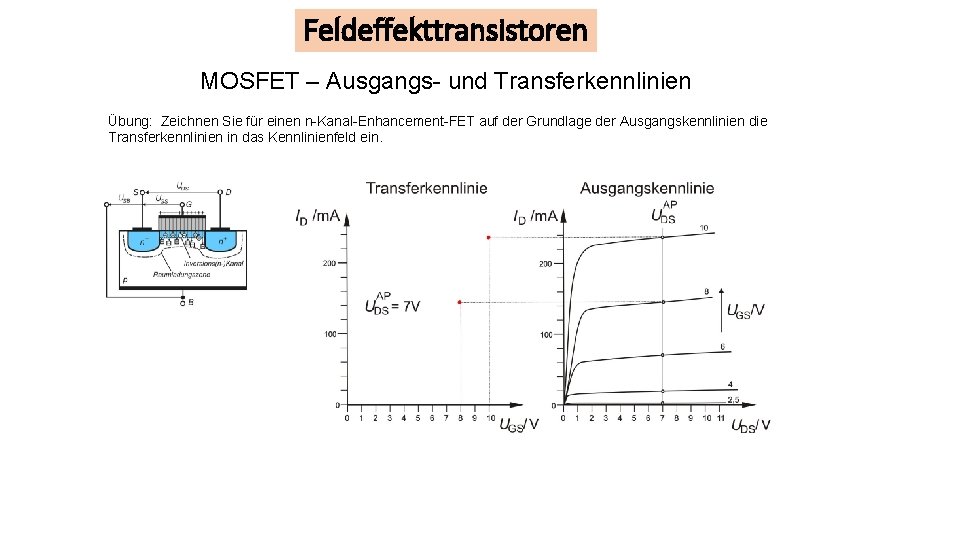

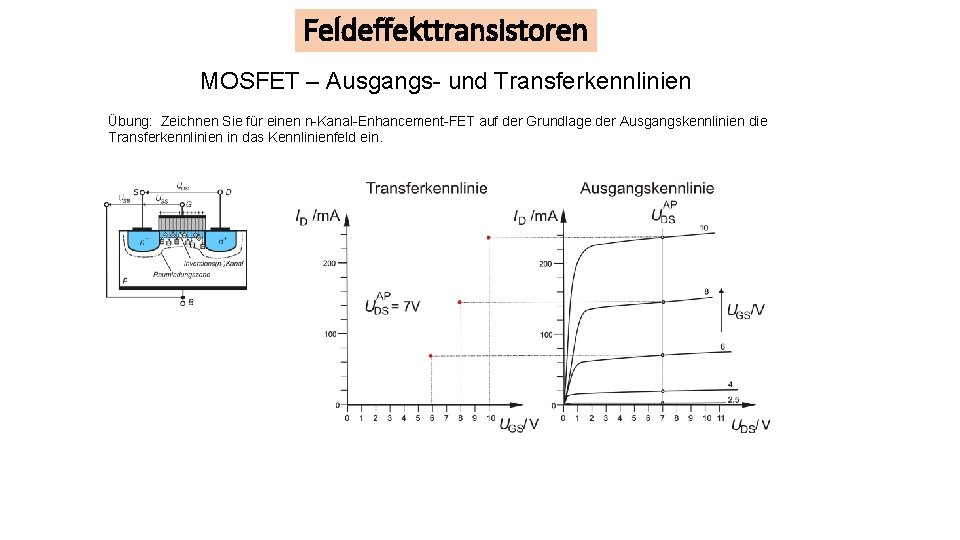

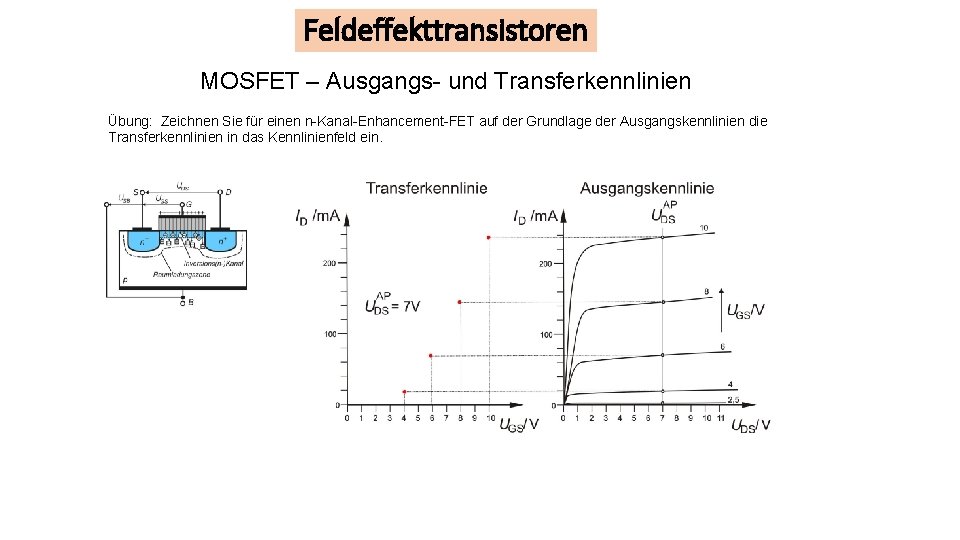

Feldeffekttransistoren MOSFET – Ausgangs- und Transferkennlinien Übung: Zeichnen Sie für einen n-Kanal-Enhancement-FET auf der Grundlage der Ausgangskennlinien die Transferkennlinien in das Kennlinienfeld ein.

Feldeffekttransistoren MOSFET – Ausgangs- und Transferkennlinien Übung: Zeichnen Sie für einen n-Kanal-Enhancement-FET auf der Grundlage der Ausgangskennlinien die Transferkennlinien in das Kennlinienfeld ein.

Feldeffekttransistoren MOSFET – Ausgangs- und Transferkennlinien Übung: Zeichnen Sie für einen n-Kanal-Enhancement-FET auf der Grundlage der Ausgangskennlinien die Transferkennlinien in das Kennlinienfeld ein.

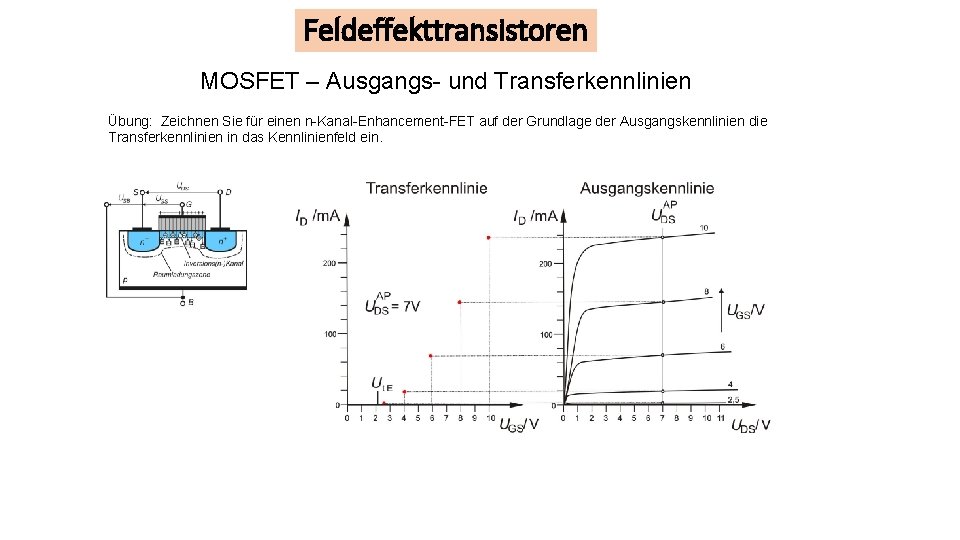

Feldeffekttransistoren MOSFET – Ausgangs- und Transferkennlinien Übung: Zeichnen Sie für einen n-Kanal-Enhancement-FET auf der Grundlage der Ausgangskennlinien die Transferkennlinien in das Kennlinienfeld ein.

Feldeffekttransistoren MOSFET – Ausgangs- und Transferkennlinien Übung: Zeichnen Sie für einen n-Kanal-Enhancement-FET auf der Grundlage der Ausgangskennlinien die Transferkennlinien in das Kennlinienfeld ein.

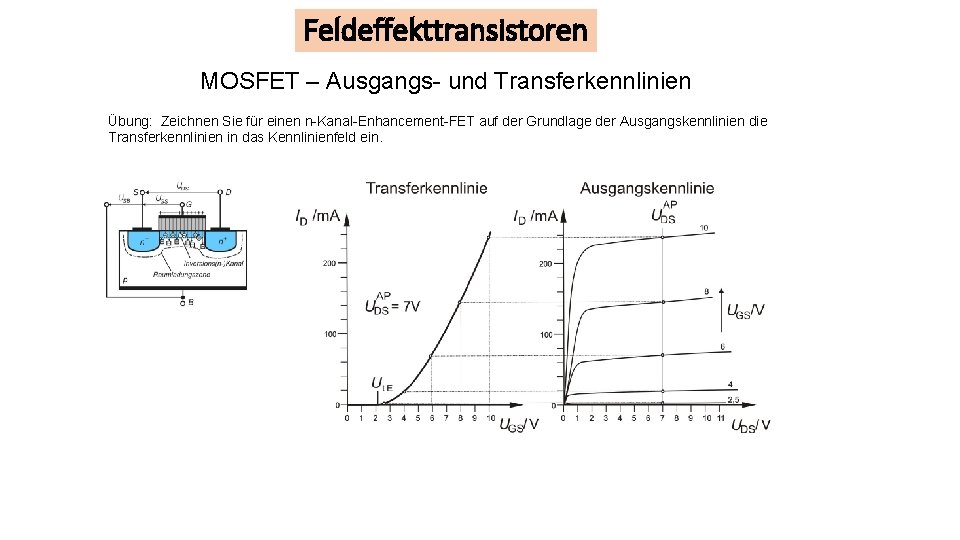

Feldeffekttransistoren MOSFET – Ausgangs- und Transferkennlinien Übung: Zeichnen Sie für einen n-Kanal-Enhancement-FET auf der Grundlage der Ausgangskennlinien die Transferkennlinien in das Kennlinienfeld ein.

Feldeffekttransistoren MOSFET – Ausgangs- und Transferkennlinien Übung: Zeichnen Sie für einen n-Kanal-Enhancement-FET auf der Grundlage der Ausgangskennlinien die Transferkennlinien in das Kennlinienfeld ein.

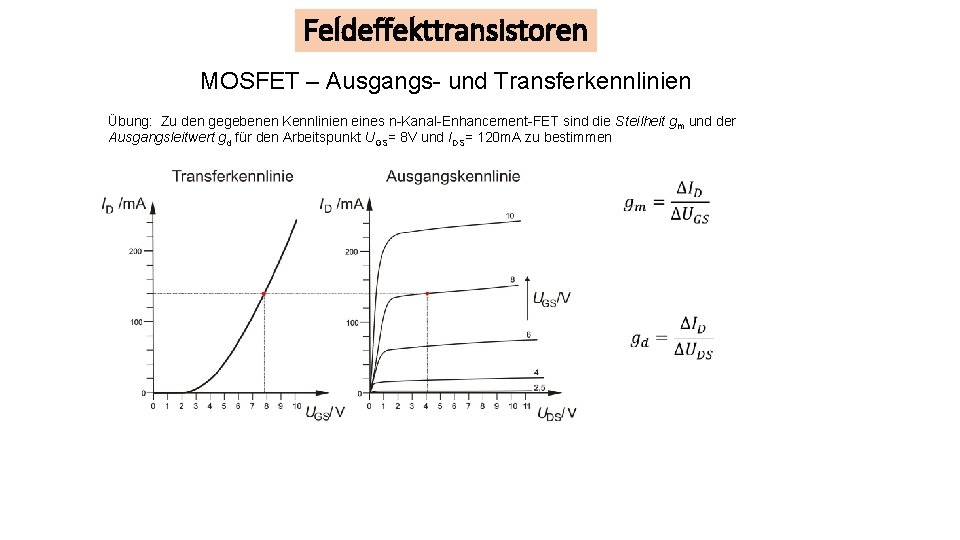

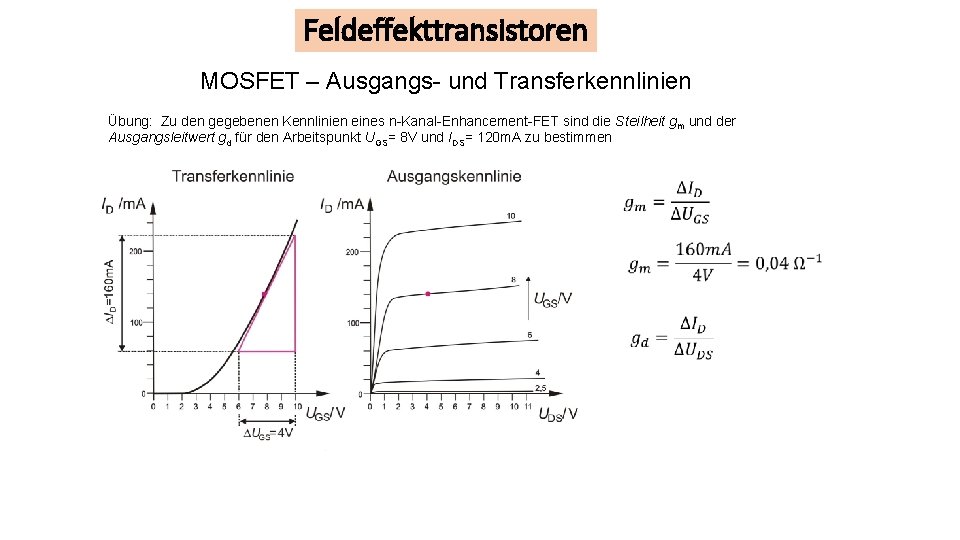

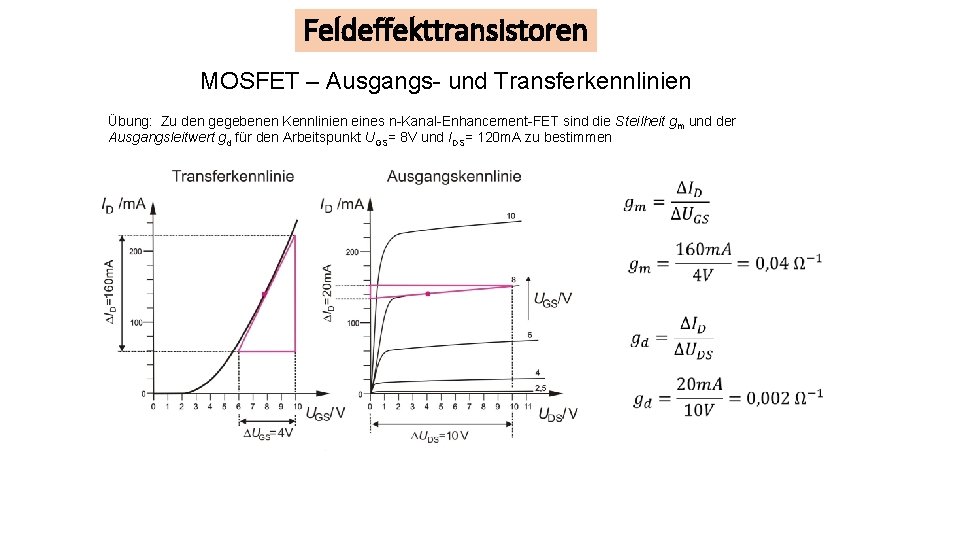

Feldeffekttransistoren MOSFET – Ausgangs- und Transferkennlinien Übung: Zu den gegebenen Kennlinien eines n-Kanal-Enhancement-FET sind die Steilheit gm und der Ausgangsleitwert gd für den Arbeitspunkt UGS= 8 V und IDS= 120 m. A zu bestimmen

Feldeffekttransistoren MOSFET – Ausgangs- und Transferkennlinien Übung: Zu den gegebenen Kennlinien eines n-Kanal-Enhancement-FET sind die Steilheit gm und der Ausgangsleitwert gd für den Arbeitspunkt UGS= 8 V und IDS= 120 m. A zu bestimmen

Feldeffekttransistoren MOSFET – Ausgangs- und Transferkennlinien Übung: Zu den gegebenen Kennlinien eines n-Kanal-Enhancement-FET sind die Steilheit gm und der Ausgangsleitwert gd für den Arbeitspunkt UGS= 8 V und IDS= 120 m. A zu bestimmen

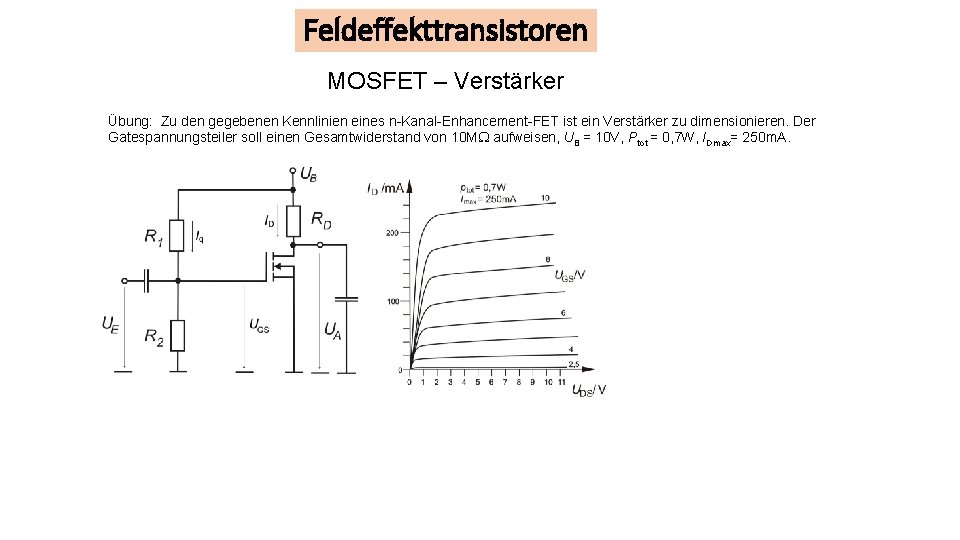

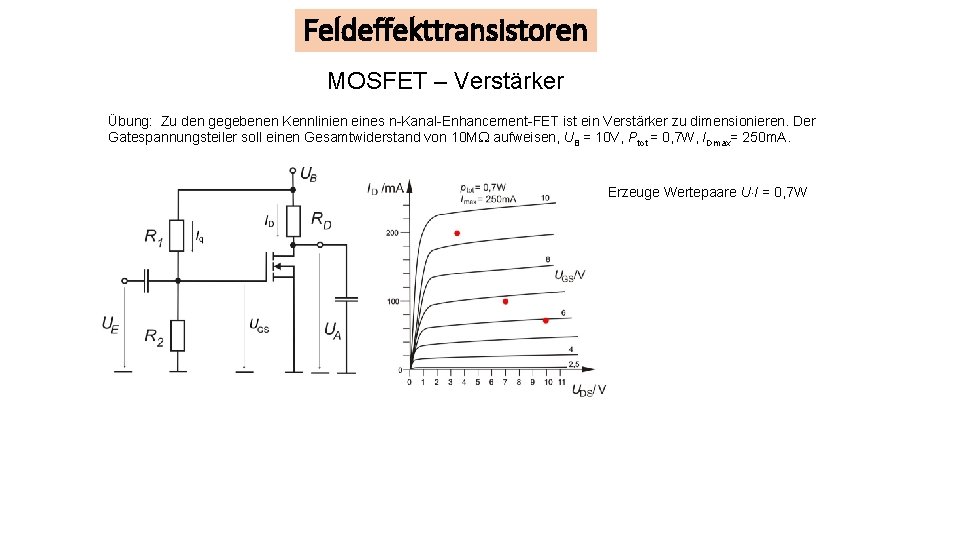

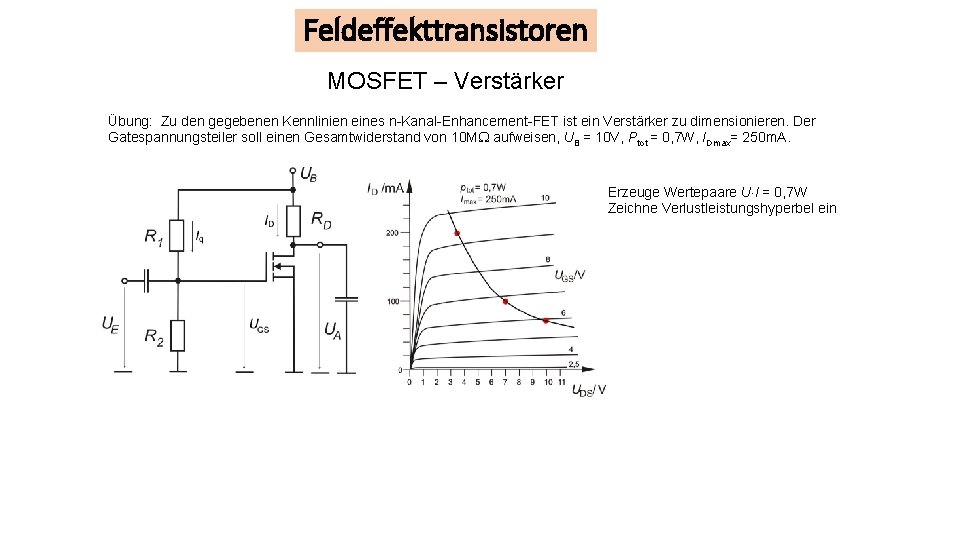

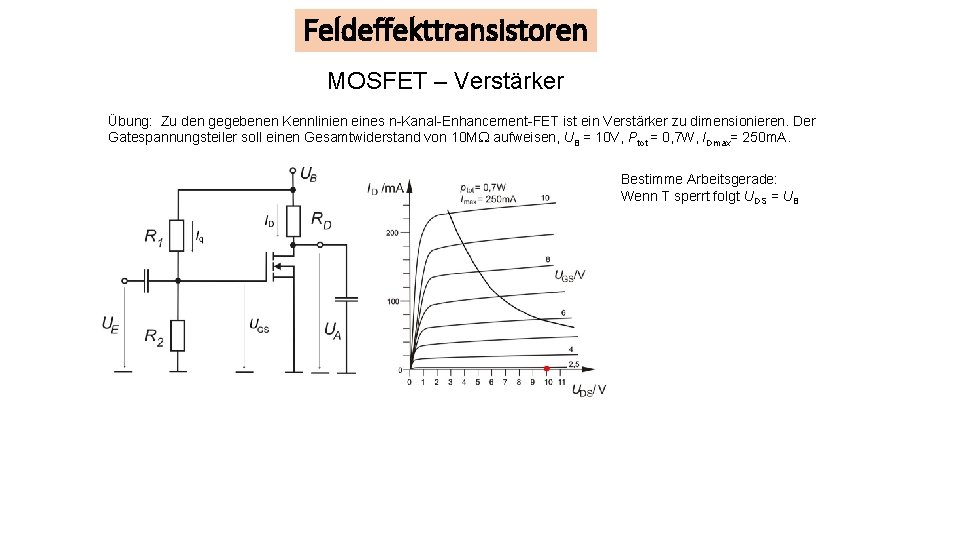

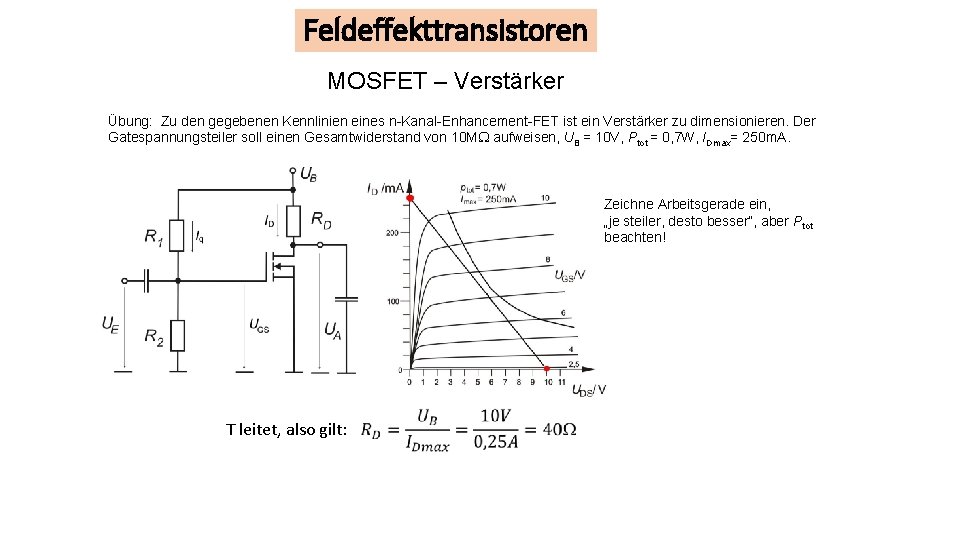

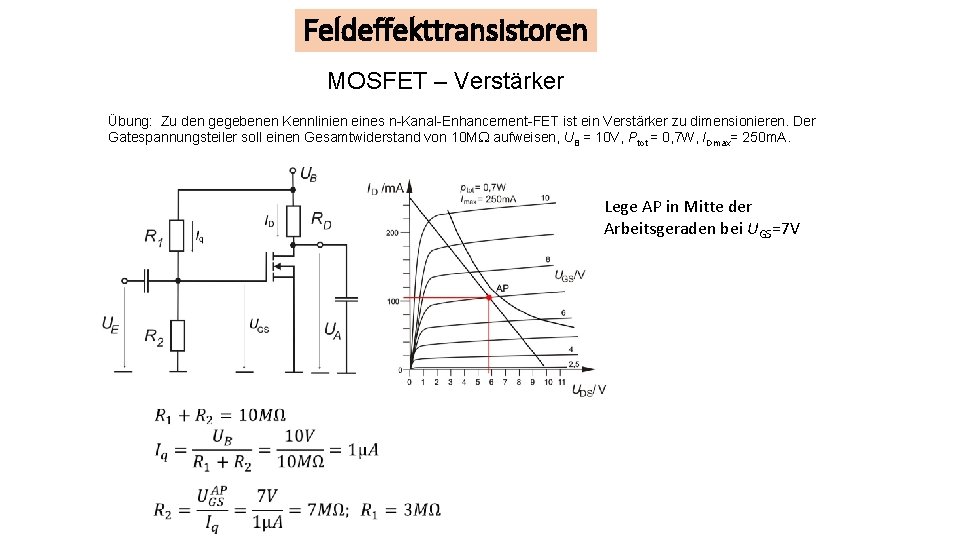

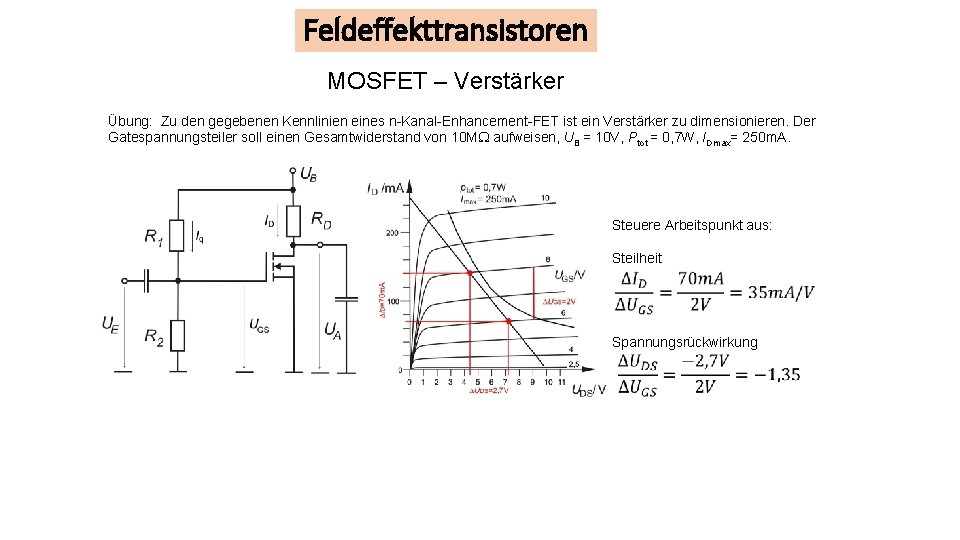

Feldeffekttransistoren MOSFET – Verstärker Übung: Zu den gegebenen Kennlinien eines n-Kanal-Enhancement-FET ist ein Verstärker zu dimensionieren. Der Gatespannungsteiler soll einen Gesamtwiderstand von 10 MW aufweisen, UB = 10 V, Ptot = 0, 7 W, IDmax= 250 m. A.

Feldeffekttransistoren MOSFET – Verstärker Übung: Zu den gegebenen Kennlinien eines n-Kanal-Enhancement-FET ist ein Verstärker zu dimensionieren. Der Gatespannungsteiler soll einen Gesamtwiderstand von 10 MW aufweisen, UB = 10 V, Ptot = 0, 7 W, IDmax= 250 m. A. Erzeuge Wertepaare U I = 0, 7 W

Feldeffekttransistoren MOSFET – Verstärker Übung: Zu den gegebenen Kennlinien eines n-Kanal-Enhancement-FET ist ein Verstärker zu dimensionieren. Der Gatespannungsteiler soll einen Gesamtwiderstand von 10 MW aufweisen, UB = 10 V, Ptot = 0, 7 W, IDmax= 250 m. A. Erzeuge Wertepaare U I = 0, 7 W Zeichne Verlustleistungshyperbel ein

Feldeffekttransistoren MOSFET – Verstärker Übung: Zu den gegebenen Kennlinien eines n-Kanal-Enhancement-FET ist ein Verstärker zu dimensionieren. Der Gatespannungsteiler soll einen Gesamtwiderstand von 10 MW aufweisen, UB = 10 V, Ptot = 0, 7 W, IDmax= 250 m. A. Bestimme Arbeitsgerade: Wenn T sperrt folgt UDS = UB

Feldeffekttransistoren MOSFET – Verstärker Übung: Zu den gegebenen Kennlinien eines n-Kanal-Enhancement-FET ist ein Verstärker zu dimensionieren. Der Gatespannungsteiler soll einen Gesamtwiderstand von 10 MW aufweisen, UB = 10 V, Ptot = 0, 7 W, IDmax= 250 m. A. Zeichne Arbeitsgerade ein, „je steiler, desto besser“, aber Ptot beachten! T leitet, also gilt:

Feldeffekttransistoren MOSFET – Verstärker Übung: Zu den gegebenen Kennlinien eines n-Kanal-Enhancement-FET ist ein Verstärker zu dimensionieren. Der Gatespannungsteiler soll einen Gesamtwiderstand von 10 MW aufweisen, UB = 10 V, Ptot = 0, 7 W, IDmax= 250 m. A. Lege AP in Mitte der Arbeitsgeraden bei UGS=7 V

Feldeffekttransistoren MOSFET – Verstärker Übung: Zu den gegebenen Kennlinien eines n-Kanal-Enhancement-FET ist ein Verstärker zu dimensionieren. Der Gatespannungsteiler soll einen Gesamtwiderstand von 10 MW aufweisen, UB = 10 V, Ptot = 0, 7 W, IDmax= 250 m. A. Steuere Arbeitspunkt aus: Steilheit Spannungsrückwirkung

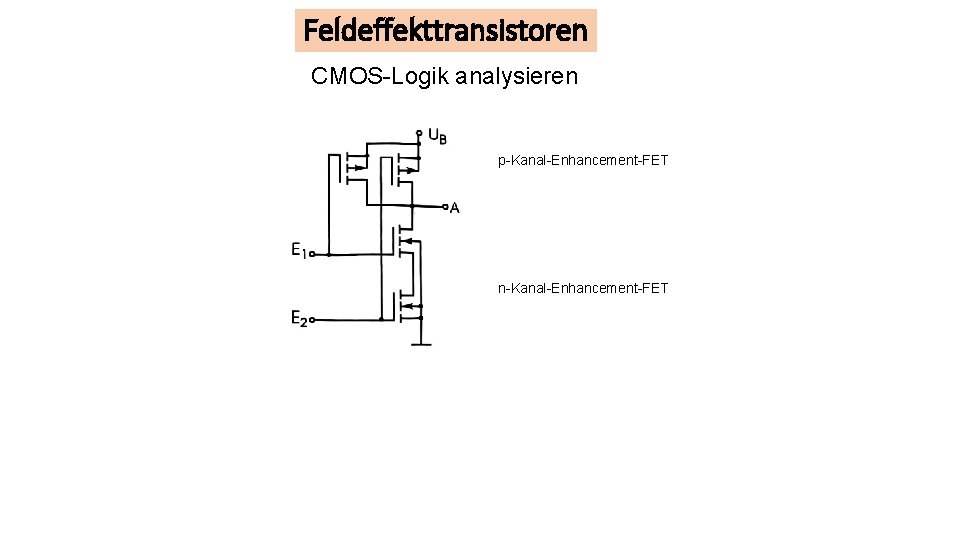

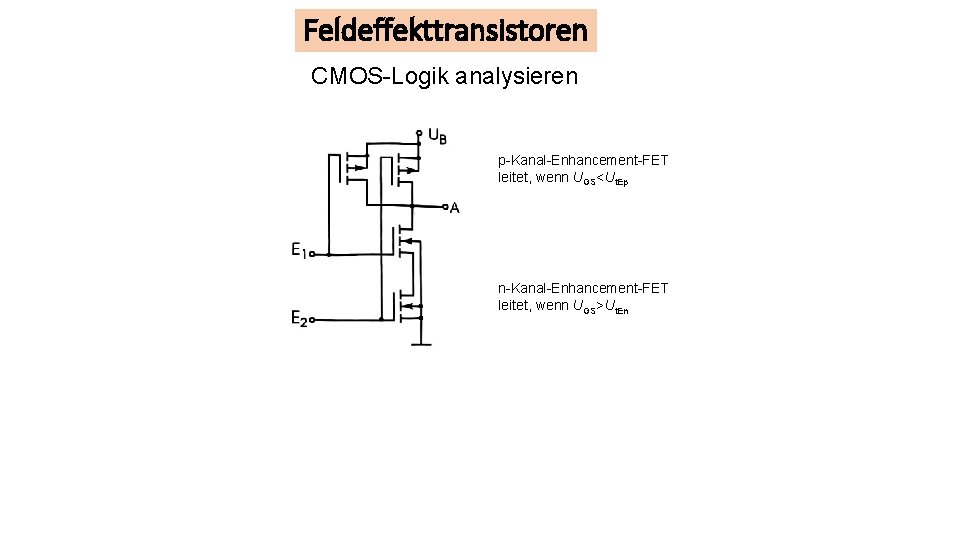

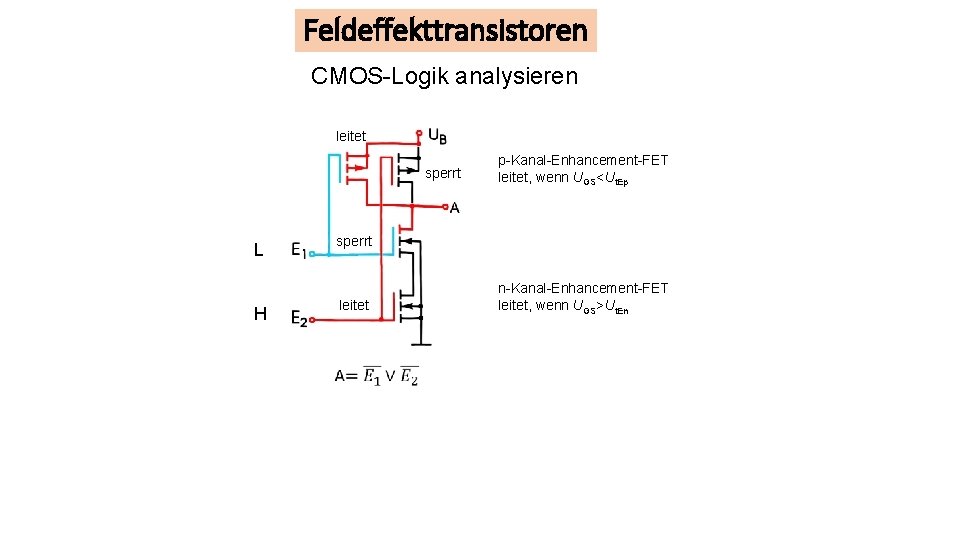

Feldeffekttransistoren CMOS-Logik analysieren p-Kanal-Enhancement-FET n-Kanal-Enhancement-FET

Feldeffekttransistoren CMOS-Logik analysieren p-Kanal-Enhancement-FET leitet, wenn UGS<Ut. Ep n-Kanal-Enhancement-FET leitet, wenn UGS>Ut. En

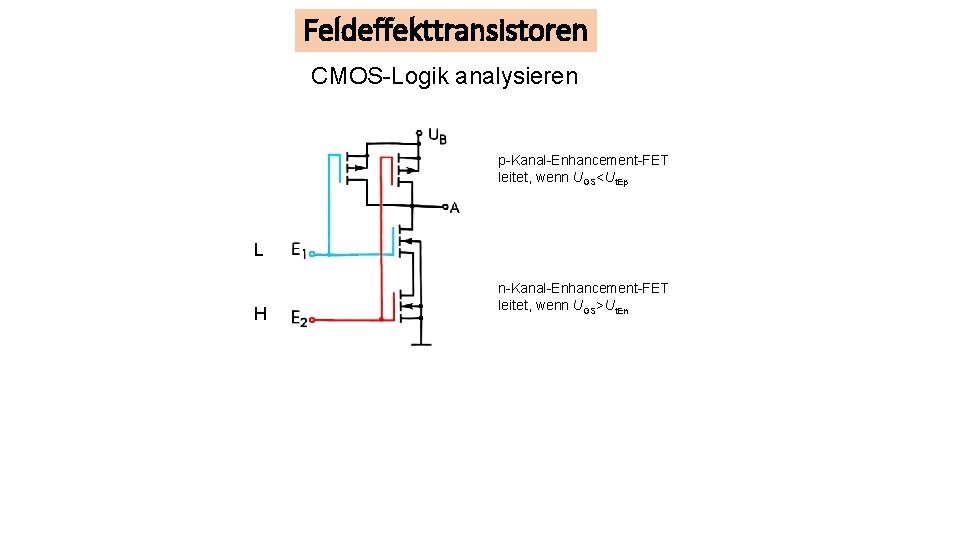

Feldeffekttransistoren CMOS-Logik analysieren p-Kanal-Enhancement-FET leitet, wenn UGS<Ut. Ep L H n-Kanal-Enhancement-FET leitet, wenn UGS>Ut. En

Feldeffekttransistoren CMOS-Logik analysieren leitet sperrt L H p-Kanal-Enhancement-FET leitet, wenn UGS<Ut. Ep sperrt leitet n-Kanal-Enhancement-FET leitet, wenn UGS>Ut. En

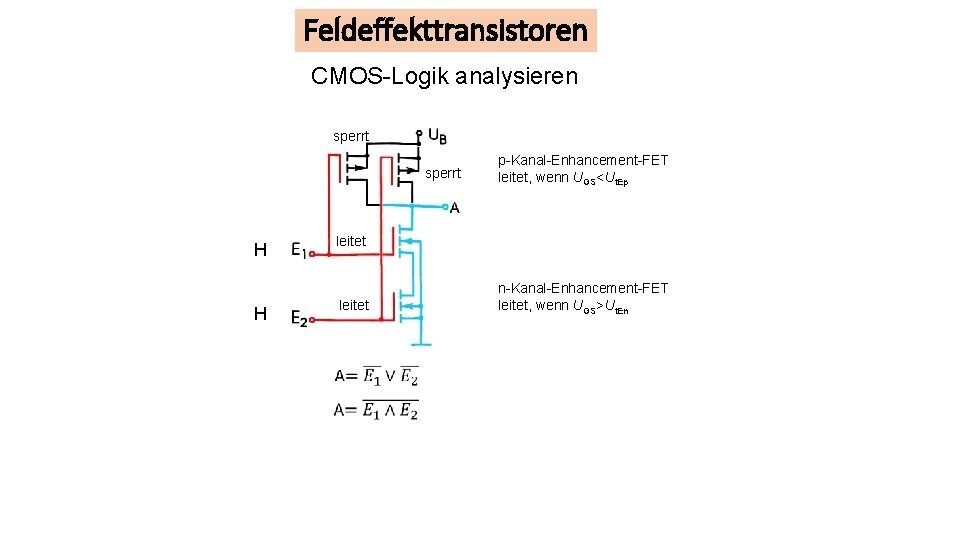

Feldeffekttransistoren CMOS-Logik analysieren sperrt H H p-Kanal-Enhancement-FET leitet, wenn UGS<Ut. Ep leitet n-Kanal-Enhancement-FET leitet, wenn UGS>Ut. En

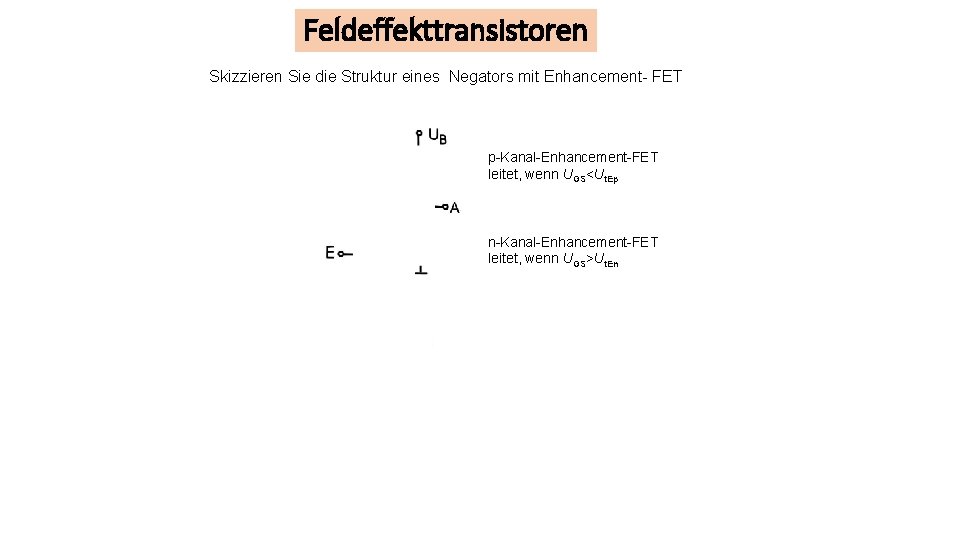

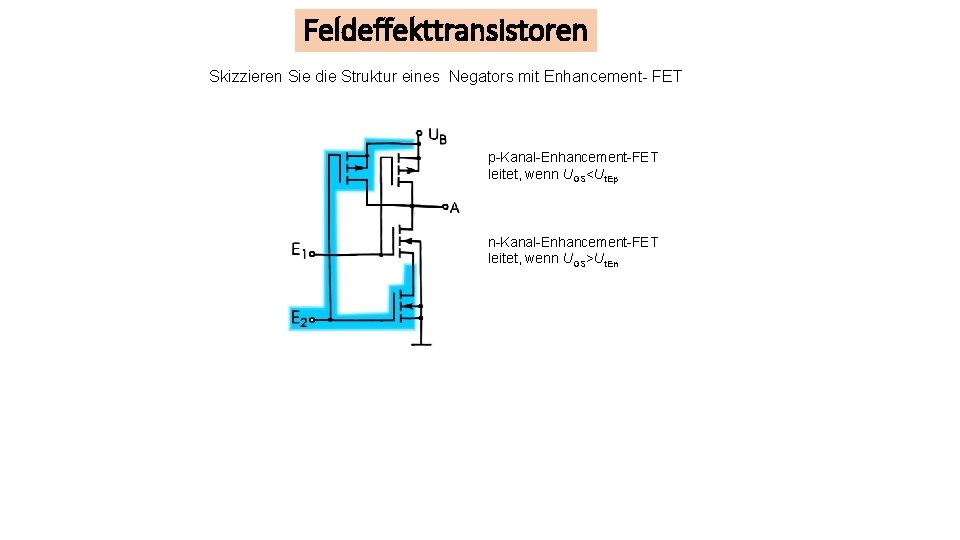

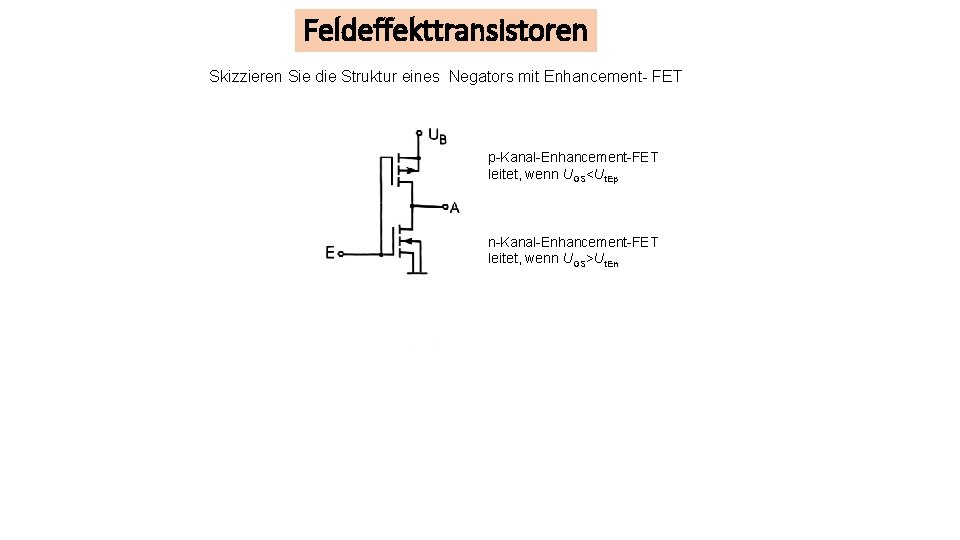

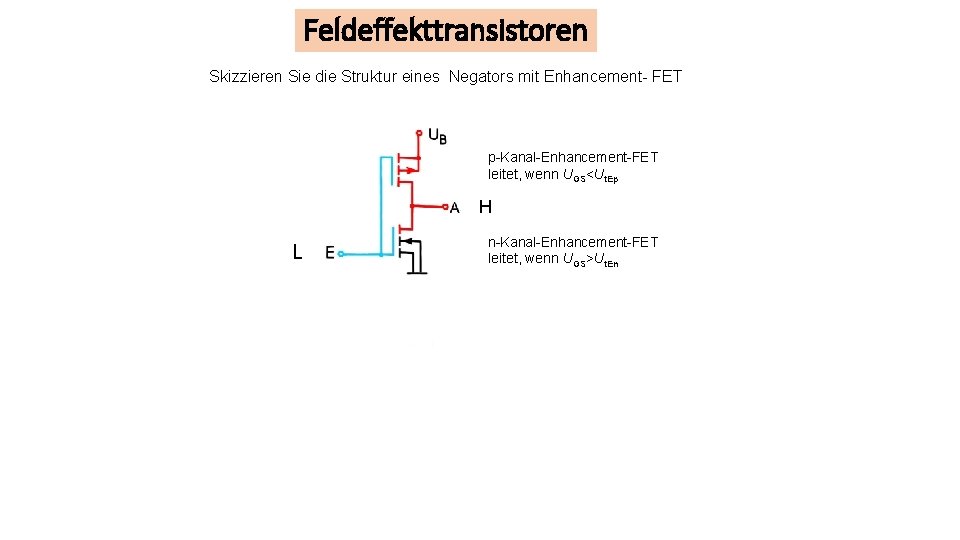

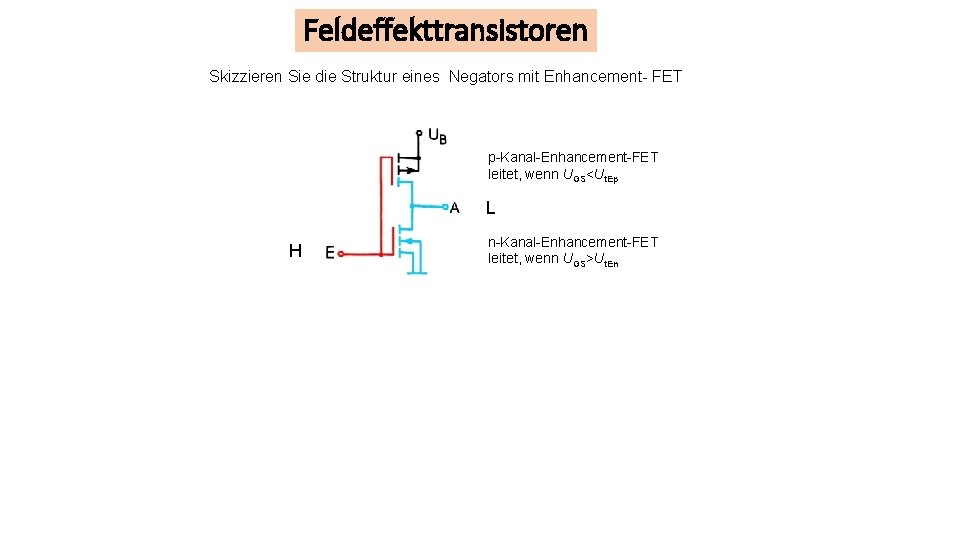

Feldeffekttransistoren Skizzieren Sie die Struktur eines Negators mit Enhancement- FET p-Kanal-Enhancement-FET leitet, wenn UGS<Ut. Ep n-Kanal-Enhancement-FET leitet, wenn UGS>Ut. En

Feldeffekttransistoren Skizzieren Sie die Struktur eines Negators mit Enhancement- FET p-Kanal-Enhancement-FET leitet, wenn UGS<Ut. Ep n-Kanal-Enhancement-FET leitet, wenn UGS>Ut. En

Feldeffekttransistoren Skizzieren Sie die Struktur eines Negators mit Enhancement- FET p-Kanal-Enhancement-FET leitet, wenn UGS<Ut. Ep n-Kanal-Enhancement-FET leitet, wenn UGS>Ut. En

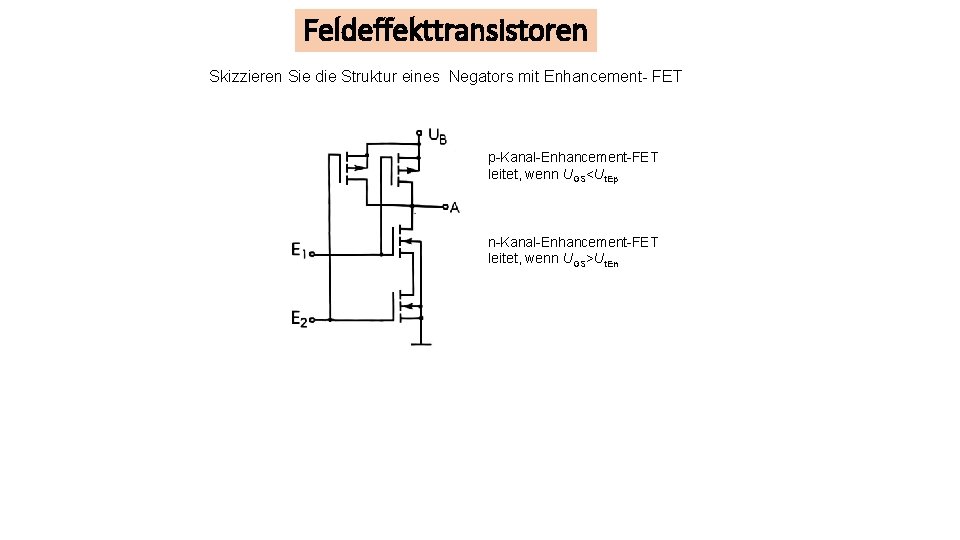

Feldeffekttransistoren Skizzieren Sie die Struktur eines Negators mit Enhancement- FET p-Kanal-Enhancement-FET leitet, wenn UGS<Ut. Ep n-Kanal-Enhancement-FET leitet, wenn UGS>Ut. En

Feldeffekttransistoren Skizzieren Sie die Struktur eines Negators mit Enhancement- FET p-Kanal-Enhancement-FET leitet, wenn UGS<Ut. Ep H L n-Kanal-Enhancement-FET leitet, wenn UGS>Ut. En

Feldeffekttransistoren Skizzieren Sie die Struktur eines Negators mit Enhancement- FET p-Kanal-Enhancement-FET leitet, wenn UGS<Ut. Ep L H n-Kanal-Enhancement-FET leitet, wenn UGS>Ut. En

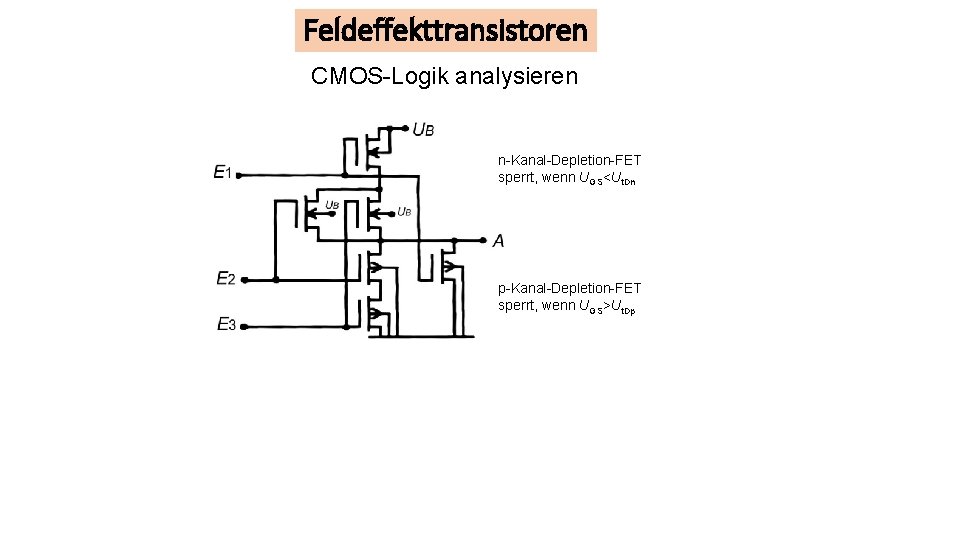

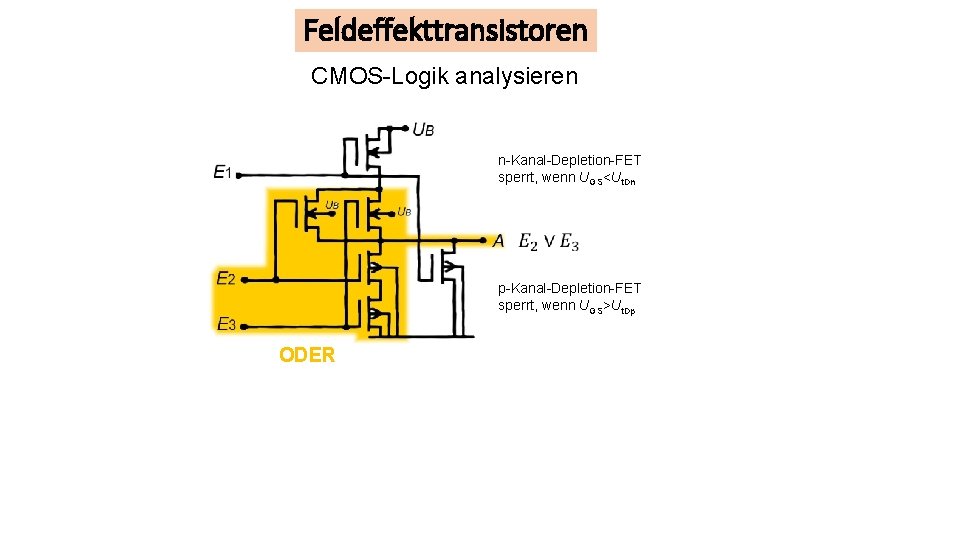

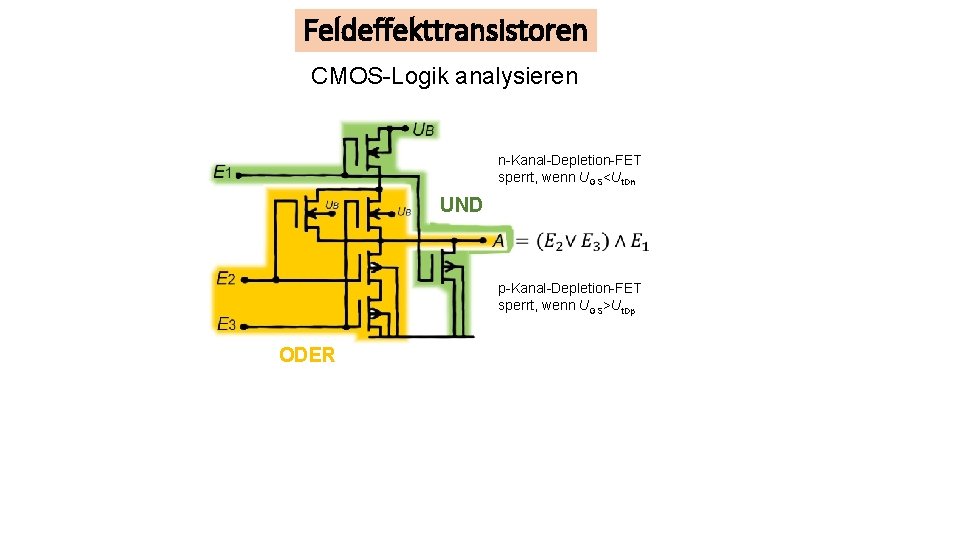

Feldeffekttransistoren CMOS-Logik analysieren n-Kanal-Depletion-FET sperrt, wenn UGS<Ut. Dn p-Kanal-Depletion-FET sperrt, wenn UGS>Ut. Dp

Feldeffekttransistoren CMOS-Logik analysieren n-Kanal-Depletion-FET sperrt, wenn UGS<Ut. Dn p-Kanal-Depletion-FET sperrt, wenn UGS>Ut. Dp ODER

Feldeffekttransistoren CMOS-Logik analysieren n-Kanal-Depletion-FET sperrt, wenn UGS<Ut. Dn UND p-Kanal-Depletion-FET sperrt, wenn UGS>Ut. Dp ODER

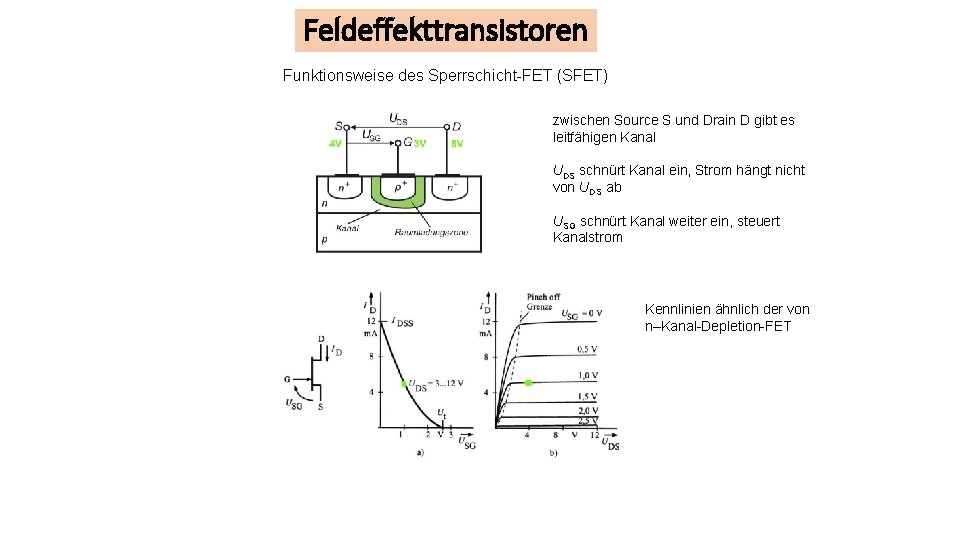

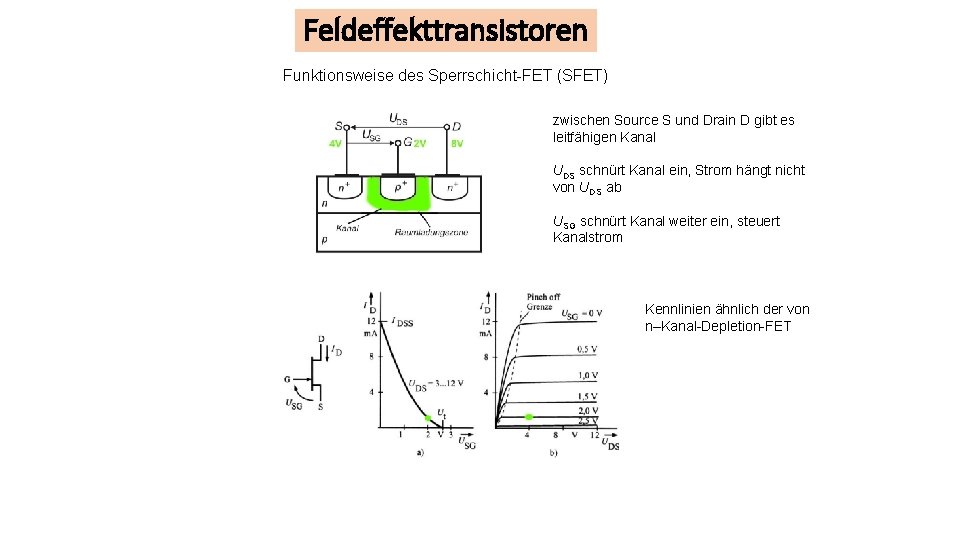

Feldeffekttransistoren Funktionsweise des Sperrschicht-FET (SFET) zwischen Source S und Drain D gibt es leitfähigen Kanal UDS schnürt Kanal ein, Strom hängt nicht von UDS ab USG schnürt Kanal weiter ein, steuert Kanalstrom Kennlinien ähnlich der von n–Kanal-Depletion-FET

Feldeffekttransistoren Funktionsweise des Sperrschicht-FET (SFET) zwischen Source S und Drain D gibt es leitfähigen Kanal UDS schnürt Kanal ein, Strom hängt nicht von UDS ab USG schnürt Kanal weiter ein, steuert Kanalstrom Kennlinien ähnlich der von n–Kanal-Depletion-FET

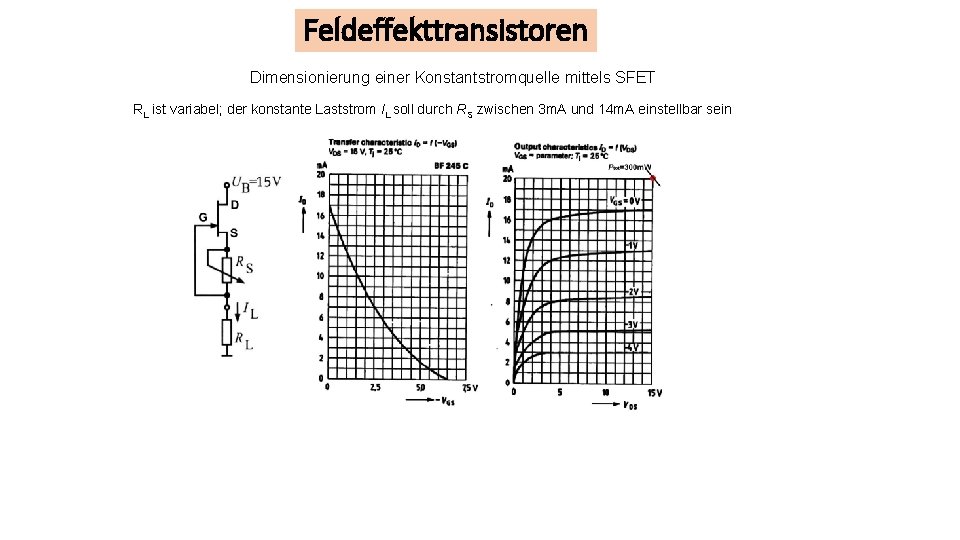

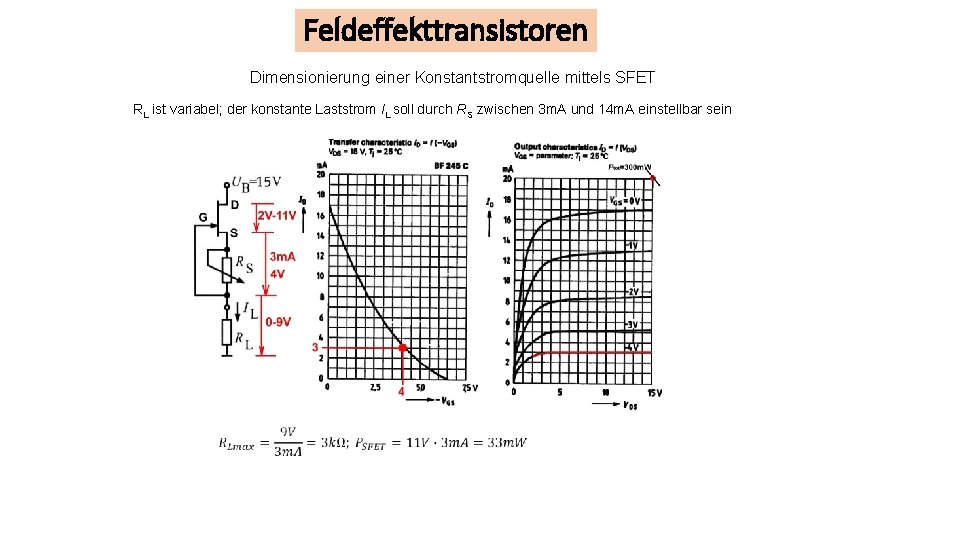

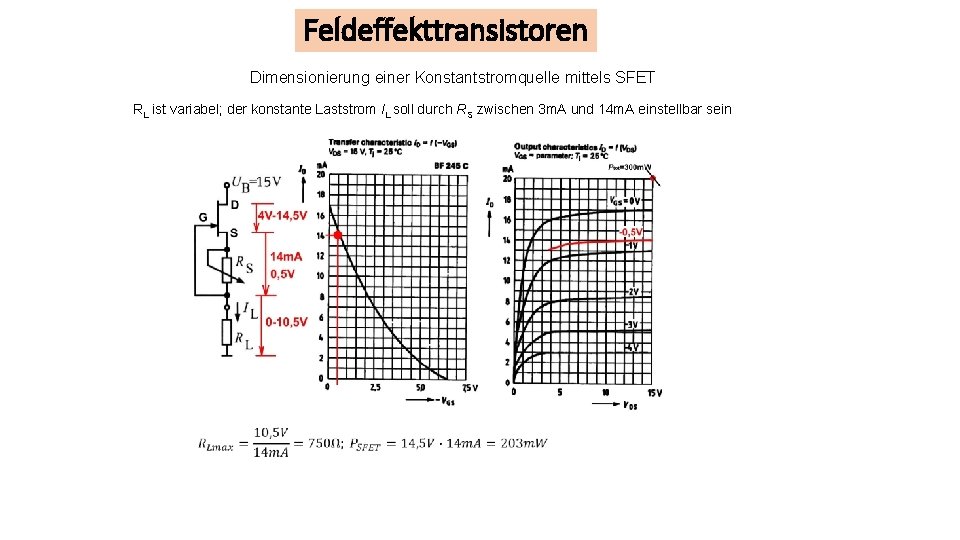

Feldeffekttransistoren Dimensionierung einer Konstantstromquelle mittels SFET RL ist variabel; der konstante Laststrom IL soll durch RS zwischen 3 m. A und 14 m. A einstellbar sein

Feldeffekttransistoren Dimensionierung einer Konstantstromquelle mittels SFET RL ist variabel; der konstante Laststrom IL soll durch RS zwischen 3 m. A und 14 m. A einstellbar sein

Feldeffekttransistoren Dimensionierung einer Konstantstromquelle mittels SFET RL ist variabel; der konstante Laststrom IL soll durch RS zwischen 3 m. A und 14 m. A einstellbar sein

- Slides: 45