Aufbau und Funktionsweise einer CPU 06 12 2020

Aufbau und Funktionsweise einer CPU 06. 12. 2020 Mikroprozessor-Simulation 1

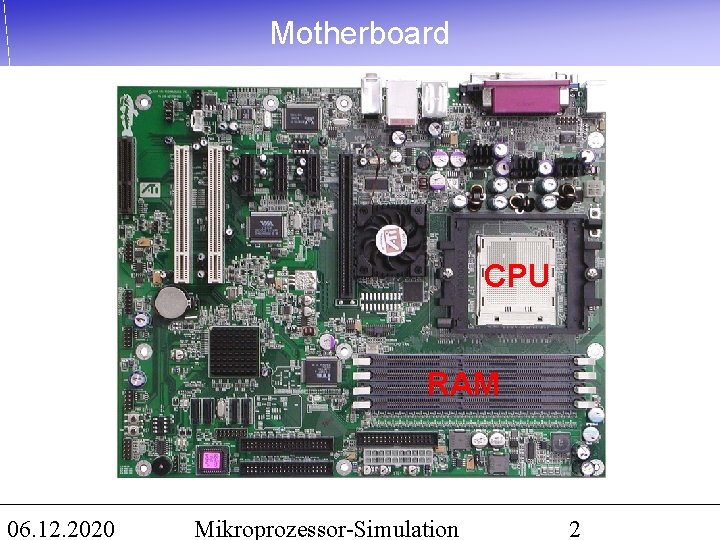

Motherboard CPU RAM 06. 12. 2020 Mikroprozessor-Simulation 2

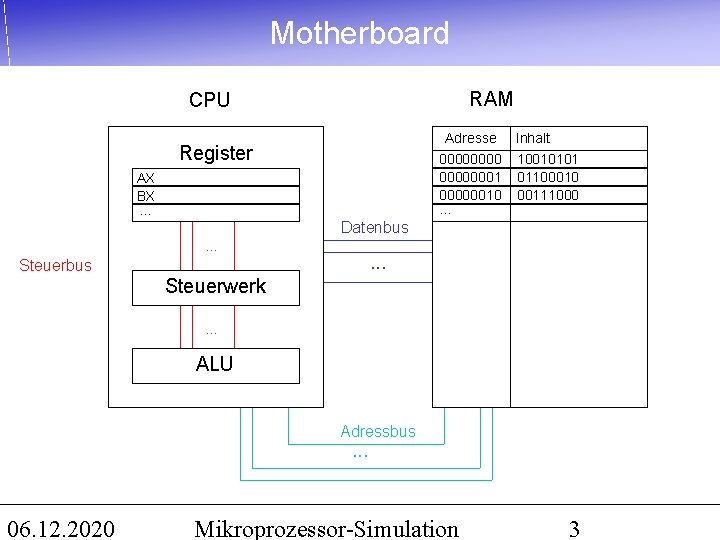

Motherboard RAM CPU Adresse 00000001 00000010. . . Register AX BX. . . Inhalt 10010101 01100010 00111000 Datenbus. . . Steuerbus Steuerwerk. . . ALU Adressbus . . . 06. 12. 2020 Mikroprozessor-Simulation 3

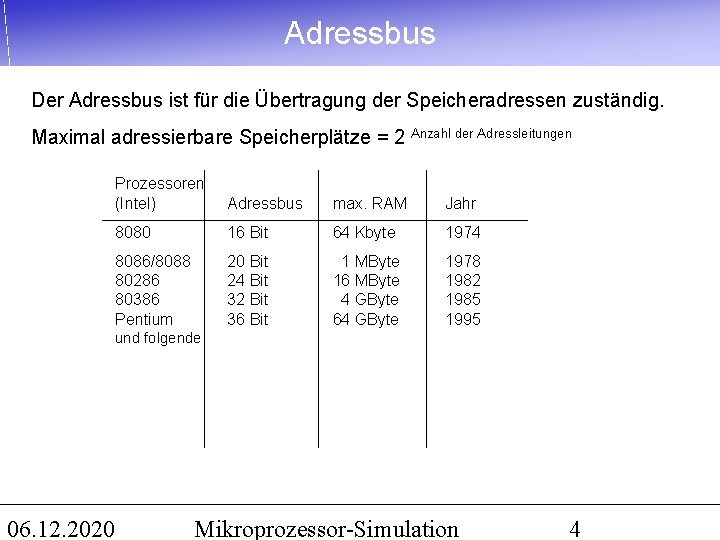

Adressbus Der Adressbus ist für die Übertragung der Speicheradressen zuständig. Maximal adressierbare Speicherplätze = 2 Anzahl der Adressleitungen Prozessoren (Intel) Adressbus max. RAM Jahr 8080 16 Bit 64 Kbyte 1974 8086/8088 80286 80386 Pentium 20 Bit 24 Bit 32 Bit 36 Bit 1 MByte 16 MByte 4 GByte 64 GByte 1978 1982 1985 1995 und folgende 06. 12. 2020 Mikroprozessor-Simulation 4

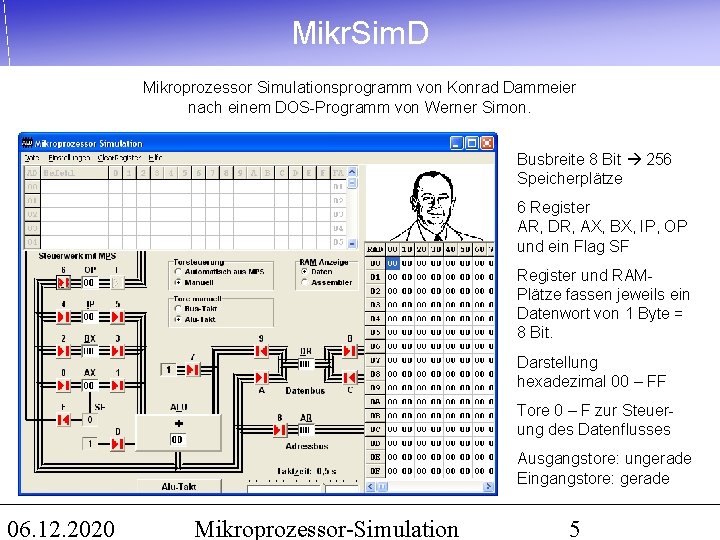

Mikr. Sim. D Mikroprozessor Simulationsprogramm von Konrad Dammeier nach einem DOS-Programm von Werner Simon. Busbreite 8 Bit 256 Speicherplätze 6 Register AR, DR, AX, BX, IP, OP und ein Flag SF Register und RAMPlätze fassen jeweils ein Datenwort von 1 Byte = 8 Bit. Darstellung hexadezimal 00 – FF Tore 0 – F zur Steuerung des Datenflusses Ausgangstore: ungerade Eingangstore: gerade 06. 12. 2020 Mikroprozessor-Simulation 5

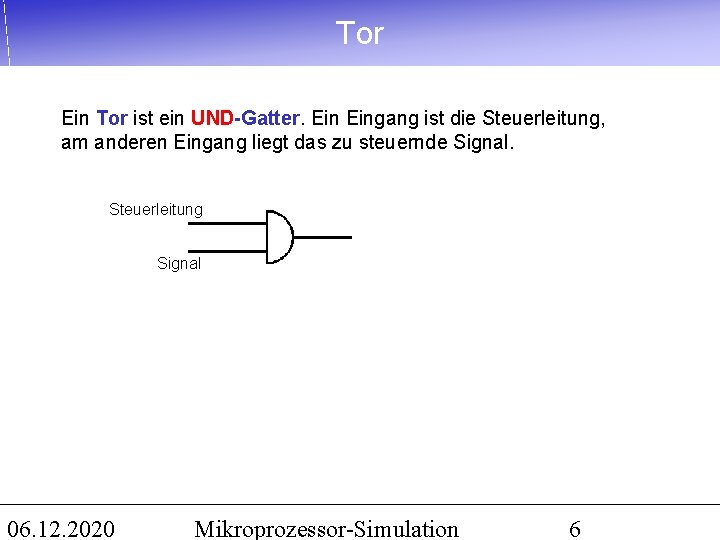

Tor Ein Tor ist ein UND-Gatter. Eingang ist die Steuerleitung, am anderen Eingang liegt das zu steuernde Signal. Steuerleitung Signal 06. 12. 2020 Mikroprozessor-Simulation 6

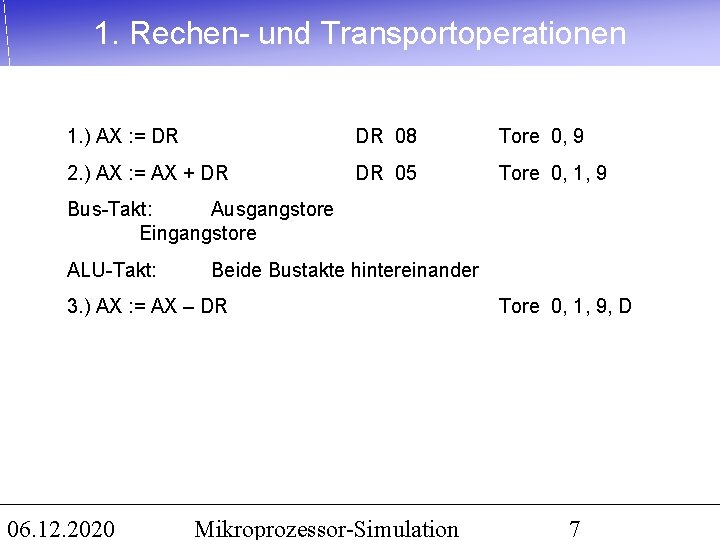

1. Rechen- und Transportoperationen 1. ) AX : = DR DR 08 Tore 0, 9 2. ) AX : = AX + DR DR 05 Tore 0, 1, 9 Bus-Takt: Ausgangstore Eingangstore ALU-Takt: Beide Bustakte hintereinander 3. ) AX : = AX – DR 06. 12. 2020 Mikroprozessor-Simulation Tore 0, 1, 9, D 7

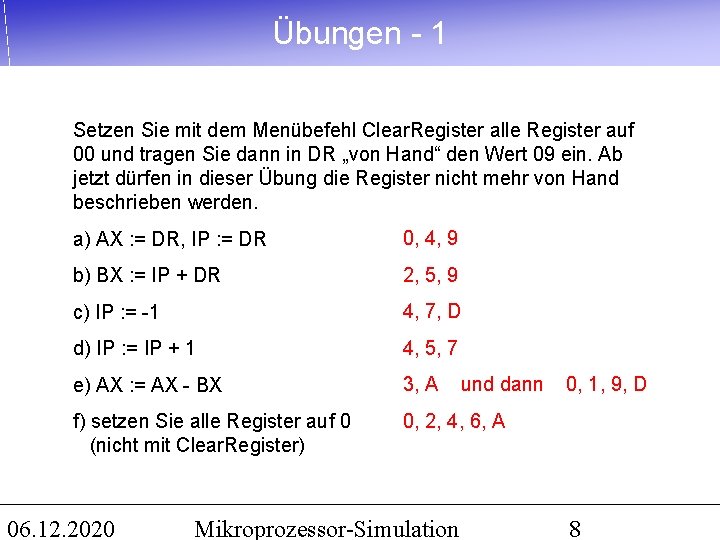

Übungen - 1 Setzen Sie mit dem Menübefehl Clear. Register alle Register auf 00 und tragen Sie dann in DR „von Hand“ den Wert 09 ein. Ab jetzt dürfen in dieser Übung die Register nicht mehr von Hand beschrieben werden. a) AX : = DR, IP : = DR 0, 4, 9 b) BX : = IP + DR 2, 5, 9 c) IP : = -1 4, 7, D d) IP : = IP + 1 4, 5, 7 e) AX : = AX - BX 3, A f) setzen Sie alle Register auf 0 (nicht mit Clear. Register) 0, 2, 4, 6, A 06. 12. 2020 Mikroprozessor-Simulation und dann 0, 1, 9, D 8

2. Verwendung des MPS: Mikroprogrammspeicher Jeder Mikrobefehl ist 24 Bit groß. Die ersten 16 Bit sind über Steuerleitungen (nicht sichtbar) mit den Toren 0 – F verbunden. Die nächsten 8 Bit (hexadezimal dargestellt) liefern die Adresse des, als nächstes auszuführenden Mikrobefehls. Ist die Folgeadresse FA 00, dann Stopp. AX : = AX – BX 06. 12. 2020 Tore 3, A 0, 1, 9, D FA 00 Mikroprozessor-Simulation 9

3. RAM - Zugriff Der RAM-Speicher ist über den Adressbus und den Datenbus mit der CPU verbunden. Der Datenverkehr erfolgt über AR (Adressregister) und DR (Datenregister). RAD: RAM-Adresse Lesen aus RAM AX : = RAM[13] Kommentar DR : = RAM[13] AX : = DR Schreiben in RAM[BX] : = AX Kommentar AR : = BX DR : = AX RAM[AR] : = DR 06. 12. 2020 Tore C 0, 9 FA 00 Tore 3, 8 1, A B Mikroprozessor-Simulation FA 00 10

Übungen - 2 a) Füllen Sie die ersten 3 RAM-Plätze mit 1, 3, 5 ohne das RAMFenster direkt zu benutzen und ohne direktes Schreiben in ein Register. b) Die Summe der Zahlen aus RAM[00], RAM[01] und RAM[02] soll nach RAM[03]. 06. 12. 2020 Mikroprozessor-Simulation 11

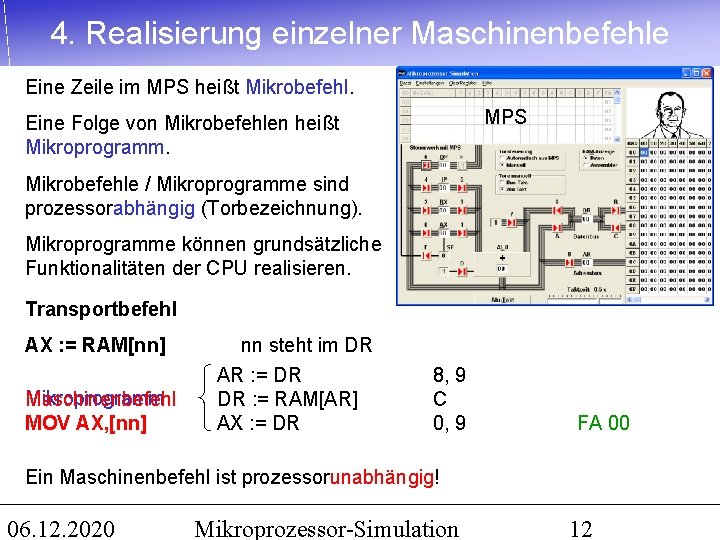

4. Realisierung einzelner Maschinenbefehle Eine Zeile im MPS heißt Mikrobefehl. MPS Eine Folge von Mikrobefehlen heißt Mikroprogramm. Mikrobefehle / Mikroprogramme sind prozessorabhängig (Torbezeichnung). Mikroprogramme können grundsätzliche Funktionalitäten der CPU realisieren. Transportbefehl AX : = RAM[nn] Mikroprogramm Maschinenbefehl MOV AX, [nn] nn steht im DR AR : = DR DR : = RAM[AR] AX : = DR 8, 9 C 0, 9 FA 00 Ein Maschinenbefehl ist prozessorunabhängig! 06. 12. 2020 Mikroprozessor-Simulation 12

![4. Realisierung einzelner Maschinenbefehle Maschinenbefehl MOV AX, [nn] Operator Operand Die Bezeichnung MOV für 4. Realisierung einzelner Maschinenbefehle Maschinenbefehl MOV AX, [nn] Operator Operand Die Bezeichnung MOV für](http://slidetodoc.com/presentation_image_h/f1e70b847423a49473b42bfb9dc14894/image-13.jpg)

4. Realisierung einzelner Maschinenbefehle Maschinenbefehl MOV AX, [nn] Operator Operand Die Bezeichnung MOV für diese Operation nennt man Mnemonik. Gibt man Maschinenbefehle mit Hilfe von Mnemoniks an, so spricht man von der Assemblerschreibweise der Maschinenbefehle. Transportbefehl MOV [nn], AX nn steht im DR AR : = DR DR : = AX RAM[AR] : = DR 8, 9 1, A B FA 00 MOV AX, [nn] im MPS ab Adresse 10, MOV [nn], AX ab 13 eingeben. 06. 12. 2020 Mikroprozessor-Simulation 13

![4. Realisierung einzelner Maschinenbefehle Rechenbefehl ADD AX, [nn] AR : = DR DR : 4. Realisierung einzelner Maschinenbefehle Rechenbefehl ADD AX, [nn] AR : = DR DR :](http://slidetodoc.com/presentation_image_h/f1e70b847423a49473b42bfb9dc14894/image-14.jpg)

4. Realisierung einzelner Maschinenbefehle Rechenbefehl ADD AX, [nn] AR : = DR DR : = RAM[AR] AX : = AX + DR nn steht im DR 8, 9 C 0, 1, 9 FA 00 ADD AX, [nn] im MPS ab Adresse 20 eingeben. 06. 12. 2020 Mikroprozessor-Simulation 14

![5. Halbautomatische Ausführung eines Maschinenprogramm zur Berechnung von RAM[0 C] : = RAM[0 A] 5. Halbautomatische Ausführung eines Maschinenprogramm zur Berechnung von RAM[0 C] : = RAM[0 A]](http://slidetodoc.com/presentation_image_h/f1e70b847423a49473b42bfb9dc14894/image-15.jpg)

5. Halbautomatische Ausführung eines Maschinenprogramm zur Berechnung von RAM[0 C] : = RAM[0 A] + RAM[0 B] Assemblerschreibweise Startadresse im MPS DR MOV AX, [0 A] 10 0 A ADD AX, [0 B] 20 0 B MOV [0 C], AX 13 0 C Ist Tor F geöffnet, dann gilt für die Folgeadresse FA FA : = FA + OP Damit ein Maschinenbefehl halbautomatisch ablaufen kann, muss jeweils die Startadresse des Mikroprogramms in OP und der Operand in DR. Außerdem erste Zeile im MPS: Tor F und FA 00 06. 12. 2020 Mikroprozessor-Simulation 15

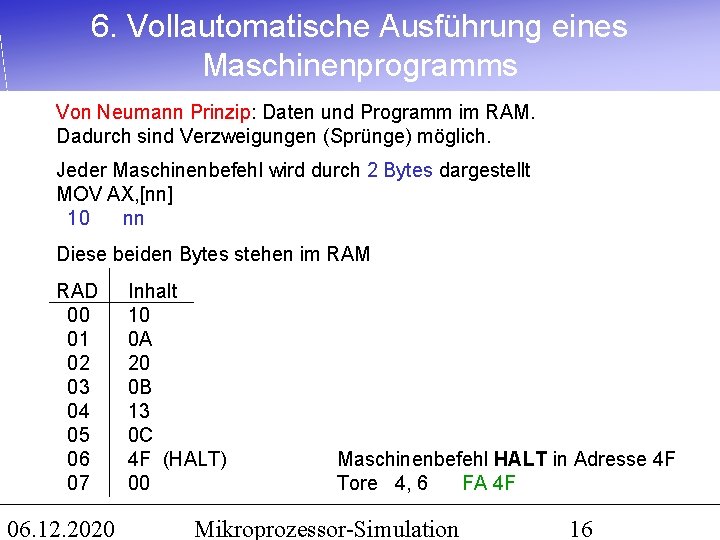

6. Vollautomatische Ausführung eines Maschinenprogramms Von Neumann Prinzip: Daten und Programm im RAM. Dadurch sind Verzweigungen (Sprünge) möglich. Jeder Maschinenbefehl wird durch 2 Bytes dargestellt MOV AX, [nn] 10 nn Diese beiden Bytes stehen im RAM RAD 00 01 02 03 04 05 06 07 06. 12. 2020 Inhalt 10 0 A 20 0 B 13 0 C 4 F (HALT) 00 Maschinenbefehl HALT in Adresse 4 F Tore 4, 6 FA 4 F Mikroprozessor-Simulation 16

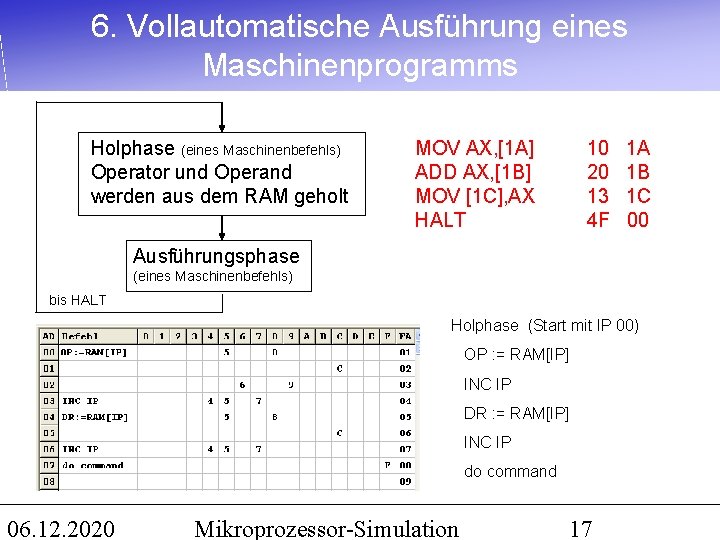

6. Vollautomatische Ausführung eines Maschinenprogramms Holphase (eines Maschinenbefehls) Operator und Operand werden aus dem RAM geholt MOV AX, [1 A] ADD AX, [1 B] MOV [1 C], AX HALT 10 20 13 4 F 1 A 1 B 1 C 00 Ausführungsphase (eines Maschinenbefehls) bis HALT Holphase (Start mit IP 00) OP : = RAM[IP] INC IP DR : = RAM[IP] INC IP do command 06. 12. 2020 Mikroprozessor-Simulation 17

![Übungen - 3 RAM[1 D] : = RAM[1 A] + RAM[1 B] – RAM[1 Übungen - 3 RAM[1 D] : = RAM[1 A] + RAM[1 B] – RAM[1](http://slidetodoc.com/presentation_image_h/f1e70b847423a49473b42bfb9dc14894/image-18.jpg)

Übungen - 3 RAM[1 D] : = RAM[1 A] + RAM[1 B] – RAM[1 C] Dazu Maschinenbefehl SUB AX, [nn] ab Adresse 23 (nn steht in DR) SUB AX, [nn] AR : = DR DR : = RAM[AR] AX : = AX - DR 06. 12. 2020 8, 9 C 0, 1, 9, D Mikroprozessor-Simulation FA 00 18

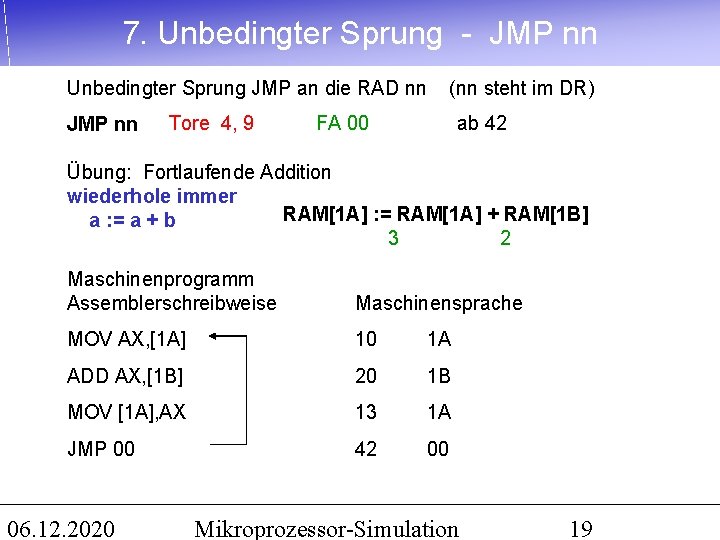

7. Unbedingter Sprung - JMP nn Unbedingter Sprung JMP an die RAD nn JMP nn Tore 4, 9 (nn steht im DR) FA 00 ab 42 Übung: Fortlaufende Addition wiederhole immer RAM[1 A] : = RAM[1 A] + RAM[1 B] a : = a + b 3 2 Maschinenprogramm Assemblerschreibweise Maschinensprache MOV AX, [1 A] 10 1 A ADD AX, [1 B] 20 1 B MOV [1 A], AX 13 1 A JMP 00 42 00 06. 12. 2020 Mikroprozessor-Simulation 19

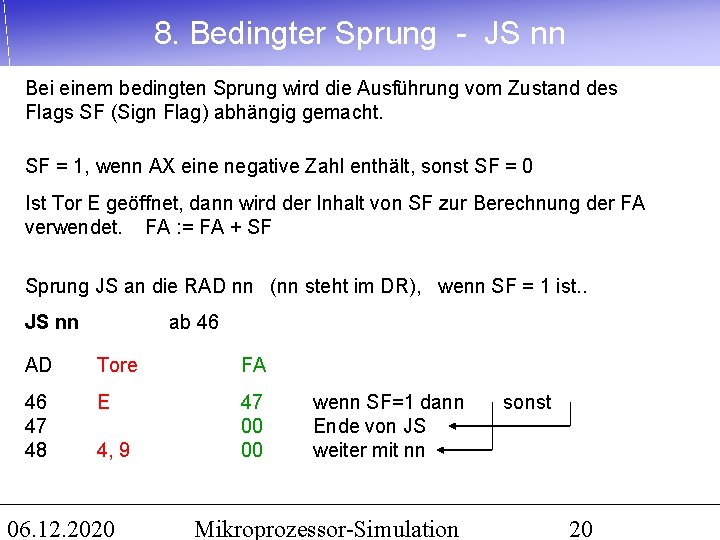

8. Bedingter Sprung - JS nn Bei einem bedingten Sprung wird die Ausführung vom Zustand des Flags SF (Sign Flag) abhängig gemacht. SF = 1, wenn AX eine negative Zahl enthält, sonst SF = 0 Ist Tor E geöffnet, dann wird der Inhalt von SF zur Berechnung der FA verwendet. FA : = FA + SF Sprung JS an die RAD nn (nn steht im DR), wenn SF = 1 ist. . JS nn ab 46 AD Tore FA 46 47 48 E 47 00 00 4, 9 06. 12. 2020 wenn SF=1 dann Ende von JS weiter mit nn Mikroprozessor-Simulation sonst 20

Mi. Si. Int. mpd Die Datei Mi. Si. Int. mpd enthält einen Interpreter für einen sinnvollen Befehlssatz für Mikr. Sim. D. 06. 12. 2020 Mikroprozessor-Simulation 21

![Übungen – 4 c : = a * b RAM[1 C] : = RAM[1 Übungen – 4 c : = a * b RAM[1 C] : = RAM[1](http://slidetodoc.com/presentation_image_h/f1e70b847423a49473b42bfb9dc14894/image-22.jpg)

Übungen – 4 c : = a * b RAM[1 C] : = RAM[1 A] * RAM[1 B] c a b c : = a * b = b +. . . + b Start c : = 0 c : = c + b nein c : = 0 SUB AX, AX MOV [1 C], AX a : = a - 1 MOV AX, [1 A] DEC AX MOV [1 A], AX a : = a - 1 a<0 ja (a >= 0) c : = c + b Ende JS MOV AX, [1 C] ADD AX, [1 B] MOV [1 C], AX JMP HALT 06. 12. 2020 Mikroprozessor-Simulation 22 (ab 2 E) (ab 3 D)

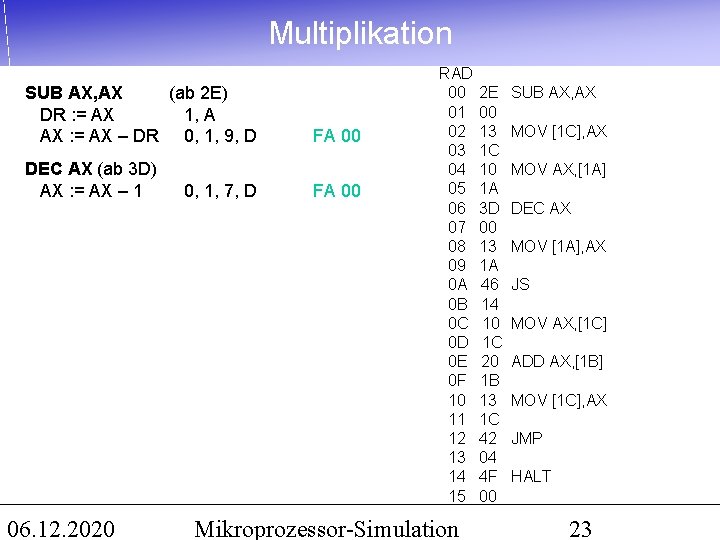

Multiplikation SUB AX, AX (ab 2 E) DR : = AX 1, A AX : = AX – DR 0, 1, 9, D DEC AX (ab 3 D) AX : = AX – 1 06. 12. 2020 0, 1, 7, D FA 00 RAD 00 01 02 03 04 05 06 07 08 09 0 A 0 B 0 C 0 D 0 E 0 F 10 11 12 13 14 15 Mikroprozessor-Simulation 2 E 00 13 1 C 10 1 A 3 D 00 13 1 A 46 14 10 1 C 20 1 B 13 1 C 42 04 4 F 00 SUB AX, AX MOV [1 C], AX MOV AX, [1 A] DEC AX MOV [1 A], AX JS MOV AX, [1 C] ADD AX, [1 B] MOV [1 C], AX JMP HALT 23

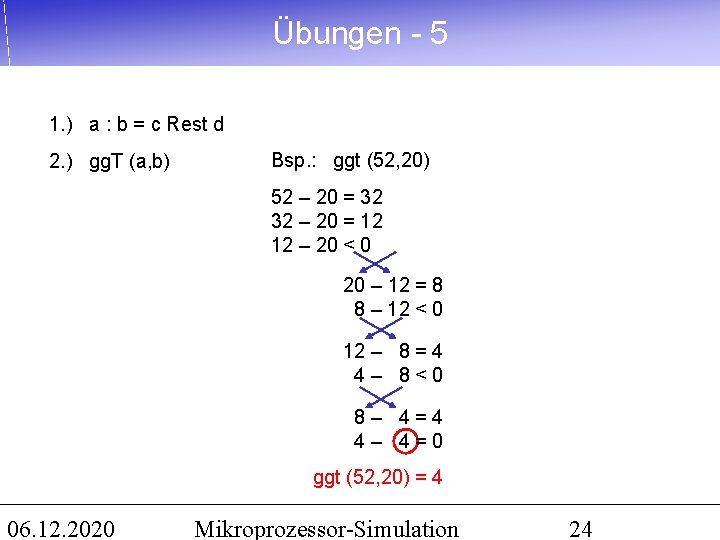

Übungen - 5 1. ) a : b = c Rest d 2. ) gg. T (a, b) Bsp. : ggt (52, 20) 52 – 20 = 32 32 – 20 = 12 12 – 20 < 0 20 – 12 = 8 8 – 12 < 0 12 – 8 = 4 4– 8<0 8– 4=4 4– 4=0 ggt (52, 20) = 4 06. 12. 2020 Mikroprozessor-Simulation 24

- Slides: 24