ELETTRONICA DIGITALE II Parte 10 240111 RIEPILOGO CORSO

- Slides: 75

ELETTRONICA DIGITALE (II Parte) (10) 24/01/11 RIEPILOGO CORSO Elettronica Digitale (II Parte) 10 -11_10 1

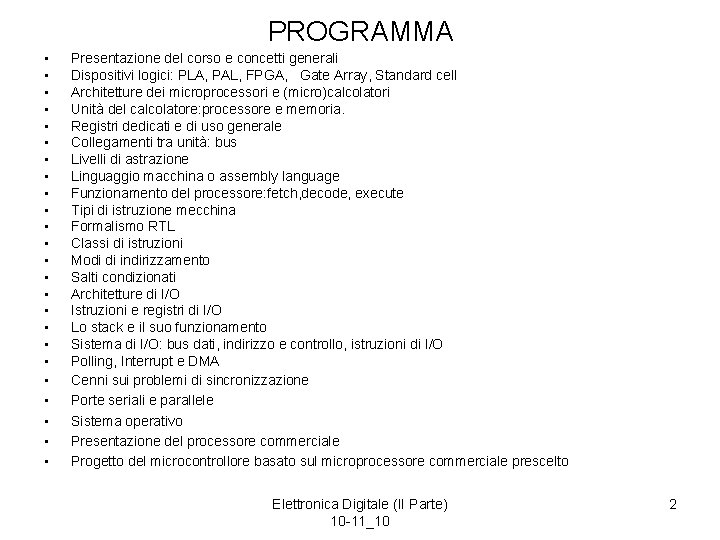

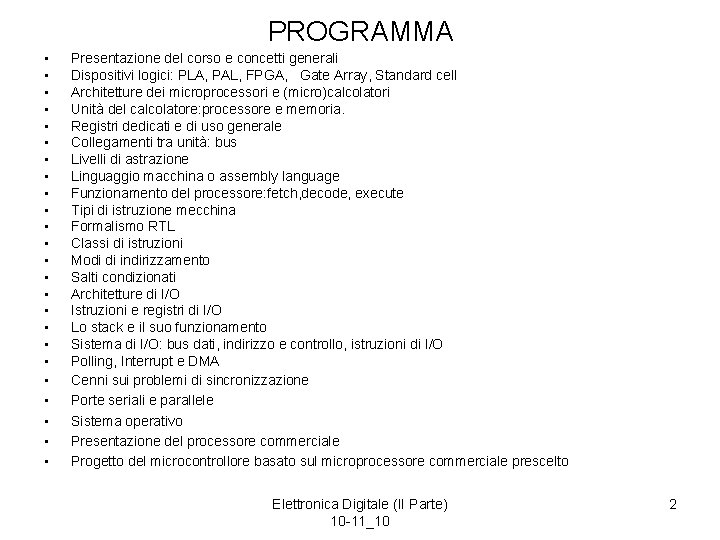

PROGRAMMA • • • • • • Presentazione del corso e concetti generali Dispositivi logici: PLA, PAL, FPGA, Gate Array, Standard cell Architetture dei microprocessori e (micro)calcolatori Unità del calcolatore: processore e memoria. Registri dedicati e di uso generale Collegamenti tra unità: bus Livelli di astrazione Linguaggio macchina o assembly language Funzionamento del processore: fetch, decode, execute Tipi di istruzione mecchina Formalismo RTL Classi di istruzioni Modi di indirizzamento Salti condizionati Architetture di I/O Istruzioni e registri di I/O Lo stack e il suo funzionamento Sistema di I/O: bus dati, indirizzo e controllo, istruzioni di I/O Polling, Interrupt e DMA Cenni sui problemi di sincronizzazione Porte seriali e parallele Sistema operativo Presentazione del processore commerciale Progetto del microcontrollore basato sul microprocessore commerciale prescelto Elettronica Digitale (II Parte) 10 -11_10 2

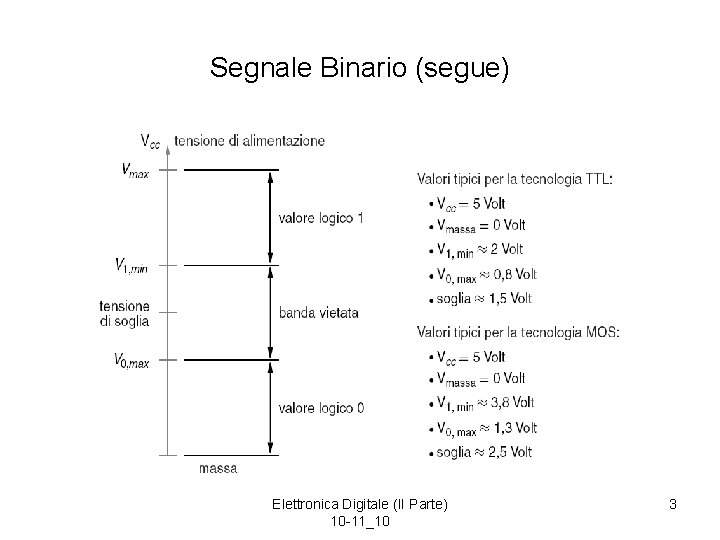

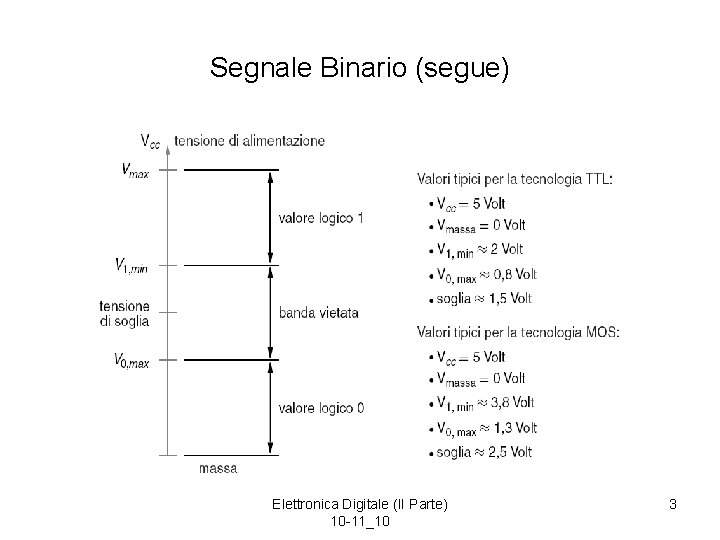

Segnale Binario (segue) Elettronica Digitale (II Parte) 10 -11_10 3

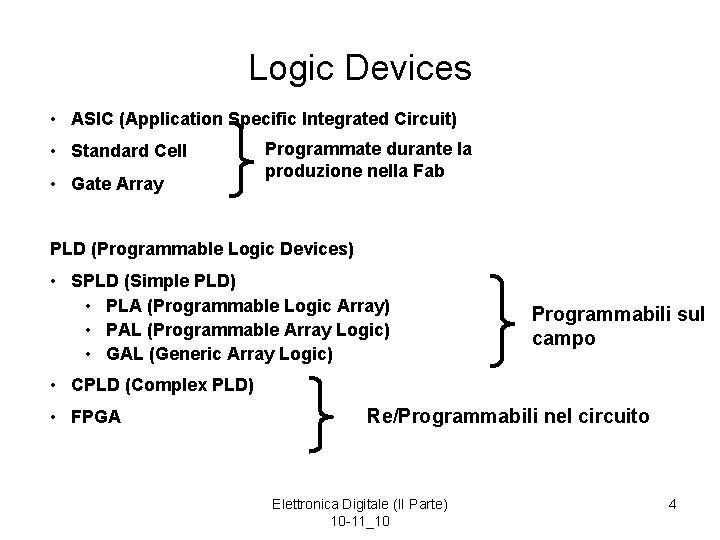

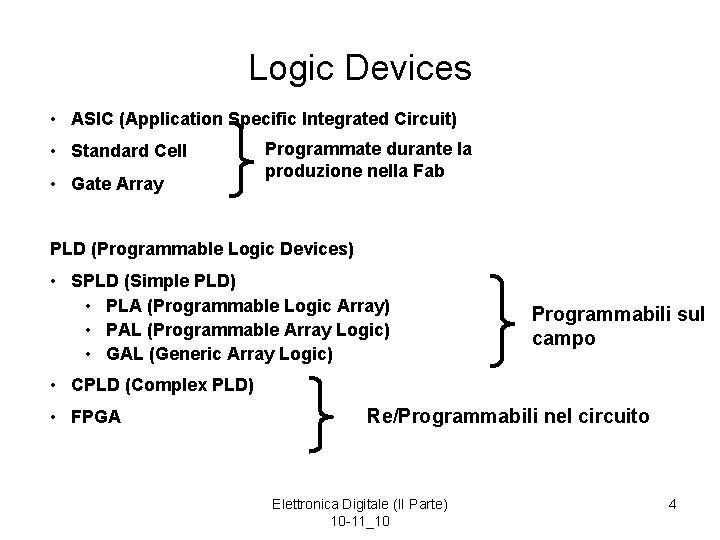

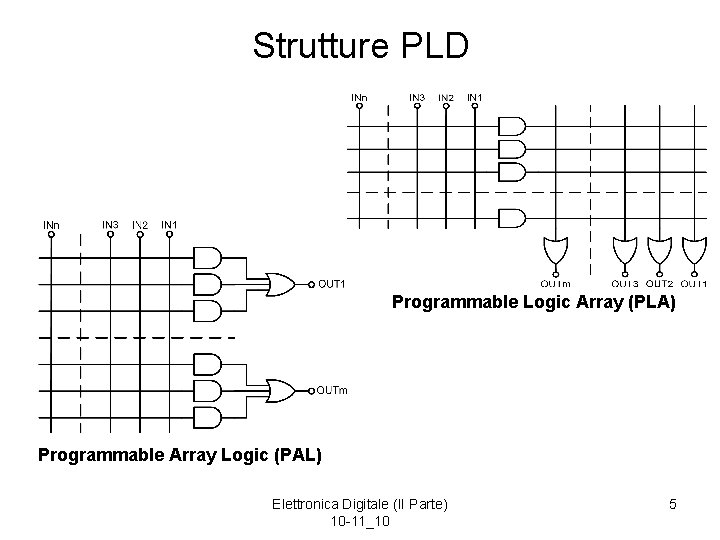

Logic Devices • ASIC (Application Specific Integrated Circuit) • Standard Cell • Gate Array Programmate durante la produzione nella Fab PLD (Programmable Logic Devices) • SPLD (Simple PLD) • PLA (Programmable Logic Array) • PAL (Programmable Array Logic) • GAL (Generic Array Logic) Programmabili sul campo • CPLD (Complex PLD) • FPGA Re/Programmabili nel circuito Elettronica Digitale (II Parte) 10 -11_10 4

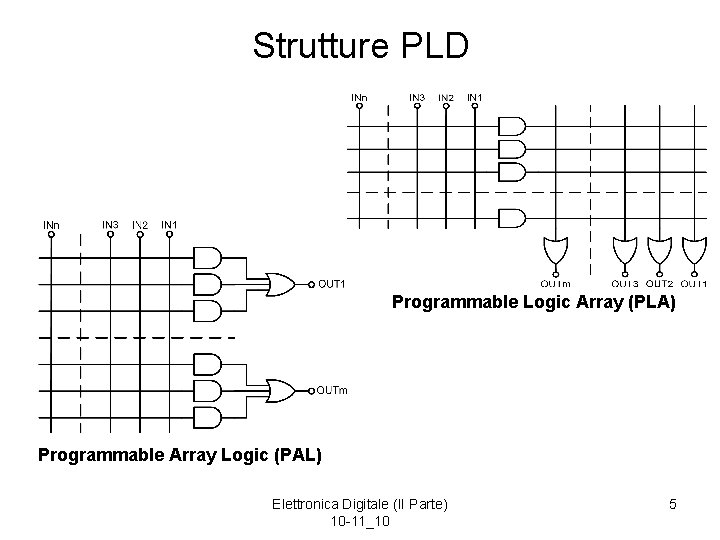

Strutture PLD Programmable Logic Array (PLA) Programmable Array Logic (PAL) Elettronica Digitale (II Parte) 10 -11_10 5

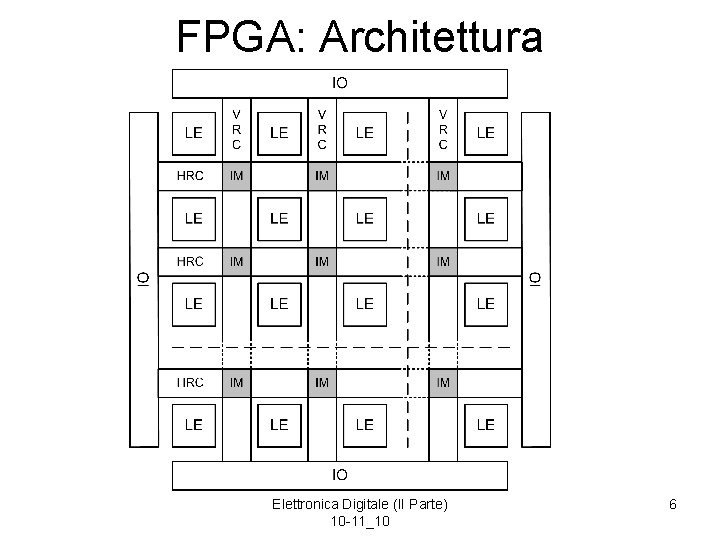

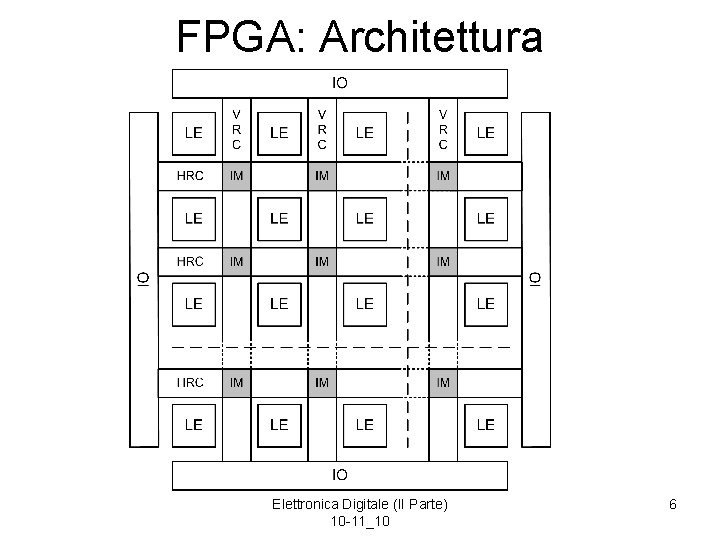

FPGA: Architettura Elettronica Digitale (II Parte) 10 -11_10 6

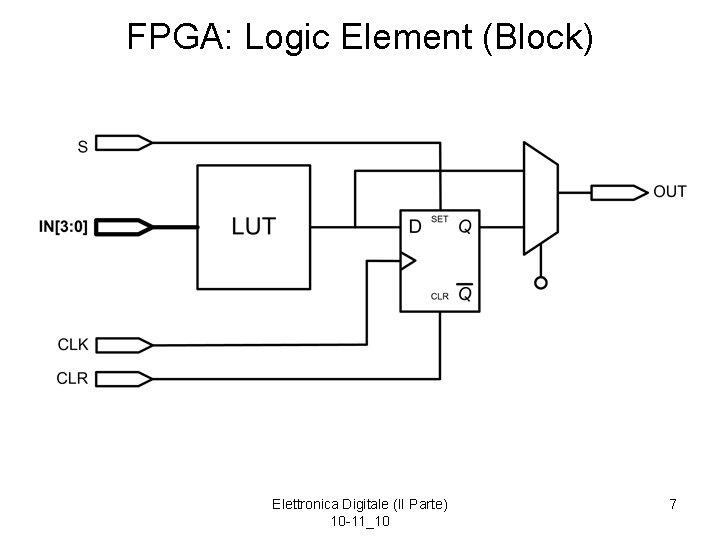

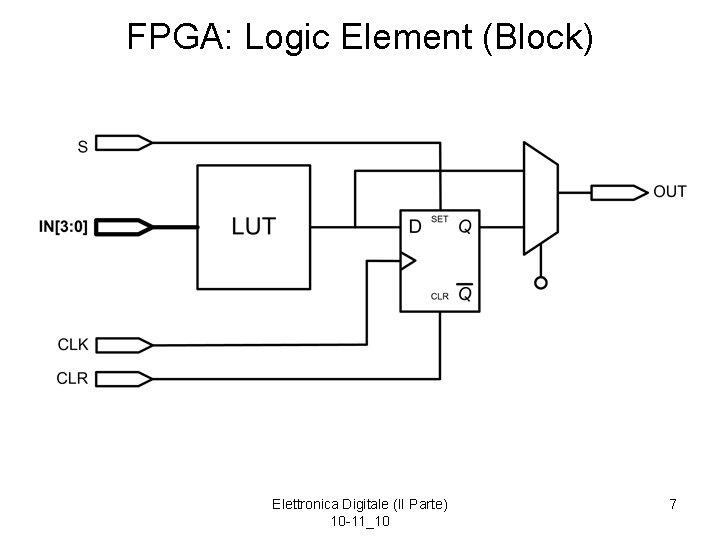

FPGA: Logic Element (Block) Elettronica Digitale (II Parte) 10 -11_10 7

FPGA : motivi delle scelte • Riprogrammabilità anche parziale • Funzionalità volatili e non volatili: SRAM, FLASH, FUSE e MPGA • Tool molto efficienti (HDL) • Prototipi di test • Ecc. Elettronica Digitale (II Parte) 10 -11_10 8

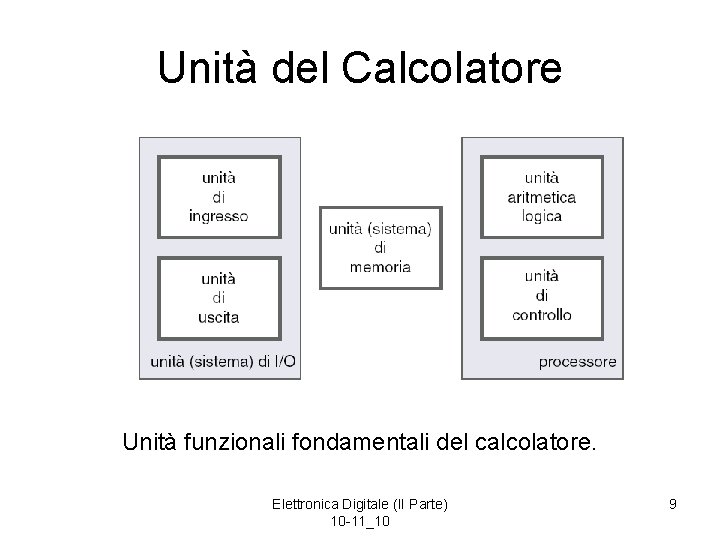

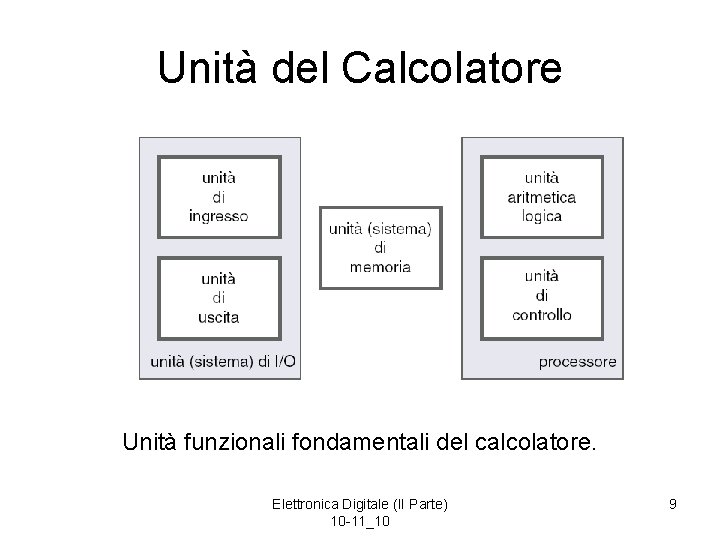

Unità del Calcolatore Unità funzionali fondamentali del calcolatore. Elettronica Digitale (II Parte) 10 -11_10 9

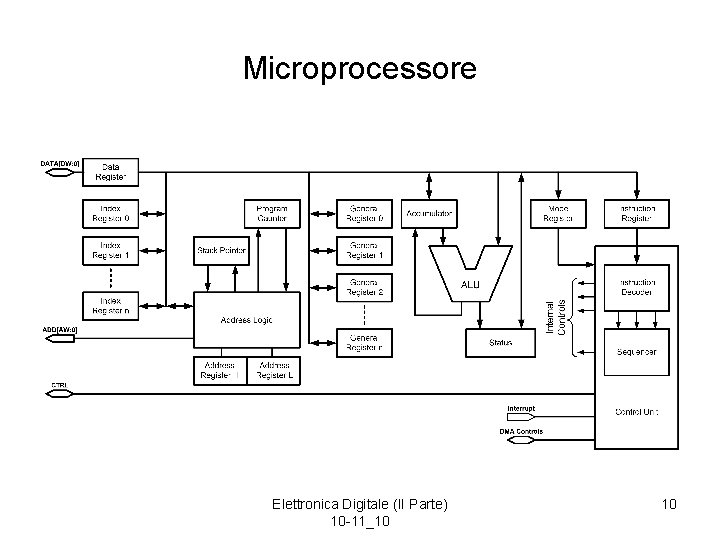

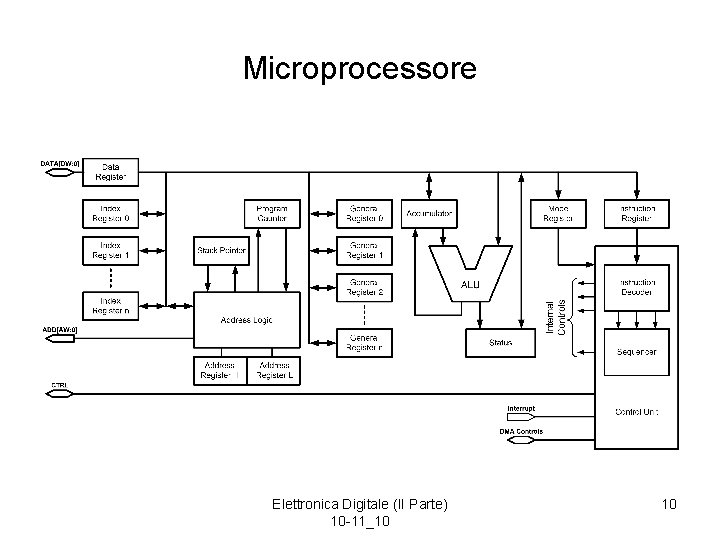

Microprocessore Elettronica Digitale (II Parte) 10 -11_10 10

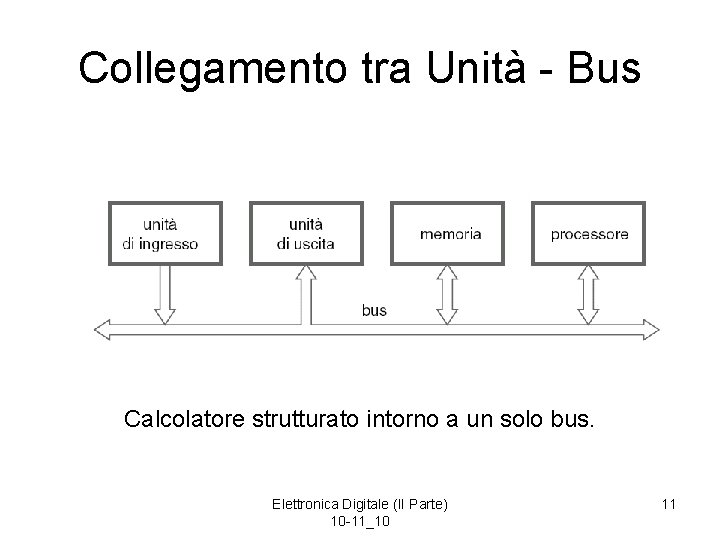

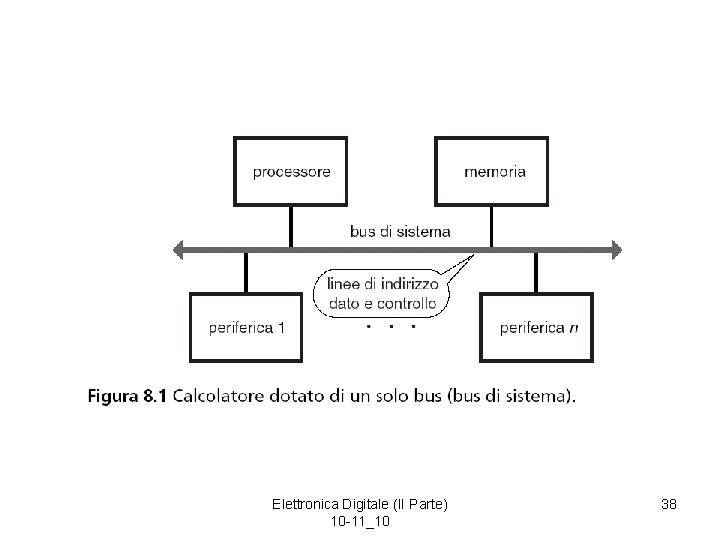

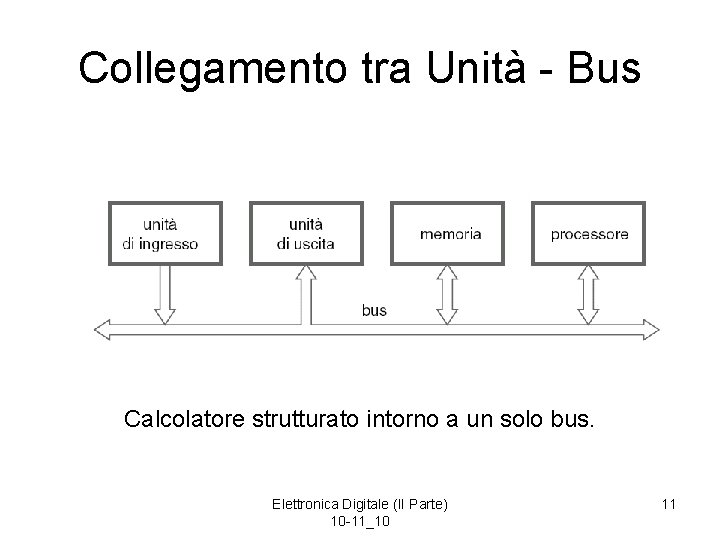

Collegamento tra Unità - Bus Calcolatore strutturato intorno a un solo bus. Elettronica Digitale (II Parte) 10 -11_10 11

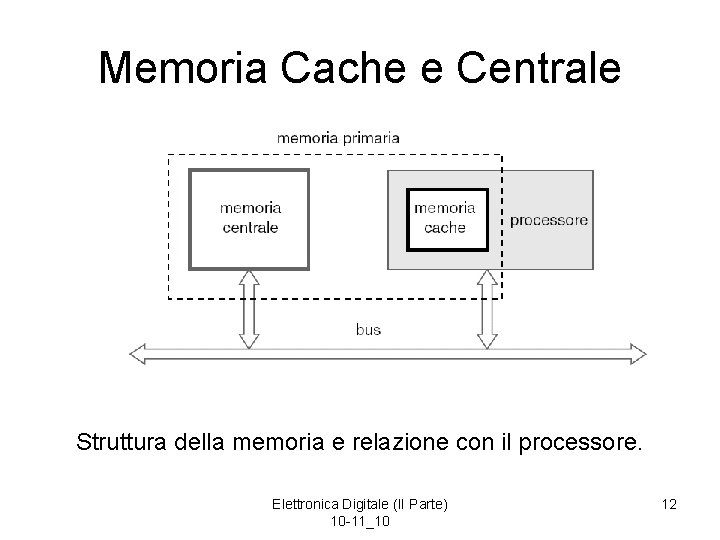

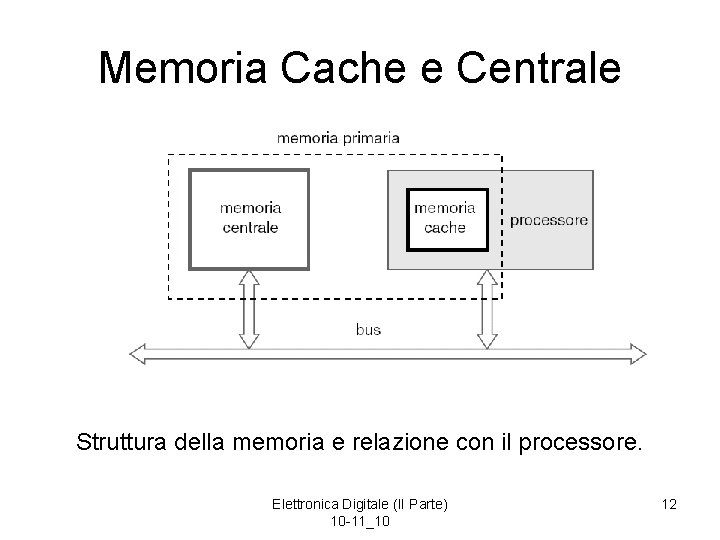

Memoria Cache e Centrale Struttura della memoria e relazione con il processore. Elettronica Digitale (II Parte) 10 -11_10 12

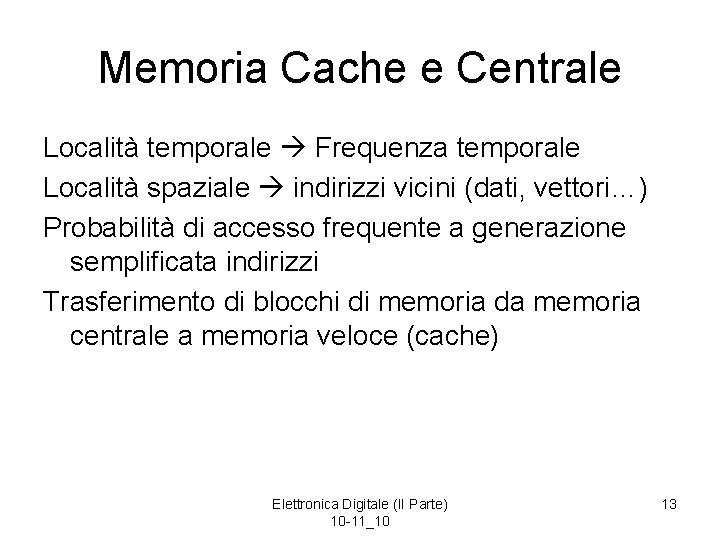

Memoria Cache e Centrale Località temporale Frequenza temporale Località spaziale indirizzi vicini (dati, vettori…) Probabilità di accesso frequente a generazione semplificata indirizzi Trasferimento di blocchi di memoria da memoria centrale a memoria veloce (cache) Elettronica Digitale (II Parte) 10 -11_10 13

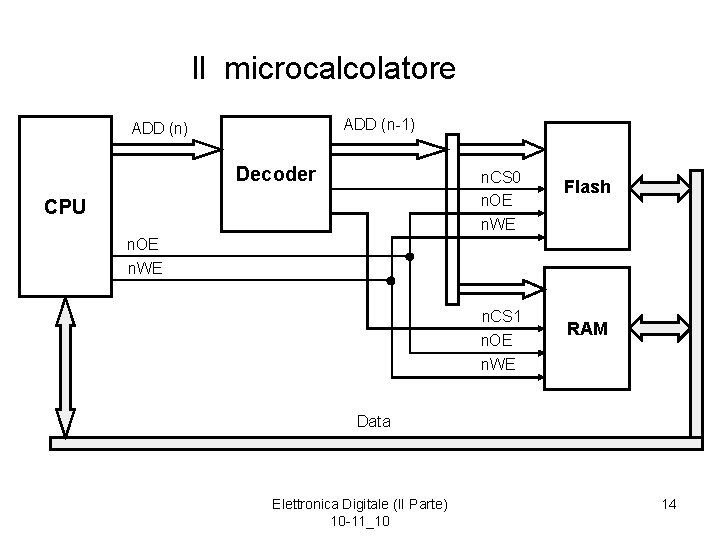

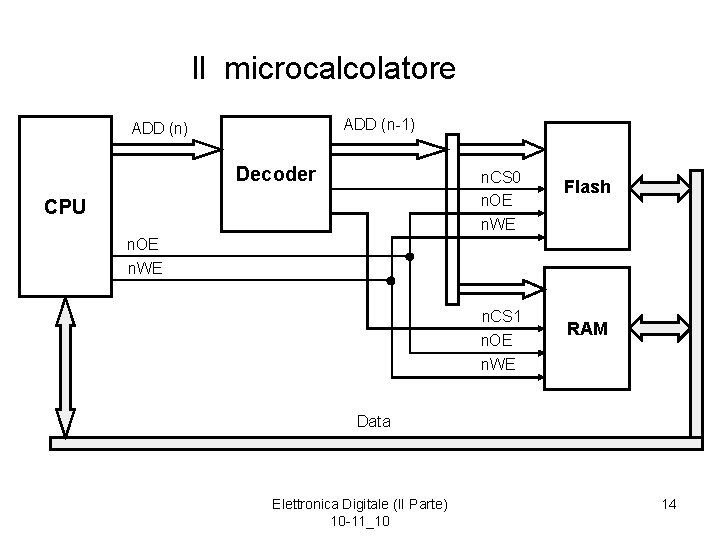

Il microcalcolatore ADD (n-1) ADD (n) Decoder n. CS 0 n. OE CPU Flash n. WE n. OE n. WE n. CS 1 n. OE RAM n. WE Data Elettronica Digitale (II Parte) 10 -11_10 14

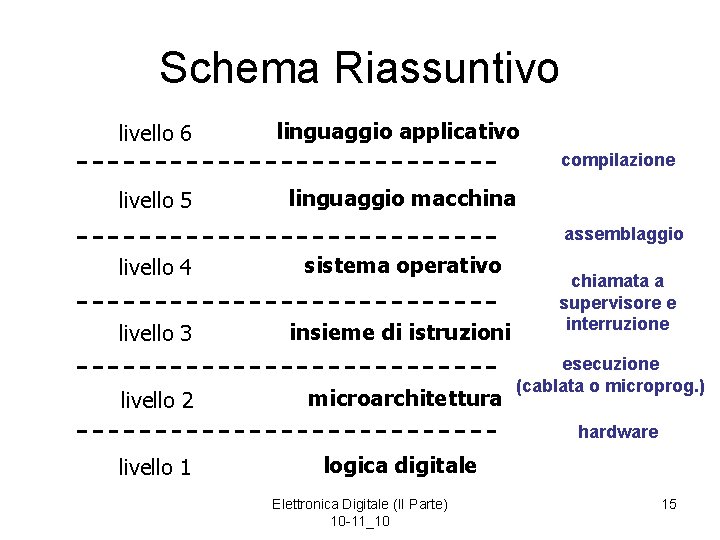

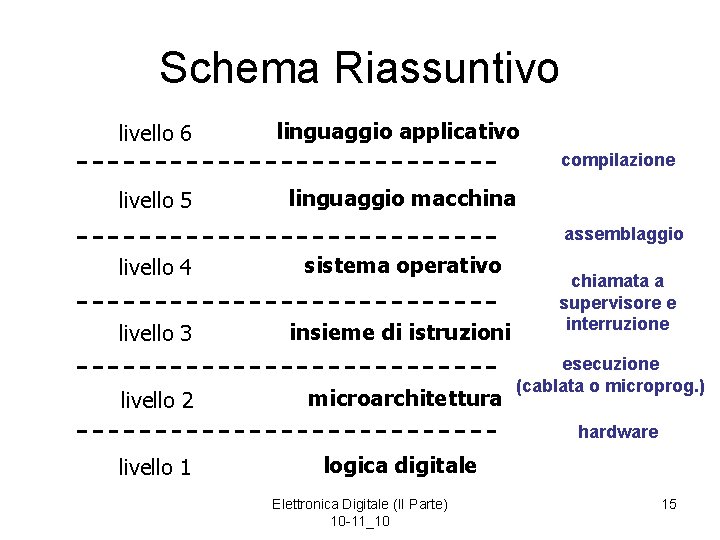

Schema Riassuntivo livello 6 linguaggio applicativo compilazione livello 5 linguaggio macchina assemblaggio livello 4 sistema operativo livello 3 insieme di istruzioni livello 2 microarchitettura chiamata a supervisore e interruzione esecuzione (cablata o microprog. ) hardware livello 1 logica digitale Elettronica Digitale (II Parte) 10 -11_10 15

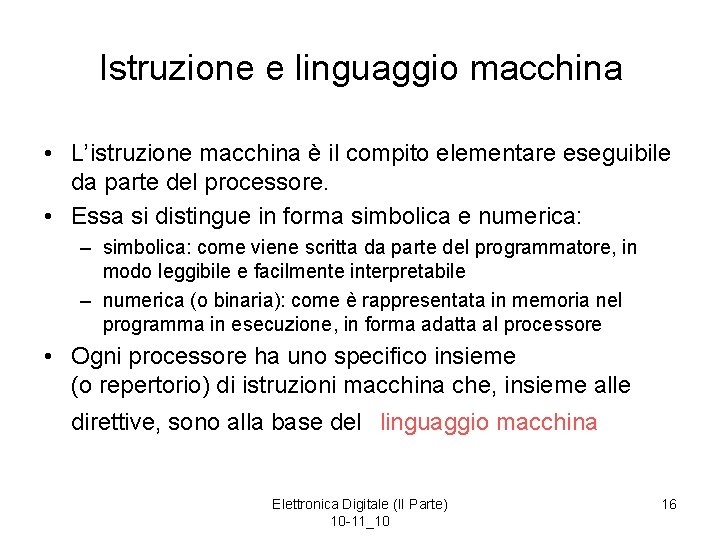

Istruzione e linguaggio macchina • L’istruzione macchina è il compito elementare eseguibile da parte del processore. • Essa si distingue in forma simbolica e numerica: – simbolica: come viene scritta da parte del programmatore, in modo leggibile e facilmente interpretabile – numerica (o binaria): come è rappresentata in memoria nel programma in esecuzione, in forma adatta al processore • Ogni processore ha uno specifico insieme (o repertorio) di istruzioni macchina che, insieme alle direttive, sono alla base del linguaggio macchina Elettronica Digitale (II Parte) 10 -11_10 16

Assemblatore • Il linguaggio macchina in forma simbolica è chiamato anche linguaggio assemblatore o assembly language. • L’assemblatore (assembler) è uno strumento SW che esamina il programma in linguaggio macchina simbolico e, se non ha errori, lo traduce (o assembla) generandone la forma numerica corrispondente • L’assemblatore è legato alle caratteristiche del processore Elettronica Digitale (II Parte) 10 -11_10 17

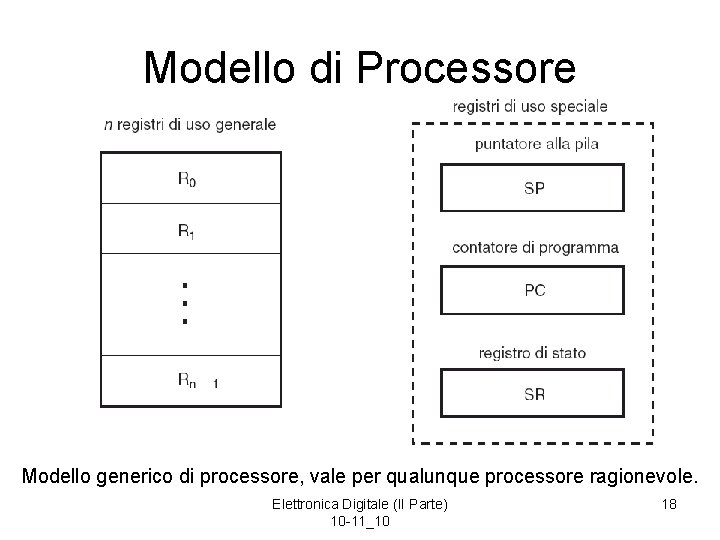

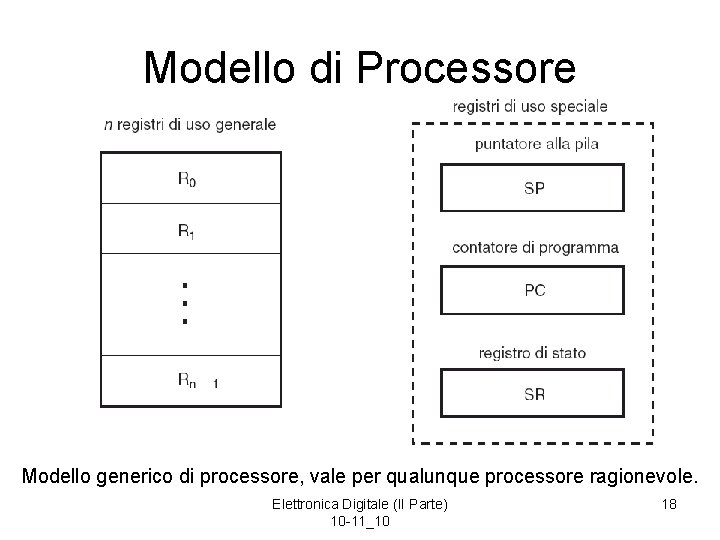

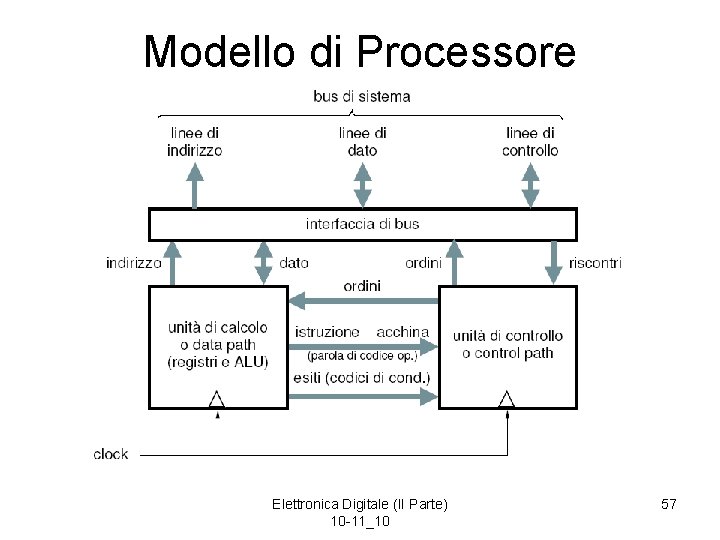

Modello di Processore Modello generico di processore, vale per qualunque processore ragionevole. Elettronica Digitale (II Parte) 10 -11_10 18

Ciclo di Prelievo-Esecuzione • Il processore preleva (fetch) da memoria centrale l’istruzione macchina da eseguire • Il processore decodifica (decode) l’istruzione, cioè la analizza e ne determina il significato. • Il processore esegue (execute) l’istruzione, elaborando i dati opportuni e producendo il risultato: – i dati, o si trovano già nei registri o vanno caricati da memoria – il risultato, o viene lasciato in un registro o viene memorizzato Elettronica Digitale (II Parte) 10 -11_10 19

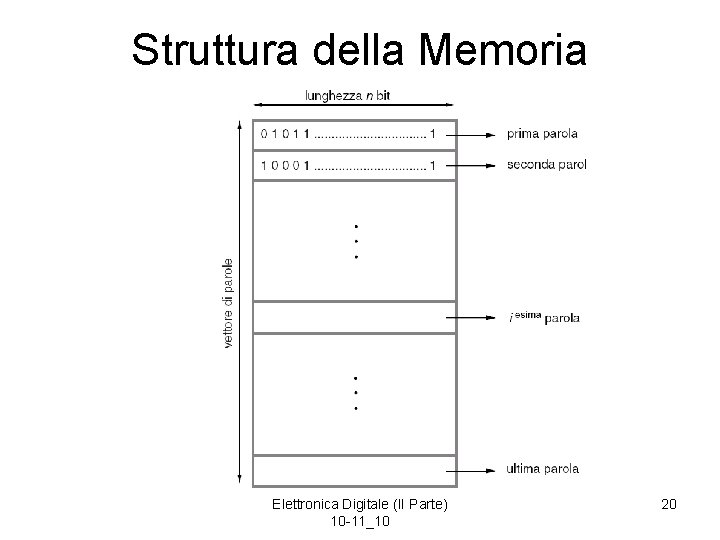

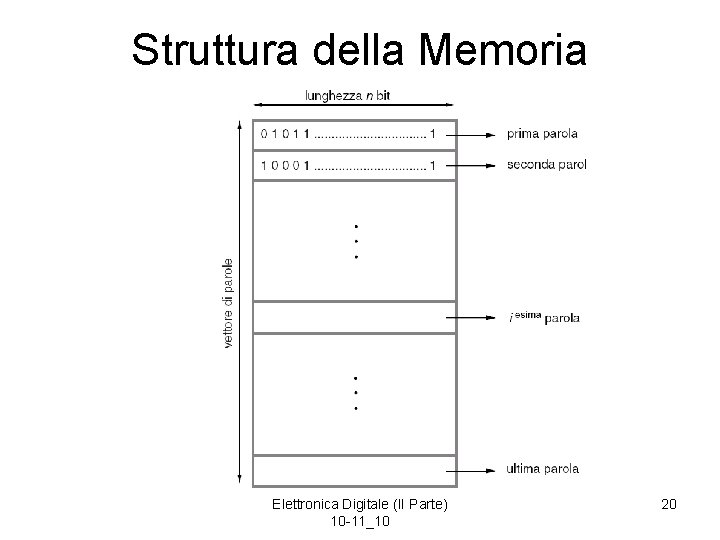

Struttura della Memoria Elettronica Digitale (II Parte) 10 -11_10 20

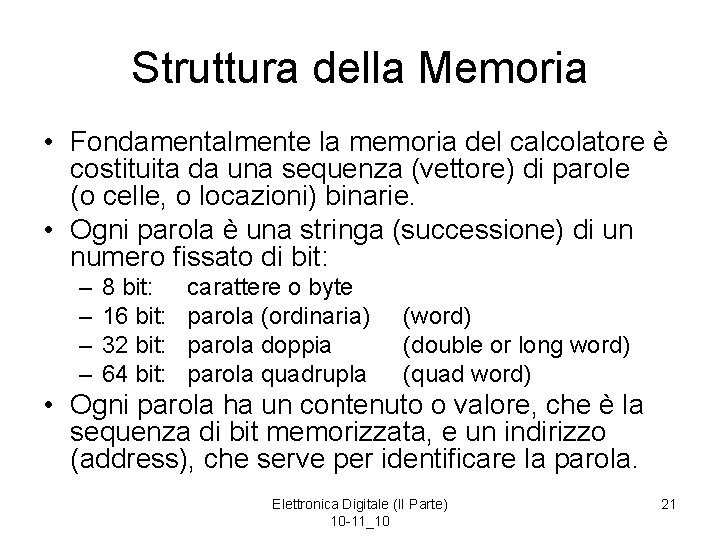

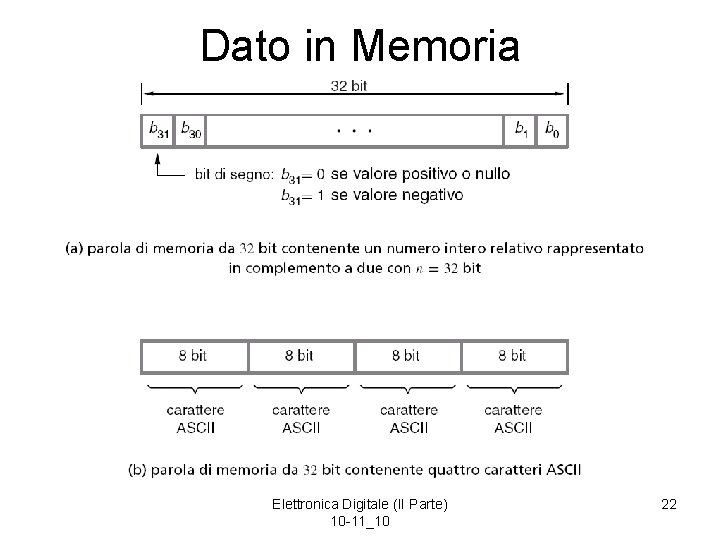

Struttura della Memoria • Fondamentalmente la memoria del calcolatore è costituita da una sequenza (vettore) di parole (o celle, o locazioni) binarie. • Ogni parola è una stringa (successione) di un numero fissato di bit: – – 8 bit: 16 bit: 32 bit: 64 bit: carattere o byte parola (ordinaria) parola doppia parola quadrupla (word) (double or long word) (quad word) • Ogni parola ha un contenuto o valore, che è la sequenza di bit memorizzata, e un indirizzo (address), che serve per identificare la parola. Elettronica Digitale (II Parte) 10 -11_10 21

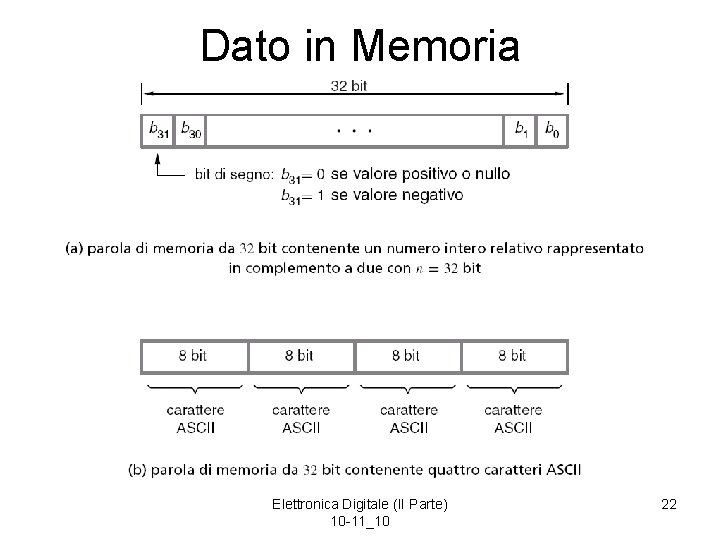

Dato in Memoria Elettronica Digitale (II Parte) 10 -11_10 22

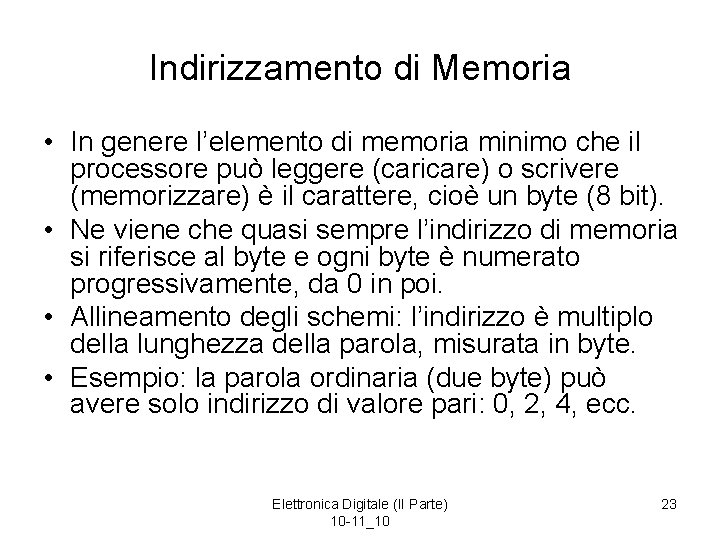

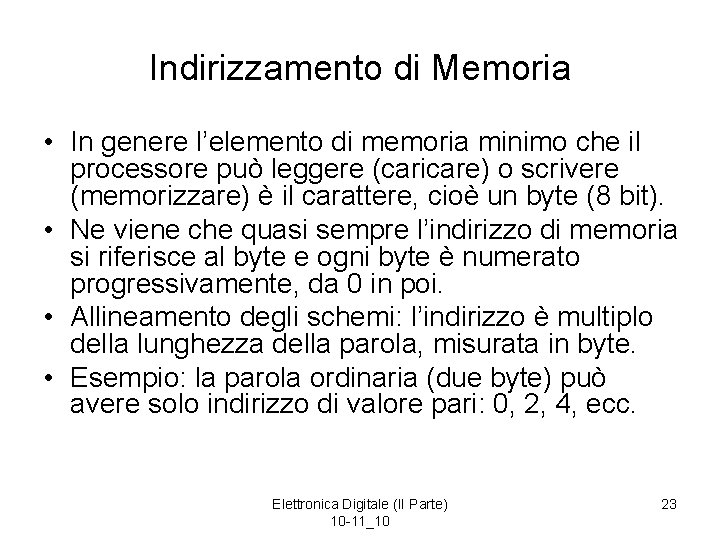

Indirizzamento di Memoria • In genere l’elemento di memoria minimo che il processore può leggere (caricare) o scrivere (memorizzare) è il carattere, cioè un byte (8 bit). • Ne viene che quasi sempre l’indirizzo di memoria si riferisce al byte e ogni byte è numerato progressivamente, da 0 in poi. • Allineamento degli schemi: l’indirizzo è multiplo della lunghezza della parola, misurata in byte. • Esempio: la parola ordinaria (due byte) può avere solo indirizzo di valore pari: 0, 2, 4, ecc. Elettronica Digitale (II Parte) 10 -11_10 23

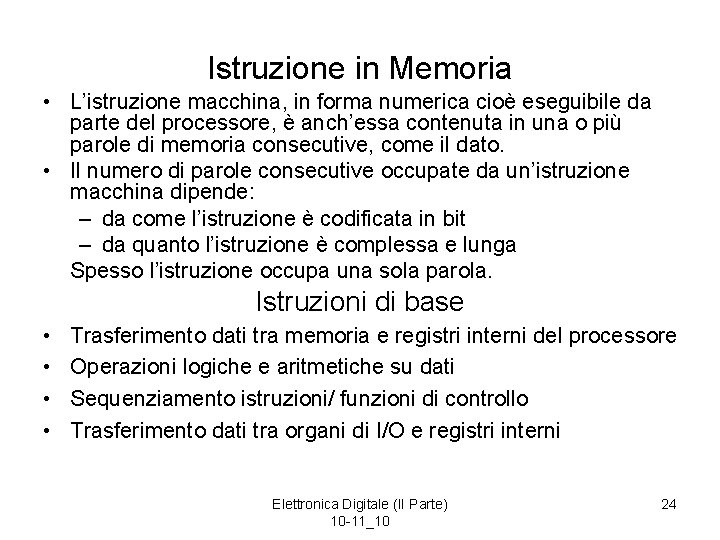

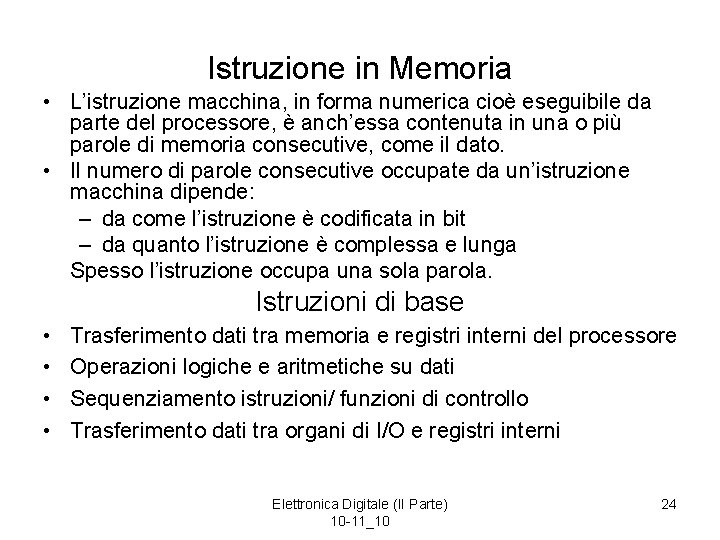

Istruzione in Memoria • L’istruzione macchina, in forma numerica cioè eseguibile da parte del processore, è anch’essa contenuta in una o più parole di memoria consecutive, come il dato. • Il numero di parole consecutive occupate da un’istruzione macchina dipende: – da come l’istruzione è codificata in bit – da quanto l’istruzione è complessa e lunga Spesso l’istruzione occupa una sola parola. Istruzioni di base • • Trasferimento dati tra memoria e registri interni del processore Operazioni logiche e aritmetiche su dati Sequenziamento istruzioni/ funzioni di controllo Trasferimento dati tra organi di I/O e registri interni Elettronica Digitale (II Parte) 10 -11_10 24

Forma Simbolica • Il programmatore denota l’istruzione macchina in forma simbolica, facilmente leggibile, come per esempio: NOME arg 1, arg 2, … commento • Il nome (o codice mnemonico) indica l’operazione: MOVE (carica, memorizza o copia dato), ADD (addiziona dato), SUB (sottrai), ecc • Gli elementi arg 1, arg 2, ecc, sono gli argomenti e indicano i dati da elaborare o dove scrivere il risultato, o anche, nelle istruzioni di salto, dove reperire la prossima istruzione da eseguire. • Argimenti di tipo sorgente (dato), destinazione (dato) e destinazione di salto (indirizzo) … Elettronica Digitale (II Parte) 10 -11_10 25

Argomenti: Sorgente-Destinazione e numero • Nel linguaggio macchina della maggior parte delle famiglie di processori, gli argomenti sorgente precedono quello destinazione. • Prototipici: NOME arg_sorg 1, arg_sorg_2, arg_dest NOME arg_sorg, arg_sorg_e_dest • I linguaggi macchina si dividono in: – linguaggi a due argomenti: le istruzioni che fanno operazioni con due operandi lo sovrascrivono a uno degli operandi, il quale va dunque perso – linguaggi a tre argomenti: le istruzioni non modificano gli operandi e scrivono altrove il risultato Elettronica Digitale (II Parte) 10 -11_10 26

Tipi di istruzione • Tre argomenti: ADD R 1, R 2, R 3 – sovrascrivendone addiziona i contenuti di R 1 e R 2 e scrivi la somma in R 3, il contenuto precedente – R 1 e R 2 sono sorgente, R 3 è destinazione • Due argomenti: ADD R 1, R 2 – addiziona i contenuti di R 1 e R 2 e scrivi la somma in R 2, sovrascrivendone il contenuto precedente – R 1 è sorgente, R 2 è sia sorgente sia destinazione • Un argomento: DEC R 1 – decrementa il contenuto di R 1 – R 1 è sia sorgente sia destinazione • Un argomento (salto): JMP 10 – sposta il flusso di esecuzione del programma all’istruzione collocata all’indirizzo 10 - 10 è destinazione di salto Elettronica Digitale (II Parte) 10 -11_10 27

Formalismo RTL • Register transfer language: è un formalismo notazionale di specifica per istruzioni, di tipo matematico, formale e preciso, per specificare che cosa faccia un’istruzione. • Somiglia al costrutto di assegnamento a variabile, come si trova in C, Pascal e simili. Elettronica Digitale (II Parte) 10 -11_10 28

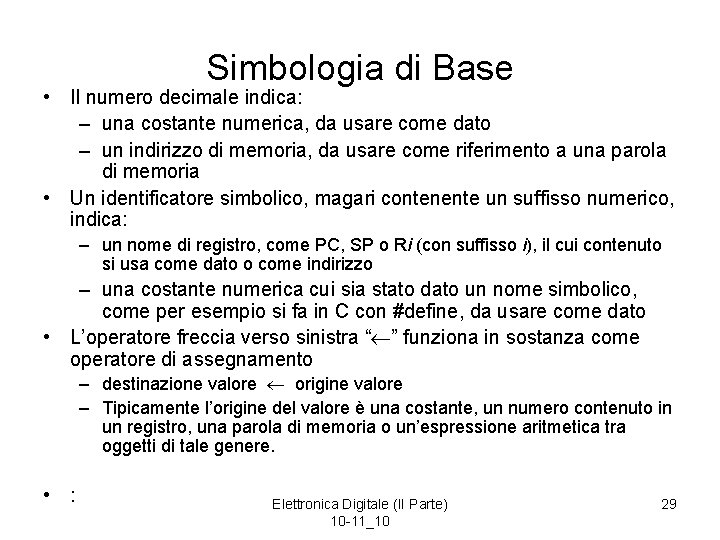

Simbologia di Base • Il numero decimale indica: – una costante numerica, da usare come dato – un indirizzo di memoria, da usare come riferimento a una parola di memoria • Un identificatore simbolico, magari contenente un suffisso numerico, indica: – un nome di registro, come PC, SP o Ri (con suffisso i), il cui contenuto si usa come dato o come indirizzo – una costante numerica cui sia stato dato un nome simbolico, come per esempio si fa in C con #define, da usare come dato • L’operatore freccia verso sinistra “ ” funziona in sostanza come operatore di assegnamento – destinazione valore origine valore – Tipicamente l’origine del valore è una costante, un numero contenuto in un registro, una parola di memoria o un’espressione aritmetica tra oggetti di tale genere. • : Elettronica Digitale (II Parte) 10 -11_10 29

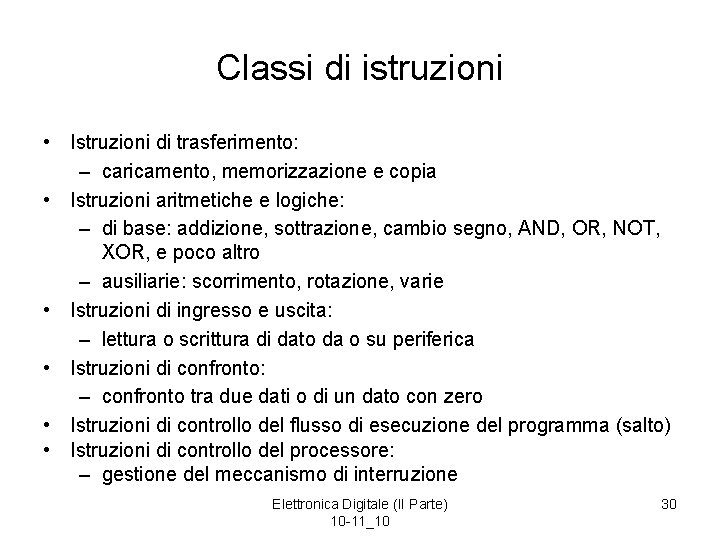

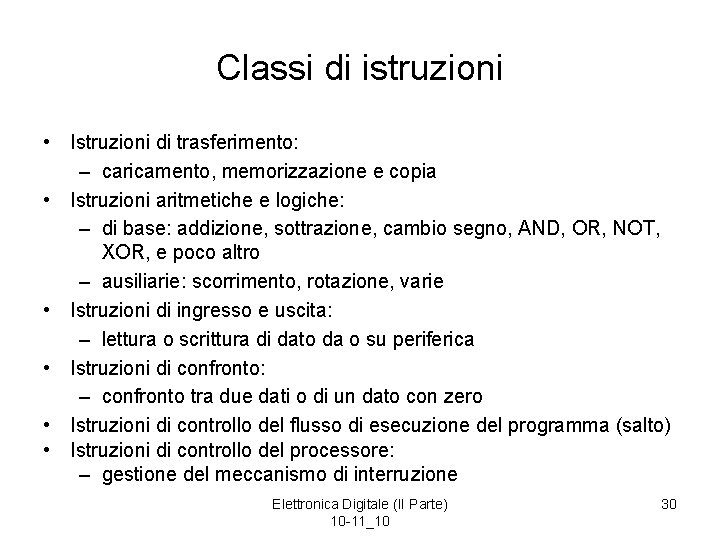

Classi di istruzioni • Istruzioni di trasferimento: – caricamento, memorizzazione e copia • Istruzioni aritmetiche e logiche: – di base: addizione, sottrazione, cambio segno, AND, OR, NOT, XOR, e poco altro – ausiliarie: scorrimento, rotazione, varie • Istruzioni di ingresso e uscita: – lettura o scrittura di dato da o su periferica • Istruzioni di confronto: – confronto tra due dati o di un dato con zero • Istruzioni di controllo del flusso di esecuzione del programma (salto) • Istruzioni di controllo del processore: – gestione del meccanismo di interruzione Elettronica Digitale (II Parte) 10 -11_10 30

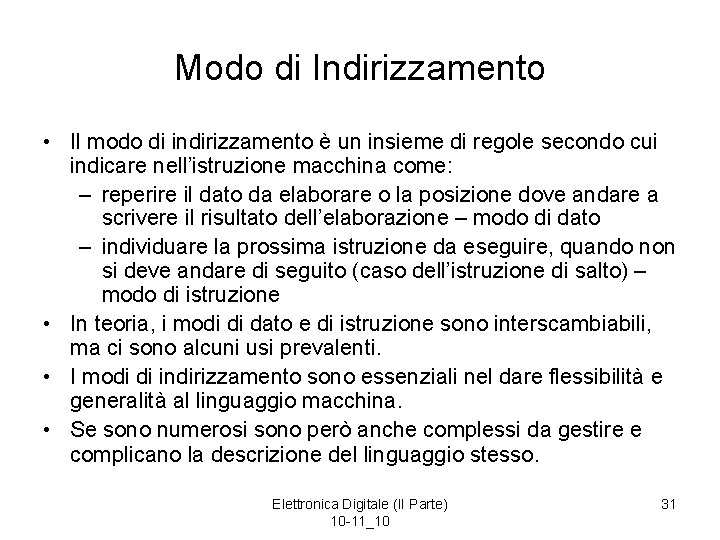

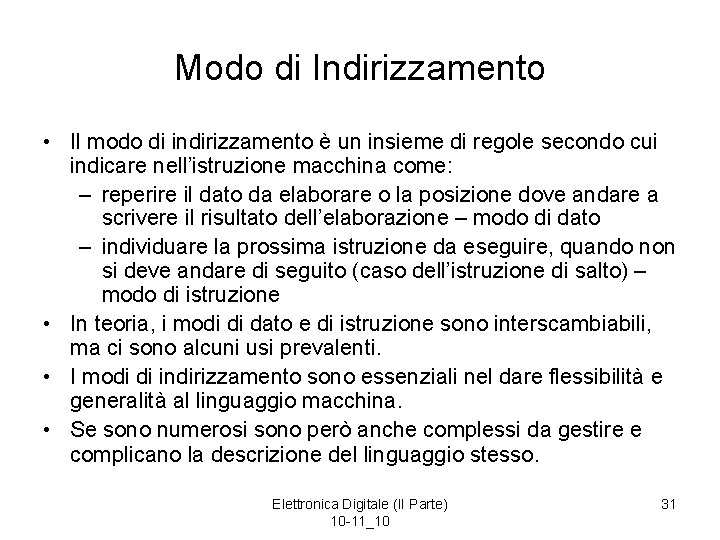

Modo di Indirizzamento • Il modo di indirizzamento è un insieme di regole secondo cui indicare nell’istruzione macchina come: – reperire il dato da elaborare o la posizione dove andare a scrivere il risultato dell’elaborazione – modo di dato – individuare la prossima istruzione da eseguire, quando non si deve andare di seguito (caso dell’istruzione di salto) – modo di istruzione • In teoria, i modi di dato e di istruzione sono interscambiabili, ma ci sono alcuni usi prevalenti. • I modi di indirizzamento sono essenziali nel dare flessibilità e generalità al linguaggio macchina. • Se sono numerosi sono però anche complessi da gestire e complicano la descrizione del linguaggio stesso. Elettronica Digitale (II Parte) 10 -11_10 31

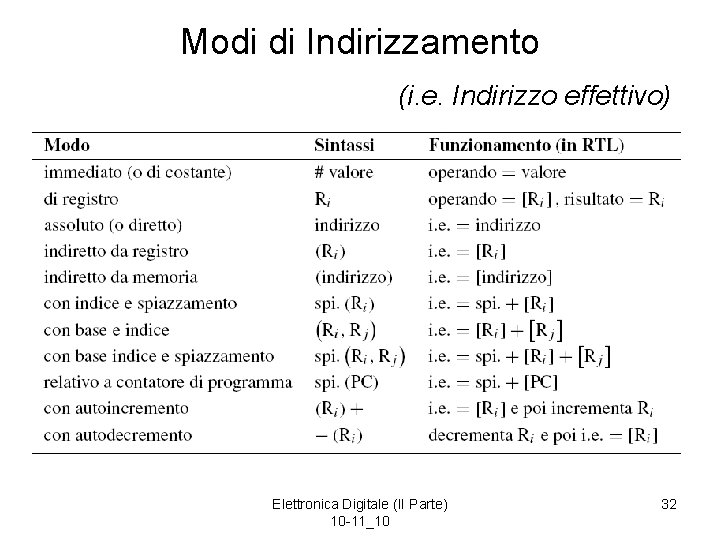

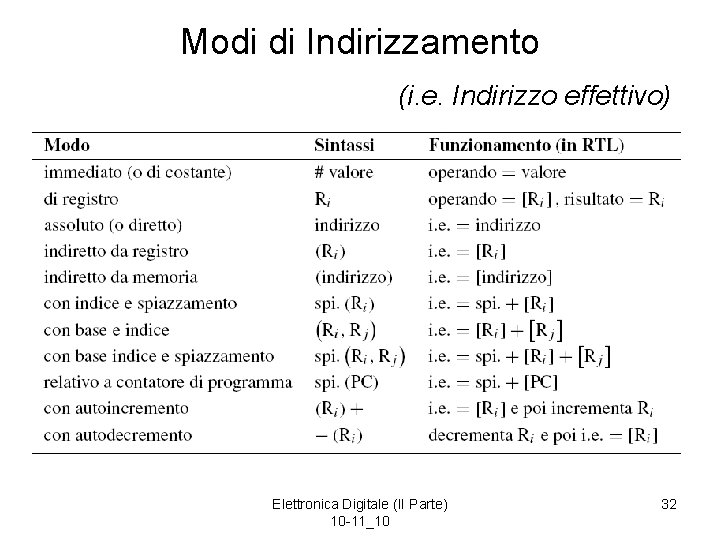

Modi di Indirizzamento (i. e. Indirizzo effettivo) Elettronica Digitale (II Parte) 10 -11_10 32

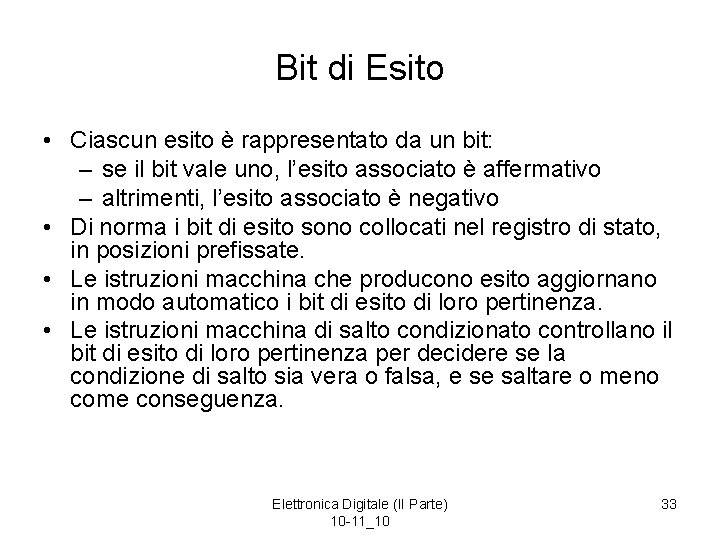

Bit di Esito • Ciascun esito è rappresentato da un bit: – se il bit vale uno, l’esito associato è affermativo – altrimenti, l’esito associato è negativo • Di norma i bit di esito sono collocati nel registro di stato, in posizioni prefissate. • Le istruzioni macchina che producono esito aggiornano in modo automatico i bit di esito di loro pertinenza. • Le istruzioni macchina di salto condizionato controllano il bit di esito di loro pertinenza per decidere se la condizione di salto sia vera o falsa, e se saltare o meno come conseguenza. Elettronica Digitale (II Parte) 10 -11_10 33

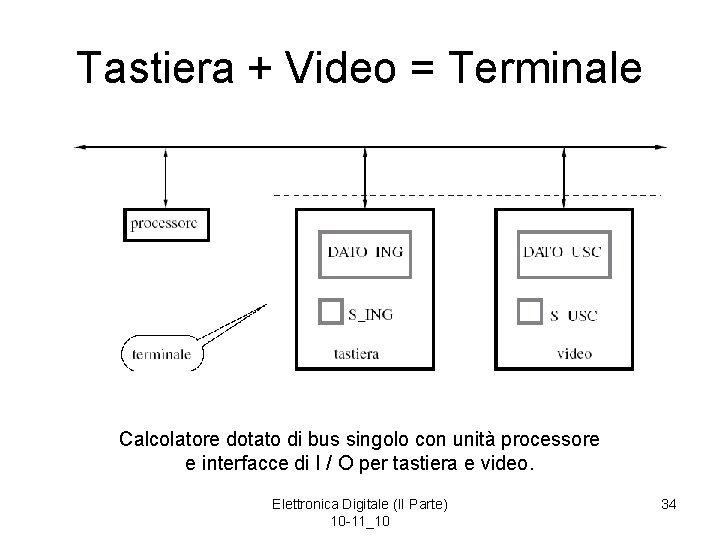

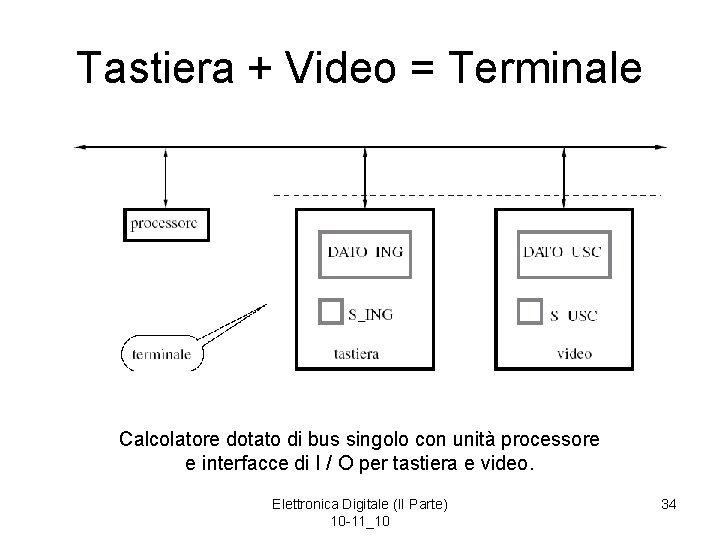

Tastiera + Video = Terminale Calcolatore dotato di bus singolo con unità processore e interfacce di I / O per tastiera e video. Elettronica Digitale (II Parte) 10 -11_10 34

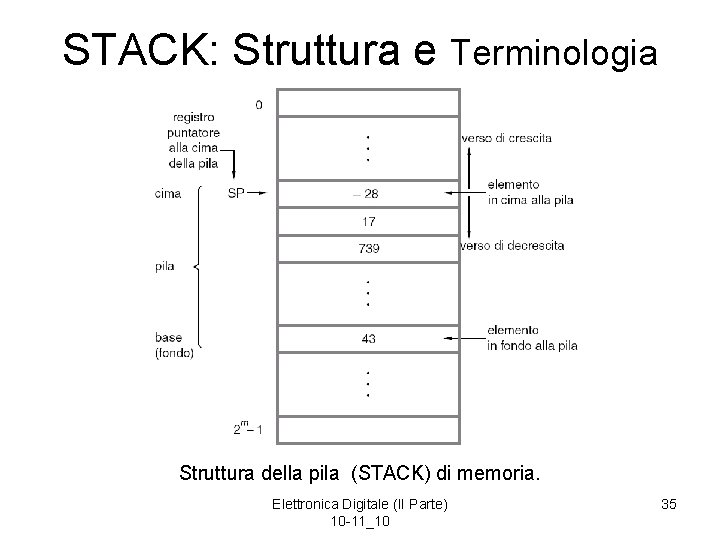

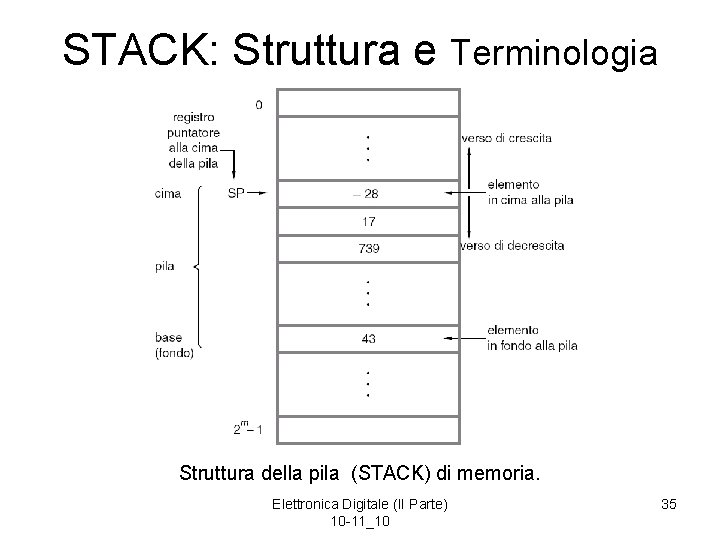

STACK: Struttura e Terminologia Struttura della pila (STACK) di memoria. Elettronica Digitale (II Parte) 10 -11_10 35

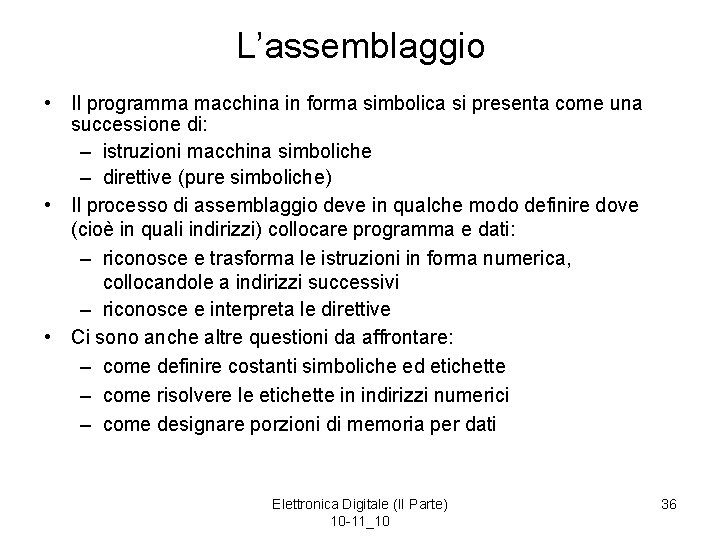

L’assemblaggio • Il programma macchina in forma simbolica si presenta come una successione di: – istruzioni macchina simboliche – direttive (pure simboliche) • Il processo di assemblaggio deve in qualche modo definire dove (cioè in quali indirizzi) collocare programma e dati: – riconosce e trasforma le istruzioni in forma numerica, collocandole a indirizzi successivi – riconosce e interpreta le direttive • Ci sono anche altre questioni da affrontare: – come definire costanti simboliche ed etichette – come risolvere le etichette in indirizzi numerici – come designare porzioni di memoria per dati Elettronica Digitale (II Parte) 10 -11_10 36

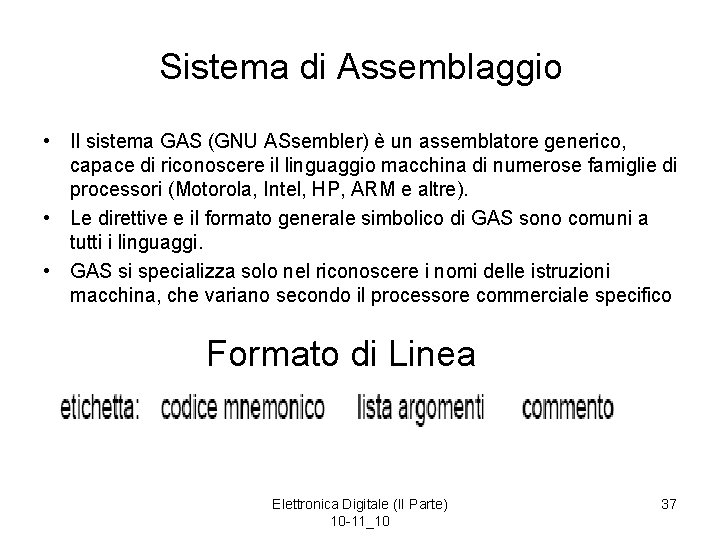

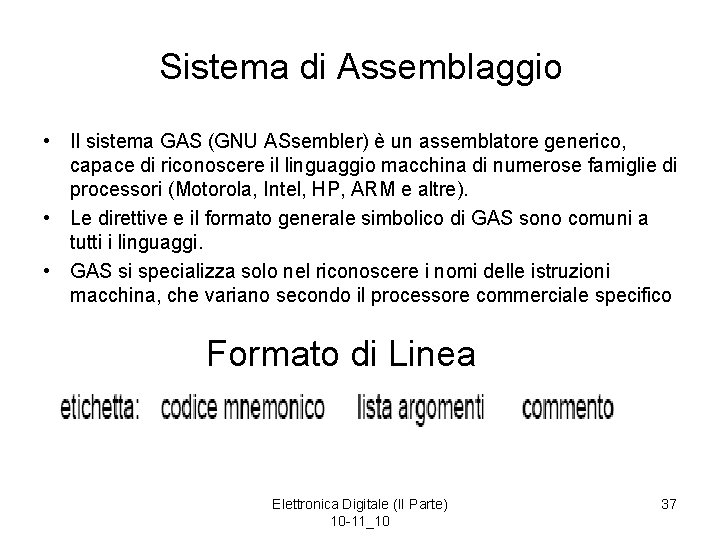

Sistema di Assemblaggio • Il sistema GAS (GNU ASsembler) è un assemblatore generico, capace di riconoscere il linguaggio macchina di numerose famiglie di processori (Motorola, Intel, HP, ARM e altre). • Le direttive e il formato generale simbolico di GAS sono comuni a tutti i linguaggi. • GAS si specializza solo nel riconoscere i nomi delle istruzioni macchina, che variano secondo il processore commerciale specifico Formato di Linea Elettronica Digitale (II Parte) 10 -11_10 37

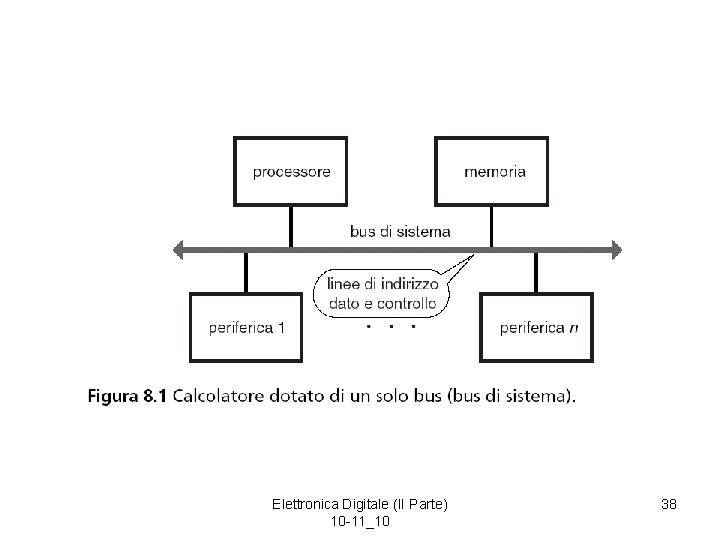

Elettronica Digitale (II Parte) 10 -11_10 38

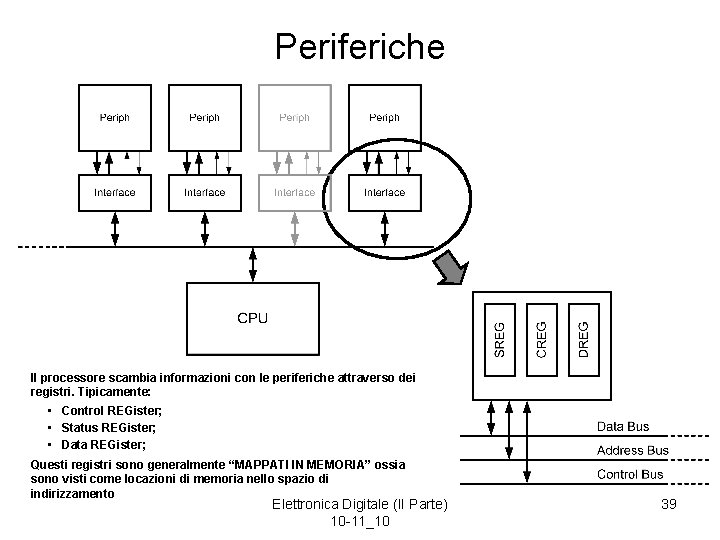

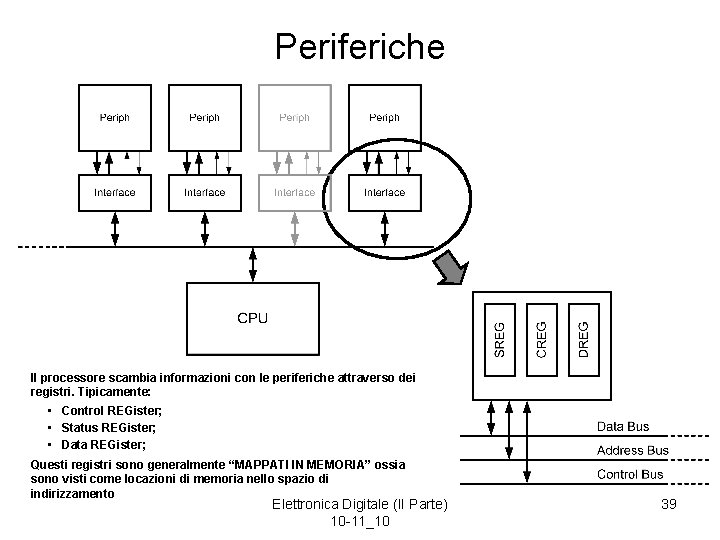

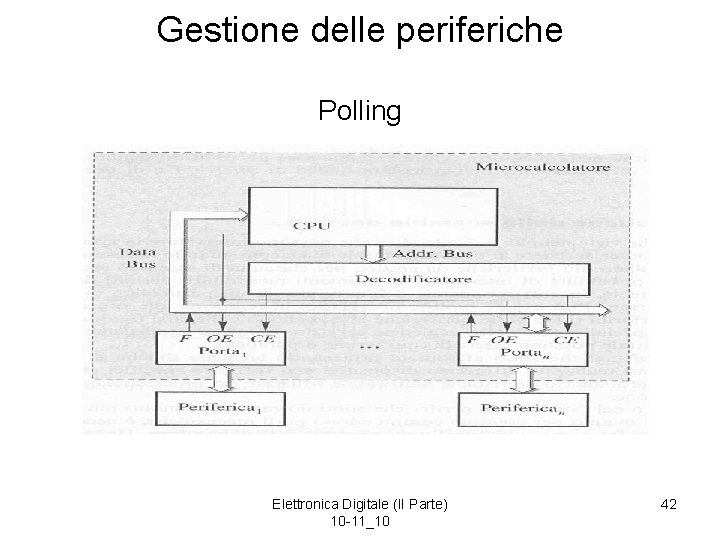

Periferiche Il processore scambia informazioni con le periferiche attraverso dei registri. Tipicamente: • Control REGister; • Status REGister; • Data REGister; Questi registri sono generalmente “MAPPATI IN MEMORIA” ossia sono visti come locazioni di memoria nello spazio di indirizzamento Elettronica Digitale (II Parte) 10 -11_10 39

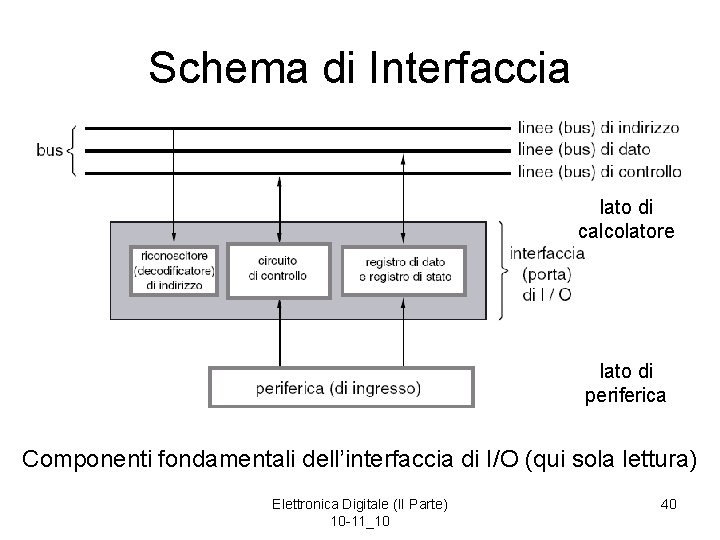

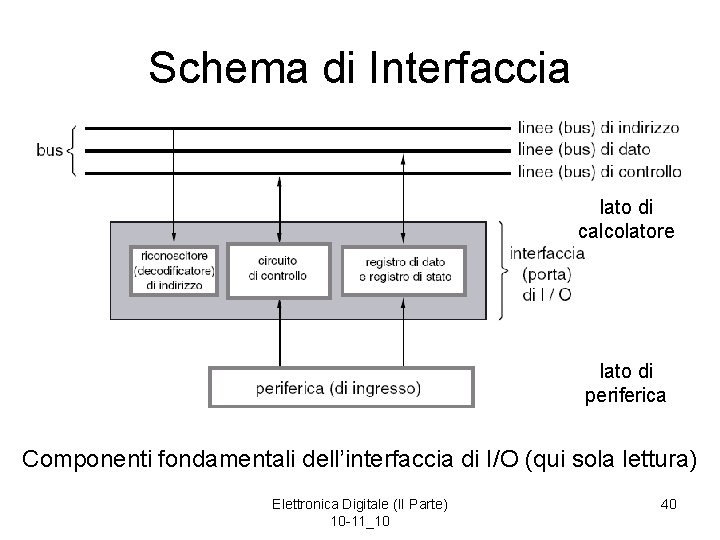

Schema di Interfaccia lato di calcolatore lato di periferica Componenti fondamentali dell’interfaccia di I/O (qui sola lettura) Elettronica Digitale (II Parte) 10 -11_10 40

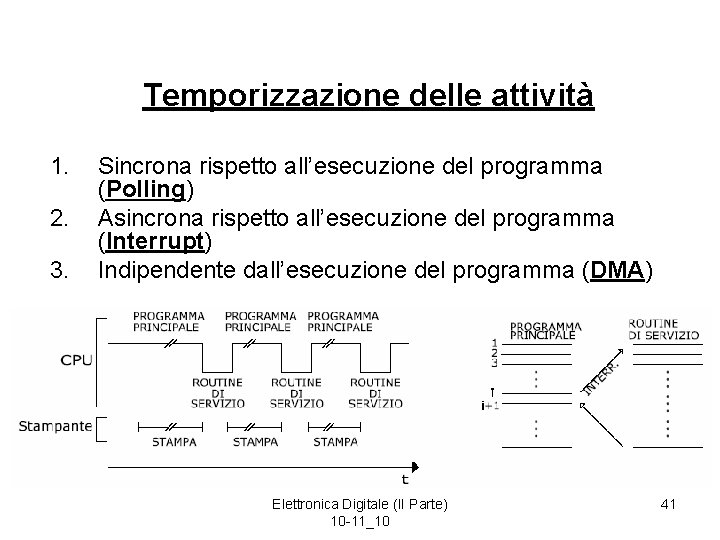

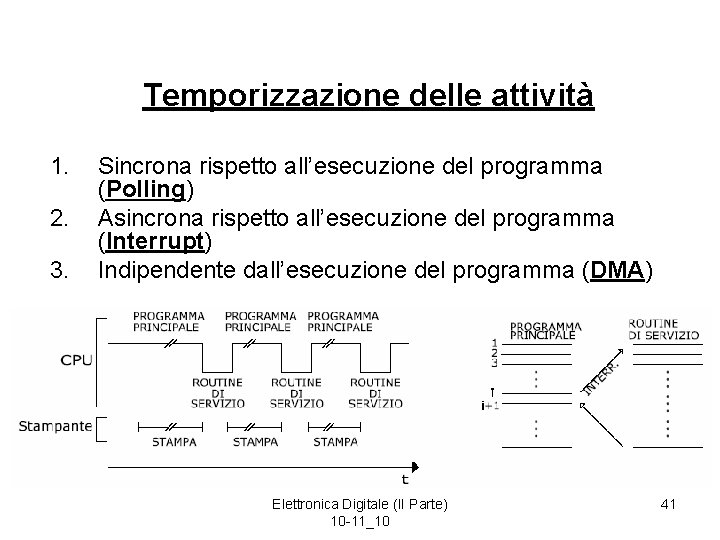

Temporizzazione delle attività 1. 2. 3. Sincrona rispetto all’esecuzione del programma (Polling) Asincrona rispetto all’esecuzione del programma (Interrupt) Indipendente dall’esecuzione del programma (DMA) Elettronica Digitale (II Parte) 10 -11_10 41

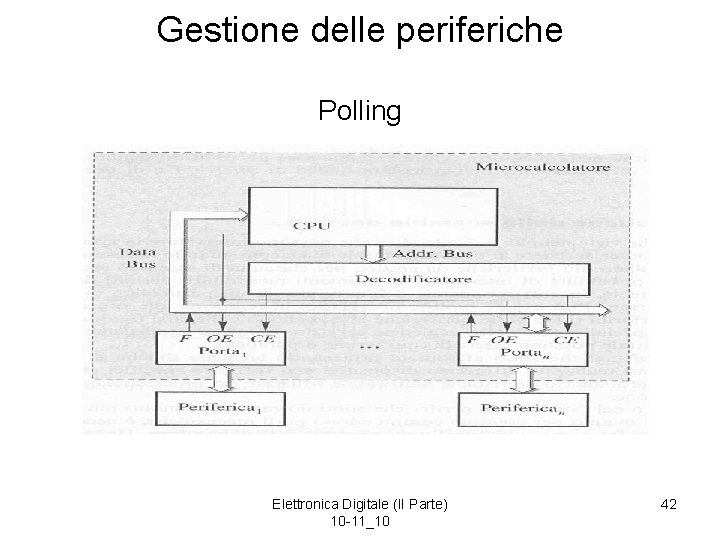

Gestione delle periferiche Polling Elettronica Digitale (II Parte) 10 -11_10 42

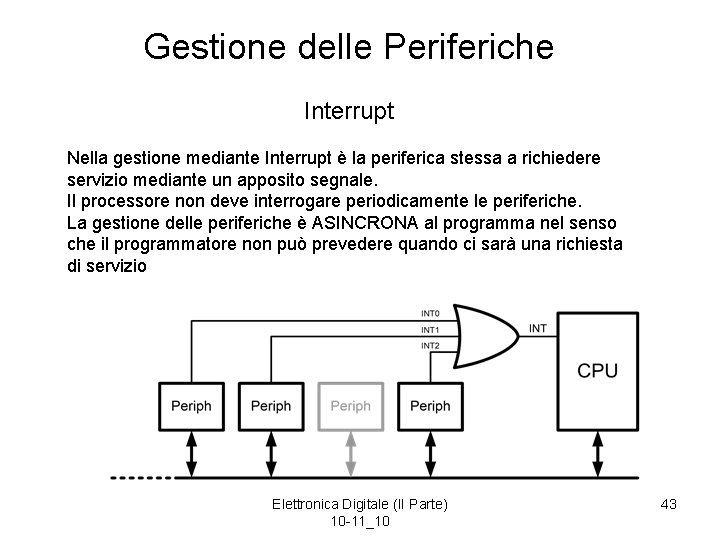

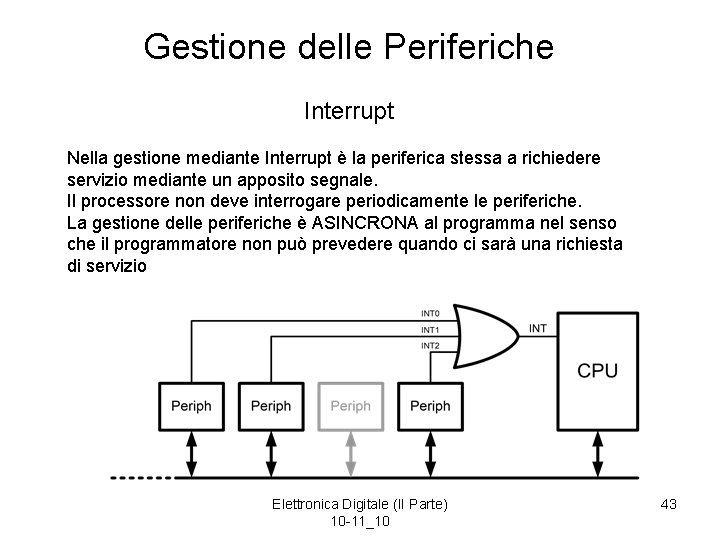

Gestione delle Periferiche Interrupt Nella gestione mediante Interrupt è la periferica stessa a richiedere servizio mediante un apposito segnale. Il processore non deve interrogare periodicamente le periferiche. La gestione delle periferiche è ASINCRONA al programma nel senso che il programmatore non può prevedere quando ci sarà una richiesta di servizio Elettronica Digitale (II Parte) 10 -11_10 43

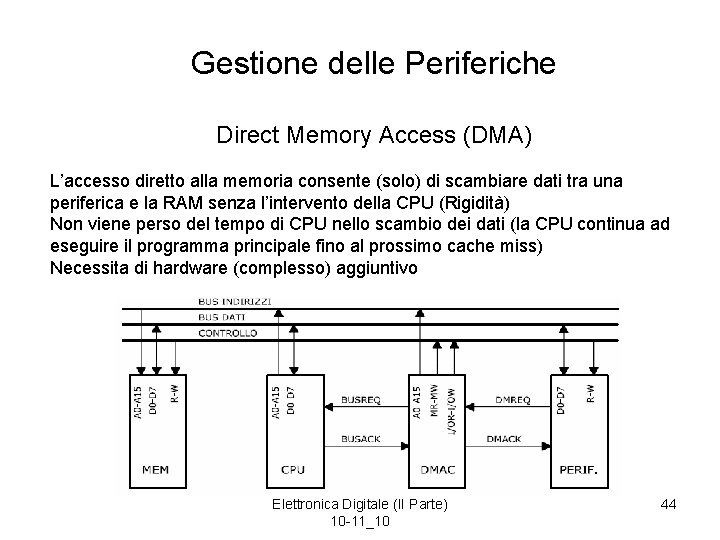

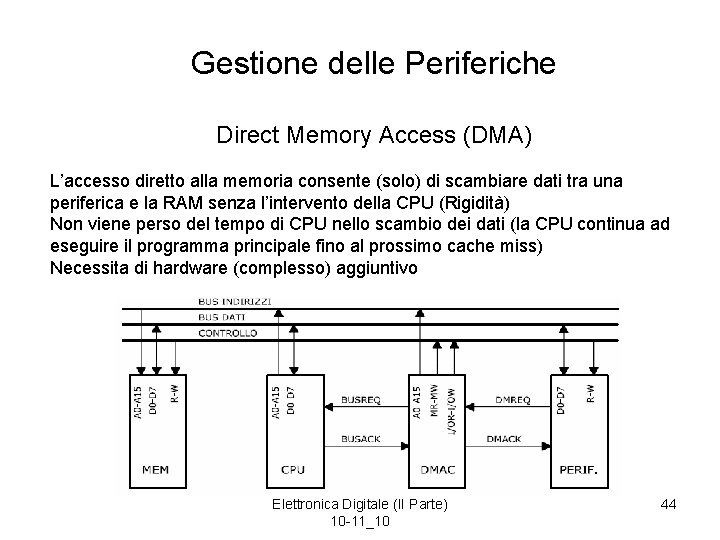

Gestione delle Periferiche Direct Memory Access (DMA) L’accesso diretto alla memoria consente (solo) di scambiare dati tra una periferica e la RAM senza l’intervento della CPU (Rigidità) Non viene perso del tempo di CPU nello scambio dei dati (la CPU continua ad eseguire il programma principale fino al prossimo cache miss) Necessita di hardware (complesso) aggiuntivo Elettronica Digitale (II Parte) 10 -11_10 44

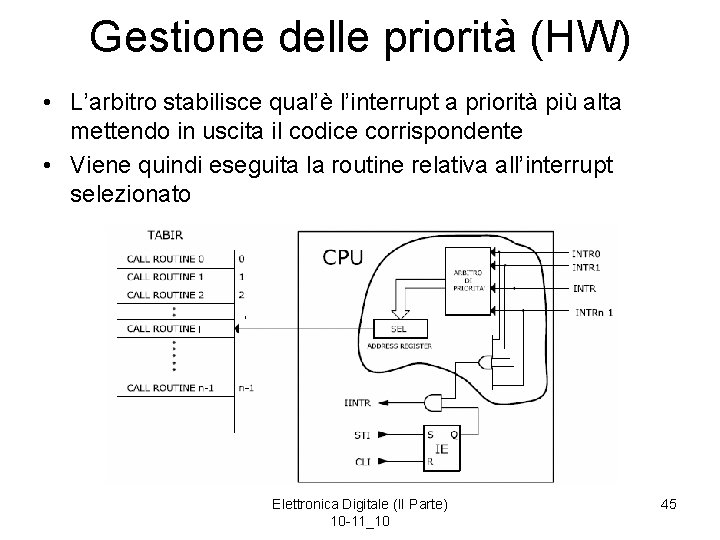

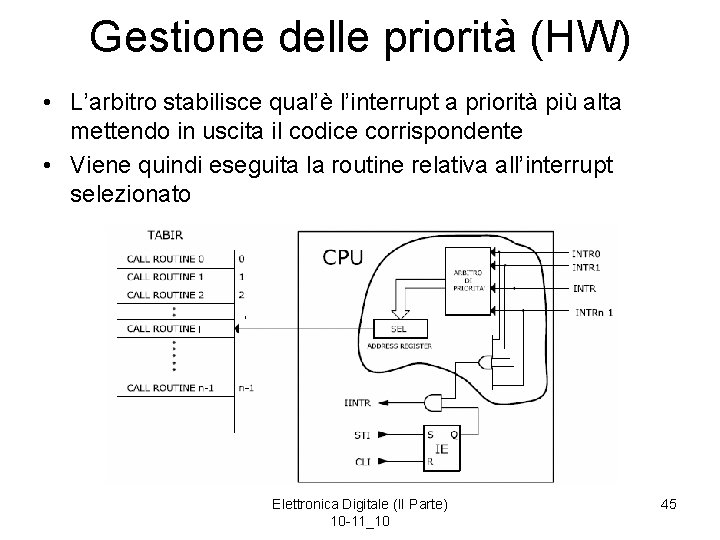

Gestione delle priorità (HW) • L’arbitro stabilisce qual’è l’interrupt a priorità più alta mettendo in uscita il codice corrispondente • Viene quindi eseguita la routine relativa all’interrupt selezionato Elettronica Digitale (II Parte) 10 -11_10 45

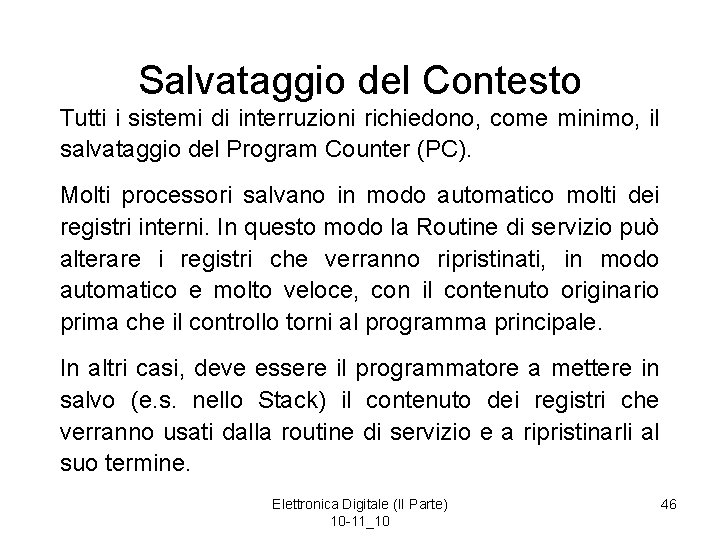

Salvataggio del Contesto Tutti i sistemi di interruzioni richiedono, come minimo, il salvataggio del Program Counter (PC). Molti processori salvano in modo automatico molti dei registri interni. In questo modo la Routine di servizio può alterare i registri che verranno ripristinati, in modo automatico e molto veloce, con il contenuto originario prima che il controllo torni al programma principale. In altri casi, deve essere il programmatore a mettere in salvo (e. s. nello Stack) il contenuto dei registri che verranno usati dalla routine di servizio e a ripristinarli al suo termine. Elettronica Digitale (II Parte) 10 -11_10 46

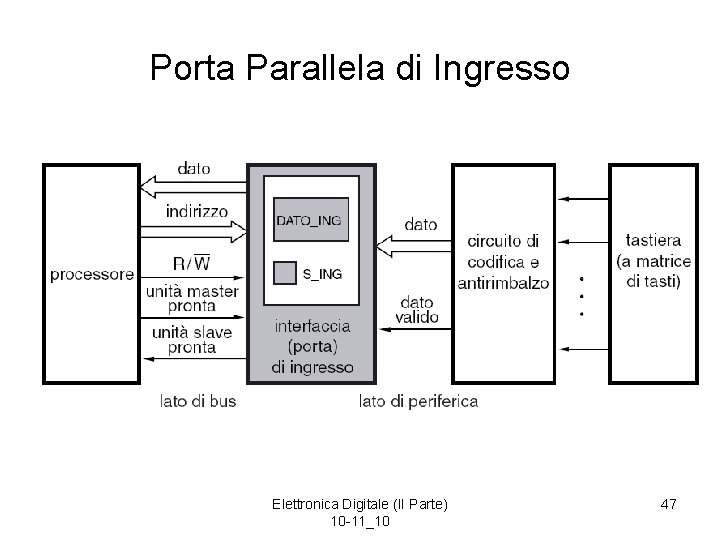

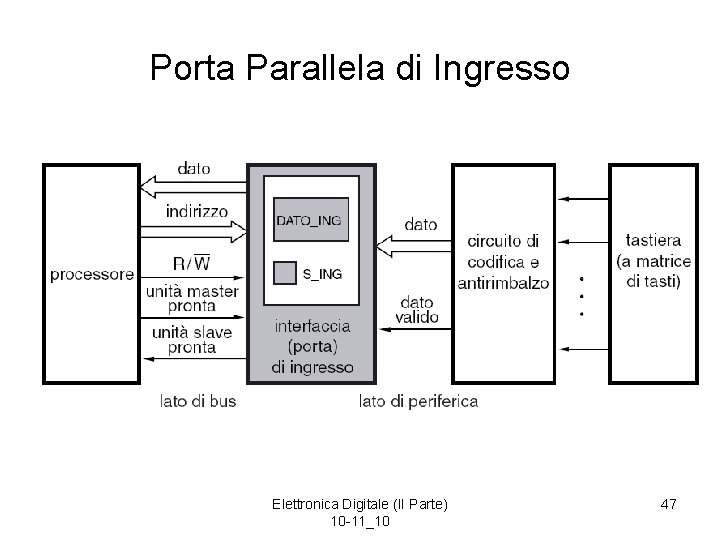

Porta Parallela di Ingresso Elettronica Digitale (II Parte) 10 -11_10 47

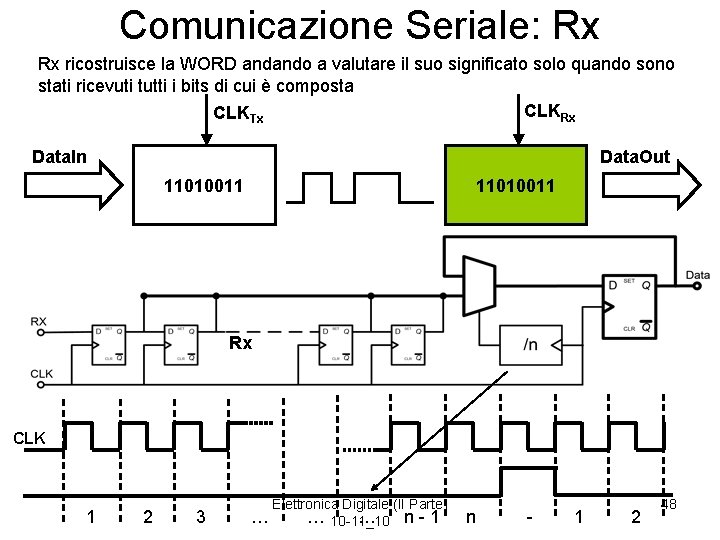

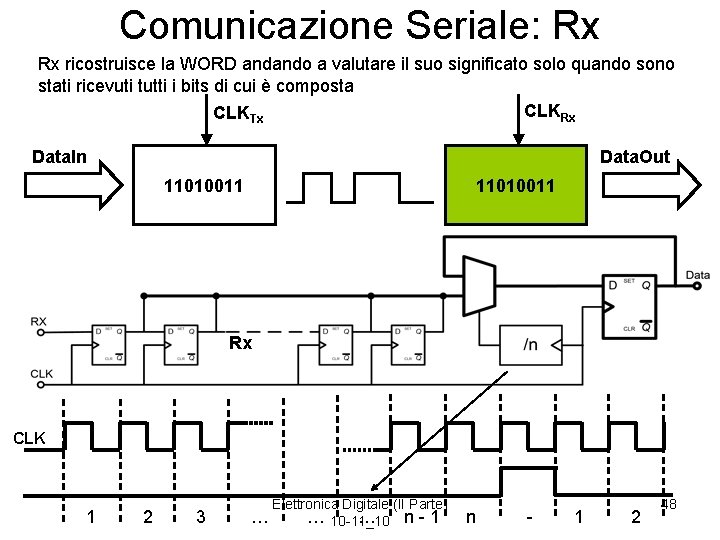

Comunicazione Seriale: Rx Rx ricostruisce la WORD andando a valutare il suo significato solo quando sono stati ricevuti tutti i bits di cui è composta CLKRx CLKTx Data. In Data. Out 11010011 Rx CLK 1 2 3 … Elettronica Digitale (II Parte) n-1 … 10 -11_10 … n - 1 2 48

Ruolo del Sistema Operativo • Normalmente il calcolatore è equipaggiato con un sistema operativo (SO). • Il SO è un complesso di programmi che danno al calcolatore funzionalità minimali: – caricare e attivare uno o più programmi – gestire le unità funzionali di memoria e I/O – permettere l’esecuzione simultanea di due o più programmi (processi): concorrenza – permettere la compresenza di più utenti – garantire affidabilità e sicurezza del calcolatore. Elettronica Digitale (II Parte) 10 -11_10 49

Memoria • Memoria interna o centrale o principale – ROM, PROM – RAM (SRAM, DRAM) • Memoria esterna o ausiliaria – Dischi rigidi (magnetici, ottici, magneto-ottici) – Floppy – Nastri – Cassette Elettronica Digitale (II Parte) 10 -11_10 50

Elettronica Digitale (II Parte) 10 -11_10 51

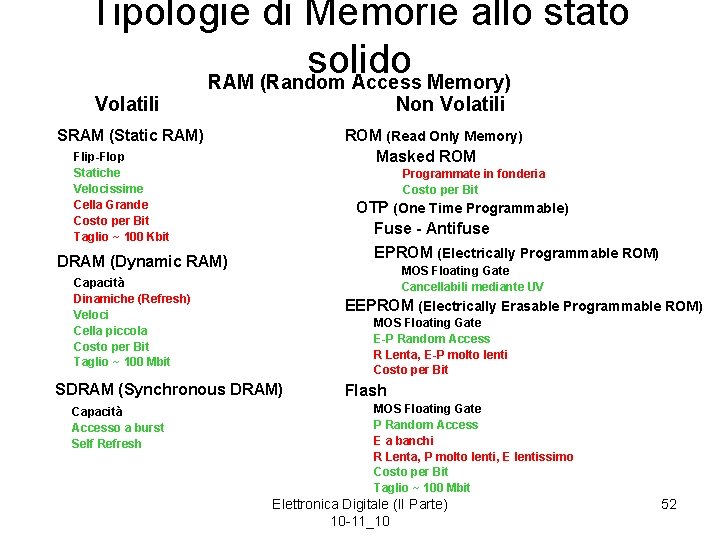

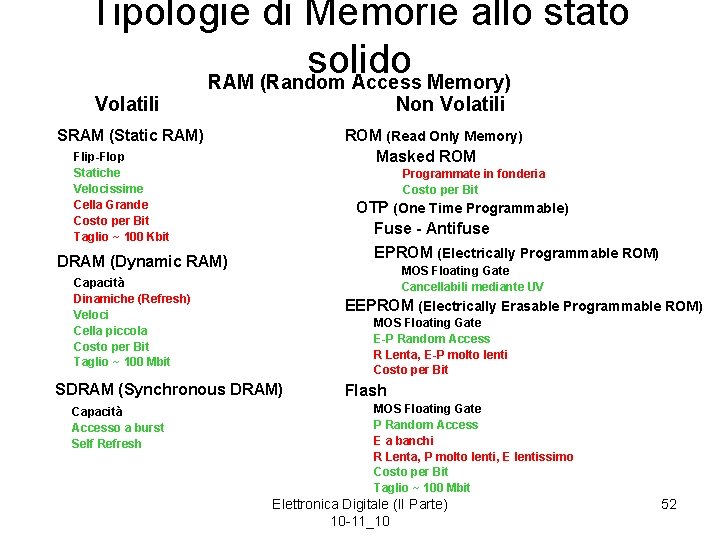

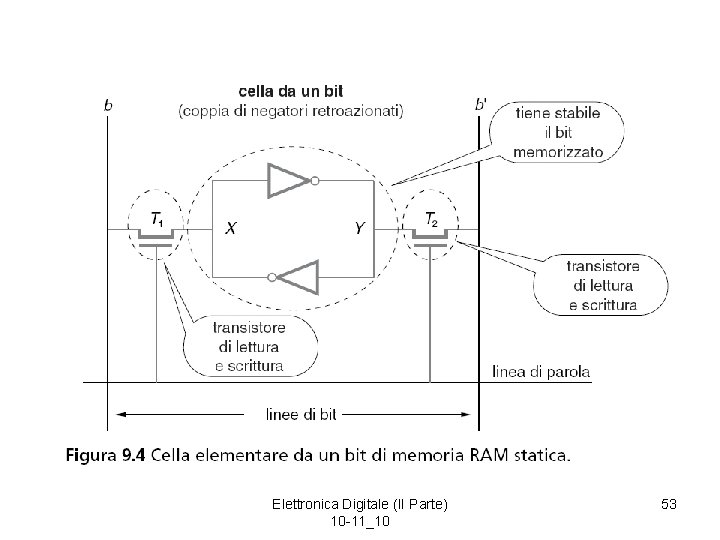

Tipologie di Memorie allo stato solido RAM (Random Access Memory) Volatili Non Volatili SRAM (Static RAM) ROM (Read Only Memory) Masked ROM Flip-Flop Statiche Velocissime Cella Grande Costo per Bit Taglio ~ 100 Kbit Programmate in fonderia Costo per Bit OTP (One Time Programmable) Fuse - Antifuse EPROM (Electrically Programmable ROM) DRAM (Dynamic RAM) MOS Floating Gate Cancellabili mediante UV Capacità Dinamiche (Refresh) Veloci Cella piccola Costo per Bit Taglio ~ 100 Mbit EEPROM (Electrically Erasable Programmable ROM) MOS Floating Gate E-P Random Access R Lenta, E-P molto lenti Costo per Bit SDRAM (Synchronous DRAM) Capacità Accesso a burst Self Refresh Flash MOS Floating Gate P Random Access E a banchi R Lenta, P molto lenti, E lentissimo Costo per Bit Taglio ~ 100 Mbit Elettronica Digitale (II Parte) 10 -11_10 52

Elettronica Digitale (II Parte) 10 -11_10 53

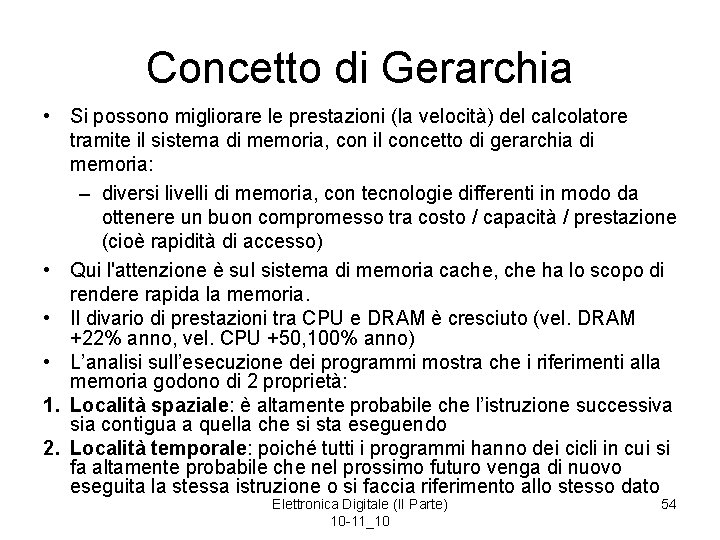

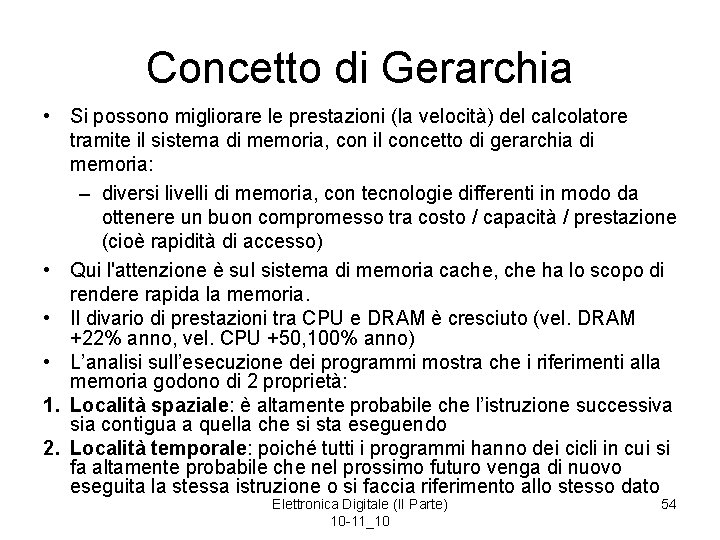

Concetto di Gerarchia • Si possono migliorare le prestazioni (la velocità) del calcolatore tramite il sistema di memoria, con il concetto di gerarchia di memoria: – diversi livelli di memoria, con tecnologie differenti in modo da ottenere un buon compromesso tra costo / capacità / prestazione (cioè rapidità di accesso) • Qui l'attenzione è sul sistema di memoria cache, che ha lo scopo di rendere rapida la memoria. • Il divario di prestazioni tra CPU e DRAM è cresciuto (vel. DRAM +22% anno, vel. CPU +50, 100% anno) • L’analisi sull’esecuzione dei programmi mostra che i riferimenti alla memoria godono di 2 proprietà: 1. Località spaziale: è altamente probabile che l’istruzione successiva sia contigua a quella che si sta eseguendo 2. Località temporale: poiché tutti i programmi hanno dei cicli in cui si fa altamente probabile che nel prossimo futuro venga di nuovo eseguita la stessa istruzione o si faccia riferimento allo stesso dato Elettronica Digitale (II Parte) 10 -11_10 54

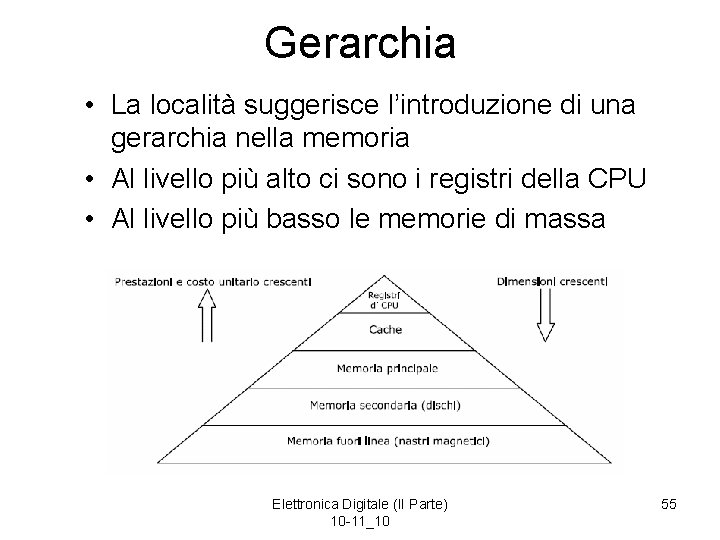

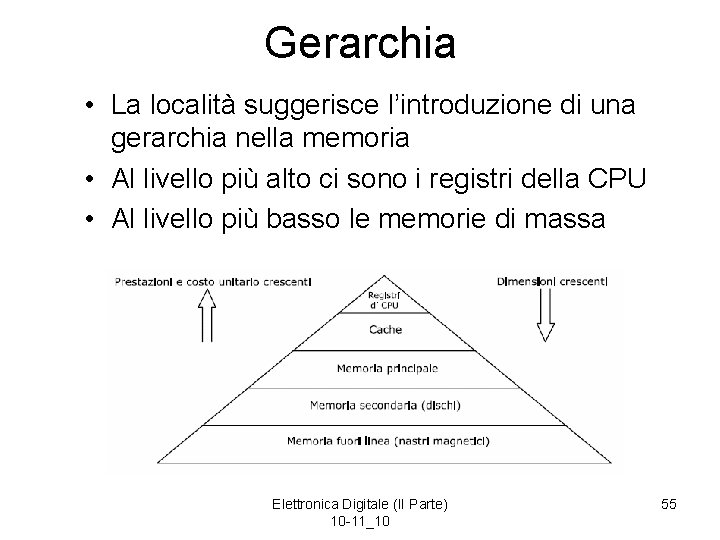

Gerarchia • La località suggerisce l’introduzione di una gerarchia nella memoria • Al livello più alto ci sono i registri della CPU • Al livello più basso le memorie di massa Elettronica Digitale (II Parte) 10 -11_10 55

Sistemi tecnologici Tre sottosistemi tecnologici: • registri interni del processore per dati e indirizzi dove lavorano correntemente le istruzioni: alta velocità bassa capacità • memoria primaria per programmi in esecuzione e dati in elaborazione corrente: serie di tecnologie, tutte elettroniche, veloci, capaci, volatili • memoria secondaria per programmi e dati in deposito permanente o di uso differito: tecnologie, magnetiche od ottiche, lente, molto capaci, persistenti (ma di basso costo per bit memorizzato) Elettronica Digitale (II Parte) 10 -11_10 56

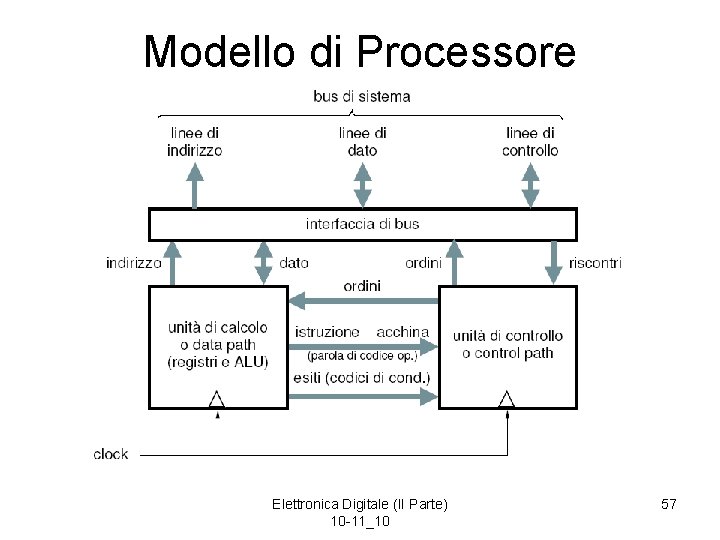

Modello di Processore Elettronica Digitale (II Parte) 10 -11_10 57

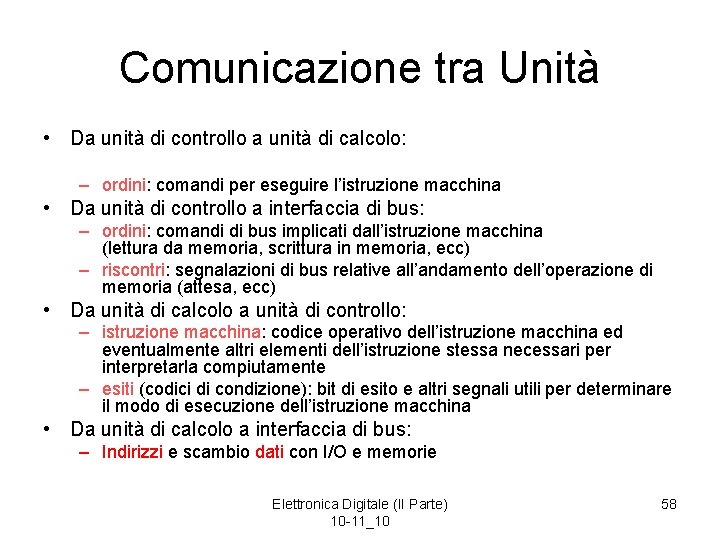

Comunicazione tra Unità • Da unità di controllo a unità di calcolo: – ordini: comandi per eseguire l’istruzione macchina • Da unità di controllo a interfaccia di bus: – ordini: comandi di bus implicati dall’istruzione macchina (lettura da memoria, scrittura in memoria, ecc) – riscontri: segnalazioni di bus relative all’andamento dell’operazione di memoria (attesa, ecc) • Da unità di calcolo a unità di controllo: – istruzione macchina: codice operativo dell’istruzione macchina ed eventualmente altri elementi dell’istruzione stessa necessari per interpretarla compiutamente – esiti (codici di condizione): bit di esito e altri segnali utili per determinare il modo di esecuzione dell’istruzione macchina • Da unità di calcolo a interfaccia di bus: – Indirizzi e scambio dati con I/O e memorie Elettronica Digitale (II Parte) 10 -11_10 58

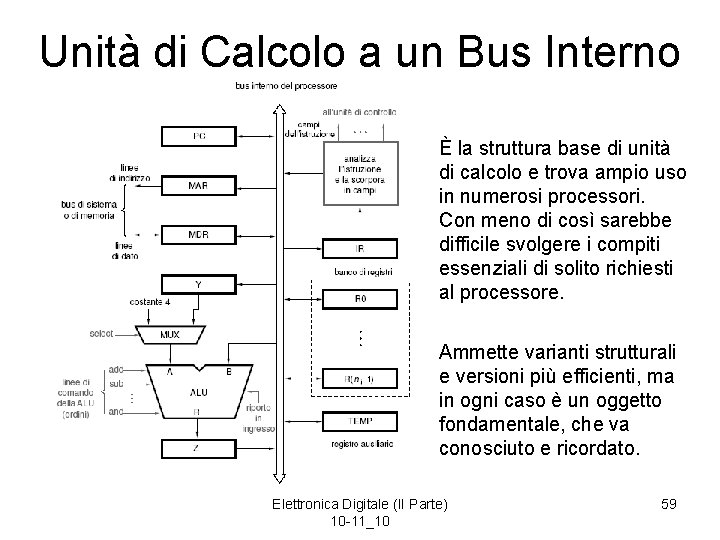

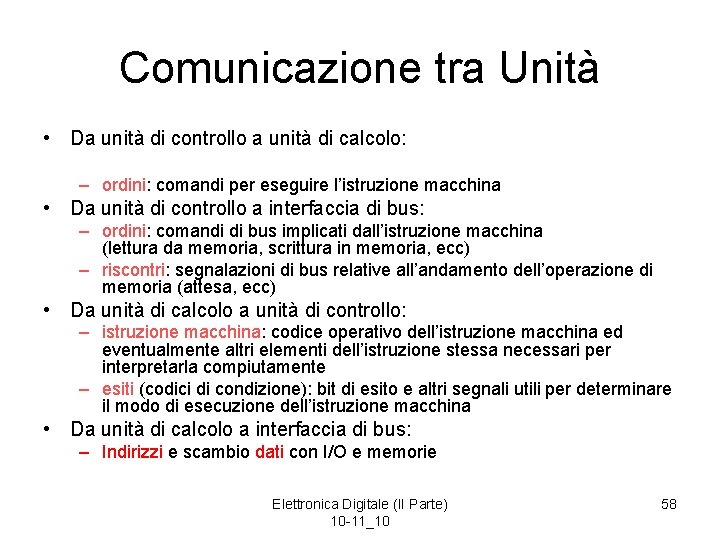

Unità di Calcolo a un Bus Interno È la struttura base di unità di calcolo e trova ampio uso in numerosi processori. Con meno di così sarebbe difficile svolgere i compiti essenziali di solito richiesti al processore. Ammette varianti strutturali e versioni più efficienti, ma in ogni caso è un oggetto fondamentale, che va conosciuto e ricordato. Elettronica Digitale (II Parte) 10 -11_10 59

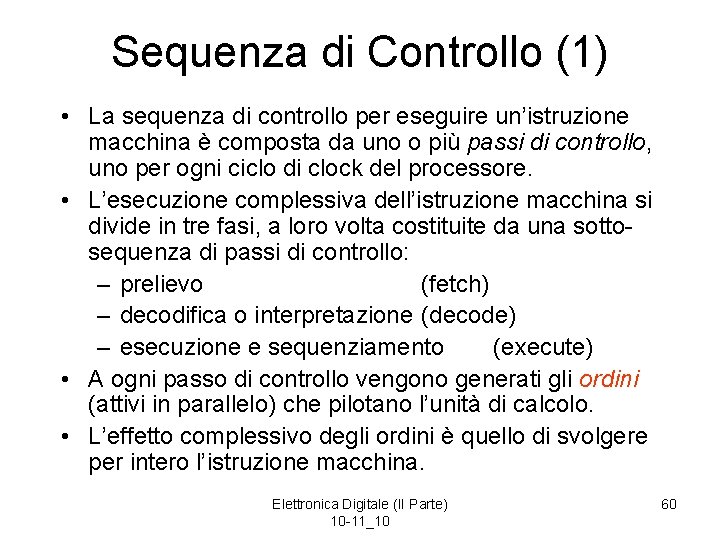

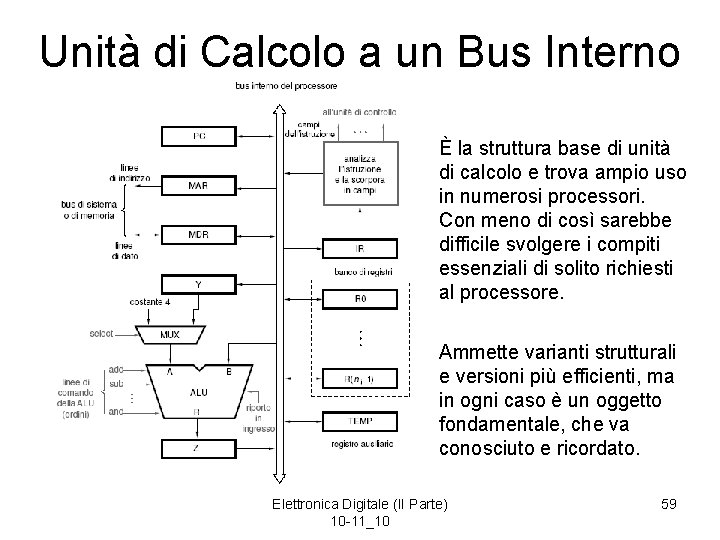

Sequenza di Controllo (1) • La sequenza di controllo per eseguire un’istruzione macchina è composta da uno o più passi di controllo, uno per ogni ciclo di clock del processore. • L’esecuzione complessiva dell’istruzione macchina si divide in tre fasi, a loro volta costituite da una sottosequenza di passi di controllo: – prelievo (fetch) – decodifica o interpretazione (decode) – esecuzione e sequenziamento (execute) • A ogni passo di controllo vengono generati gli ordini (attivi in parallelo) che pilotano l’unità di calcolo. • L’effetto complessivo degli ordini è quello di svolgere per intero l’istruzione macchina. Elettronica Digitale (II Parte) 10 -11_10 60

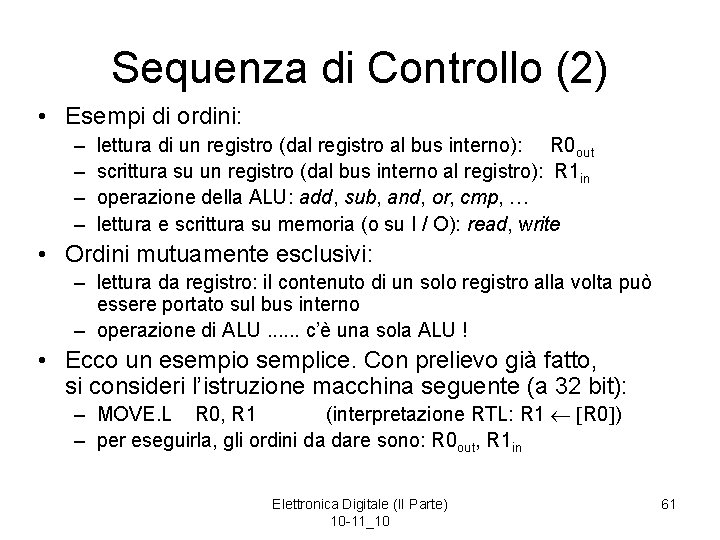

Sequenza di Controllo (2) • Esempi di ordini: – – lettura di un registro (dal registro al bus interno): R 0 out scrittura su un registro (dal bus interno al registro): R 1 in operazione della ALU: add, sub, and, or, cmp, … lettura e scrittura su memoria (o su I / O): read, write • Ordini mutuamente esclusivi: – lettura da registro: il contenuto di un solo registro alla volta può essere portato sul bus interno – operazione di ALU. . . c’è una sola ALU ! • Ecco un esempio semplice. Con prelievo già fatto, si consideri l’istruzione macchina seguente (a 32 bit): – MOVE. L R 0, R 1 (interpretazione RTL: R 1 R 0 ) – per eseguirla, gli ordini da dare sono: R 0 out, R 1 in Elettronica Digitale (II Parte) 10 -11_10 61

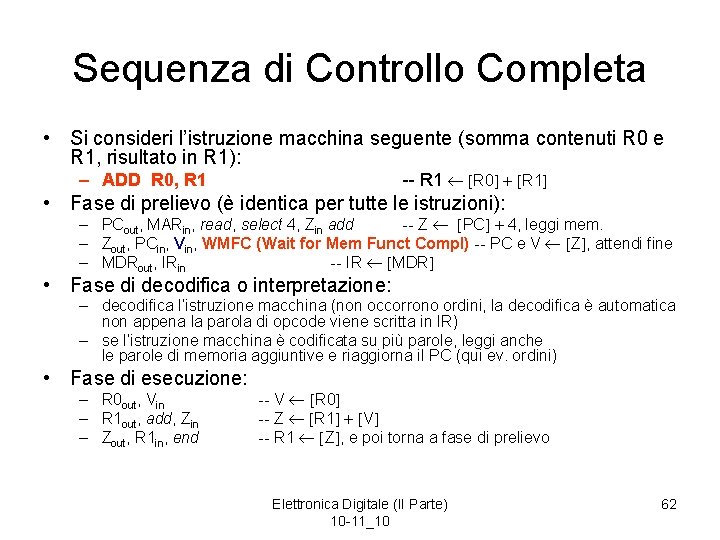

Sequenza di Controllo Completa • Si consideri l’istruzione macchina seguente (somma contenuti R 0 e R 1, risultato in R 1): – ADD R 0, R 1 -- R 1 R 0 R 1 • Fase di prelievo (è identica per tutte le istruzioni): – PCout, MARin, read, select 4, Zin add -- Z PC 4, leggi mem. – Zout, PCin, Vin, WMFC (Wait for Mem Funct Compl) -- PC e V Z , attendi fine – MDRout, IRin -- IR MDR • Fase di decodifica o interpretazione: – decodifica l’istruzione macchina (non occorrono ordini, la decodifica è automatica non appena la parola di opcode viene scritta in IR) – se l’istruzione macchina è codificata su più parole, leggi anche le parole di memoria aggiuntive e riaggiorna il PC (qui ev. ordini) • Fase di esecuzione: – R 0 out, Vin – R 1 out, add, Zin – Zout, R 1 in, end -- V R 0 -- Z R 1 V -- R 1 Z , e poi torna a fase di prelievo Elettronica Digitale (II Parte) 10 -11_10 62

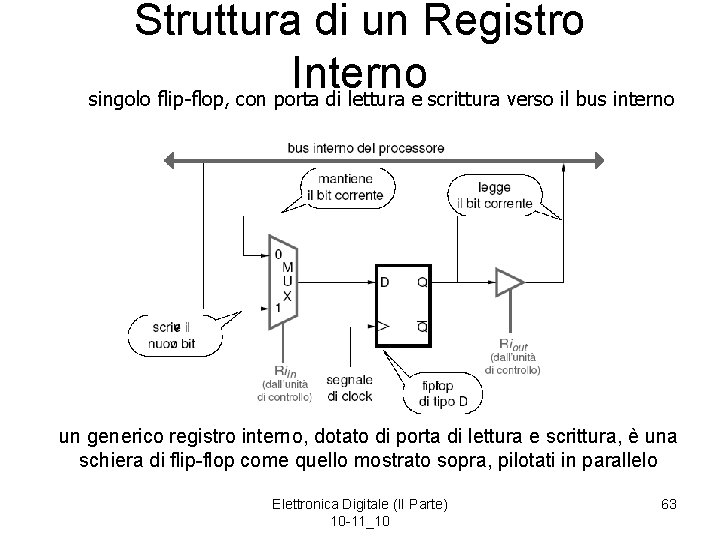

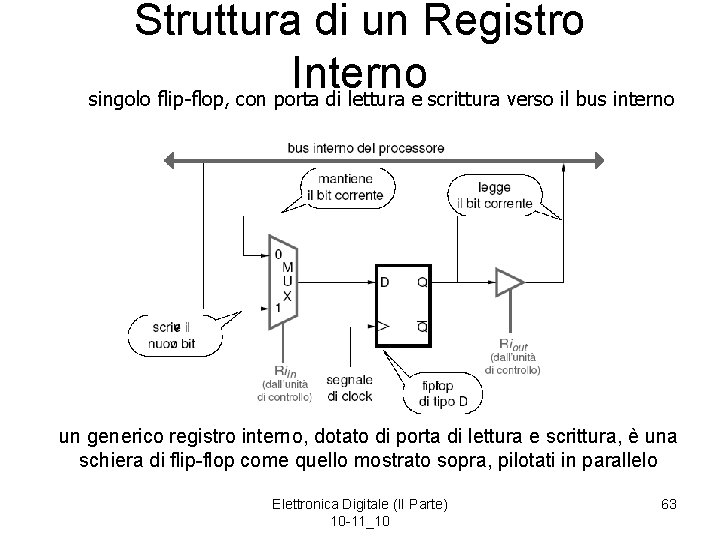

Struttura di un Registro Interno singolo flip-flop, con porta di lettura e scrittura verso il bus interno un generico registro interno, dotato di porta di lettura e scrittura, è una schiera di flip-flop come quello mostrato sopra, pilotati in parallelo Elettronica Digitale (II Parte) 10 -11_10 63

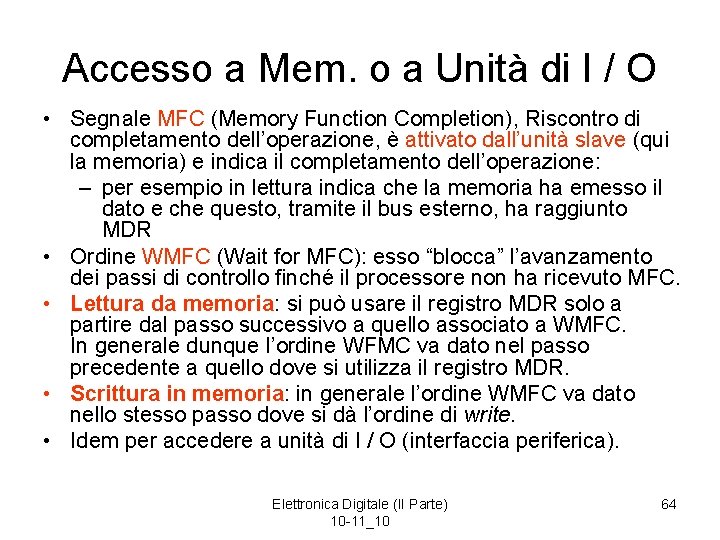

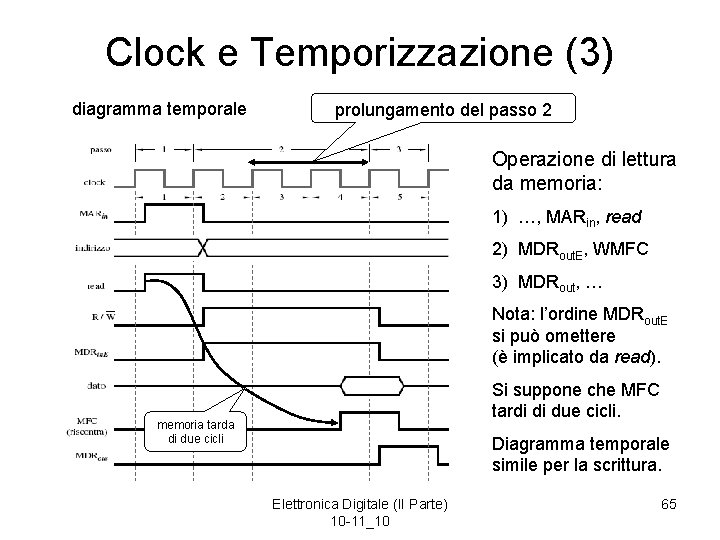

Accesso a Mem. o a Unità di I / O • Segnale MFC (Memory Function Completion), Riscontro di completamento dell’operazione, è attivato dall’unità slave (qui la memoria) e indica il completamento dell’operazione: – per esempio in lettura indica che la memoria ha emesso il dato e che questo, tramite il bus esterno, ha raggiunto MDR • Ordine WMFC (Wait for MFC): esso “blocca” l’avanzamento dei passi di controllo finché il processore non ha ricevuto MFC. • Lettura da memoria: si può usare il registro MDR solo a partire dal passo successivo a quello associato a WMFC. In generale dunque l’ordine WFMC va dato nel passo precedente a quello dove si utilizza il registro MDR. • Scrittura in memoria: in generale l’ordine WMFC va dato nello stesso passo dove si dà l’ordine di write. • Idem per accedere a unità di I / O (interfaccia periferica). Elettronica Digitale (II Parte) 10 -11_10 64

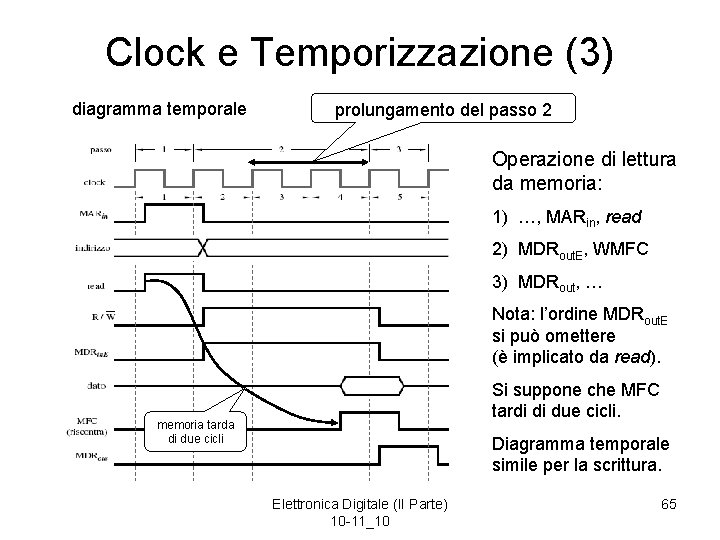

Clock e Temporizzazione (3) diagramma temporale prolungamento del passo 2 Operazione di lettura da memoria: 1) …, MARin, read 2) MDRout. E, WMFC 3) MDRout, … Nota: l’ordine MDRout. E si può omettere (è implicato da read). Si suppone che MFC tardi di due cicli. memoria tarda di due cicli Diagramma temporale simile per la scrittura. Elettronica Digitale (II Parte) 10 -11_10 65

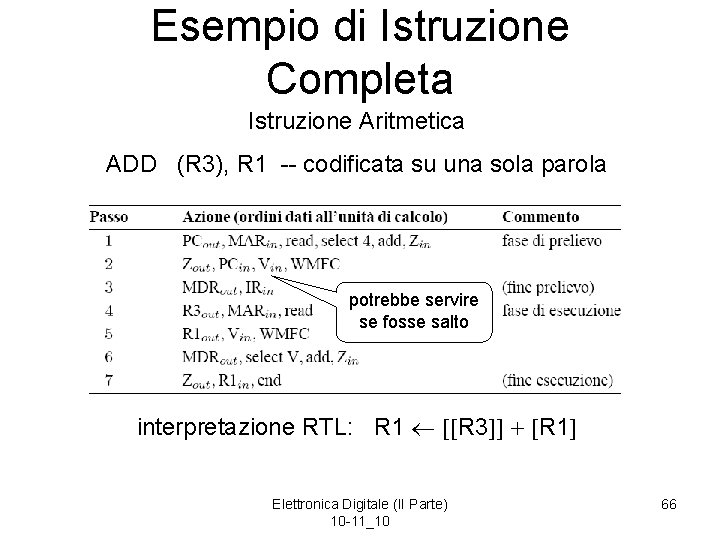

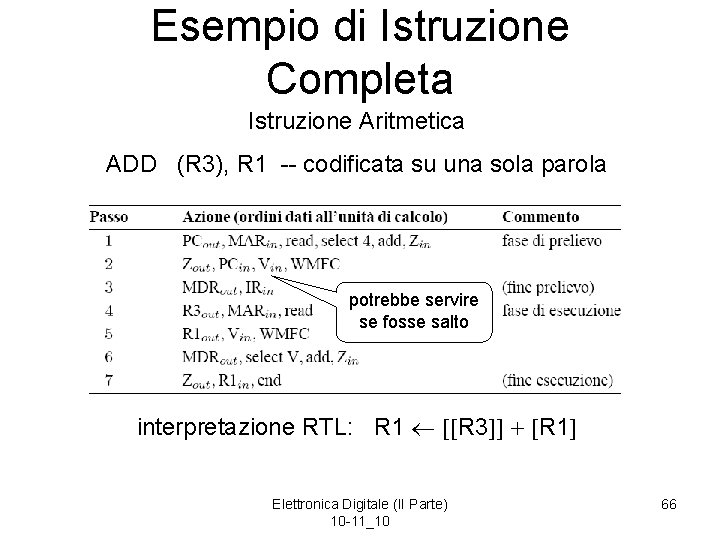

Esempio di Istruzione Completa Istruzione Aritmetica ADD (R 3), R 1 -- codificata su una sola parola potrebbe servire se fosse salto interpretazione RTL: R 1 R 3 R 1 Elettronica Digitale (II Parte) 10 -11_10 66

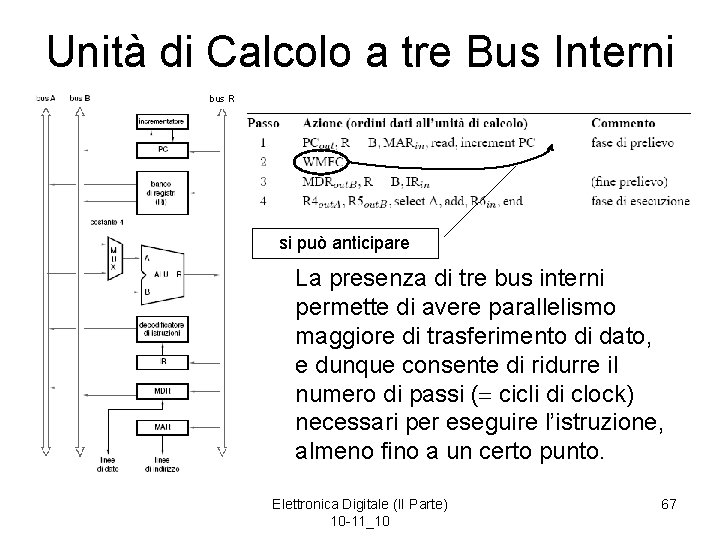

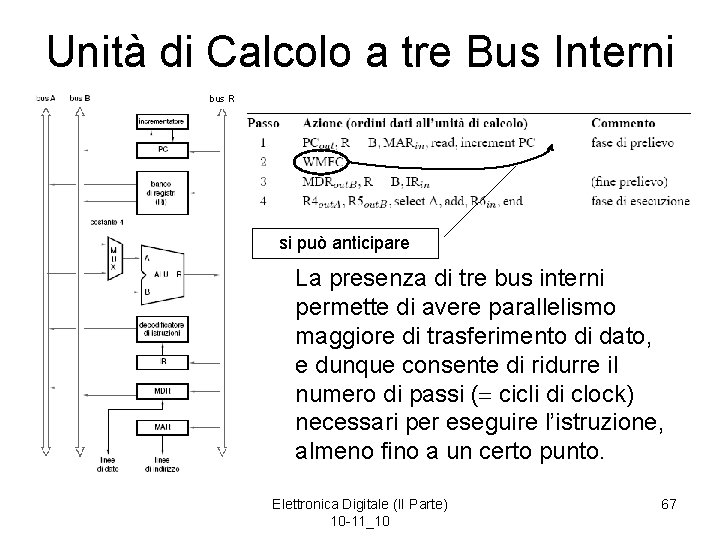

Unità di Calcolo a tre Bus Interni bus R si può anticipare La presenza di tre bus interni permette di avere parallelismo maggiore di trasferimento di dato, e dunque consente di ridurre il numero di passi ( cicli di clock) necessari per eseguire l’istruzione, almeno fino a un certo punto. Elettronica Digitale (II Parte) 10 -11_10 67

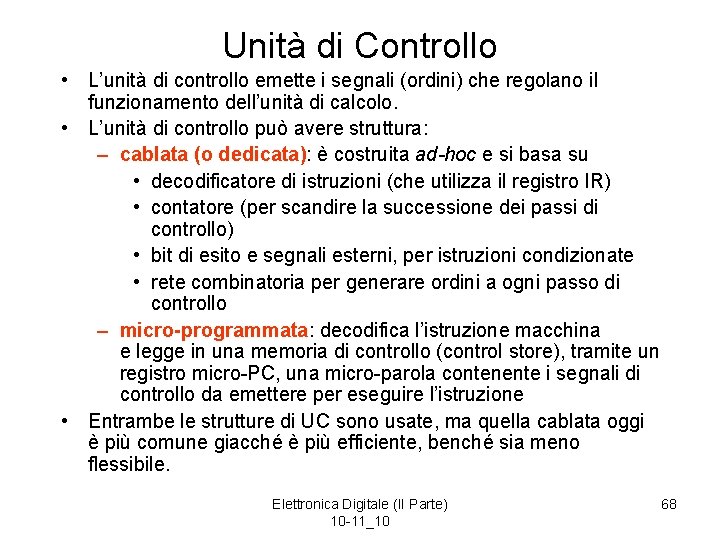

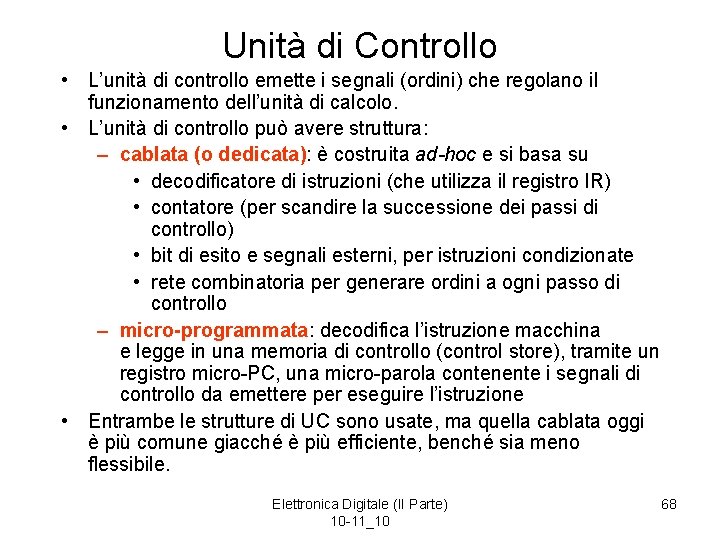

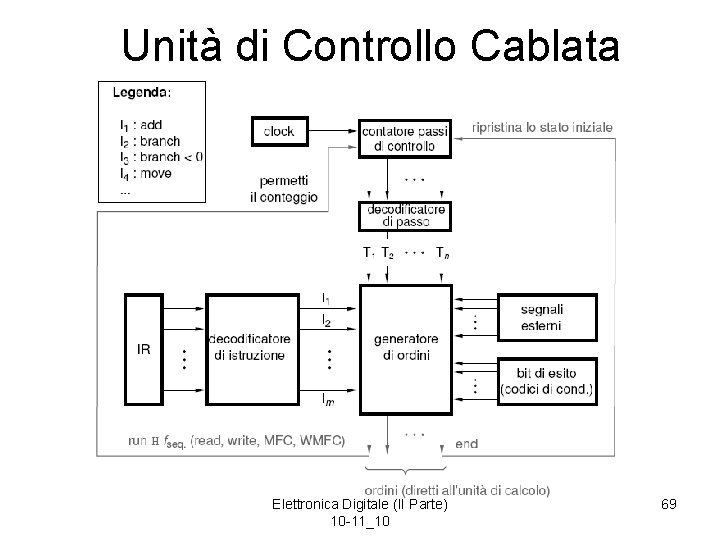

Unità di Controllo • L’unità di controllo emette i segnali (ordini) che regolano il funzionamento dell’unità di calcolo. • L’unità di controllo può avere struttura: – cablata (o dedicata): è costruita ad-hoc e si basa su • decodificatore di istruzioni (che utilizza il registro IR) • contatore (per scandire la successione dei passi di controllo) • bit di esito e segnali esterni, per istruzioni condizionate • rete combinatoria per generare ordini a ogni passo di controllo – micro-programmata: decodifica l’istruzione macchina e legge in una memoria di controllo (control store), tramite un registro micro-PC, una micro-parola contenente i segnali di controllo da emettere per eseguire l’istruzione • Entrambe le strutture di UC sono usate, ma quella cablata oggi è più comune giacché è più efficiente, benché sia meno flessibile. Elettronica Digitale (II Parte) 10 -11_10 68

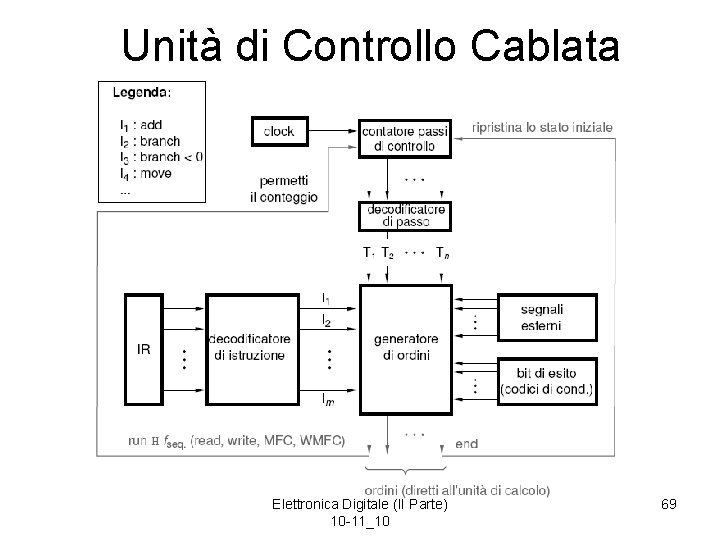

Unità di Controllo Cablata Elettronica Digitale (II Parte) 10 -11_10 69

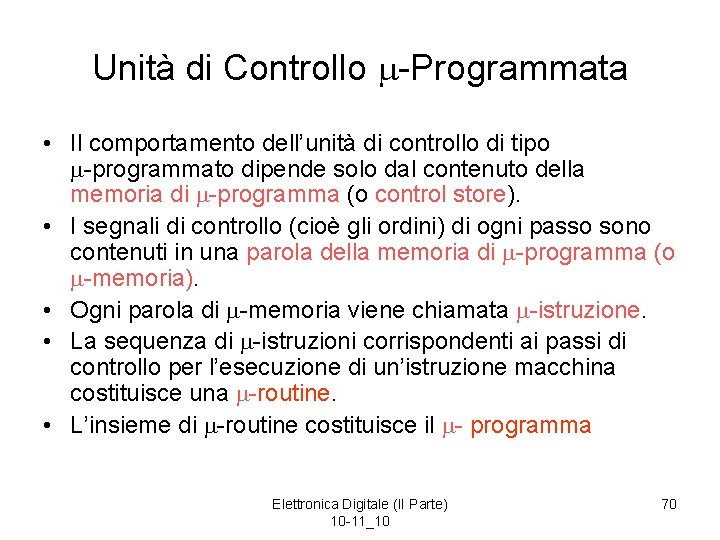

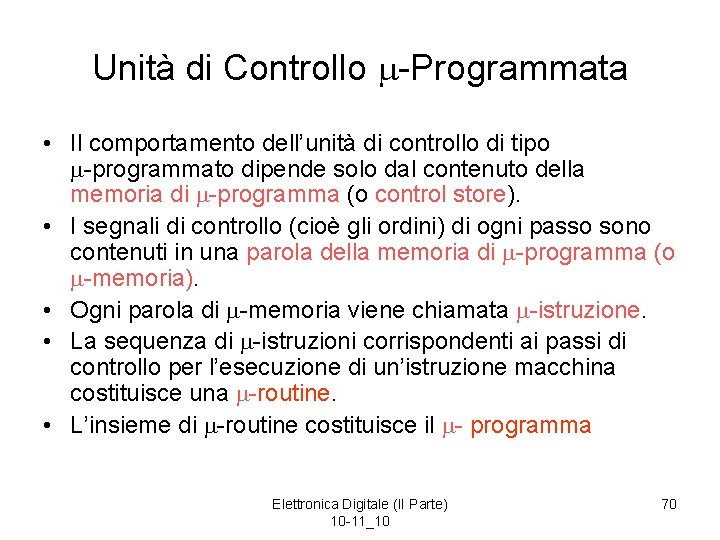

Unità di Controllo -Programmata • Il comportamento dell’unità di controllo di tipo -programmato dipende solo dal contenuto della memoria di -programma (o control store). • I segnali di controllo (cioè gli ordini) di ogni passo sono contenuti in una parola della memoria di -programma (o -memoria). • Ogni parola di -memoria viene chiamata -istruzione. • La sequenza di -istruzioni corrispondenti ai passi di controllo per l’esecuzione di un’istruzione macchina costituisce una -routine. • L’insieme di -routine costituisce il - programma Elettronica Digitale (II Parte) 10 -11_10 70

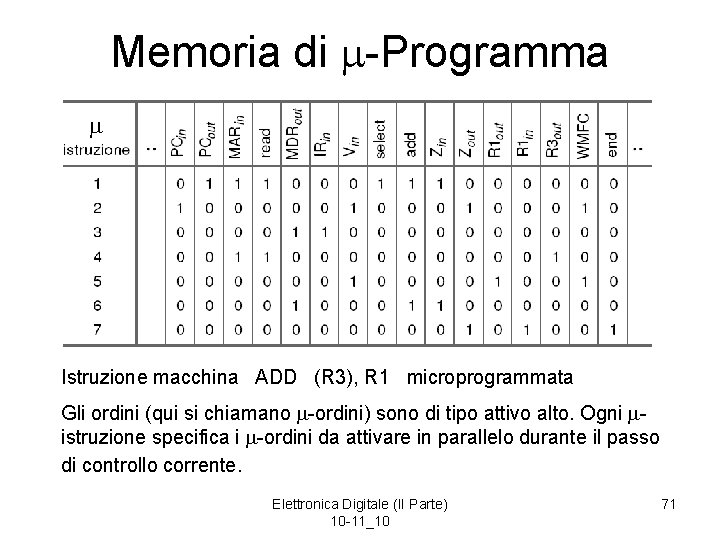

Memoria di -Programma Istruzione macchina ADD (R 3), R 1 microprogrammata Gli ordini (qui si chiamano -ordini) sono di tipo attivo alto. Ogni istruzione specifica i -ordini da attivare in parallelo durante il passo di controllo corrente. Elettronica Digitale (II Parte) 10 -11_10 71

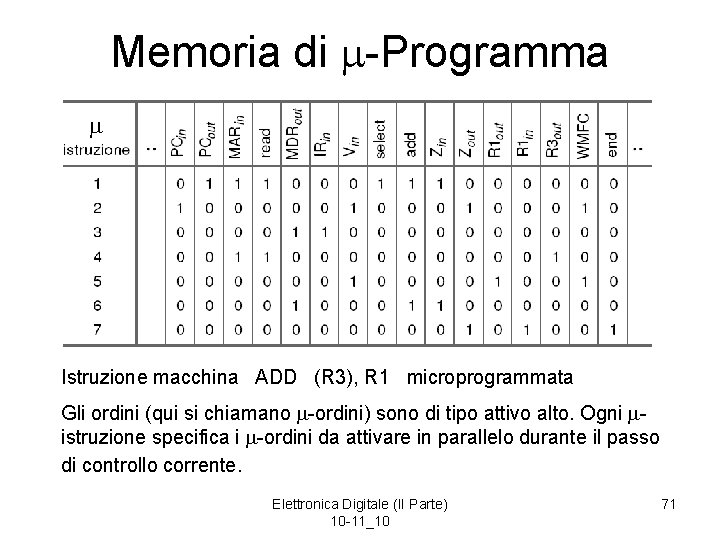

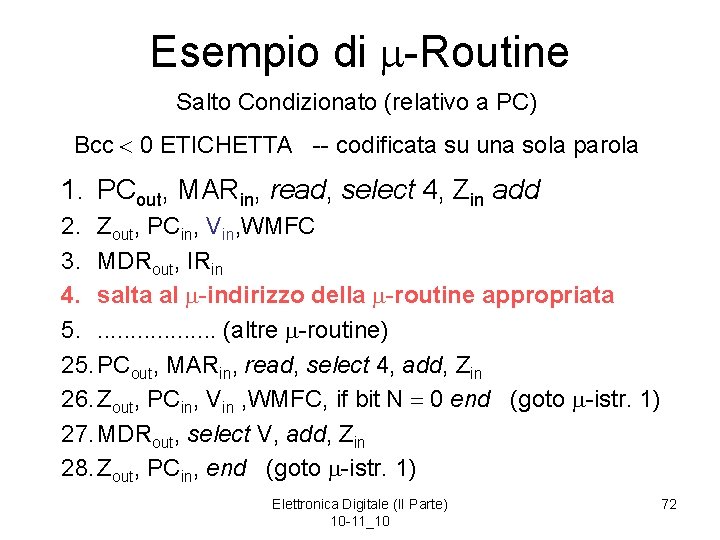

Esempio di -Routine Salto Condizionato (relativo a PC) Bcc 0 ETICHETTA -- codificata su una sola parola 1. PCout, MARin, read, select 4, Zin add 2. Zout, PCin, Vin, WMFC 3. MDRout, IRin 4. salta al -indirizzo della -routine appropriata 5. . . . . (altre -routine) 25. PCout, MARin, read, select 4, add, Zin 26. Zout, PCin, Vin , WMFC, if bit N 0 end (goto -istr. 1) 27. MDRout, select V, add, Zin 28. Zout, PCin, end (goto -istr. 1) Elettronica Digitale (II Parte) 10 -11_10 72

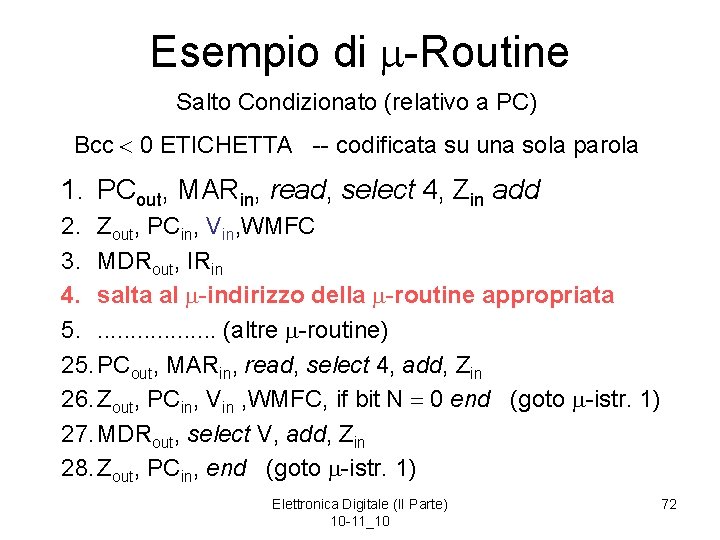

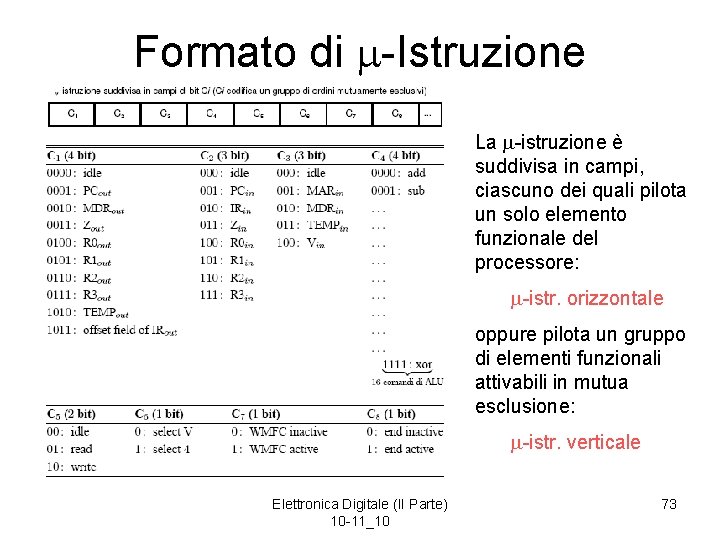

Formato di -Istruzione La -istruzione è suddivisa in campi, ciascuno dei quali pilota un solo elemento funzionale del processore: -istr. orizzontale oppure pilota un gruppo di elementi funzionali attivabili in mutua esclusione: -istr. verticale Elettronica Digitale (II Parte) 10 -11_10 73

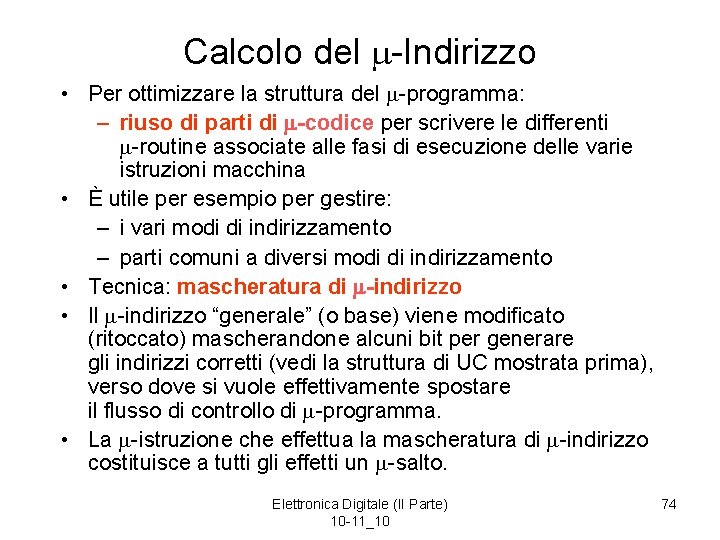

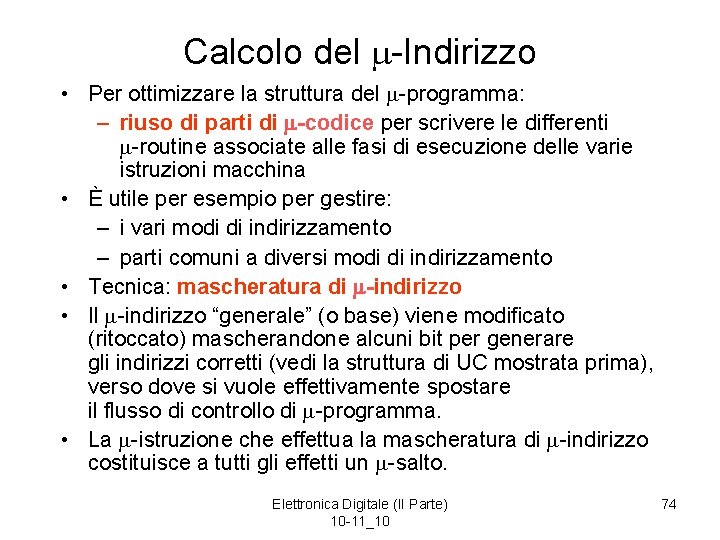

Calcolo del -Indirizzo • Per ottimizzare la struttura del -programma: – riuso di parti di -codice per scrivere le differenti -routine associate alle fasi di esecuzione delle varie istruzioni macchina • È utile per esempio per gestire: – i vari modi di indirizzamento – parti comuni a diversi modi di indirizzamento • Tecnica: mascheratura di -indirizzo • Il -indirizzo “generale” (o base) viene modificato (ritoccato) mascherandone alcuni bit per generare gli indirizzi corretti (vedi la struttura di UC mostrata prima), verso dove si vuole effettivamente spostare il flusso di controllo di -programma. • La -istruzione che effettua la mascheratura di -indirizzo costituisce a tutti gli effetti un -salto. Elettronica Digitale (II Parte) 10 -11_10 74

Elettronica Digitale (II Parte) 10 -11_10 75