EE 4271 VLSI Design Professor Shiyan Hu Office

- Slides: 37

EE 4271 VLSI Design Professor Shiyan Hu Office: EERC 518 shiyan@mtu. edu Introduction Adapted and modified from Digital Integrated Circuits: A Design Perspective by Jan M. Rabaey, Anantha Chandrakasan, and Borivoje Nikolic. © EE 141 Digital Integrated Circuits 2 nd 1 Introduction

Class Time and Office Hour q q q Class Time: MWF 16: 05 -16: 55 (EERC 214) Office Hours: MWF 15: 00 -16: 00 or by appointment, office: EERC 518 Textbook (required): Digital Integrated Circuits: A Design Perspective, second edition, by Jan M. Rabaey, Anantha Chandrakasan and Borivoje Nikolic, Prentice Hall, 2003. or CMOS VLSI Design: A Circuits and Systems Perspective, fourth edition, by Neil H. E. Weste and David M. Harris, Addiuson Wesley, 2009 Grading: § § Homework 20% Midterm 20% Final 30% Lab 30% © EE 141 Digital Integrated Circuits 2 nd 2 Introduction

Course Website q q http: //www. ece. mtu. edu/faculty/shiyan/EE 4271 Fall 16. htm Contact information of instructor § § Professor Shiyan Hu Email: shiyan@mtu. edu EERC 518 Instructor’s webpage: http: //www. ece. mtu. edu/faculty/shiyan © EE 141 Digital Integrated Circuits 2 nd 3 Introduction

What is this course all about? q Introduction to digital integrated circuits. § CMOS devices and manufacturing technology. CMOS inverters and gates. Propagation delay, noise margins, and power dissipation. Combinatorial Circuits and Sequential circuits. Computer-Aided Design. q What will you learn? § Understanding, designing, and optimizing digital circuits with respect to different quality metrics: speed, power dissipation, cost, and reliability © EE 141 Digital Integrated Circuits 2 nd 4 Introduction

Agenda q q q q q Introduction: Issues in digital integrated circuit (IC) design Device: MOS Transistors Wire: R, L and C Fabrication process CMOS inverter Combinational logic structures Sequential logic gates Design methodologies VLSI Computer-Aided Design Timing/power optimizations on gate and interconnect © EE 141 Digital Integrated Circuits 2 nd 5 Introduction

Introduction q Why is designing digital ICs different today than it was before? q What is the challenge? © EE 141 Digital Integrated Circuits 2 nd 6 Introduction

The Transistor Revolution First transistor Bell Labs, 1948 © EE 141 Digital Integrated Circuits 2 nd Introduction

The First Integrated Circuit First IC Jack Kilby Texas Instruments 1958 © EE 141 Digital Integrated Circuits 2 nd Introduction

Intel 4004 Micro-Processor 1971 1000 transistors 1 MHz operation © EE 141 Digital Integrated Circuits 2 nd 9 Introduction

Intel 8080 Micro-Processor 1974 4500 transistors © EE 141 Digital Integrated Circuits 2 nd Introduction

Intel Pentium (IV) microprocessor 2000 42 million transistors 1. 5 GHz © EE 141 Digital Integrated Circuits 2 nd 11 Introduction

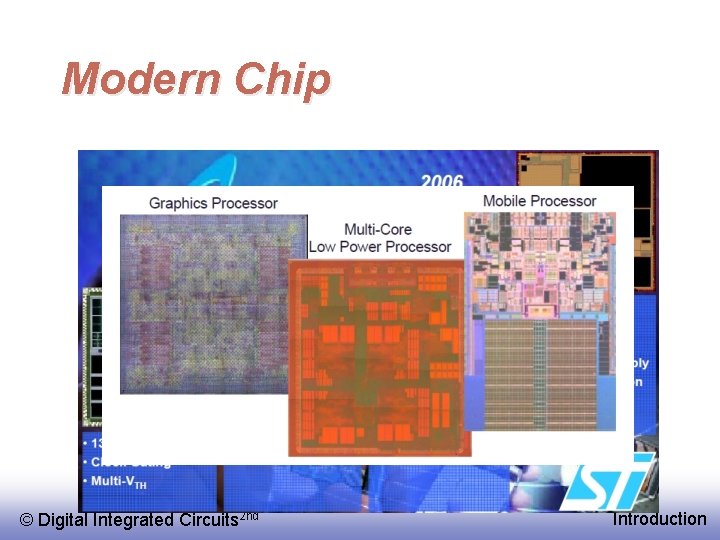

Modern Chip © EE 141 Digital Integrated Circuits 2 nd Introduction

Moore’s Law l. In 1965, Gordon Moore noted that the number of transistors on a chip doubled every 18 to 24 months. © EE 141 Digital Integrated Circuits 2 nd 13 Introduction

Moore’s law Twice the number of transistors, approximately every two years © EE 141 Digital Integrated Circuits 2 nd Introduction

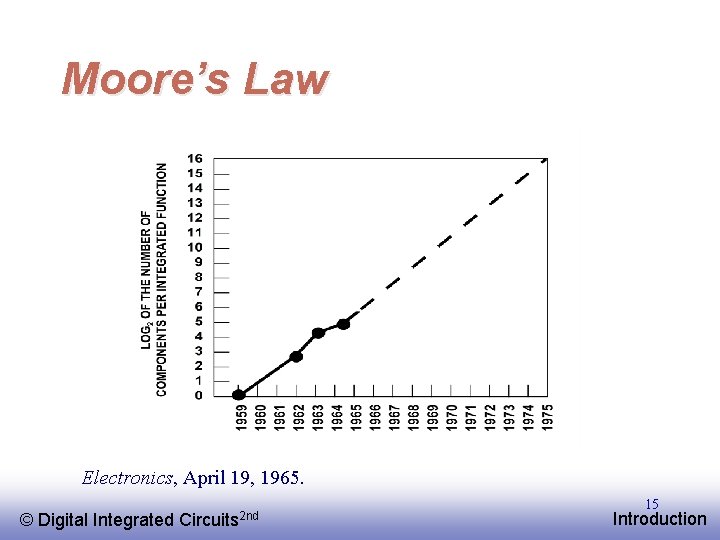

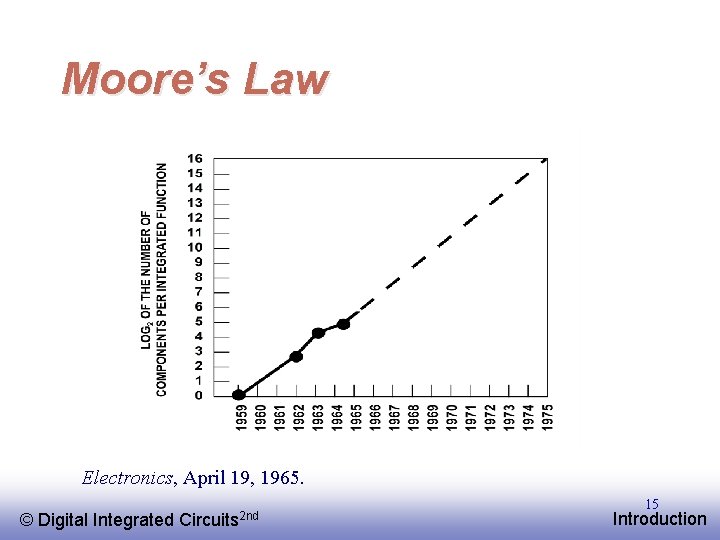

Moore’s Law Electronics, April 19, 1965. © EE 141 Digital Integrated Circuits 2 nd 15 Introduction

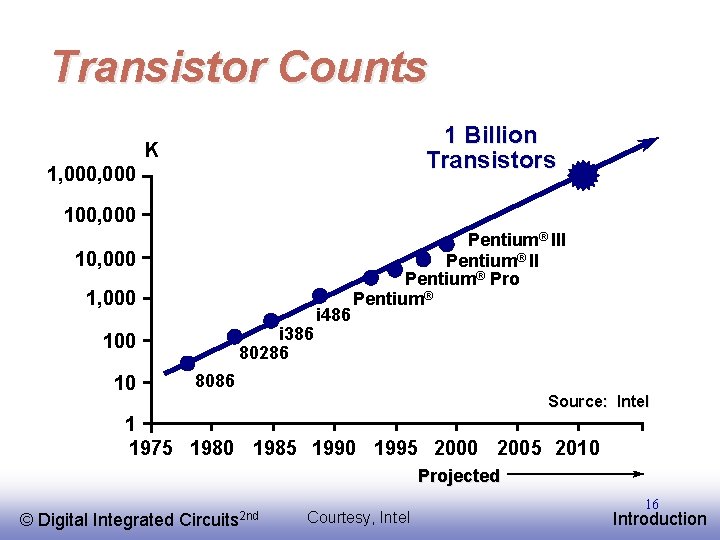

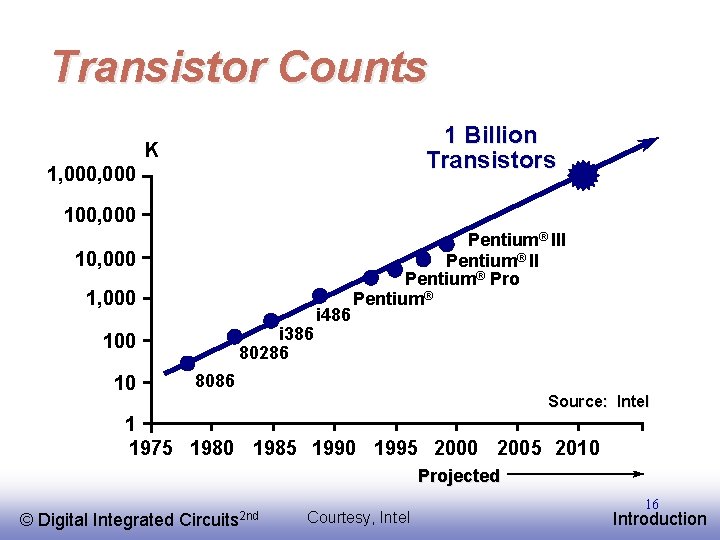

Transistor Counts 1 Billion Transistors K 1, 000 100, 000 1, 000 i 386 80286 100 10 i 486 Pentium® III Pentium® Pro Pentium® 8086 Source: Intel 1 1975 1980 1985 1990 1995 2000 2005 2010 Projected © EE 141 Digital Integrated Circuits 2 nd Courtesy, Intel 16 Introduction

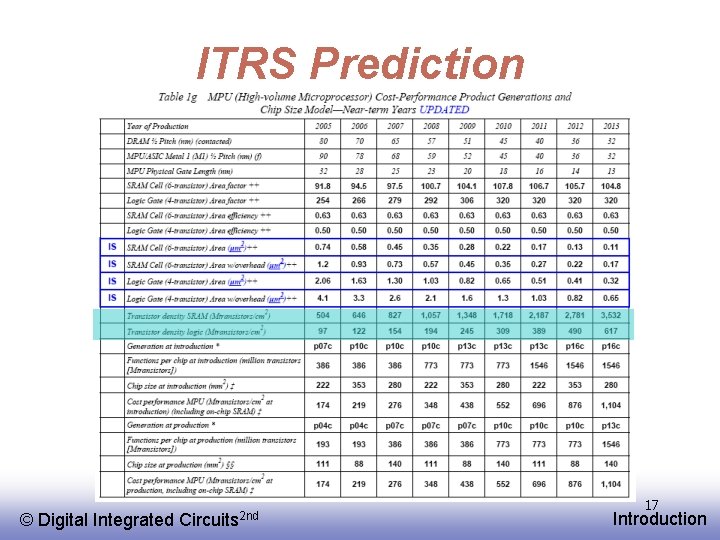

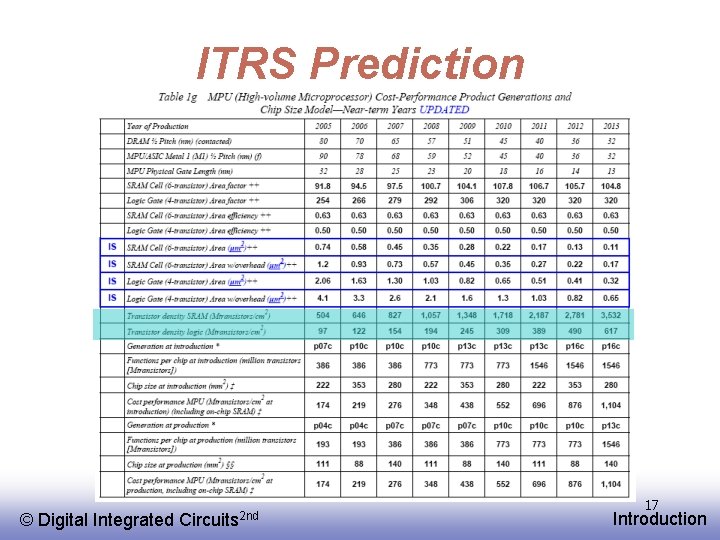

ITRS Prediction © EE 141 Digital Integrated Circuits 2 nd 17 Introduction

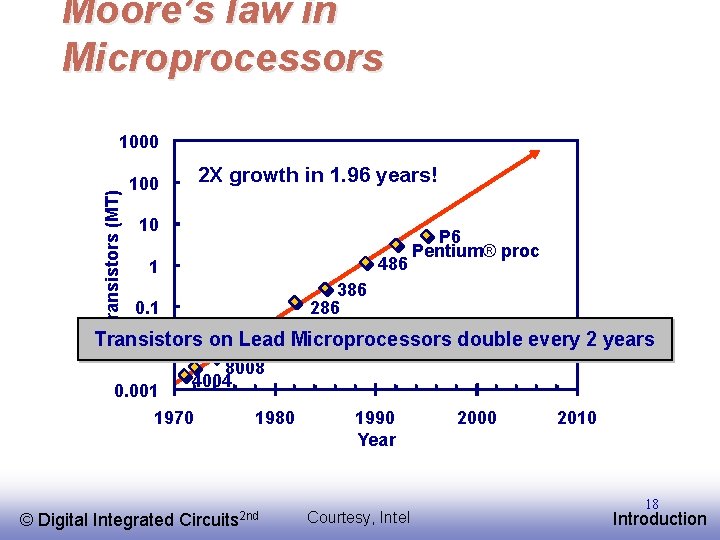

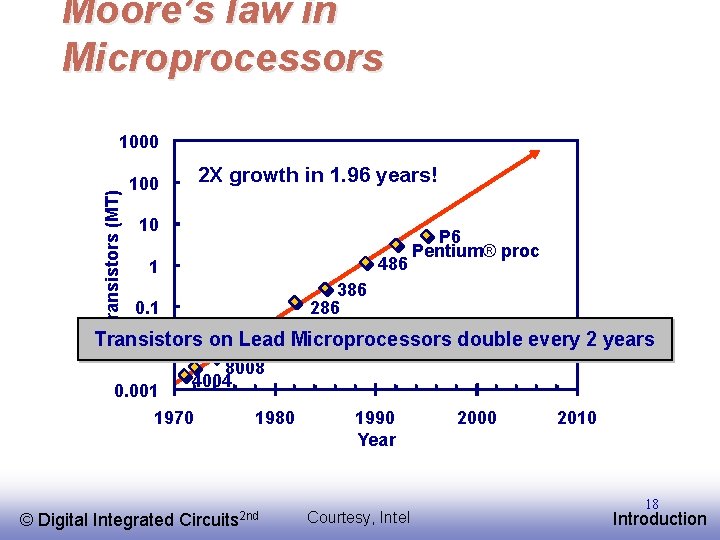

Moore’s law in Microprocessors Transistors (MT) 1000 2 X growth in 1. 96 years! 100 10 486 1 P 6 Pentium® proc 386 286 0. 1 8086 8080 8008 4004 8085 Transistors on Lead Microprocessors double every 2 years 0. 01 0. 001 1970 © EE 141 Digital Integrated 1980 Circuits 2 nd 1990 Year Courtesy, Intel 2000 2010 18 Introduction

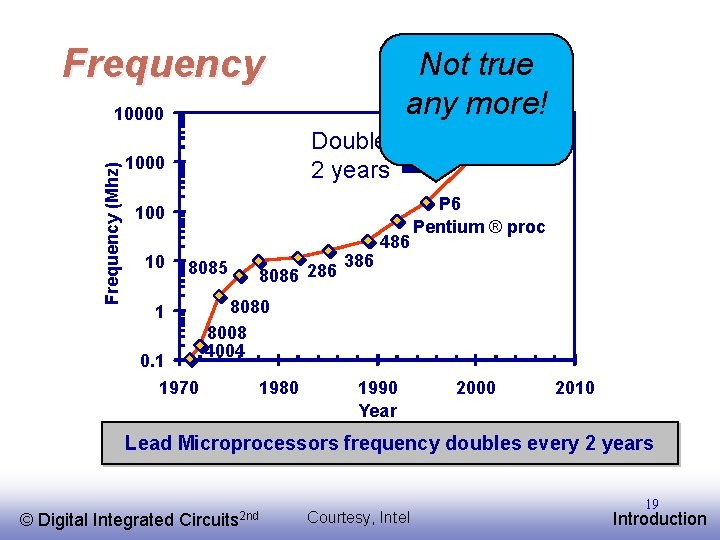

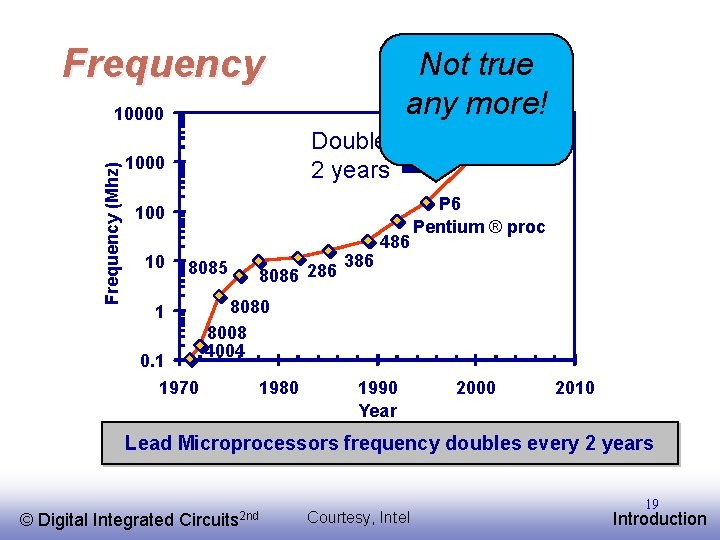

Frequency Not true any more! Frequency (Mhz) 10000 Doubles every 2 years 1000 10 8085 1 0. 1 1970 8086 286 386 486 P 6 Pentium ® proc 8080 8008 4004 1980 1990 Year 2000 2010 Lead Microprocessors frequency doubles every 2 years © EE 141 Digital Integrated Circuits 2 nd Courtesy, Intel 19 Introduction

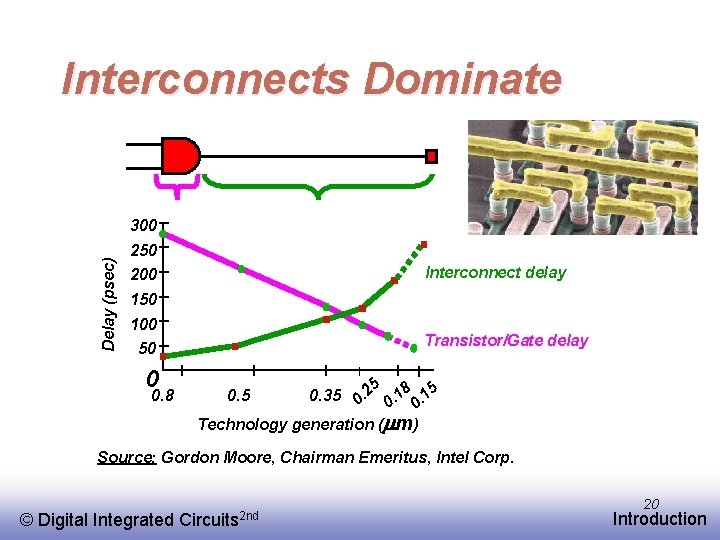

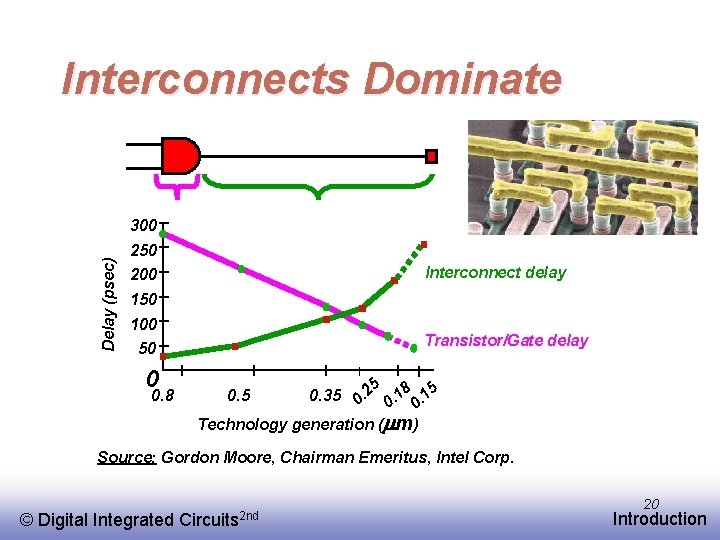

Interconnects Dominate Delay (psec) 300 250 Interconnect delay 200 150 100 Transistor/Gate delay 50 0 0. 8 25. 18. 15. 0. 35 0. 25 0 0 0 Technology generation ( m) 0. 5 Source: Gordon Moore, Chairman Emeritus, Intel Corp. © EE 141 Digital Integrated Circuits 2 nd 20 Introduction

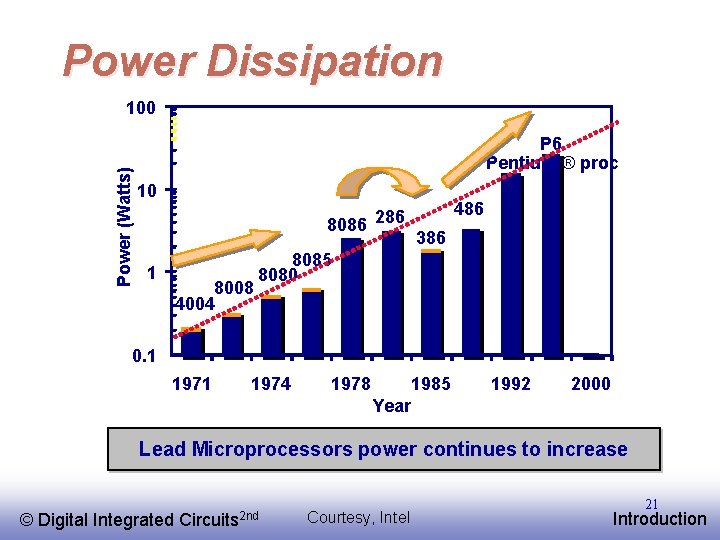

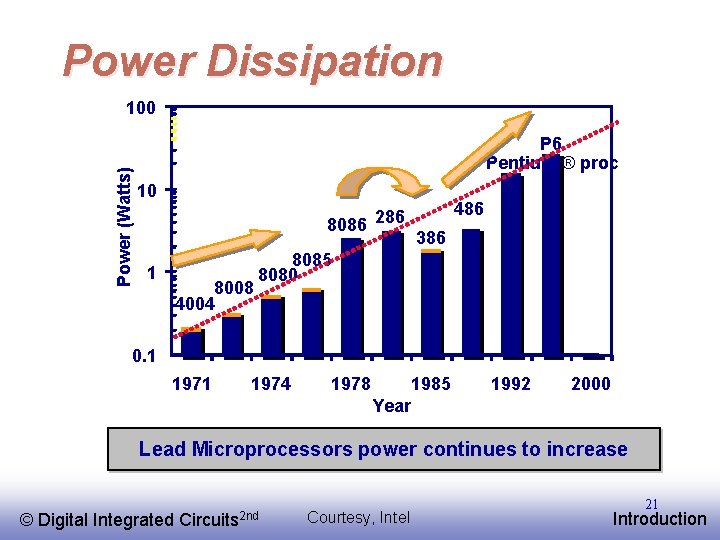

Power Dissipation Power (Watts) 100 P 6 Pentium ® proc 10 8086 286 1 8008 4004 486 386 8085 8080 0. 1 1974 1978 1985 1992 2000 Year Lead Microprocessors power continues to increase © EE 141 Digital Integrated Circuits 2 nd Courtesy, Intel 21 Introduction

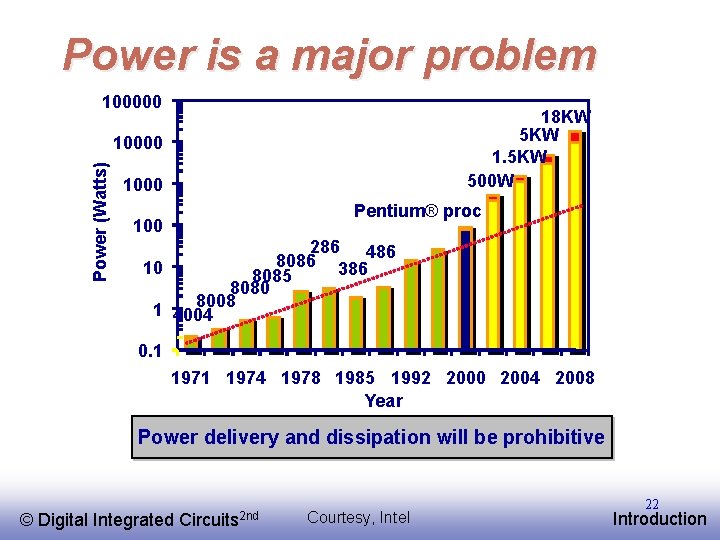

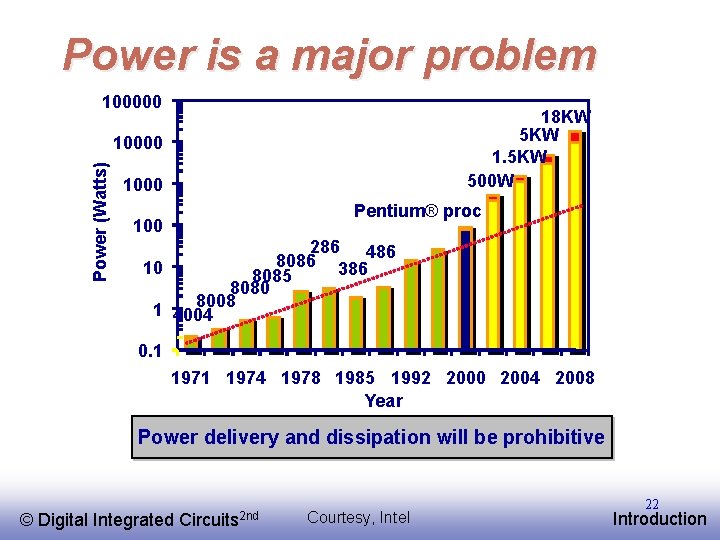

Power is a major problem 100000 18 KW 5 KW 1. 5 KW 500 W Power (Watts) 10000 1000 Pentium® proc 100 286 486 8086 10 386 8085 8080 8008 1 4004 0. 1 1974 1978 1985 1992 2000 2004 2008 Year Power delivery and dissipation will be prohibitive © EE 141 Digital Integrated Circuits 2 nd Courtesy, Intel 22 Introduction

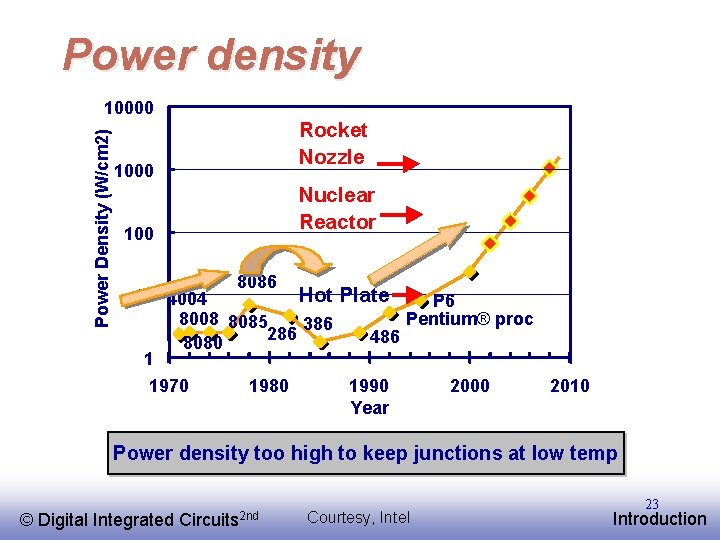

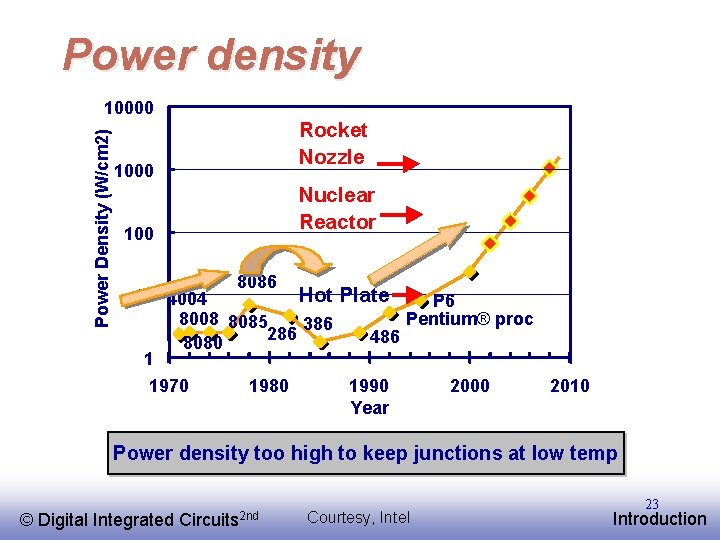

Power density Power Density (W/cm 2) 10000 Rocket Nozzle 1000 Nuclear Reactor 100 8086 10 4004 Hot Plate P 6 8008 8085 Pentium® proc 386 286 486 8080 1 1970 1980 1990 2000 2010 Year Power density too high to keep junctions at low temp © EE 141 Digital Integrated Circuits 2 nd Courtesy, Intel 23 Introduction

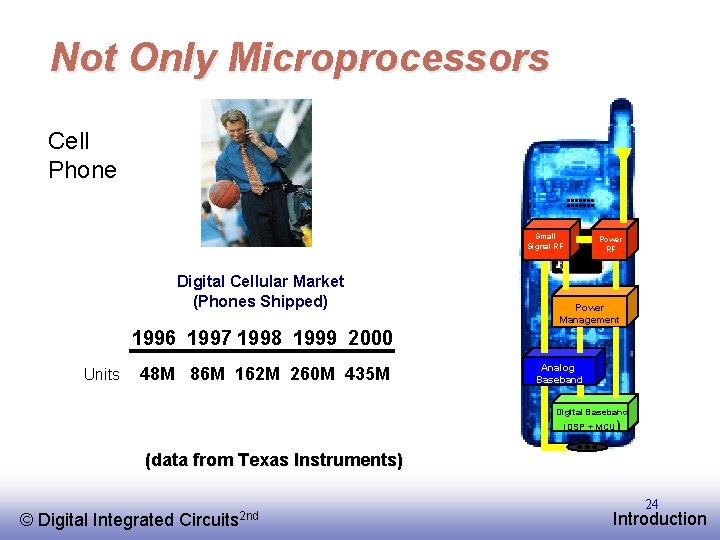

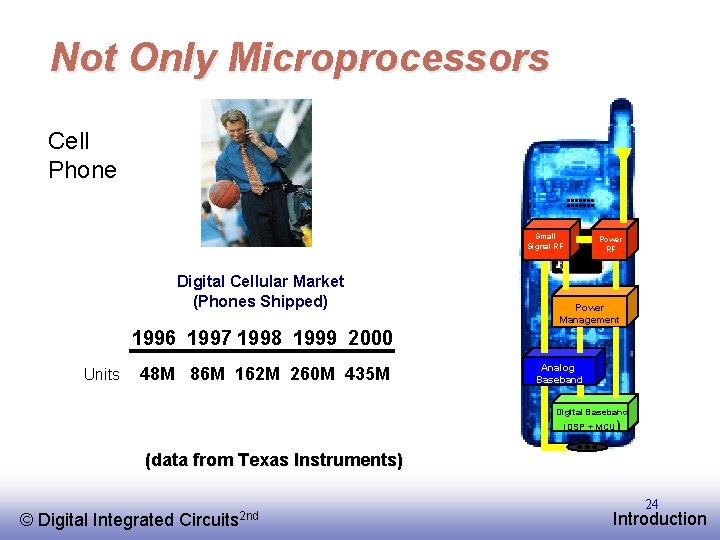

Not Only Microprocessors Cell Phone Small Signal RF Digital Cellular Market (Phones Shipped) Power RF Power Management 1996 1997 1998 1999 2000 Units 48 M 86 M 162 M 260 M 435 M Analog Baseband Digital Baseband (DSP + MCU) (data from Texas Instruments) © EE 141 Digital Integrated Circuits 2 nd 24 Introduction

Many Chips © EE 141 Digital Integrated Circuits 2 nd 25 Introduction

Challenges in Digital Design • Ultra-high speed design • Interconnect delay • Reliability, Manufacturability • Power Dissipation • Time to market © EE 141 Digital Integrated Circuits 2 nd 26 Introduction

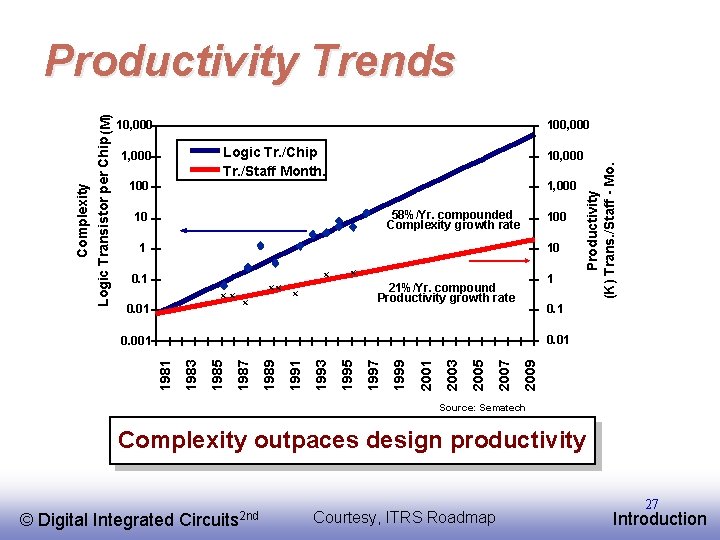

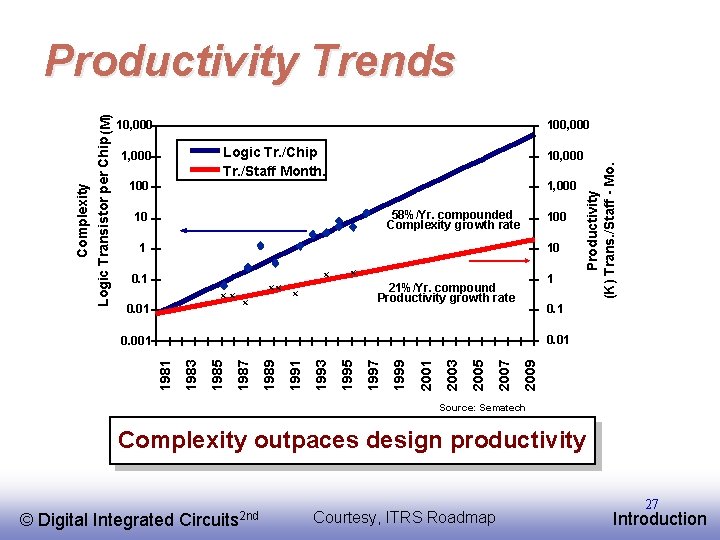

10, 000 100, 000, 000 Logic Tr. /Chip Tr. /Staff Month. 1, 000, 000 10, 000 100, 000 Productivity (K) Trans. /Staff - Mo. Complexity Logic Transistor per Chip (M) Productivity Trends 1, 000, 000 58%/Yr. compounded Complexity growth rate 10 10, 000 100, 000 1, 0001 10 10, 000 x 0. 1 100 xx 0. 01 10 xx x x 1 1, 000 21%/Yr. compound Productivity growth rate x 0. 1 100 0. 01 10 2009 2007 2005 2003 2001 1999 1997 1995 1993 1991 1989 1987 1985 1983 1981 0. 001 1 Source: Sematech Complexity outpaces design productivity © EE 141 Digital Integrated Circuits 2 nd Courtesy, ITRS Roadmap 27 Introduction

Computer-Aided Design q Every new generation can integrate 2 x more functions per chip § Chip price does not increase significantly § Cost of a function decreases by 2 x q However, § Design engineering population does not double every two years. § How to design much more complex chips (with more and more functions)? q Great need for ultra-fast design methods § Design Automation (Computer-Aided Design) © EE 141 Digital Integrated Circuits 2 nd 28 Introduction

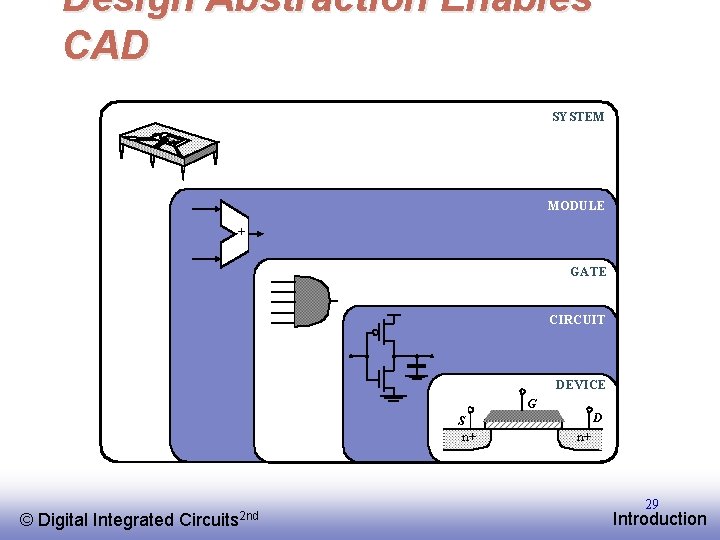

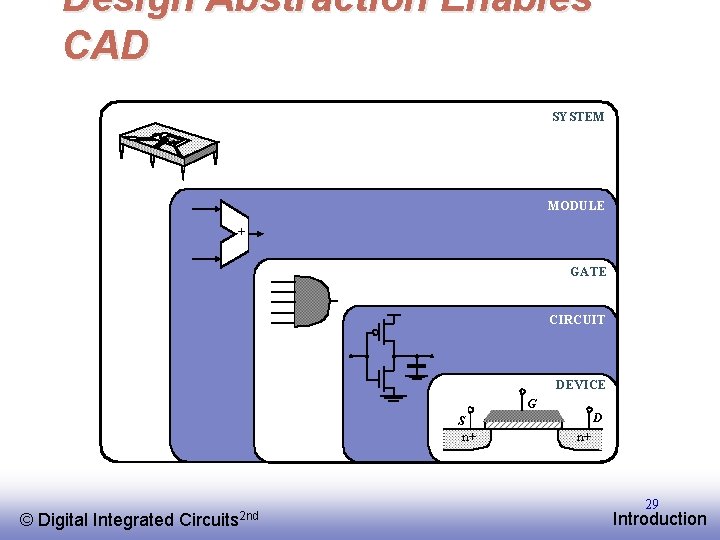

Design Abstraction Enables CAD SYSTEM MODULE + GATE CIRCUIT DEVICE G S n+ © EE 141 Digital Integrated Circuits 2 nd D n+ 29 Introduction

Design Metrics q How to evaluate performance of a digital circuit (gate, block, …)? § Speed (delay, operating frequency) § Power dissipation § Cost – Design time – Design effort § Reliability – Process, voltage and temperature variations © EE 141 Digital Integrated Circuits 2 nd 30 Introduction

Cost of Integrated Circuits q NRE (non-recurrent engineering) costs § design time and effort to design layout and mask § one-time cost factor q Recurrent costs § silicon processing, packaging, test § proportional to volume § proportional to chip area © EE 141 Digital Integrated Circuits 2 nd 31 Introduction

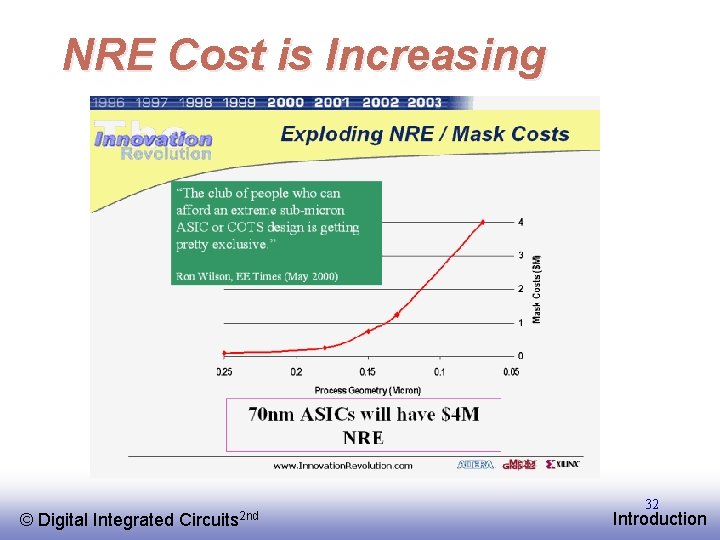

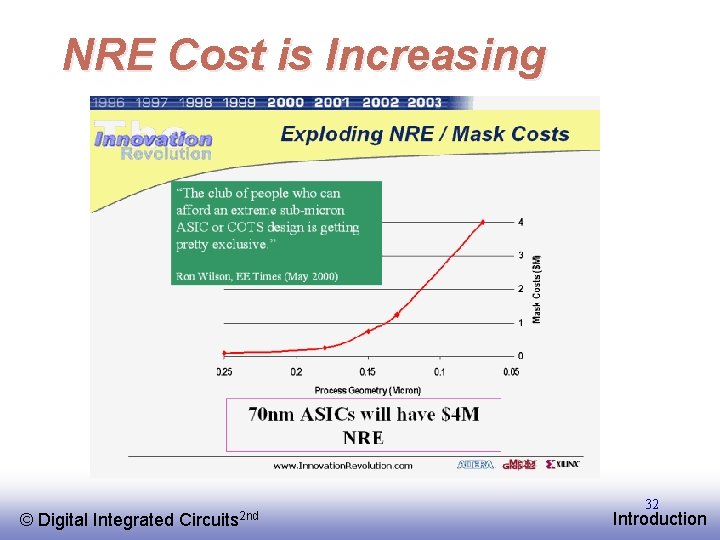

NRE Cost is Increasing © EE 141 Digital Integrated Circuits 2 nd 32 Introduction

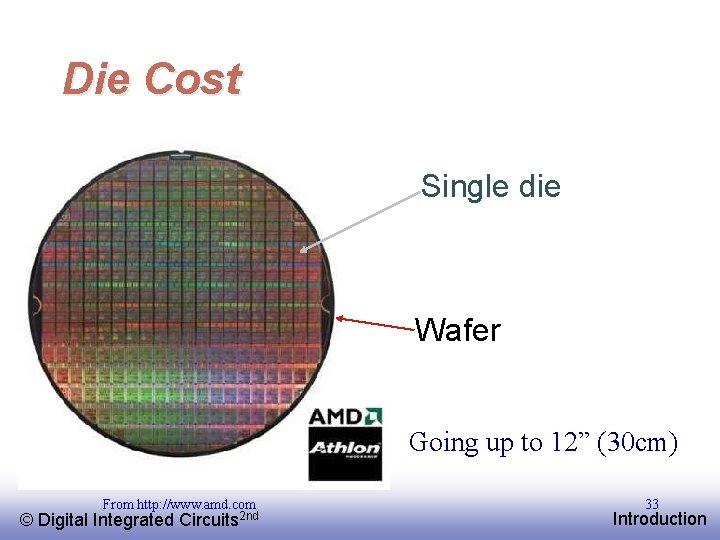

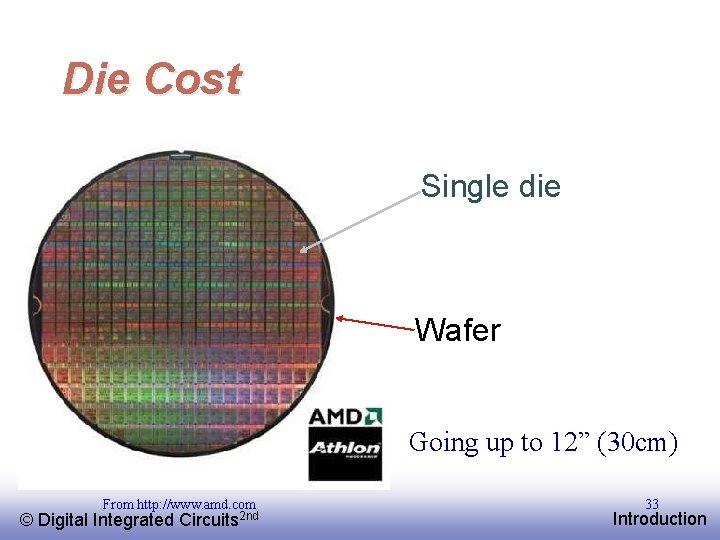

Die Cost Single die Wafer Going up to 12” (30 cm) From http: //www. amd. com © EE 141 Digital Integrated Circuits 2 nd 33 Introduction

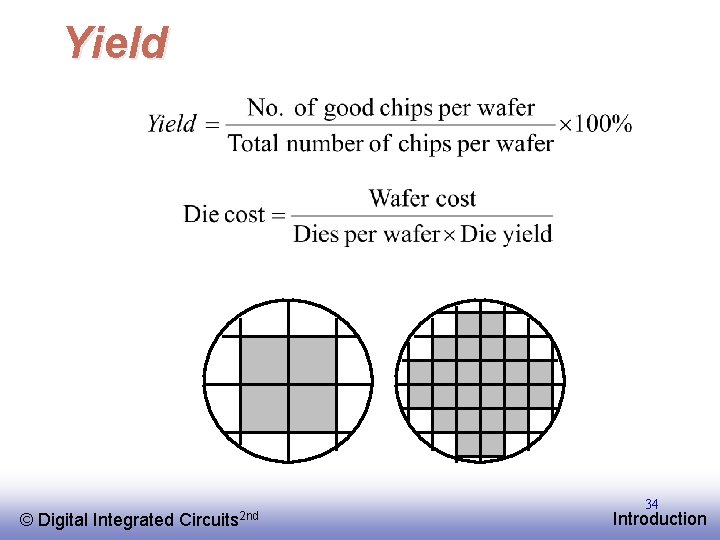

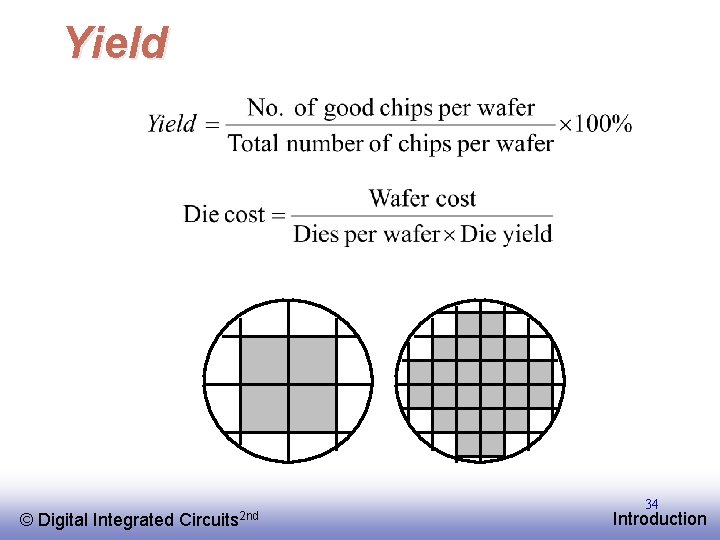

Yield © EE 141 Digital Integrated Circuits 2 nd 34 Introduction

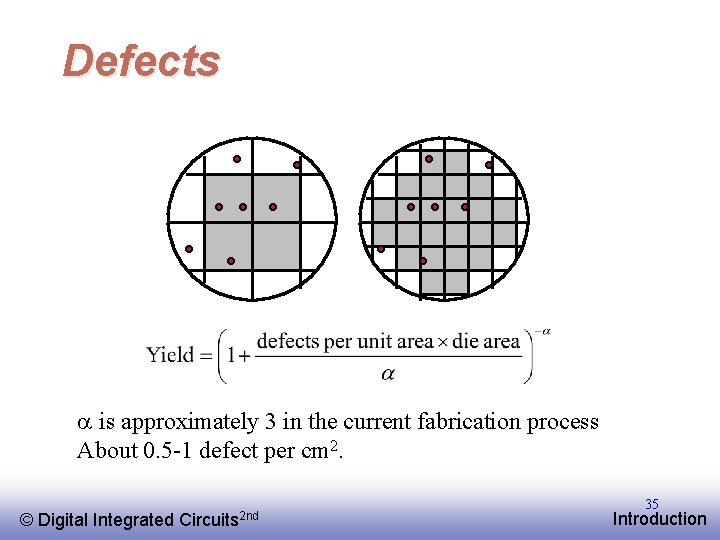

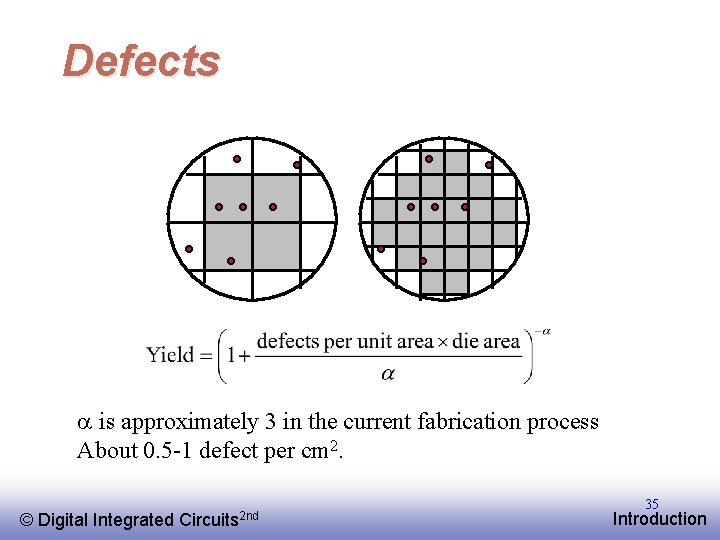

Defects a is approximately 3 in the current fabrication process About 0. 5 -1 defect per cm 2. © EE 141 Digital Integrated Circuits 2 nd 35 Introduction

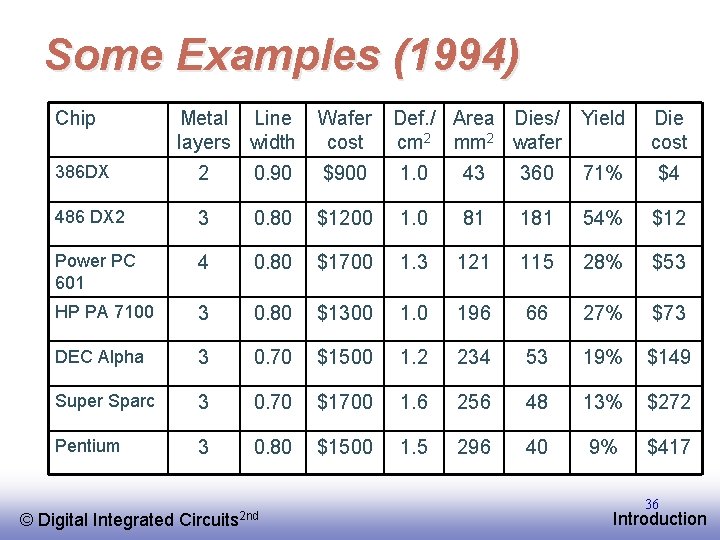

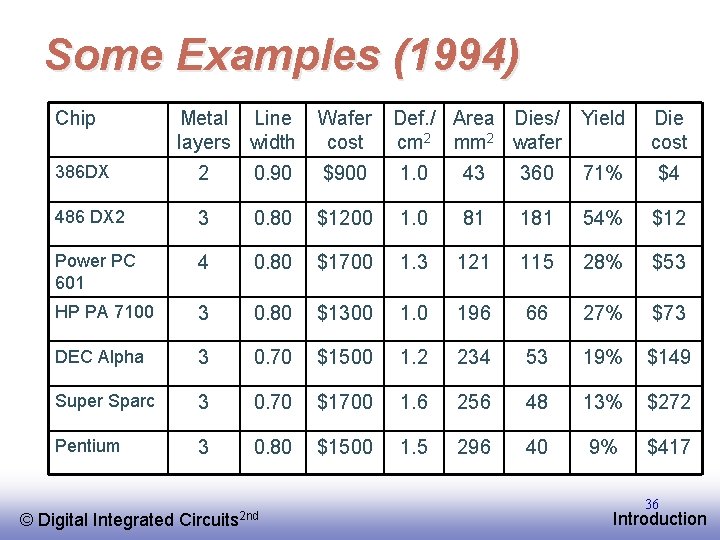

Some Examples (1994) Chip Metal Line layers width Wafer cost Def. / Area Dies/ Yield cm 2 mm 2 wafer Die cost 386 DX 2 0. 90 $900 1. 0 43 360 71% $4 486 DX 2 3 0. 80 $1200 1. 0 81 181 54% $12 Power PC 601 4 0. 80 $1700 1. 3 121 115 28% $53 HP PA 7100 3 0. 80 $1300 1. 0 196 66 27% $73 DEC Alpha 3 0. 70 $1500 1. 2 234 53 19% $149 Super Sparc 3 0. 70 $1700 1. 6 256 48 13% $272 Pentium 3 0. 80 $1500 1. 5 296 40 9% $417 © EE 141 Digital Integrated Circuits 2 nd 36 Introduction

Summary q Digital integrated circuit design faces huge challenges for the coming decades § High speed § Low power § Short design time for highly complex circuit having 1 billion transistors § Reliable under noise and variations q Purpose of the course § Understand the basics of VLSI design § Getting a clear perspective on the challenges and potential solutions © EE 141 Digital Integrated Circuits 2 nd 37 Introduction