Triton Route An Initial Detailed Router for Advanced

- Slides: 31

Triton. Route: An Initial Detailed Router for Advanced VLSI Technologies Andrew B. Kahng, Lutong Wang and Bangqi Xu UC San Diego VLSI CAD Laboratory

Outline • Background • Preliminaries • Connectivity • Preprocessing • Parallel mixed integer linear programming (MILP)-based routing • Overall flow • Panel routing • MILP formulation • Experiments • Conclusion 2

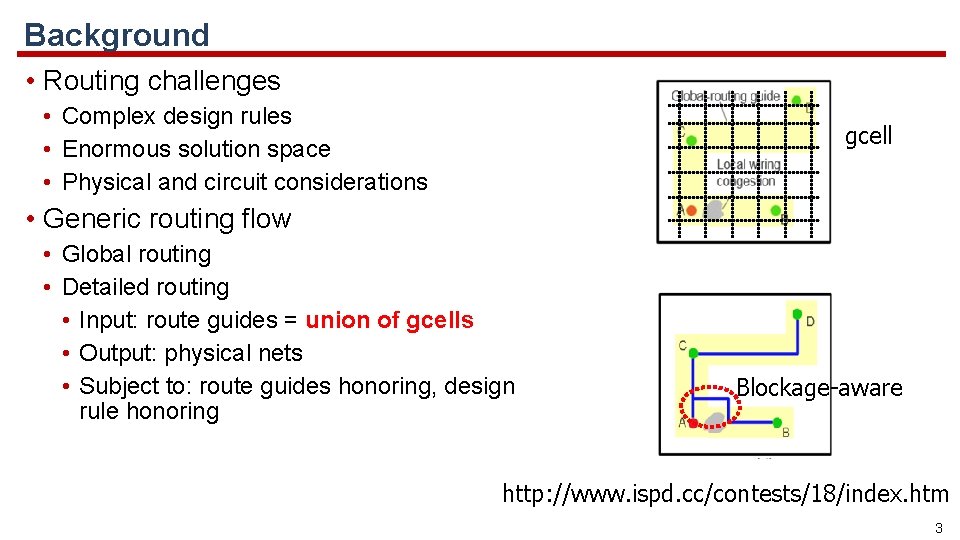

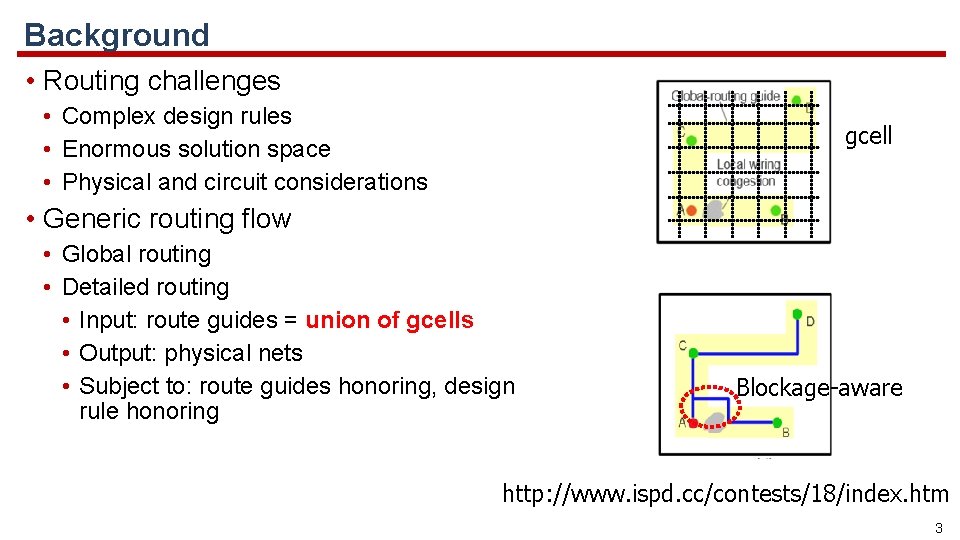

Background • Routing challenges • Complex design rules • Enormous solution space • Physical and circuit considerations gcell • Generic routing flow • Global routing • Detailed routing • Input: route guides = union of gcells • Output: physical nets • Subject to: route guides honoring, design rule honoring Blockage-aware http: //www. ispd. cc/contests/18/index. htm 3

ISPD-2018 Initial Detailed Routing Contest • Input: DEF/LEF, route guides • Output: initial detailed routed solution • Subject to: • Route guide honoring • Connectivity constraints • Design rules Our work: (i) Parallel MILP-based panel routing scheme for each layer (intra-layer parallel routing) (ii) Sequential layer by layer routing (inter-layer sequential routing) (iii) Comprehends connectivity and design rule constraints 4

Outline • Background • Preliminaries • Connectivity • Preprocessing • Parallel MILP-based routing • Overall flow • Panel routing • MILP formulation • Experiments • Conclusion 5

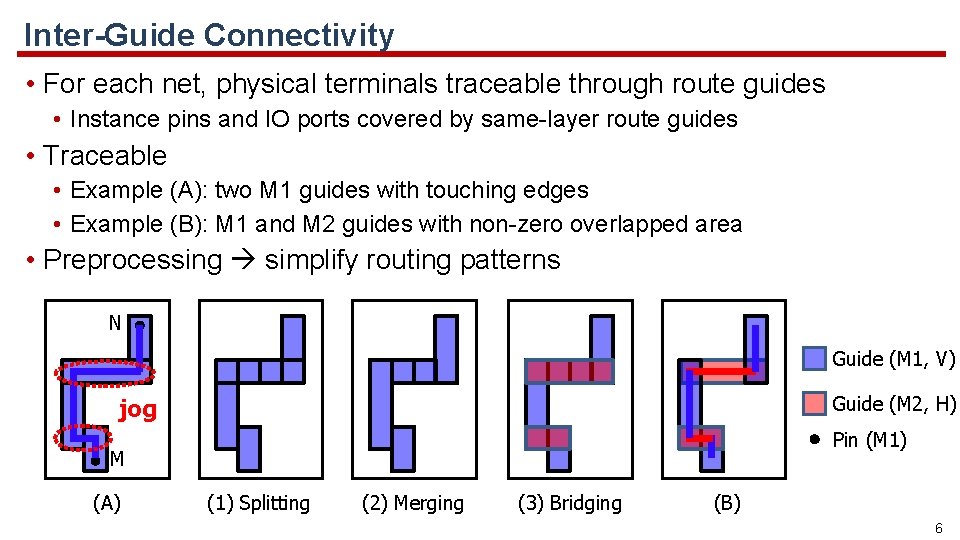

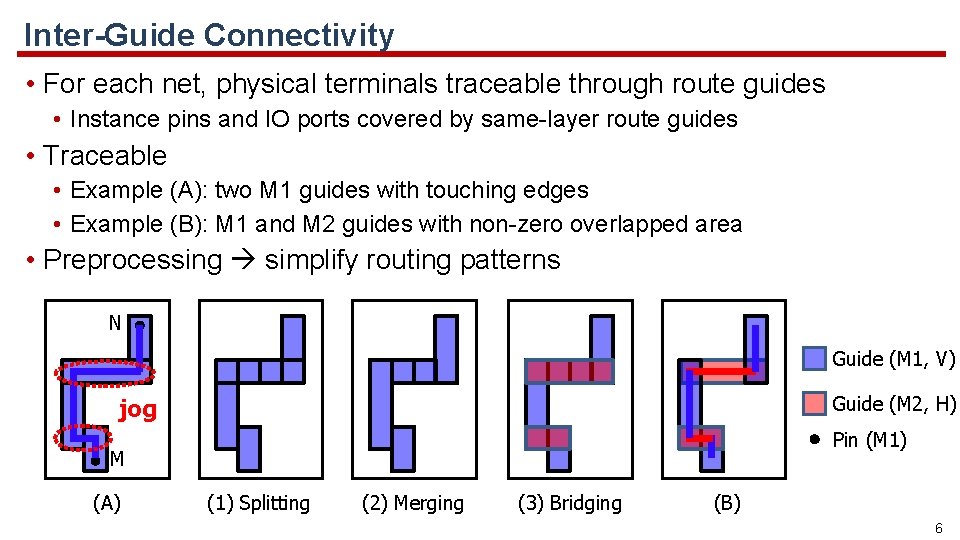

Inter-Guide Connectivity • For each net, physical terminals traceable through route guides • Instance pins and IO ports covered by same-layer route guides • Traceable • Example (A): two M 1 guides with touching edges • Example (B): M 1 and M 2 guides with non-zero overlapped area • Preprocessing simplify routing patterns N Guide (M 1, V) Guide (M 2, H) jog Pin (M 1) M (A) (1) Splitting (2) Merging (3) Bridging (B) 6

Outline • Background • Preliminaries • Connectivity • Preprocessing • Parallel MILP-based routing • Overall flow • Panel routing • MILP formulation • Experiments • Conclusion 7

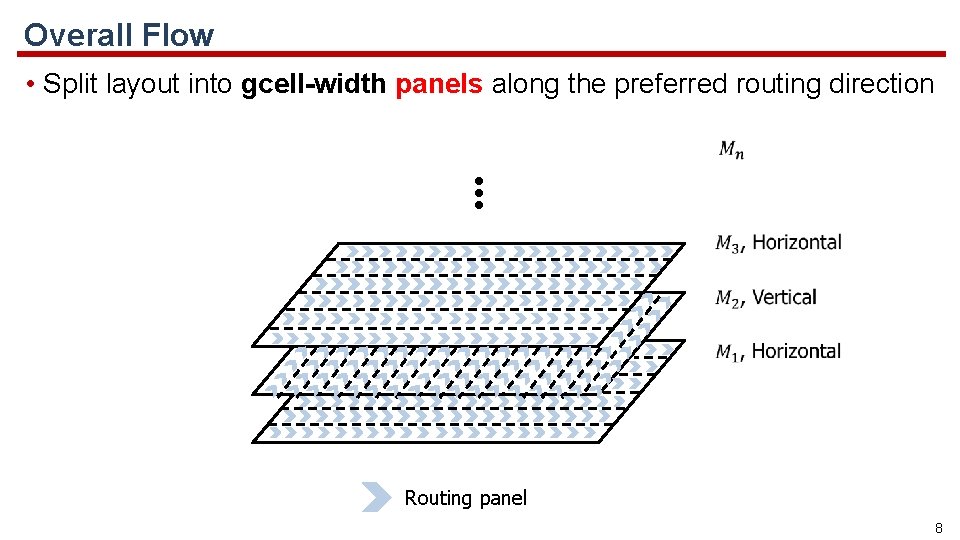

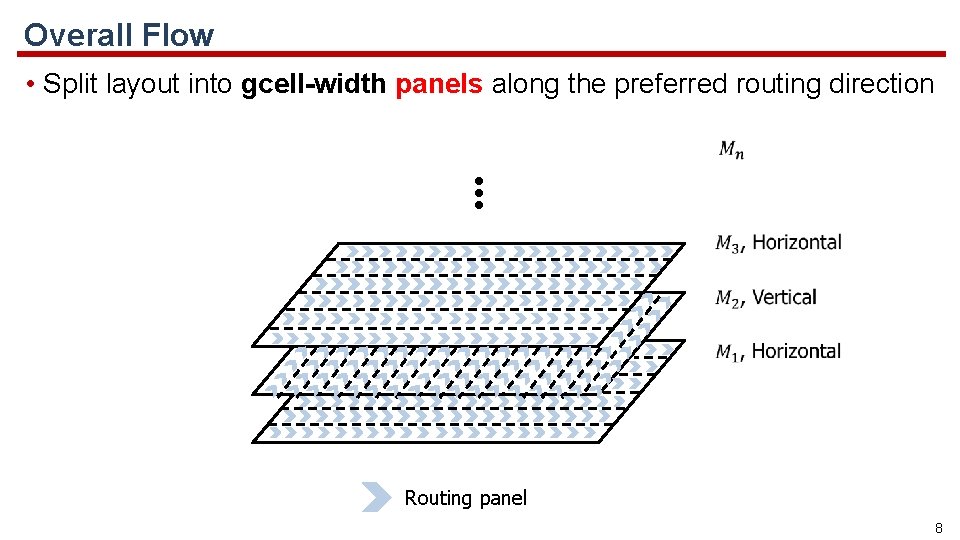

Overall Flow • Split layout into gcell-width panels along the preferred routing direction … Routing panel 8

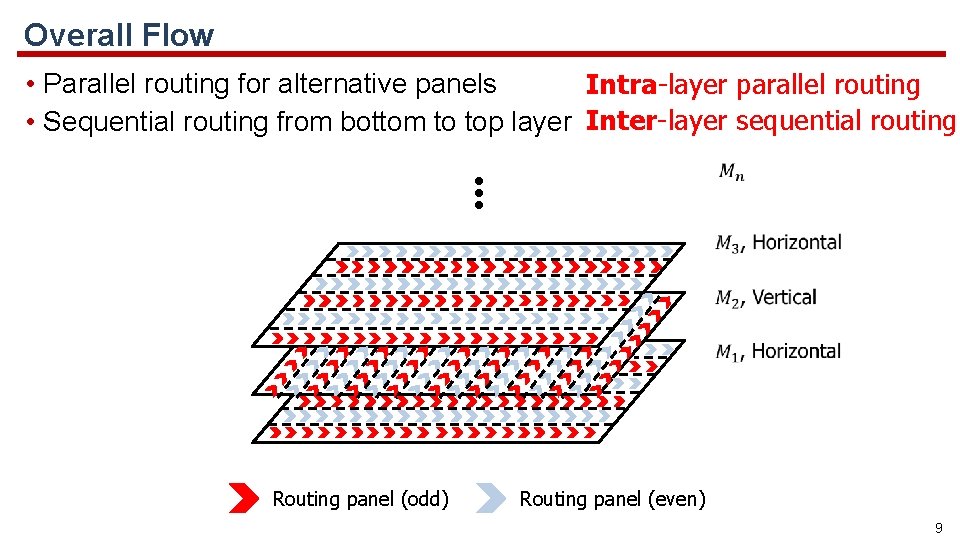

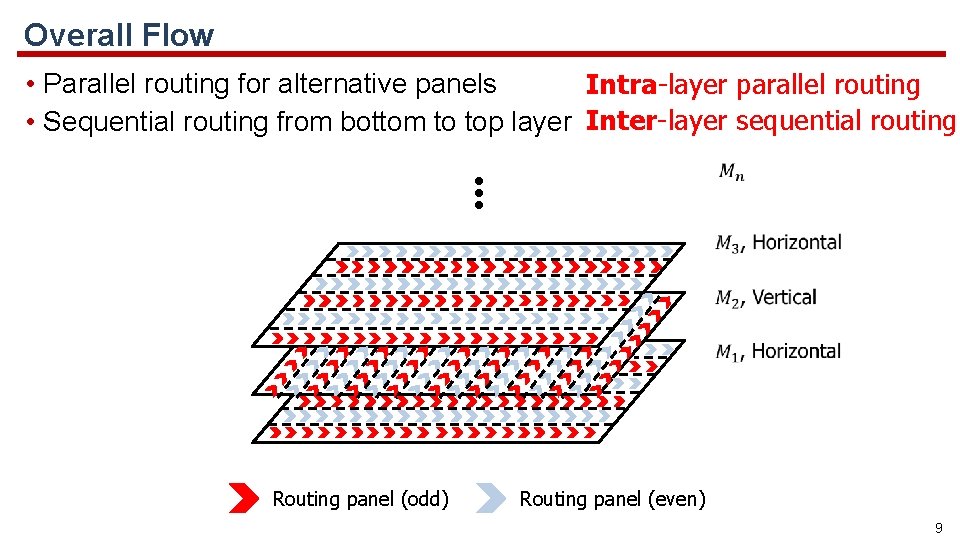

Overall Flow • Parallel routing for alternative panels Intra-layer parallel routing • Sequential routing from bottom to top layer Inter-layer sequential routing … Routing panel (odd) Routing panel (even) 9

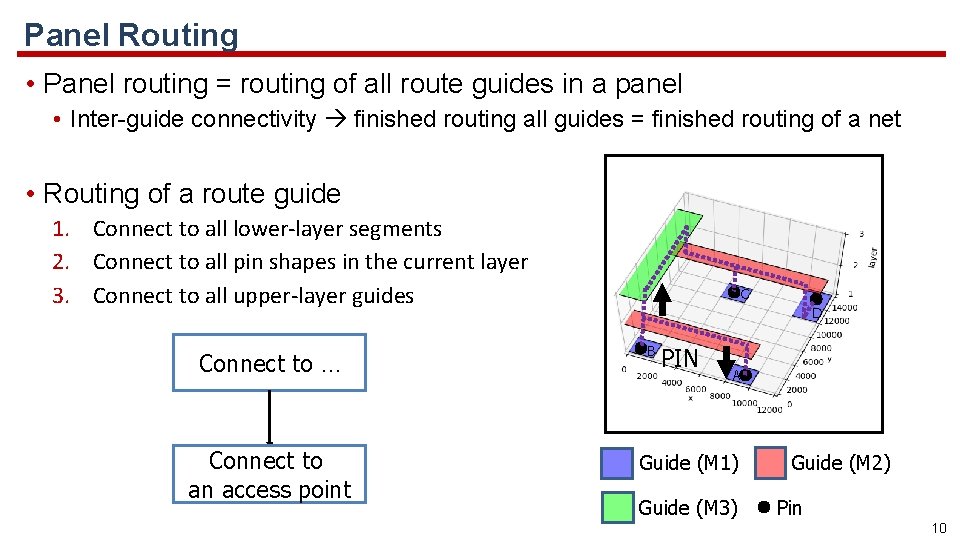

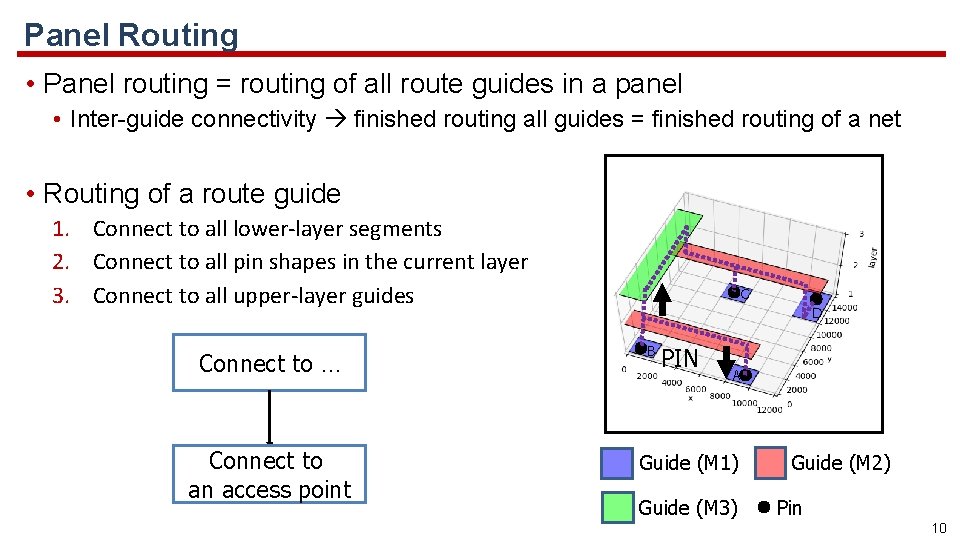

Panel Routing • Panel routing = routing of all route guides in a panel • Inter-guide connectivity finished routing all guides = finished routing of a net • Routing of a route guide 1. Connect to all lower-layer segments 2. Connect to all pin shapes in the current layer 3. Connect to all upper-layer guides Connect to … Connect to an access point C D B PIN A Guide (M 1) Guide (M 3) Guide (M 2) Pin 10

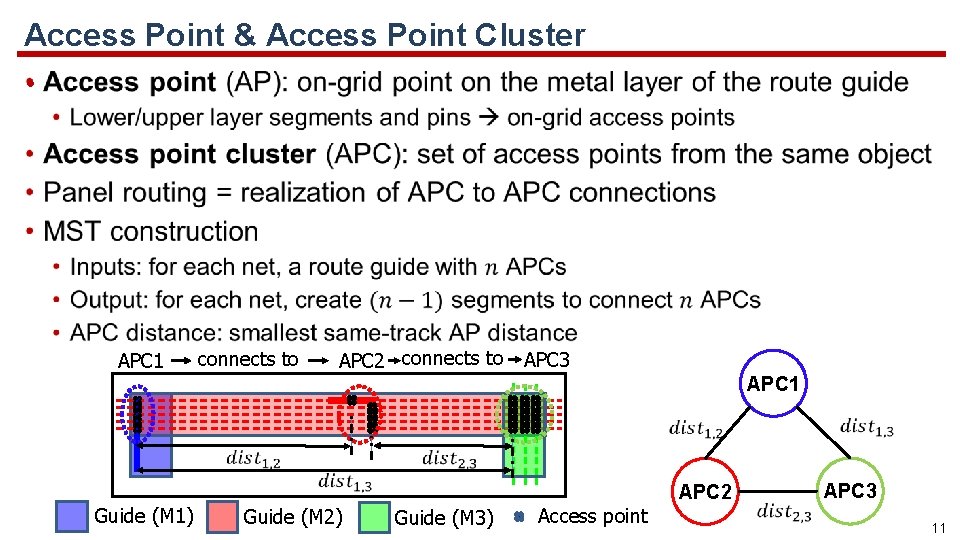

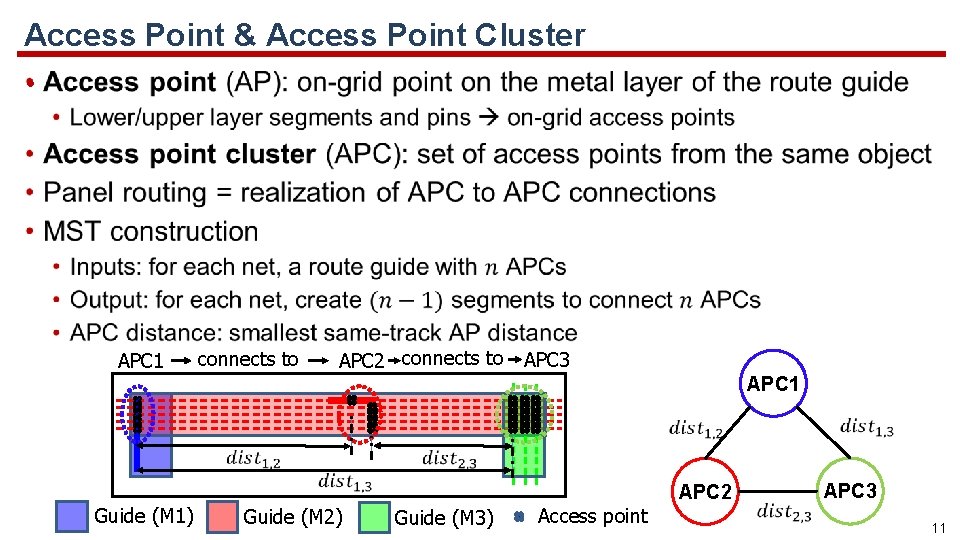

Access Point & Access Point Cluster • APC 1 APC 2 connects to APC 3 connects to APC 1 Guide (M 1) Guide (M 2) APC 2 Guide (M 3) Access point APC 3 11

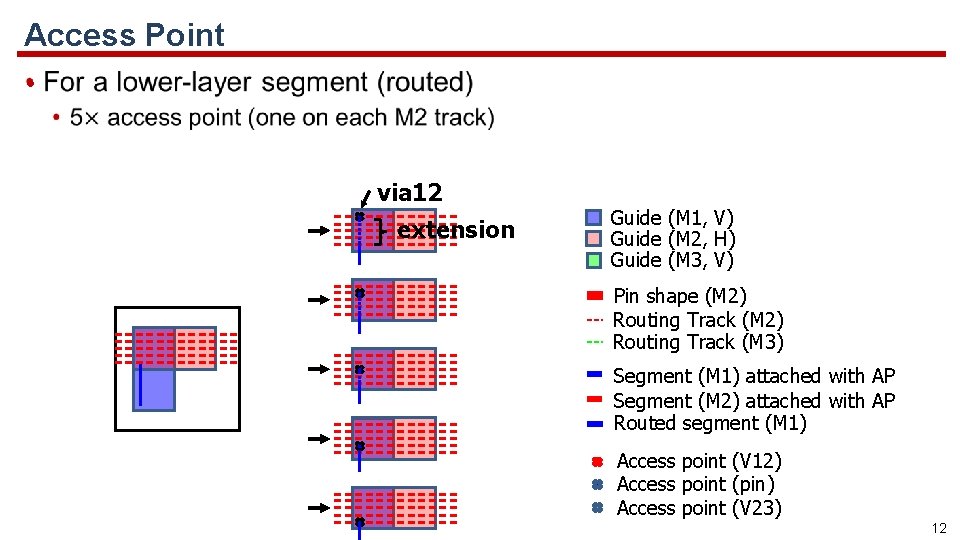

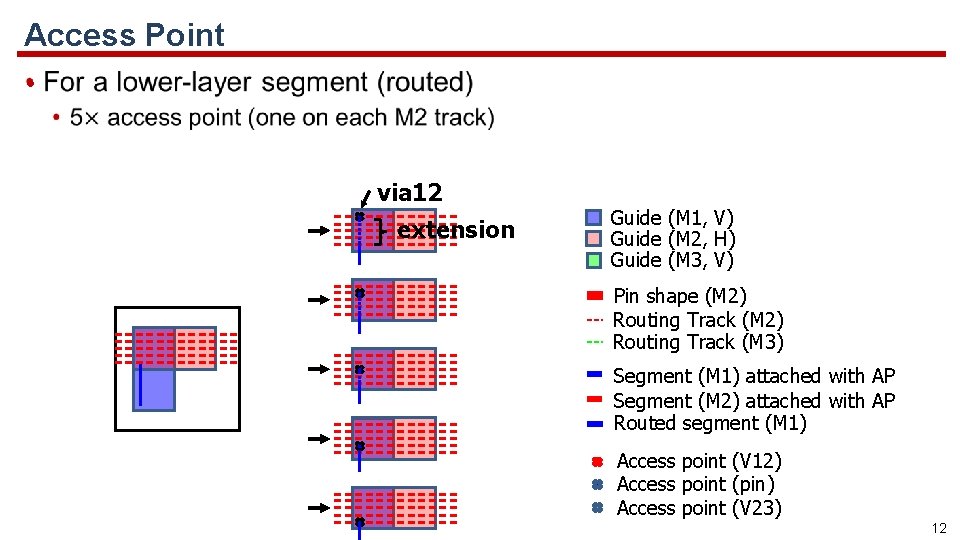

Access Point • via 12 extension Guide (M 1, V) Guide (M 2, H) Guide (M 3, V) Pin shape (M 2) Routing Track (M 3) Segment (M 1) attached with AP Segment (M 2) attached with AP Routed segment (M 1) Access point (V 12) Access point (pin) Access point (V 23) 12

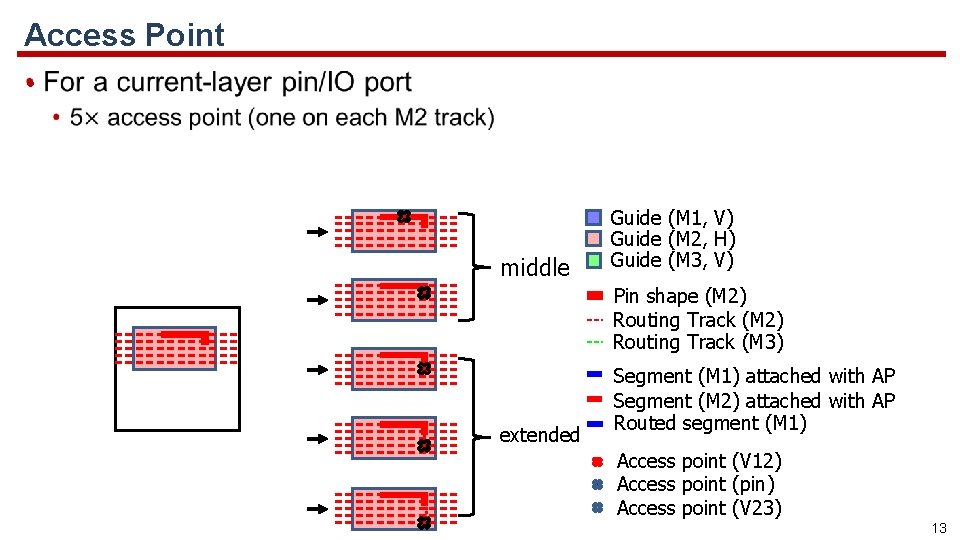

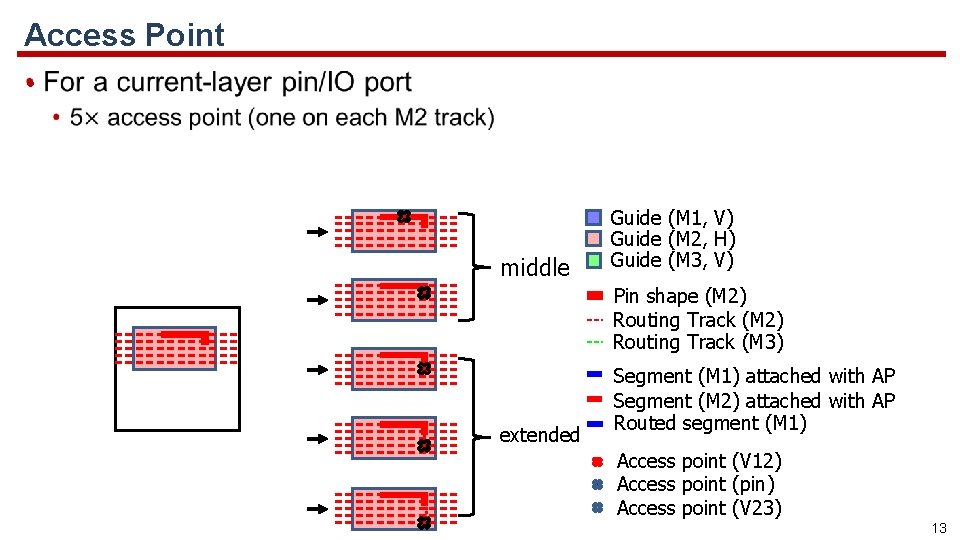

Access Point • middle Guide (M 1, V) Guide (M 2, H) Guide (M 3, V) Pin shape (M 2) Routing Track (M 3) extended Segment (M 1) attached with AP Segment (M 2) attached with AP Routed segment (M 1) Access point (V 12) Access point (pin) Access point (V 23) 13

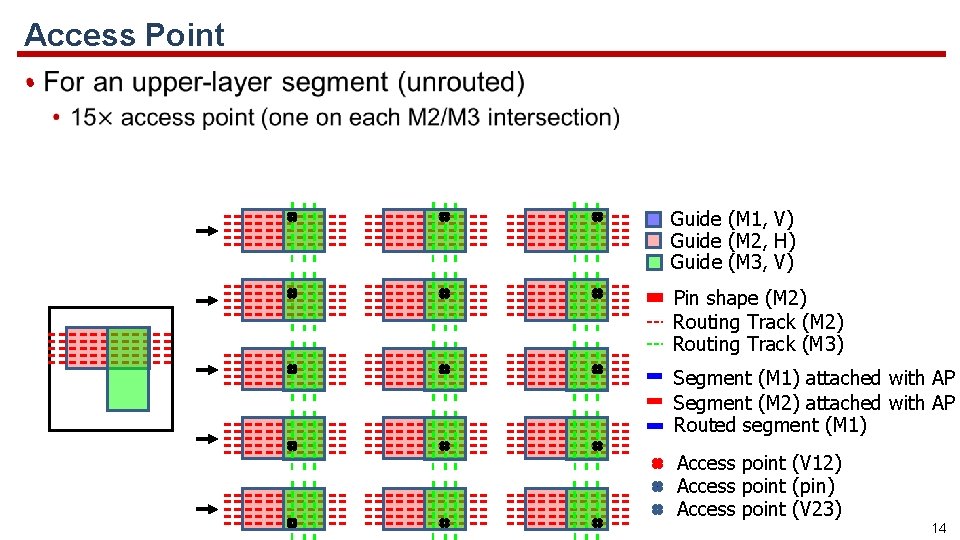

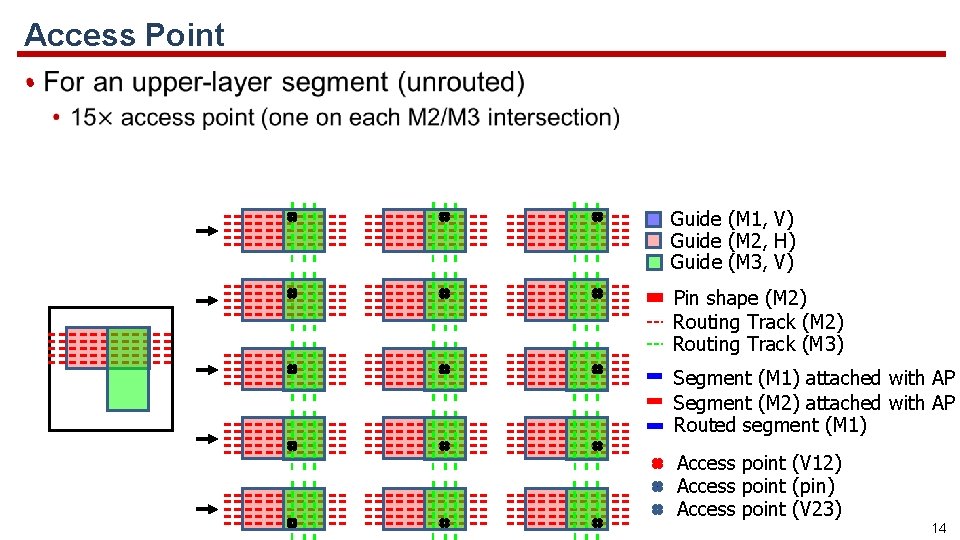

Access Point • Guide (M 1, V) Guide (M 2, H) Guide (M 3, V) Pin shape (M 2) Routing Track (M 3) Segment (M 1) attached with AP Segment (M 2) attached with AP Routed segment (M 1) Access point (V 12) Access point (pin) Access point (V 23) 14

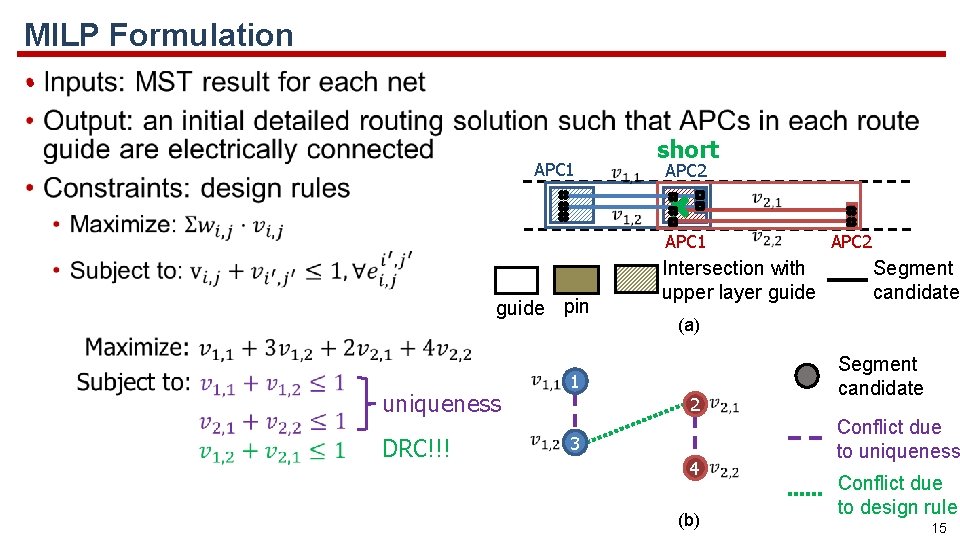

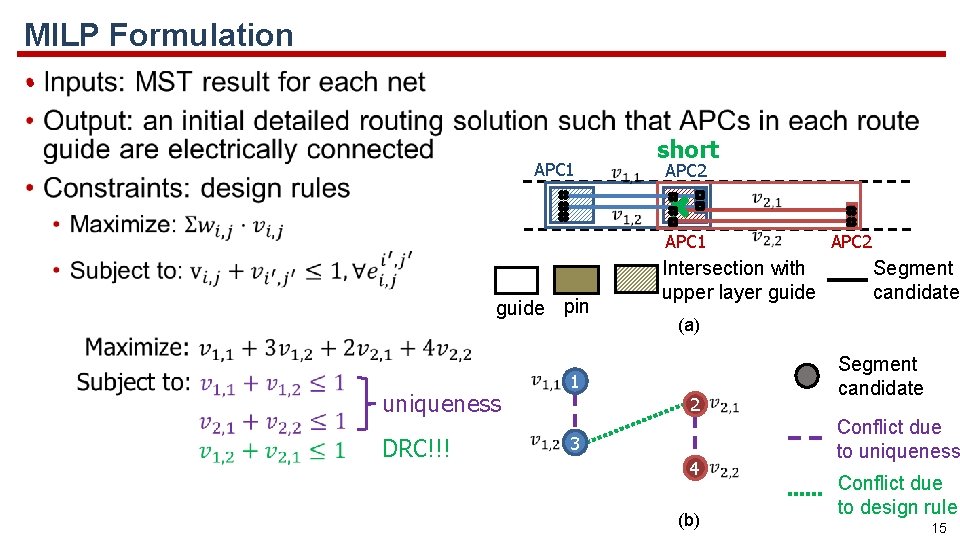

MILP Formulation • APC 1 short APC 2 APC 1 guide pin uniqueness DRC!!! 1 Intersection with upper layer guide APC 2 Segment candidate (a) 2 3 4 (b) Segment candidate Conflict due to uniqueness Conflict due to design rule 15

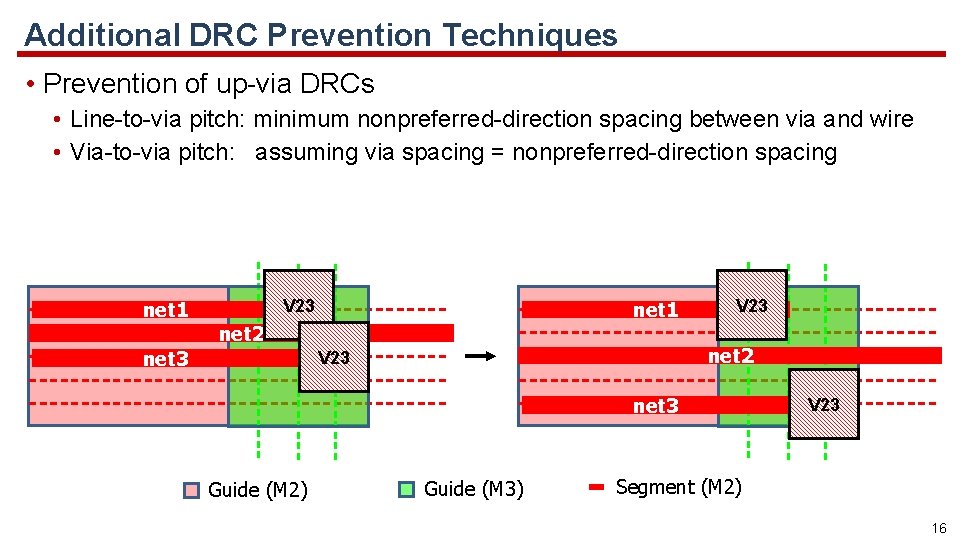

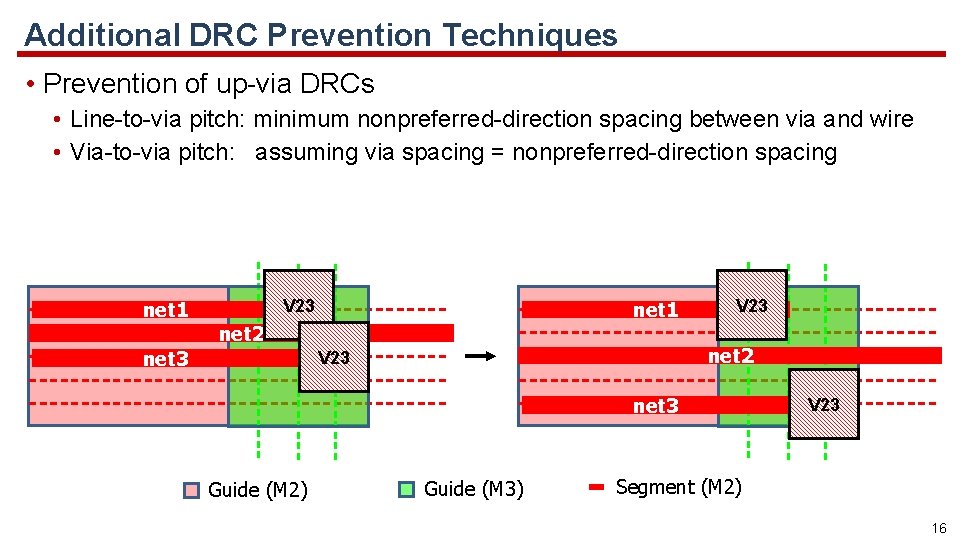

Additional DRC Prevention Techniques • Prevention of up-via DRCs • Line-to-via pitch: minimum nonpreferred-direction spacing between via and wire • Via-to-via pitch: assuming via spacing = nonpreferred-direction spacing net 1 V 23 net 1 net 2 net 3 V 23 net 2 V 23 net 3 Guide (M 2) Guide (M 3) V 23 Segment (M 2) 16

Outline • Background • Preliminaries • Connectivity • Preprocessing • Parallel MILP-based routing • Overall flow • Panel routing • MILP formulation • Experiments • Conclusion 17

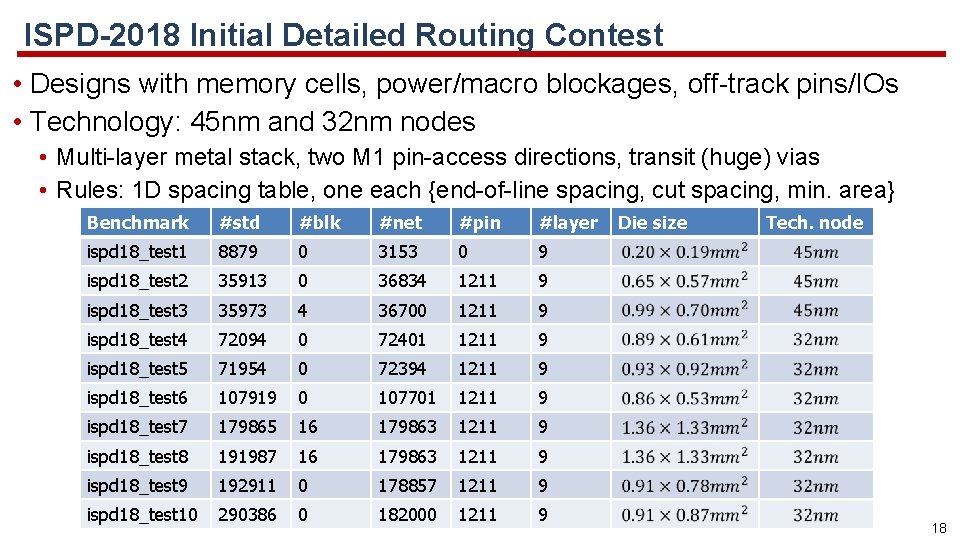

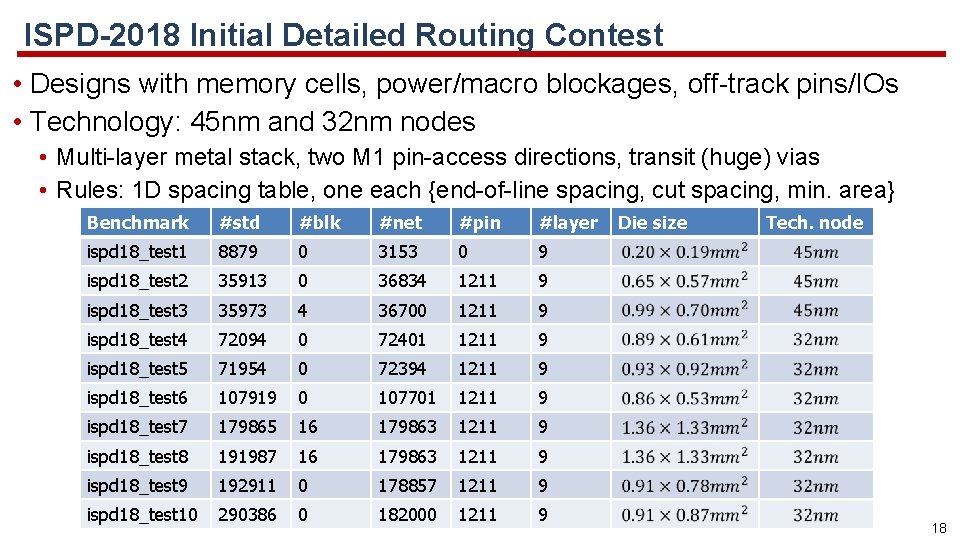

ISPD-2018 Initial Detailed Routing Contest • Designs with memory cells, power/macro blockages, off-track pins/IOs • Technology: 45 nm and 32 nm nodes • Multi-layer metal stack, two M 1 pin-access directions, transit (huge) vias • Rules: 1 D spacing table, one each {end-of-line spacing, cut spacing, min. area} Benchmark #std #blk #net #pin #layer ispd 18_test 1 8879 0 3153 0 9 ispd 18_test 2 35913 0 36834 1211 9 ispd 18_test 3 35973 4 36700 1211 9 ispd 18_test 4 72094 0 72401 1211 9 ispd 18_test 5 71954 0 72394 1211 9 ispd 18_test 6 107919 0 107701 1211 9 ispd 18_test 7 179865 16 179863 1211 9 ispd 18_test 8 191987 16 179863 1211 9 ispd 18_test 9 192911 0 178857 1211 9 ispd 18_test 10 290386 0 182000 1211 9 Die size Tech. node 18

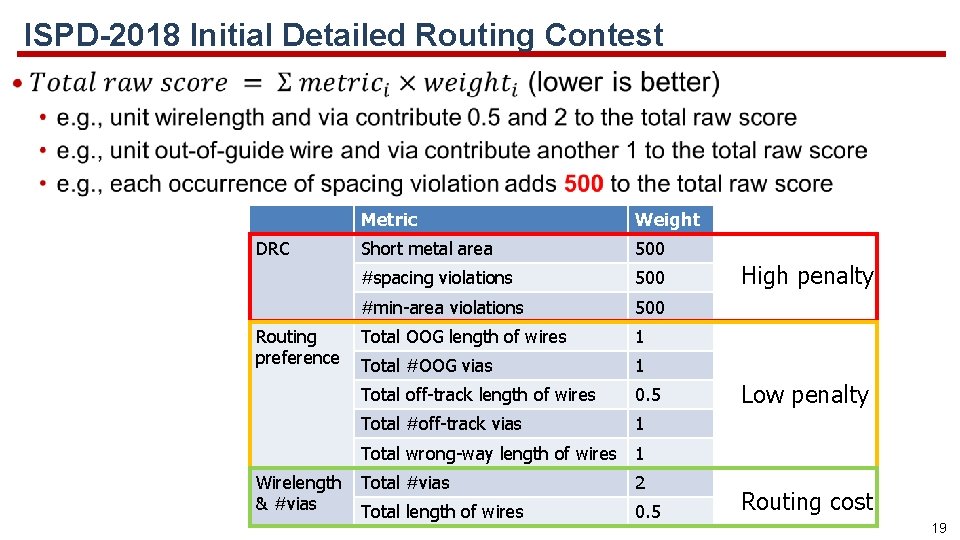

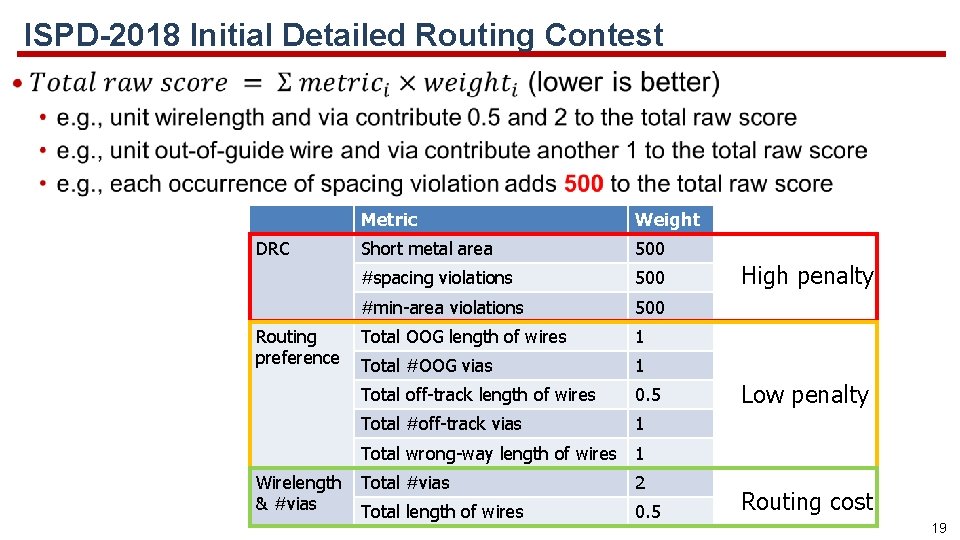

ISPD-2018 Initial Detailed Routing Contest • DRC Routing preference Metric Weight Short metal area 500 #spacing violations 500 #min-area violations 500 Total OOG length of wires 1 Total #OOG vias 1 Total off-track length of wires 0. 5 Total #off-track vias 1 High penalty Low penalty Total wrong-way length of wires 1 Wirelength Total #vias & #vias Total length of wires 2 0. 5 Routing cost 19

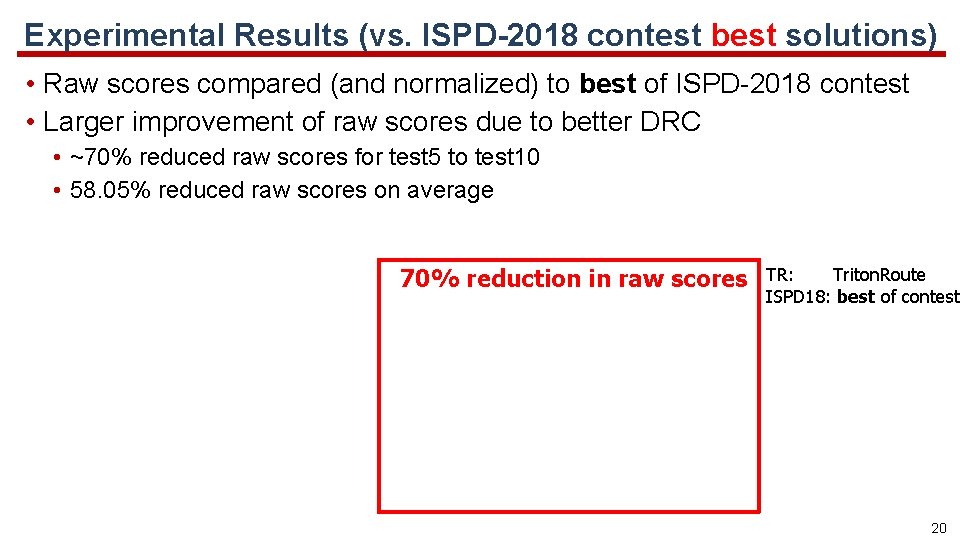

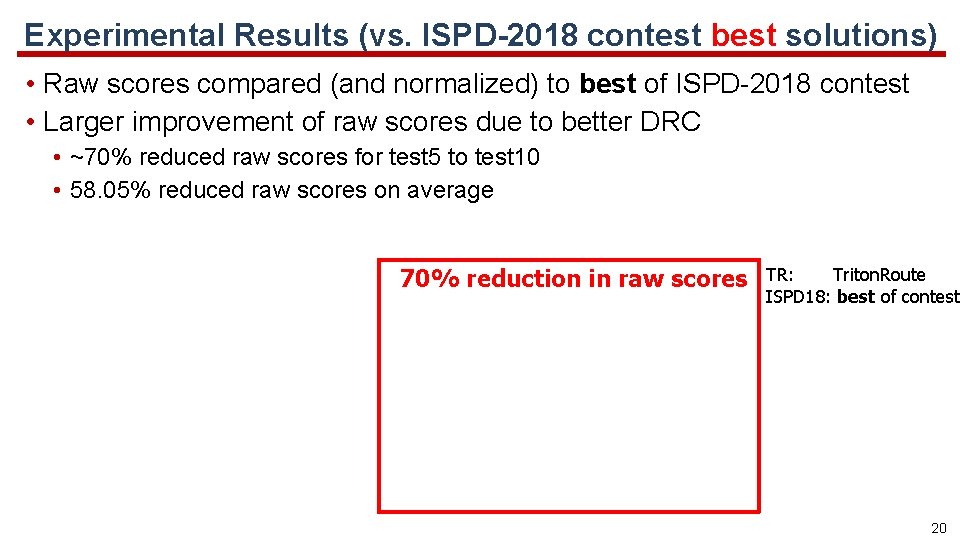

Experimental Results (vs. ISPD-2018 contest best solutions) • Raw scores compared (and normalized) to best of ISPD-2018 contest • Larger improvement of raw scores due to better DRC • ~70% reduced raw scores for test 5 to test 10 • 58. 05% reduced raw scores on average 70% reduction in raw scores TR: Triton. Route ISPD 18: best of contest 20

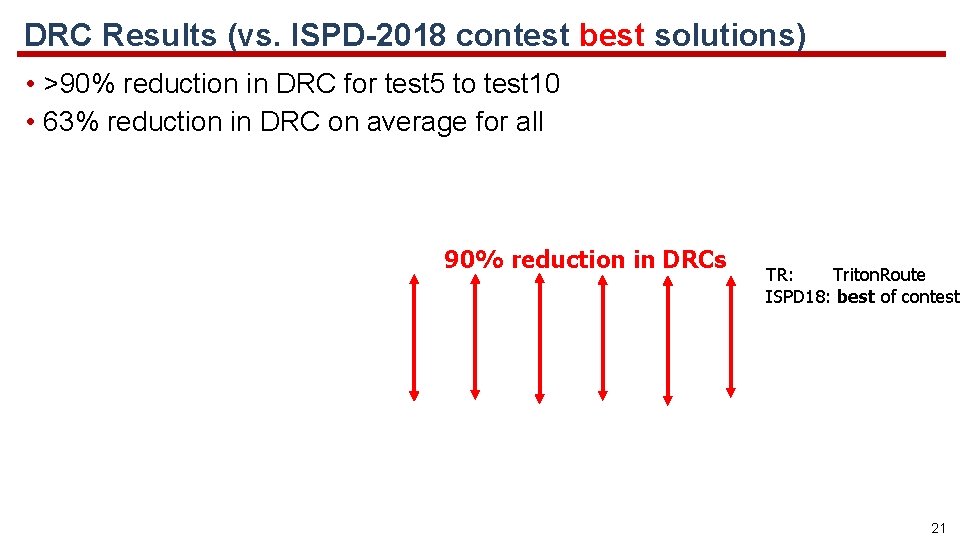

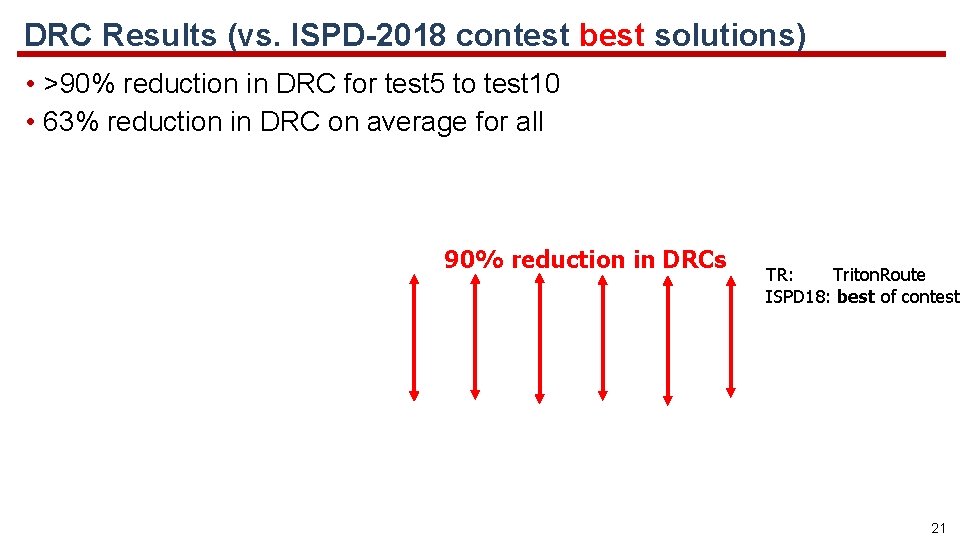

DRC Results (vs. ISPD-2018 contest best solutions) • >90% reduction in DRC for test 5 to test 10 • 63% reduction in DRC on average for all 90% reduction in DRCs TR: Triton. Route ISPD 18: best of contest 21

Conclusion and Future Goals • Parallel, MILP-based panel routing • 58. 05% better raw scores compared to ISPD 18 best results per design • >90% reduction in DRC for complex designs (test 5 – test 10) • Ongoing / future works • • • Routing refinement: topology, wirelength and via count Better detour handling Improvement of pin accessibility Improvement of rule handling Runtime and memory reduction 22

Towards Open. ROAD • Open. ROAD (theopenroadproject. org) • DARPA IDEA program • UCSD and four other universities, Qualcomm, Arm • Fully automated and open-source RTL-to-GDS tool chain in advanced node • Gaps between the contest and the “real-world” • • • Incremental routing Versatile database Non-default rules Pin accessibility Improved heuristics DRC handling Advanced-node rule deck Robust support Etc. 23

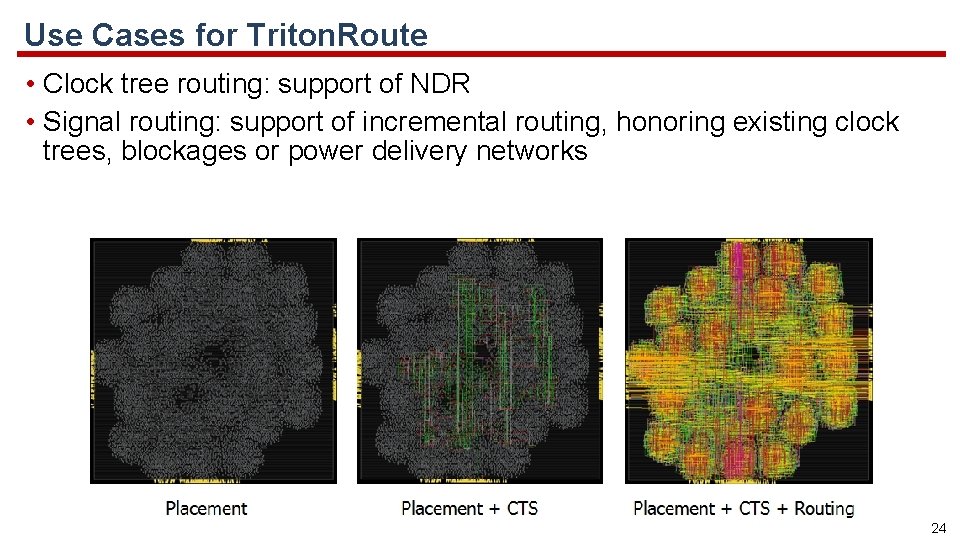

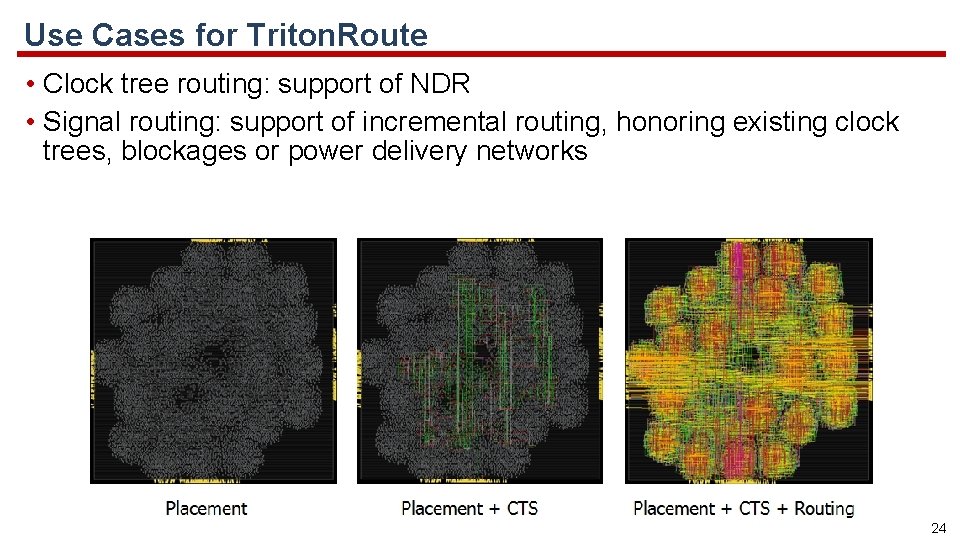

Use Cases for Triton. Route • Clock tree routing: support of NDR • Signal routing: support of incremental routing, honoring existing clock trees, blockages or power delivery networks 24

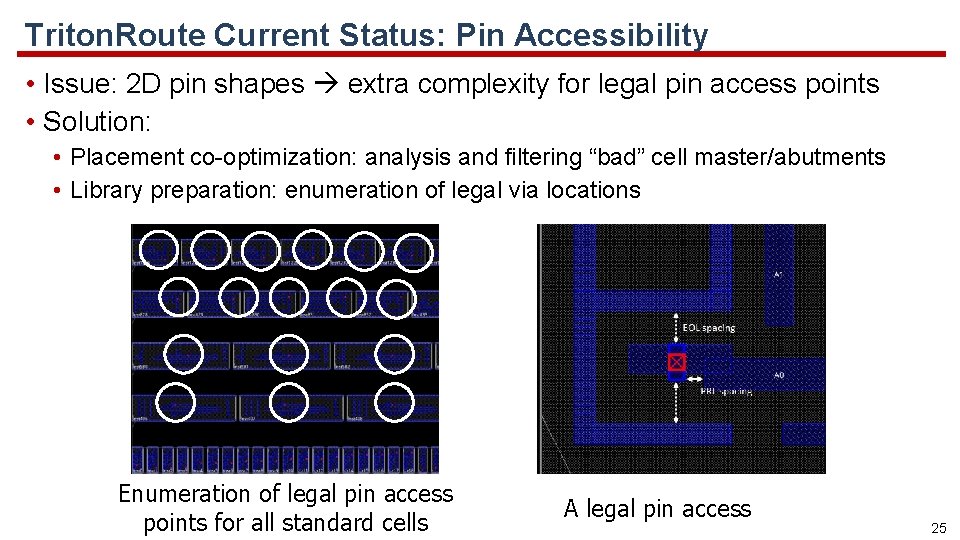

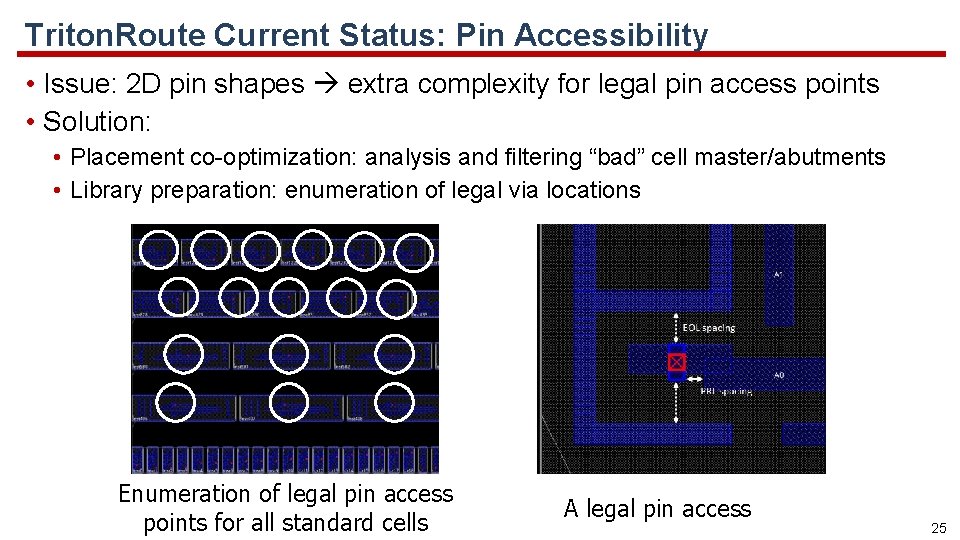

Triton. Route Current Status: Pin Accessibility • Issue: 2 D pin shapes extra complexity for legal pin access points • Solution: • Placement co-optimization: analysis and filtering “bad” cell master/abutments • Library preparation: enumeration of legal via locations Enumeration of legal pin access points for all standard cells A legal pin access 25

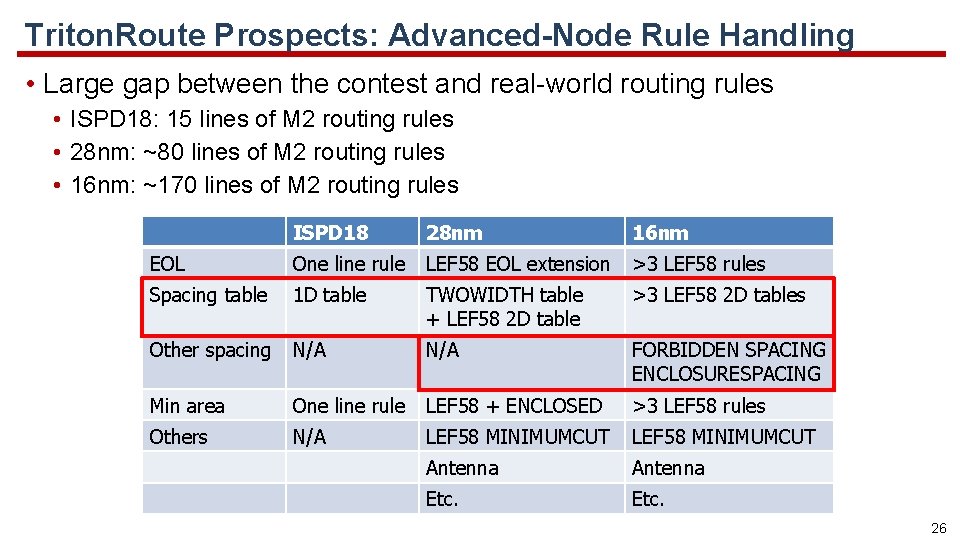

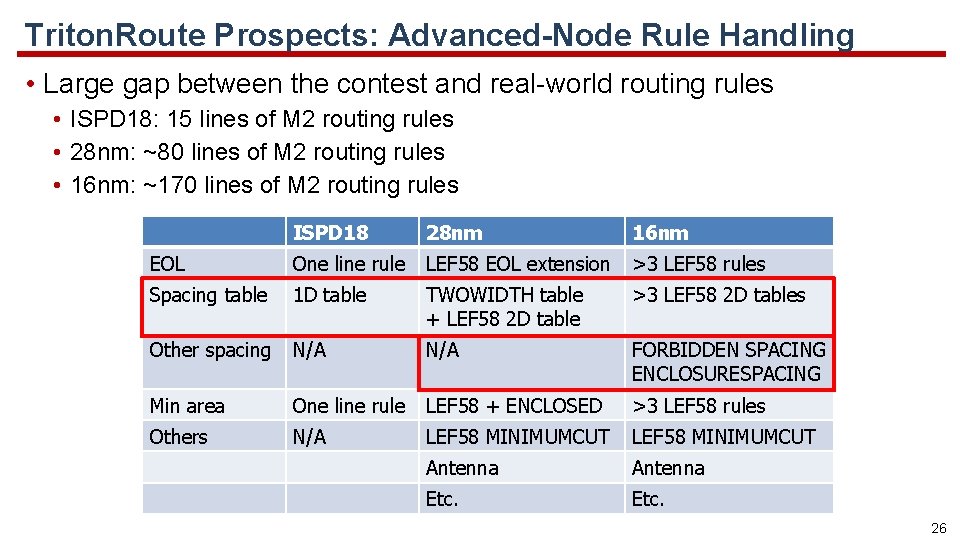

Triton. Route Prospects: Advanced-Node Rule Handling • Large gap between the contest and real-world routing rules • ISPD 18: 15 lines of M 2 routing rules • 28 nm: ~80 lines of M 2 routing rules • 16 nm: ~170 lines of M 2 routing rules ISPD 18 28 nm 16 nm EOL One line rule LEF 58 EOL extension >3 LEF 58 rules Spacing table 1 D table TWOWIDTH table + LEF 58 2 D table >3 LEF 58 2 D tables Other spacing N/A FORBIDDEN SPACING ENCLOSURESPACING Min area One line rule LEF 58 + ENCLOSED >3 LEF 58 rules Others N/A LEF 58 MINIMUMCUT Antenna Etc. 26

THANK YOU! 27

BACKUP 28

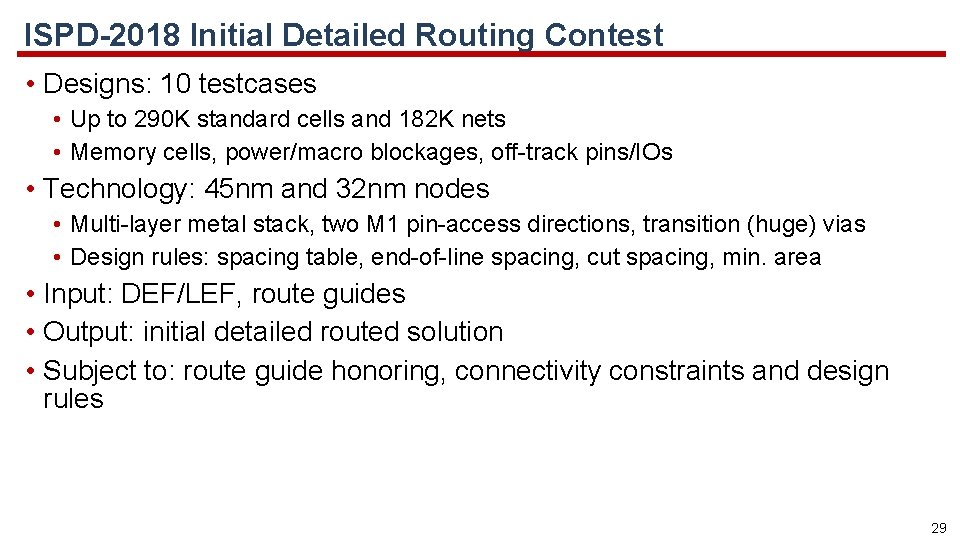

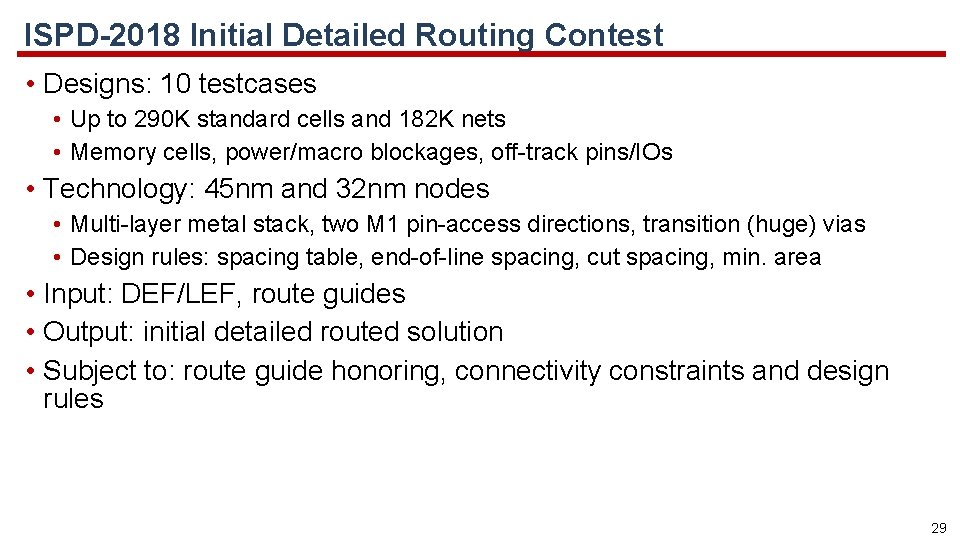

ISPD-2018 Initial Detailed Routing Contest • Designs: 10 testcases • Up to 290 K standard cells and 182 K nets • Memory cells, power/macro blockages, off-track pins/IOs • Technology: 45 nm and 32 nm nodes • Multi-layer metal stack, two M 1 pin-access directions, transition (huge) vias • Design rules: spacing table, end-of-line spacing, cut spacing, min. area • Input: DEF/LEF, route guides • Output: initial detailed routed solution • Subject to: route guide honoring, connectivity constraints and design rules 29

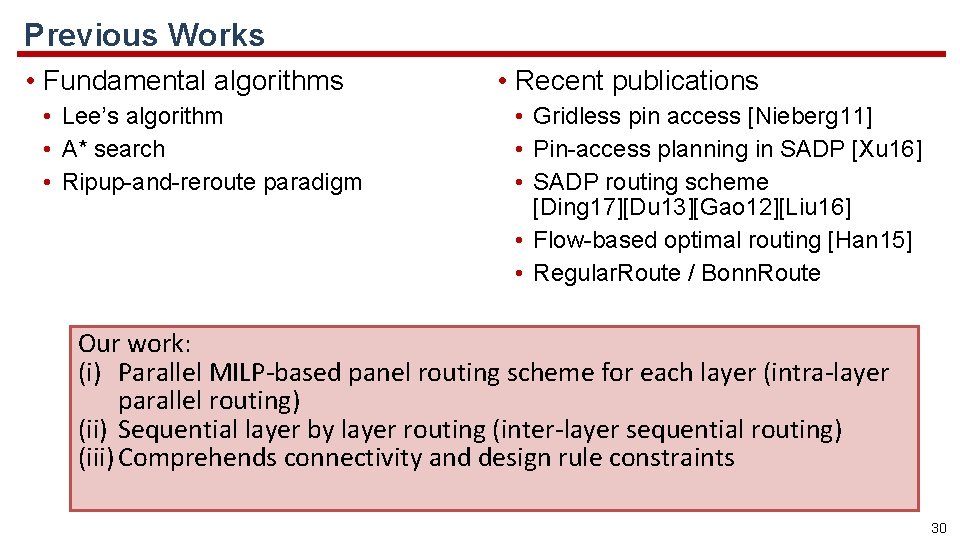

Previous Works • Fundamental algorithms • Lee’s algorithm • A* search • Ripup-and-reroute paradigm • Recent publications • Gridless pin access [Nieberg 11] • Pin-access planning in SADP [Xu 16] • SADP routing scheme [Ding 17][Du 13][Gao 12][Liu 16] • Flow-based optimal routing [Han 15] • Regular. Route / Bonn. Route Our work: (i) Parallel MILP-based panel routing scheme for each layer (intra-layer parallel routing) (ii) Sequential layer by layer routing (inter-layer sequential routing) (iii) Comprehends connectivity and design rule constraints 30

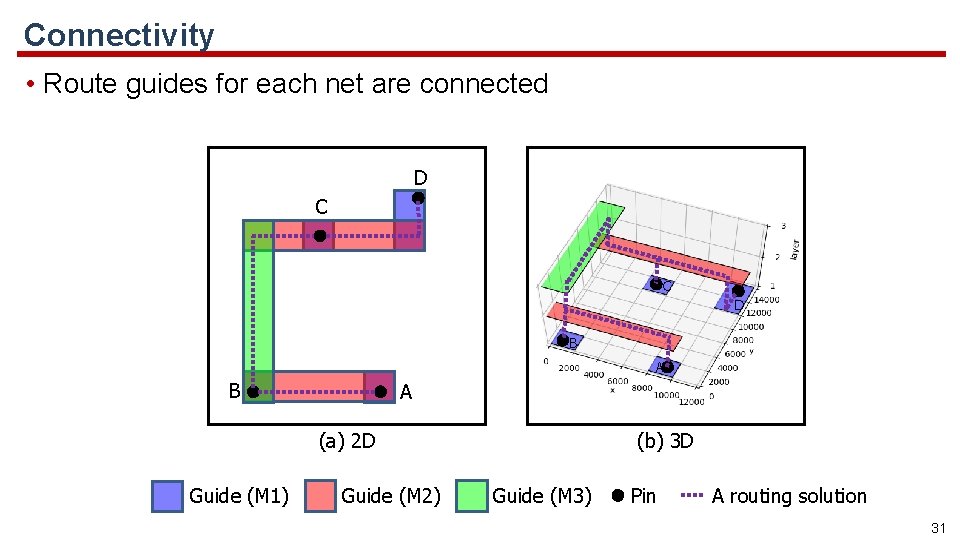

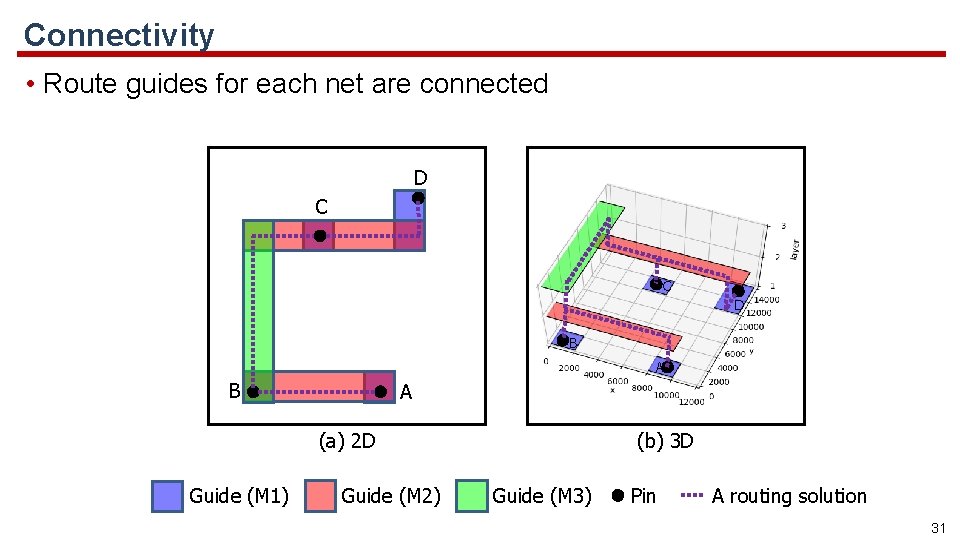

Connectivity • Route guides for each net are connected D C C D B A (a) 2 D Guide (M 1) Guide (M 2) (b) 3 D Guide (M 3) Pin A routing solution 31