EE 4271 VLSI Design Fall 2013 VLSI Quadratic

- Slides: 28

EE 4271 VLSI Design, Fall 2013 VLSI Quadratic Placement 3/8/2021 1

Problem formulation • Input: – Blocks (standard cells and macros) B 1, . . . , Bn – Shapes and Pin Positions for each block Bi – Nets N 1, . . . , Nm • Output: – Coordinates (xi , yi ) for block Bi. – The total wirelength as an estimation of timing is minimized. 3/8/2021 2

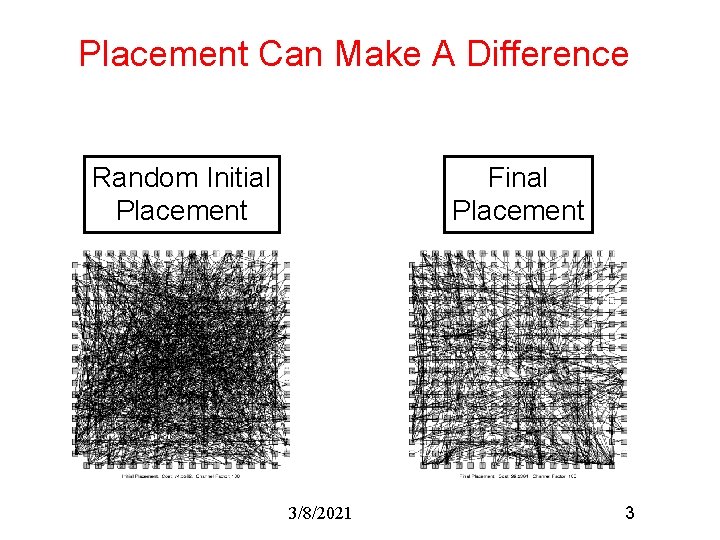

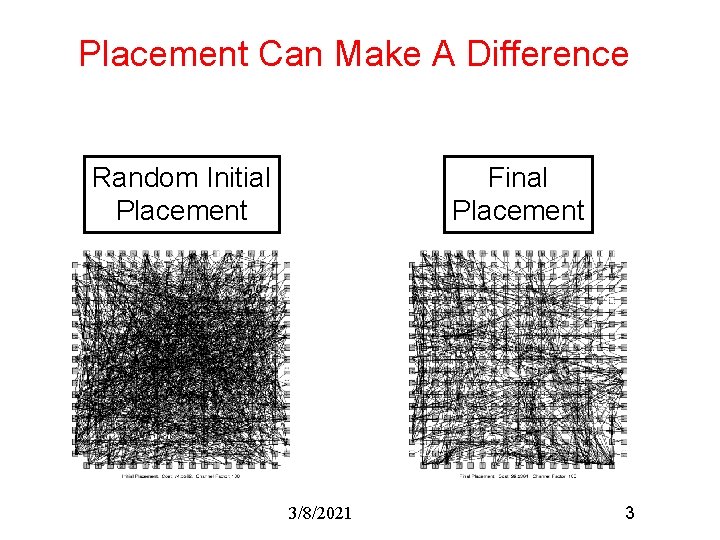

Placement Can Make A Difference Random Initial Placement Final Placement 3/8/2021 3

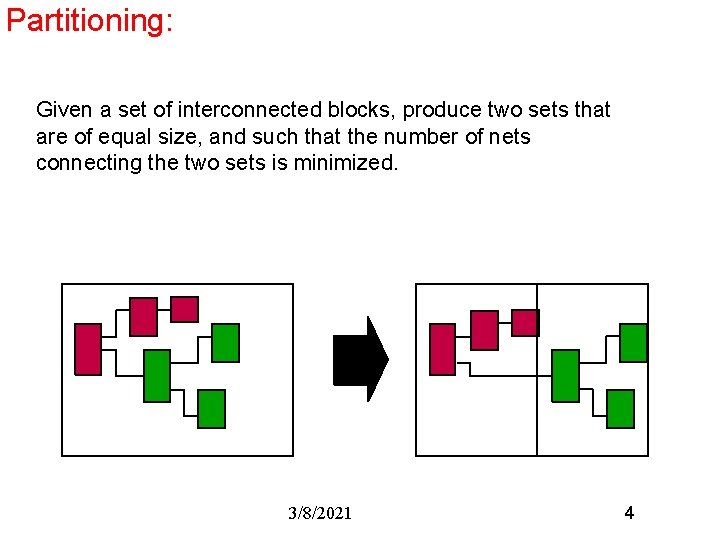

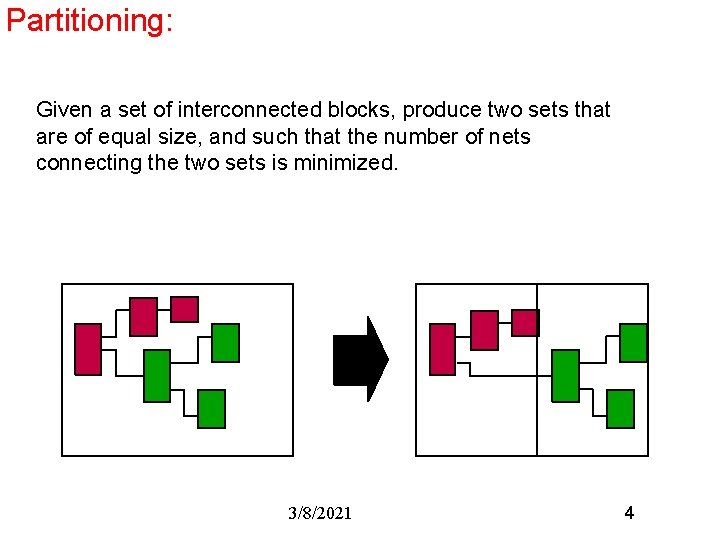

Partitioning: Given a set of interconnected blocks, produce two sets that are of equal size, and such that the number of nets connecting the two sets is minimized. 3/8/2021 4

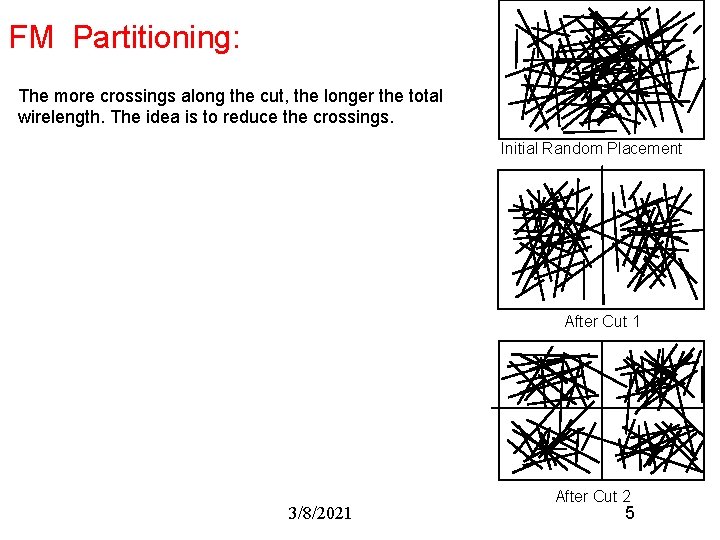

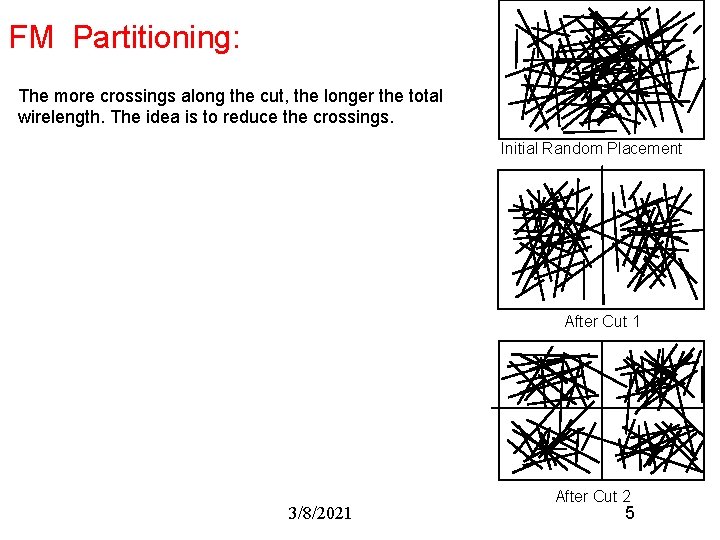

FM Partitioning: The more crossings along the cut, the longer the total wirelength. The idea is to reduce the crossings. Initial Random Placement After Cut 1 3/8/2021 After Cut 2 5

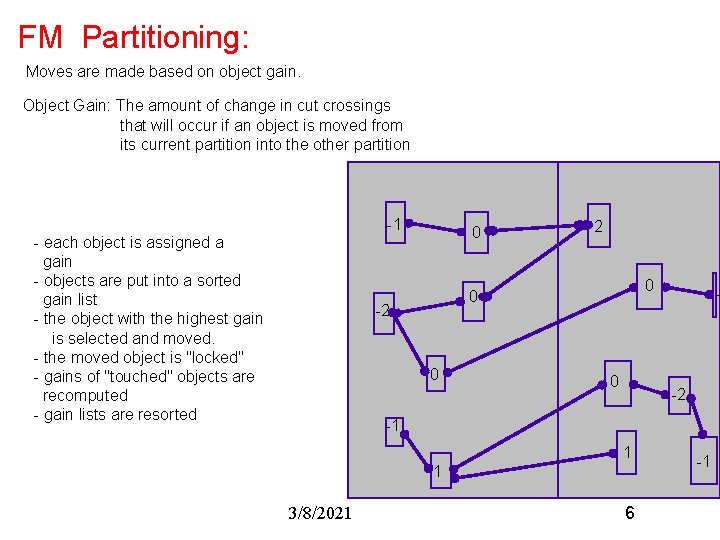

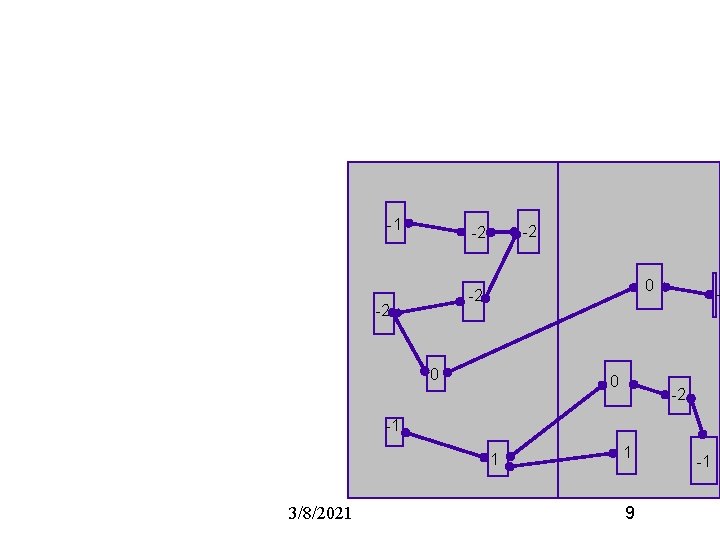

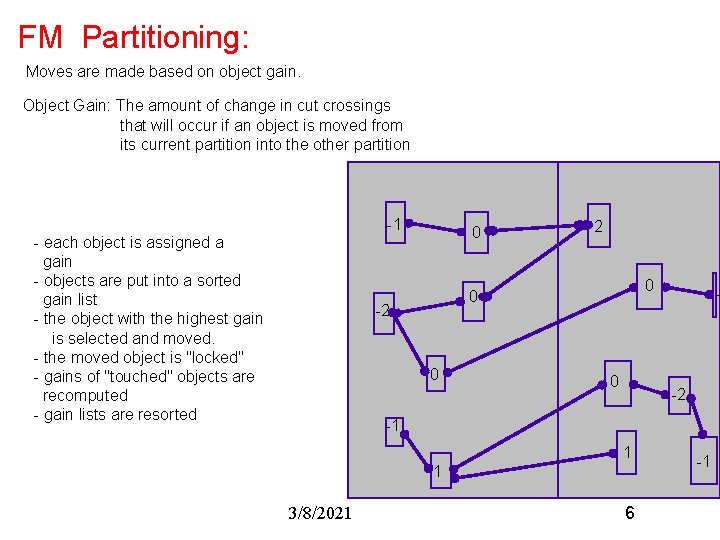

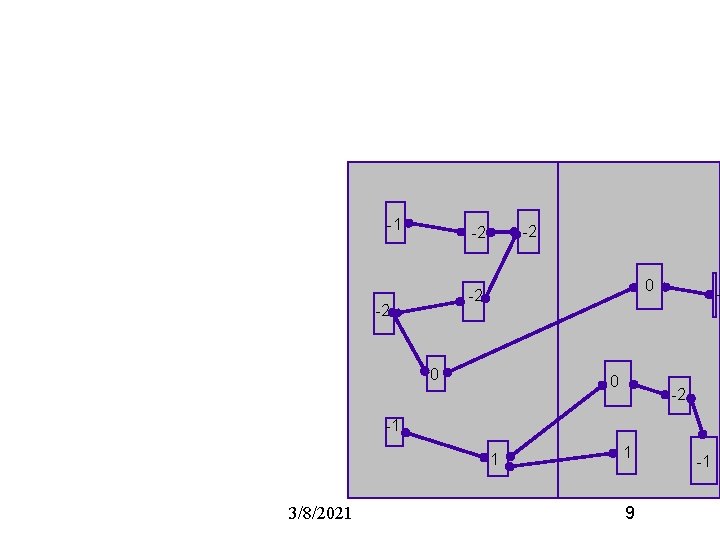

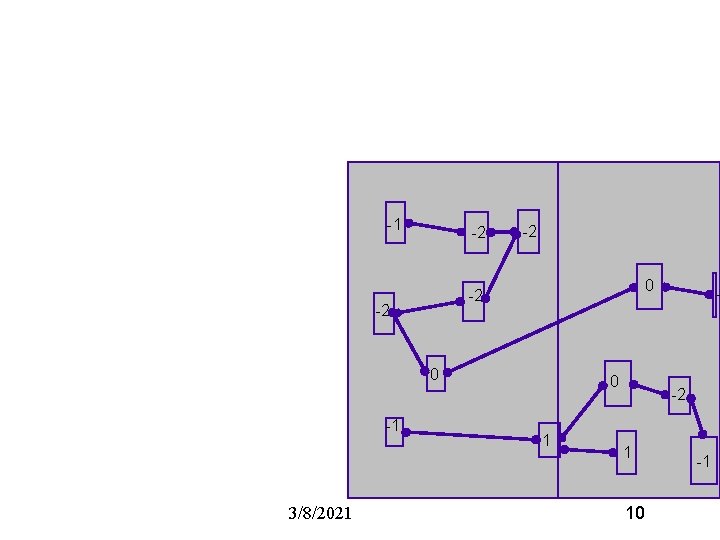

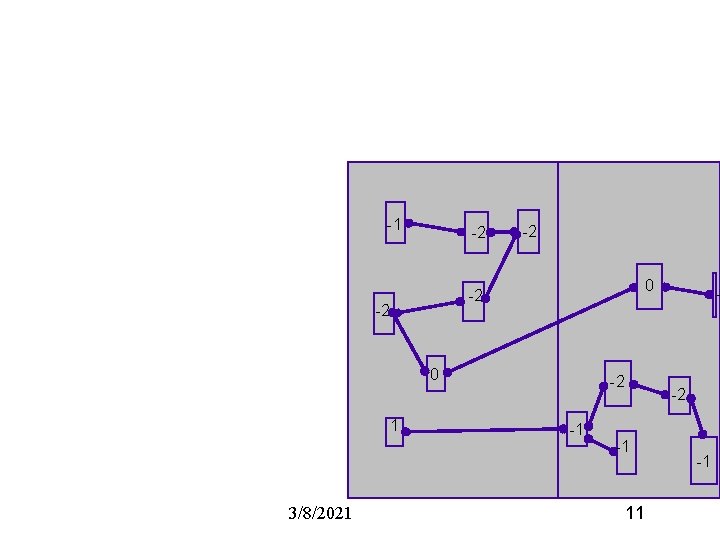

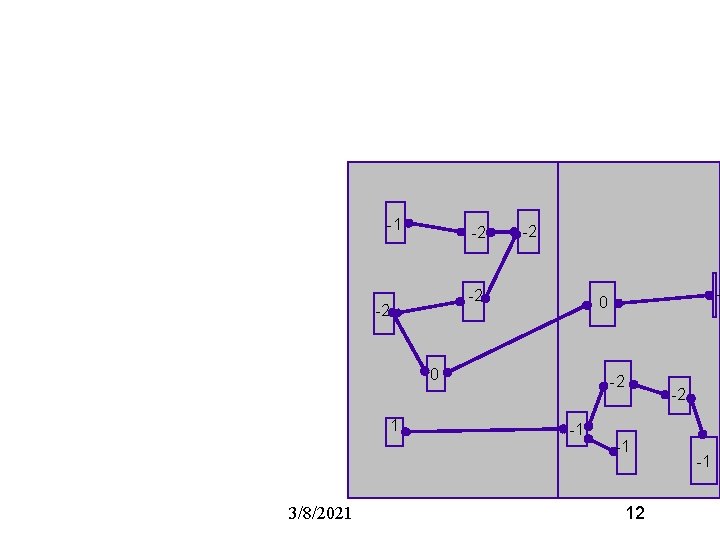

FM Partitioning: Moves are made based on object gain. Object Gain: The amount of change in cut crossings that will occur if an object is moved from its current partition into the other partition -1 - each object is assigned a gain - objects are put into a sorted gain list - the object with the highest gain is selected and moved. - the moved object is "locked" - gains of "touched" objects are recomputed - gain lists are resorted 0 2 0 0 - -2 -1 1 1 3/8/2021 6 -1

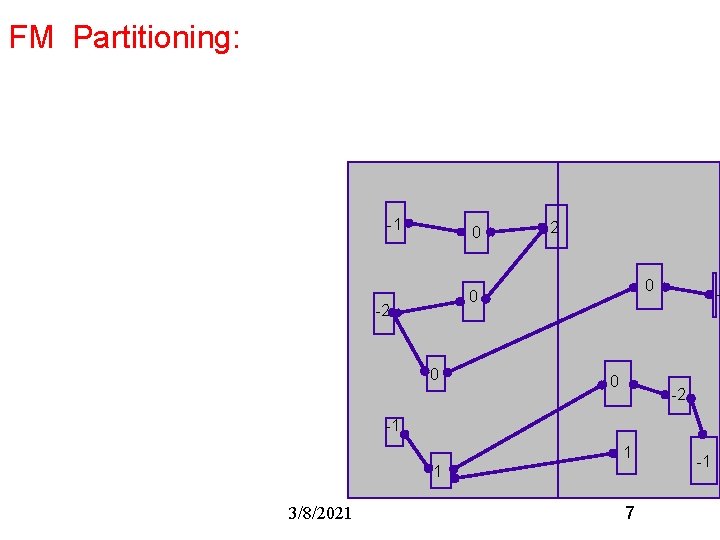

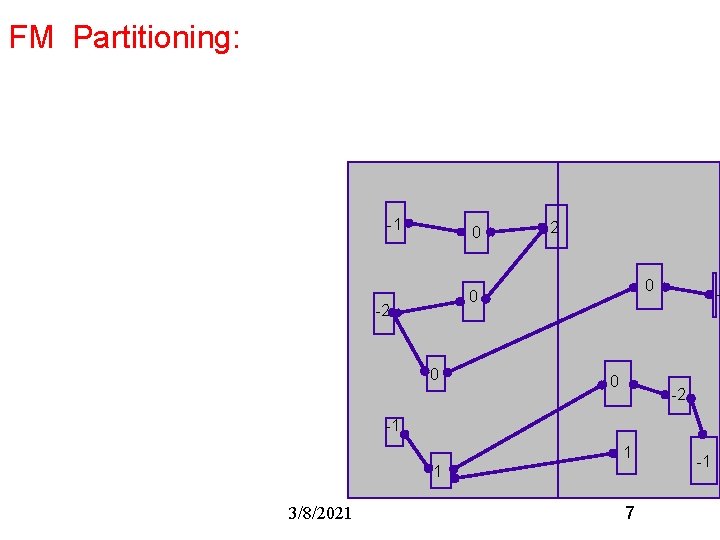

FM Partitioning: -1 0 2 0 0 - -2 -1 1 1 3/8/2021 7 -1

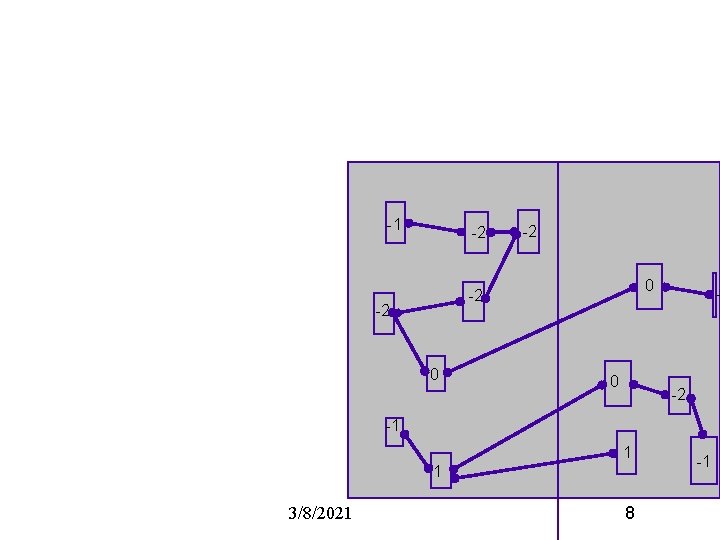

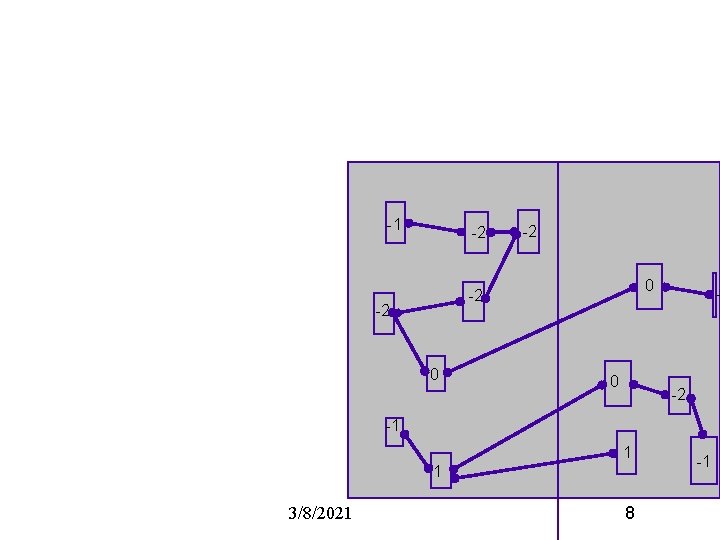

-1 -2 -2 0 0 - -2 -1 1 1 3/8/2021 8 -1

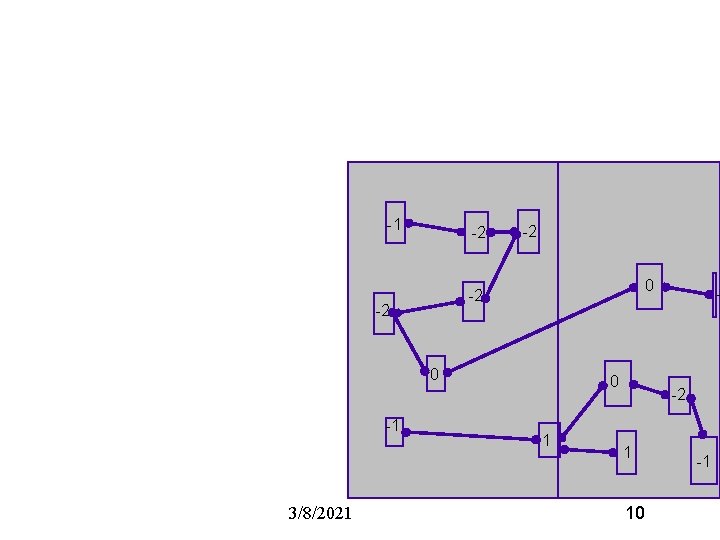

-1 -2 -2 0 0 - -2 -1 1 3/8/2021 1 9 -1

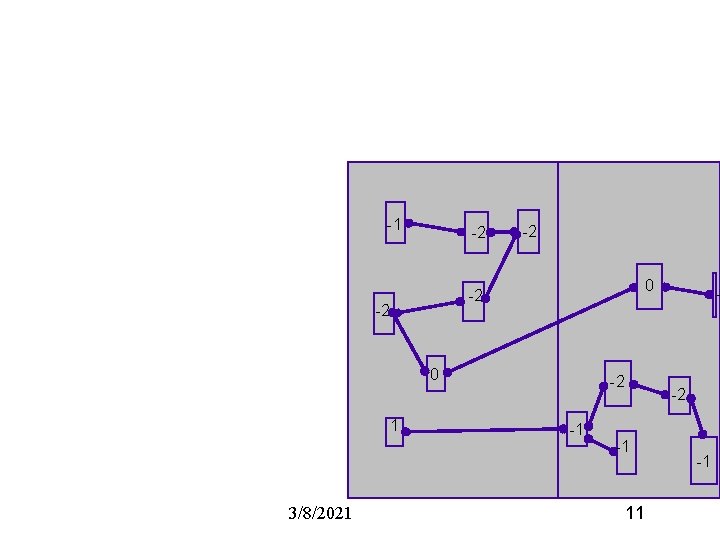

-1 -2 -2 0 -1 3/8/2021 0 1 - -2 1 10 -1

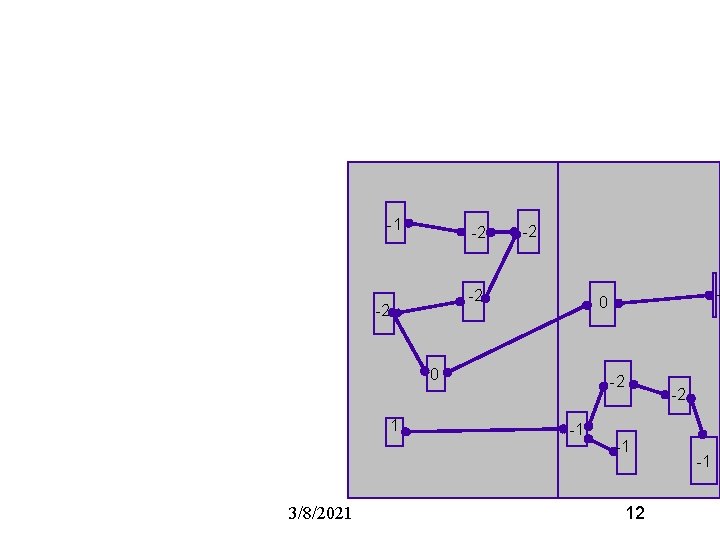

-1 -2 -2 0 1 3/8/2021 -2 -1 - -2 -1 11 -1

-1 -2 -2 0 1 3/8/2021 - 0 -2 -1 12 -1

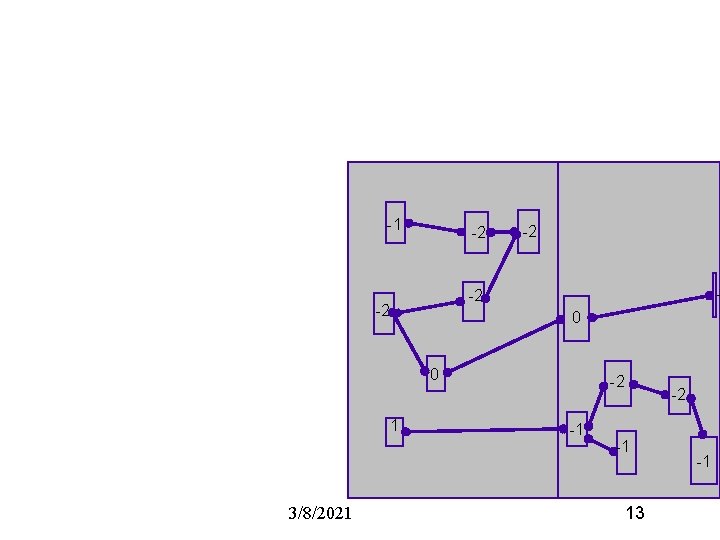

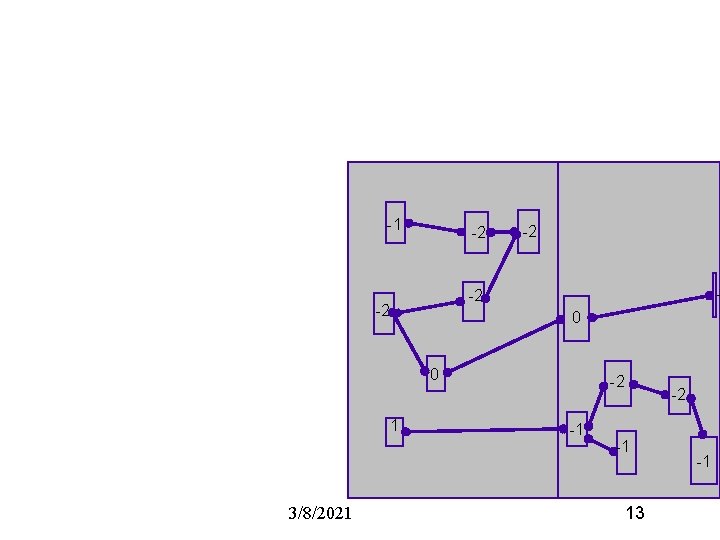

-1 -2 -2 -2 0 0 1 3/8/2021 -2 -1 13 -1

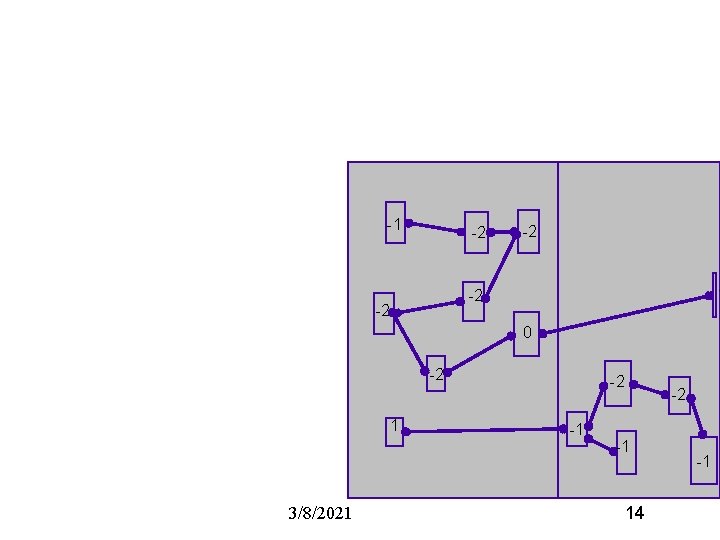

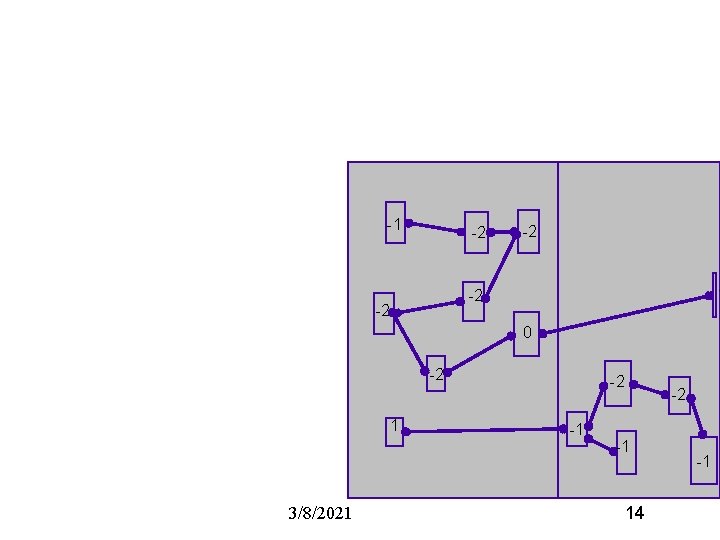

-1 -2 -2 0 -2 1 3/8/2021 -2 -1 14 -1

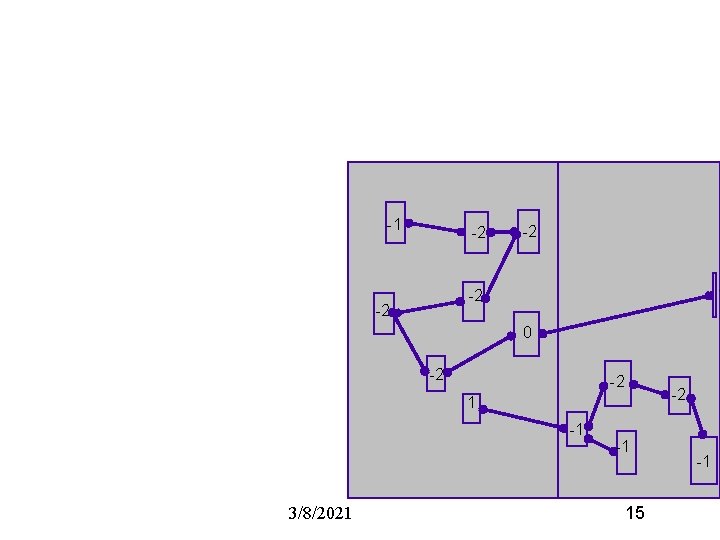

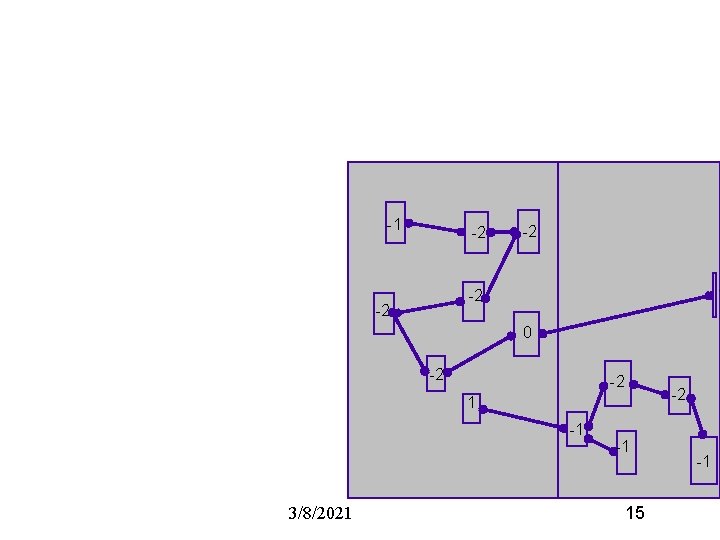

-1 -2 -2 0 -2 -2 -2 1 -1 3/8/2021 -1 15 -1

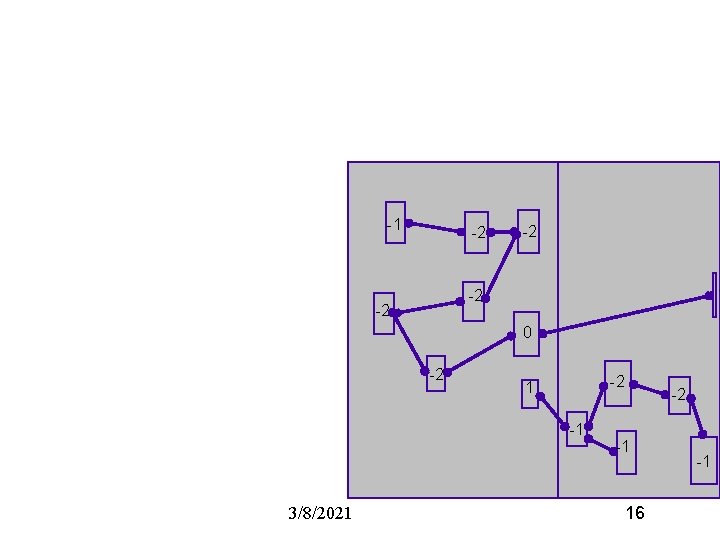

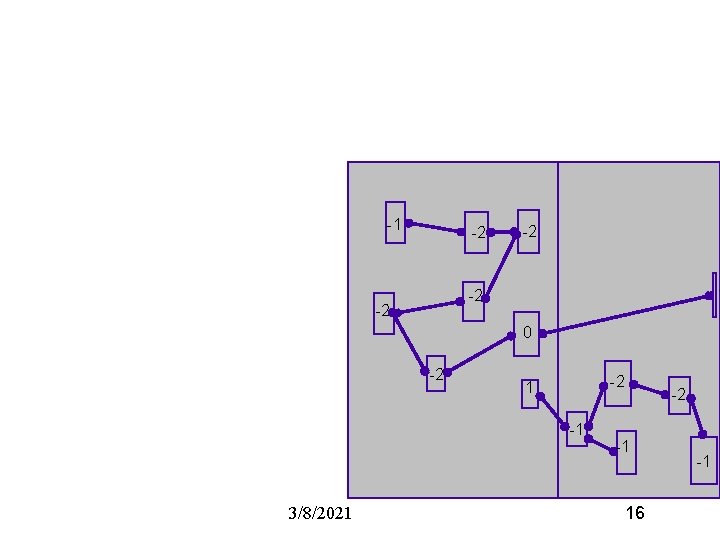

-1 -2 -2 0 -2 -2 1 -1 3/8/2021 -2 -1 16 -1

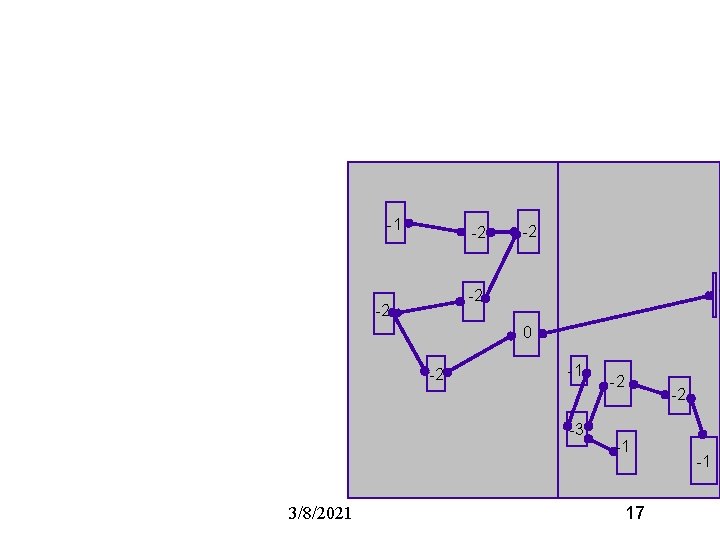

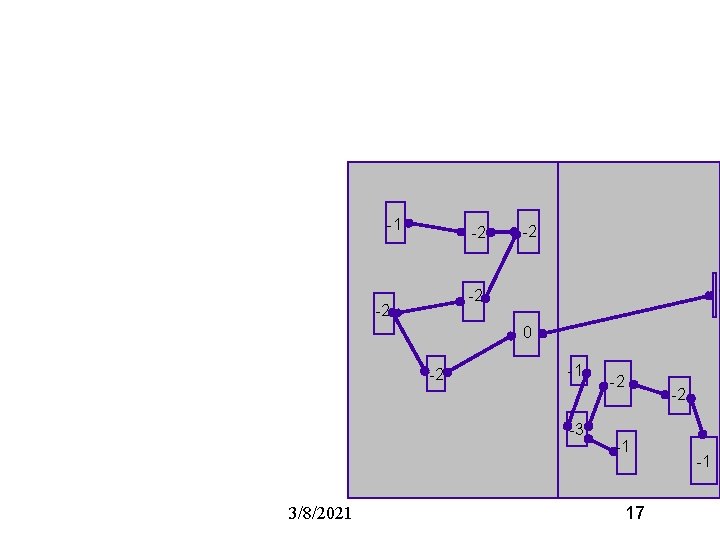

-1 -2 -2 0 -2 -1 -3 3/8/2021 -2 -2 -1 17 -1

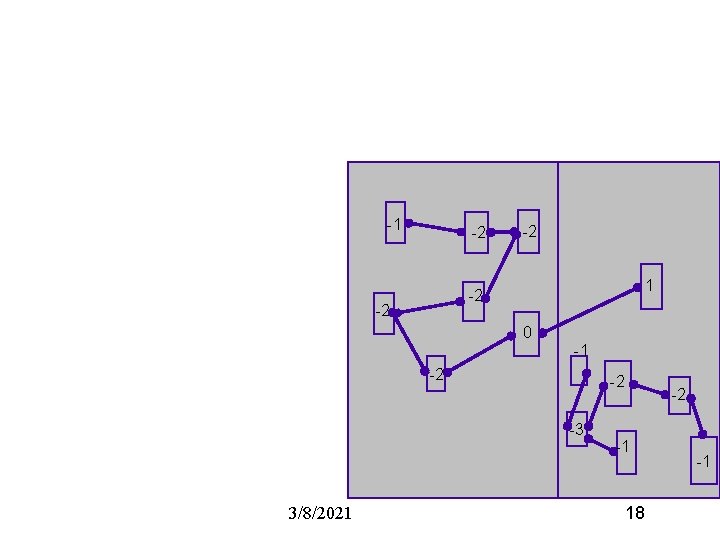

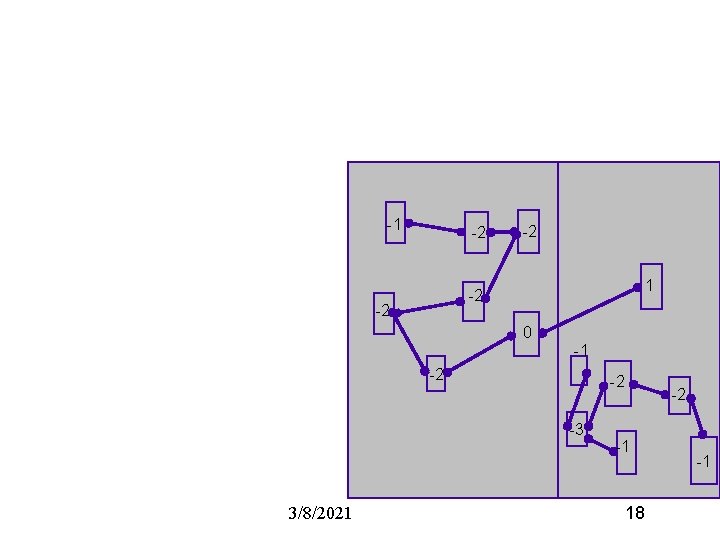

-1 -2 -2 0 -1 -2 -2 -3 3/8/2021 -2 -1 18 -1

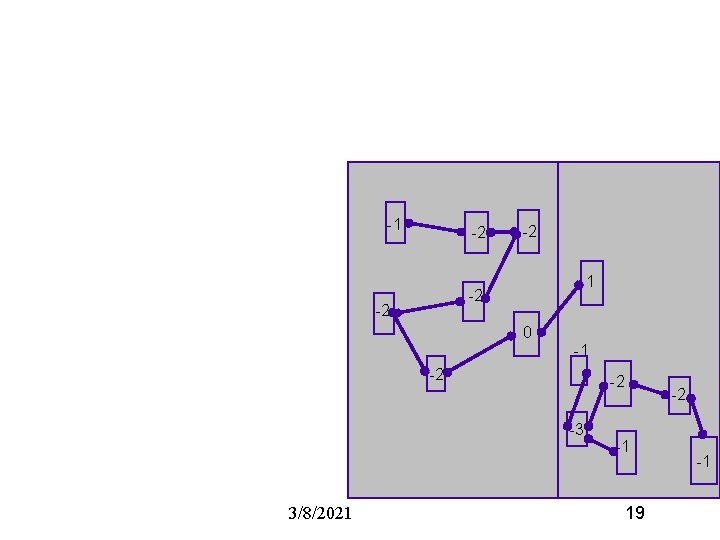

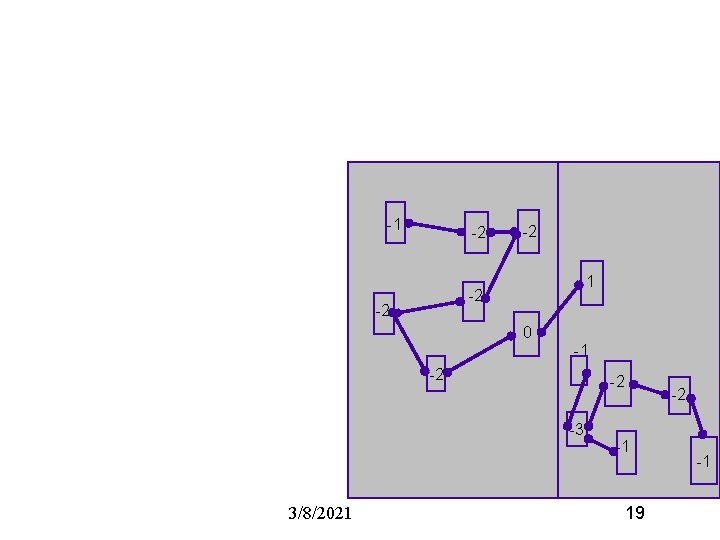

-1 -2 -2 0 -1 -2 -2 -3 3/8/2021 -2 -1 19 -1

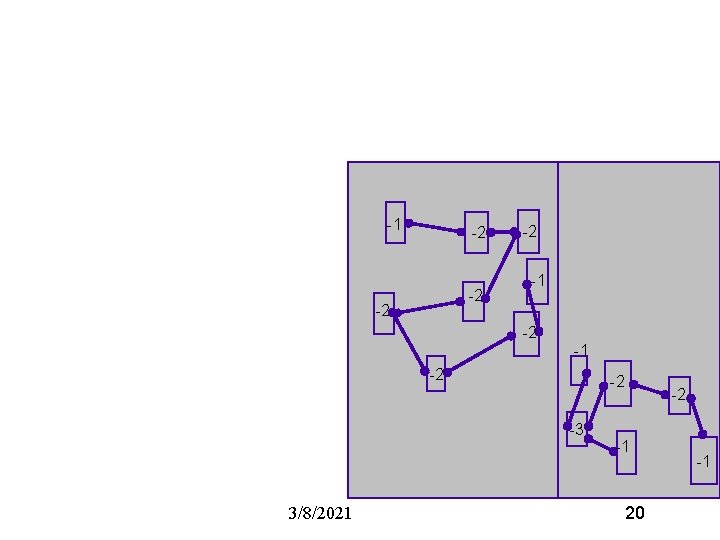

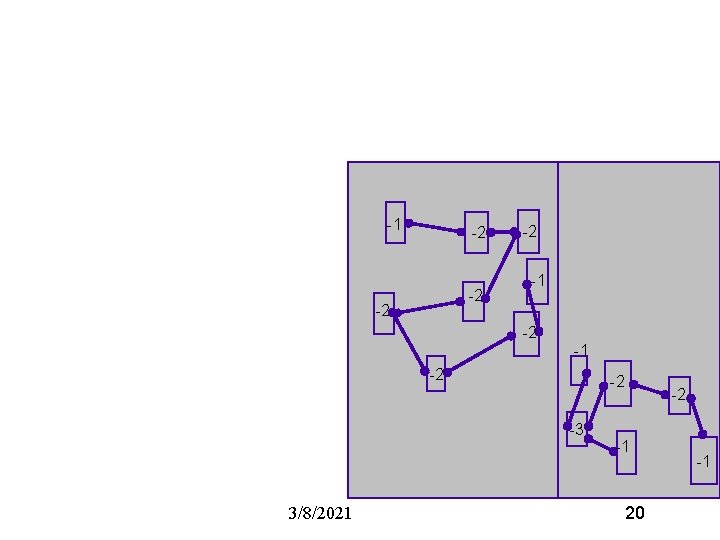

-1 -2 -2 -3 3/8/2021 -2 -1 20 -1

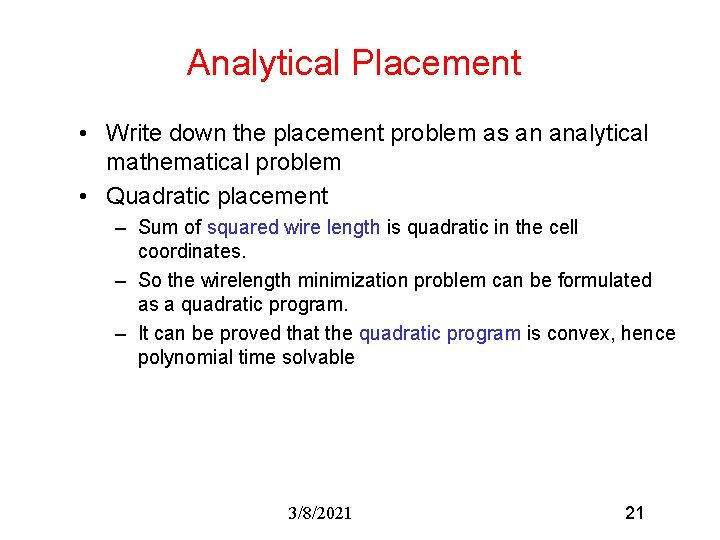

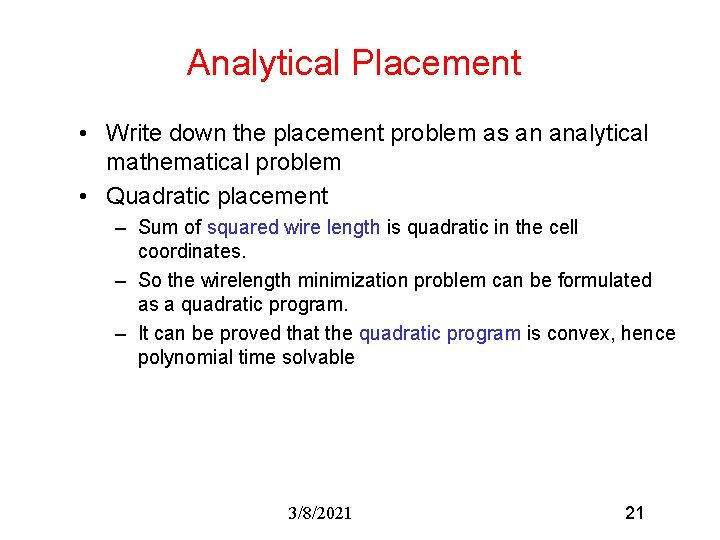

Analytical Placement • Write down the placement problem as an analytical mathematical problem • Quadratic placement – Sum of squared wire length is quadratic in the cell coordinates. – So the wirelength minimization problem can be formulated as a quadratic program. – It can be proved that the quadratic program is convex, hence polynomial time solvable 3/8/2021 21

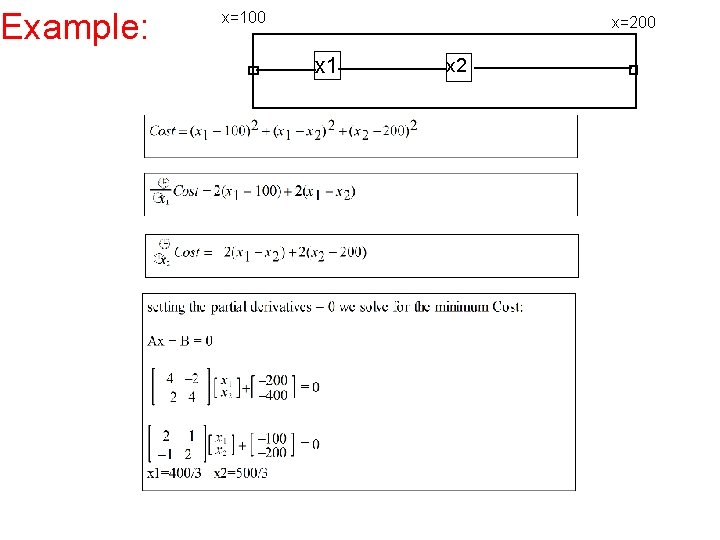

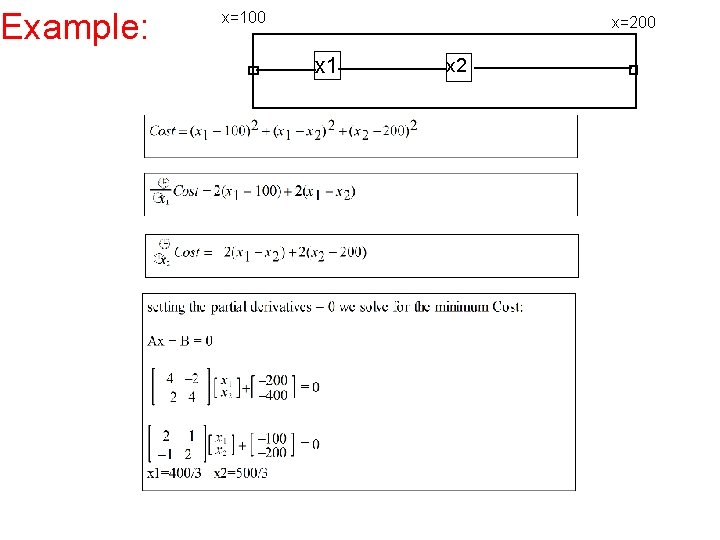

Example: x=100 x=200 x 1 3/8/2021 x 2 22

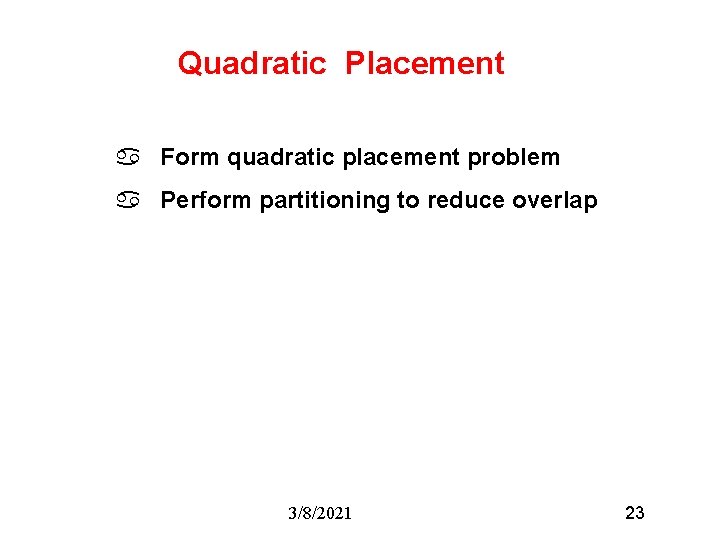

Quadratic Placement a Form quadratic placement problem a Perform partitioning to reduce overlap 3/8/2021 23

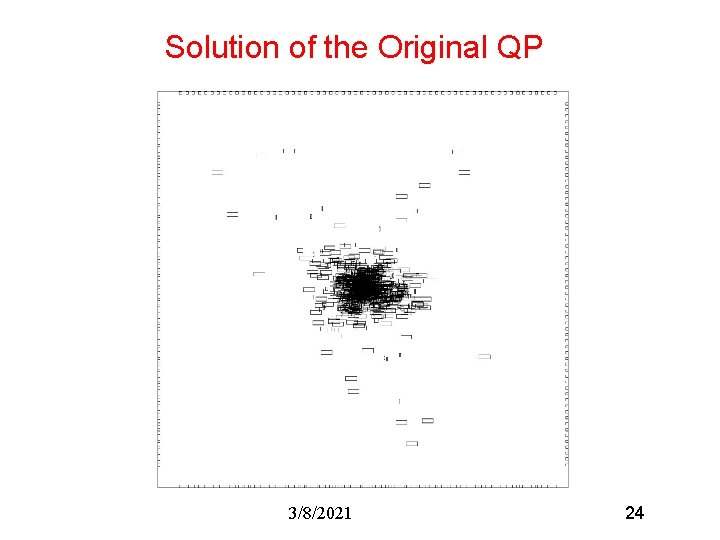

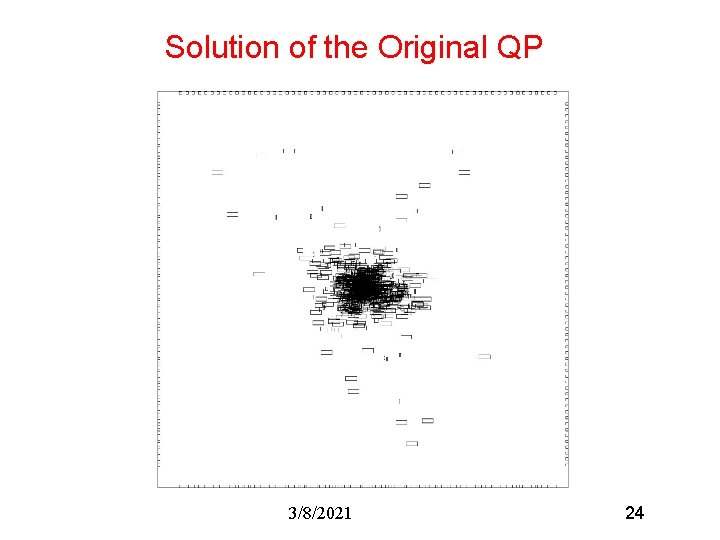

Solution of the Original QP 3/8/2021 24

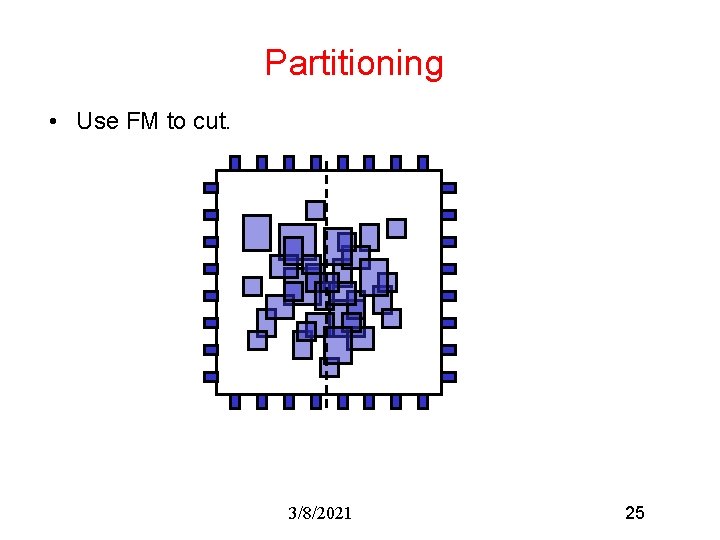

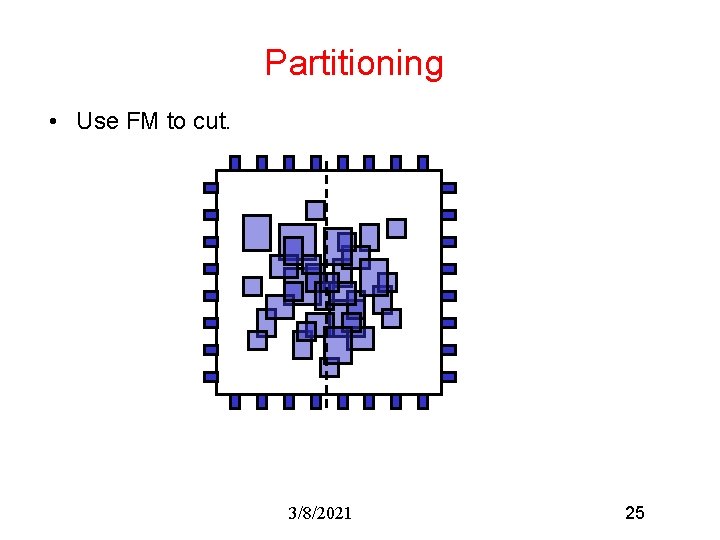

Partitioning • Use FM to cut. 3/8/2021 25

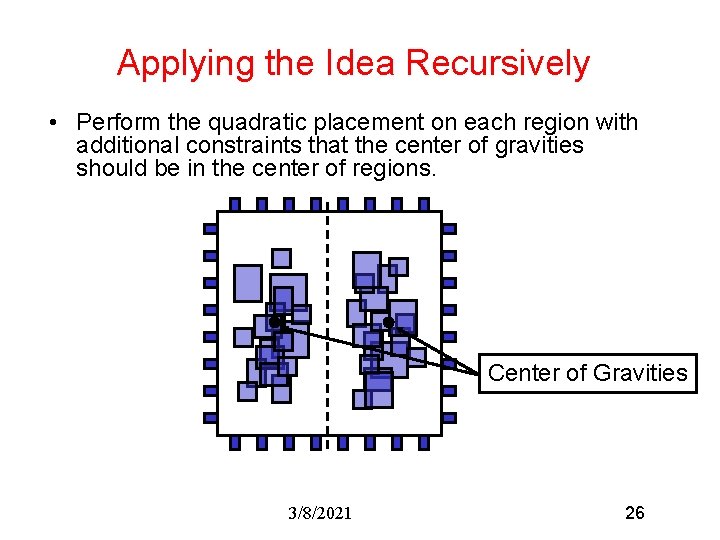

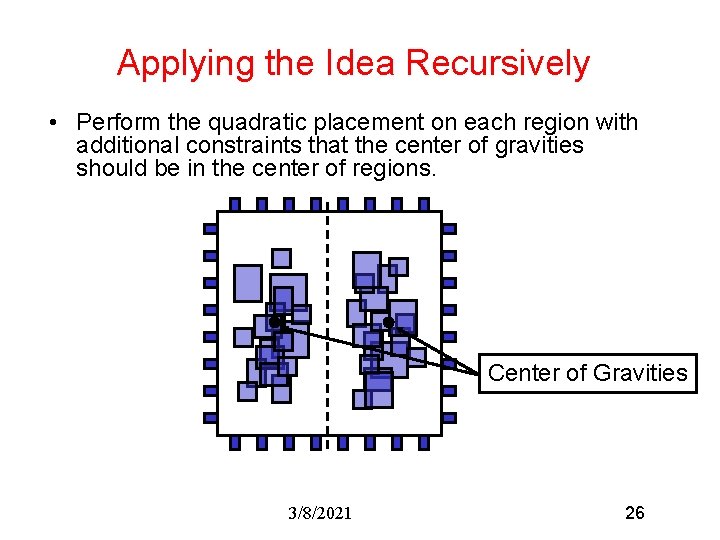

Applying the Idea Recursively • Perform the quadratic placement on each region with additional constraints that the center of gravities should be in the center of regions. Center of Gravities 3/8/2021 26

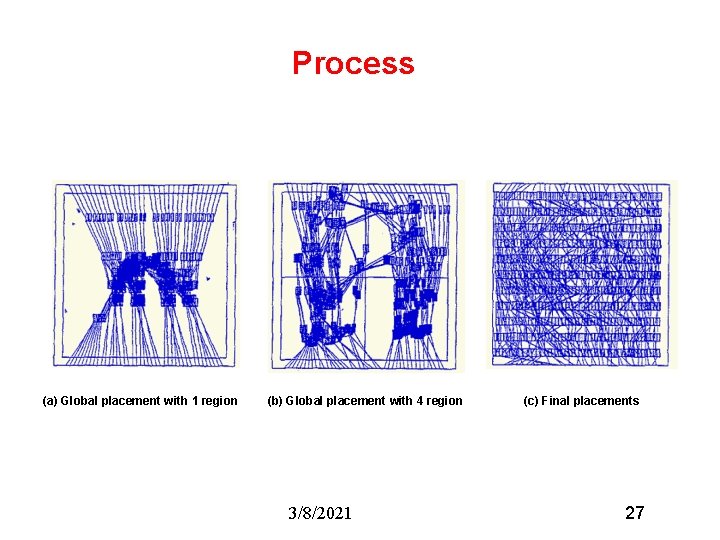

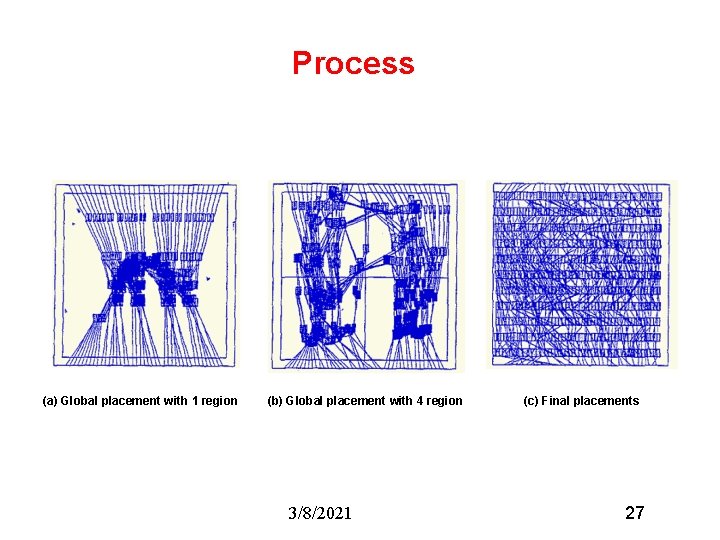

Process (a) Global placement with 1 region (b) Global placement with 4 region 3/8/2021 (c) Final placements 27

Summary • Definition of VLSI quadratic placement problem • Partitioning technique 3/8/2021 28