EE 4271 VLSI Design Dr Shiyan Hu Office

- Slides: 20

EE 4271 VLSI Design Dr. Shiyan Hu Office: EERC 731 shiyan@mtu. edu The Inverter Adapted and modified from Digital Integrated Circuits: A Design Perspective by Jan M. Rabaey, Anantha Chandrakasan, and Borivoje Nikolic. © Digital Integrated Circuits 2 nd Inverter

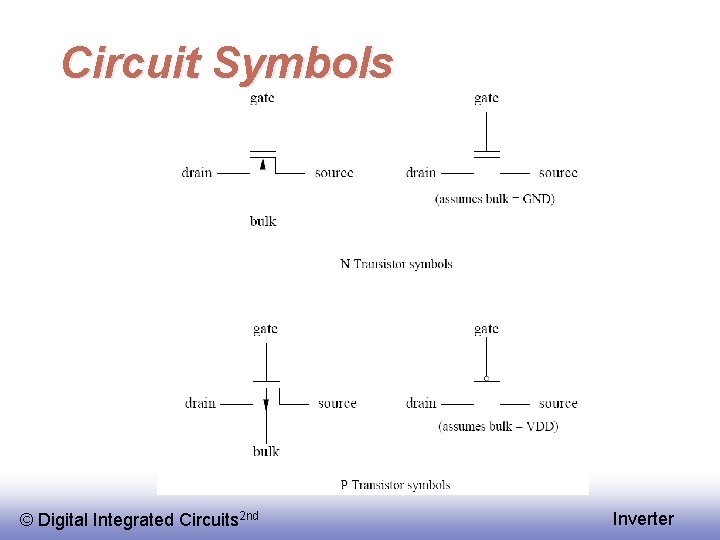

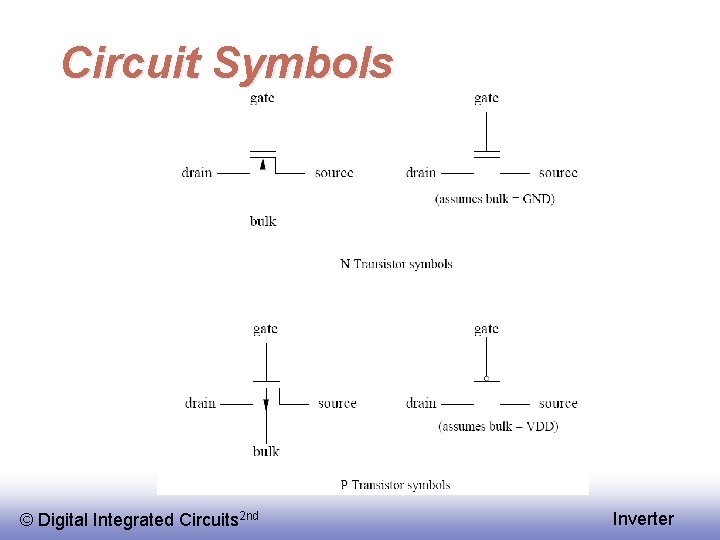

Circuit Symbols © Digital Integrated Circuits 2 nd Inverter

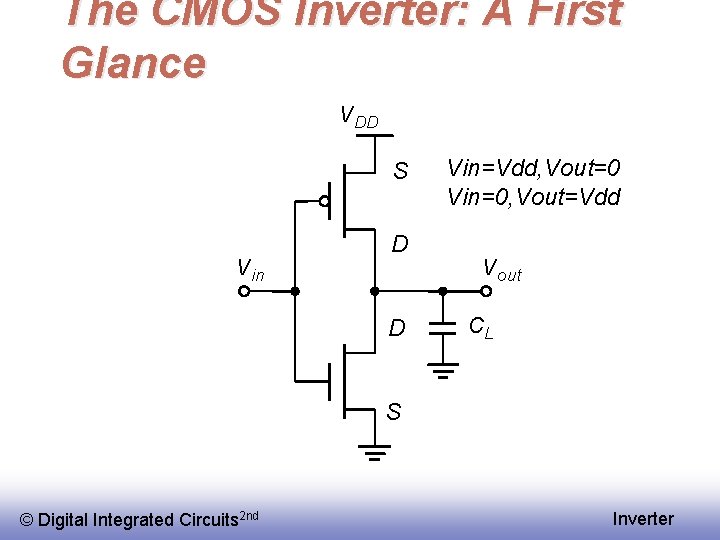

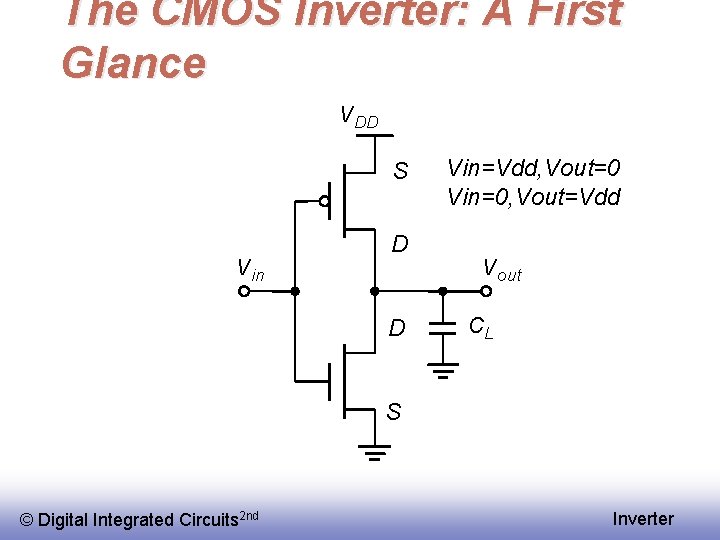

The CMOS Inverter: A First Glance V DD S V in D D Vin=Vdd, Vout=0 Vin=0, Vout=Vdd V out CL S © Digital Integrated Circuits 2 nd Inverter

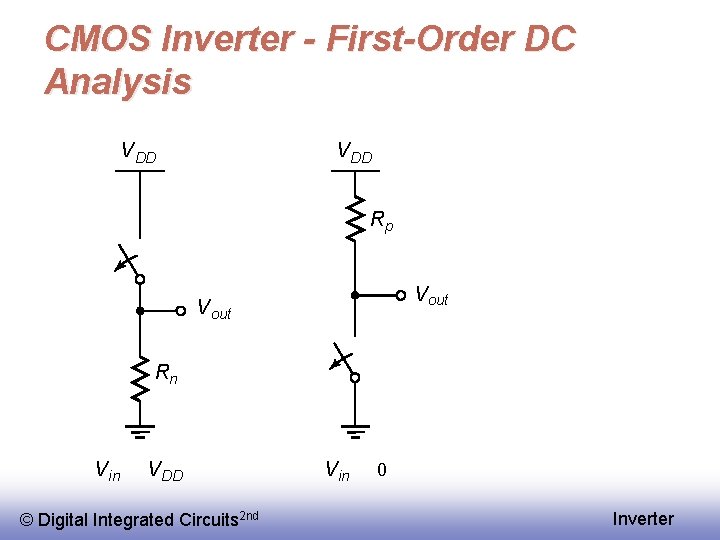

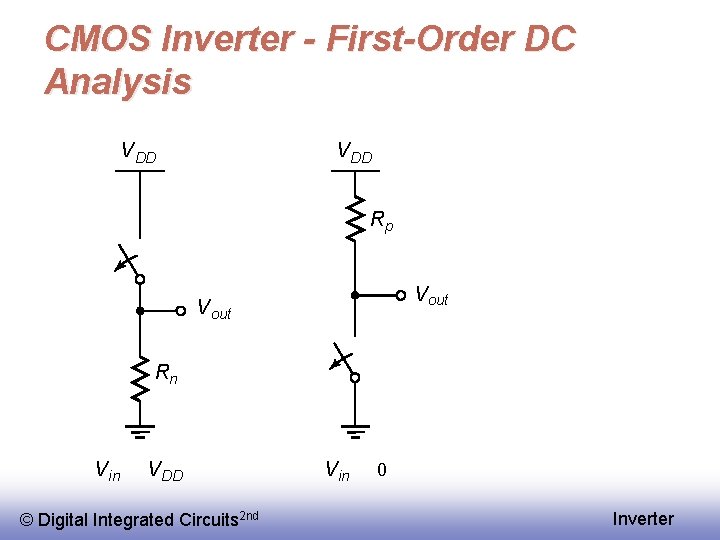

CMOS Inverter - First-Order DC Analysis V DD Rp V out Rn V in V DD © Digital Integrated Circuits 2 nd V in 0 Inverter

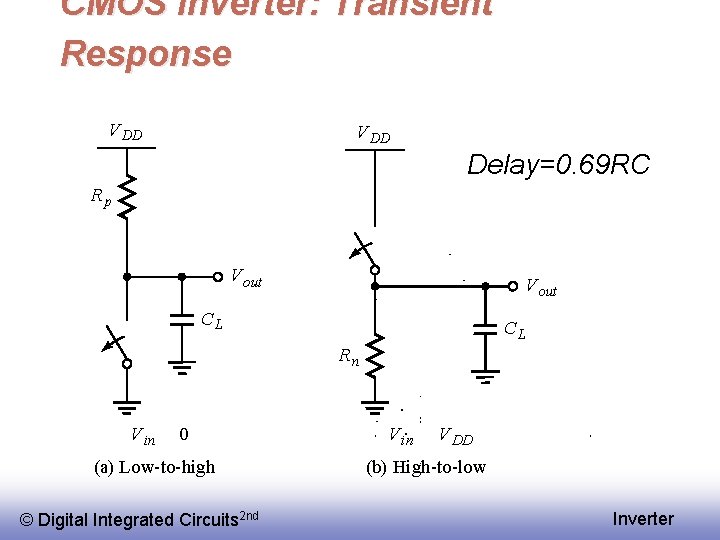

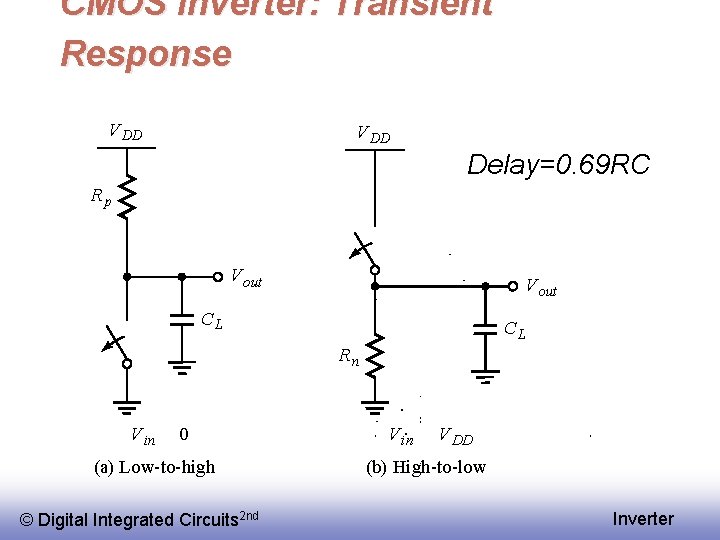

CMOS Inverter: Transient Response V DD Delay=0. 69 RC Rp V out CL CL Rn V in 0 (a) Low-to-high © Digital Integrated Circuits 2 nd V in V DD (b) High-to-low Inverter

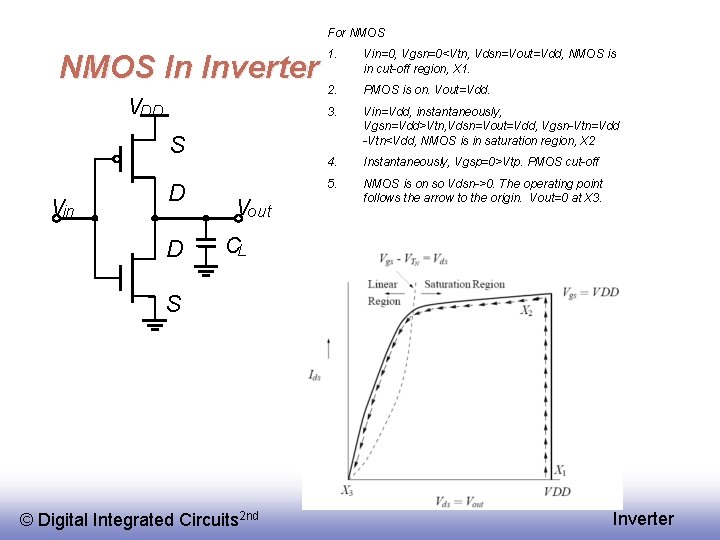

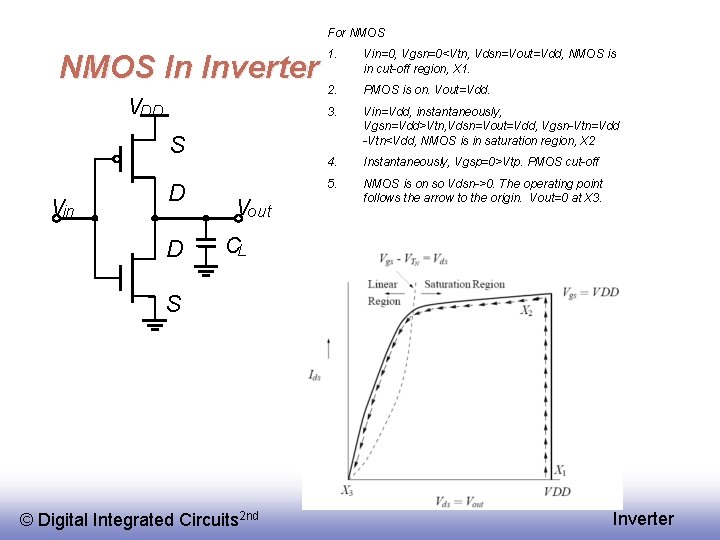

For NMOS In Inverter VDD S Vin D D Vout 1. Vin=0, Vgsn=0<Vtn, Vdsn=Vout=Vdd, NMOS is in cut-off region, X 1. 2. PMOS is on. Vout=Vdd. 3. Vin=Vdd, instantaneously, Vgsn=Vdd>Vtn, Vdsn=Vout=Vdd, Vgsn-Vtn=Vdd -Vtn<Vdd, NMOS is in saturation region, X 2 4. Instantaneously, Vgsp=0>Vtp. PMOS cut-off 5. NMOS is on so Vdsn->0. The operating point follows the arrow to the origin. Vout=0 at X 3. CL S © Digital Integrated Circuits 2 nd Inverter

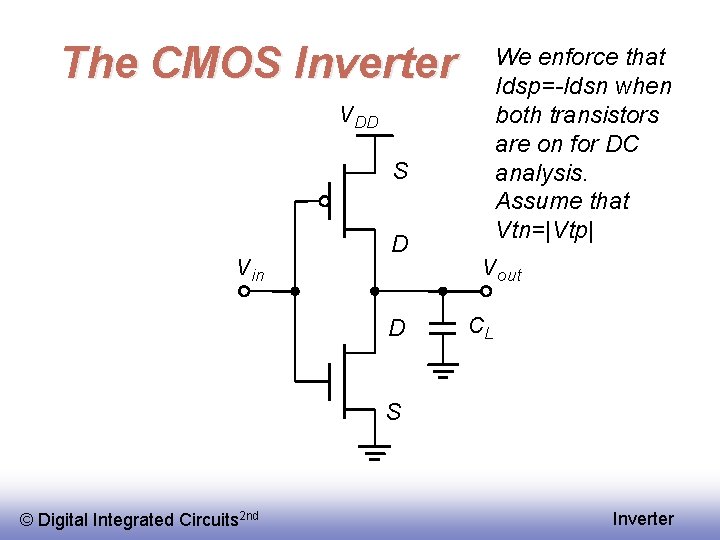

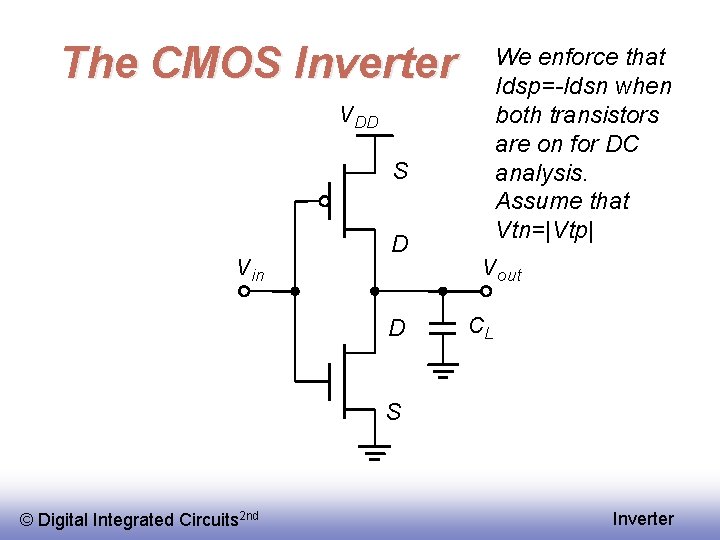

The CMOS Inverter We enforce that Idsp=-Idsn when both transistors are on for DC analysis. Assume that Vtn=|Vtp| V DD S V in D D V out CL S © Digital Integrated Circuits 2 nd Inverter

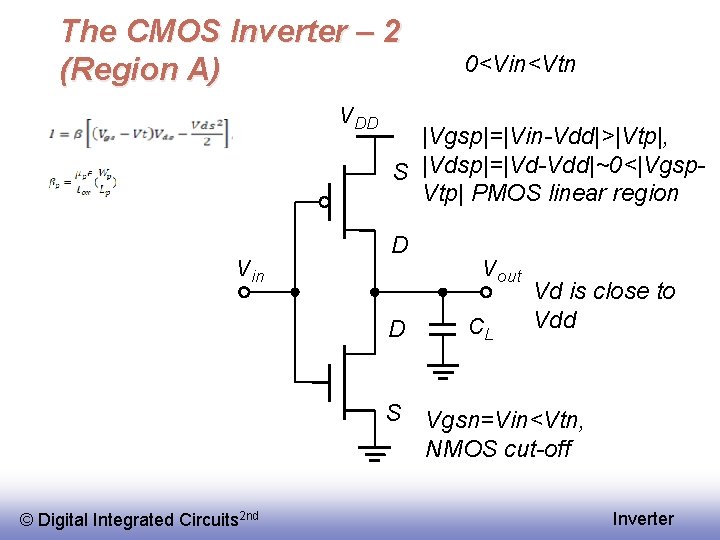

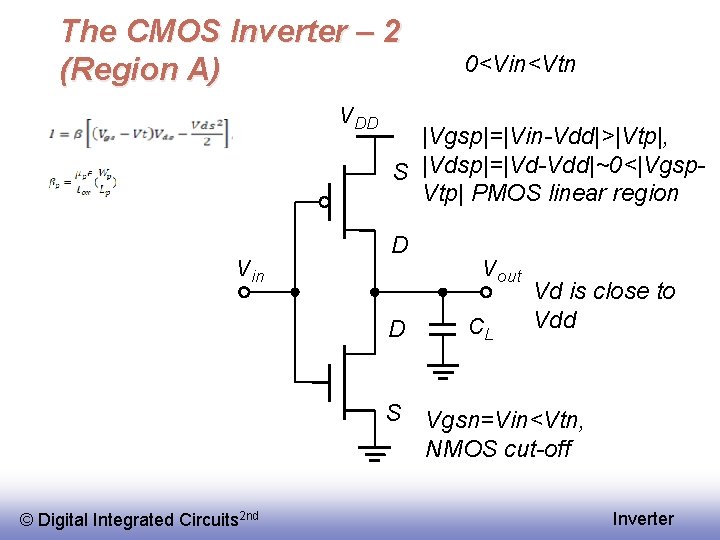

The CMOS Inverter – 2 (Region A) V DD V in |Vgsp|=|Vin-Vdd|>|Vtp|, S |Vdsp|=|Vd-Vdd|~0<|Vgsp. Vtp| PMOS linear region D D S © Digital Integrated Circuits 2 nd 0<Vin<Vtn V out CL Vd is close to Vdd Vgsn=Vin<Vtn, NMOS cut-off Inverter

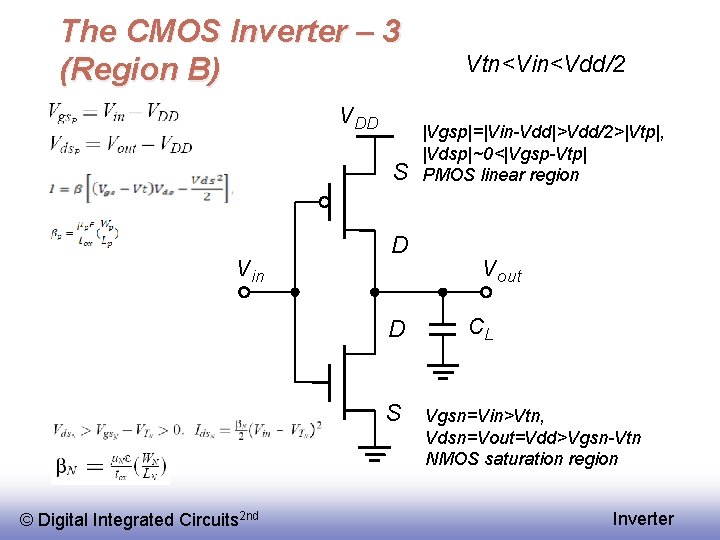

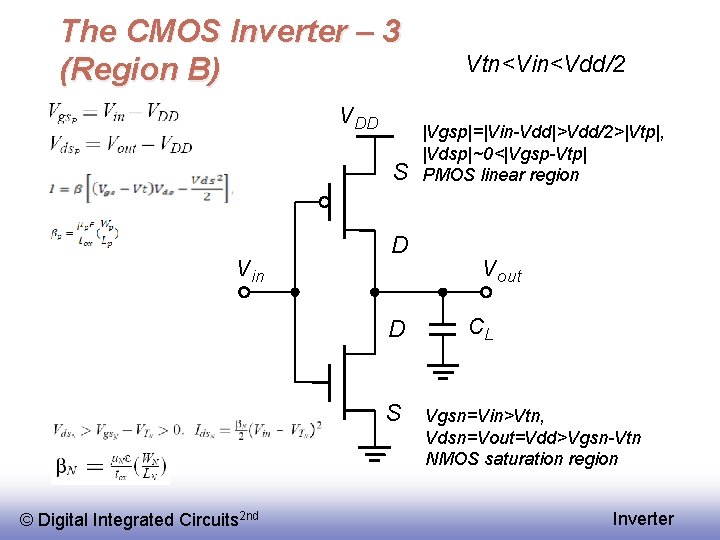

The CMOS Inverter – 3 (Region B) V DD S V in D D S © Digital Integrated Circuits 2 nd Vtn<Vin<Vdd/2 |Vgsp|=|Vin-Vdd|>Vdd/2>|Vtp|, |Vdsp|~0<|Vgsp-Vtp| PMOS linear region V out CL Vgsn=Vin>Vtn, Vdsn=Vout=Vdd>Vgsn-Vtn NMOS saturation region Inverter

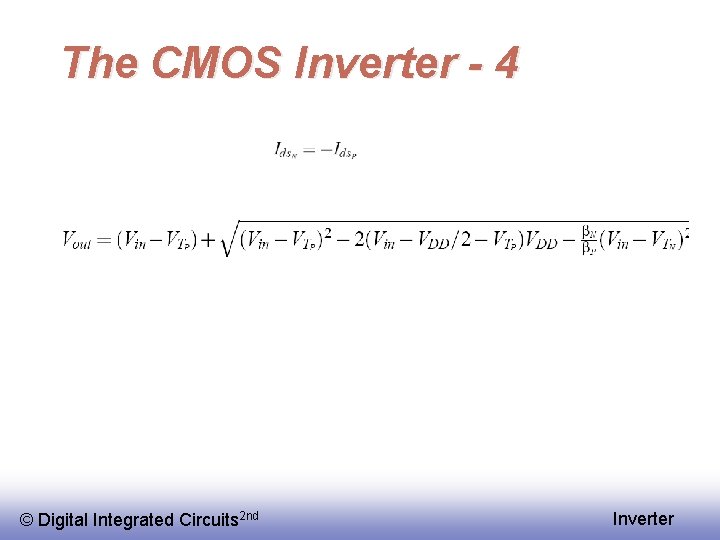

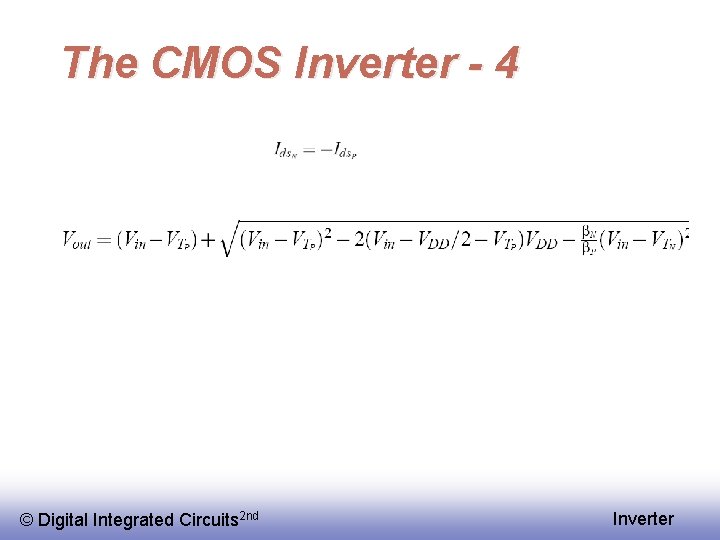

The CMOS Inverter - 4 © Digital Integrated Circuits 2 nd Inverter

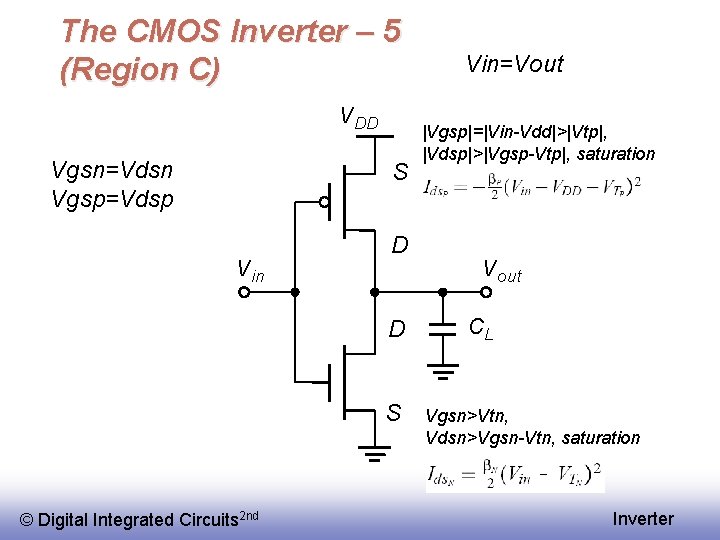

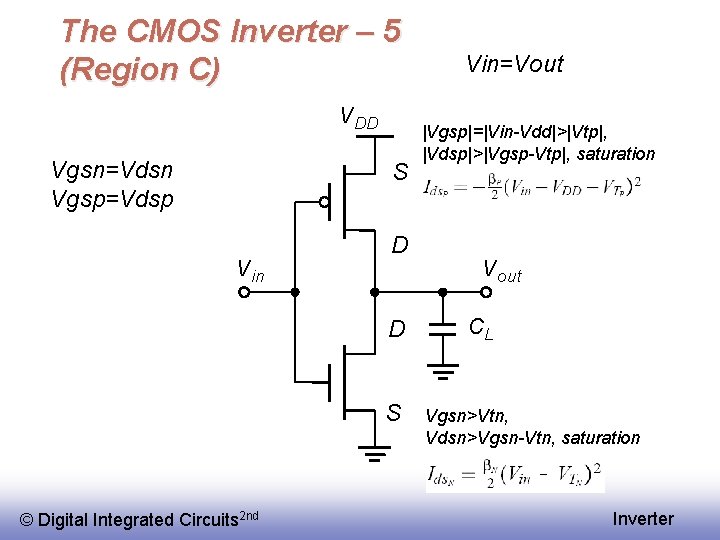

The CMOS Inverter – 5 (Region C) V DD Vgsn=Vdsn Vgsp=Vdsp S V in D D S © Digital Integrated Circuits 2 nd Vin=Vout |Vgsp|=|Vin-Vdd|>|Vtp|, |Vdsp|>|Vgsp-Vtp|, saturation V out CL Vgsn>Vtn, Vdsn>Vgsn-Vtn, saturation Inverter

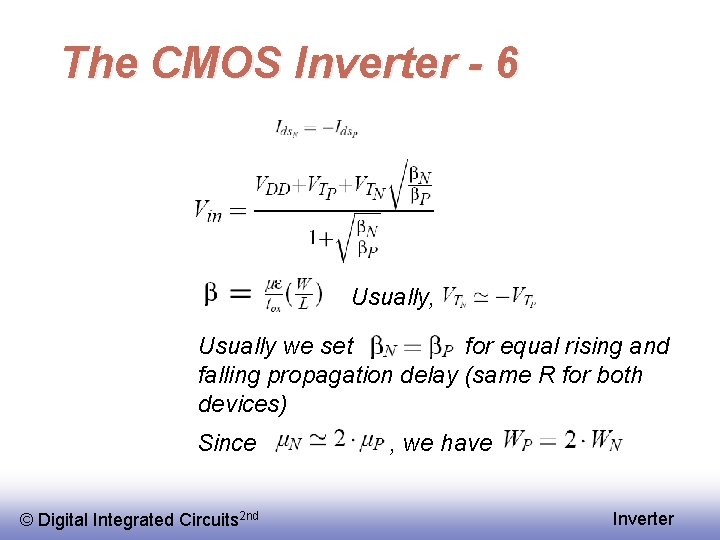

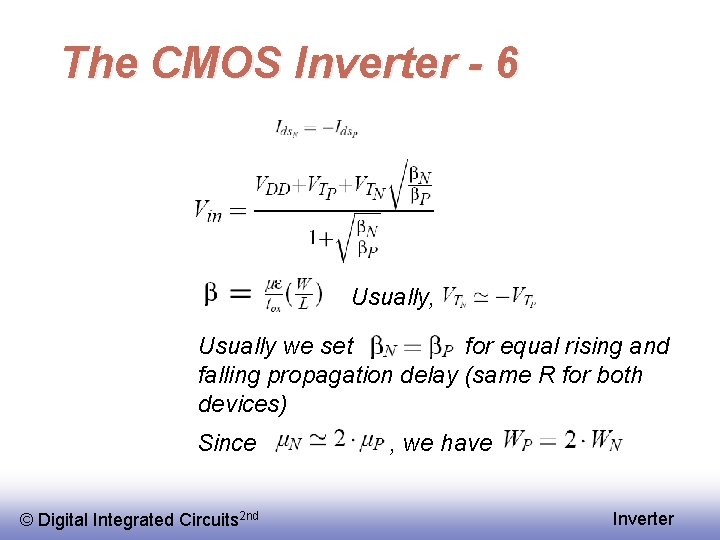

The CMOS Inverter - 6 Usually, Usually we set for equal rising and falling propagation delay (same R for both devices) Since © Digital Integrated Circuits 2 nd , we have Inverter

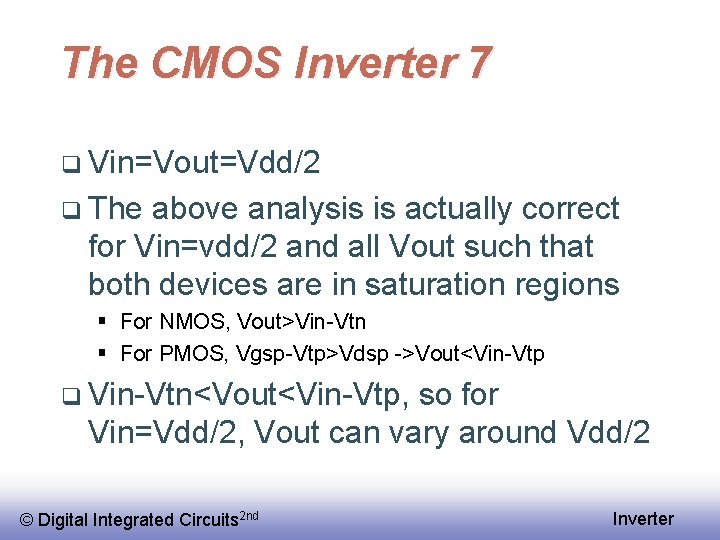

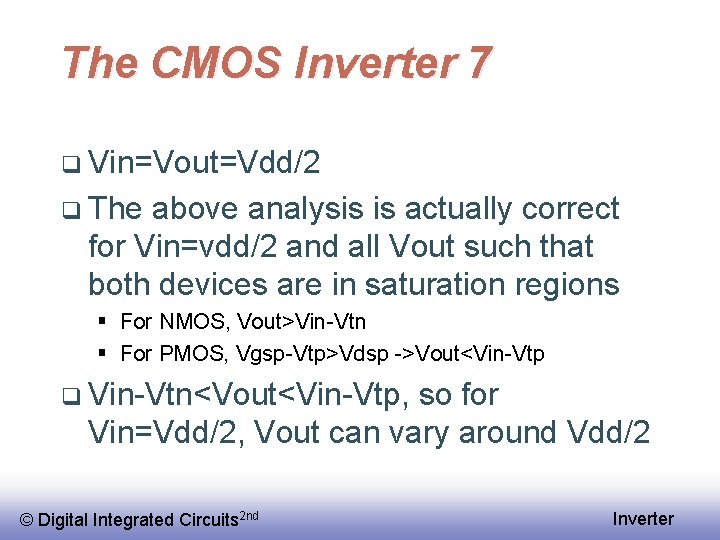

The CMOS Inverter 7 q Vin=Vout=Vdd/2 q The above analysis is actually correct for Vin=vdd/2 and all Vout such that both devices are in saturation regions § For NMOS, Vout>Vin-Vtn § For PMOS, Vgsp-Vtp>Vdsp ->Vout<Vin-Vtp q Vin-Vtn<Vout<Vin-Vtp, so for Vin=Vdd/2, Vout can vary around Vdd/2 © Digital Integrated Circuits 2 nd Inverter

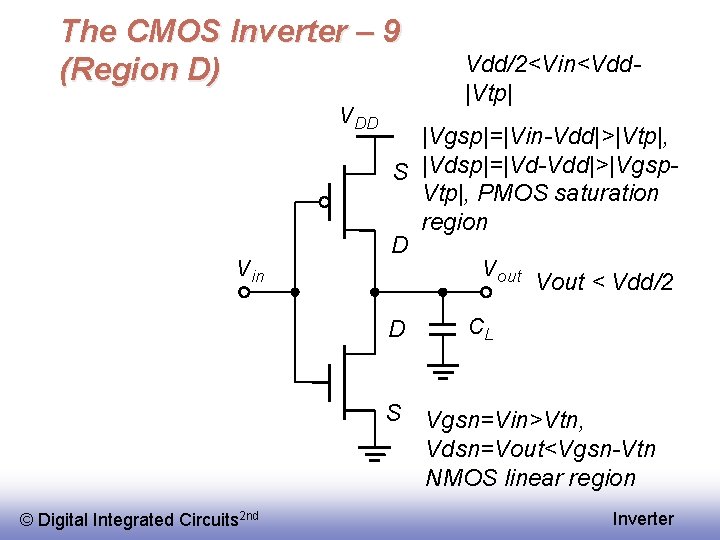

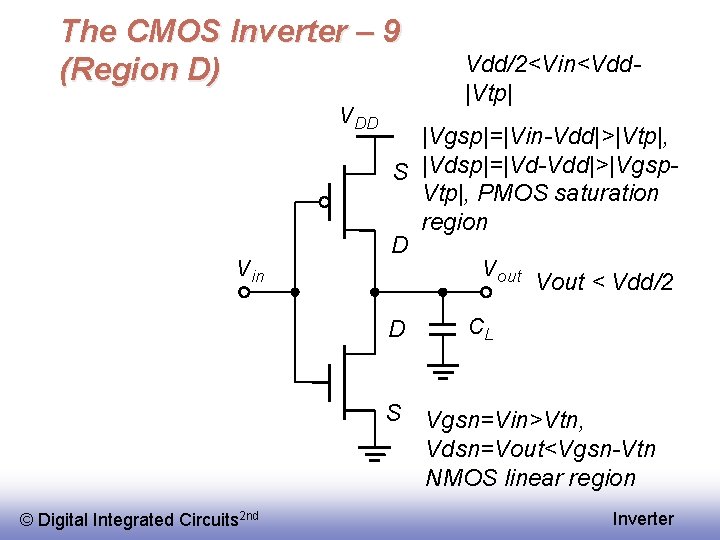

The CMOS Inverter – 9 (Region D) V DD V in |Vgsp|=|Vin-Vdd|>|Vtp|, S |Vdsp|=|Vd-Vdd|>|Vgsp. Vtp|, PMOS saturation region D V out D S © Digital Integrated Circuits 2 nd Vdd/2<Vin<Vdd|Vtp| Vout < Vdd/2 CL Vgsn=Vin>Vtn, Vdsn=Vout<Vgsn-Vtn NMOS linear region Inverter

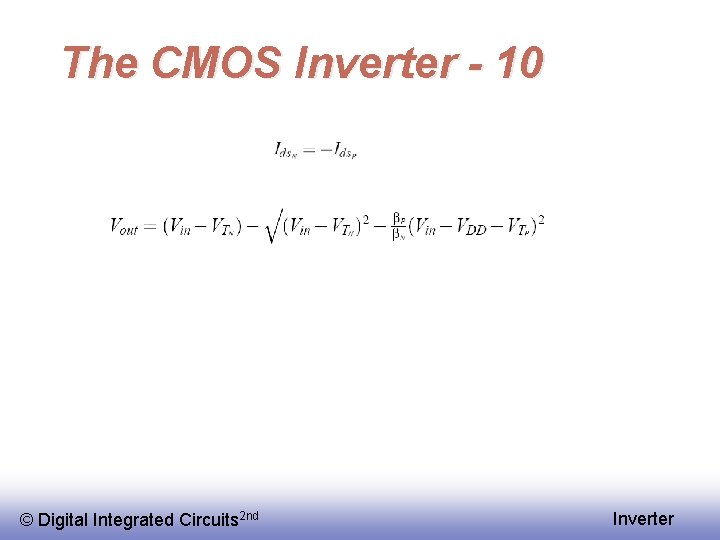

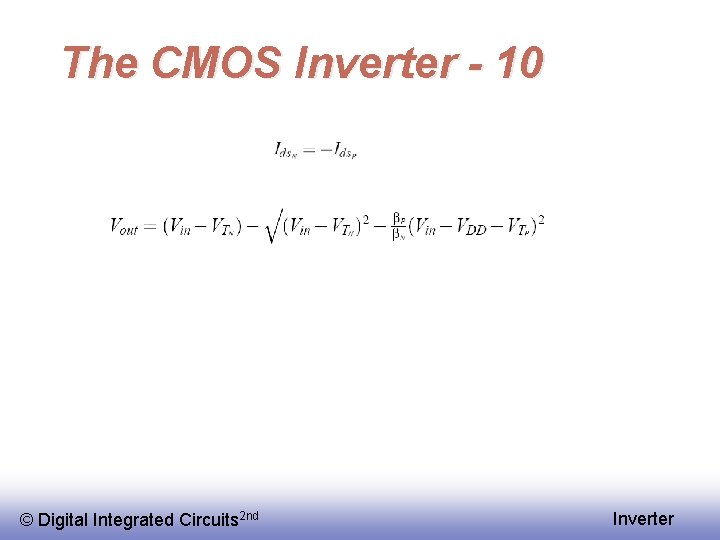

The CMOS Inverter - 10 © Digital Integrated Circuits 2 nd Inverter

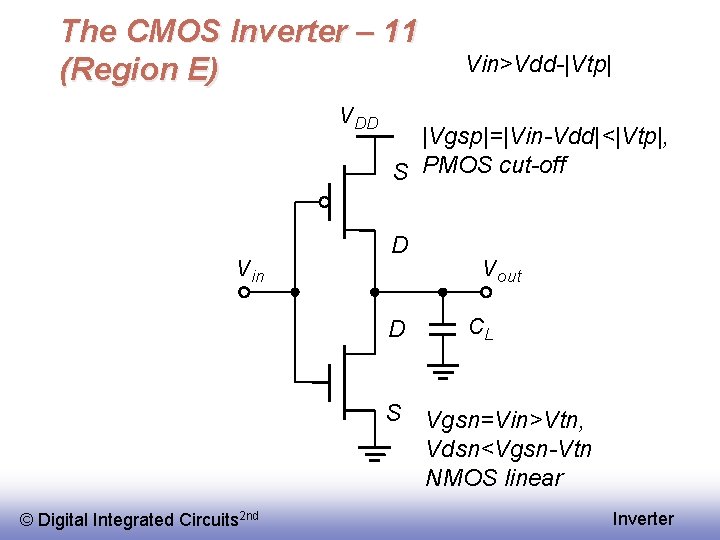

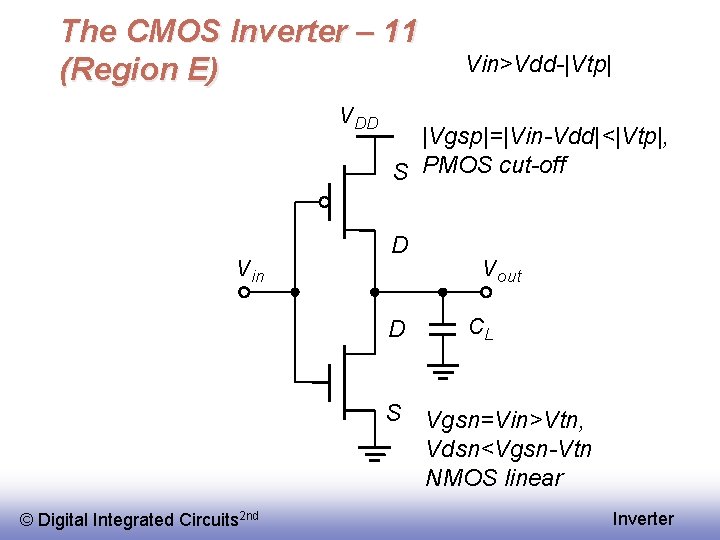

The CMOS Inverter – 11 (Region E) V DD V in |Vgsp|=|Vin-Vdd|<|Vtp|, S PMOS cut-off D D S © Digital Integrated Circuits 2 nd Vin>Vdd-|Vtp| V out CL Vgsn=Vin>Vtn, Vdsn<Vgsn-Vtn NMOS linear Inverter

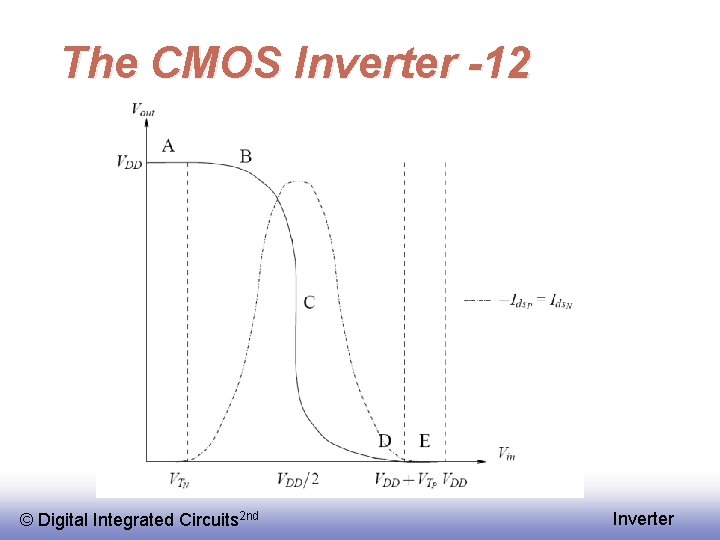

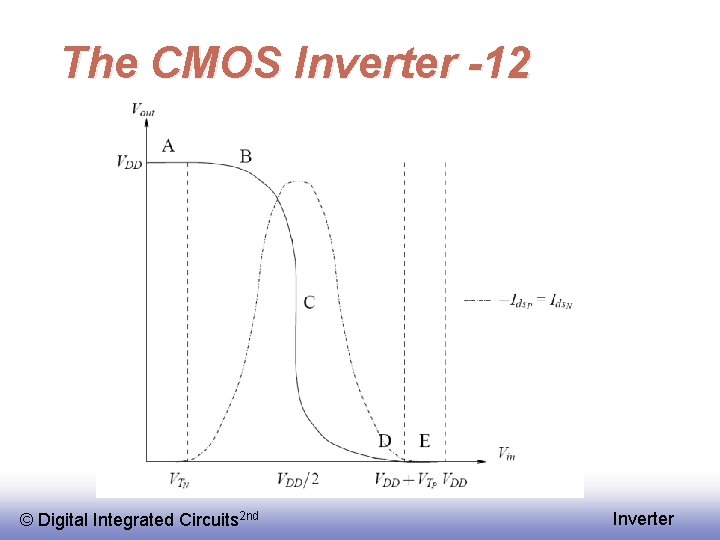

The CMOS Inverter -12 © Digital Integrated Circuits 2 nd Inverter

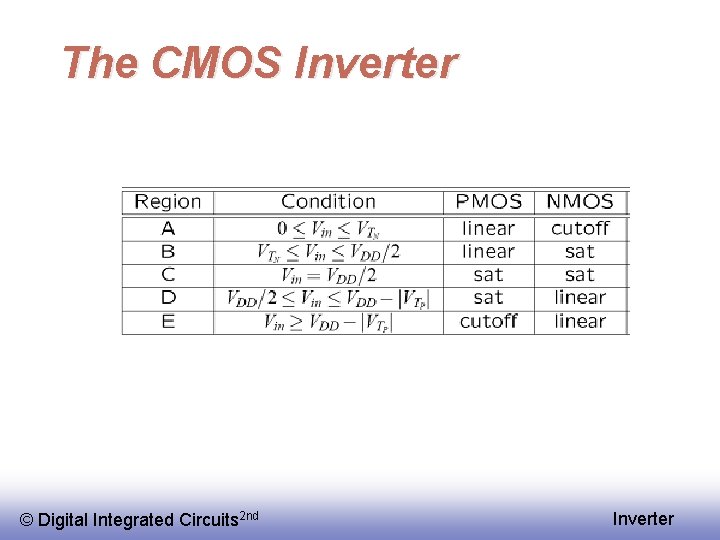

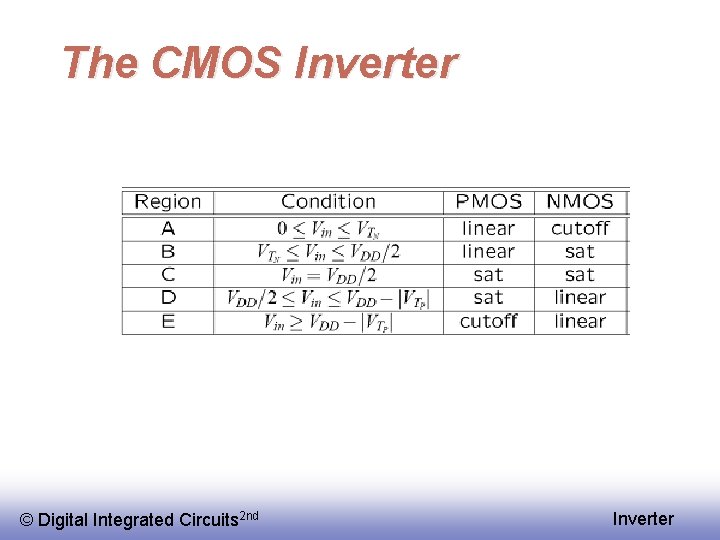

The CMOS Inverter © Digital Integrated Circuits 2 nd Inverter

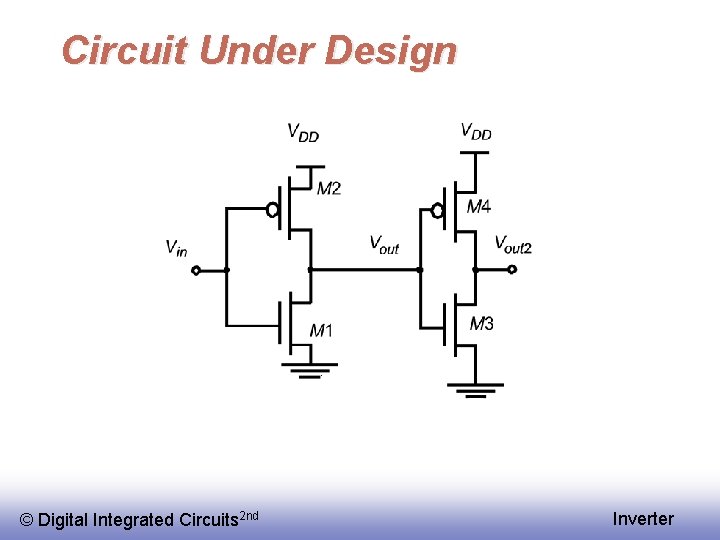

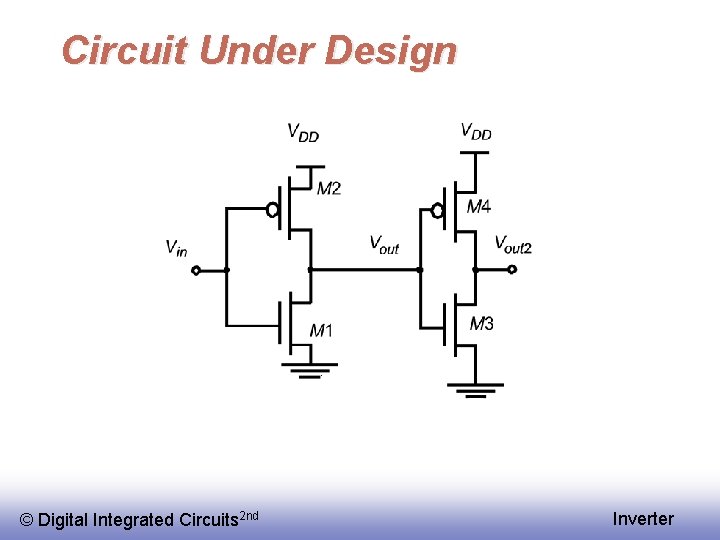

Circuit Under Design © Digital Integrated Circuits 2 nd Inverter

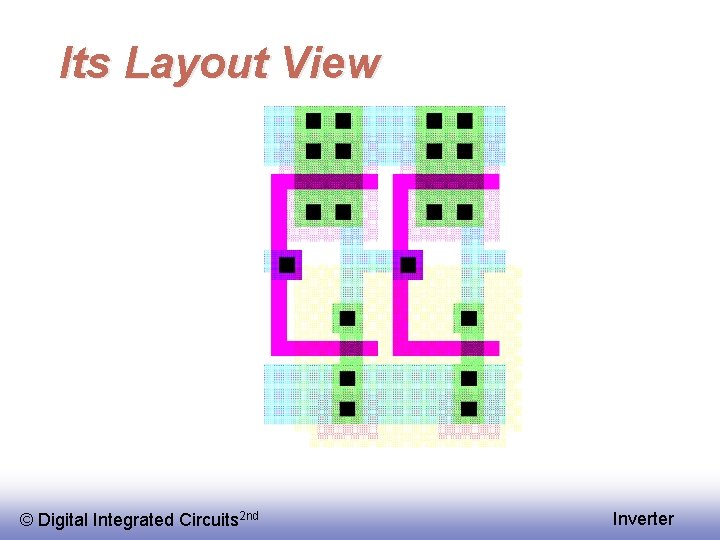

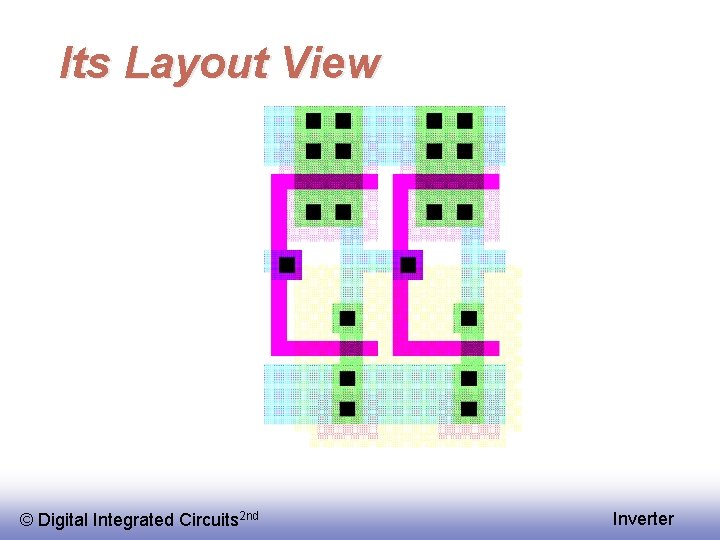

Its Layout View © Digital Integrated Circuits 2 nd Inverter