ECE 426 VLSI System Design Lecture 3 Verilog

![Verilog functions } Function Declaration: function [ range_or_type ] fname; input_declarations statement endfunction } Verilog functions } Function Declaration: function [ range_or_type ] fname; input_declarations statement endfunction }](https://slidetodoc.com/presentation_image_h/f8045169e547c64d0b5cf14bcbbcb56a/image-25.jpg)

![Verilog Functions (cont'd) } Function examples: function calc_parity; input [31: 0] val; begin calc_parity Verilog Functions (cont'd) } Function examples: function calc_parity; input [31: 0] val; begin calc_parity](https://slidetodoc.com/presentation_image_h/f8045169e547c64d0b5cf14bcbbcb56a/image-27.jpg)

![Verilog Tasks (cont'd) } Task example: task Reverse. Byte; input [7: 0] a; output Verilog Tasks (cont'd) } Task example: task Reverse. Byte; input [7: 0] a; output](https://slidetodoc.com/presentation_image_h/f8045169e547c64d0b5cf14bcbbcb56a/image-29.jpg)

- Slides: 40

ECE 426 - VLSI System Design Lecture 3 - Verilog Delay Modeling February 3, 2003 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042 nestorj@lafayette. edu 2/3/03 ECE 426 - Lecture 3 1

Announcements } Reading } Wolf: 8. 1 -8. 3 2/3/03 ECE 426 - Lecture 3 2

Where we are. . . } Last Time: } Verilog Review } Event-Driven Simulation } Today: } } } Timing and Delay in Event-Driven Simulation Verilog Delay Constructs initial blocks Tasks and Functions Discuss Lab 1 2/3/03 ECE 426 - Lecture 3 3

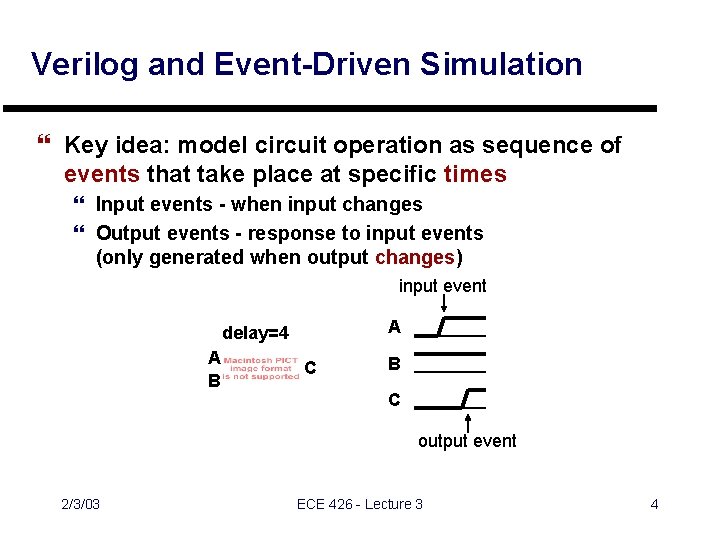

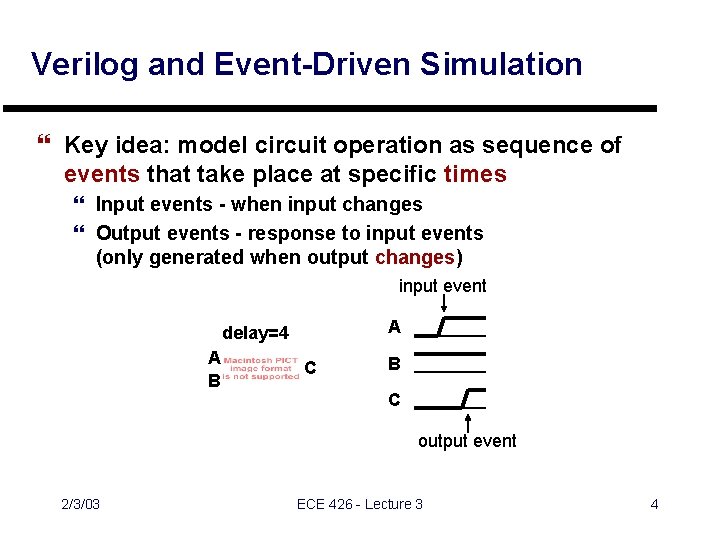

Verilog and Event-Driven Simulation } Key idea: model circuit operation as sequence of events that take place at specific times } Input events - when input changes } Output events - response to input events (only generated when output changes) input event A delay=4 A B C output event 2/3/03 ECE 426 - Lecture 3 4

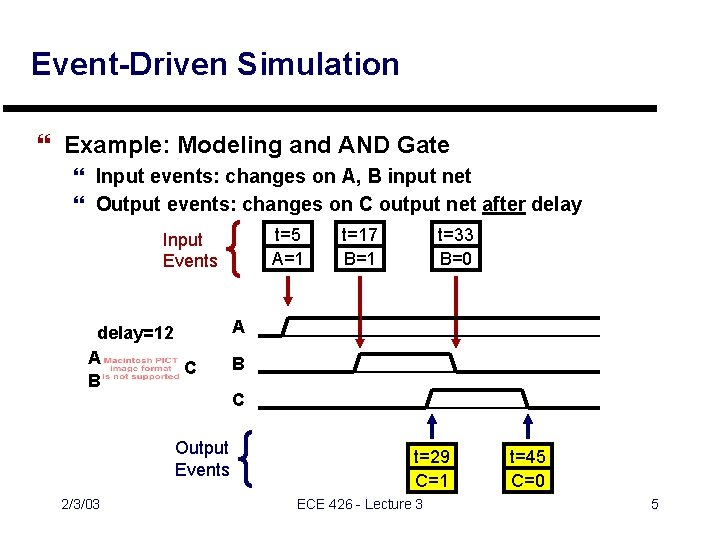

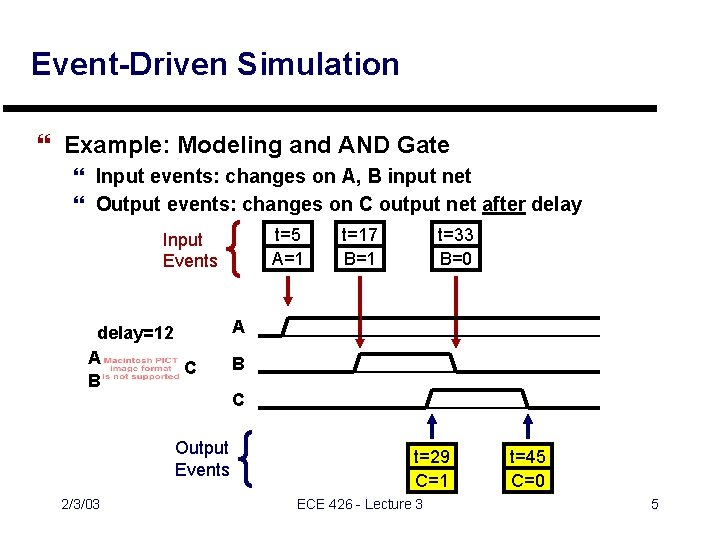

Event-Driven Simulation } Example: Modeling and AND Gate } Input events: changes on A, B input net } Output events: changes on C output net after delay t=5 A=1 Input Events delay=12 A C B Output Events 2/3/03 t=17 B=1 t=33 B=0 A B C t=29 C=1 ECE 426 - Lecture 3 t=45 C=0 5

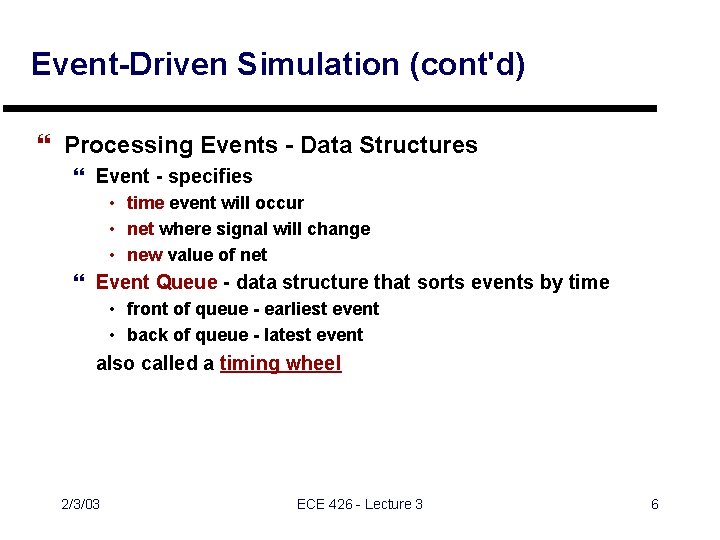

Event-Driven Simulation (cont'd) } Processing Events - Data Structures } Event - specifies • time event will occur • net where signal will change • new value of net } Event Queue - data structure that sorts events by time • front of queue - earliest event • back of queue - latest event also called a timing wheel 2/3/03 ECE 426 - Lecture 3 6

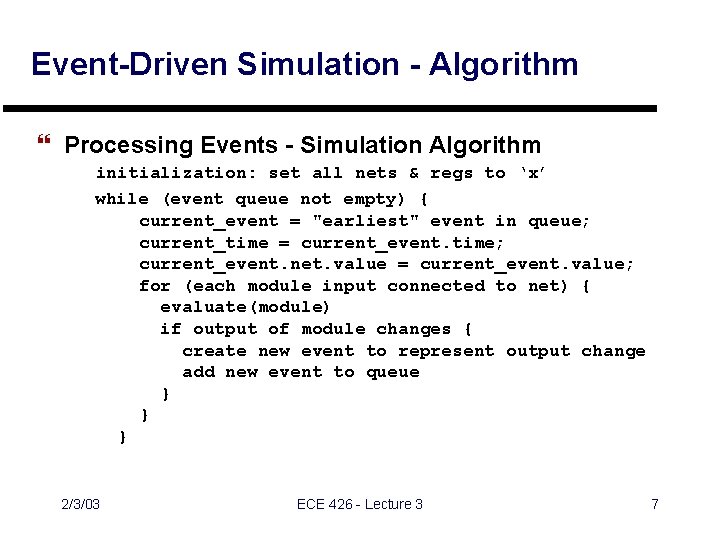

Event-Driven Simulation - Algorithm } Processing Events - Simulation Algorithm initialization: set all nets & regs to ‘x’ while (event queue not empty) { current_event = "earliest" event in queue; current_time = current_event. time; current_event. net. value = current_event. value; for (each module input connected to net) { evaluate(module) if output of module changes { create new event to represent output change add new event to queue } } } 2/3/03 ECE 426 - Lecture 3 7

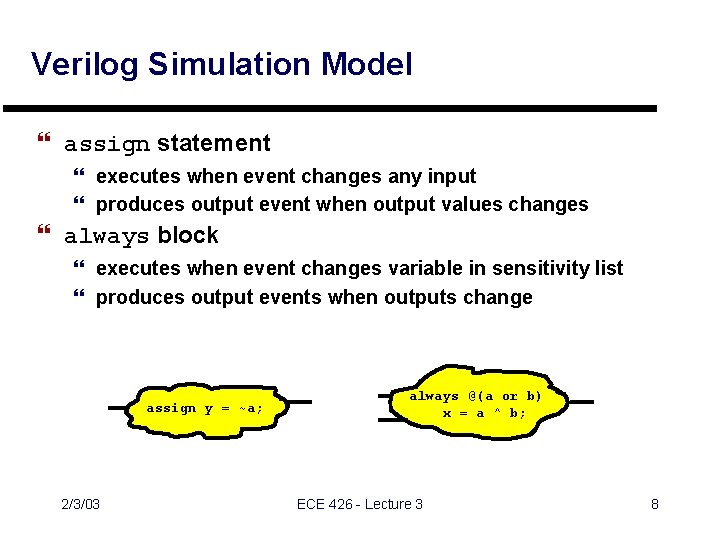

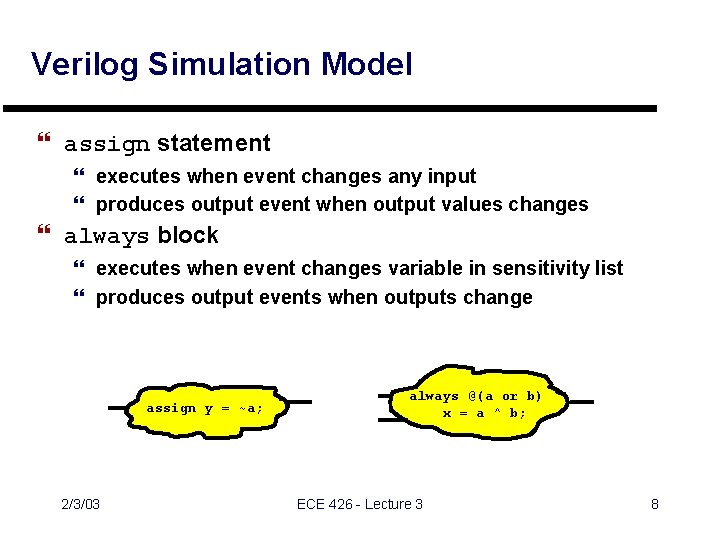

Verilog Simulation Model } assign statement } executes when event changes any input } produces output event when output values changes } always block } executes when event changes variable in sensitivity list } produces output events when outputs change assign y = ~a; 2/3/03 always @(a or b) x = a ^ b; ECE 426 - Lecture 3 8

Delays in Event-Driven Simulation } Two kinds of delays supported: } Inertial delays - reflects limited response time in real gates } Transport delays - try to model delay through a wire 2/3/03 ECE 426 - Lecture 3 9

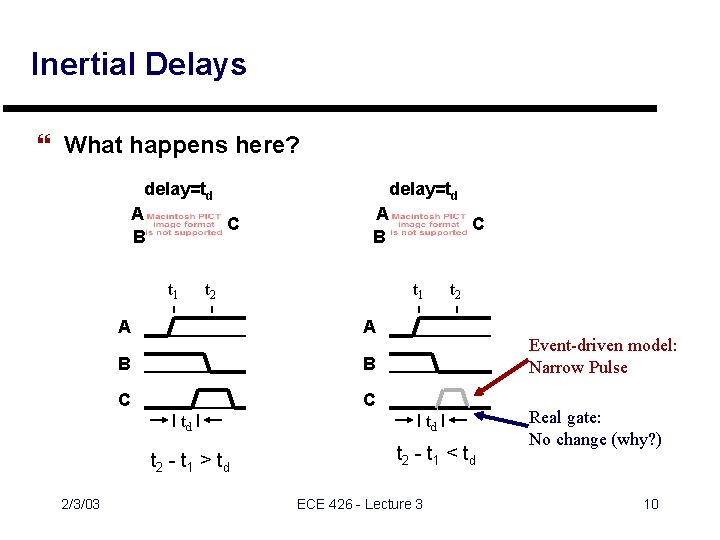

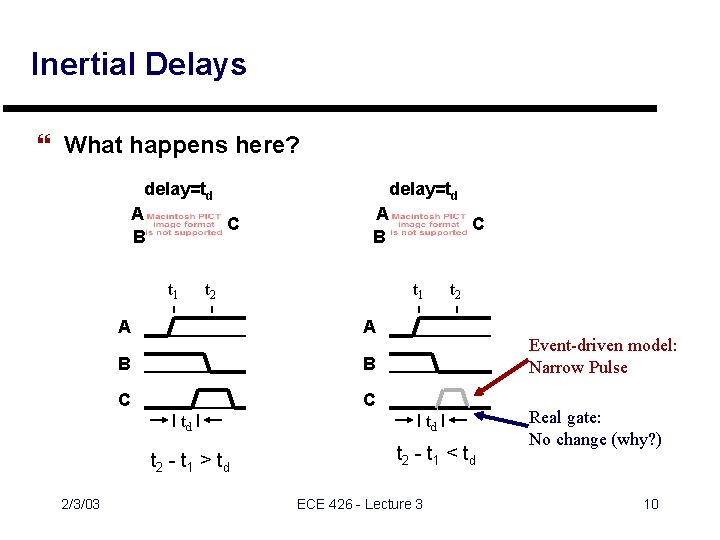

Inertial Delays } What happens here? delay=td A C B t 2 t 1 2/3/03 delay=td A C B t 2 t 1 A A B B C C Event-driven model: Narrow Pulse td td t 2 - t 1 > t d t 2 - t 1 < t d ECE 426 - Lecture 3 Real gate: No change (why? ) 10

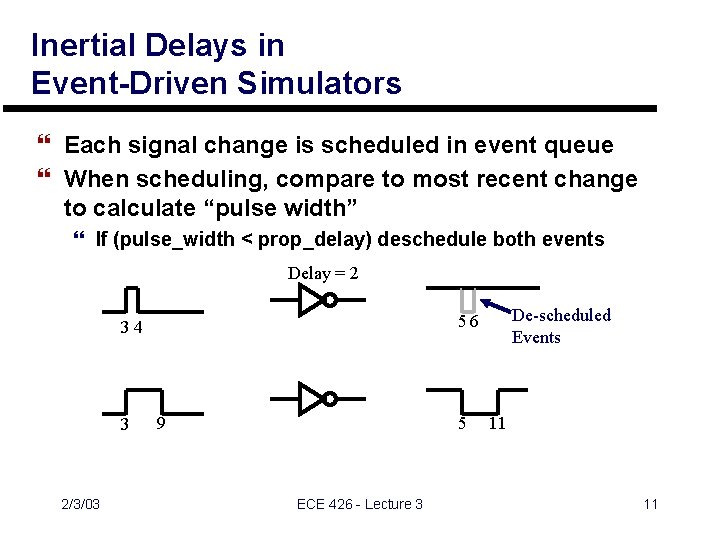

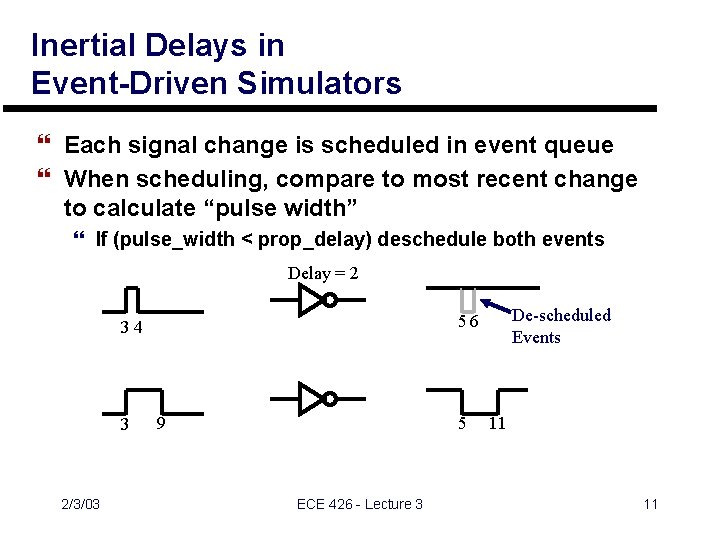

Inertial Delays in Event-Driven Simulators } Each signal change is scheduled in event queue } When scheduling, compare to most recent change to calculate “pulse width” } If (pulse_width < prop_delay) deschedule both events Delay = 2 3 2/3/03 De-scheduled Events 56 34 9 5 ECE 426 - Lecture 3 11 11

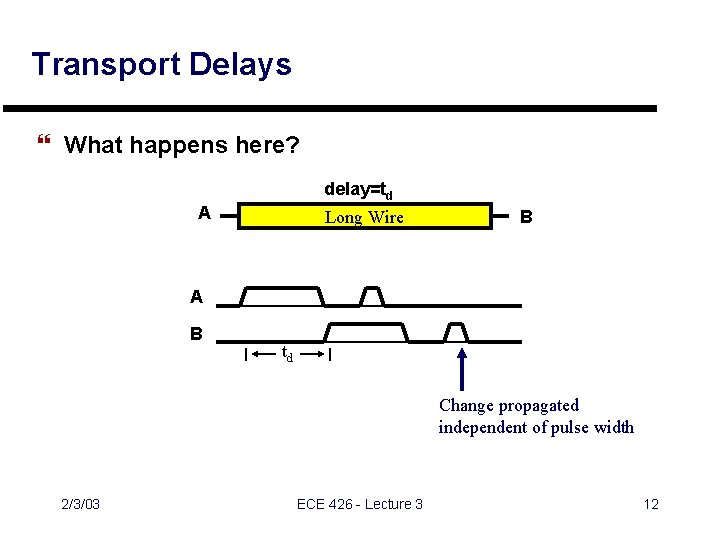

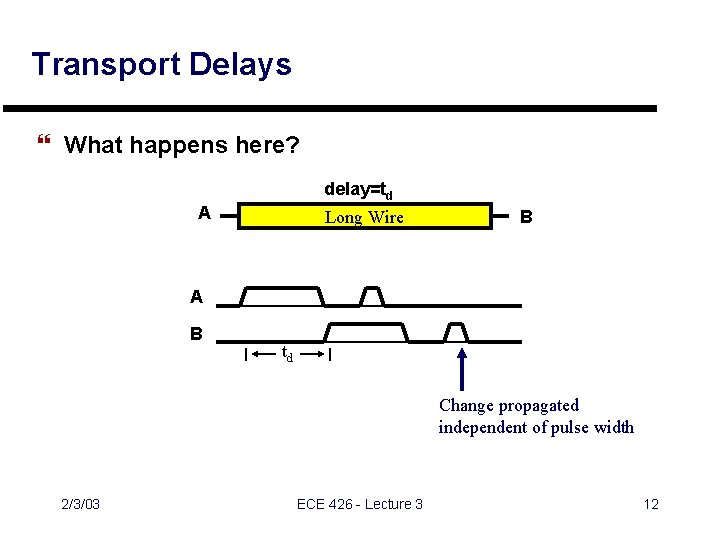

Transport Delays } What happens here? delay=td A C Long Wire B A B td Change propagated independent of pulse width 2/3/03 ECE 426 - Lecture 3 12

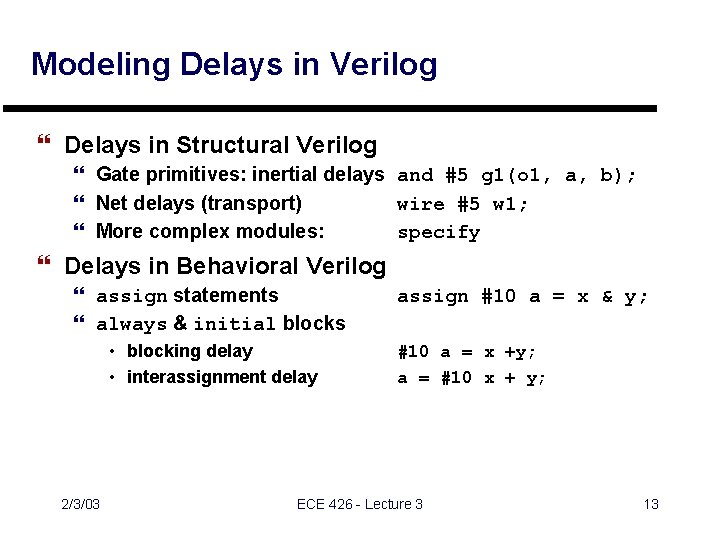

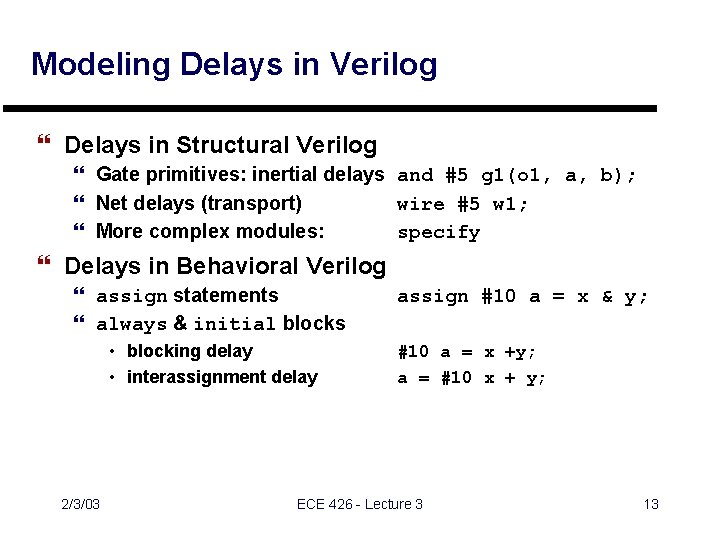

Modeling Delays in Verilog } Delays in Structural Verilog } Gate primitives: inertial delays and #5 g 1(o 1, a, b); } Net delays (transport) wire #5 w 1; } More complex modules: specify } Delays in Behavioral Verilog } assign statements } always & initial blocks • blocking delay • interassignment delay 2/3/03 assign #10 a = x & y; #10 a = x +y; a = #10 x + y; ECE 426 - Lecture 3 13

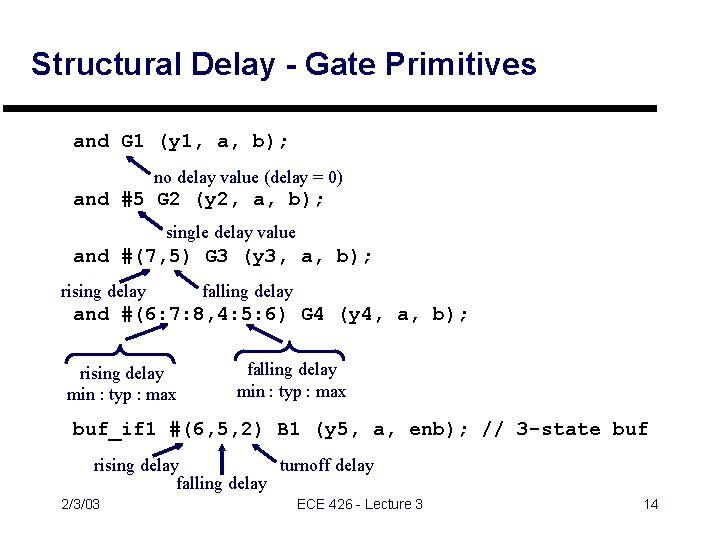

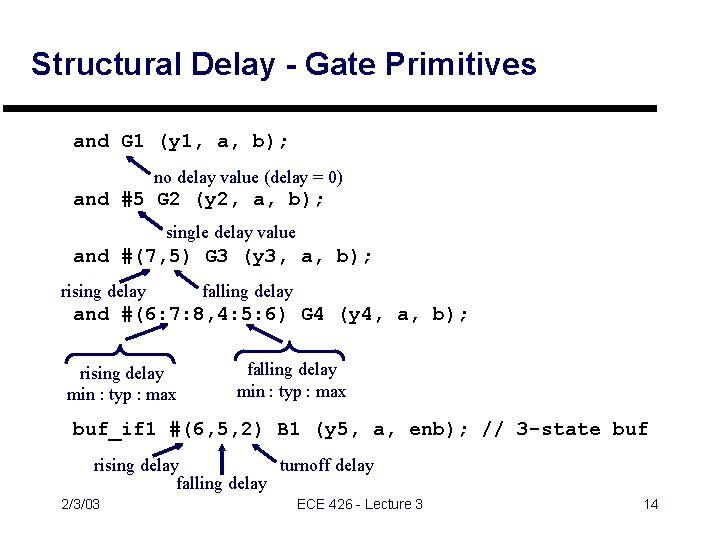

Structural Delay - Gate Primitives and G 1 (y 1, a, b); no delay value (delay = 0) and #5 G 2 (y 2, a, b); single delay value and #(7, 5) G 3 (y 3, a, b); rising delay falling delay and #(6: 7: 8, 4: 5: 6) G 4 (y 4, a, b); rising delay min : typ : max falling delay min : typ : max buf_if 1 #(6, 5, 2) B 1 (y 5, a, enb); // 3 -state buf rising delay turnoff delay falling delay 2/3/03 ECE 426 - Lecture 3 14

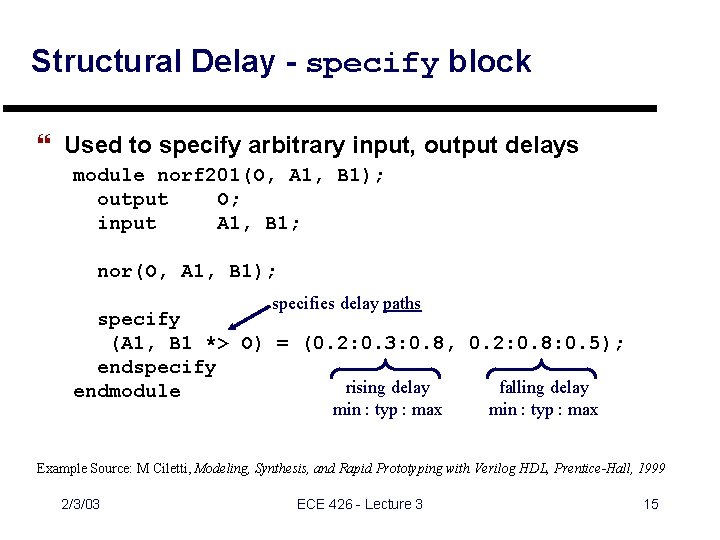

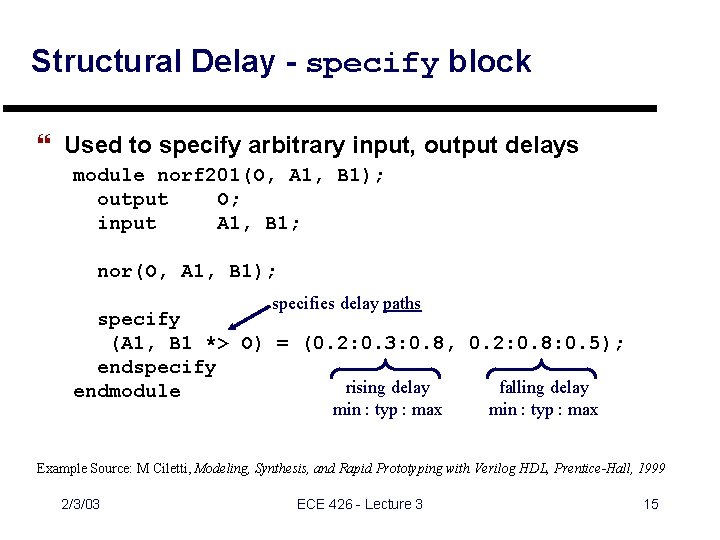

Structural Delay - specify block } Used to specify arbitrary input, output delays module norf 201(O, A 1, B 1); output O; input A 1, B 1; nor(O, A 1, B 1); specifies delay paths specify (A 1, B 1 *> O) = (0. 2: 0. 3: 0. 8, 0. 2: 0. 8: 0. 5); endspecify rising delay falling delay endmodule min : typ : max Example Source: M Ciletti, Modeling, Synthesis, and Rapid Prototyping with Verilog HDL, Prentice-Hall, 1999 2/3/03 ECE 426 - Lecture 3 15

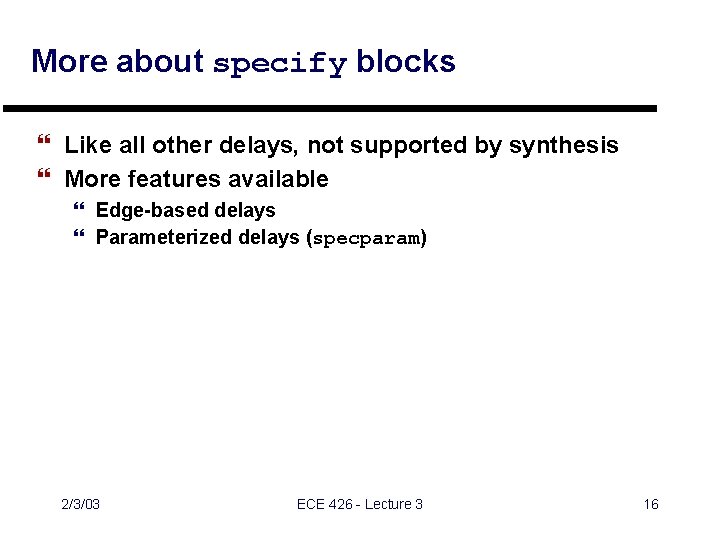

More about specify blocks } Like all other delays, not supported by synthesis } More features available } Edge-based delays } Parameterized delays (specparam) 2/3/03 ECE 426 - Lecture 3 16

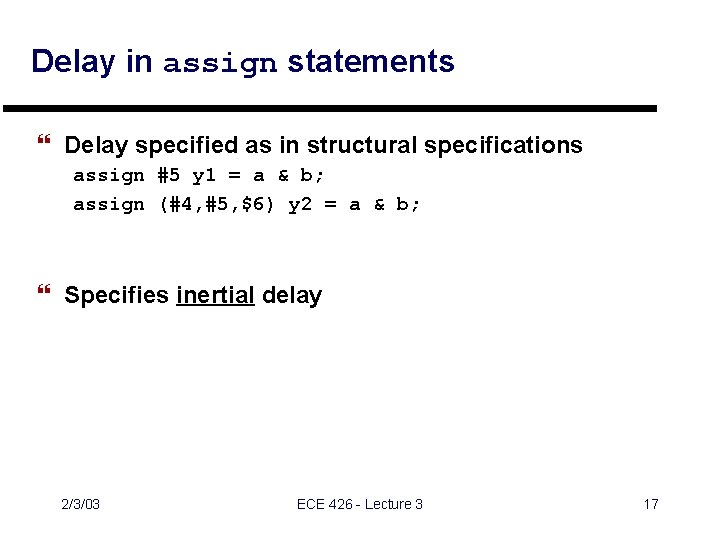

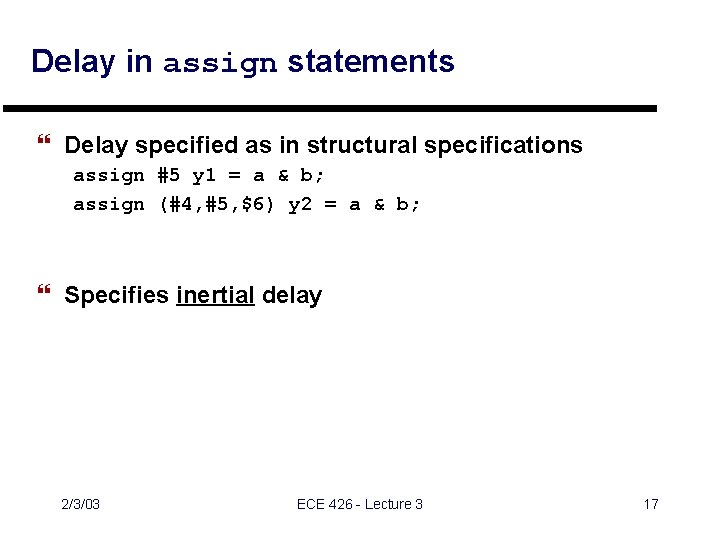

Delay in assign statements } Delay specified as in structural specifications assign #5 y 1 = a & b; assign (#4, #5, $6) y 2 = a & b; } Specifies inertial delay 2/3/03 ECE 426 - Lecture 3 17

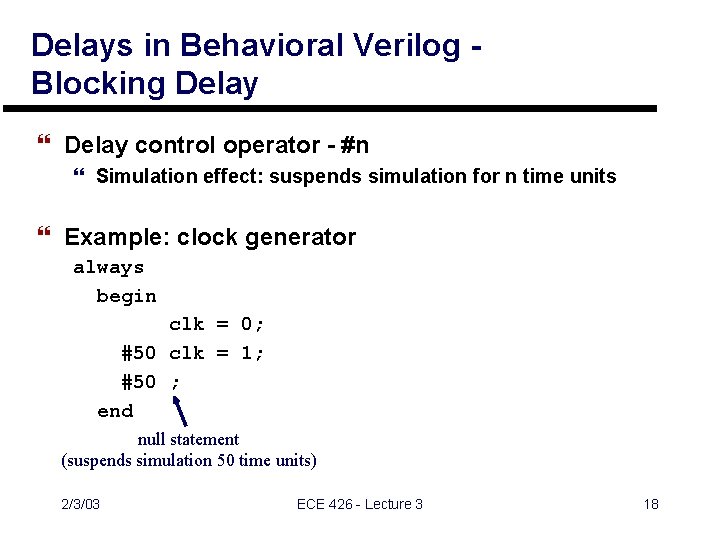

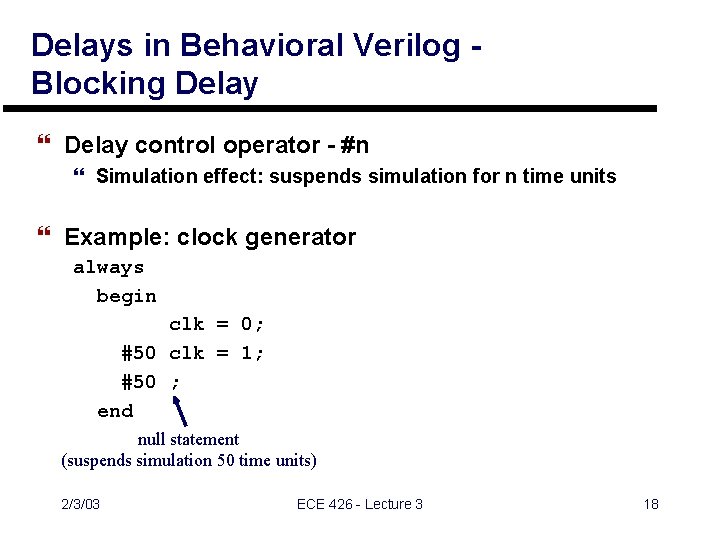

Delays in Behavioral Verilog Blocking Delay } Delay control operator - #n } Simulation effect: suspends simulation for n time units } Example: clock generator always begin clk = 0; #50 clk = 1; #50 ; end null statement (suspends simulation 50 time units) 2/3/03 ECE 426 - Lecture 3 18

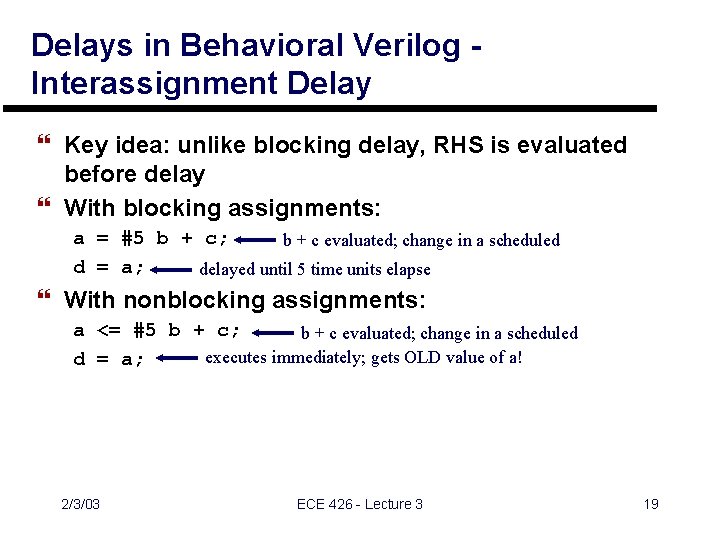

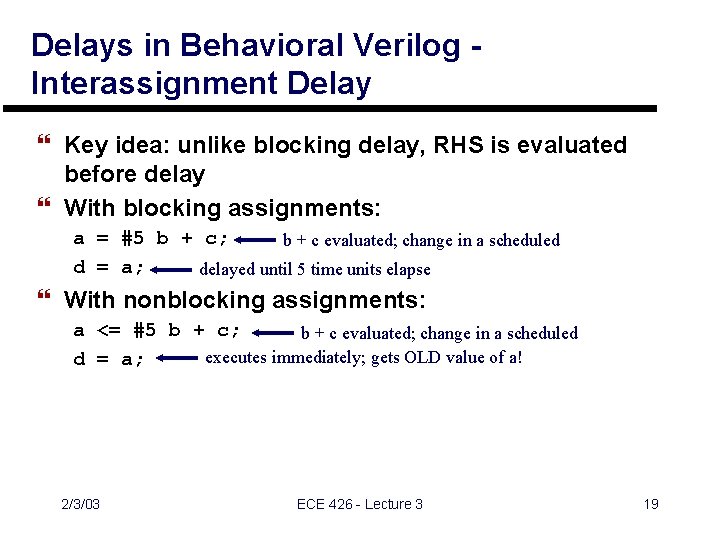

Delays in Behavioral Verilog Interassignment Delay } Key idea: unlike blocking delay, RHS is evaluated before delay } With blocking assignments: a = #5 b + c; b + c evaluated; change in a scheduled d = a; delayed until 5 time units elapse } With nonblocking assignments: a <= #5 b + c; b + c evaluated; change in a scheduled executes immediately; gets OLD value of a! d = a; 2/3/03 ECE 426 - Lecture 3 19

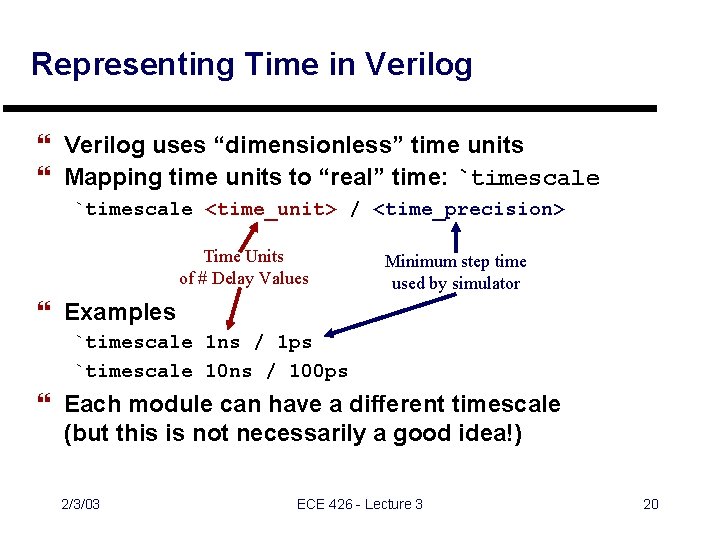

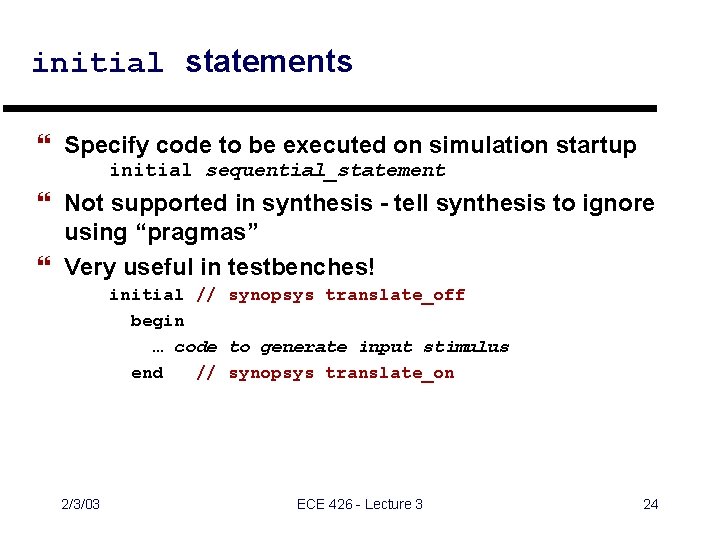

Representing Time in Verilog } Verilog uses “dimensionless” time units } Mapping time units to “real” time: `timescale <time_unit> / <time_precision> Time Units of # Delay Values Minimum step time used by simulator } Examples `timescale 1 ns / 1 ps `timescale 10 ns / 100 ps } Each module can have a different timescale (but this is not necessarily a good idea!) 2/3/03 ECE 426 - Lecture 3 20

Simulation Time in Verilog: # and `timescale } `timescale controls simulation time `timescale time_unit time_precision `timescale 1 ns 100 ps } # operator specifies delay in terms of time units `timescale 1 ns 100 ps #5 // delays 5*1 ns = 5 ns; // rounds times to 100 ps `timescale 4 ns 1 ns #3 // delays 3*4 ns = 12 ns // rounds times to 1 ns 2/3/03 ECE 426 - Lecture 3 21

What happens when no delays are specified? } Each output event has a “delta” delay } Events processed in order of scheduling 2/3/03 ECE 426 - Lecture 3 22

More about Verilog } } initial blocks functions tasks forks & joins 2/3/03 ECE 426 - Lecture 3 23

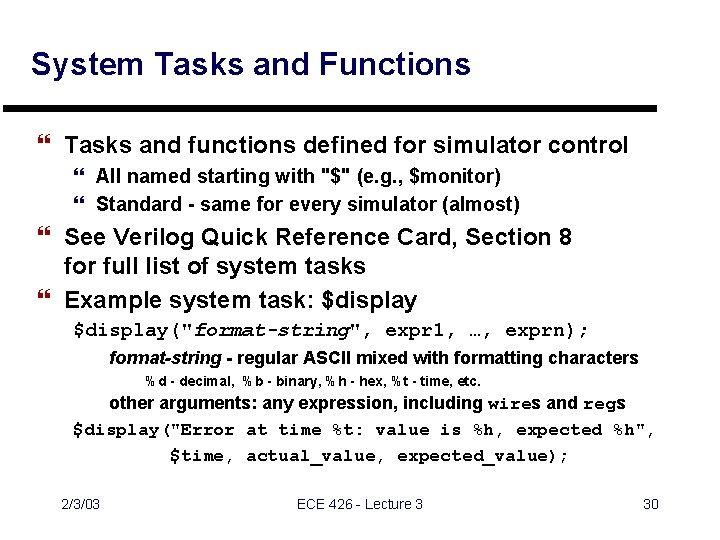

initial statements } Specify code to be executed on simulation startup initial sequential_statement } Not supported in synthesis - tell synthesis to ignore using “pragmas” } Very useful in testbenches! initial // synopsys translate_off begin … code to generate input stimulus end // synopsys translate_on 2/3/03 ECE 426 - Lecture 3 24

![Verilog functions Function Declaration function rangeortype fname inputdeclarations statement endfunction Verilog functions } Function Declaration: function [ range_or_type ] fname; input_declarations statement endfunction }](https://slidetodoc.com/presentation_image_h/f8045169e547c64d0b5cf14bcbbcb56a/image-25.jpg)

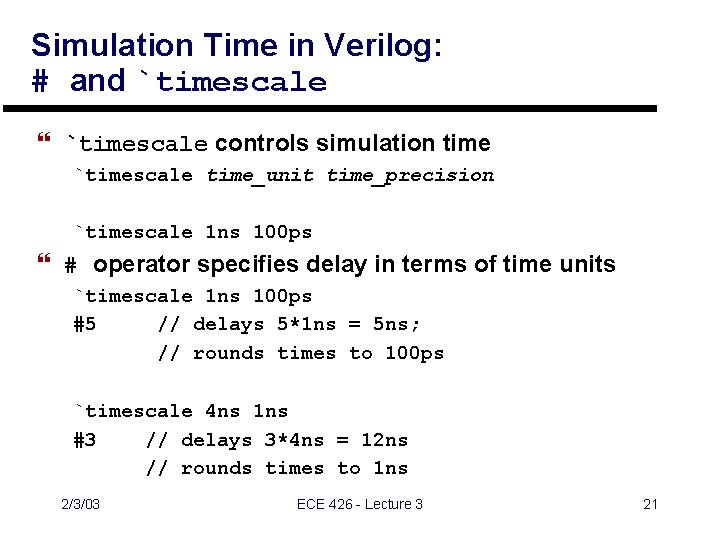

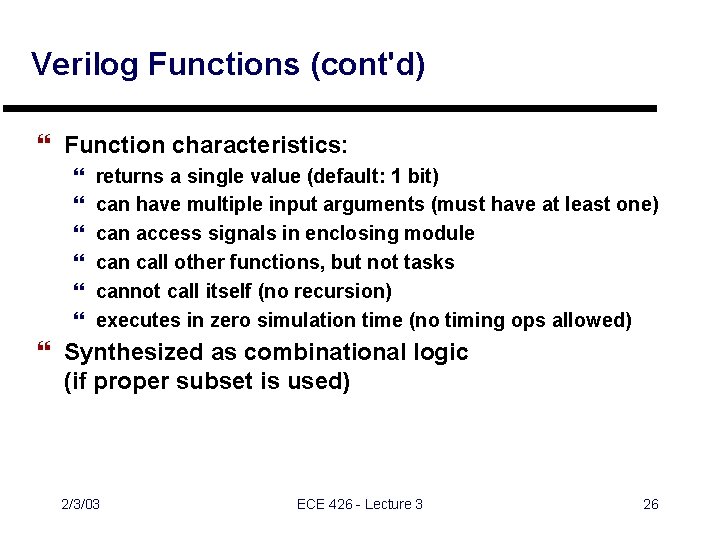

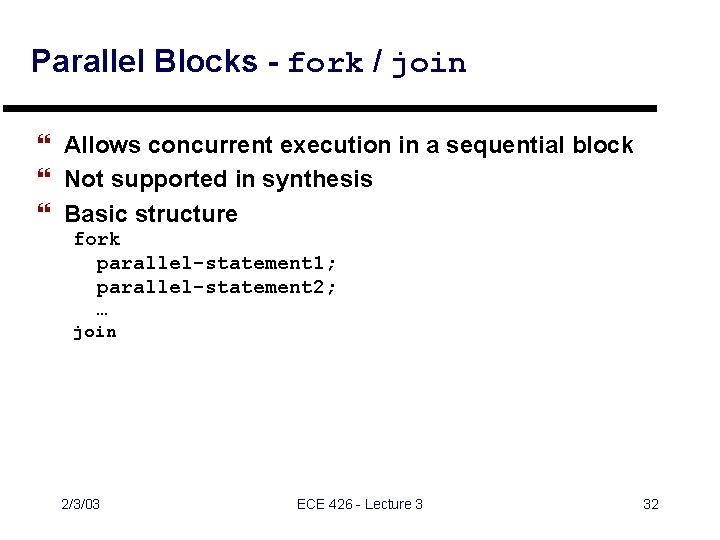

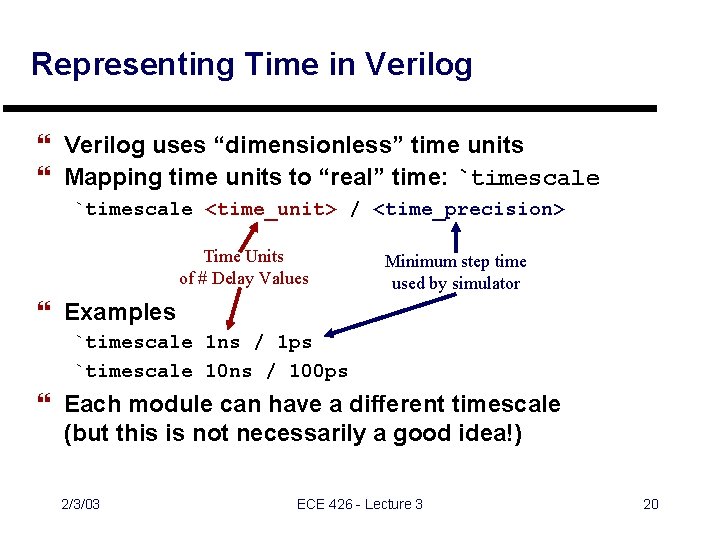

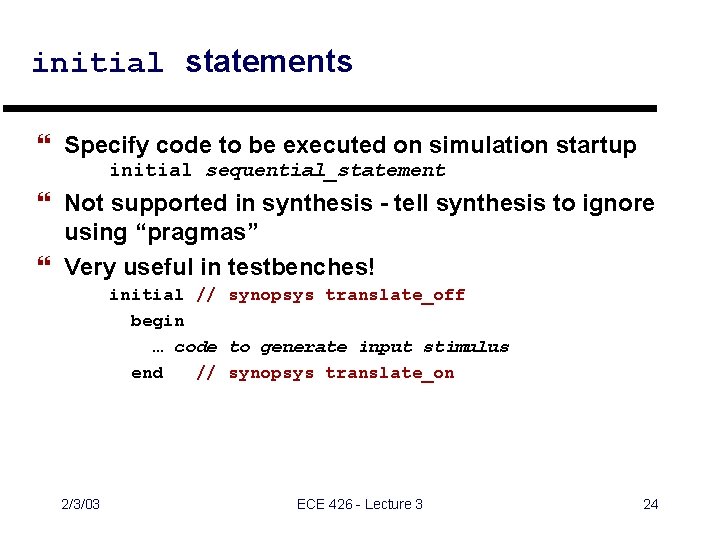

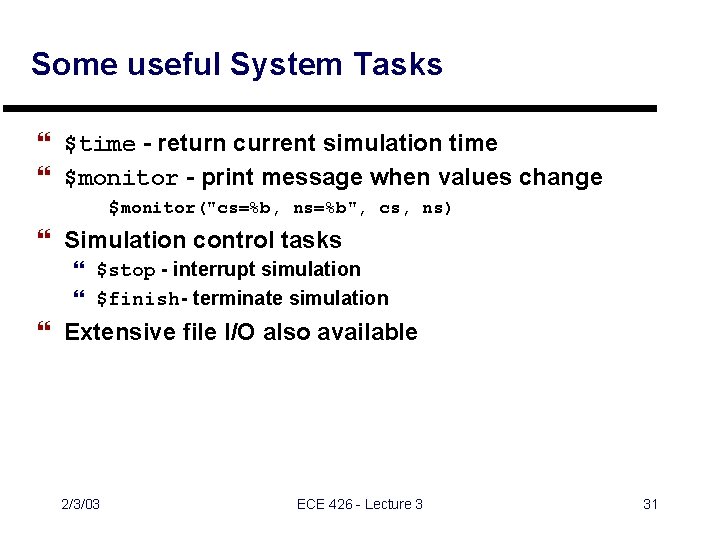

Verilog functions } Function Declaration: function [ range_or_type ] fname; input_declarations statement endfunction } Return value: function body must assign: fname = expression; } Function call: 2/3/03 fname ( expression, … ) ECE 426 - Lecture 3 25

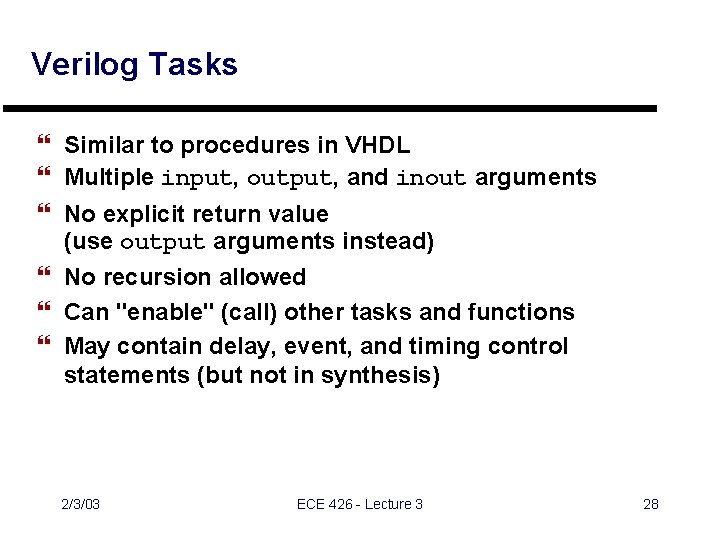

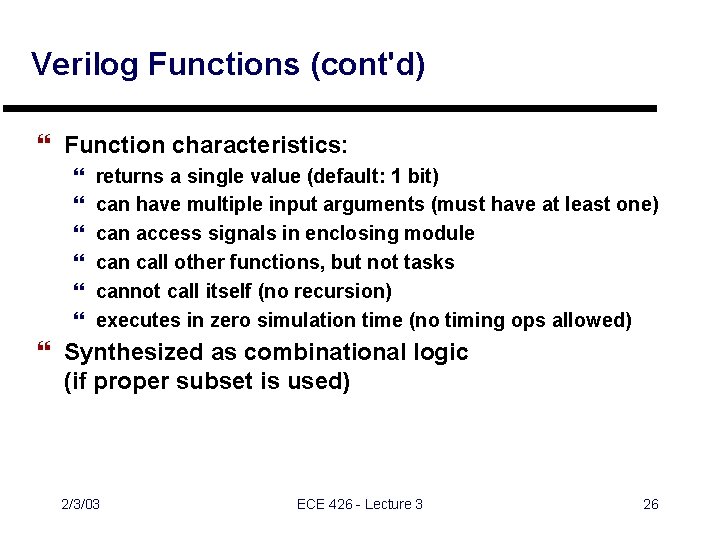

Verilog Functions (cont'd) } Function characteristics: } } } returns a single value (default: 1 bit) can have multiple input arguments (must have at least one) can access signals in enclosing module can call other functions, but not tasks cannot call itself (no recursion) executes in zero simulation time (no timing ops allowed) } Synthesized as combinational logic (if proper subset is used) 2/3/03 ECE 426 - Lecture 3 26

![Verilog Functions contd Function examples function calcparity input 31 0 val begin calcparity Verilog Functions (cont'd) } Function examples: function calc_parity; input [31: 0] val; begin calc_parity](https://slidetodoc.com/presentation_image_h/f8045169e547c64d0b5cf14bcbbcb56a/image-27.jpg)

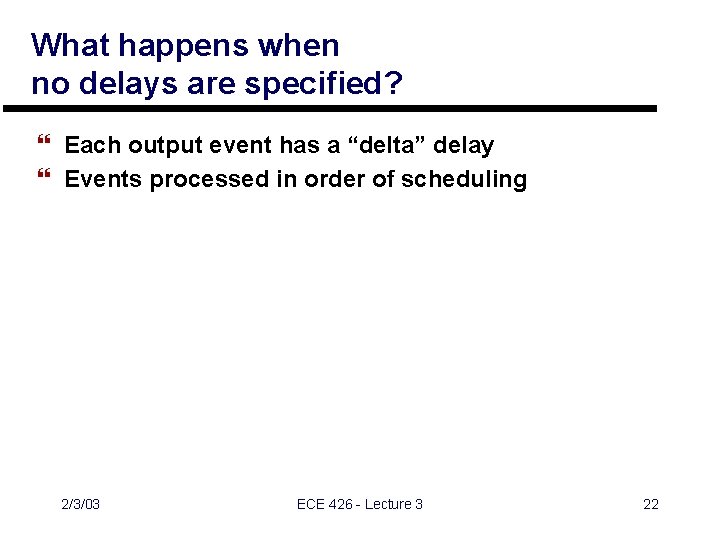

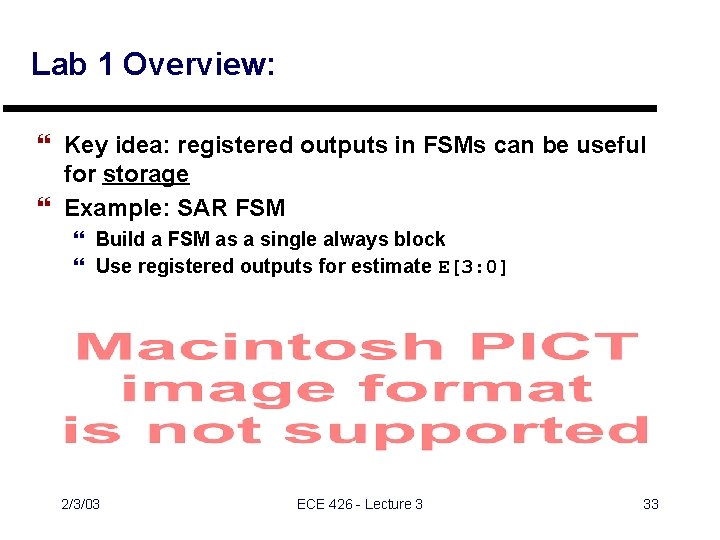

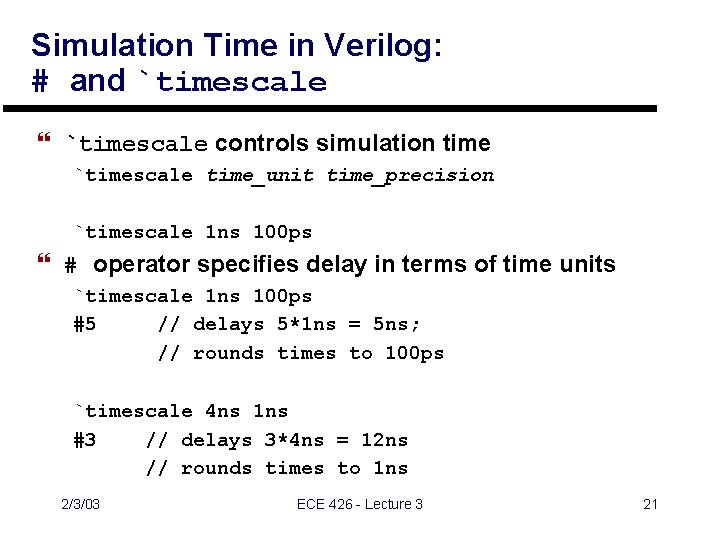

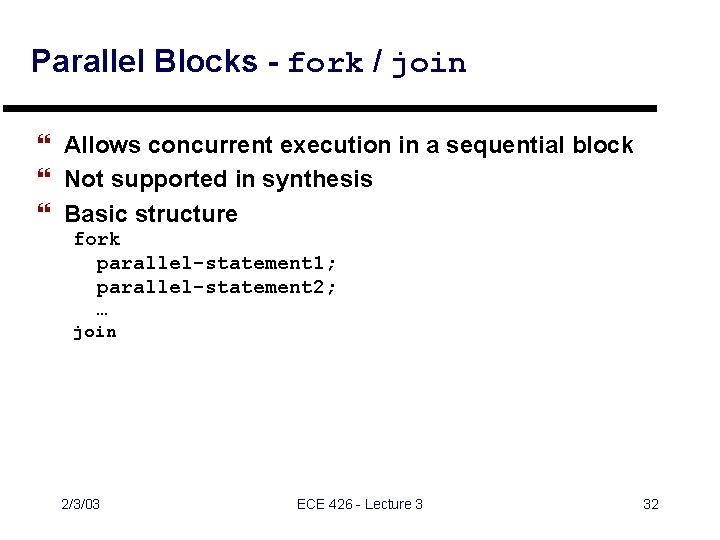

Verilog Functions (cont'd) } Function examples: function calc_parity; input [31: 0] val; begin calc_parity = ^val; endfunction [15: 0] average; input [15: 0] a, b, c, d; begin average = (a + b + c + d) >> 2; endfunction; 2/3/03 ECE 426 - Lecture 3 27

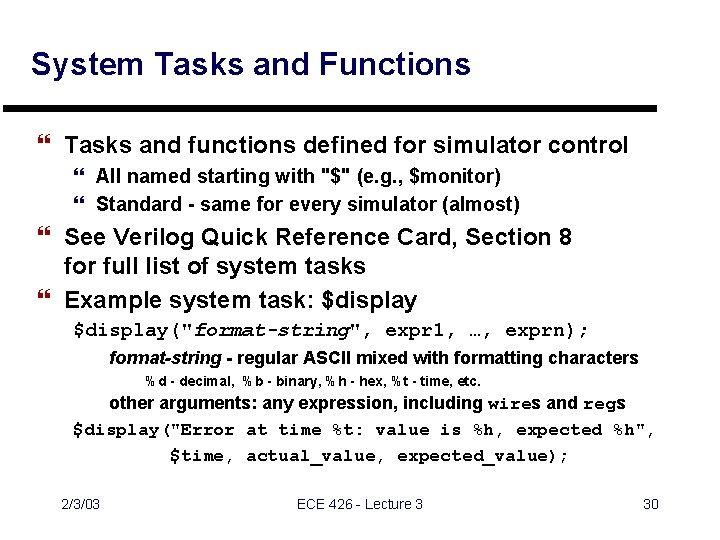

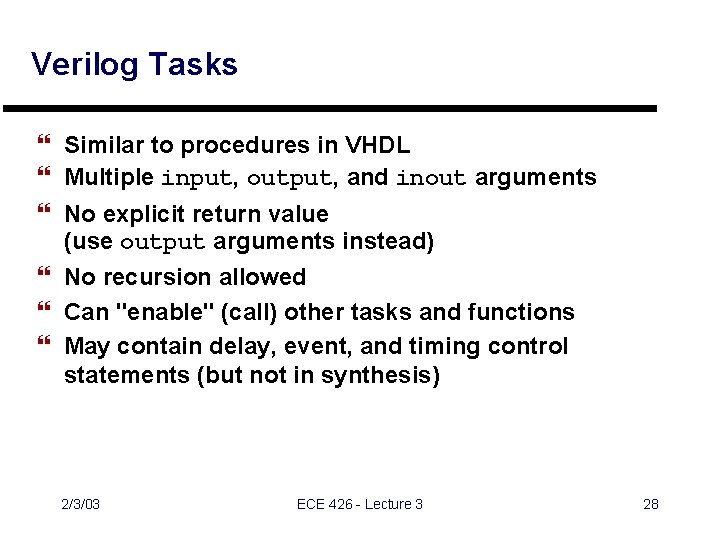

Verilog Tasks } Similar to procedures in VHDL } Multiple input, output, and inout arguments } No explicit return value (use output arguments instead) } No recursion allowed } Can "enable" (call) other tasks and functions } May contain delay, event, and timing control statements (but not in synthesis) 2/3/03 ECE 426 - Lecture 3 28

![Verilog Tasks contd Task example task Reverse Byte input 7 0 a output Verilog Tasks (cont'd) } Task example: task Reverse. Byte; input [7: 0] a; output](https://slidetodoc.com/presentation_image_h/f8045169e547c64d0b5cf14bcbbcb56a/image-29.jpg)

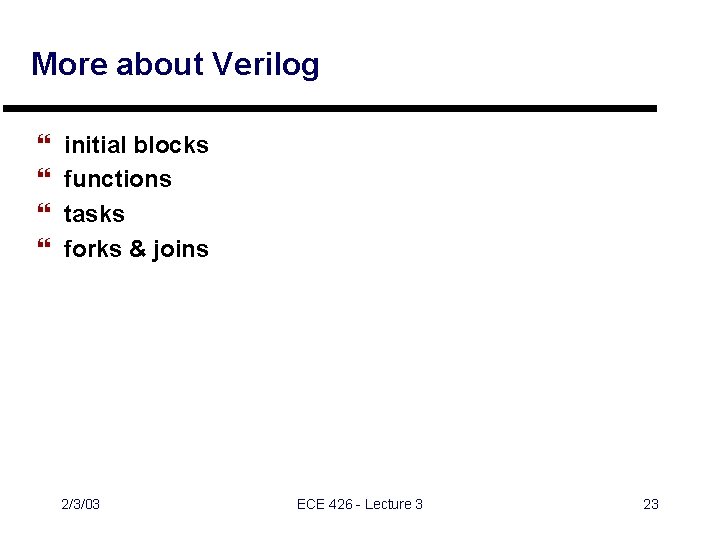

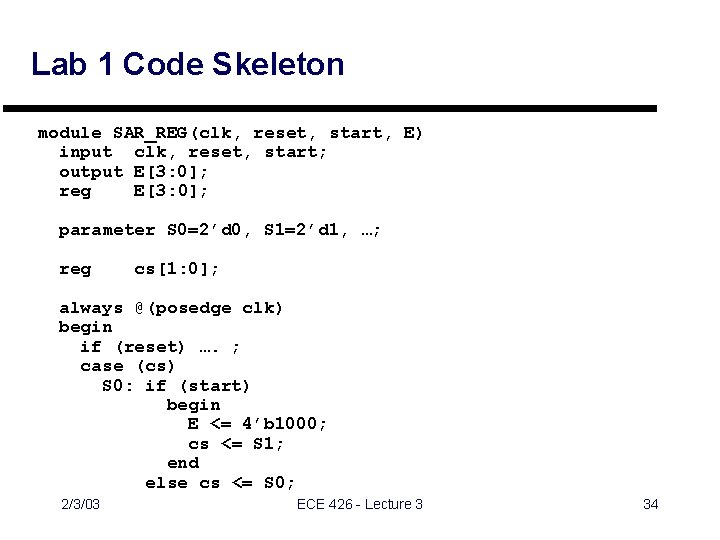

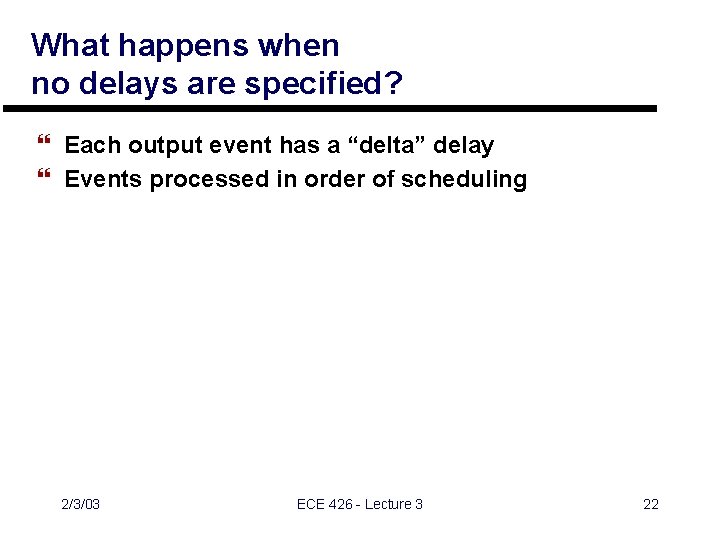

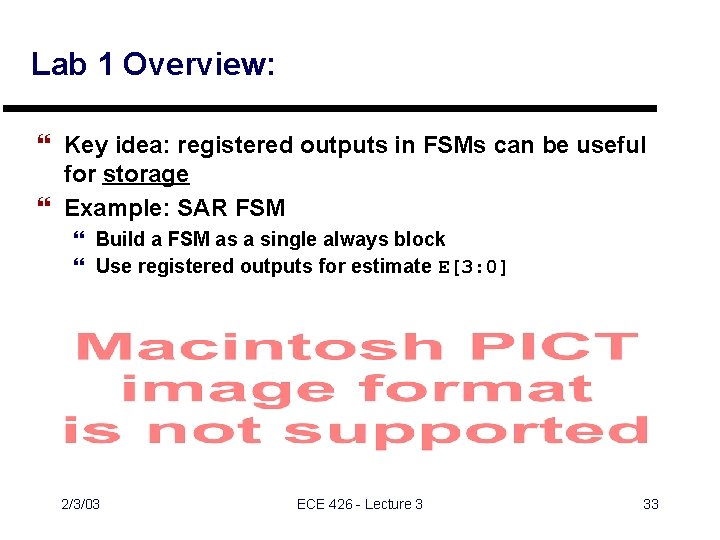

Verilog Tasks (cont'd) } Task example: task Reverse. Byte; input [7: 0] a; output [7: 0] ra; integer j; begin for (j = 7; j >=0; j=j-1) ra[j] = a[7 -j]; end endtask // Adapted from "Verilog HDL Synthesis: A Practical // Primer", by J. Bhasker 2/3/03 ECE 426 - Lecture 3 29

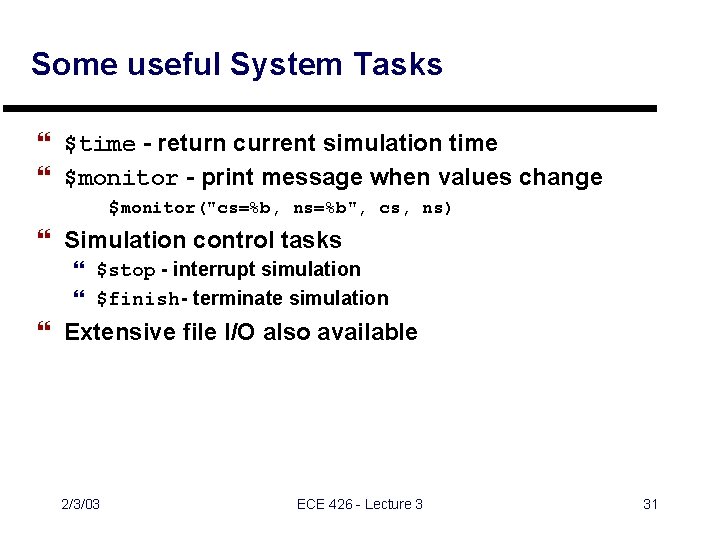

System Tasks and Functions } Tasks and functions defined for simulator control } All named starting with "$" (e. g. , $monitor) } Standard - same for every simulator (almost) } See Verilog Quick Reference Card, Section 8 for full list of system tasks } Example system task: $display("format-string", expr 1, …, exprn); format-string - regular ASCII mixed with formatting characters %d - decimal, %b - binary, %h - hex, %t - time, etc. other arguments: any expression, including wires and regs $display("Error at time %t: value is %h, expected %h", $time, actual_value, expected_value); 2/3/03 ECE 426 - Lecture 3 30

Some useful System Tasks } $time - return current simulation time } $monitor - print message when values change $monitor("cs=%b, ns=%b", cs, ns) } Simulation control tasks } $stop - interrupt simulation } $finish- terminate simulation } Extensive file I/O also available 2/3/03 ECE 426 - Lecture 3 31

Parallel Blocks - fork / join } Allows concurrent execution in a sequential block } Not supported in synthesis } Basic structure fork parallel-statement 1; parallel-statement 2; … join 2/3/03 ECE 426 - Lecture 3 32

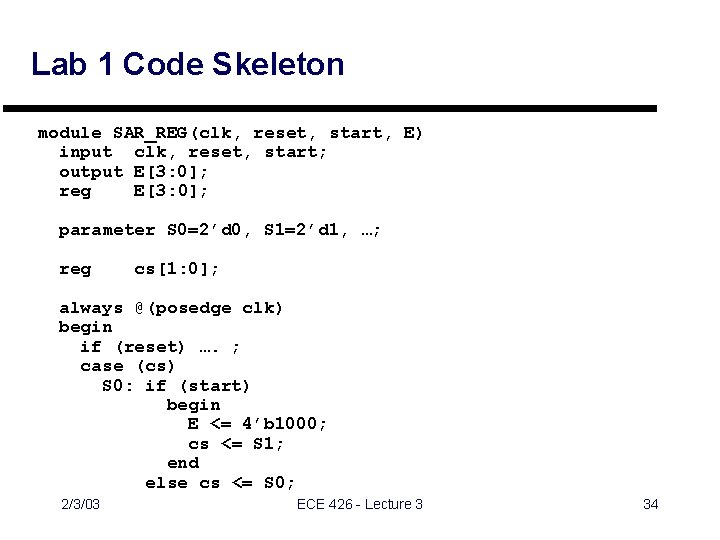

Lab 1 Overview: } Key idea: registered outputs in FSMs can be useful for storage } Example: SAR FSM } Build a FSM as a single always block } Use registered outputs for estimate E[3: 0] 2/3/03 ECE 426 - Lecture 3 33

Lab 1 Code Skeleton module SAR_REG(clk, reset, start, E) input clk, reset, start; output E[3: 0]; reg E[3: 0]; parameter S 0=2’d 0, S 1=2’d 1, …; reg cs[1: 0]; always @(posedge clk) begin if (reset) …. ; case (cs) S 0: if (start) begin E <= 4’b 1000; cs <= S 1; end else cs <= S 0; 2/3/03 ECE 426 - Lecture 3 34

Lab 1 Tasks } Re-Code FSM using Registered Outputs } Simulate w/ Verilogger to check outputs } Synthesize & compare to original design from last semester 2/3/03 ECE 426 - Lecture 3 35

Coming Up: } Verilog coding styles } Behavioral Modeling } Testbenches and Verification 2/3/03 ECE 426 - Lecture 3 36

Verilog Stuff we Won’t Talk about Much } Procedural continuous assignment } Assign / desassign as procedural statements } Not synthesizeable } User-Defined Primitives (UDPs) 2/3/03 ECE 426 - Lecture 3 37

More about Verilog FSMs } Many ways to describe } Explicit Style 1 • State register - clocked always block • Next-state Logic - combinational always block • Output logic - combinational always block (or assign) } Explicit Style 2 • Next-state logic AND state register: clocked always block • Output logic - combinational always block (or assign) 2/3/03 ECE 426 - Lecture 3 38

Lab 1 - FSM Coding } Re-code SAR as } Explicit FSM w/ registered outputs } Implicit FSM 2/3/03 ECE 426 - Lecture 3 39

System Design Issues } } ASM Diagrams Synchronization & Metastability Handshaking Working with Multiple Clocks 2/3/03 ECE 426 - Lecture 3 40