VLSI Design Basic Interconnects VLSI Design EE 213

VLSI Design Basic Interconnects VLSI Design EE 213 These slides contain some notes on interconnections in VLSI circuits. Full details are in Pucknell and Eshraghian pages 94 - 107 EE 213 VLSI Design Stephen Daniels 2003

VLSI Introduction Design • Wiring-Up of chip devices takes place through various conductors produced during processing • Today, interconnects constitute the main source of delay in MOS circuits • We will examine: – – – Sheet Resistance – Resistance / Unit Area Capacitance Delay Units CMOS Inverter Delay Rise and Fall Time Estimation EE 213 VLSI Design Stephen Daniels 2003

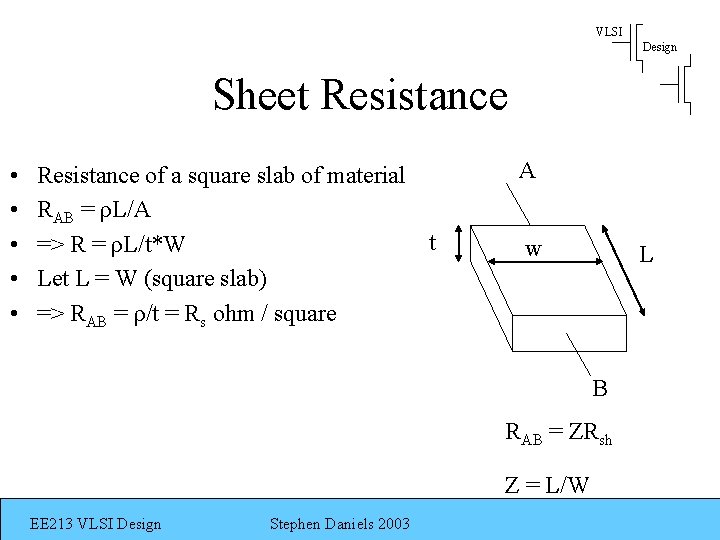

VLSI Design Sheet Resistance • • • Resistance of a square slab of material RAB = ρL/A t => R = ρL/t*W Let L = W (square slab) => RAB = ρ/t = Rs ohm / square A w L B RAB = ZRsh Z = L/W EE 213 VLSI Design Stephen Daniels 2003

Typical sheet resistance values for materials are very well characterised Layer Rs (Ohm / Sq Aluminium 0. 03 N Diffusion 10 – 50 Silicide 2– 4 Polysilicon 15 - 100 N-transistor Channel P-transistor Channel 104 2. 5 x 104 Typical Sheet Resistances for 5µm Technology EE 213 VLSI Design Stephen Daniels 2003 VLSI Design

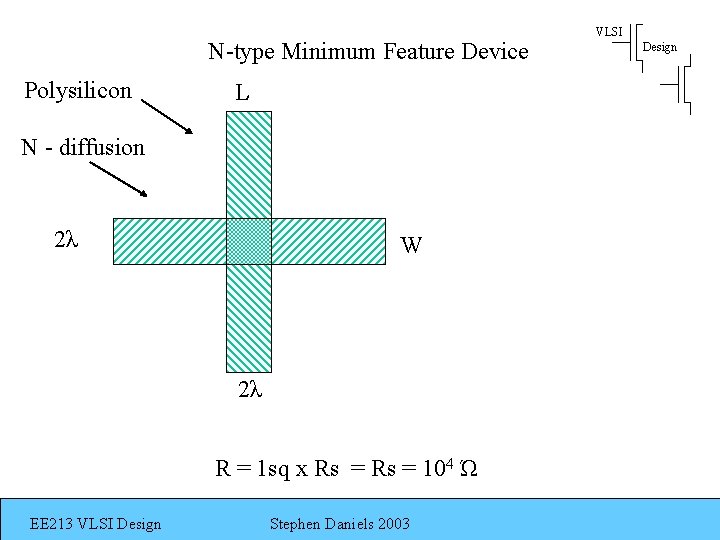

N-type Minimum Feature Device Polysilicon L N - diffusion 2λ W 2λ R = 1 sq x Rs = 104 Ώ EE 213 VLSI Design Stephen Daniels 2003 VLSI Design

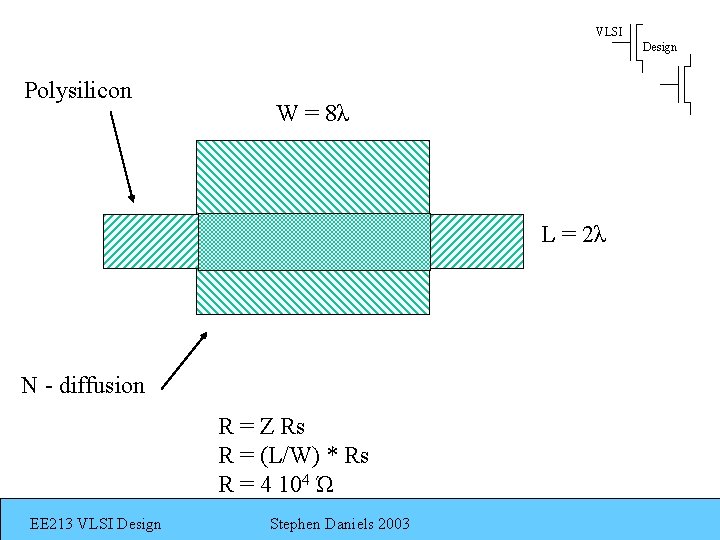

VLSI Design Polysilicon W = 8λ L = 2λ N - diffusion R = Z Rs R = (L/W) * Rs R = 4 104 Ώ EE 213 VLSI Design Stephen Daniels 2003

VLSI Design Exercise Calculate the ON resistance for a depletion pull – up Nmos inverter with Zpu : Zpd ratio 4: 1 Use sheet resistance values given in earlier slide EE 213 VLSI Design Stephen Daniels 2003

VLSI Design Area Capacitance of Layers • Conducting layers are separated from each other by insulators (typically Si. O 2) • This may constitute a parallel plate capacitor, C = є 0єox A / D (farads) • D = thickness of oxide, A = area, • єox = 4 F/µm 2 • Area capacitance given in p. F/µm 2 EE 213 VLSI Design Stephen Daniels 2003

VLSI Design Capacitance • Standard unit for a technology node is the gate - channel capacitance of the minimum sized transistor (2λ x 2λ), given as � Cg • This is a ‘technology specific’ value EE 213 VLSI Design Stephen Daniels 2003

VLSI Design References • Pucknell and Eshraghian pages 94 - 102 EE 213 VLSI Design Stephen Daniels 2003

VLSI Design Delay Unit • For a feature size square gate, τ = Rs x � Cg • i. e for 5µm technology, τ = 104 ohm/sq x 0. 01 p. F = 0. 1 ns • Because of effects of parasitics which we have not considered in our model, delay is typically of the order of 0. 2 - 0. 3 ns • Note that τ is very similar to channel transit time τsd EE 213 VLSI Design Stephen Daniels 2003

VLSI Design CMOS Inverter Delay • Pull-down delay = Rpd x 2 � Cg • Pull-up delay = Rpu x 2� Cg • Asymmetry in rise and fall due to resistance difference between pull-up and pull-down (factor of 2. 5) (due to mobilities of carriers) • Delay through a pair of inverters is 2 τ (fall time) + 5 τ (rise time) • Delay through a pair of CMOS inverters is therefore 7 τ EE 213 VLSI Design Stephen Daniels 2003

VLSI Design CMOS Inverter Delay • Asymmetry can be improved by reducing resistance of pull - up • Reduce resistance of pull - up by increasing channel width ( typically by a factor of 2. 5) • Note that increasing channel width also increases the capacitance • The overall delay (after increasing channel width by 2. 5) will be the same 7 τ EE 213 VLSI Design Stephen Daniels 2003

VLSI Design CMOS Inverter Rise and Fall Time Estimation • Tf ~ 3 CL / βVDD • Τr ~ 3 CL / βVDD • (Derivations for the above are in Pucknell and Eshraghian Pages 105 - 107) • So, τ r/ τf = βn/βp • Given that (due to mobilities) βn = 2. 5 βp, rise time is slower by a factor of 2. 5 when using minimum dimensions of n and p transistors EE 213 VLSI Design Stephen Daniels 2003

- Slides: 14