332 437 Lecture 9 Verilog Example Verilog Design

![Module Declaration module pinballmachine (input clk, reset_bar, output reg [0: 2] pstate, output reg Module Declaration module pinballmachine (input clk, reset_bar, output reg [0: 2] pstate, output reg](https://slidetodoc.com/presentation_image/fc095c8da72346de2bcb934f65f1583d/image-11.jpg)

![system Module module system (); wire clk; wire reset_bar; wire [0: 2] pstate; wire system Module module system (); wire clk; wire reset_bar; wire [0: 2] pstate; wire](https://slidetodoc.com/presentation_image/fc095c8da72346de2bcb934f65f1583d/image-30.jpg)

- Slides: 31

332: 437 Lecture 9 Verilog Example Verilog Design Methodology n Pinball Machine n Verilog Coding n States n State transition diagram n Final Verilog Code n Summary n 10/7/2020 Bushnell: Digital Systems Design Lecture 9 1

Verilog Design Methodology n Draw a System Block Diagram As if you were designing the hardware by hand n Label all signals n n For each block: n Determine whether it is controlled by clocks or reset signals • If so, it is sequential • If not, it is combinational 10/7/2020 Bushnell: Digital Systems Design Lecture 9 2

Verilog Design Methodology n Combinational blocks n n Map into combinational always block or into assign statement Sequential blocks n Map into always block controlled by: • {posedge, negedge} clk • {posedge, negedge} reset, set 10/7/2020 Bushnell: Digital Systems Design Lecture 9 3

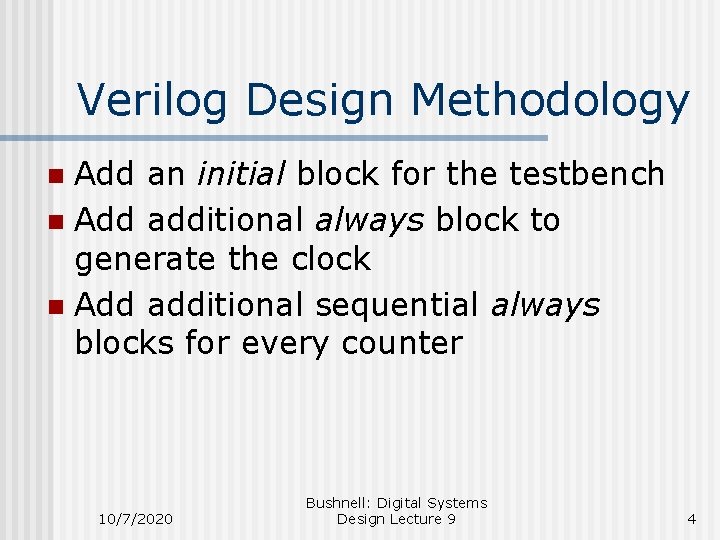

Verilog Design Methodology Add an initial block for the testbench n Add additional always block to generate the clock n Add additional sequential always blocks for every counter n 10/7/2020 Bushnell: Digital Systems Design Lecture 9 4

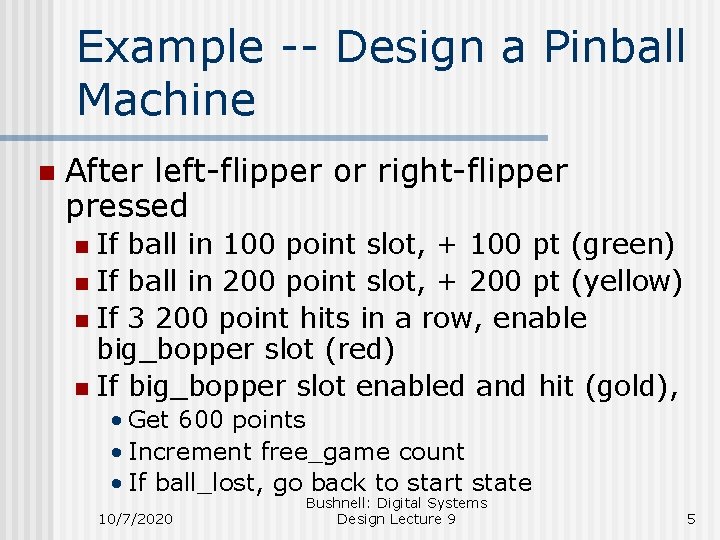

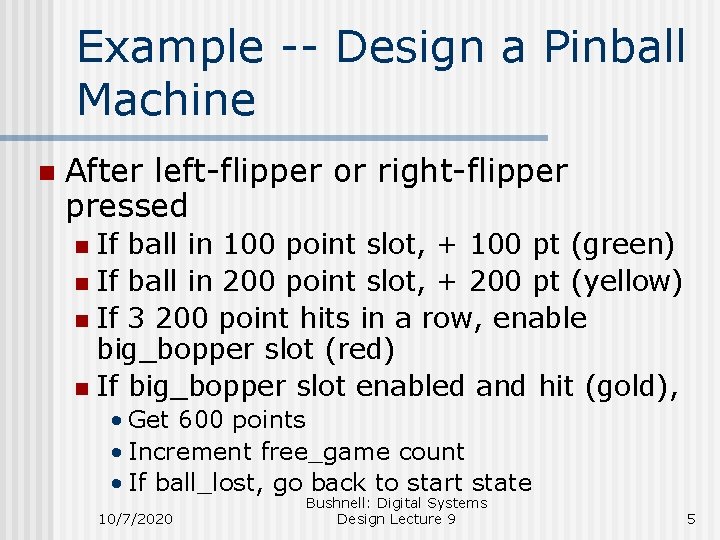

Example -- Design a Pinball Machine n After left-flipper or right-flipper pressed If ball in 100 point slot, + 100 pt (green) n If ball in 200 point slot, + 200 pt (yellow) n If 3 200 point hits in a row, enable big_bopper slot (red) n If big_bopper slot enabled and hit (gold), n • Get 600 points • Increment free_game count • If ball_lost, go back to start state 10/7/2020 Bushnell: Digital Systems Design Lecture 9 5

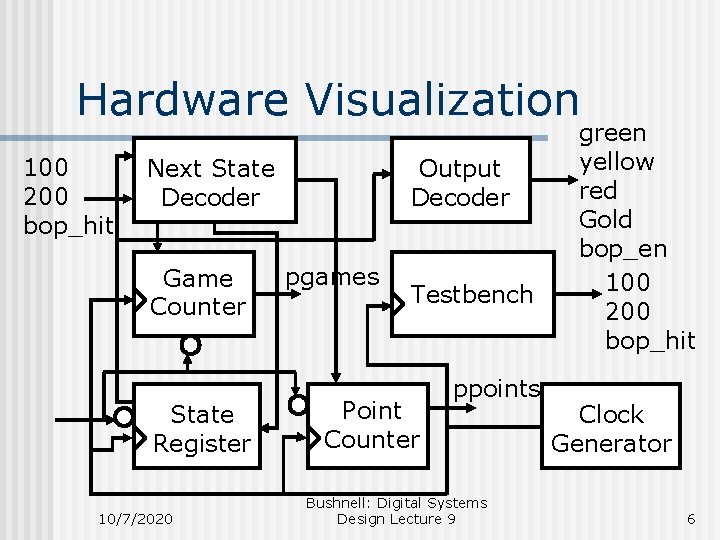

Hardware Visualization 100 200 bop_hit Next State Decoder Game Counter State Register 10/7/2020 Output Decoder pgames Testbench Point Counter ppoints Bushnell: Digital Systems Design Lecture 9 green yellow red Gold bop_en 100 200 bop_hit Clock Generator 6

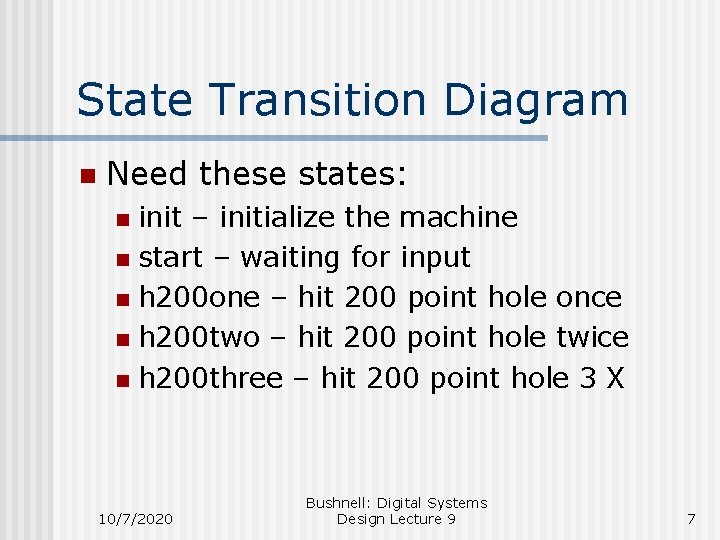

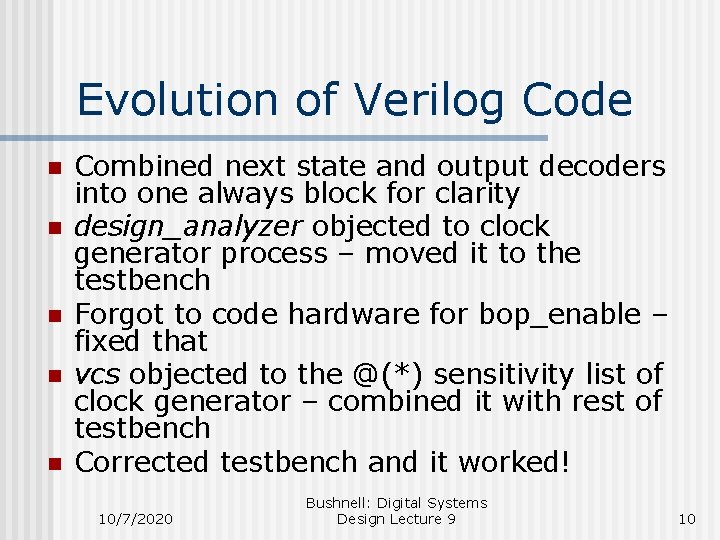

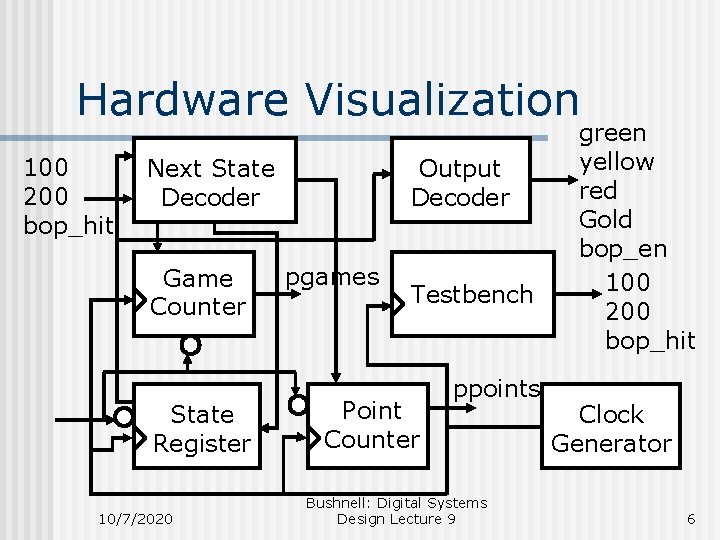

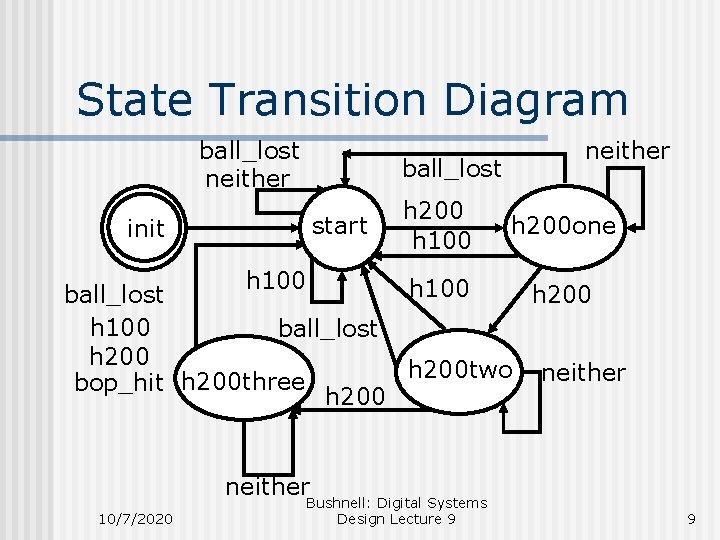

State Transition Diagram n Need these states: init – initialize the machine n start – waiting for input n h 200 one – hit 200 point hole once n h 200 two – hit 200 point hole twice n h 200 three – hit 200 point hole 3 X n 10/7/2020 Bushnell: Digital Systems Design Lecture 9 7

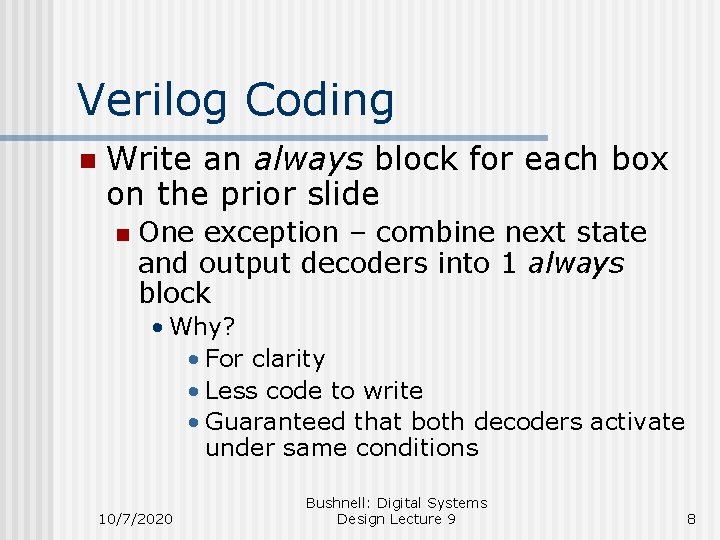

Verilog Coding n Write an always block for each box on the prior slide n One exception – combine next state and output decoders into 1 always block • Why? • For clarity • Less code to write • Guaranteed that both decoders activate under same conditions 10/7/2020 Bushnell: Digital Systems Design Lecture 9 8

State Transition Diagram ball_lost neither ball_lost start init h 200 h 100 neither h 200 one h 100 ball_lost h 200 two neither bop_hit h 200 three h 200 neither 10/7/2020 Bushnell: Digital Systems Design Lecture 9 9

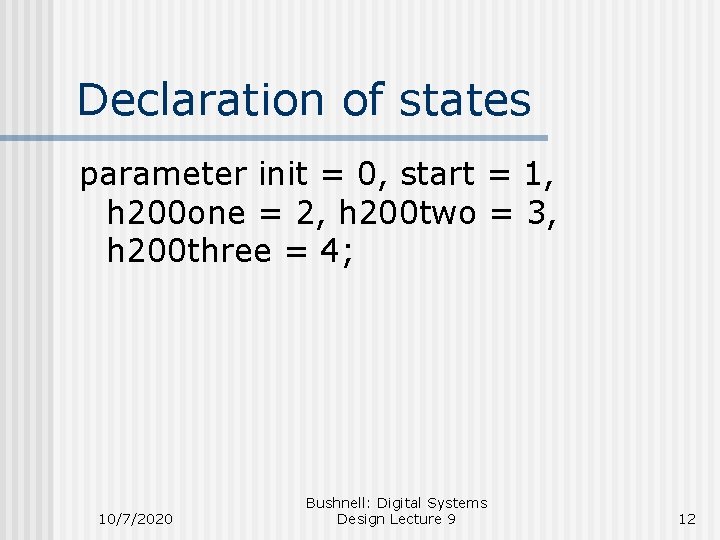

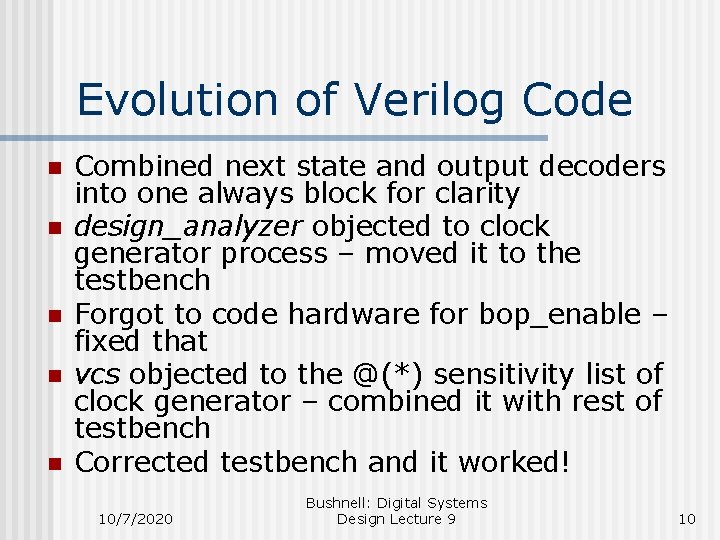

Evolution of Verilog Code n n n Combined next state and output decoders into one always block for clarity design_analyzer objected to clock generator process – moved it to the testbench Forgot to code hardware for bop_enable – fixed that vcs objected to the @(*) sensitivity list of clock generator – combined it with rest of testbench Corrected testbench and it worked! 10/7/2020 Bushnell: Digital Systems Design Lecture 9 10

![Module Declaration module pinballmachine input clk resetbar output reg 0 2 pstate output reg Module Declaration module pinballmachine (input clk, reset_bar, output reg [0: 2] pstate, output reg](https://slidetodoc.com/presentation_image/fc095c8da72346de2bcb934f65f1583d/image-11.jpg)

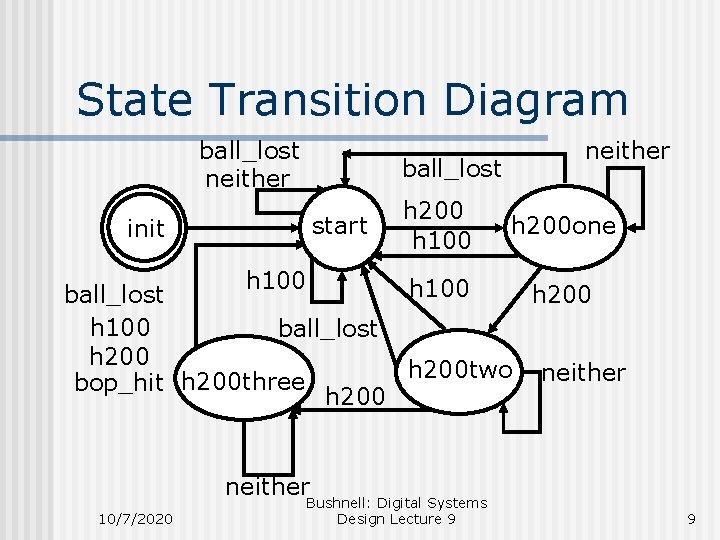

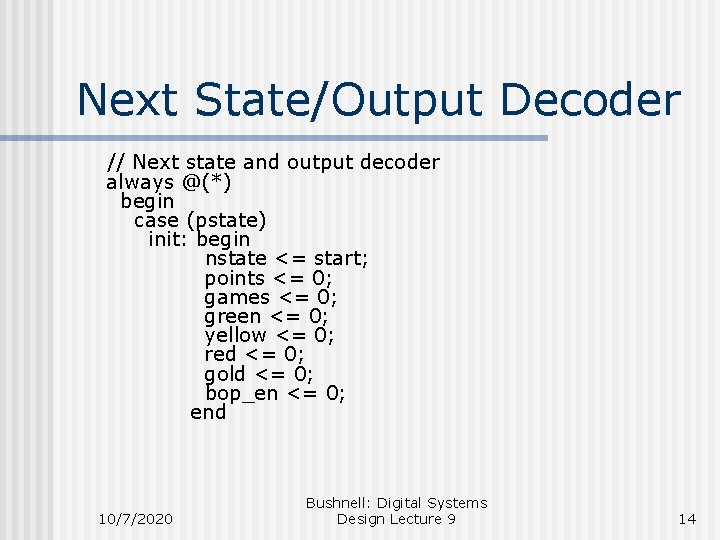

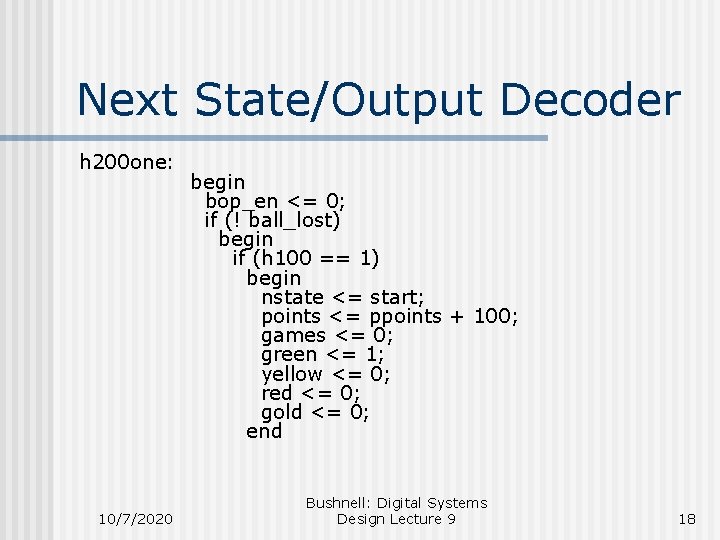

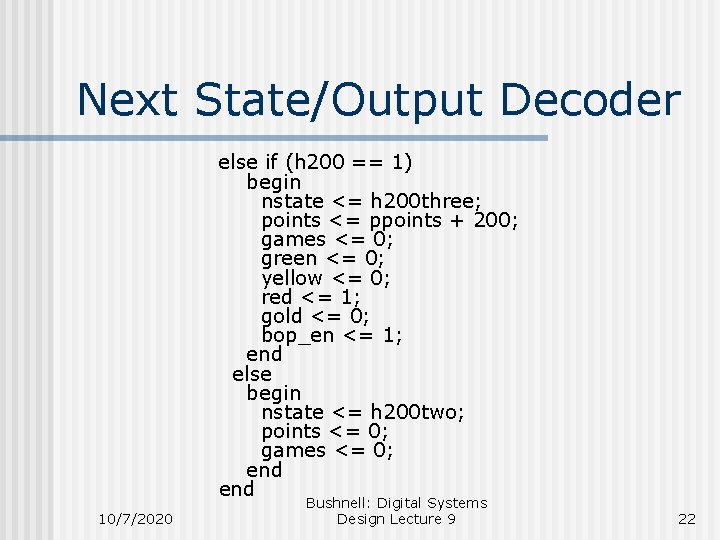

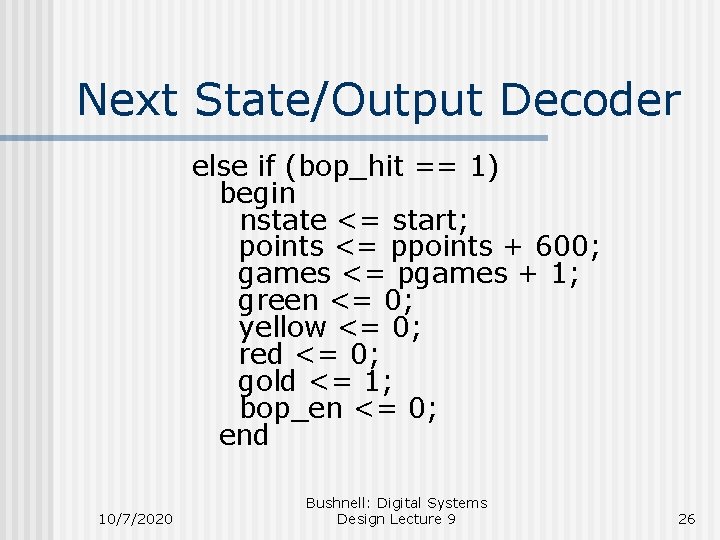

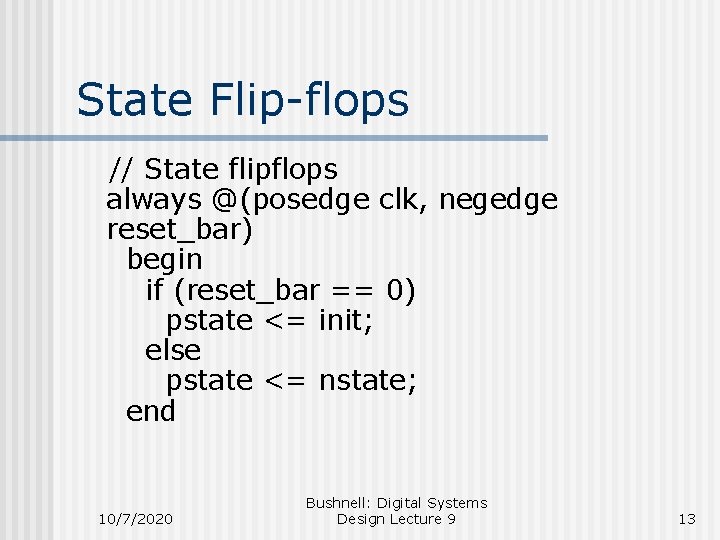

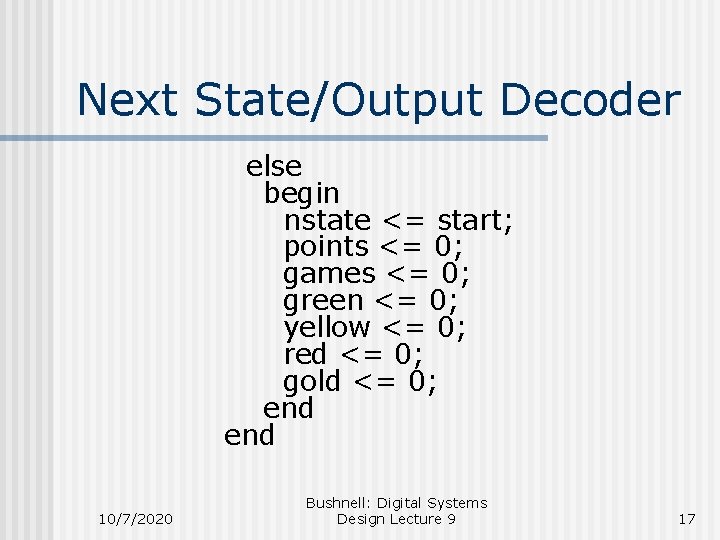

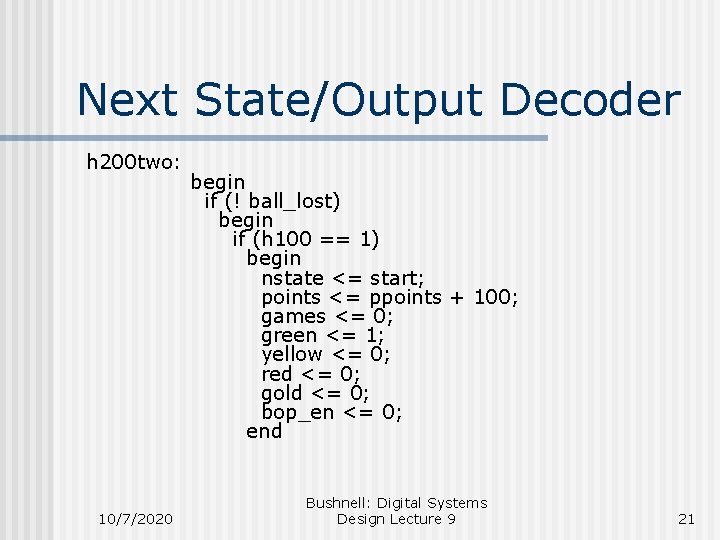

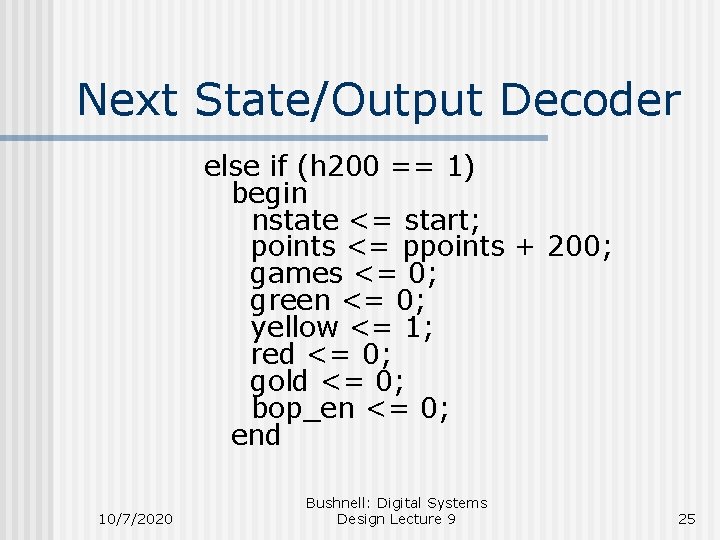

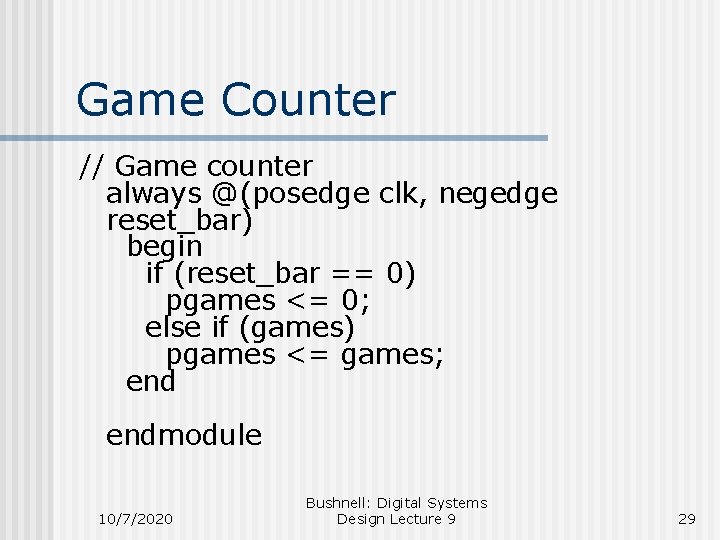

Module Declaration module pinballmachine (input clk, reset_bar, output reg [0: 2] pstate, output reg [0: 2] nstate, output reg [0: 4] games, output reg [0: 15] points, output reg [0: 4] pgames, output reg [0: 15] ppoints, input h 100, h 200, bop_hit, ball_lost, output reg bop_en, green, yellow, red, gold); 10/7/2020 Bushnell: Digital Systems Design Lecture 9 11

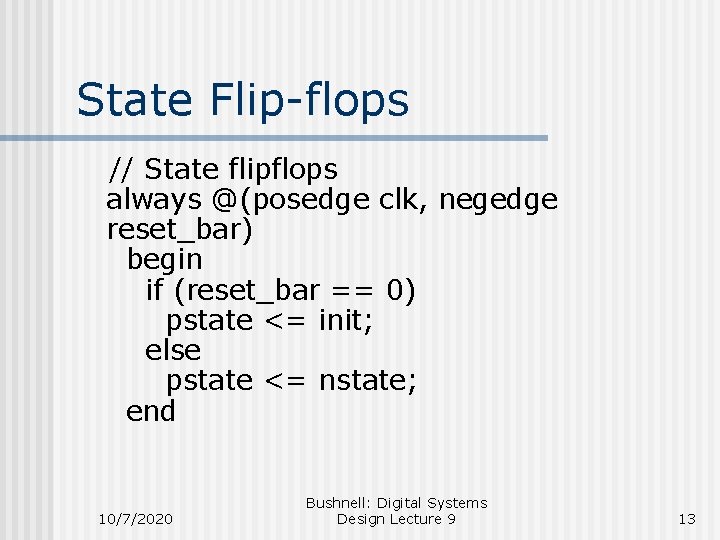

Declaration of states parameter init = 0, start = 1, h 200 one = 2, h 200 two = 3, h 200 three = 4; 10/7/2020 Bushnell: Digital Systems Design Lecture 9 12

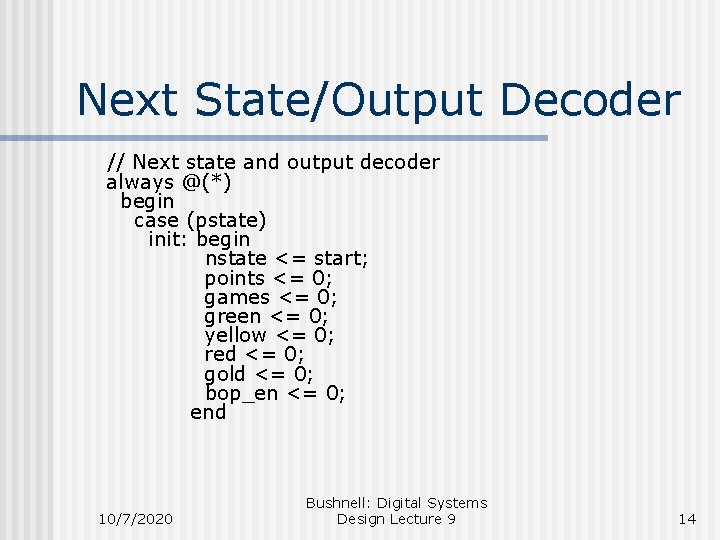

State Flip-flops // State flipflops always @(posedge clk, negedge reset_bar) begin if (reset_bar == 0) pstate <= init; else pstate <= nstate; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 13

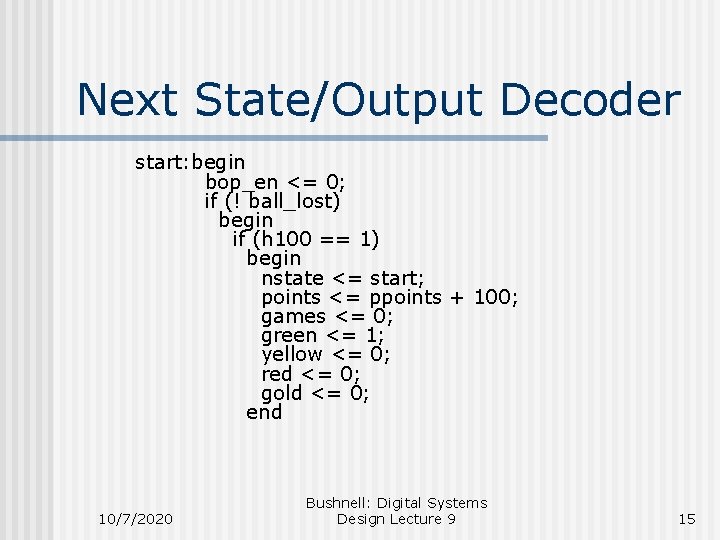

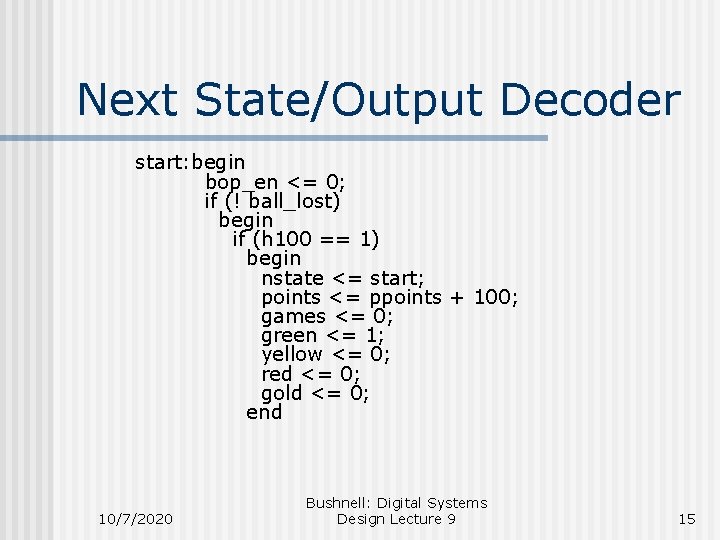

Next State/Output Decoder // Next state and output decoder always @(*) begin case (pstate) init: begin nstate <= start; points <= 0; games <= 0; green <= 0; yellow <= 0; red <= 0; gold <= 0; bop_en <= 0; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 14

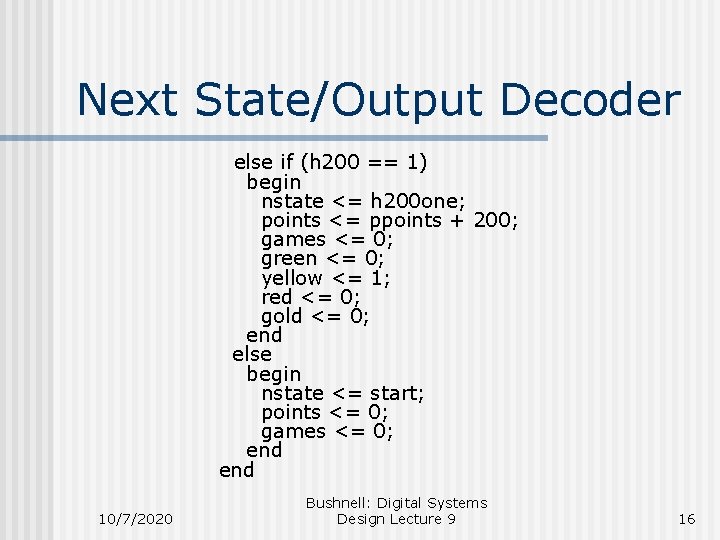

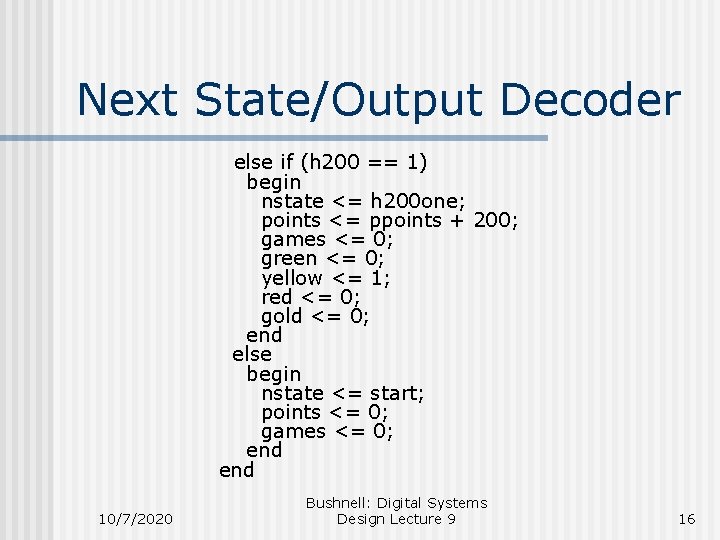

Next State/Output Decoder start: begin bop_en <= 0; if (! ball_lost) begin if (h 100 == 1) begin nstate <= start; points <= ppoints + 100; games <= 0; green <= 1; yellow <= 0; red <= 0; gold <= 0; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 15

Next State/Output Decoder else if (h 200 == 1) begin nstate <= h 200 one; points <= ppoints + 200; games <= 0; green <= 0; yellow <= 1; red <= 0; gold <= 0; end else begin nstate <= start; points <= 0; games <= 0; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 16

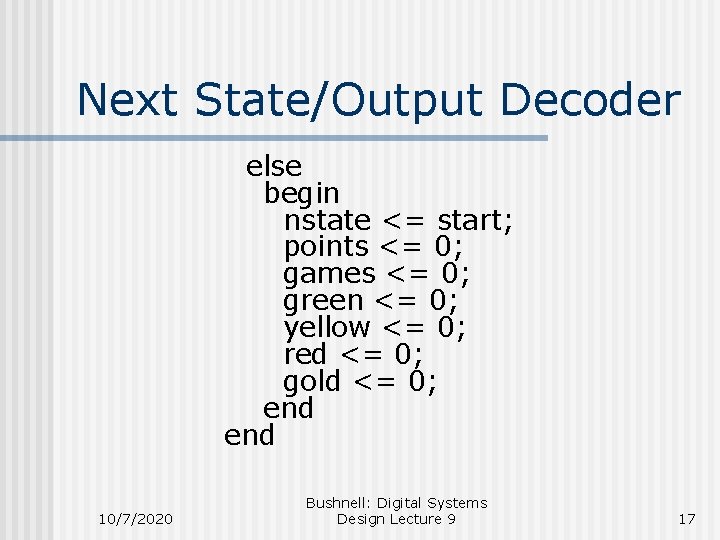

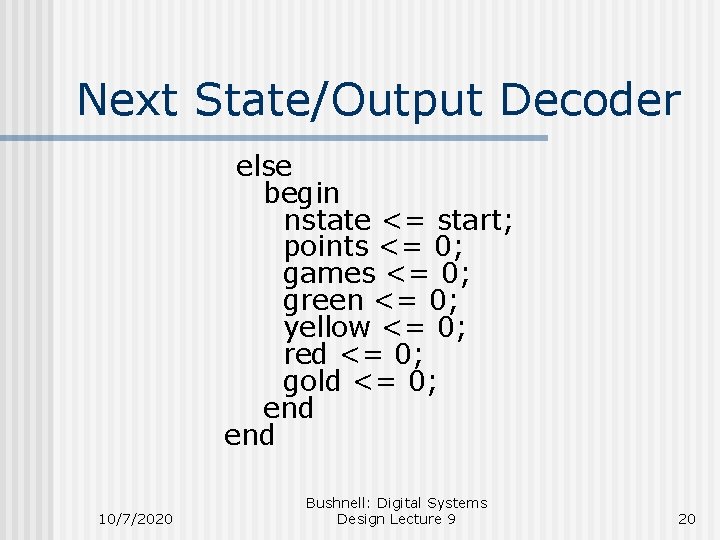

Next State/Output Decoder else begin nstate <= start; points <= 0; games <= 0; green <= 0; yellow <= 0; red <= 0; gold <= 0; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 17

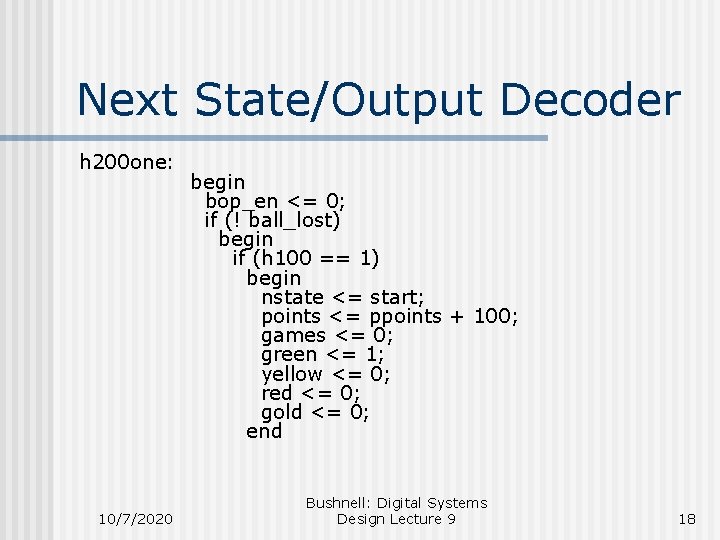

Next State/Output Decoder h 200 one: 10/7/2020 begin bop_en <= 0; if (! ball_lost) begin if (h 100 == 1) begin nstate <= start; points <= ppoints + 100; games <= 0; green <= 1; yellow <= 0; red <= 0; gold <= 0; end Bushnell: Digital Systems Design Lecture 9 18

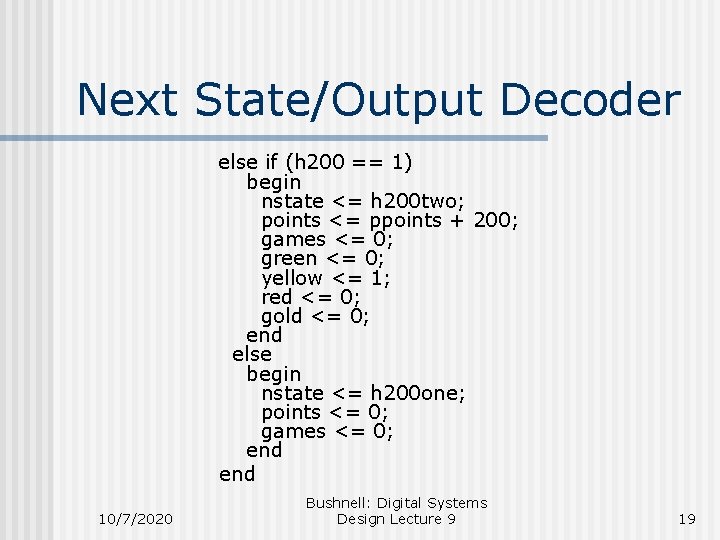

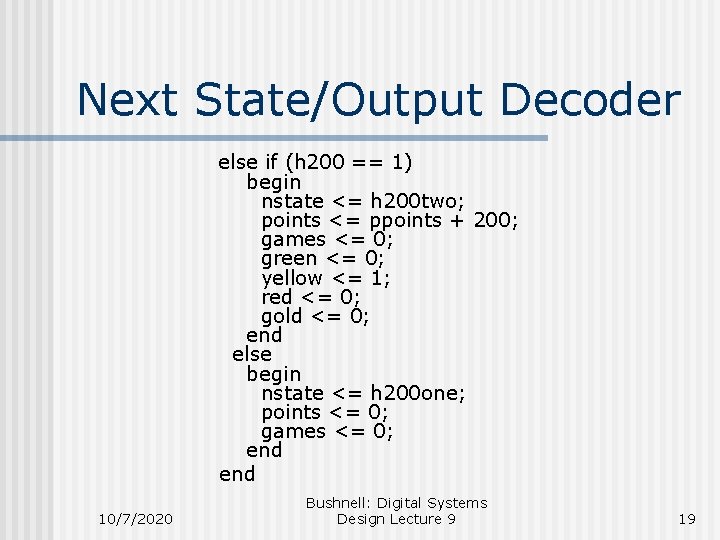

Next State/Output Decoder else if (h 200 == 1) begin nstate <= h 200 two; points <= ppoints + 200; games <= 0; green <= 0; yellow <= 1; red <= 0; gold <= 0; end else begin nstate <= h 200 one; points <= 0; games <= 0; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 19

Next State/Output Decoder else begin nstate <= start; points <= 0; games <= 0; green <= 0; yellow <= 0; red <= 0; gold <= 0; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 20

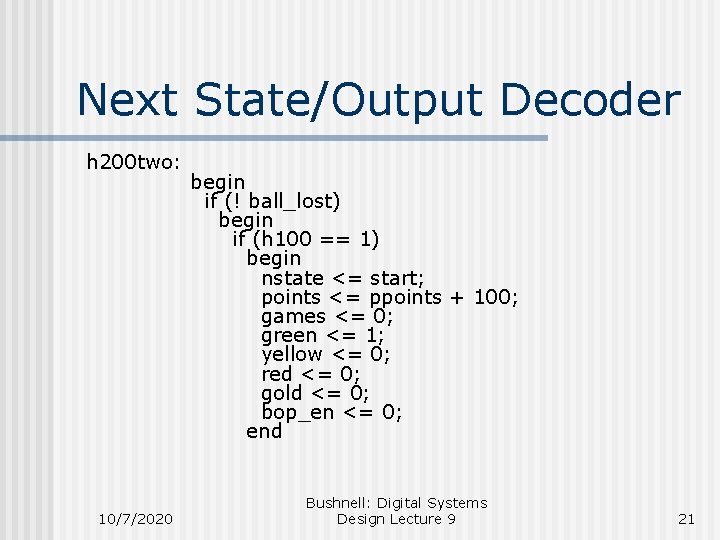

Next State/Output Decoder h 200 two: 10/7/2020 begin if (! ball_lost) begin if (h 100 == 1) begin nstate <= start; points <= ppoints + 100; games <= 0; green <= 1; yellow <= 0; red <= 0; gold <= 0; bop_en <= 0; end Bushnell: Digital Systems Design Lecture 9 21

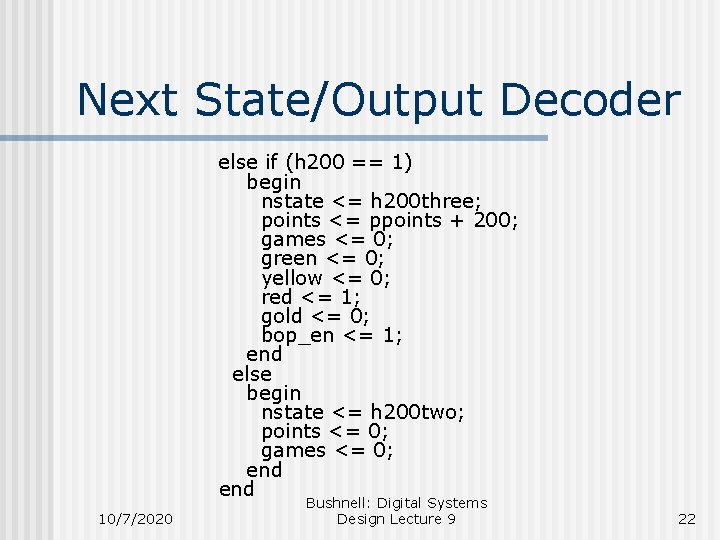

Next State/Output Decoder else if (h 200 == 1) begin nstate <= h 200 three; points <= ppoints + 200; games <= 0; green <= 0; yellow <= 0; red <= 1; gold <= 0; bop_en <= 1; end else begin nstate <= h 200 two; points <= 0; games <= 0; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 22

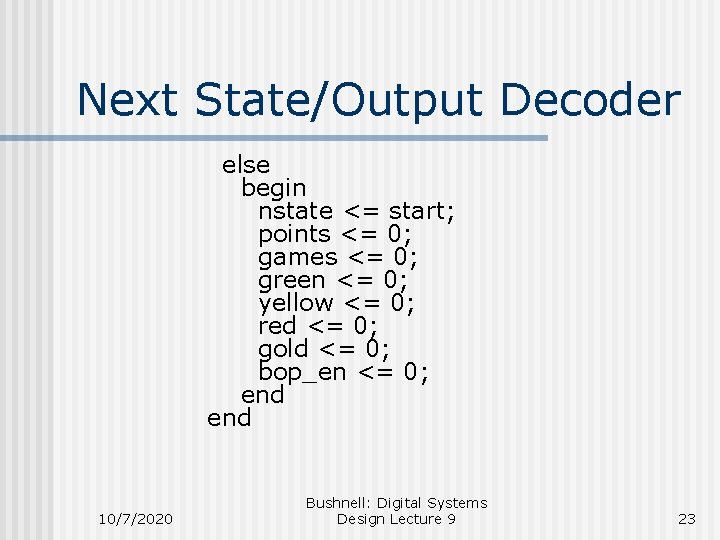

Next State/Output Decoder else begin nstate <= start; points <= 0; games <= 0; green <= 0; yellow <= 0; red <= 0; gold <= 0; bop_en <= 0; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 23

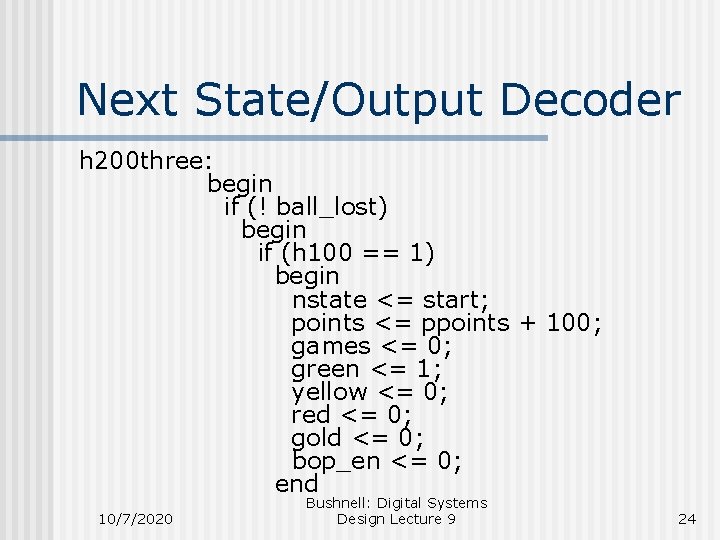

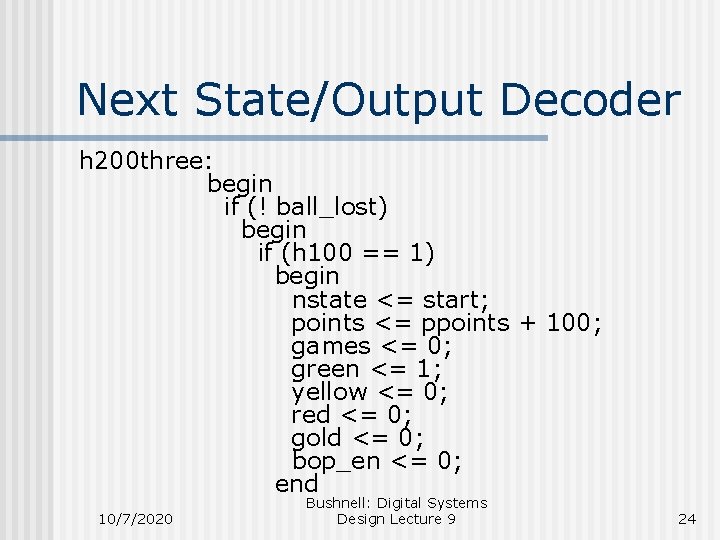

Next State/Output Decoder h 200 three: begin if (! ball_lost) begin if (h 100 == 1) begin nstate <= start; points <= ppoints + 100; games <= 0; green <= 1; yellow <= 0; red <= 0; gold <= 0; bop_en <= 0; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 24

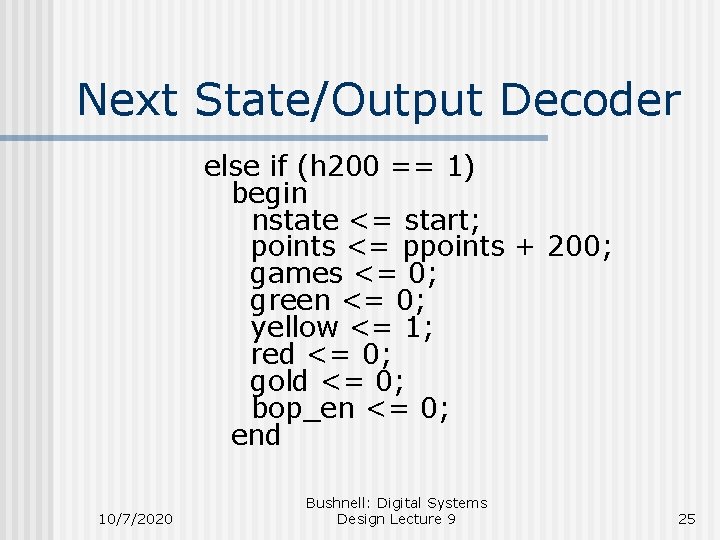

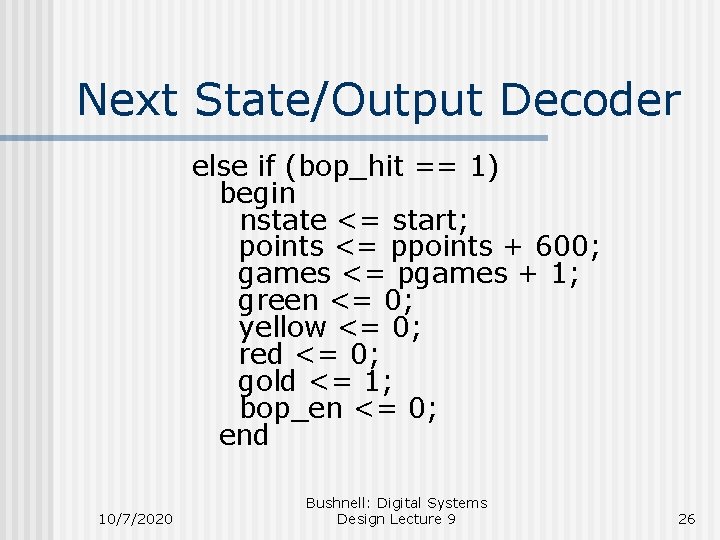

Next State/Output Decoder else if (h 200 == 1) begin nstate <= start; points <= ppoints + 200; games <= 0; green <= 0; yellow <= 1; red <= 0; gold <= 0; bop_en <= 0; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 25

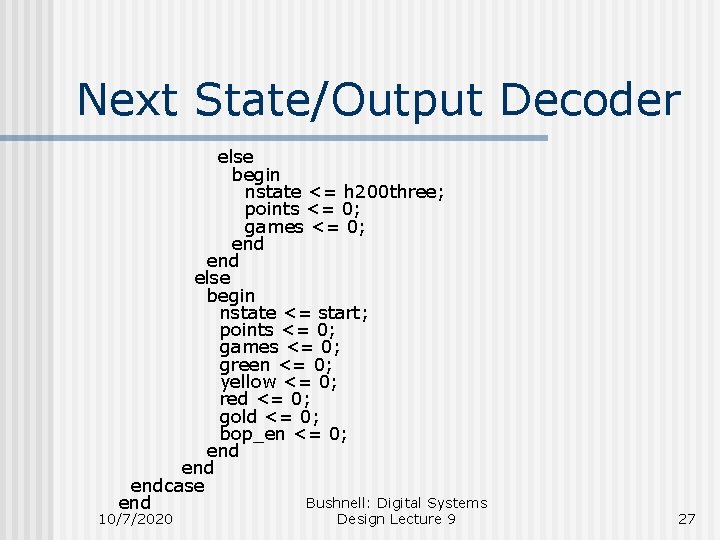

Next State/Output Decoder else if (bop_hit == 1) begin nstate <= start; points <= ppoints + 600; games <= pgames + 1; green <= 0; yellow <= 0; red <= 0; gold <= 1; bop_en <= 0; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 26

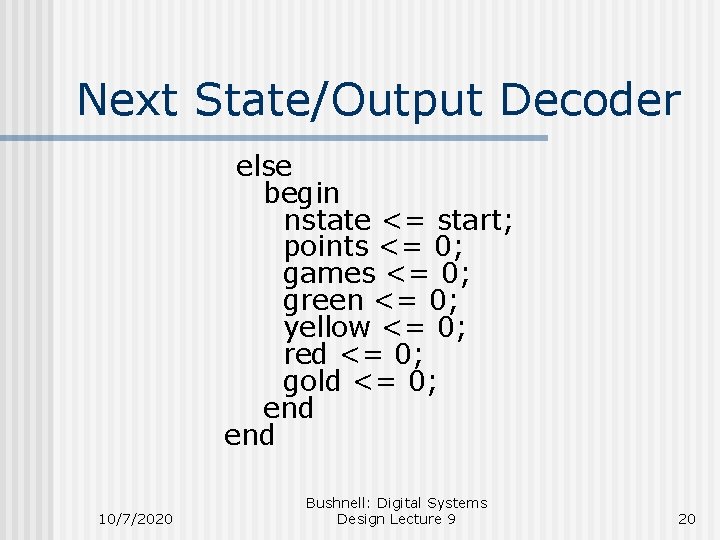

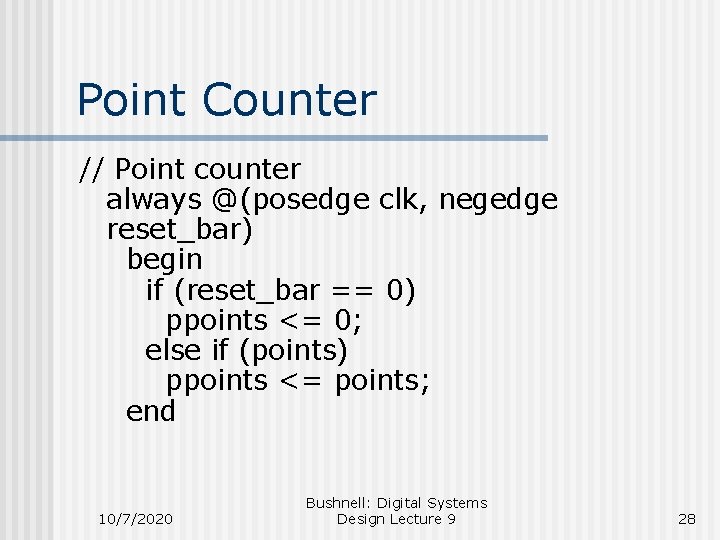

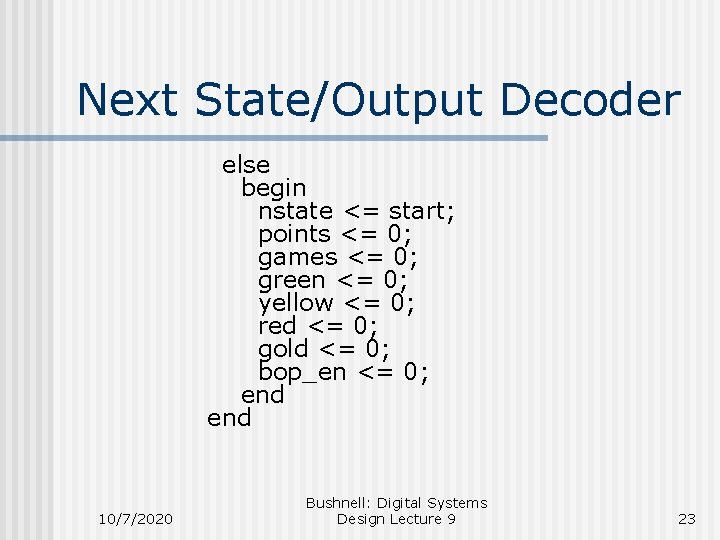

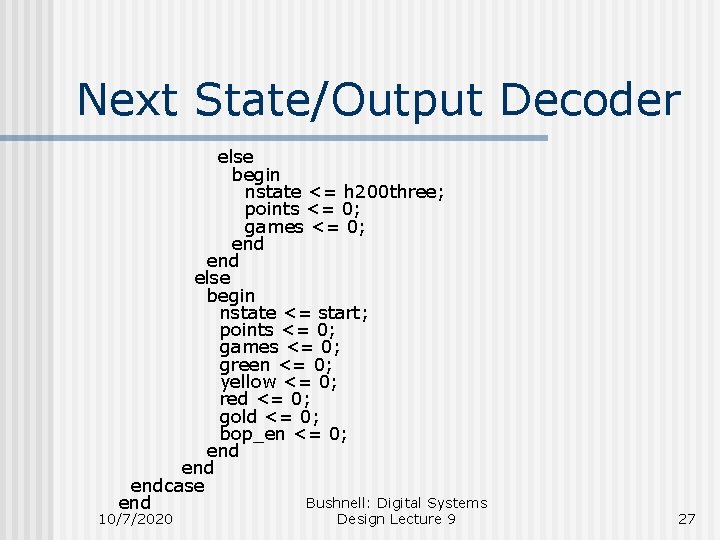

Next State/Output Decoder else begin nstate <= h 200 three; points <= 0; games <= 0; end else begin nstate <= start; points <= 0; games <= 0; green <= 0; yellow <= 0; red <= 0; gold <= 0; bop_en <= 0; end endcase Bushnell: Digital Systems end 10/7/2020 Design Lecture 9 27

Point Counter // Point counter always @(posedge clk, negedge reset_bar) begin if (reset_bar == 0) ppoints <= 0; else if (points) ppoints <= points; end 10/7/2020 Bushnell: Digital Systems Design Lecture 9 28

Game Counter // Game counter always @(posedge clk, negedge reset_bar) begin if (reset_bar == 0) pgames <= 0; else if (games) pgames <= games; endmodule 10/7/2020 Bushnell: Digital Systems Design Lecture 9 29

![system Module module system wire clk wire resetbar wire 0 2 pstate wire system Module module system (); wire clk; wire reset_bar; wire [0: 2] pstate; wire](https://slidetodoc.com/presentation_image/fc095c8da72346de2bcb934f65f1583d/image-30.jpg)

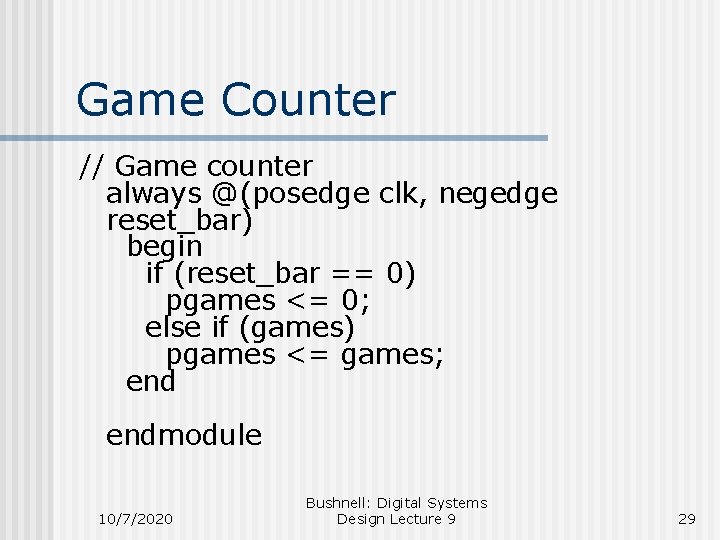

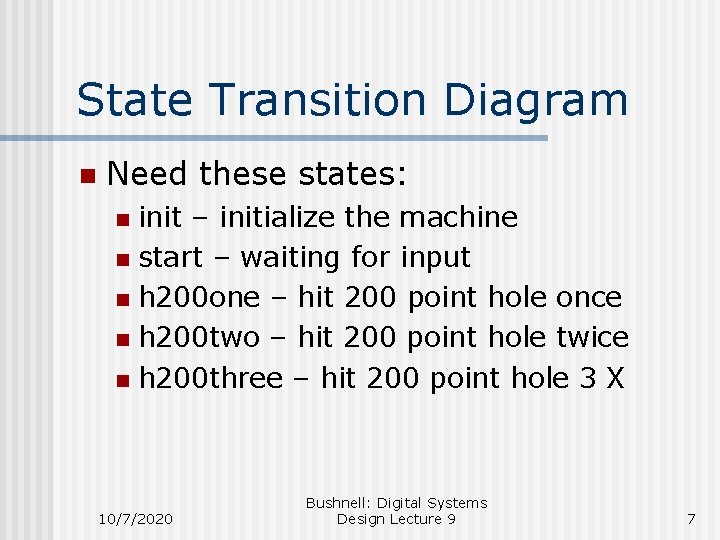

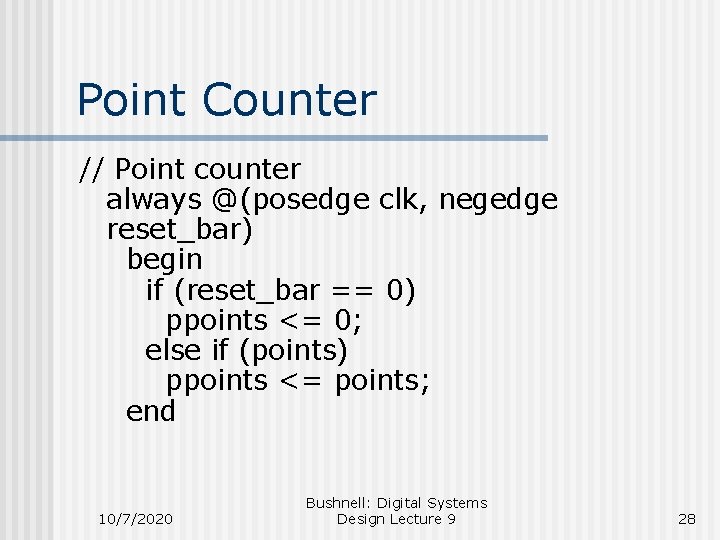

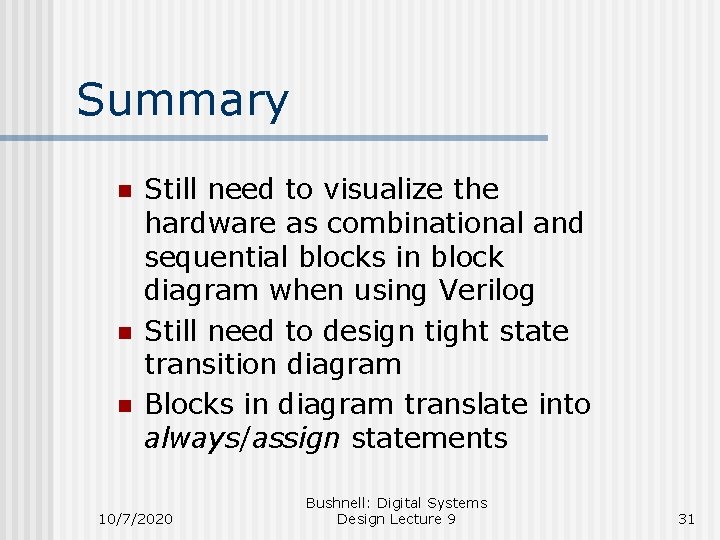

system Module module system (); wire clk; wire reset_bar; wire [0: 2] pstate; wire [0: 2] nstate; wire [0: 4] games; wire [0: 15] points; wire [0: 4] pgames; wire [0: 15] ppoints; wire h 100, h 200, bop_hit, ball_lost; wire bop_en; wire green, yellow, red, gold; pinballmachine (clk, reset_bar, pstate, nstate, games, points, pgames, ppoints, h 100, h 200, bop_hit, ball_lost, bop_en, green, yellow, red, gold); testbench (clk, reset_bar, pstate, nstate, games, points, pgames, ppoints, h 100, h 200, bop_hit, ball_lost, bop_en, green, yellow, red, gold); endmodule 10/7/2020 Bushnell: Digital Systems Design Lecture 9 30

Summary n n n Still need to visualize the hardware as combinational and sequential blocks in block diagram when using Verilog Still need to design tight state transition diagram Blocks in diagram translate into always/assign statements 10/7/2020 Bushnell: Digital Systems Design Lecture 9 31