ECE 425 VLSI Circuit Design Lecture 1 Course

- Slides: 42

ECE 425 - VLSI Circuit Design Lecture 1 - Course Overview Spring 2007 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042 nestorj@lafayette. edu ECE 425 Spring 2007 Lecture 1 - Course Overview 1

Announcements } Course Website: http: //foghorn. cadlab. lafayette. edu/ece 425/ } Brief Lab Tomorrow in AEC 400 } Reading } Wolf 1, 2. 1 -2. 3 ECE 425 Spring 2007 Lecture 1 - Course Overview 2

Today’s Topics } Course overview } Objectives } Roadmap for the Semester } Administrative Details } VLSI Overview } } Transistor Structure Static CMOS Logic Design Methods & Design Styles VLSI Trends ECE 425 Spring 2007 Lecture 1 - Course Overview 3

Course Objectives } Students should be able to… } VLSI Circuit Analysis: • • • Understand MOS transistor operation, design eqns. Understand parasitics & perform simple calculations Understand static & dynamic CMOS logic Estimate delay of CMOS gates, networks, & long wires Estimate power consumption Understand design and operation of latches & flip/flops } CMOS Processing and Layout • • • Understand the VLSI manufacturing process. Have an appreciation of current trends in VLSI manufacturing. Understand layout design rules. Design and analyze layouts for simple digital CMOS circuits Design and analyze hierarchical circuit layouts. Understand ASIC Layout styles. ECE 425 Spring 2007 Lecture 1 - Course Overview 4

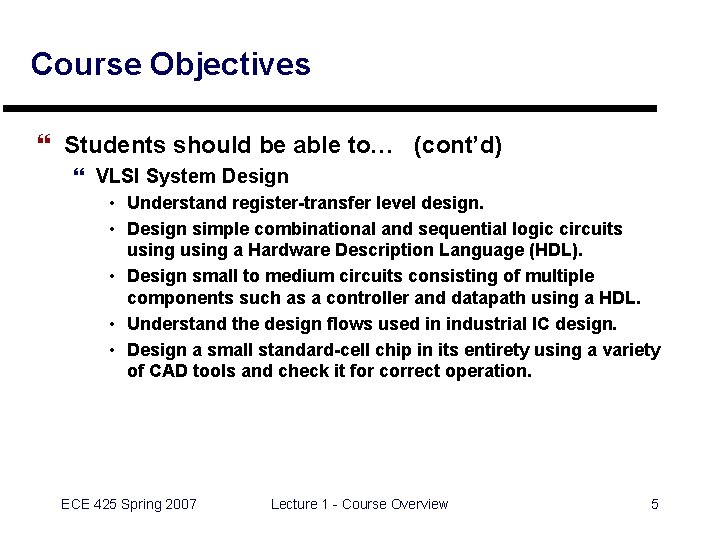

Course Objectives } Students should be able to… (cont’d) } VLSI System Design • Understand register-transfer level design. • Design simple combinational and sequential logic circuits using a Hardware Description Language (HDL). • Design small to medium circuits consisting of multiple components such as a controller and datapath using a HDL. • Understand the design flows used in industrial IC design. • Design a small standard-cell chip in its entirety using a variety of CAD tools and check it for correct operation. ECE 425 Spring 2007 Lecture 1 - Course Overview 5

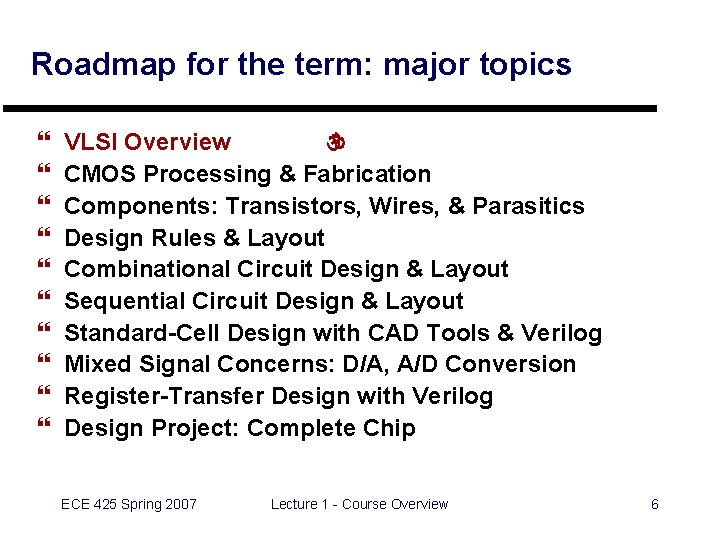

Roadmap for the term: major topics } } } } } VLSI Overview CMOS Processing & Fabrication Components: Transistors, Wires, & Parasitics Design Rules & Layout Combinational Circuit Design & Layout Sequential Circuit Design & Layout Standard-Cell Design with CAD Tools & Verilog Mixed Signal Concerns: D/A, A/D Conversion Register-Transfer Design with Verilog Design Project: Complete Chip ECE 425 Spring 2007 Lecture 1 - Course Overview 6

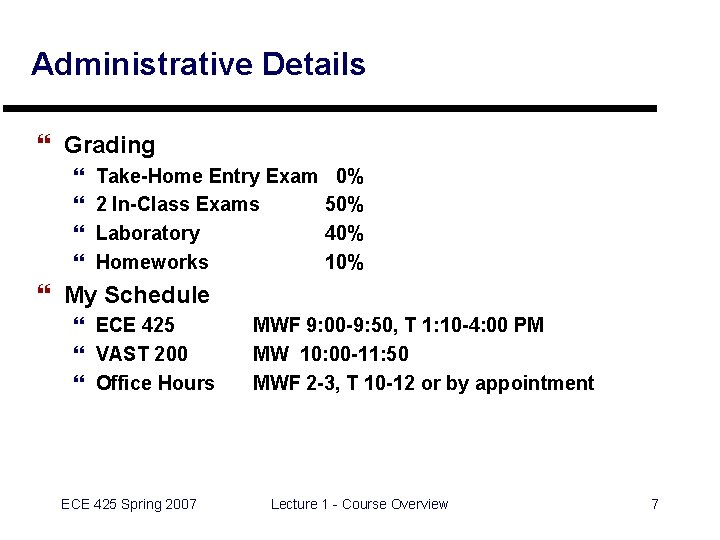

Administrative Details } Grading } } Take-Home Entry Exam 2 In-Class Exams Laboratory Homeworks 0% 50% 40% 10% } My Schedule } ECE 425 } VAST 200 } Office Hours ECE 425 Spring 2007 MWF 9: 00 -9: 50, T 1: 10 -4: 00 PM MW 10: 00 -11: 50 MWF 2 -3, T 10 -12 or by appointment Lecture 1 - Course Overview 7

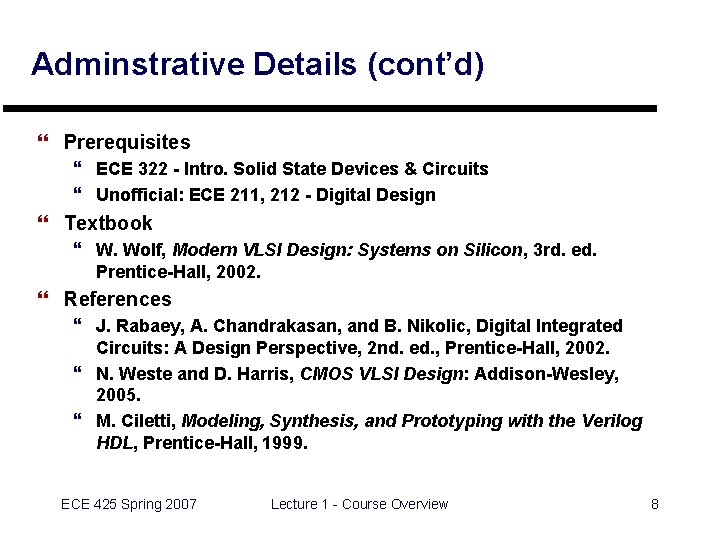

Adminstrative Details (cont’d) } Prerequisites } ECE 322 - Intro. Solid State Devices & Circuits } Unofficial: ECE 211, 212 - Digital Design } Textbook } W. Wolf, Modern VLSI Design: Systems on Silicon, 3 rd. ed. Prentice-Hall, 2002. } References } J. Rabaey, A. Chandrakasan, and B. Nikolic, Digital Integrated Circuits: A Design Perspective, 2 nd. ed. , Prentice-Hall, 2002. } N. Weste and D. Harris, CMOS VLSI Design: Addison-Wesley, 2005. } M. Ciletti, Modeling, Synthesis, and Prototyping with the Verilog HDL, Prentice-Hall, 1999. ECE 425 Spring 2007 Lecture 1 - Course Overview 8

VLSI Overview } Common technologies } CMOS Transistors & Logic Gates } Structure } “Switch-Level” Transistor Model } Basic gates } The VLSI Design Process } Levels of Abstraction } Design steps } Design styles } VLSI Trends ECE 425 Spring 2007 Lecture 1 - Course Overview 9

VLSI Technology Overview } Common technologies: } } } CMOS* (dominant technology) Bipolar (e. g. , TTL) Bi-CMOS - hybrid Bipolar, CMOS (for high speed) Ga. As - Gallium Arsenide (for high speed) Si-Ge - Silicon Germanium (for RF) } Key manufacturing technology: photolithography *Complementary Metal Oxide Semiconductor ECE 425 Spring 2007 Lecture 1 - Course Overview 10

VLSI Technology - CMOS Transistors Key feature: transistor length L ECE 425 Spring 2007 2002: L=130 nm 2003: L=90 nm 2005: L=65 nm 2007: L=45 nm? Lecture 1 - Course Overview 11

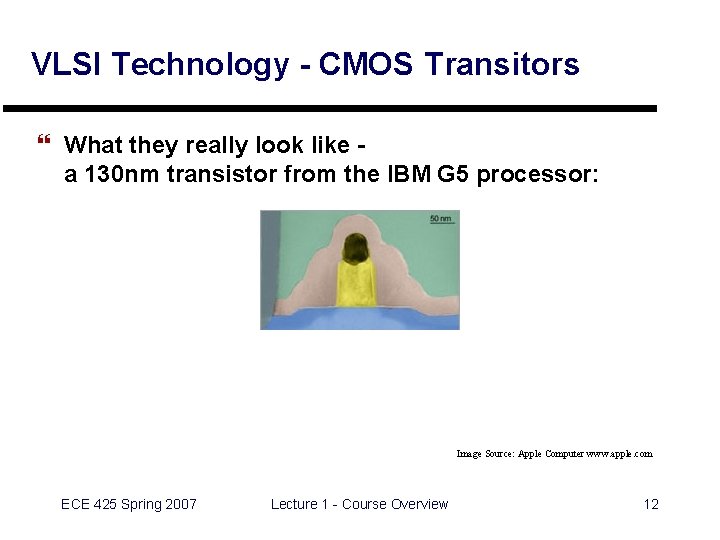

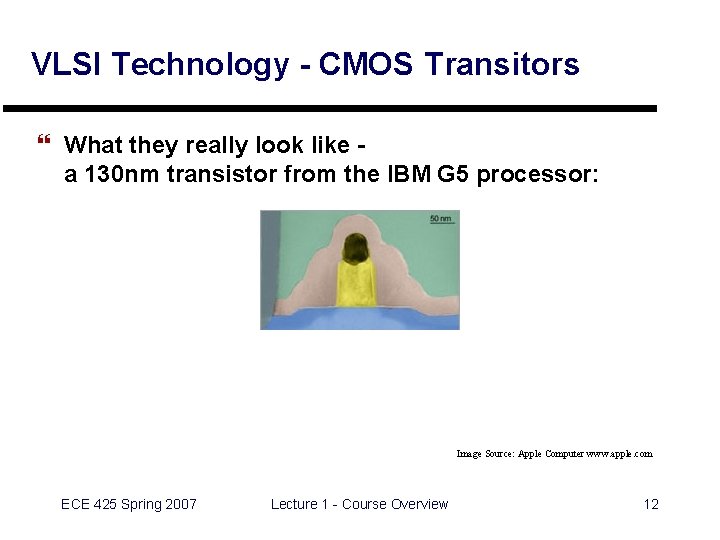

VLSI Technology - CMOS Transitors } What they really look like a 130 nm transistor from the IBM G 5 processor: Image Source: Apple Computer www. apple. com ECE 425 Spring 2007 Lecture 1 - Course Overview 12

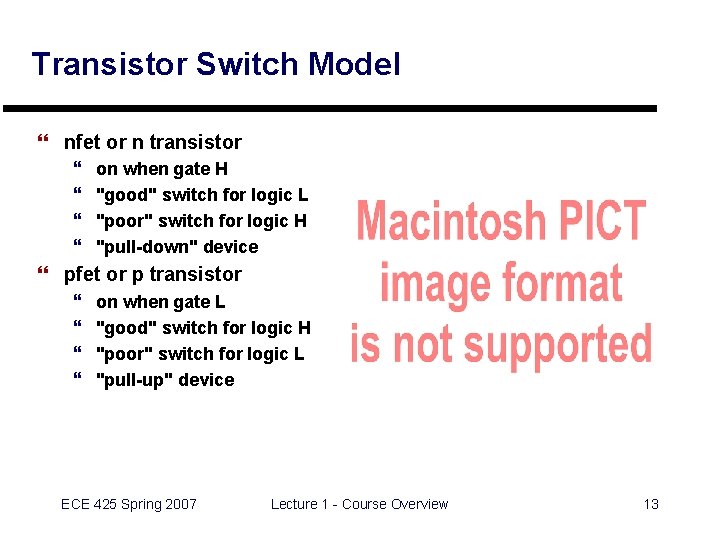

Transistor Switch Model } nfet or n transistor } } on when gate H "good" switch for logic L "poor" switch for logic H "pull-down" device } pfet or p transistor } } on when gate L "good" switch for logic H "poor" switch for logic L "pull-up" device ECE 425 Spring 2007 Lecture 1 - Course Overview 13

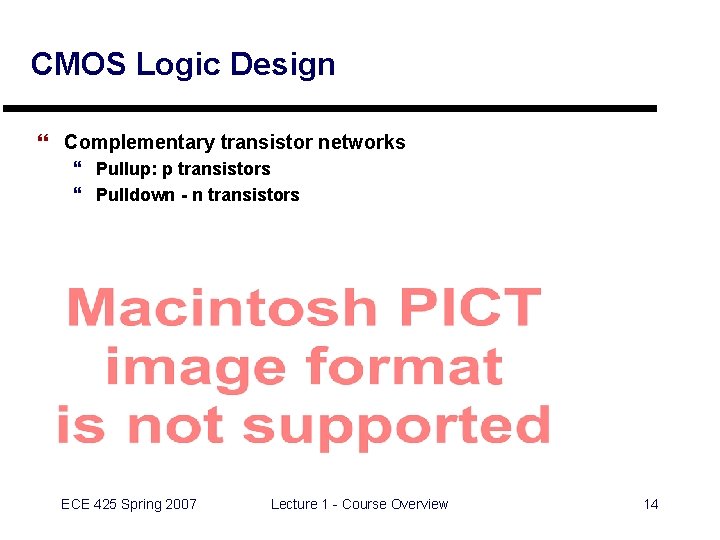

CMOS Logic Design } Complementary transistor networks } Pullup: p transistors } Pulldown - n transistors ECE 425 Spring 2007 Lecture 1 - Course Overview 14

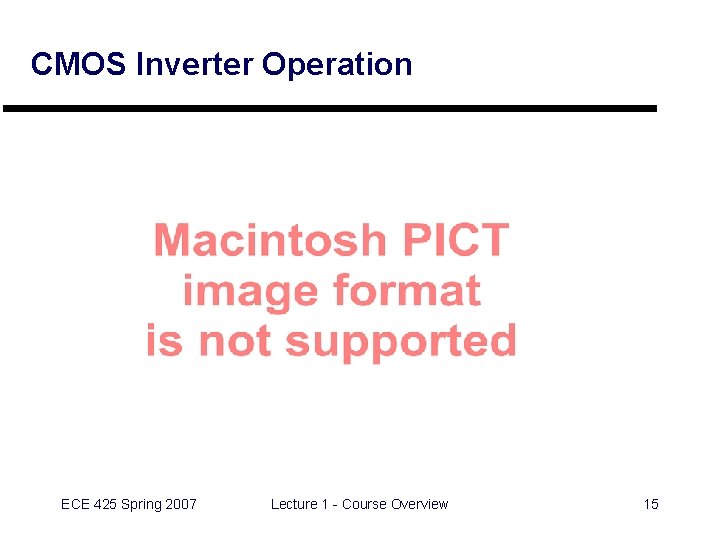

CMOS Inverter Operation ECE 425 Spring 2007 Lecture 1 - Course Overview 15

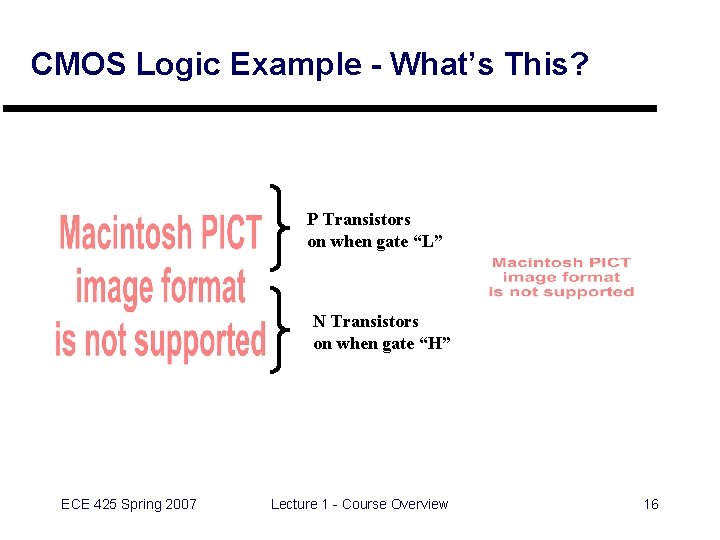

CMOS Logic Example - What’s This? P Transistors on when gate “L” N Transistors on when gate “H” ECE 425 Spring 2007 Lecture 1 - Course Overview 16

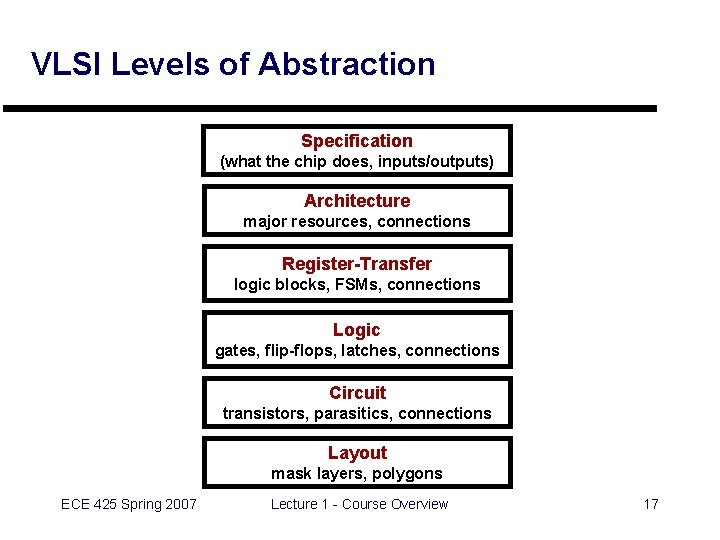

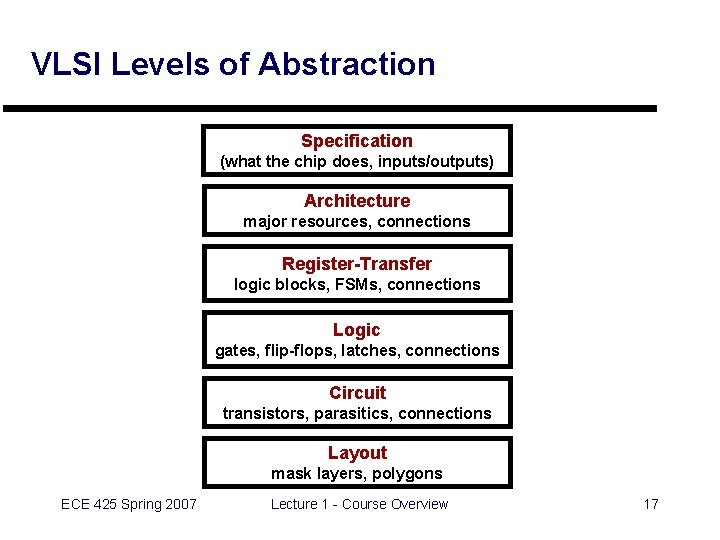

VLSI Levels of Abstraction Specification (what the chip does, inputs/outputs) Architecture major resources, connections Register-Transfer logic blocks, FSMs, connections Logic gates, flip-flops, latches, connections Circuit transistors, parasitics, connections Layout mask layers, polygons ECE 425 Spring 2007 Lecture 1 - Course Overview 17

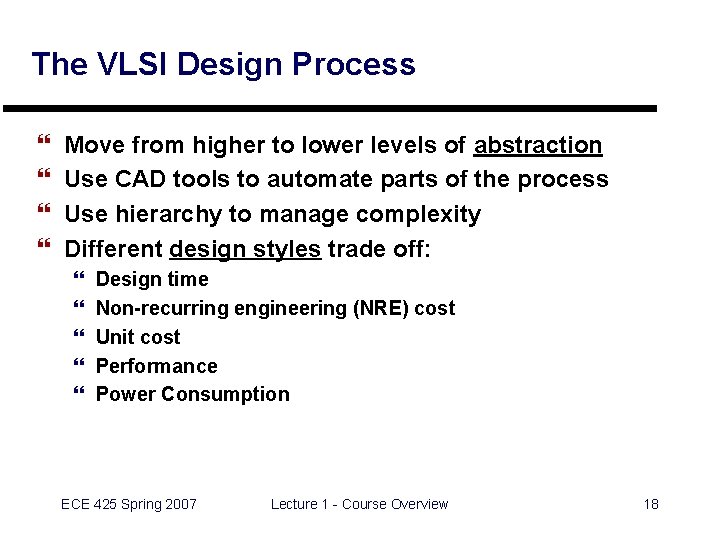

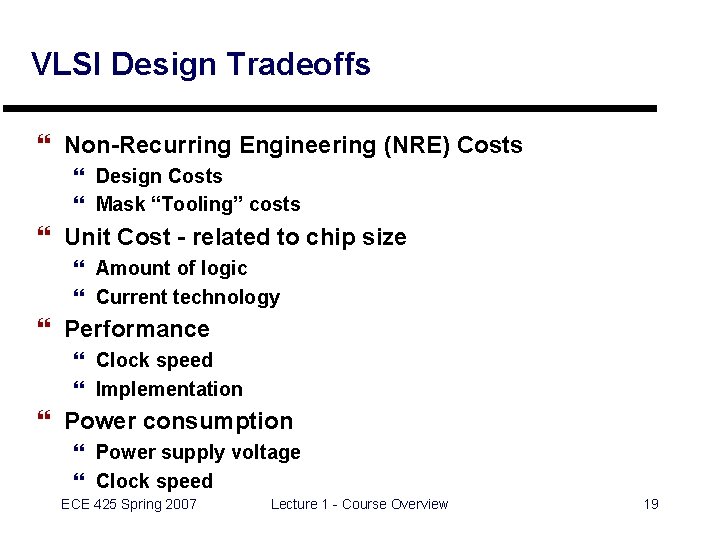

The VLSI Design Process } } Move from higher to lower levels of abstraction Use CAD tools to automate parts of the process Use hierarchy to manage complexity Different design styles trade off: } } } Design time Non-recurring engineering (NRE) cost Unit cost Performance Power Consumption ECE 425 Spring 2007 Lecture 1 - Course Overview 18

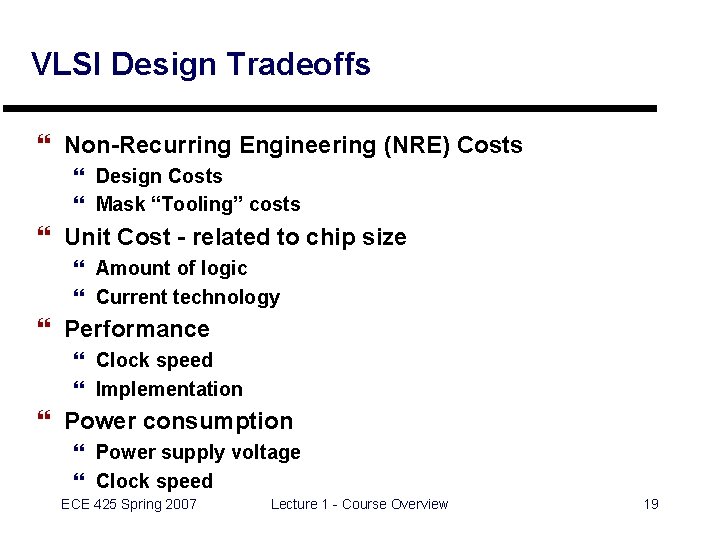

VLSI Design Tradeoffs } Non-Recurring Engineering (NRE) Costs } Design Costs } Mask “Tooling” costs } Unit Cost - related to chip size } Amount of logic } Current technology } Performance } Clock speed } Implementation } Power consumption } Power supply voltage } Clock speed ECE 425 Spring 2007 Lecture 1 - Course Overview 19

VLSI Design Styles } } Full Custom ASIC - Application-Specific Integrated Circuit PLD, FPGA - Programmable Logic So. C - System-on-a-Chip ECE 425 Spring 2007 Lecture 1 - Course Overview 20

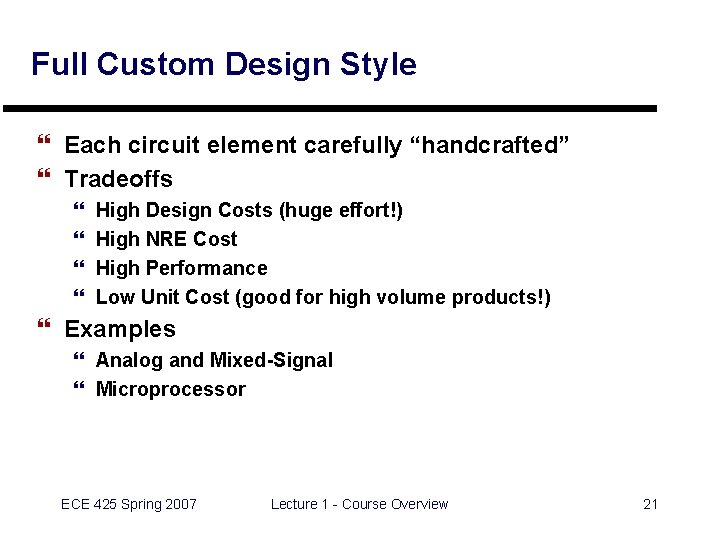

Full Custom Design Style } Each circuit element carefully “handcrafted” } Tradeoffs } } High Design Costs (huge effort!) High NRE Cost High Performance Low Unit Cost (good for high volume products!) } Examples } Analog and Mixed-Signal } Microprocessor ECE 425 Spring 2007 Lecture 1 - Course Overview 21

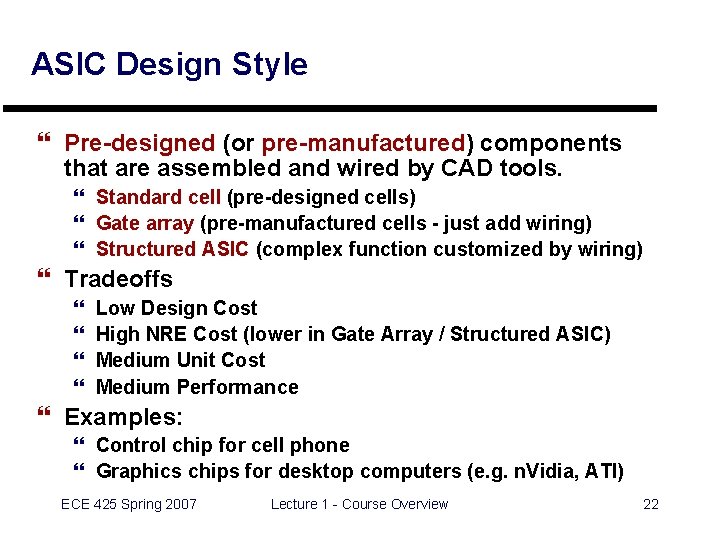

ASIC Design Style } Pre-designed (or pre-manufactured) components that are assembled and wired by CAD tools. } Standard cell (pre-designed cells) } Gate array (pre-manufactured cells - just add wiring) } Structured ASIC (complex function customized by wiring) } Tradeoffs } } Low Design Cost High NRE Cost (lower in Gate Array / Structured ASIC) Medium Unit Cost Medium Performance } Examples: } Control chip for cell phone } Graphics chips for desktop computers (e. g. n. Vidia, ATI) ECE 425 Spring 2007 Lecture 1 - Course Overview 22

Programmable Logic Design Style } Pre-manufactured components with programmable interconnect wired by CAD tools } Tradeoffs } } Low Design Cost Low NRE Cost (basically 0) Low performance High unit cost } Examples } Network routers (e. g. , Cisco) } Gibson “digital” electric guitar ECE 425 Spring 2007 Lecture 1 - Course Overview 23

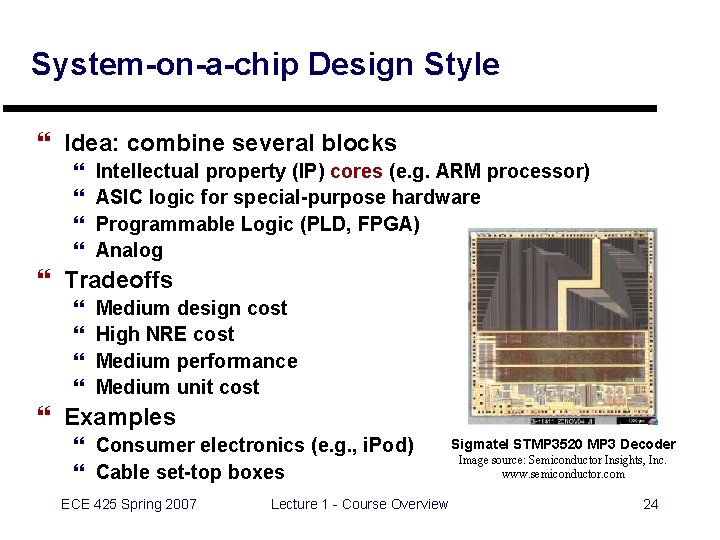

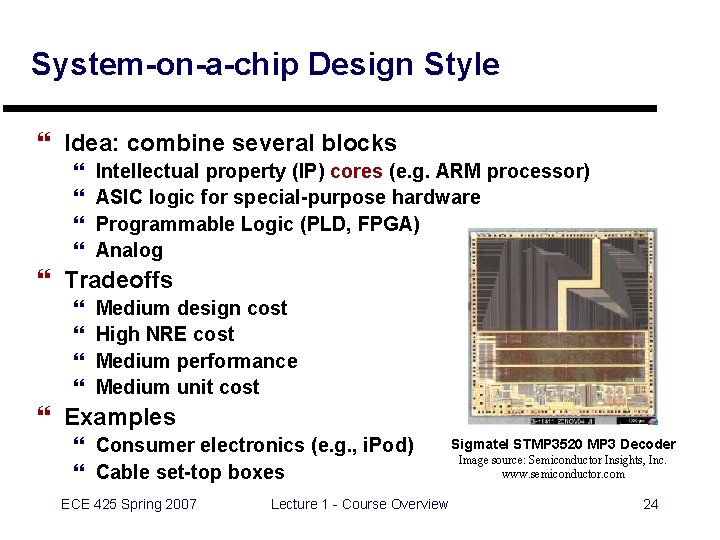

System-on-a-chip Design Style } Idea: combine several blocks } } Intellectual property (IP) cores (e. g. ARM processor) ASIC logic for special-purpose hardware Programmable Logic (PLD, FPGA) Analog } Tradeoffs } } Medium design cost High NRE cost Medium performance Medium unit cost } Examples } Consumer electronics (e. g. , i. Pod) } Cable set-top boxes ECE 425 Spring 2007 Lecture 1 - Course Overview Sigmatel STMP 3520 MP 3 Decoder Image source: Semiconductor Insights, Inc. www. semiconductor. com 24

Perspective on Design Styles } Few engineers will design custom chips } Some engineers will design ASICs & SOCs } Many engineers will design FPGA systems ECE 425 Spring 2007 Lecture 1 - Course Overview 25

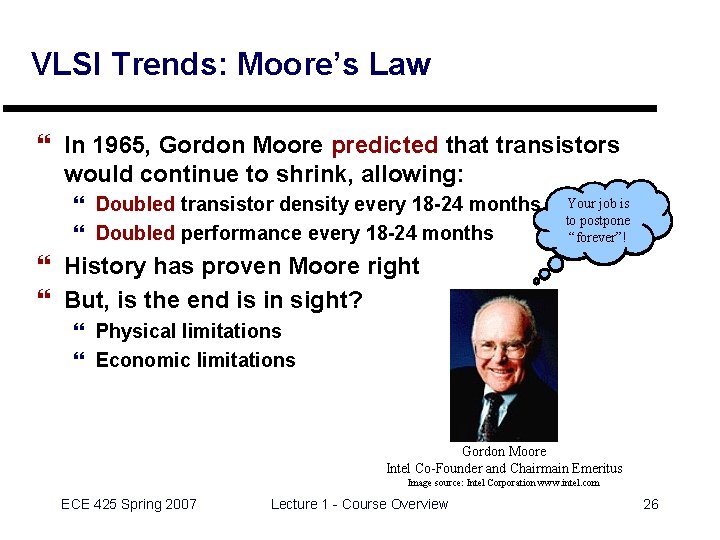

VLSI Trends: Moore’s Law } In 1965, Gordon Moore predicted that transistors would continue to shrink, allowing: } Doubled transistor density every 18 -24 months } Doubled performance every 18 -24 months job is No. Your exponential tois postpone forever, “forever”! BUT } History has proven Moore right } But, is the end is in sight? } Physical limitations } Economic limitations Gordon Moore Intel Co-Founder and Chairmain Emeritus Image source: Intel Corporation www. intel. com ECE 425 Spring 2007 Lecture 1 - Course Overview 26

Microprocessor Trends (Intel) “Deep Submicron” Source: http: //www. intel. com/pressroom/kits/quickreffam. htm, media reports ECE 425 Spring 2007 Lecture 1 - Course Overview 27

Microprocessor Trends Alpha (R. I. P) P 4 G 4 Sources: http: //www. intel. com/pressroom/kits/quickreffam. htm, www. geek. com ECE 425 Spring 2007 Lecture 1 - Course Overview 28

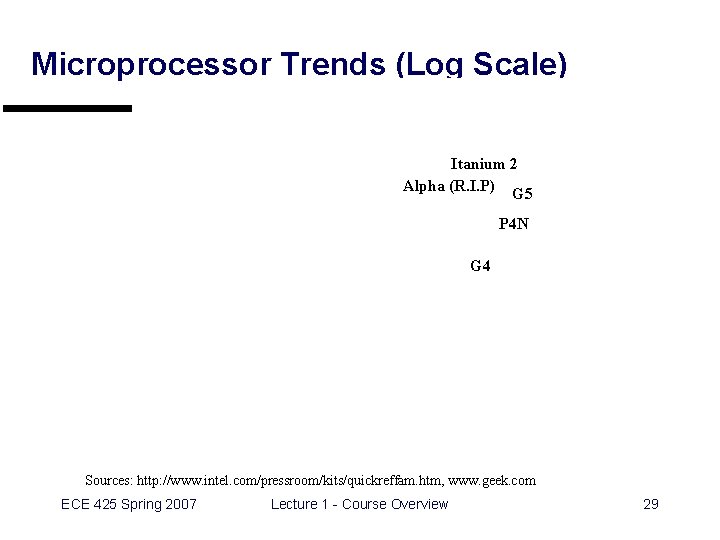

Microprocessor Trends (Log Scale) Itanium 2 Alpha (R. I. P) G 5 P 4 N G 4 Sources: http: //www. intel. com/pressroom/kits/quickreffam. htm, www. geek. com ECE 425 Spring 2007 Lecture 1 - Course Overview 29

DRAM Memory Trends (Log Scale) Source: Textbook, Industry Reports ECE 425 Spring 2007 Lecture 1 - Course Overview 30

Processor Performance Trends Vax 11/780 Source: Hennesy & Patterson Computer Architecture: A Quantitative Approach, 3 rd Ed. , Morgan-Kaufmann, 2002. ECE 425 Spring 2007 Lecture 1 - Course Overview 31

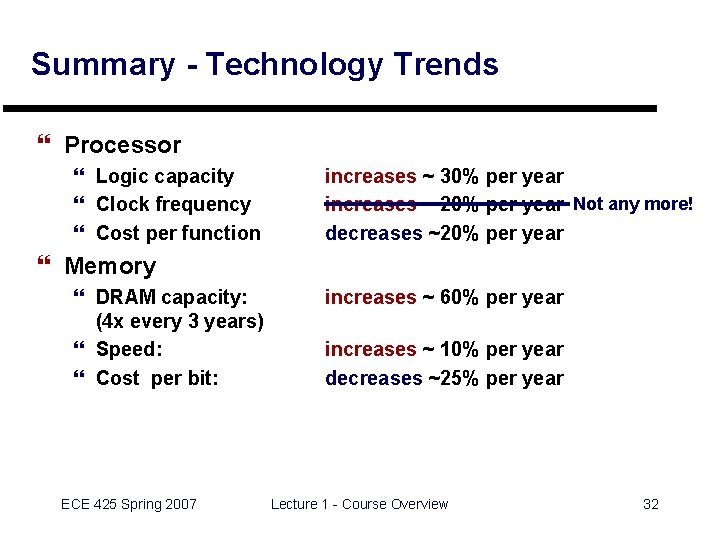

Summary - Technology Trends } Processor } Logic capacity } Clock frequency } Cost per function increases ~ 30% per year increases ~ 20% per year Not any more! decreases ~20% per year } Memory } DRAM capacity: (4 x every 3 years) } Speed: } Cost per bit: ECE 425 Spring 2007 increases ~ 60% per year increases ~ 10% per year decreases ~25% per year Lecture 1 - Course Overview 32

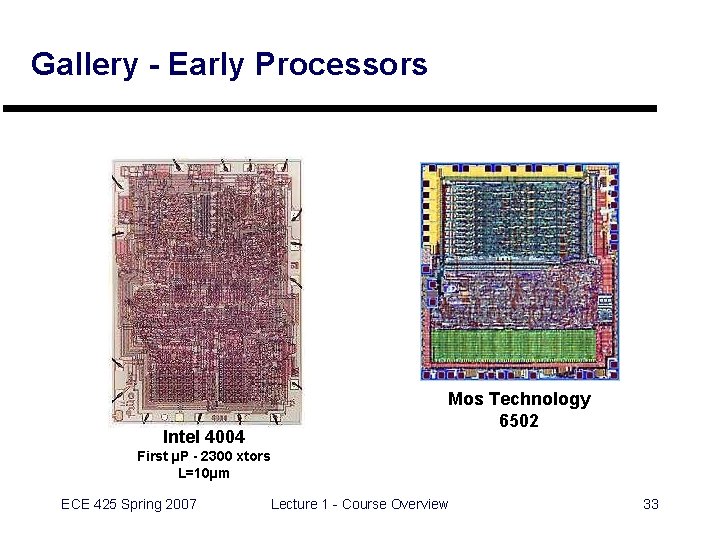

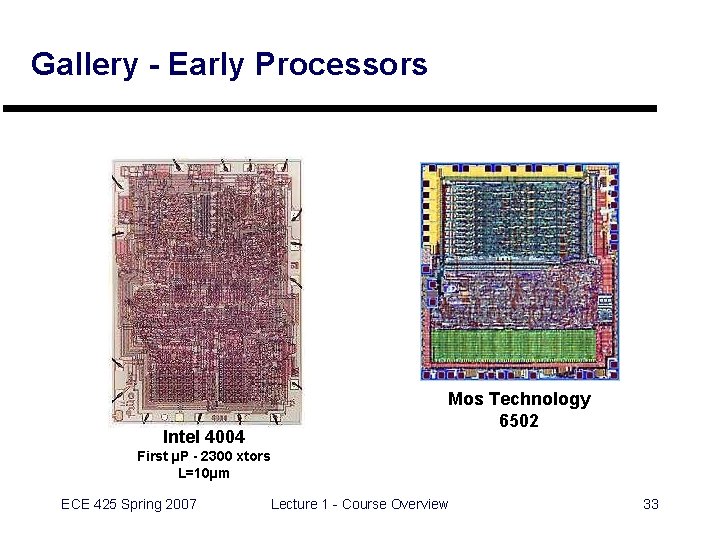

Gallery - Early Processors Intel 4004 Mos Technology 6502 First µP - 2300 xtors L=10µm ECE 425 Spring 2007 Lecture 1 - Course Overview 33

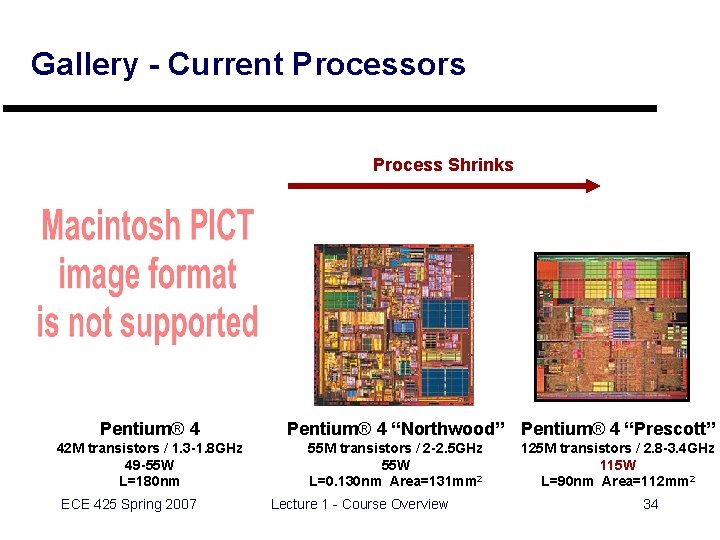

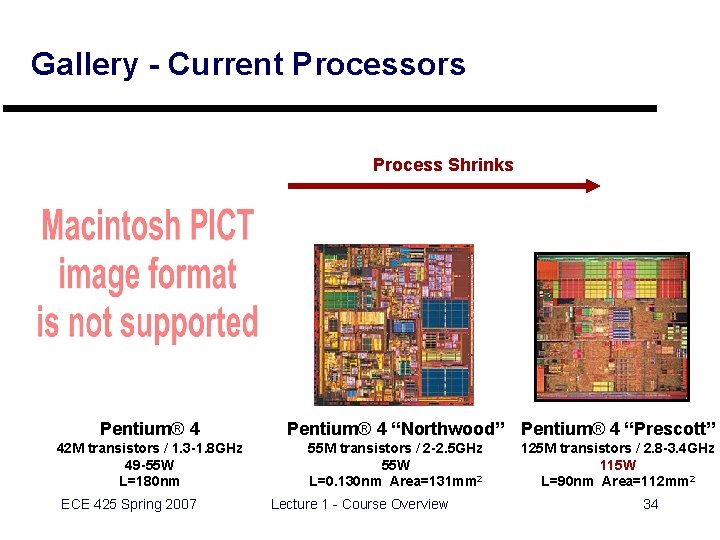

Gallery - Current Processors Process Shrinks Pentium® 4 42 M transistors / 1. 3 -1. 8 GHz 49 -55 W L=180 nm ECE 425 Spring 2007 Pentium® 4 “Northwood” Pentium® 4 “Prescott” 55 M transistors / 2 -2. 5 GHz 55 W L=0. 130 nm Area=131 mm 2 Lecture 1 - Course Overview 125 M transistors / 2. 8 -3. 4 GHz 115 W L=90 nm Area=112 mm 2 34

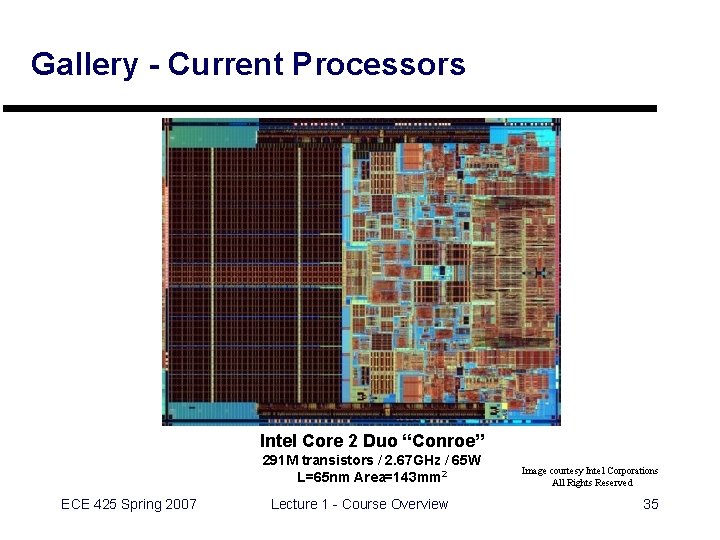

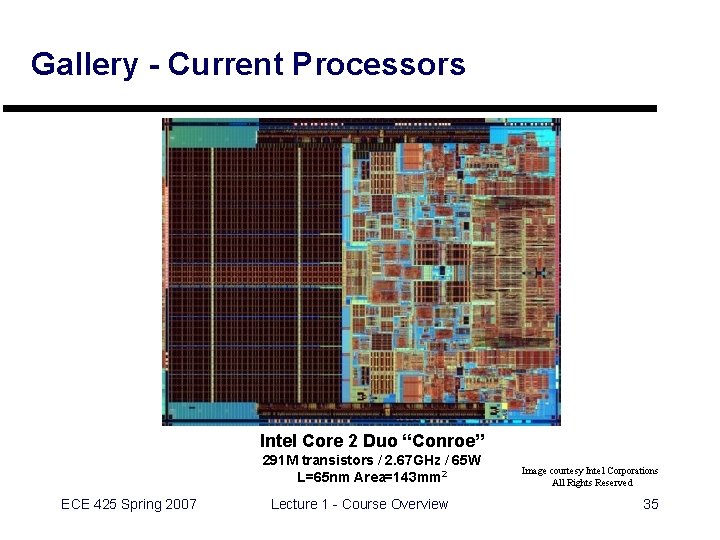

Gallery - Current Processors Intel Core 2 Duo “Conroe” 291 M transistors / 2. 67 GHz / 65 W L=65 nm Area=143 mm 2 ECE 425 Spring 2007 Lecture 1 - Course Overview Image courtesy Intel Corporations All Rights Reserved 35

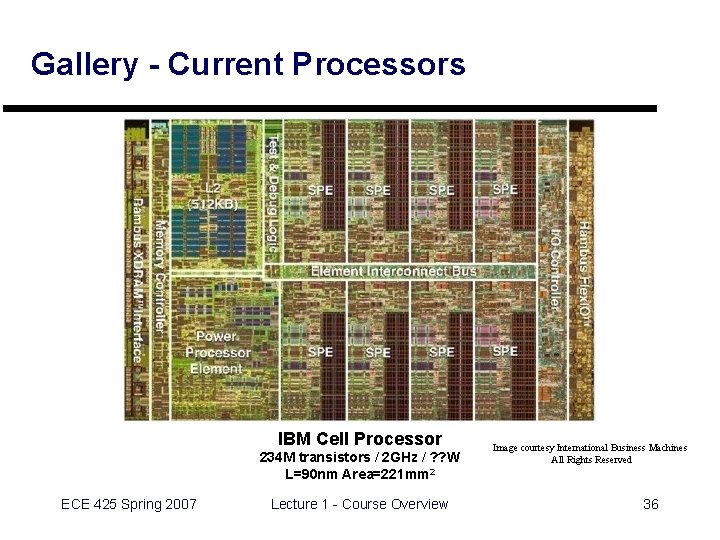

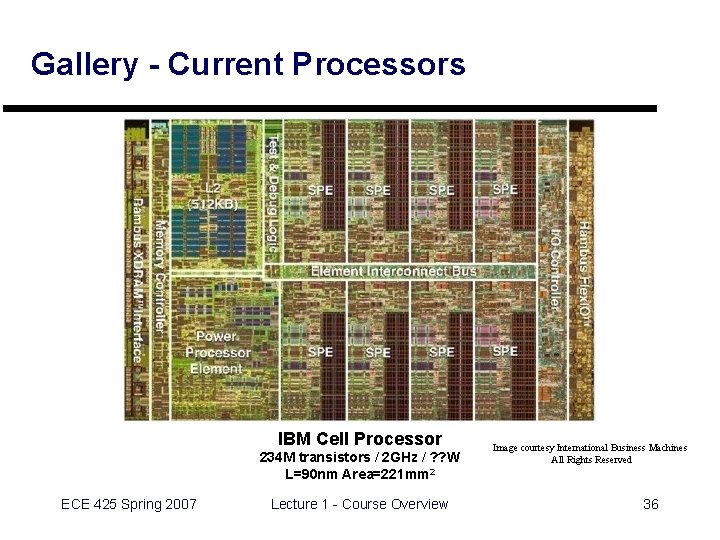

Gallery - Current Processors IBM Cell Processor 234 M transistors / 2 GHz / ? ? W L=90 nm Area=221 mm 2 ECE 425 Spring 2007 Lecture 1 - Course Overview Image courtesy International Business Machines All Rights Reserved 36

Gallery - Current FPGA Xilinx Virtex FPGA ECE 425 Spring 2007 Lecture 1 - Course Overview 37

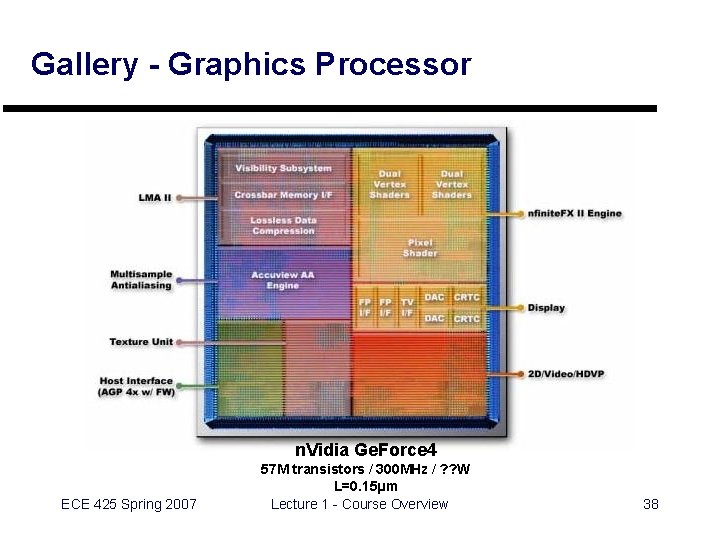

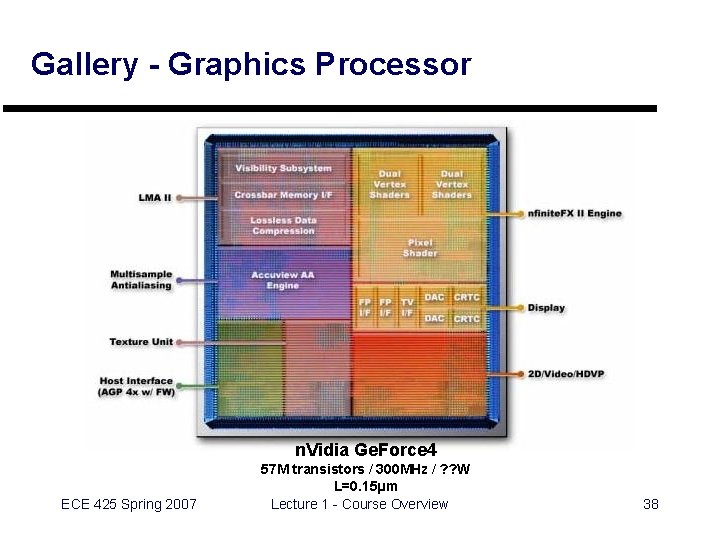

Gallery - Graphics Processor n. Vidia Ge. Force 4 ECE 425 Spring 2007 57 M transistors / 300 MHz / ? ? W L=0. 15µm Lecture 1 - Course Overview 38

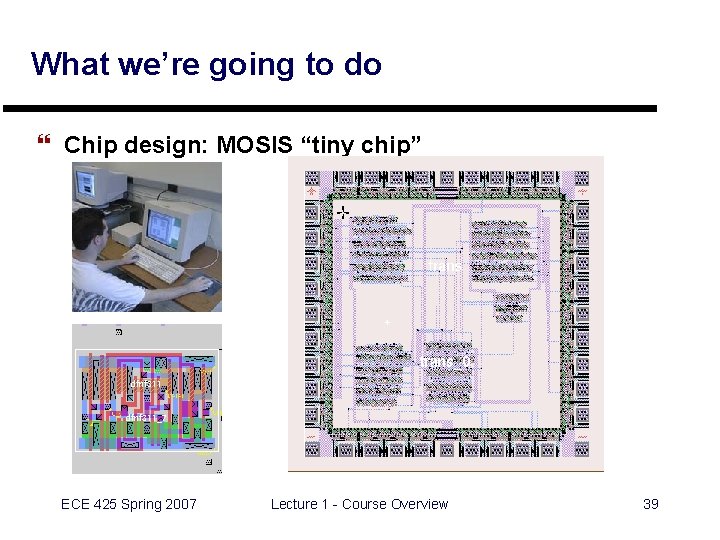

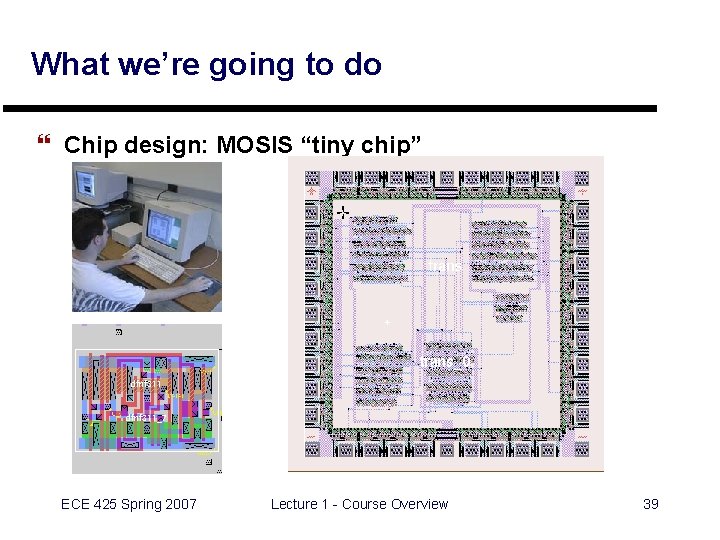

What we’re going to do } Chip design: MOSIS “tiny chip” ECE 425 Spring 2007 Lecture 1 - Course Overview 39

What we’re going to do } Fabricated MOSIS “Tiny Chip” ECE 425 Spring 2007 Lecture 1 - Course Overview 40

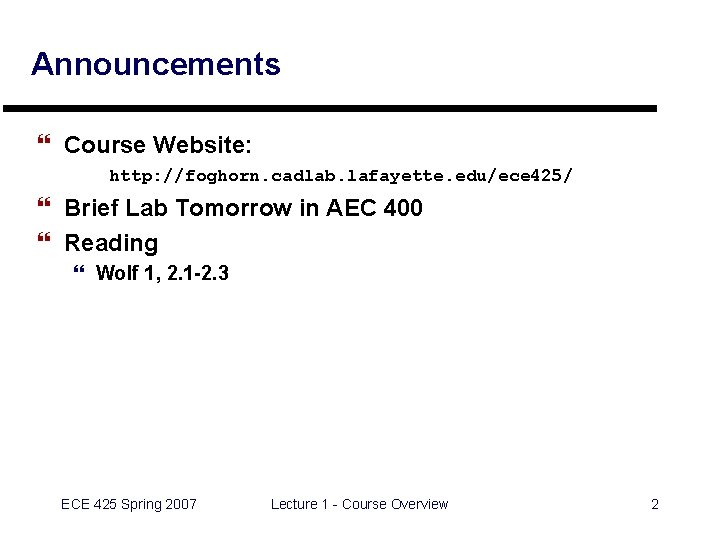

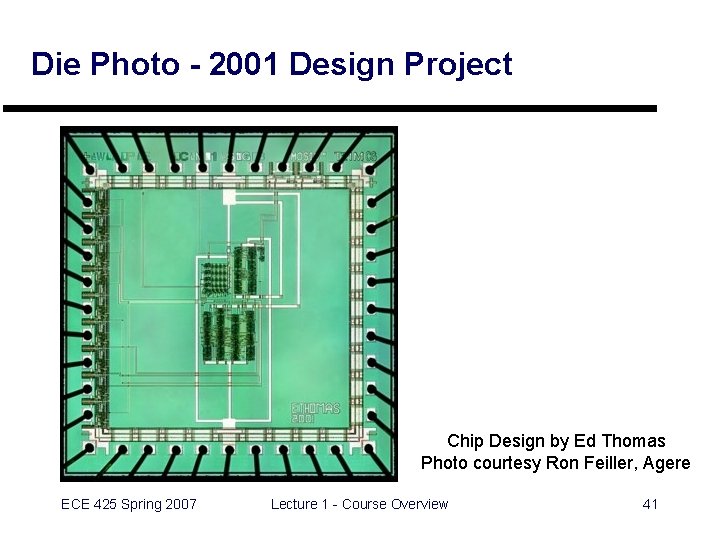

Die Photo - 2001 Design Project Chip Design by Ed Thomas Photo courtesy Ron Feiller, Agere ECE 425 Spring 2007 Lecture 1 - Course Overview 41

Coming Up: } } } Fabrication Basics: Photolithography Transistor Structure Transistor Operation CMOS Processing Steps Layout Design ECE 425 Spring 2007 Lecture 1 - Course Overview 42