ECE 425 VLSI Circuit Design Lecture 24 Subsystem

ECE 425 - VLSI Circuit Design Lecture 24 Subsystem Design (cont’d) Spring 2005 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042 nestorj@lafayette. edu ECE 425 Spring 2005 Lecture 24 - Subsystem Design 1

Announcements } Reading } Wolf: 6. 1 -6. 9 } These notes drawn in part from handouts by } J. Rabaey, Digital Integrated Circuits, © Prentice-Hall 1995. ECE 425 Spring 2005 Lecture 24 - Subsystem Design 2

Where We Are: } Last Time: } Custom Subsystem Design - Shifters, Adders } Today: } Custom Subsystem Design Continued - Multipliers } DAC Video: “Designing Mega-ASICs in Nanotechnology” ECE 425 Spring 2005 Lecture 24 - Subsystem Design 3

Subsystem Design } General Techniques. Goals } Pipelining } Datapath Design } Common Subsystems } } } Shifters Adders ALUs Multipliers Memories Structured Logic ECE 425 Spring 2005 Lecture 24 - Subsystem Design 4

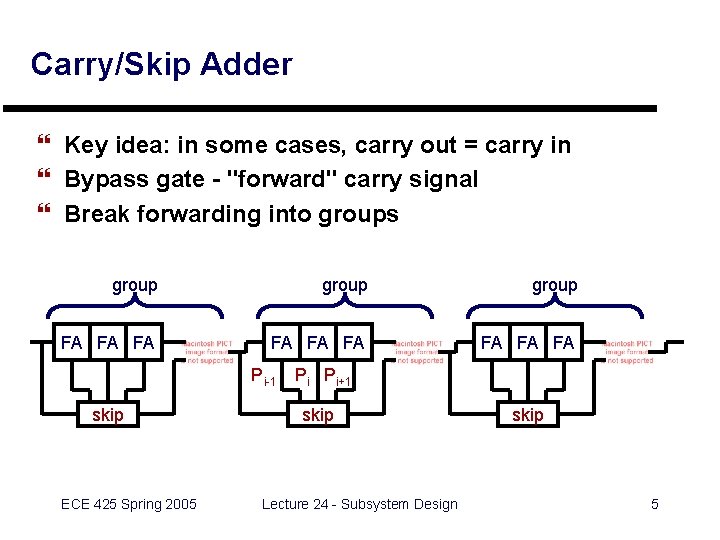

Carry/Skip Adder } Key idea: in some cases, carry out = carry in } Bypass gate - "forward" carry signal } Break forwarding into groups group FA FA FA Pi-1 skip ECE 425 Spring 2005 Pi Pi+1 skip Lecture 24 - Subsystem Design skip 5

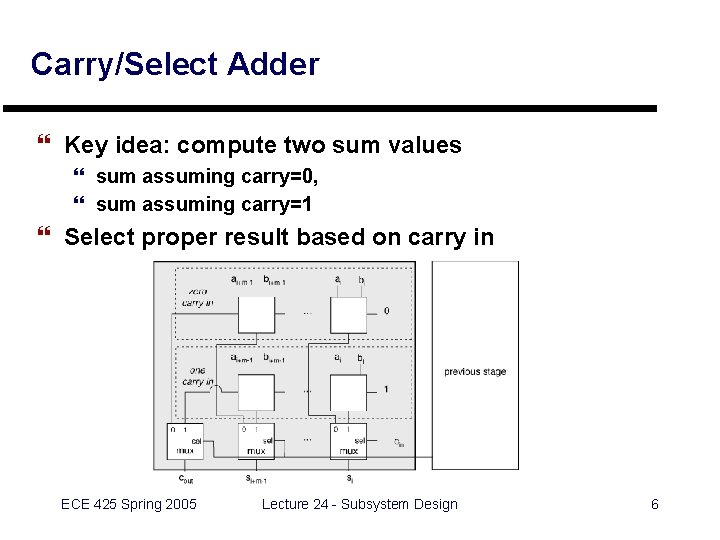

Carry/Select Adder } Key idea: compute two sum values } sum assuming carry=0, } sum assuming carry=1 } Select proper result based on carry in ECE 425 Spring 2005 Lecture 24 - Subsystem Design 6

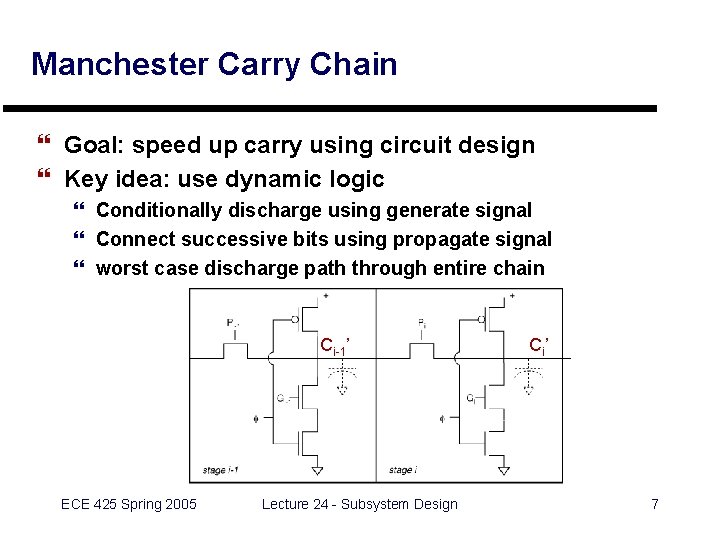

Manchester Carry Chain } Goal: speed up carry using circuit design } Key idea: use dynamic logic } Conditionally discharge using generate signal } Connect successive bits using propagate signal } worst case discharge path through entire chain Ci-1’ ECE 425 Spring 2005 Lecture 24 - Subsystem Design Ci’ 7

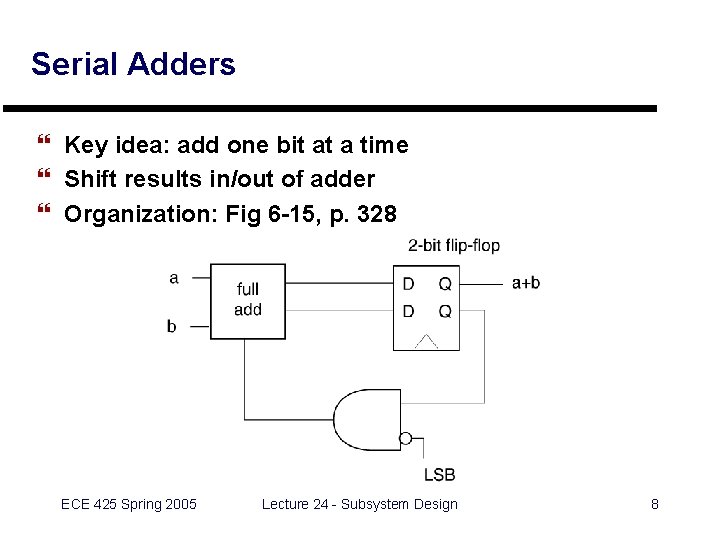

Serial Adders } Key idea: add one bit at a time } Shift results in/out of adder } Organization: Fig 6 -15, p. 328 ECE 425 Spring 2005 Lecture 24 - Subsystem Design 8

Subraction } A-B = A + (-B) } Recall two's complement arithmetic } -B = TC(B) = OC(B) + 1 } Get OC(B) with inverter } Use carry in to get +1 ECE 425 Spring 2005 Lecture 24 - Subsystem Design 9

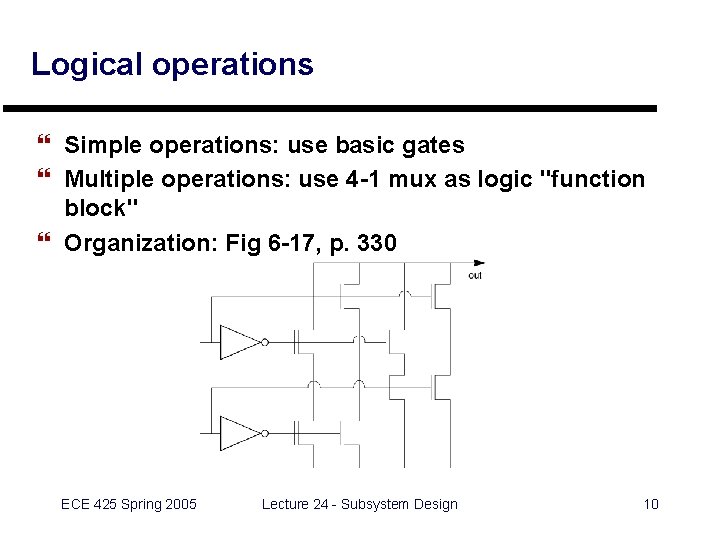

Logical operations } Simple operations: use basic gates } Multiple operations: use 4 -1 mux as logic "function block" } Organization: Fig 6 -17, p. 330 ECE 425 Spring 2005 Lecture 24 - Subsystem Design 10

Subsystem Design } General Techniques. Goals } Pipelining } Datapath Design } Common Subsystems } } } Shifters Adders ALUs Multipliers Memories Structured Logic ECE 425 Spring 2005 Lecture 24 - Subsystem Design 11

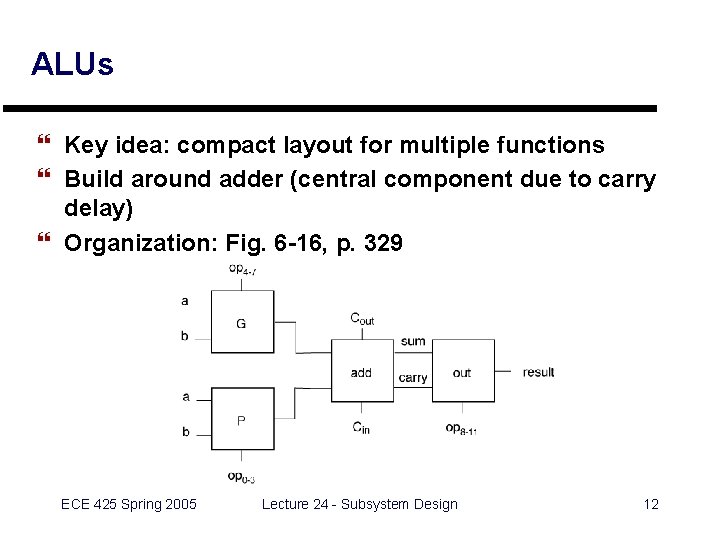

ALUs } Key idea: compact layout for multiple functions } Build around adder (central component due to carry delay) } Organization: Fig. 6 -16, p. 329 ECE 425 Spring 2005 Lecture 24 - Subsystem Design 12

Subsystem Design } General Techniques. Goals } Pipelining } Datapath Design } Common Subsystems } } } Shifters Adders ALUs Multipliers Memories Structured Logic ECE 425 Spring 2005 Lecture 24 - Subsystem Design 13

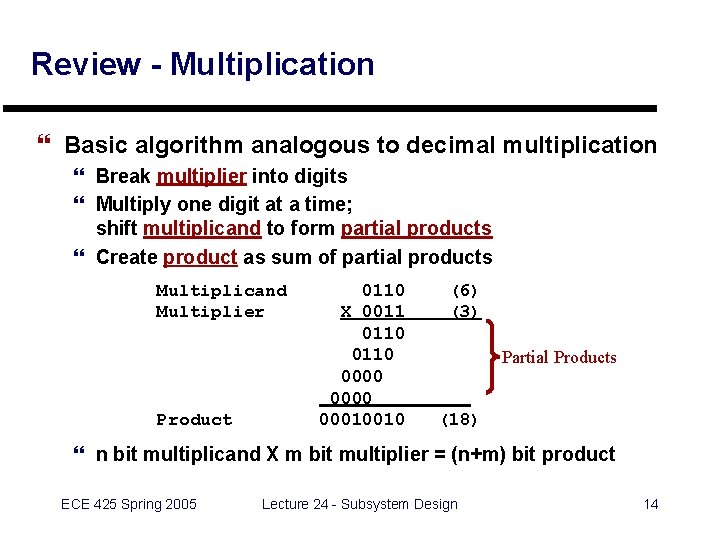

Review - Multiplication } Basic algorithm analogous to decimal multiplication } Break multiplier into digits } Multiply one digit at a time; shift multiplicand to form partial products } Create product as sum of partial products Multiplicand Multiplier Product 0110 X 0011 0110 0000 00010010 (6) (3) Partial Products (18) } n bit multiplicand X m bit multiplier = (n+m) bit product ECE 425 Spring 2005 Lecture 24 - Subsystem Design 14

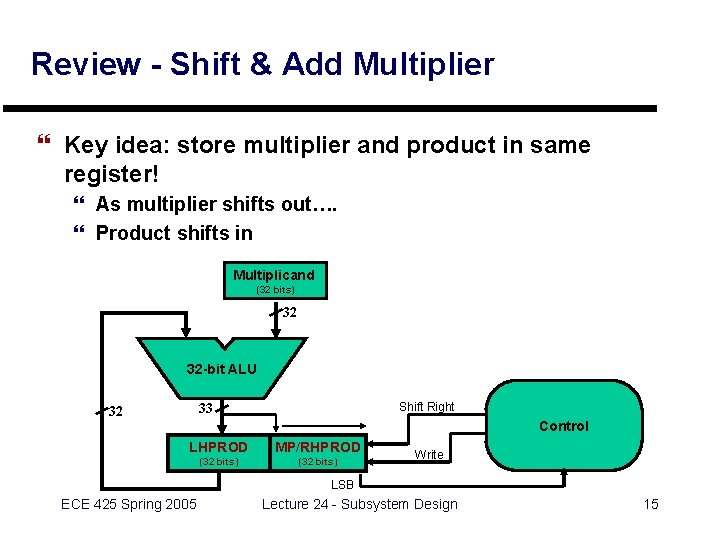

Review - Shift & Add Multiplier } Key idea: store multiplier and product in same register! } As multiplier shifts out…. } Product shifts in Multiplicand (32 bits) 32 32 -bit ALU Shift Right 33 32 Control Product LHPROD MP/RHPROD (32 bits) (64 bits) (32 bits) Write LSB ECE 425 Spring 2005 Lecture 24 - Subsystem Design 15

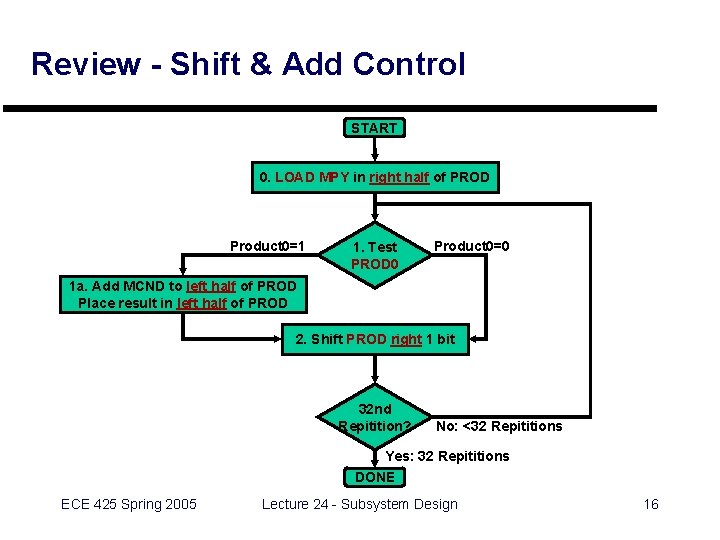

Review - Shift & Add Control START 0. LOAD MPY in right half of PROD Product 0=1 1. Test PROD 0 Product 0=0 1 a. Add MCND to left half of PROD Place result in left half of PROD 2. Shift PROD right 1 bit 32 nd Repitition? No: <32 Repititions Yes: 32 Repititions DONE ECE 425 Spring 2005 Lecture 24 - Subsystem Design 16

Review - Booth’s Algorithm } Originally proposed to reduce addition steps } Bonus: works for two’s complement numbers } Uses shifting, addition, and subtraction ECE 425 Spring 2005 Lecture 24 - Subsystem Design 17

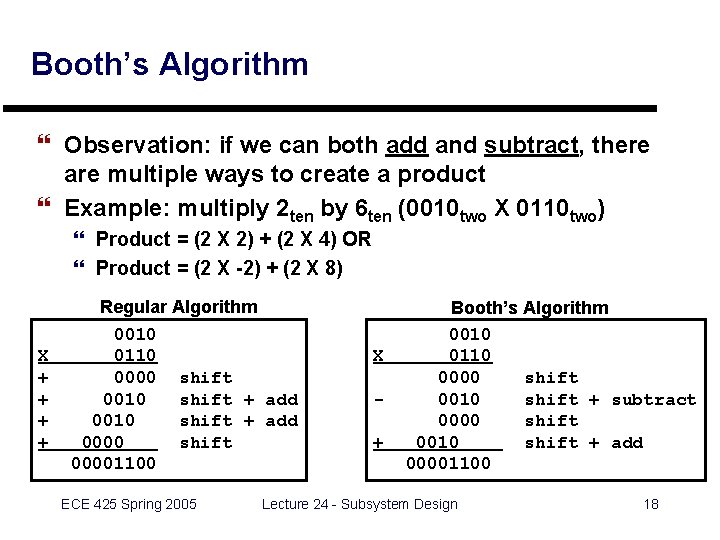

Booth’s Algorithm } Observation: if we can both add and subtract, there are multiple ways to create a product } Example: multiply 2 ten by 6 ten (0010 two X 0110 two) } Product = (2 X 2) + (2 X 4) OR } Product = (2 X -2) + (2 X 8) Regular Algorithm X + + 0010 0110 0000 0010 00001100 X shift + add shift ECE 425 Spring 2005 + Booth’s Algorithm 0010 0110 0000 shift 0010 shift + subtract 0000 shift 0010 shift + add 00001100 Lecture 24 - Subsystem Design 18

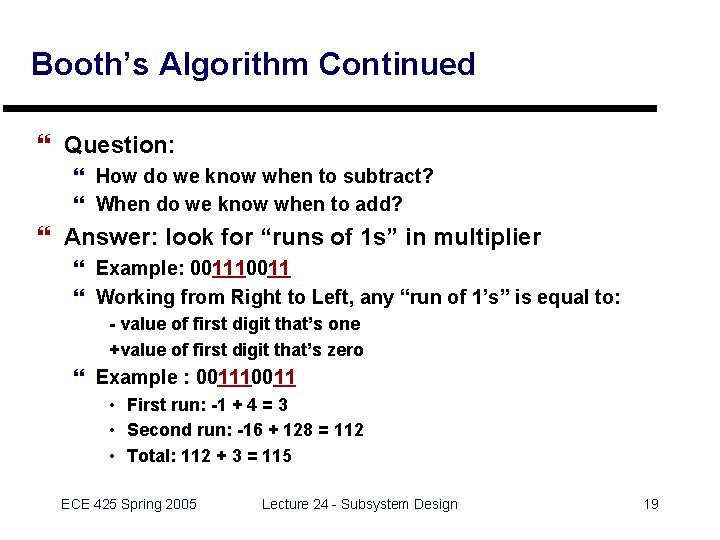

Booth’s Algorithm Continued } Question: } How do we know when to subtract? } When do we know when to add? } Answer: look for “runs of 1 s” in multiplier } Example: 001110011 } Working from Right to Left, any “run of 1’s” is equal to: - value of first digit that’s one +value of first digit that’s zero } Example : 001110011 • First run: -1 + 4 = 3 • Second run: -16 + 128 = 112 • Total: 112 + 3 = 115 ECE 425 Spring 2005 Lecture 24 - Subsystem Design 19

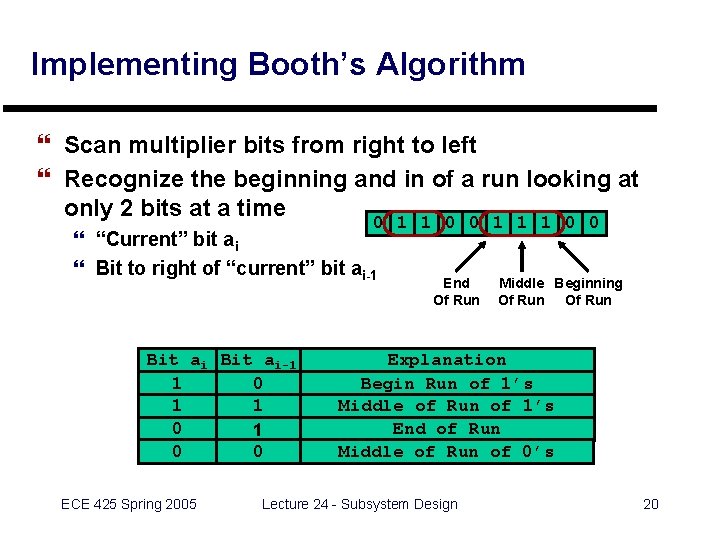

Implementing Booth’s Algorithm } Scan multiplier bits from right to left } Recognize the beginning and in of a run looking at only 2 bits at a time 0 1 1 0 0 1 1 1 0 0 } “Current” bit ai } Bit to right of “current” bit ai-1 Bit ai-1 1 0 1 0 0 ECE 425 Spring 2005 End Of Run Middle Beginning Of Run Explanation Begin Run of 1’s Middle of Run of 1’s End of Run Middle of Run of 0’s Lecture 24 - Subsystem Design 20

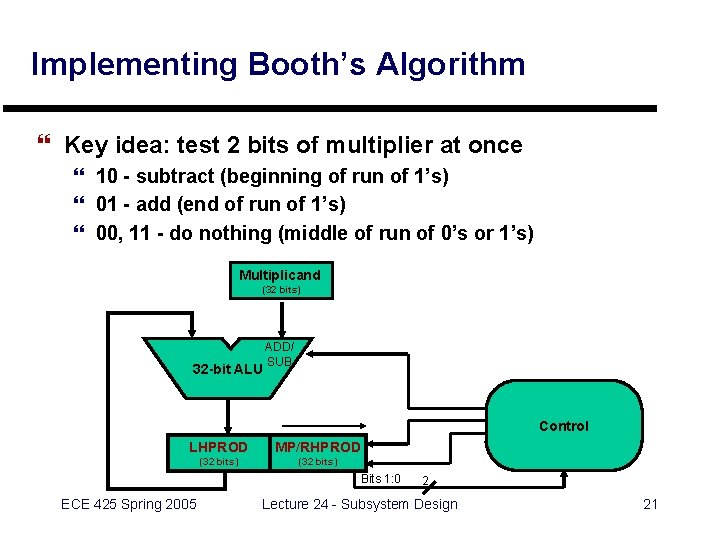

Implementing Booth’s Algorithm } Key idea: test 2 bits of multiplier at once } 10 - subtract (beginning of run of 1’s) } 01 - add (end of run of 1’s) } 00, 11 - do nothing (middle of run of 0’s or 1’s) Multiplicand (32 bits) 32 -bit ALU ADD/ SUB Control Shift Left Product LHPROD MP/RHPROD (32 bits) (64 bits) (32 bits)Write Bits 1: 0 ECE 425 Spring 2005 2 Lecture 24 - Subsystem Design 21

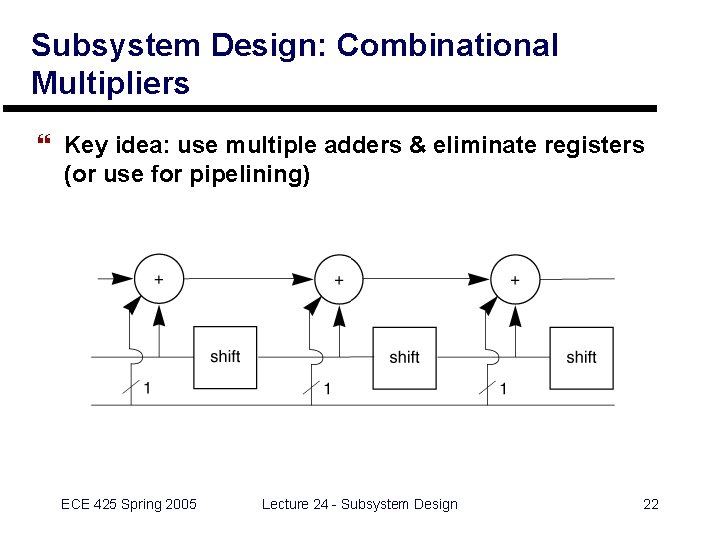

Subsystem Design: Combinational Multipliers } Key idea: use multiple adders & eliminate registers (or use for pipelining) ECE 425 Spring 2005 Lecture 24 - Subsystem Design 22

Array Multiplier X 3 ECE 425 Spring 2005 X 2 Lecture 24 - Subsystem Design X 1 X 0 Y 0 23

Array Multiplier - Critical Paths Critical Path 1 & 2 ECE 425 Spring 2005 Lecture 24 - Subsystem Design 24

Carry-Save Multiplier ECE 425 Spring 2005 Lecture 24 - Subsystem Design 25

Carry-Save Multiplier - Floorplan ECE 425 Spring 2005 Lecture 24 - Subsystem Design 26

Wallace-Tree Multiplier ECE 425 Spring 2005 Lecture 24 - Subsystem Design 27

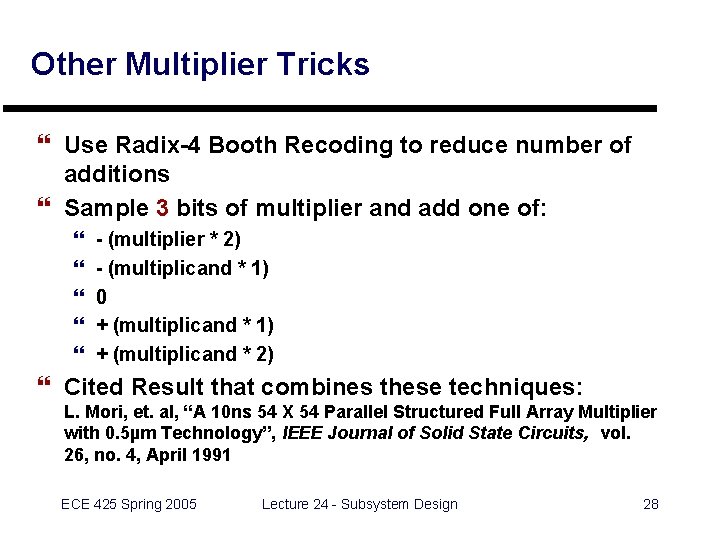

Other Multiplier Tricks } Use Radix-4 Booth Recoding to reduce number of additions } Sample 3 bits of multiplier and add one of: } } } - (multiplier * 2) - (multiplicand * 1) 0 + (multiplicand * 1) + (multiplicand * 2) } Cited Result that combines these techniques: L. Mori, et. al, “A 10 ns 54 X 54 Parallel Structured Full Array Multiplier with 0. 5µm Technology”, IEEE Journal of Solid State Circuits, vol. 26, no. 4, April 1991 ECE 425 Spring 2005 Lecture 24 - Subsystem Design 28

Subsystem Design } General Techniques. Goals } Pipelining } Datapath Design } Common Subsystems } } } Shifters Adders ALUs Multipliers Memories Structured Logic ECE 425 Spring 2005 Lecture 24 - Subsystem Design 29

- Slides: 29