ECE 425 VLSI Circuit Design Lecture 9 Combinational

ECE 425 - VLSI Circuit Design Lecture 9 Combinational Logic Design Other Logic Families Spring 2007 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042 nestorj@lafayette. edu ECE 425 Spring 2007 Lecture 9 - Comb. Logic 1

Announcements } Homework Due Mon. Mar. 5 } 3 -1, 3 -4, 3 -6, 3 -7, 3 -14, 3 -16 } Reading } 3. 1 -3. 7 } Exam 1: Scheduled for Wed. March 7 ECE 425 Spring 2007 Lecture 9 - Comb. Logic 2

Where we are. . . } Last Time: } Combinational Logic - Static CMOS (cont’d) • Transistor Sizing • Power Dissipation } Today: } Combinational Logic - Static CMOS (cont’d) • Power-Speed Product • Parasitics and Performance • Other CMOS Logic Families ECE 425 Spring 2007 Lecture 9 - Comb. Logic 3

Switch Logic } Key idea: use transistors as switches } Concern: switches are bidirectional AND OR ECE 425 Spring 2007 Lecture 9 - Comb. Logic 4

Switch Logic - Pass Transistors } Use n-transistor as “switches” } “Threshold problem” } Transistor switches off when Vgs < Vt } VDD input -> VDD-Vt output IN: VDD } Special gate needed to “restore” values ECE 425 Spring 2007 Lecture 9 - Comb. Logic OUT: VDD-Vtn A: VDD 5

Switch Logic - Transmission Gates } } Complementary transistors - n and p No threshold problem Cost: extra transistor, extra control input Not a perfect conductor! A’ A’ A A ECE 425 Spring 2007 Lecture 9 - Comb. Logic 6

Switch Logic Example - 2 -1 MUX IN ECE 425 Spring 2007 Lecture 9 - Comb. Logic 7

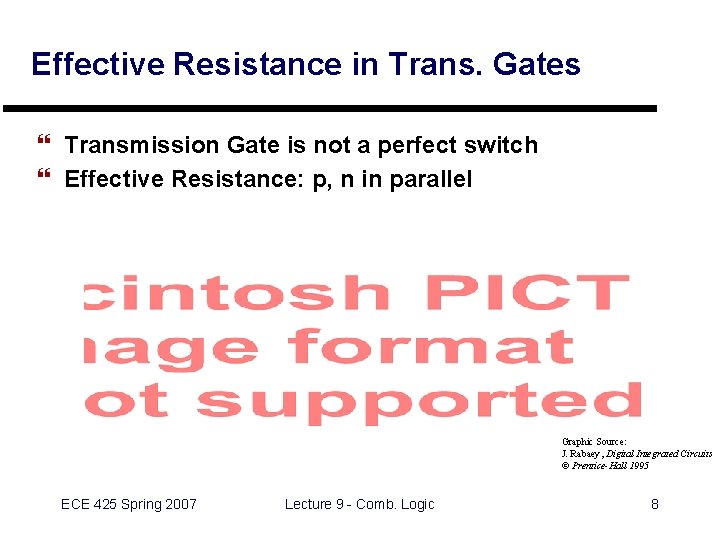

Effective Resistance in Trans. Gates } Transmission Gate is not a perfect switch } Effective Resistance: p, n in parallel Graphic Source: J. Rabaey, Digital Integrated Circuits © Prentice-Hall 1995 ECE 425 Spring 2007 Lecture 9 - Comb. Logic 8

Approximating Req in Trans. Gates } Approximation from Rabaey’s Book: } Assume both transistors in linear mode } Let VA = voltage on input node } Let VB = voltage on output node ECE 425 Spring 2007 Lecture 9 - Comb. Logic 9

Charge Sharing } Consider transmission gates in series } Each node has parasitic capacitances } Problems occur when inputs change to redistribute charge } Solution: design network so there is always a path from VDD or Gnd to output ECE 425 Spring 2007 Lecture 9 - Comb. Logic 10

Aside: Transmission Gates in Analog } Transmission Gates work with analog values, too! } Example: Voltage-Scaling D/A Converter ECE 425 Spring 2007 Lecture 9 - Comb. Logic 11

Aside - Discuss Labs 5 -7 } Digital-Analog Conversion - Common Approaches } Current-Scaling • Binary-Scaled • R 2 R network } Voltage-Scaling • Resistor-String • Folded Resistor String } Charge-Scaling } Oversampling Converters ECE 425 Spring 2007 Lecture 9 - Comb. Logic 12

Review: R-2 R D/A } You built one of these in Circuits lab ECE 425 Spring 2007 Lecture 9 - Comb. Logic 13

D/A Conversion - Voltage Scaling ECE 425 Spring 2007 Lecture 9 - Comb. Logic 14

Labs 5 -7 - Voltage-Scaling D/A Converter ECE 425 Spring 2007 Lecture 9 - Comb. Logic 15

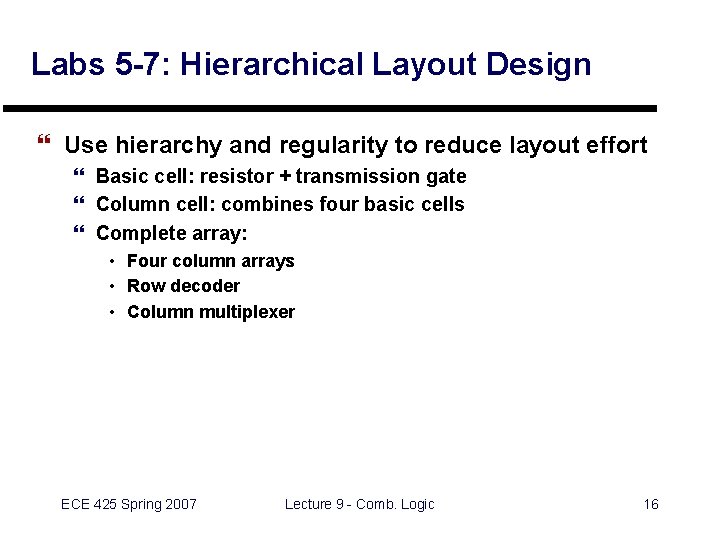

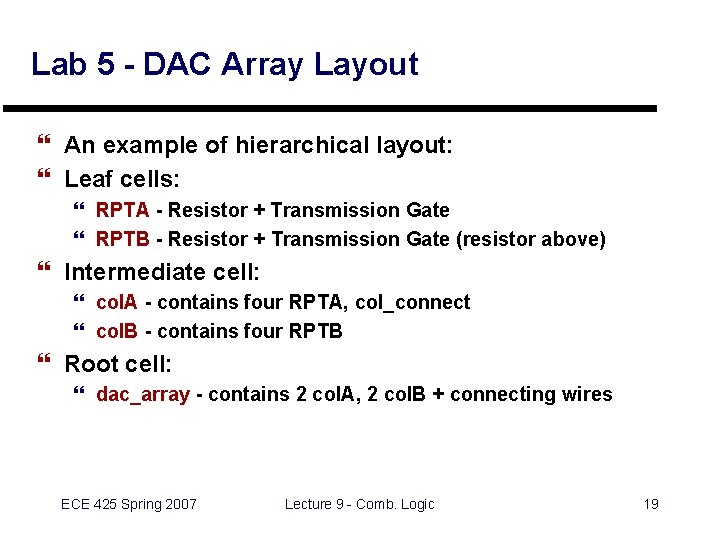

Labs 5 -7: Hierarchical Layout Design } Use hierarchy and regularity to reduce layout effort } Basic cell: resistor + transmission gate } Column cell: combines four basic cells } Complete array: • Four column arrays • Row decoder • Column multiplexer ECE 425 Spring 2007 Lecture 9 - Comb. Logic 16

Hierarchical Stick Diagram - D/A ECE 425 Spring 2007 Lecture 9 - Comb. Logic 17

Lab 5 - DAC Array Layout Even Columns Odd Columns ECE 425 Spring 2007 Lecture 9 - Comb. Logic 18

Lab 5 - DAC Array Layout } An example of hierarchical layout: } Leaf cells: } RPTA - Resistor + Transmission Gate } RPTB - Resistor + Transmission Gate (resistor above) } Intermediate cell: } col. A - contains four RPTA, col_connect } col. B - contains four RPTB } Root cell: } dac_array - contains 2 col. A, 2 col. B + connecting wires ECE 425 Spring 2007 Lecture 9 - Comb. Logic 19

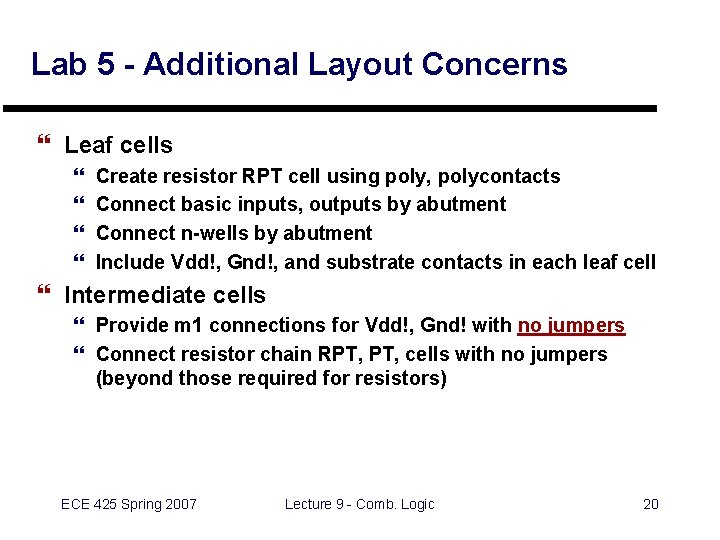

Lab 5 - Additional Layout Concerns } Leaf cells } } Create resistor RPT cell using poly, polycontacts Connect basic inputs, outputs by abutment Connect n-wells by abutment Include Vdd!, Gnd!, and substrate contacts in each leaf cell } Intermediate cells } Provide m 1 connections for Vdd!, Gnd! with no jumpers } Connect resistor chain RPT, cells with no jumpers (beyond those required for resistors) ECE 425 Spring 2007 Lecture 9 - Comb. Logic 20

Lab 6 - Completing the DAC Layout } Design Row Decoder & Add to Hierarchy } Leaf cells: NAND gates, inverters, XOR gates } Match outputs to row select lines } Design Column Multiplexer } Use row decoder + transmission gates (modify if necessary) } Match inputs to column output lines } Final result: } 4 digital inputs d 3, d 2, d 1, d 0 } 1 analog output: OUT ECE 425 Spring 2007 Lecture 9 - Comb. Logic 21

Lab 7 - Verifying the DAC } Modify RPT cell to “mark” resistor for extraction : paint rpoly } Extract circuit & make Spice deck : extract all : ext 2 spice DAC } Simulate using PSPICE and verify output for all 16 input values (0000 - 1111) ECE 425 Spring 2007 Lecture 9 - Comb. Logic 22

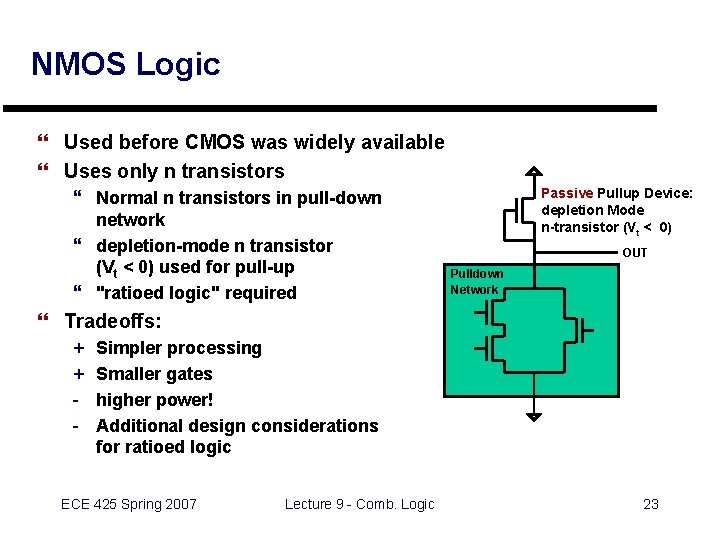

NMOS Logic } Used before CMOS was widely available } Uses only n transistors } Normal n transistors in pull-down network } depletion-mode n transistor (Vt < 0) used for pull-up } "ratioed logic" required Passive Pullup Device: depletion Mode n-transistor (Vt < 0) OUT Pulldown Network } Tradeoffs: + + - Simpler processing Smaller gates higher power! Additional design considerations for ratioed logic ECE 425 Spring 2007 Lecture 9 - Comb. Logic 23

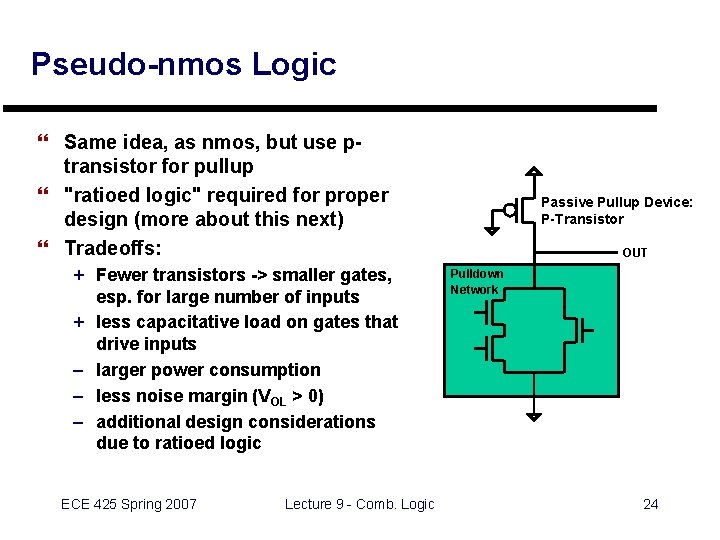

Pseudo-nmos Logic } Same idea, as nmos, but use ptransistor for pullup } "ratioed logic" required for proper design (more about this next) } Tradeoffs: + Fewer transistors -> smaller gates, esp. for large number of inputs + less capacitative load on gates that drive inputs – larger power consumption – less noise margin (VOL > 0) – additional design considerations due to ratioed logic ECE 425 Spring 2007 Lecture 9 - Comb. Logic Passive Pullup Device: P-Transistor OUT Pulldown Network 24

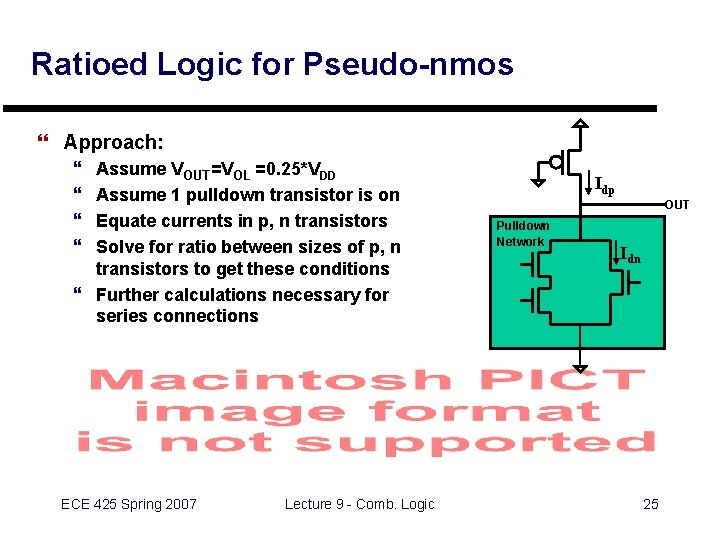

Ratioed Logic for Pseudo-nmos } Approach: } } Assume VOUT=VOL =0. 25*VDD Assume 1 pulldown transistor is on Equate currents in p, n transistors Solve for ratio between sizes of p, n transistors to get these conditions } Further calculations necessary for series connections ECE 425 Spring 2007 Lecture 9 - Comb. Logic Idp OUT Pulldown Network Idn 25

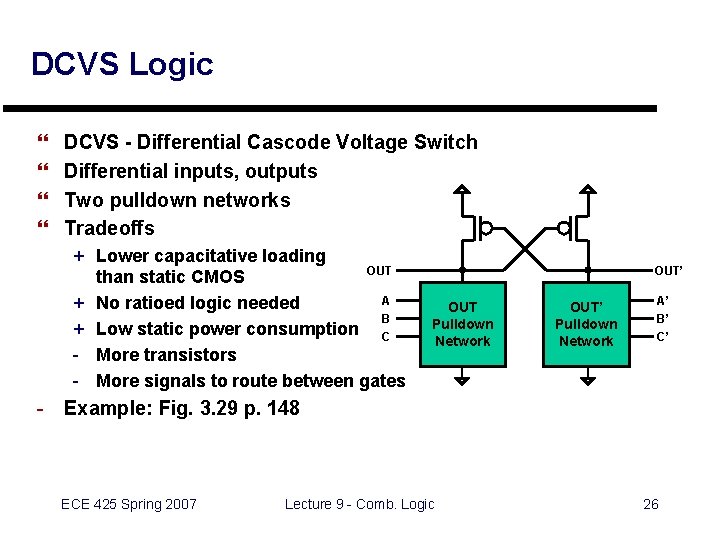

DCVS Logic } } DCVS - Differential Cascode Voltage Switch Differential inputs, outputs Two pulldown networks Tradeoffs + Lower capacitative loading OUT than static CMOS A + No ratioed logic needed B + Low static power consumption C - More transistors - More signals to route between gates OUT’ OUT Pulldown Network OUT’ Pulldown Network A’ B’ C’ - Example: Fig. 3. 29 p. 148 ECE 425 Spring 2007 Lecture 9 - Comb. Logic 26

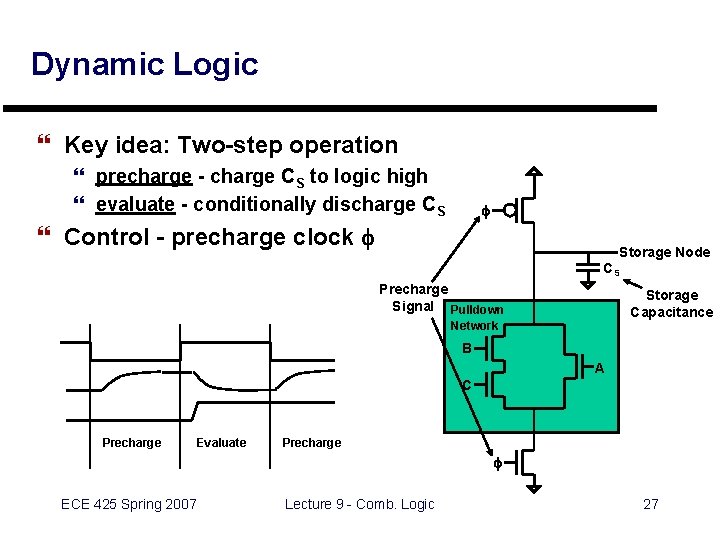

Dynamic Logic } Key idea: Two-step operation } precharge - charge CS to logic high } evaluate - conditionally discharge CS f } Control - precharge clock f Storage Node CS Precharge Signal Pulldown Storage Capacitance Network B A C Precharge Evaluate Precharge f ECE 425 Spring 2007 Lecture 9 - Comb. Logic 27

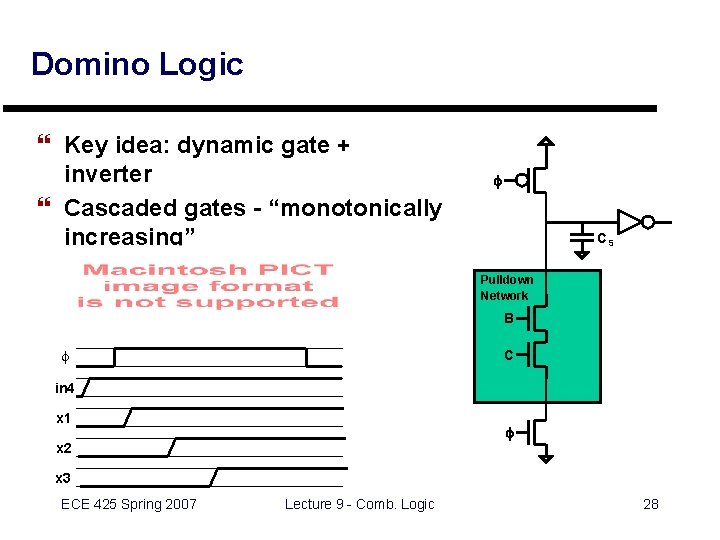

Domino Logic } Key idea: dynamic gate + inverter } Cascaded gates - “monotonically increasing” f CS Pulldown Network B C f in 4 x 1 f x 2 x 3 ECE 425 Spring 2007 Lecture 9 - Comb. Logic 28

Domino Logic Tradeoffs + + - Fewer transistors -> smaller gates Lower power consumption than pseudo-nmos Clocking required Charge sharing can be an issue (see Fig. 3. 34) Logic not complete (AND, OR, but no NOT) ECE 425 Spring 2007 Lecture 9 - Comb. Logic 29

Coming Up: } Low-Power Gates } Wire Delays, Buffering, and Sizing } Combinational Logic Networks ECE 425 Spring 2007 Lecture 9 - Comb. Logic 30

- Slides: 30