ECE 425 VLSI Circuit Design Lecture 10 Combinational

ECE 425 - VLSI Circuit Design Lecture 10 - Combinational Logic (cont’d) Low Power Logic; RC Network Delays Spring 2007 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042 nestorj@lafayette. edu ECE 425 Spring 2007 Lecture 10 - Comb. Logic 1

Announcements } Homework Due Mon. Mar. 5 } 3 -1, 3 -4, 3 -6, 3 -7, 3 -14, 3 -16 } Reading } 3. 1 -3. 7 } Exam 1: Scheduled for Wed. March 7 ECE 425 Spring 2007 Lecture 10 - Comb. Logic 2

Where we are } Last Time } } Power Consumption Parasitics and Performance Driving Large Loads Alternative Logic Families } Today } Body Effect } Techniques for Reducing Power Consumption } Delay in long wires ECE 425 Spring 2007 Lecture 10 - Comb. Logic 3

Body Effect } We’ve used fixed values for Vtp, Vtn, BUT } This is true only if source/substrate voltage Vsb=0 } Not always the case when transistors are in series } Increasing Vsb } increases width of depletion layer } raises the threshold voltage Vt } Example (p. 56): if Vsb=5 V, ∆Vt=0. 16 V (24% of Vt) ECE 425 Spring 2007 Lecture 10 - Comb. Logic 4

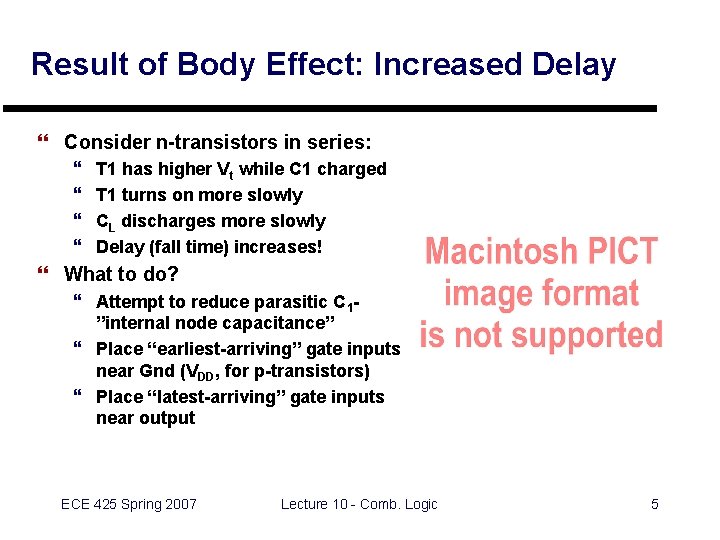

Result of Body Effect: Increased Delay } Consider n-transistors in series: } } T 1 has higher Vt while C 1 charged T 1 turns on more slowly CL discharges more slowly Delay (fall time) increases! } What to do? } Attempt to reduce parasitic C 1”internal node capacitance” } Place “earliest-arriving” gate inputs near Gnd (VDD, for p-transistors) } Place “latest-arriving” gate inputs near output ECE 425 Spring 2007 Lecture 10 - Comb. Logic 5

More Techniques for Saving Power } Reduce VDD } Reducing VDD increases delay! } Common tradeoff: add extra logic e. g. parallel adders (architecture-driven voltage scaling) } Multiple Power Supplies (level translation an issue) } High VDD for “fast” logic } Low VDD for “slow” logic } “Level converters” needed between blocks ECE 425 Spring 2007 Lecture 10 - Comb. Logic 6

More Techniques for Saving Power } DCSL - Differential Current Switch Logic ECE 425 Spring 2007 Lecture 10 - Comb. Logic 7

More Techniques for Saving Power } DCSL Key Ideas } Similar to DCVS, but with extra transistors T 9, T 11 } Cross-coupled inverters act as a sense amp } T 9, T 11 disconnect pull down networks } DCSL Operation } } } CLK low - OUT, OUT’ precharged CLK high, some inputs high - T 9, T 10, T 11 on One output drops faster than the other Cross-coupled inverters reinforce change Either T 9 or T 11 cuts off, disconnecting PDN of “high” output Dinesh Somasekhar & Kaushik Roy, "Differential Current Switch Logic: A Low Power DCVS Logic Family", European Conference on Solid State Circuits, September 1995 ECE 425 Spring 2007 Lecture 10 - Comb. Logic 8

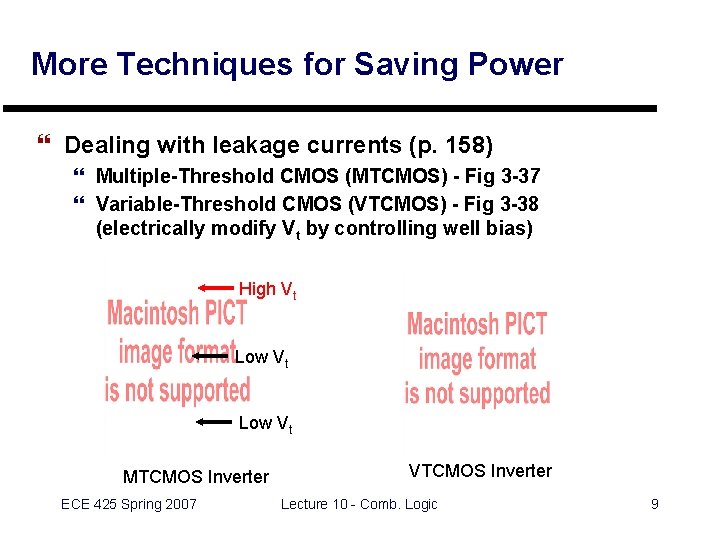

More Techniques for Saving Power } Dealing with leakage currents (p. 158) } Multiple-Threshold CMOS (MTCMOS) - Fig 3 -37 } Variable-Threshold CMOS (VTCMOS) - Fig 3 -38 (electrically modify Vt by controlling well bias) High Vt Low Vt MTCMOS Inverter ECE 425 Spring 2007 VTCMOS Inverter Lecture 10 - Comb. Logic 9

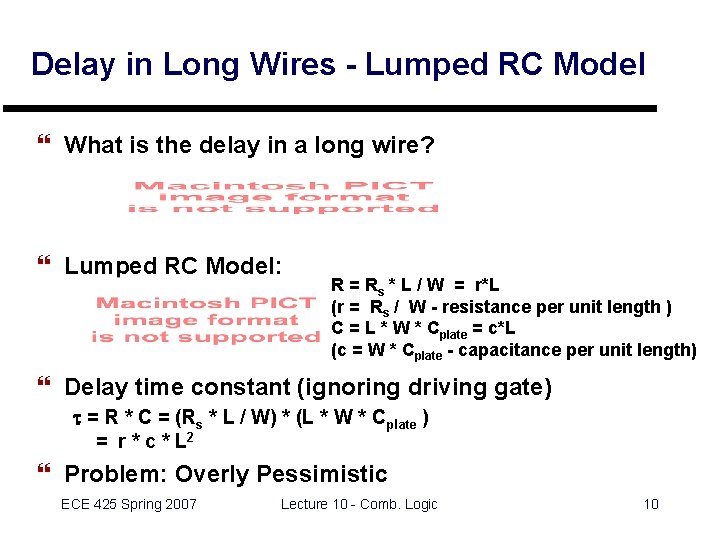

Delay in Long Wires - Lumped RC Model } What is the delay in a long wire? } Lumped RC Model: R = Rs * L / W = r*L (r = Rs / W - resistance per unit length ) C = L * W * Cplate = c*L (c = W * Cplate - capacitance per unit length) } Delay time constant (ignoring driving gate) t = R * C = (Rs * L / W) * (L * W * Cplate ) = r * c * L 2 } Problem: Overly Pessimistic ECE 425 Spring 2007 Lecture 10 - Comb. Logic 10

Delay in Long Wires Distributed RC Model } Alternative: Break wire into small segments } Approx. Solution - 1 st moment of impulse response } Important: delay still grows as square of length ECE 425 Spring 2007 Lecture 10 - Comb. Logic 11

Delay in Long Wires Consequences in design } Distributed RC model: } Delay grows as square of L! } Choose wire material that minimizes r, c } Break wire into buffered segments to optimize delay ECE 425 Spring 2007 Lecture 10 - Comb. Logic 12

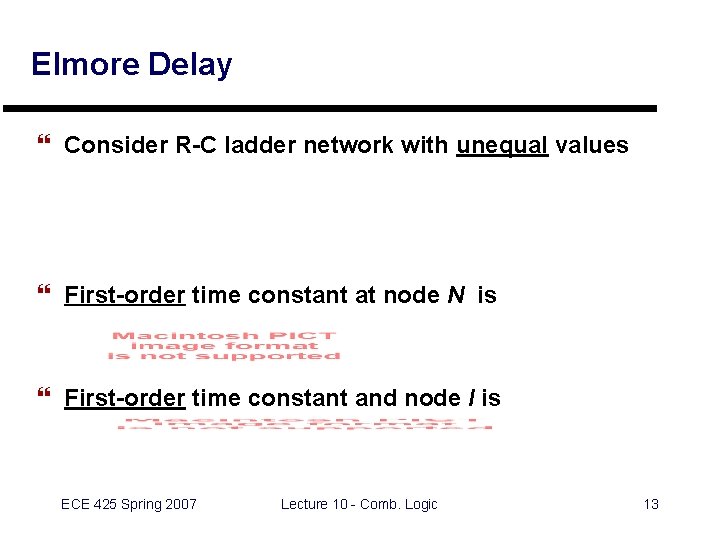

Elmore Delay } Consider R-C ladder network with unequal values } First-order time constant at node N is } First-order time constant and node I is ECE 425 Spring 2007 Lecture 10 - Comb. Logic 13

Elmore Delay Applications } Wire sizing to minimize delay } Delay prediction of complex networks (as long as they take the form of a ladder) ECE 425 Spring 2007 Lecture 10 - Comb. Logic 14

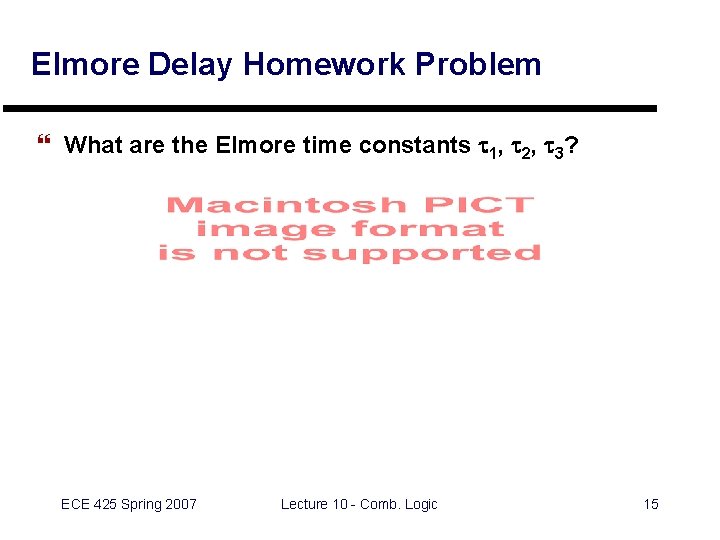

Elmore Delay Homework Problem } What are the Elmore time constants t 1, t 2, t 3? ECE 425 Spring 2007 Lecture 10 - Comb. Logic 15

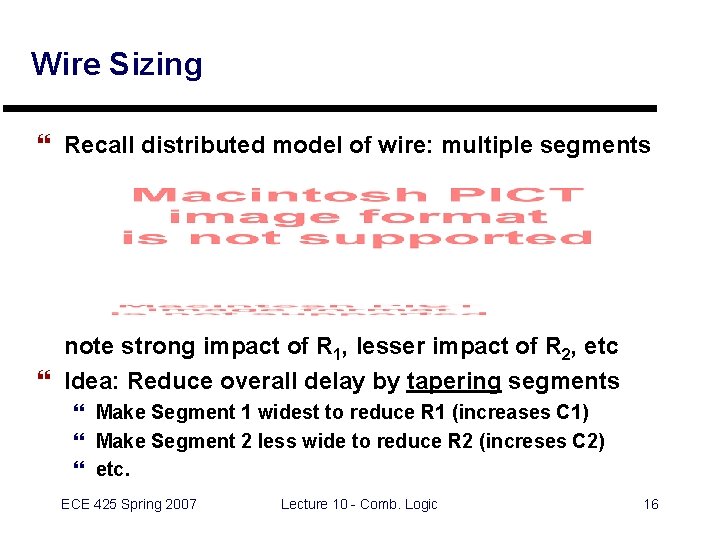

Wire Sizing } Recall distributed model of wire: multiple segments note strong impact of R 1, lesser impact of R 2, etc } Idea: Reduce overall delay by tapering segments } Make Segment 1 widest to reduce R 1 (increases C 1) } Make Segment 2 less wide to reduce R 2 (increses C 2) } etc. ECE 425 Spring 2007 Lecture 10 - Comb. Logic 16

Wire Sizing } Ideal Result wire should taper exponentially - see Eq. 3 -29, p. 163 [Fis 95]: } More pragmatic approach: step-tapered wire [Fis 95] J. Fishburn and C. Schevon, “Shaping a distributed-RC line to minimize Elmore delay”, IEEE Trans. on Circuits and Systems-I, December 1995, pp. 1020 -1022 ECE 425 Spring 2007 Lecture 10 - Comb. Logic 17

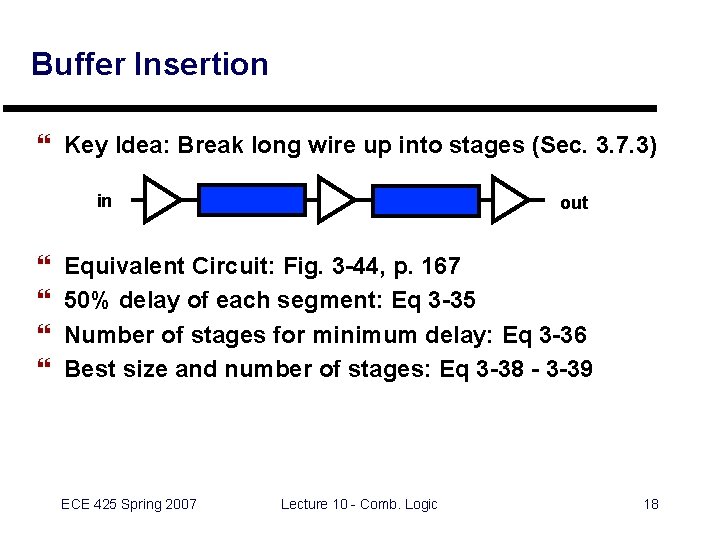

Buffer Insertion } Key Idea: Break long wire up into stages (Sec. 3. 7. 3) in } } out Equivalent Circuit: Fig. 3 -44, p. 167 50% delay of each segment: Eq 3 -35 Number of stages for minimum delay: Eq 3 -36 Best size and number of stages: Eq 3 -38 - 3 -39 ECE 425 Spring 2007 Lecture 10 - Comb. Logic 18

![Wire Sizing - New Results } Alternative approach [Alpert 01]: } Combine buffer insertion Wire Sizing - New Results } Alternative approach [Alpert 01]: } Combine buffer insertion](http://slidetodoc.com/presentation_image/4dab57fb44d6a66652760ad7802a47f2/image-19.jpg)

Wire Sizing - New Results } Alternative approach [Alpert 01]: } Combine buffer insertion and } Untapered wires of (small number of) different widths } Theoretical result: Tapering gives at best 3. 5% improvement over this approach } Practical result: tapering generally not worthwhile [Alpert 01] “Interconnect Synthesis without wire tapering”, IEEE Trans. CAD, Vol. 20, No. 1, January 2001, pp. 90 -104 ECE 425 Spring 2007 Lecture 10 - Comb. Logic 19

Delay in RC-Trees } Many interconnection networks are trees } Extracted RC circuit modeling a gate output } Clock trees ECE 425 Spring 2007 Lecture 10 - Comb. Logic 20

Delay in RC-Trees: Penfield-Rubenstein Bounds } Key idea: characterize time constants in terms of } Path resistances between nodes } Capacitance values at each node ECE 425 Spring 2007 Lecture 10 - Comb. Logic 21

Delay in RC-Trees: Penfield-Rubenstein Bounds } Time constants Tp, TDo, TRo (eqn. 3 -30 - 3 -31) } Table 3 -2 (p. 165) - bounds for time, voltage ECE 425 Spring 2007 Lecture 10 - Comb. Logic 22

RC crosstalk } Crosstalk slows down signals---increases settling noise. } Two nets in analysis: } aggressor net causes interference; } victim net is interfered with. ECE 425 Spring 2007 Lecture 10 - Comb. Logic 23

Aggressors and victims aggressor net victim net ECE 425 Spring 2007 Lecture 10 - Comb. Logic 24

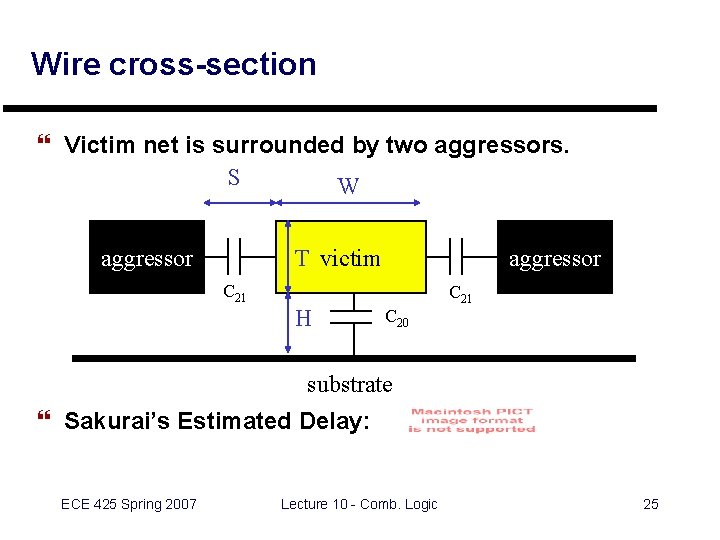

Wire cross-section } Victim net is surrounded by two aggressors. S W T victim aggressor C 21 H C 21 C 20 substrate } Sakurai’s Estimated Delay: ECE 425 Spring 2007 Lecture 10 - Comb. Logic 25

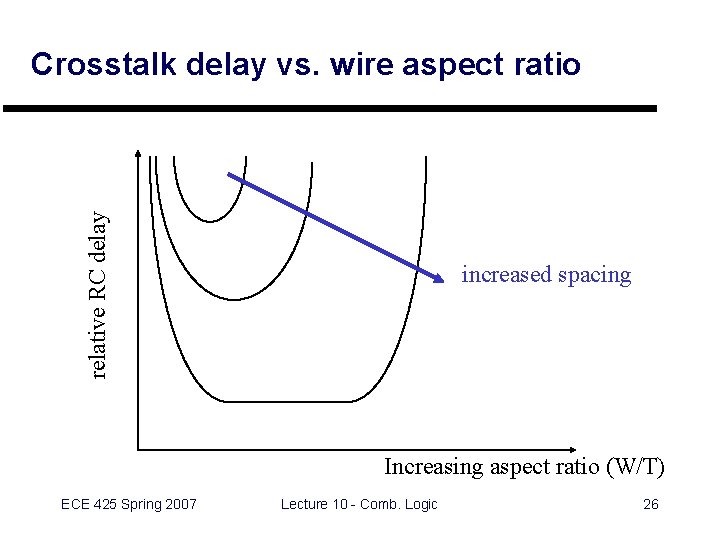

relative RC delay Crosstalk delay vs. wire aspect ratio increased spacing Increasing aspect ratio (W/T) ECE 425 Spring 2007 Lecture 10 - Comb. Logic 26

Crosstalk delay } There is an optimum wire width for any given wire spacing---at bottom of U curve. } Optimium width increases as spacing between wires increases. ECE 425 Spring 2007 Lecture 10 - Comb. Logic 27

RLC Delay } } Inductance is becoming significant in DSM Basic analysis: see Section 3. 8. 1, p. 173 Delay: see Section 3. 8. 2, p. 174 Buffer insertion: see Section 3. 8. 3, p. 175 ECE 425 Spring 2007 Lecture 10 - Comb. Logic 28

Coming Up } Combinational Logic Networks (Ch. 4) ECE 425 Spring 2007 Lecture 10 - Comb. Logic 29

- Slides: 29