ECE 425 VLSI Circuit Design Lecture 25 Subsystem

ECE 425 - VLSI Circuit Design Lecture 25 Subsystem Design (cont’d) Spring 2007 Prof. John Nestor ECE Department Lafayette College Easton, Pennsylvania 18042 nestorj@lafayette. edu ECE 425 Spring 2007 Lecture 25 - Subsystem Design 1

Announcements } No Final Exam } Reading } Wolf: 6. 1 -6. 9 } These notes drawn in part from handouts by } J. Rabaey, Digital Integrated Circuits, © Prentice-Hall 1995. ECE 425 Spring 2007 Lecture 25 - Subsystem Design 2

Where We Are: } Last Time: } Custom Subsystem Design - Multipliers } Today: } Custom Subsystem Design - Memories / Structured Logic ECE 425 Spring 2007 Lecture 25 - Subsystem Design 3

Subsystem Design } General Techniques } Pipelining } Datapath Design } Common Subsystems } } } Shifters Adders ALUs Multipliers Memories Structured Logic ECE 425 Spring 2007 Lecture 25 - Subsystem Design 4

Memory Classification ECE 425 Spring 2007 Lecture 25 - Subsystem Design 5

Memory Architecture - Decoders ECE 425 Spring 2007 Lecture 25 - Subsystem Design 6

Row/Column Memory Structure ECE 425 Spring 2007 Lecture 25 - Subsystem Design 7

Hierarchical Memory Structure ECE 425 Spring 2007 Lecture 25 - Subsystem Design 8

Memory Timing ECE 425 Spring 2007 Lecture 25 - Subsystem Design 9

DRAM vs. SRAM Timing ECE 425 Spring 2007 Lecture 25 - Subsystem Design 10

ROM Designs } Mask-Programmable - Set before fabrication } Field-Programmable - Fused connections } Electrically Programmable - Floating Gate Designs ECE 425 Spring 2007 Lecture 25 - Subsystem Design 11

Mask-Programmable ROM - MOS NOR ECE 425 Spring 2007 Lecture 25 - Subsystem Design 12

MOS NOR ROM - Contact-based Layout ECE 425 Spring 2007 Lecture 25 - Subsystem Design 13

MOS NOR Layout - Implant-based Layout ECE 425 Spring 2007 Lecture 25 - Subsystem Design 14

MOS NAND ROM ECE 425 Spring 2007 Lecture 25 - Subsystem Design 15

MOS NAND ROM - Layout ECE 425 Spring 2007 Lecture 25 - Subsystem Design 16

Nonvolatile ROM Floating-Gate MOS Transistor (FAMOS) ECE 425 Spring 2007 Lecture 25 - Subsystem Design 17

Programming a Floating-Gate Transistor (VT > VDD) ECE 425 Spring 2007 Lecture 25 - Subsystem Design 18

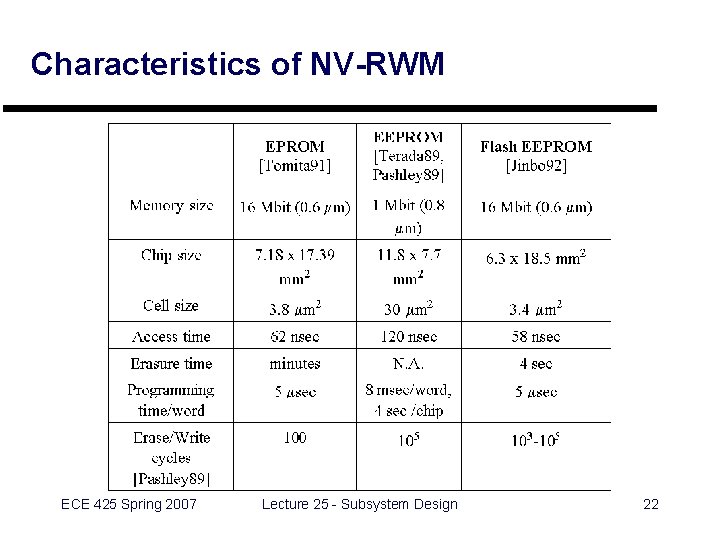

Types of NV-RWM } EPROM (FAMOS) } Program using avalanch hot-electron injection } Erase using ultraviolet light } EEPROM (FLOTOX) } Program & erase using Fowler-Nordheim Tunneling } Advantage: elecrically eraseable } Flash EPROM } Program using avalanche hot-electron injection } Erase using Fowler-Nordheim tunneling ECE 425 Spring 2007 Lecture 25 - Subsystem Design 19

FLOTOX EEPROM Transistors ECE 425 Spring 2007 Lecture 25 - Subsystem Design 20

Flash EEPROM (ETOX) Transistor ECE 425 Spring 2007 Lecture 25 - Subsystem Design 21

Characteristics of NV-RWM ECE 425 Spring 2007 Lecture 25 - Subsystem Design 22

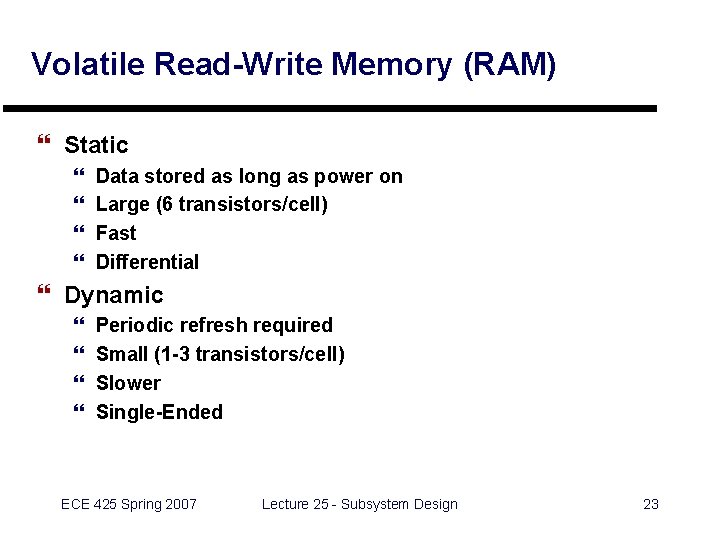

Volatile Read-Write Memory (RAM) } Static } } Data stored as long as power on Large (6 transistors/cell) Fast Differential } Dynamic } } Periodic refresh required Small (1 -3 transistors/cell) Slower Single-Ended ECE 425 Spring 2007 Lecture 25 - Subsystem Design 23

6 -Transistor CMOS SRAM ECE 425 Spring 2007 Lecture 25 - Subsystem Design 24

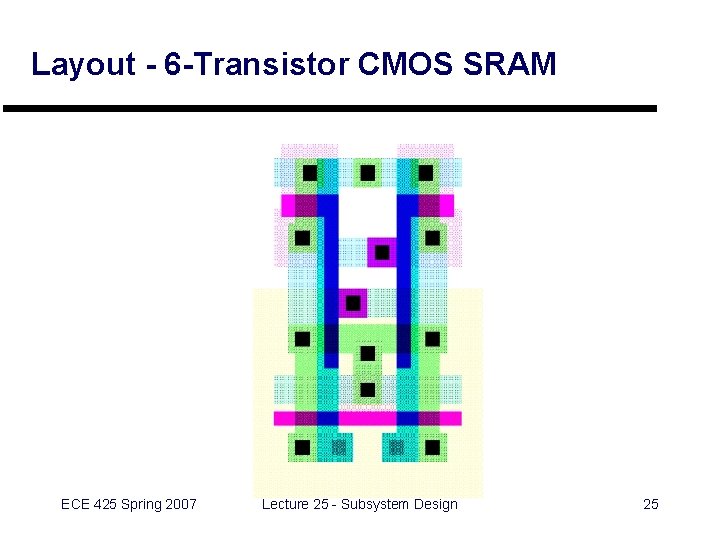

Layout - 6 -Transistor CMOS SRAM ECE 425 Spring 2007 Lecture 25 - Subsystem Design 25

3 -Transistor Dynamic RAM ECE 425 Spring 2007 Lecture 25 - Subsystem Design 26

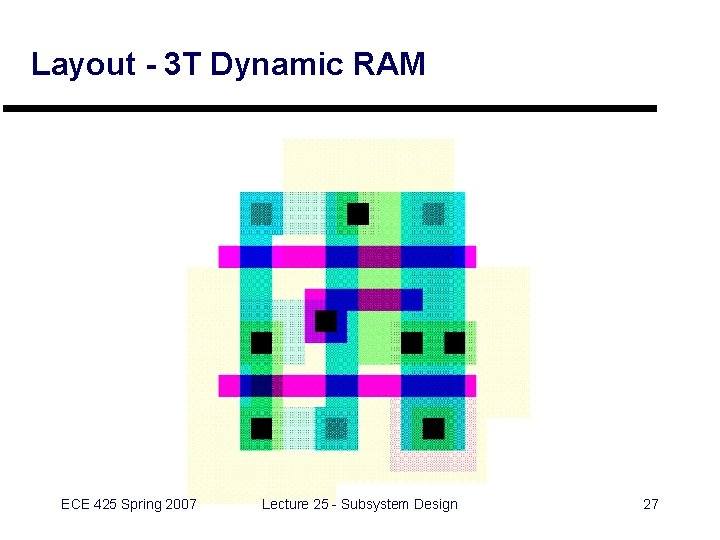

Layout - 3 T Dynamic RAM ECE 425 Spring 2007 Lecture 25 - Subsystem Design 27

1 Transistor Dynamic RAM ECE 425 Spring 2007 Lecture 25 - Subsystem Design 28

1 Transistor Dynamic RAM ECE 425 Spring 2007 Lecture 25 - Subsystem Design 29

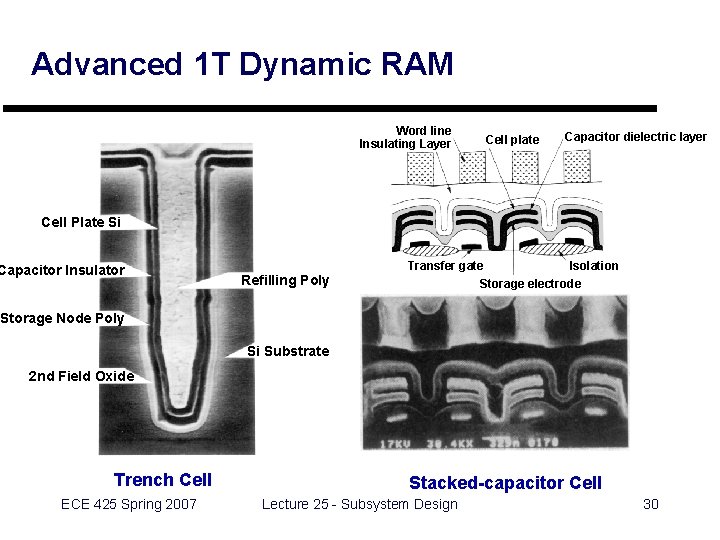

Advanced 1 T Dynamic RAM Word line Insulating Layer Cell plate Capacitor dielectric layer Cell Plate Si Capacitor Insulator Refilling Poly Transfer gate Isolation Storage electrode Storage Node Poly Si Substrate 2 nd Field Oxide Trench Cell ECE 425 Spring 2007 Stacked-capacitor Cell Lecture 25 - Subsystem Design 30

Subsystem Design } General Techniques. Goals } Pipelining } Datapath Design } Common Subsystems } } } Shifters Adders ALUs Multipliers Memories Structured Logic ECE 425 Spring 2007 Lecture 25 - Subsystem Design 31

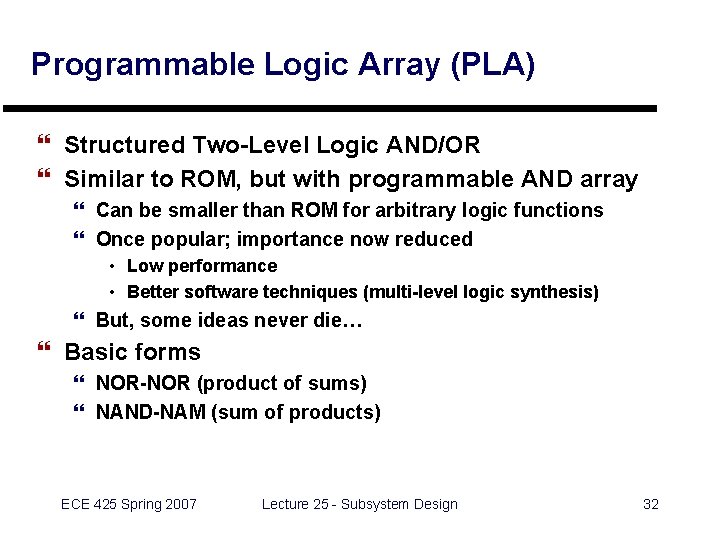

Programmable Logic Array (PLA) } Structured Two-Level Logic AND/OR } Similar to ROM, but with programmable AND array } Can be smaller than ROM for arbitrary logic functions } Once popular; importance now reduced • Low performance • Better software techniques (multi-level logic synthesis) } But, some ideas never die… } Basic forms } NOR-NOR (product of sums) } NAND-NAM (sum of products) ECE 425 Spring 2007 Lecture 25 - Subsystem Design 32

Programmable Logic Array ECE 425 Spring 2007 Lecture 25 - Subsystem Design 33

Pseudo-Static PLA ECE 425 Spring 2007 Lecture 25 - Subsystem Design 34

Dynamic PLA ECE 425 Spring 2007 Lecture 25 - Subsystem Design 35

Clock Signal Generation for self-timed dynamic PLA ECE 425 Spring 2007 Lecture 25 - Subsystem Design 36

PLA Layout ECE 425 Spring 2007 Lecture 25 - Subsystem Design 37

That’s all, folks! ECE 425 Spring 2007 Lecture 25 - Subsystem Design 38

- Slides: 38