COMP 541 Digital Logic and Computer Design Montek

- Slides: 57

COMP 541 Digital Logic and Computer Design Montek Singh Aug 24, 2016

Today’s Topics ã Course description l What’s this course about? l Syllabus Ø Textbook and Resources Ø Course Requirements Ø Grading Ø Policies and Honor Code ã Material from Chapter 1 (self-study review) l What is digital logic? l Binary signaling l Number systems l Codes 2

What’s This Course About? ã Digital Logic l transistors (briefly) l gates l combinational circuits l sequential circuits (state machines) ã Computer Design l arithmetic circuits l memories l processor architecture l input and output ã Emphasis on high-level descriptions l hardware description lang. (System Verilog) instead of circuits l modern design practices 3

Key Learning Objectives ã At the end of this course, you should be able to: l convert a specification into an implementation l hierarchically decompose a complex spec Ø into simpler components l understand concurrency Ø develop concurrent system specs and implementations l test a given design for correctness Ø develop a test bench and performing simulation l use state-of-the-art software tools for hardware design Ø “computer-aided-design” (CAD) tools ã Each student will have: l designed a full microprocessor (basic MIPS from COMP 411) l implemented it on a development kit l programmed it in assembly to show a demo 4

What do final projects look like? ã Full MIPS computer l mini MIPS CPU l memories l output devices Ø VGA display Ø maybe sound l input devices Ø keyboard, maybe mouse Ø joystick, accelerometer, keypad l functioning demo Ø examples (from Spring 2012) 5

Who is this course for? ã Advanced course in digital logic and computer design l follow-up to COMP 411 (Computer Organization) l full-gate level implementation of MIPS processor from 411 Ø including memories and I/O ã Who should take this course? l undergrads who want to pursue a career or further studies in the fields of: Ø computer architecture Ø chip design, or other engineering disciples l grad students looking to fill a gap in their coursework l anyone interested in learning how a digital system is implemented, in a hands-on manner 6

How will we build an entire computer? ã Labs on Fridays l hands-on experience in designing digital circuits/systems l start small, but quickly go to higher levels of abstraction ã We will write descriptions of design l instead of drawing circuit diagrams l descriptions look like “code” Ø high-level language Ø BEWARE: these are not software programs! l use compilation tools to convert into gates and wires l map (“burn”) these designs onto a reconfigurable chip Ø called Field Programmable Gate Array (FPGAs) Ø chips with a lot of circuits (millions of transistors) Ø sort of like burning music to a rewritable CD 7

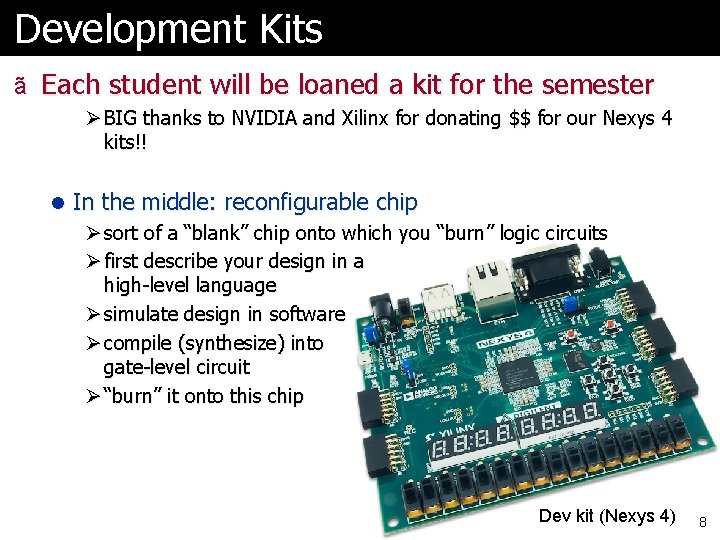

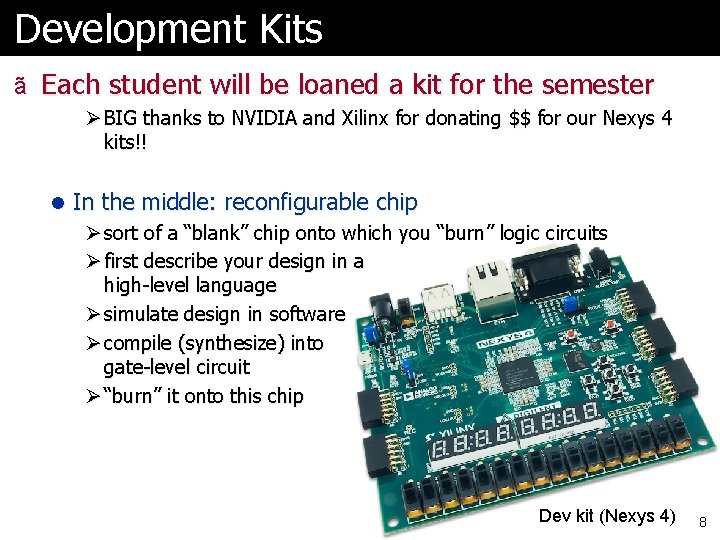

Development Kits ã Each student will be loaned a kit for the semester Ø BIG thanks to NVIDIA and Xilinx for donating $$ for our Nexys 4 kits!! l In the middle: reconfigurable chip Ø sort of a “blank” chip onto which you “burn” logic circuits Ø first describe your design in a high-level language Ø simulate design in software Ø compile (synthesize) into gate-level circuit Ø “burn” it onto this chip Dev kit (Nexys 4) 8

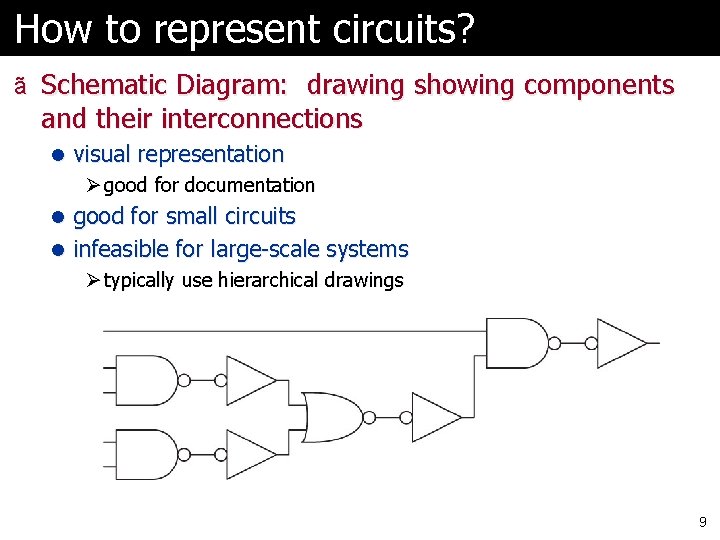

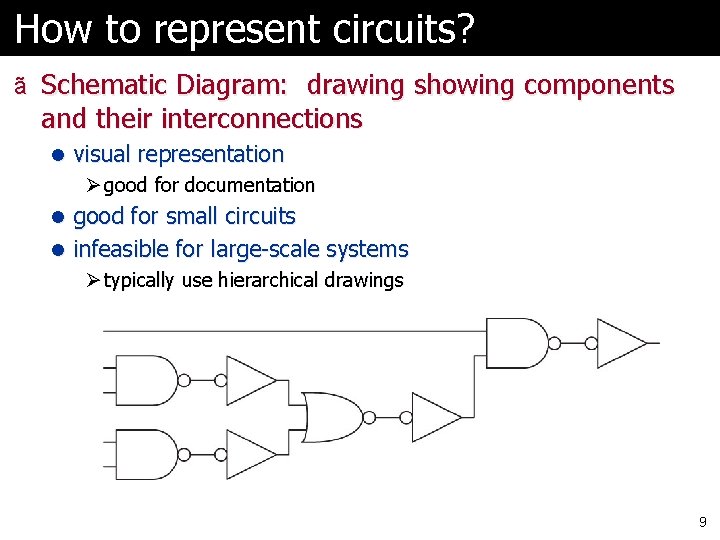

How to represent circuits? ã Schematic Diagram: drawing showing components and their interconnections l visual representation Ø good for documentation l good for small circuits l infeasible for large-scale systems Ø typically use hierarchical drawings 9

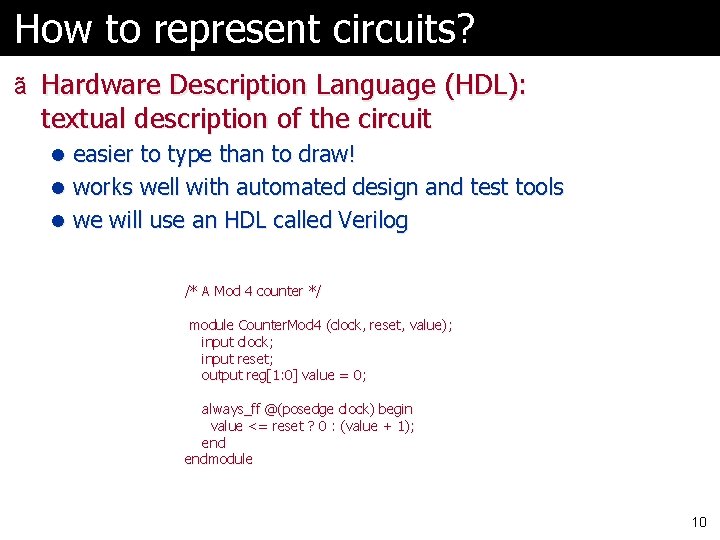

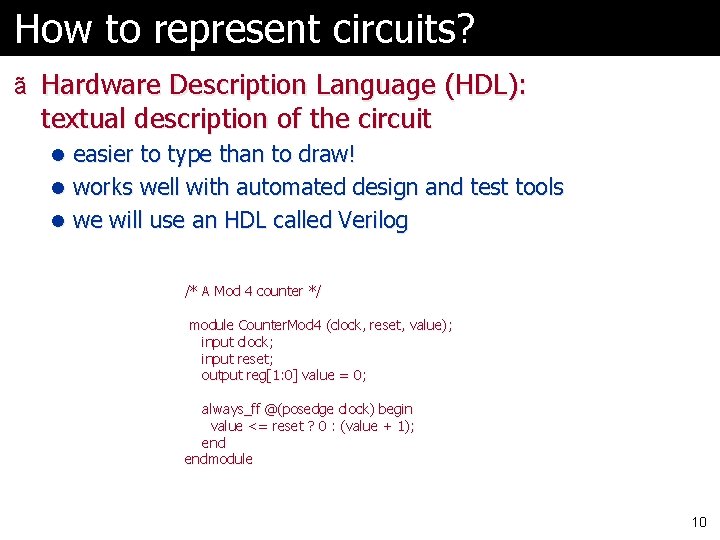

How to represent circuits? ã Hardware Description Language (HDL): textual description of the circuit l easier to type than to draw! l works well with automated design and test tools l we will use an HDL called Verilog /* A Mod 4 counter */ module Counter. Mod 4 (clock, reset, value); input clock; input reset; output reg[1: 0] value = 0; always_ff @(posedge clock) begin value <= reset ? 0 : (value + 1); endmodule 10

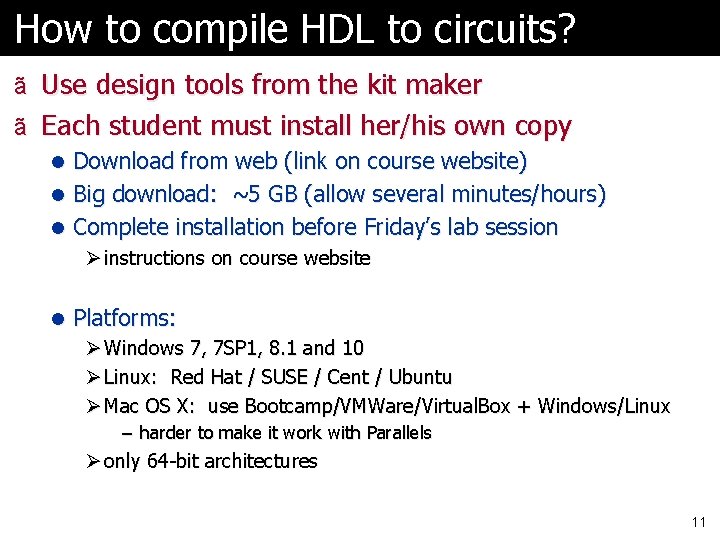

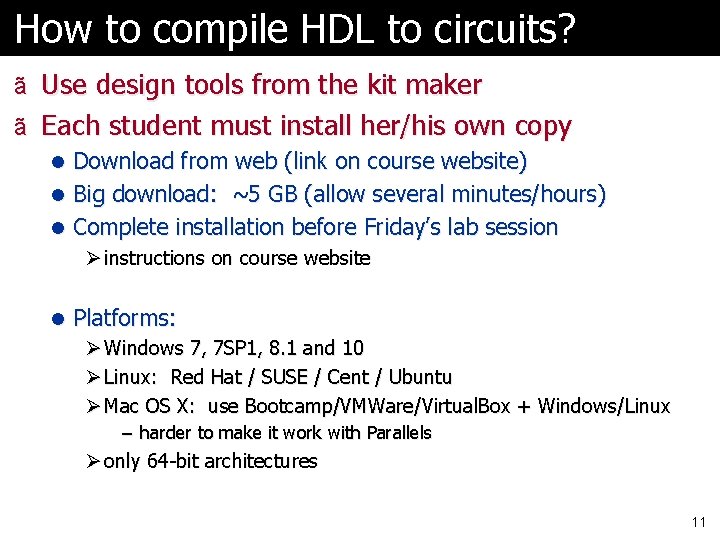

How to compile HDL to circuits? ã Use design tools from the kit maker ã Each student must install her/his own copy l Download from web (link on course website) l Big download: ~5 GB (allow several minutes/hours) l Complete installation before Friday’s lab session Ø instructions on course website l Platforms: Ø Windows 7, 7 SP 1, 8. 1 and 10 Ø Linux: Red Hat / SUSE / Cent / Ubuntu Ø Mac OS X: use Bootcamp/VMWare/Virtual. Box + Windows/Linux – harder to make it work with Parallels Ø only 64 -bit architectures 11

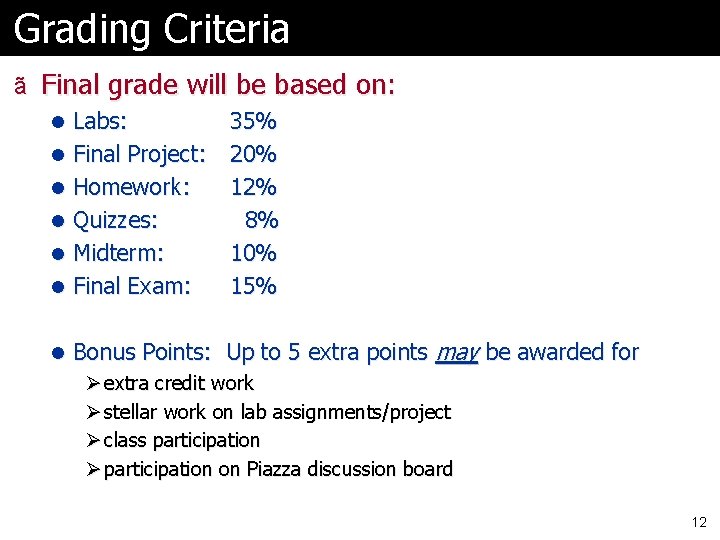

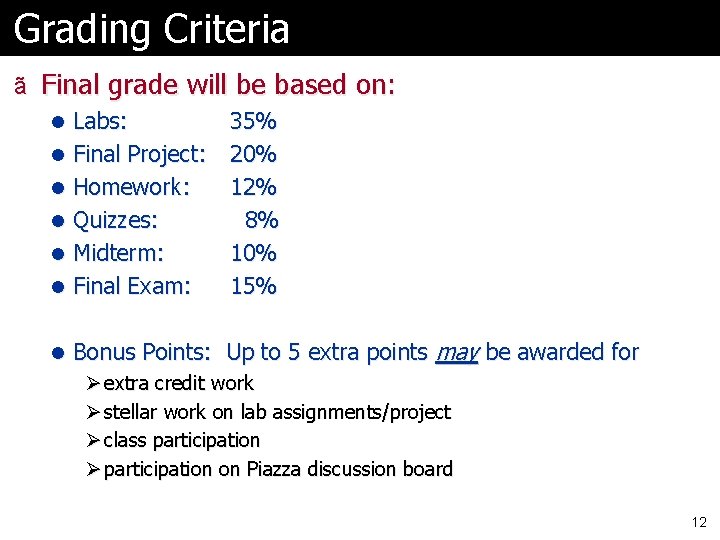

Grading Criteria ã Final grade will be based on: l Labs: l Final Project: l Homework: l Quizzes: l Midterm: l Final Exam: 35% 20% 12% 8% 10% 15% l Bonus Points: Up to 5 extra points may be awarded for Ø extra credit work Ø stellar work on lab assignments/project Ø class participation Ø participation on Piazza discussion board 12

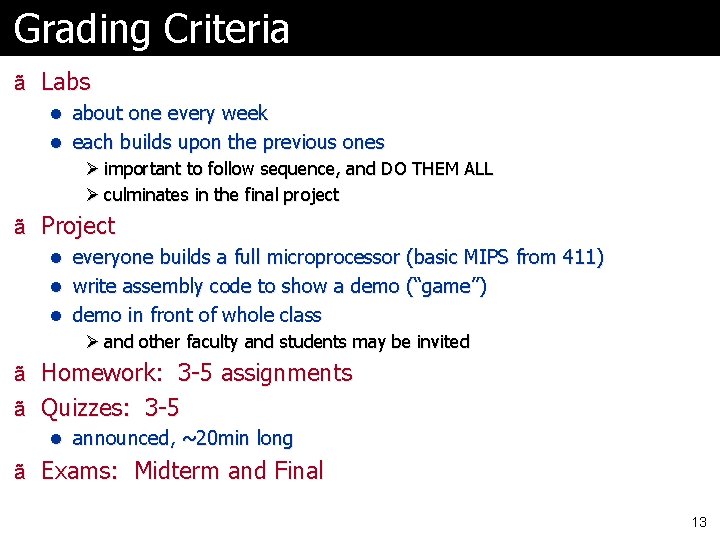

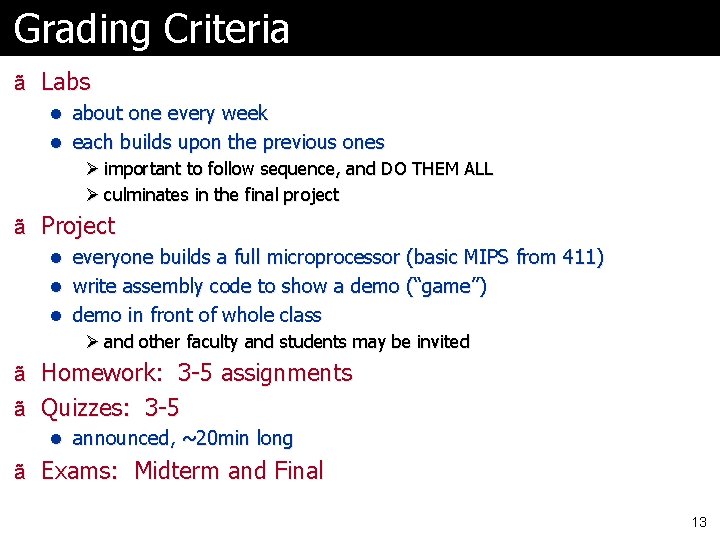

Grading Criteria ã Labs l about one every week l each builds upon the previous ones Ø important to follow sequence, and DO THEM ALL Ø culminates in the final project ã Project l everyone builds a full microprocessor (basic MIPS from 411) l write assembly code to show a demo (“game”) l demo in front of whole class Ø and other faculty and students may be invited ã Homework: 3 -5 assignments ã Quizzes: 3 -5 l announced, ~20 min long ã Exams: Midterm and Final 13

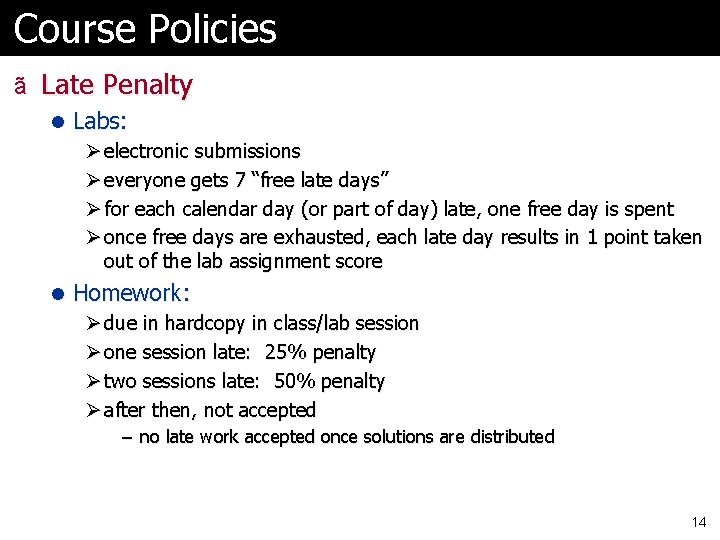

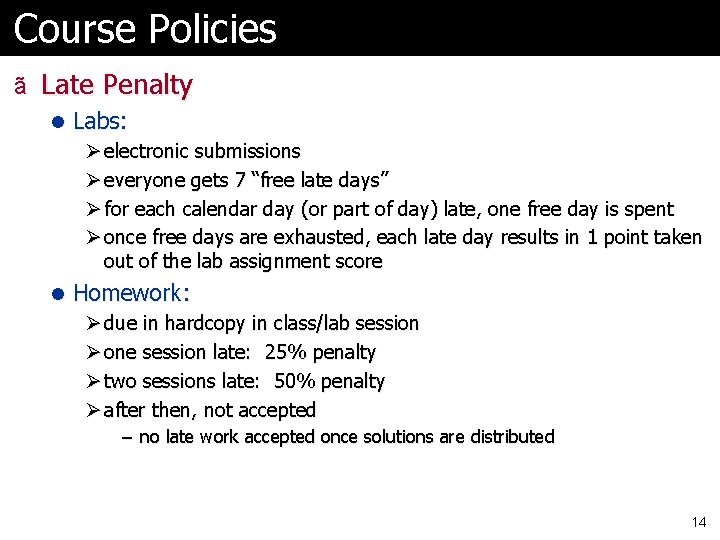

Course Policies ã Late Penalty l Labs: Ø electronic submissions Ø everyone gets 7 “free late days” Ø for each calendar day (or part of day) late, one free day is spent Ø once free days are exhausted, each late day results in 1 point taken out of the lab assignment score l Homework: Ø due in hardcopy in class/lab session Ø one session late: 25% penalty Ø two sessions late: 50% penalty Ø after then, not accepted – no late work accepted once solutions are distributed 14

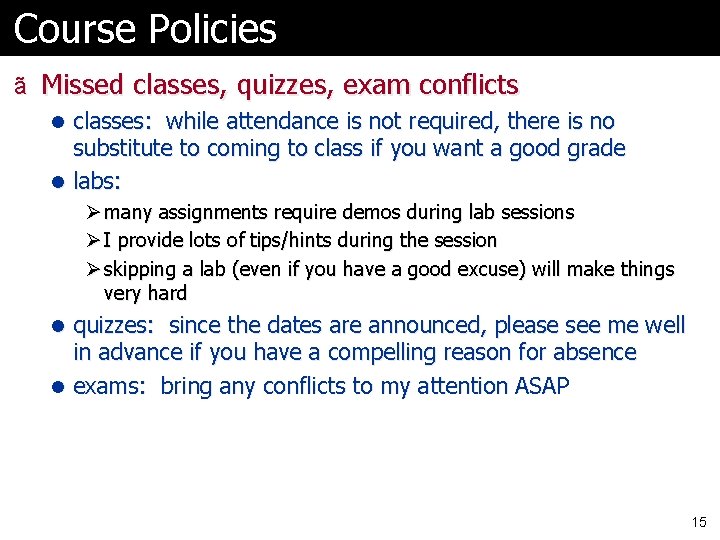

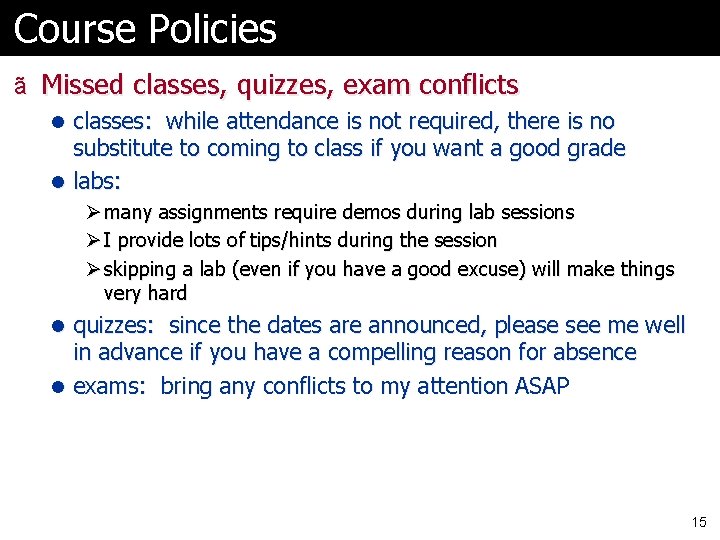

Course Policies ã Missed classes, quizzes, exam conflicts l classes: while attendance is not required, there is no substitute to coming to class if you want a good grade l labs: Ø many assignments require demos during lab sessions Ø I provide lots of tips/hints during the session Ø skipping a lab (even if you have a good excuse) will make things very hard l quizzes: since the dates are announced, please see me well in advance if you have a compelling reason for absence l exams: bring any conflicts to my attention ASAP 15

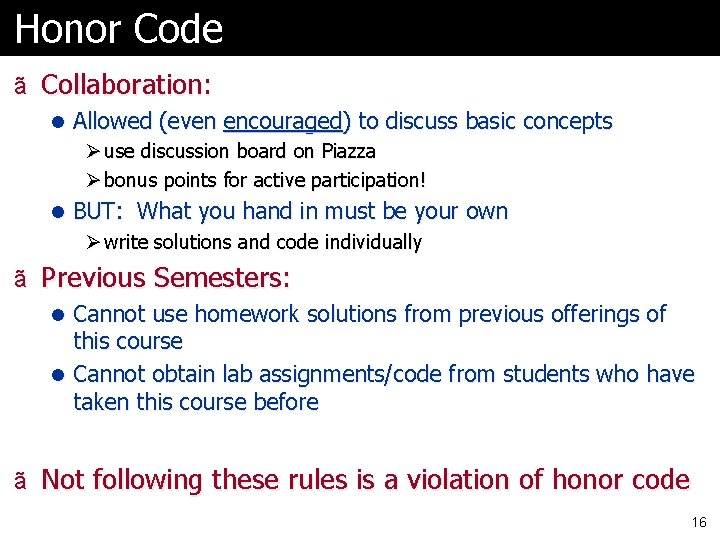

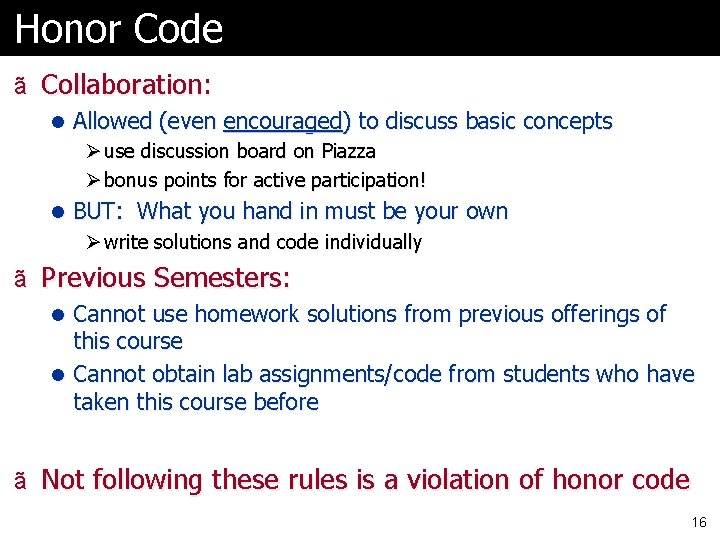

Honor Code ã Collaboration: l Allowed (even encouraged) to discuss basic concepts Ø use discussion board on Piazza Ø bonus points for active participation! l BUT: What you hand in must be your own Ø write solutions and code individually ã Previous Semesters: l Cannot use homework solutions from previous offerings of this course l Cannot obtain lab assignments/code from students who have taken this course before ã Not following these rules is a violation of honor code 16

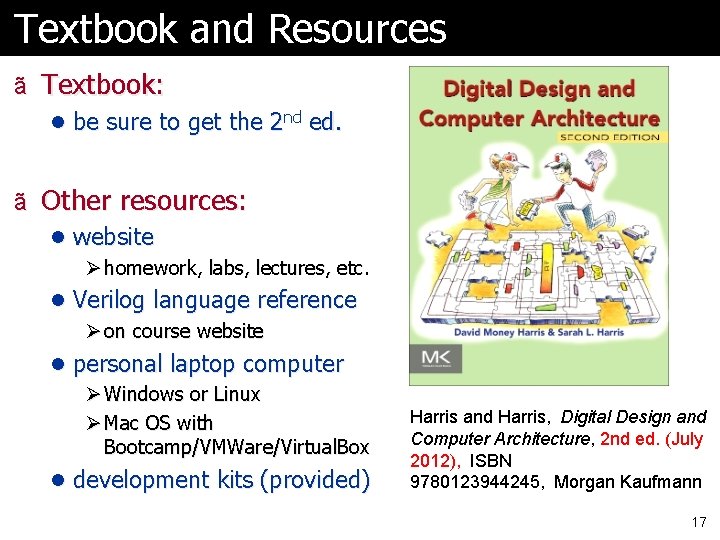

Textbook and Resources ã Textbook: l be sure to get the 2 nd ed. ã Other resources: l website Ø homework, labs, lectures, etc. l Verilog language reference Ø on course website l personal laptop computer Ø Windows or Linux Ø Mac OS with Bootcamp/VMWare/Virtual. Box l development kits (provided) Harris and Harris, Digital Design and Computer Architecture, 2 nd ed. (July 2012), ISBN 9780123944245, Morgan Kaufmann 17

Overview of Textbook ã Chapters 1 -5: Digital logic l Combinational, sequential, basic circuits, HDL ã Chapter 6: Architecture l Fast – review for those who took COMP 411 ã Chapter 7: Microarchitectures ã Chapters 8: Memories ã Appendix A: Implementation l FPGAs, etc. ã Order of topics: l Will change order from that in book Ø to try to get you working on interesting labs sooner 18

Class Web Page Website: l http: //comp 541 fall 16. web. unc. edu l Linked from my home page http: //www. cs. unc. edu/~montek l All lecture slides, lab assignments posted there l Syllabus, homework, etc. posted there l See Sakai for scores/grades l Use Piazza for questions/discussions ã TAs: Abu Raja and Jordan Elliott ã Office Hours l to be finalized by Monday, Aug 29 19

Now Shift to Technology Should be a review for all of you

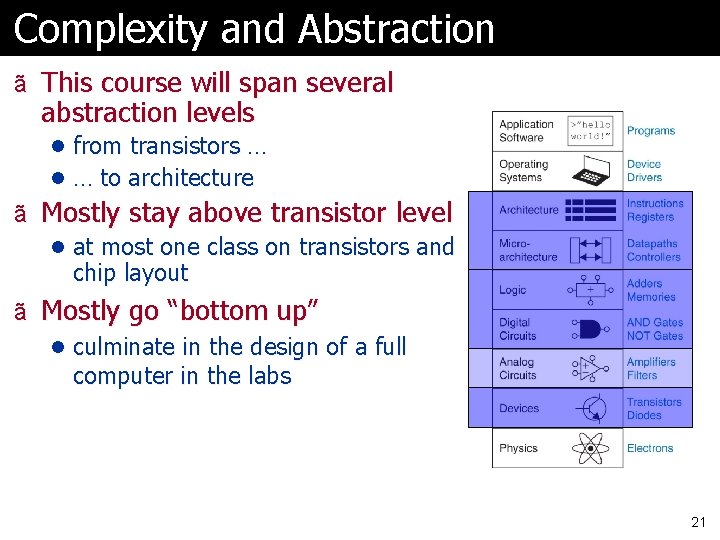

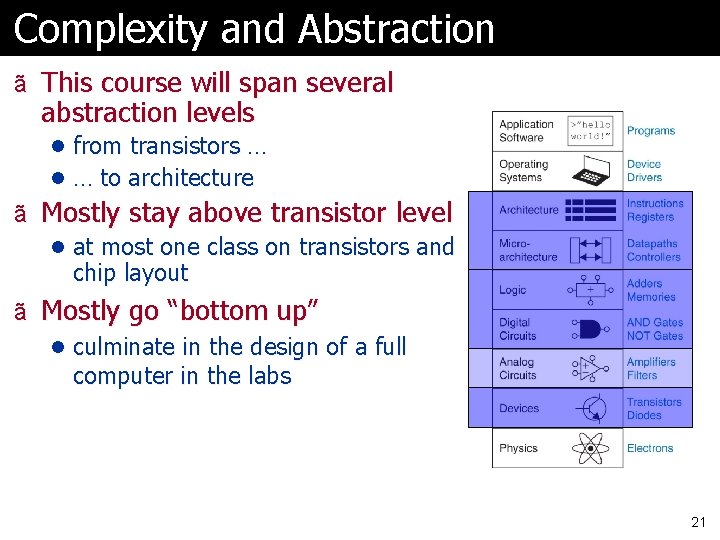

Complexity and Abstraction ã This course will span several abstraction levels l from transistors … l … to architecture ã Mostly stay above transistor level l at most one class on transistors and chip layout ã Mostly go “bottom up” l culminate in the design of a full computer in the labs 21

The Three -Y’s ã Hierarchy l divide a system into modules and submodules Ø keep dividing until pieces are easy to understand ã Modularity l modules have well-defined functions and interfaces Ø so can be connected easily without surprises ã Regularity l encouraging uniformity, so modules can be easily reused Ø so same set of basic building blocks can be used Ø e. g. , a 16 -bit adder uses the same basic blocks as an 8 -bit adder 22

Digital vs. Analog ã Analog – infinite resolution l Like (old fashioned) radio dial l We’ll do very little with analog Ø VGA, maybe sound: approximate them using digital values ã Digital – a finite set of values l Like money l Can’t get smaller than cents l Typically also has maximum value 23

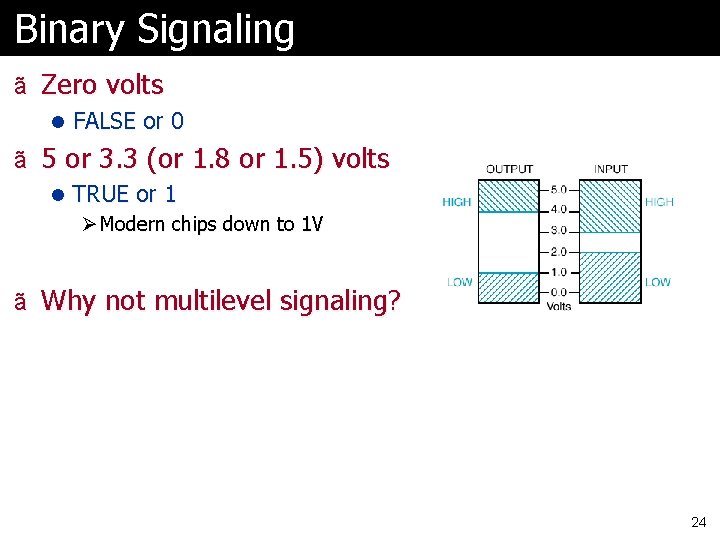

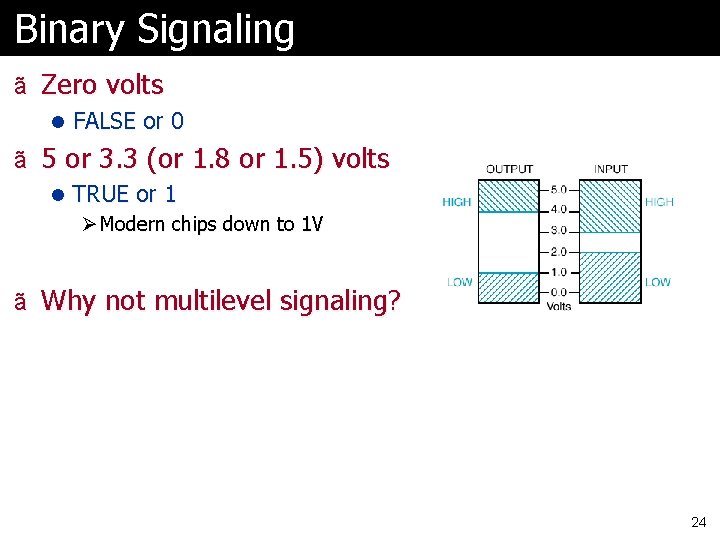

Binary Signaling ã Zero volts l FALSE or 0 ã 5 or 3. 3 (or 1. 8 or 1. 5) volts l TRUE or 1 Ø Modern chips down to 1 V ã Why not multilevel signaling? 24

Discrete Data ã Some data inherently discrete l Names (sets of letters) ã Some quantized l Music recorded from microphone l Note that other examples like music from CD or electronic keyboard already quantized l Mouse movement is quantized 25

Numbers and Arithmetic ã I have put most of these slides at end l Backup in case you’ve forgotten ã Review of: l binary/octal/hexadecimal numbers l arithmetic ã Let’s cover l Other codes, parity 26

BCD ã Binary Coded Decimal ã Decimal digits stored in binary l Four bits/digit l Like hex, except stops at 9 l Example 931 is coded as 1001 0011 0001 ã Remember: these are just by us. encodings. Meanings are assigned 27

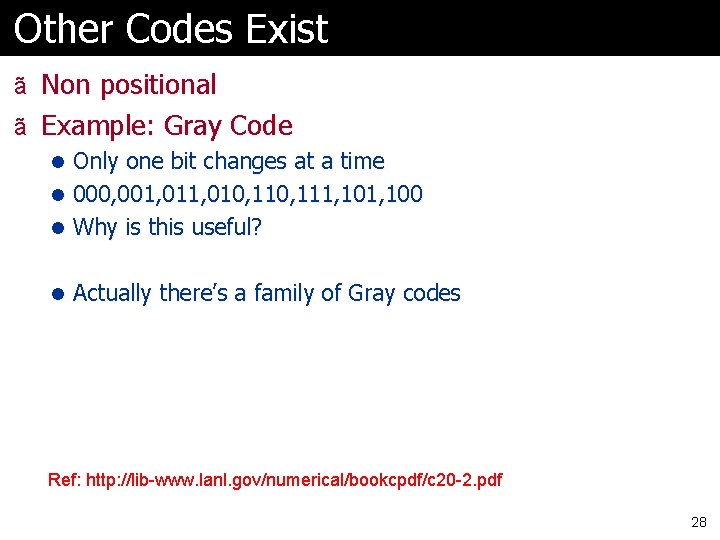

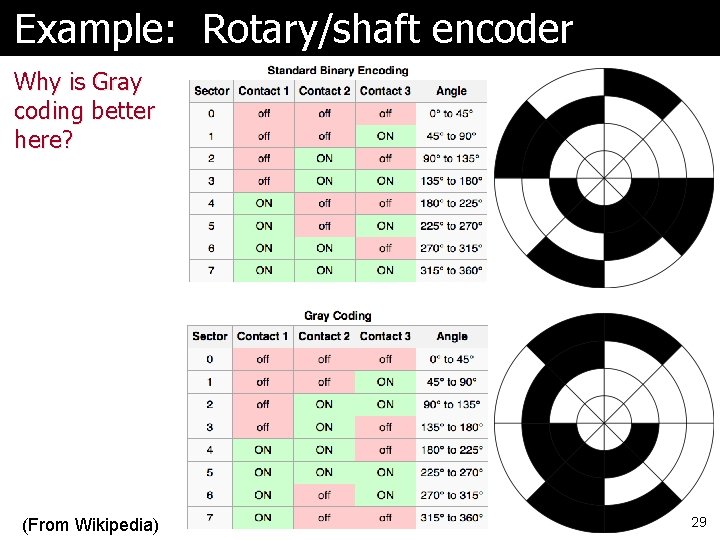

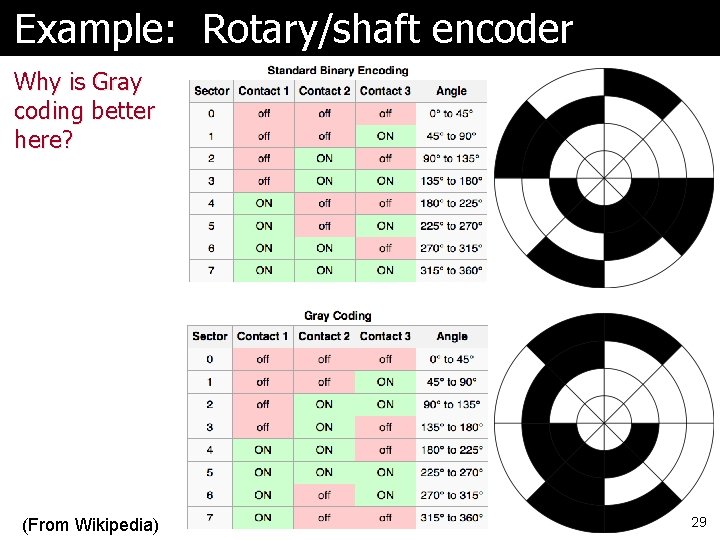

Other Codes Exist ã Non positional ã Example: Gray Code l Only one bit changes at a time l 000, 001, 010, 111, 100 l Why is this useful? l Actually there’s a family of Gray codes Ref: http: //lib-www. lanl. gov/numerical/bookcpdf/c 20 -2. pdf 28

Example: Rotary/shaft encoder Why is Gray coding better here? (From Wikipedia) 29

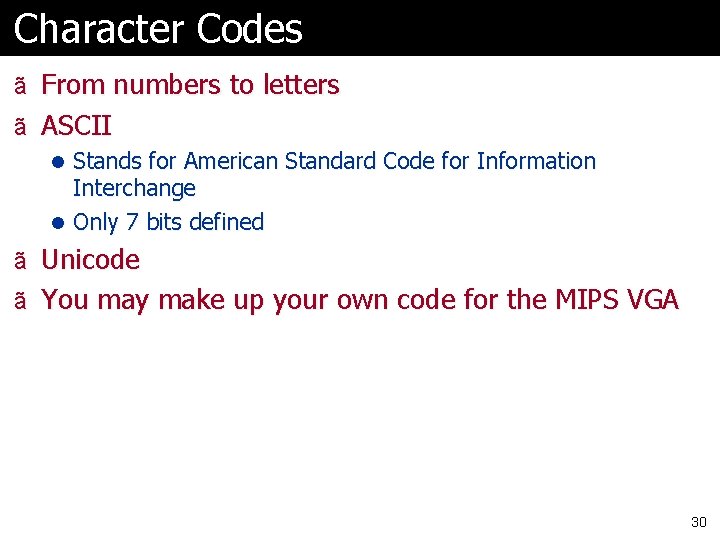

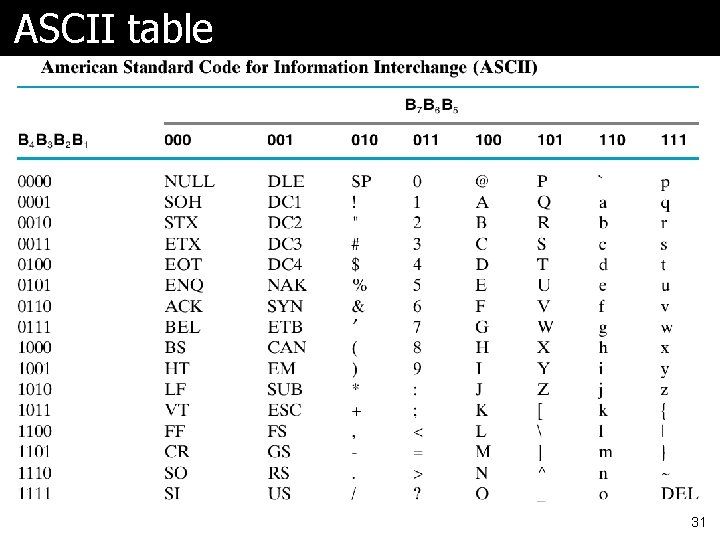

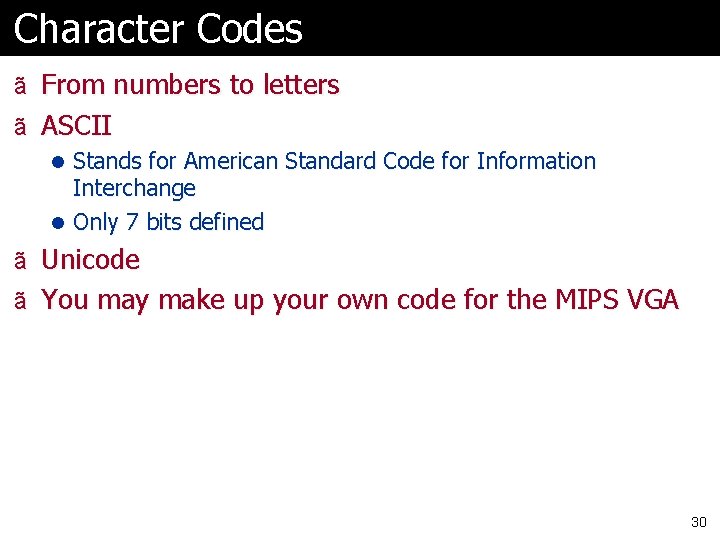

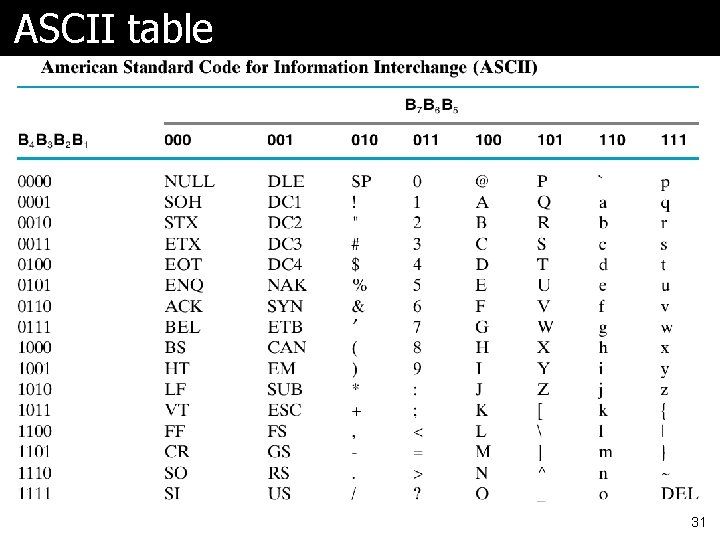

Character Codes ã From numbers to letters ã ASCII l Stands for American Standard Code for Information Interchange l Only 7 bits defined ã Unicode ã You may make up your own code for the MIPS VGA 30

ASCII table 31

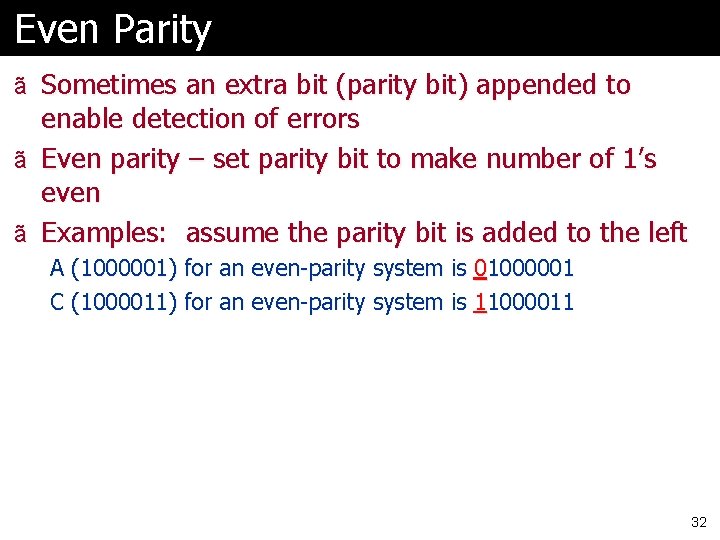

Even Parity ã Sometimes an extra bit (parity bit) appended to enable detection of errors ã Even parity – set parity bit to make number of 1’s even ã Examples: assume the parity bit is added to the left A (1000001) for an even-parity system is 01000001 C (1000011) for an even-parity system is 11000011 32

Odd Parity ã Similar except make the number of 1’s odd ã Examples A (1000001) for an odd-parity system is 11000001 C (1000011) for an odd-parity system is 01000011 33

Error Detection ã Note that parity detects only simple errors l One, three, etc. bits ã More complex methods exist ã Some that enable recovery of original info l Cost is more redundant bits 34

Reading ã Read Chapter 1 35

Next Class ã Combinational Logic Basics First Lab: Fri, Aug 26 l I will demo tools l You should have your tools installed and bring your laptop 36

Reference Slides Should be all review material

Binary Numbers ã Strings of binary digits (“bits”) l One bit can store a number from 0 to 1 l n bits can store numbers from 0 to 2 n 38

Binary – Powers of 2 ã Positional representation ã Each digit represents a power of 2 So 101 binary is 1 • 2 2 + 0 • 21 + 1 • 2 0 or 1 • 4 + 0 • 2 + 1 • 1=5 39

Converting Binary to Decimal ã Easy, just multiply digit by power of 2 ã Just like a decimal number is represented ã Example follows 40

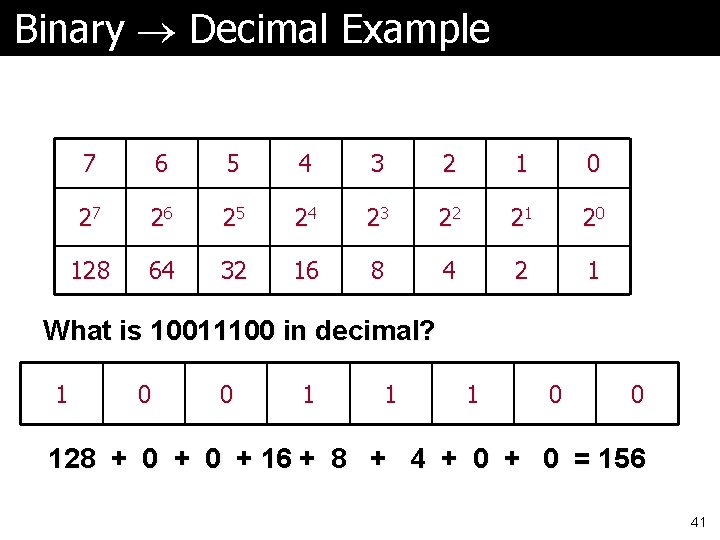

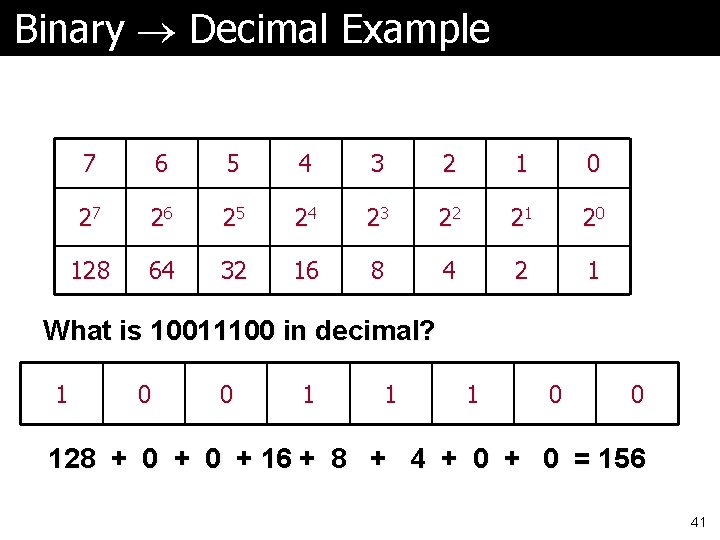

Binary Decimal Example 7 6 5 4 3 2 1 0 27 26 25 24 23 22 21 20 128 64 32 16 8 4 2 1 What is 10011100 in decimal? 1 0 0 1 1 1 0 0 128 + 0 + 16 + 8 + 4 + 0 = 156 41

Decimal to Binary ã A little more work than binary to decimal ã Some examples l 3 = 2 + 1 = 11 (that’s 1 • 21 + 1 • 20) l 5 = 4 + 1 = 101 (that’s 1 • 22 + 0 • 21 + 1 • 20) 42

Algorithm – Decimal to Binary ã Find largest power-of-two smaller than decimal number ã Make the appropriate binary digit a ‘ 1’ ã Subtract the power of 2 from decimal ã Do the same thing again 43

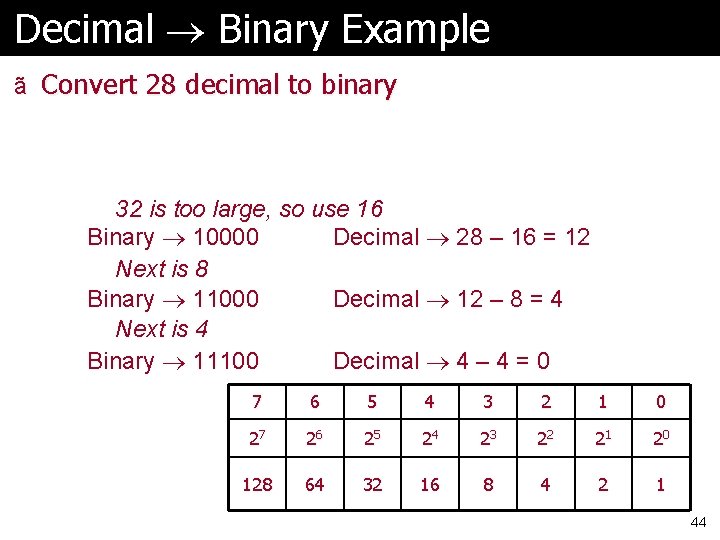

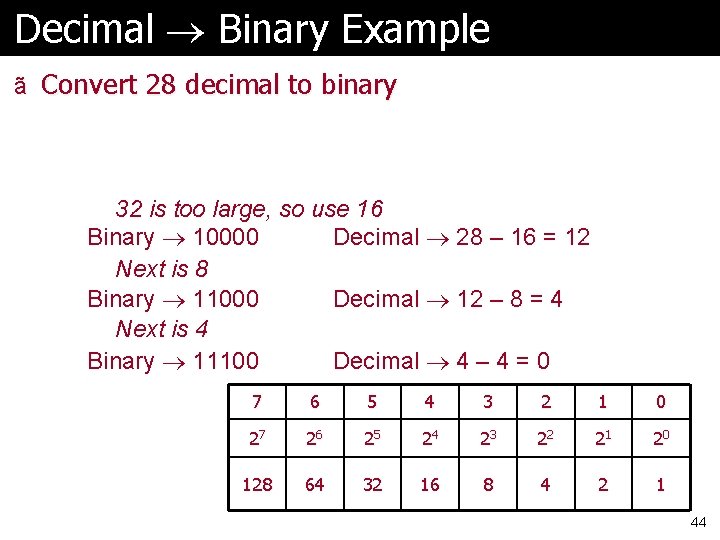

Decimal Binary Example ã Convert 28 decimal to binary 32 is too large, so use 16 Binary 10000 Decimal 28 – 16 = 12 Next is 8 Binary 11000 Decimal 12 – 8 = 4 Next is 4 Binary 11100 Decimal 4 – 4 = 0 7 6 5 4 3 2 1 0 27 26 25 24 23 22 21 20 128 64 32 16 8 4 2 1 44

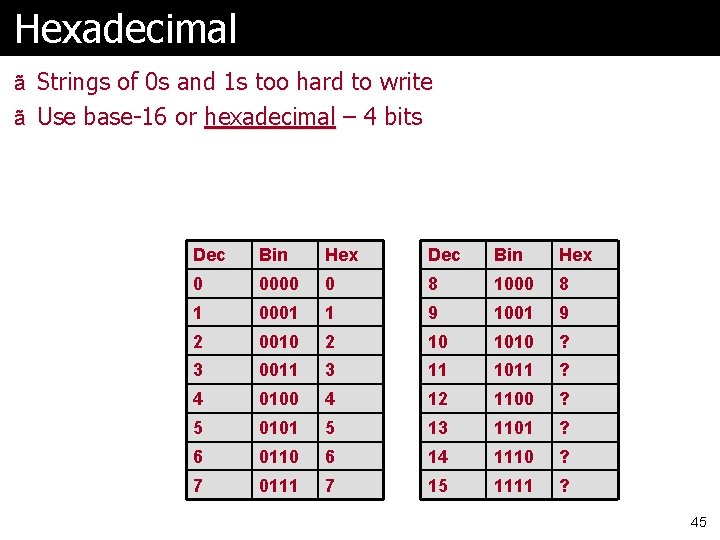

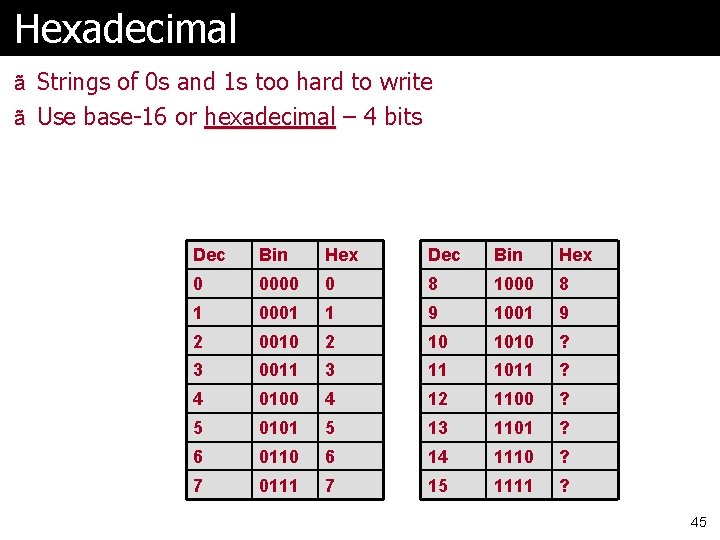

Hexadecimal ã Strings of 0 s and 1 s too hard to write ã Use base-16 or hexadecimal – 4 bits Dec Bin Hex 0 0000 0 8 1000 8 1 0001 1 9 1001 9 2 0010 2 10 1010 ? 3 0011 3 11 1011 ? 4 0100 4 12 1100 ? 5 0101 5 13 1101 ? 6 0110 6 14 1110 ? 7 0111 7 15 1111 ? 45

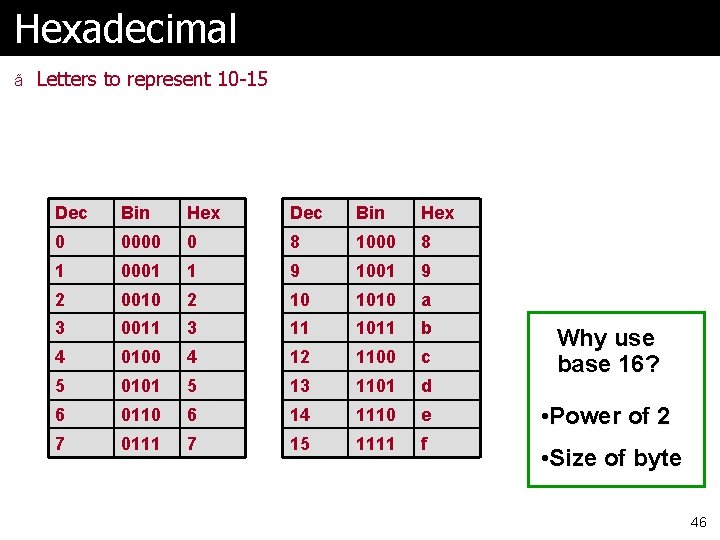

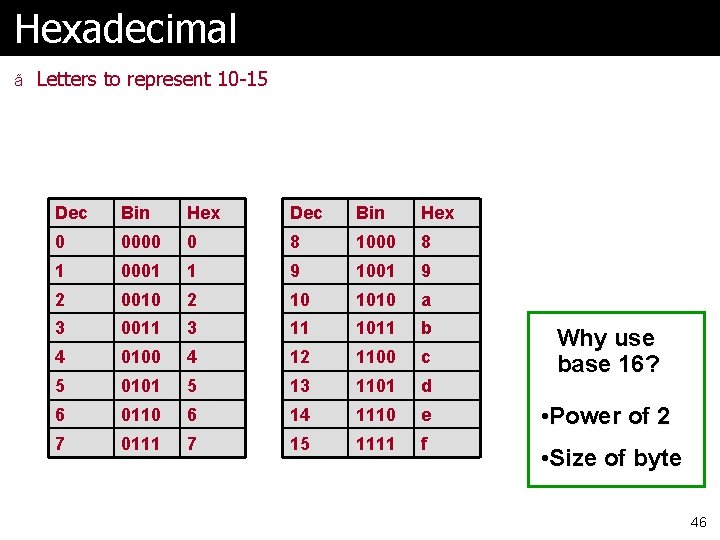

Hexadecimal ã Letters to represent 10 -15 Dec Bin Hex 0 0000 0 8 1000 8 1 0001 1 9 1001 9 2 0010 2 10 1010 a 3 0011 3 11 1011 b 4 0100 4 12 1100 c 5 0101 5 13 1101 d 6 0110 6 14 1110 e 7 0111 7 15 1111 f Why use base 16? • Power of 2 • Size of byte 46

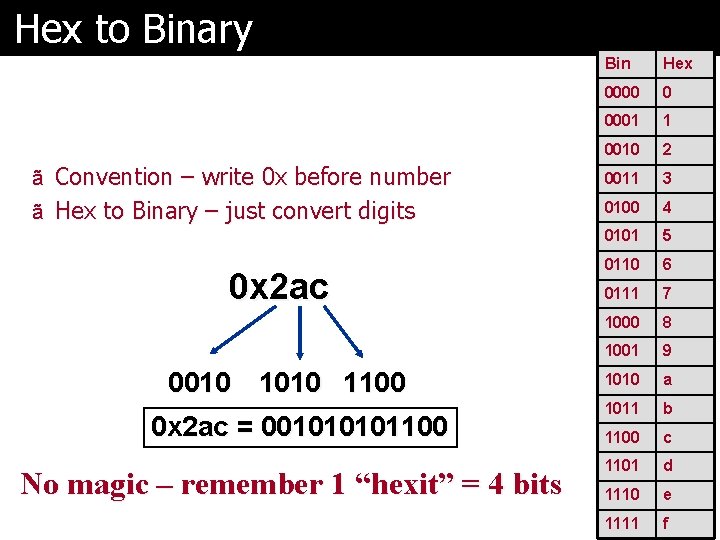

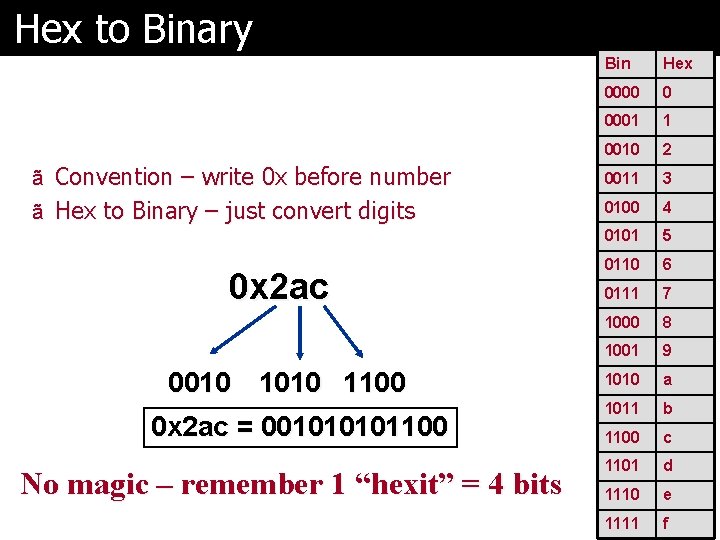

Hex to Binary Bin Hex 0000 0 0001 1 0010 2 ã Convention – write 0 x before number 0011 3 ã Hex to Binary – just convert digits 0100 4 0101 5 0110 6 0111 7 1000 8 1001 9 1010 a 1011 b 1100 c 1101 d 1110 e 1111 f 0 x 2 ac 0010 1100 0 x 2 ac = 00101100 No magic – remember 1 “hexit” = 4 bits 47

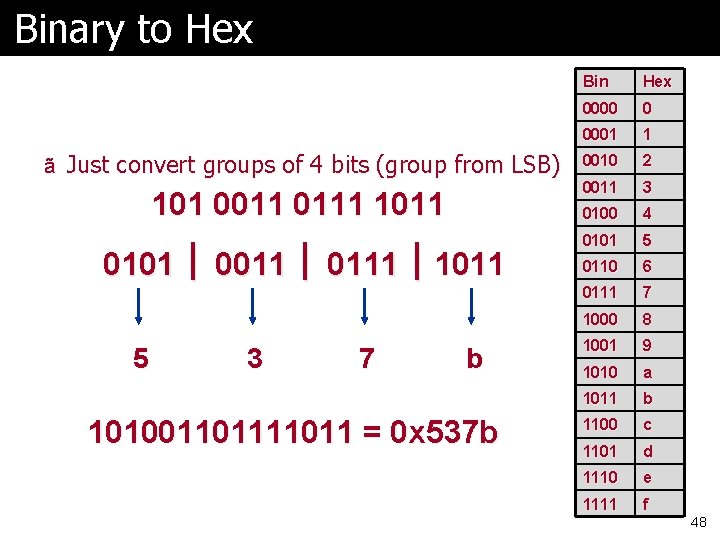

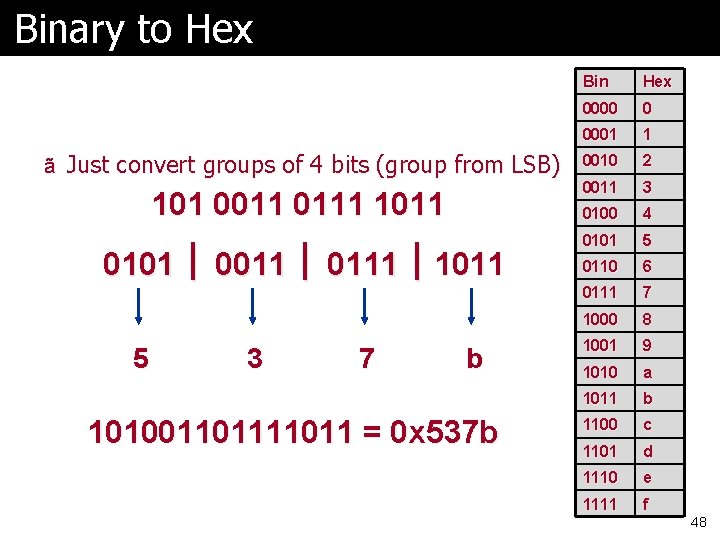

Binary to Hex ã Just convert groups of 4 bits (group from LSB) 101 0011 0111 1011 0101 0011 0111 1011 5 3 7 b 1010011011 = 0 x 537 b Bin Hex 0000 0 0001 1 0010 2 0011 3 0100 4 0101 5 0110 6 0111 7 1000 8 1001 9 1010 a 1011 b 1100 c 1101 d 1110 e 1111 f 48

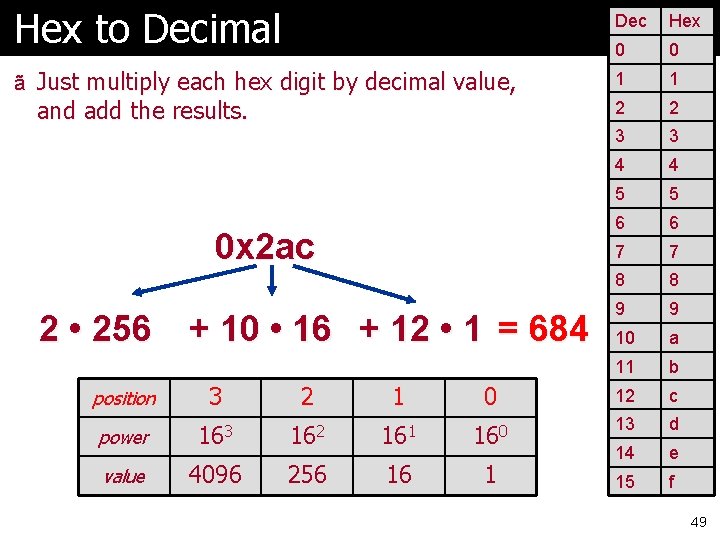

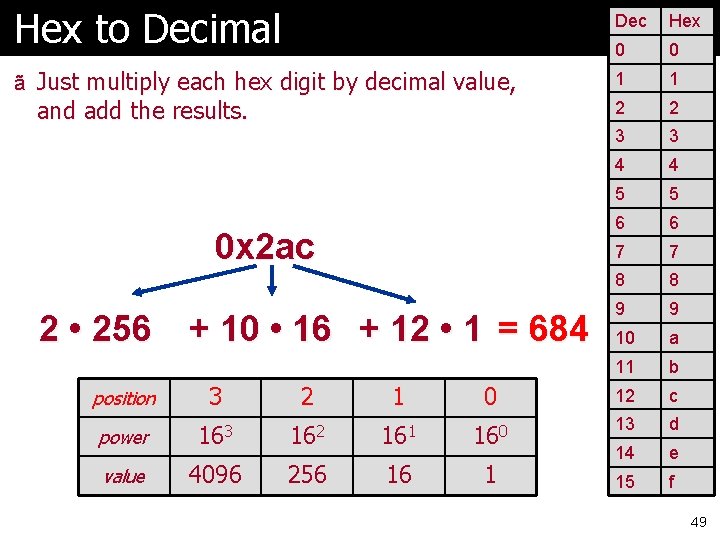

Hex to Decimal Dec Hex 0 0 ã Just multiply each hex digit by decimal value, 1 1 2 2 3 3 4 4 5 5 6 6 7 7 8 8 9 9 10 a 11 b and add the results. 0 x 2 ac 2 • 256 + 10 • 16 + 12 • 1 = 684 position 3 2 1 0 12 c power 163 162 161 160 13 d 256 16 1 e value 4096 14 15 f 49

Decimal to Hex ã Analogous to decimal binary. 1. Find largest power-of-16 smaller than decimal number 2. Divide by power-of-16. The integer result is hex digit. 3. The remainder is new decimal number. 4. Do the same thing again 5

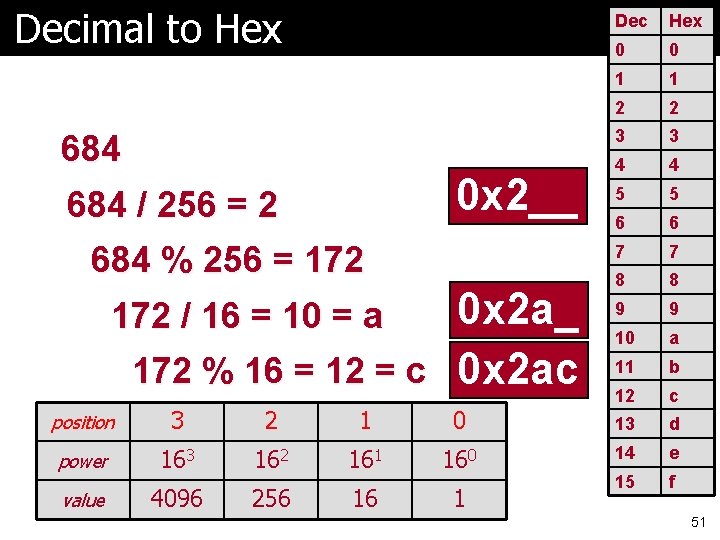

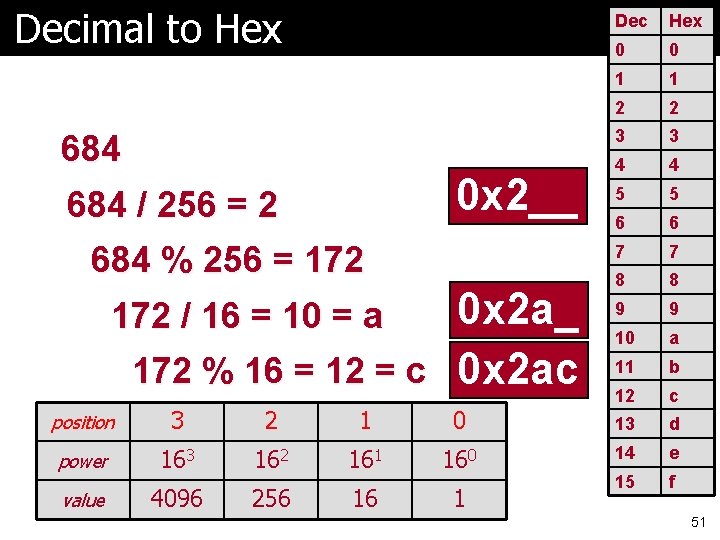

Decimal to Hex 684 0 x 2__ 684 / 256 = 2 684 % 256 = 172 0 x 2 a_ 172 % 16 = 12 = c 0 x 2 ac 172 / 16 = 10 = a Dec Hex 0 0 1 1 2 2 3 3 4 4 5 5 6 6 7 7 8 8 9 9 10 a 11 b 12 c position 3 2 1 0 13 d power 163 162 161 160 14 e 4096 256 16 1 15 f value 51

Decimal to Hex (ver 2) ã Start from the right 1. Divide the number by 16. 2. The remainder is the rightmost hexit. 3. The quotient becomes the new number. 4. Do the same thing again, appending each new hexit to the left 5

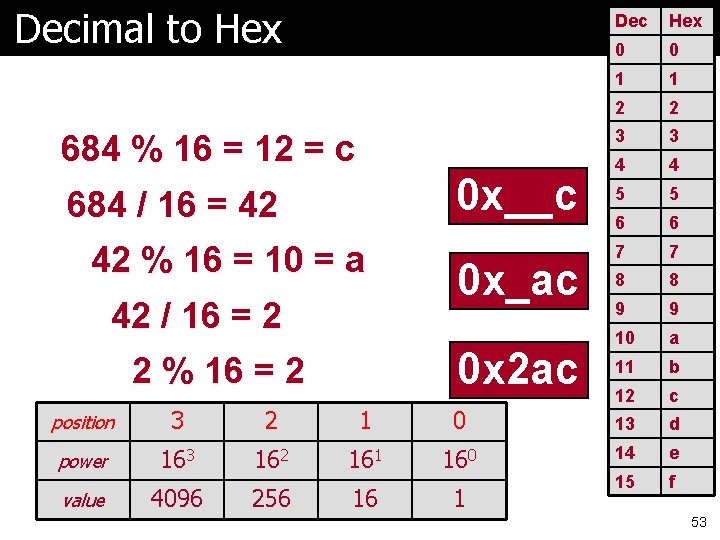

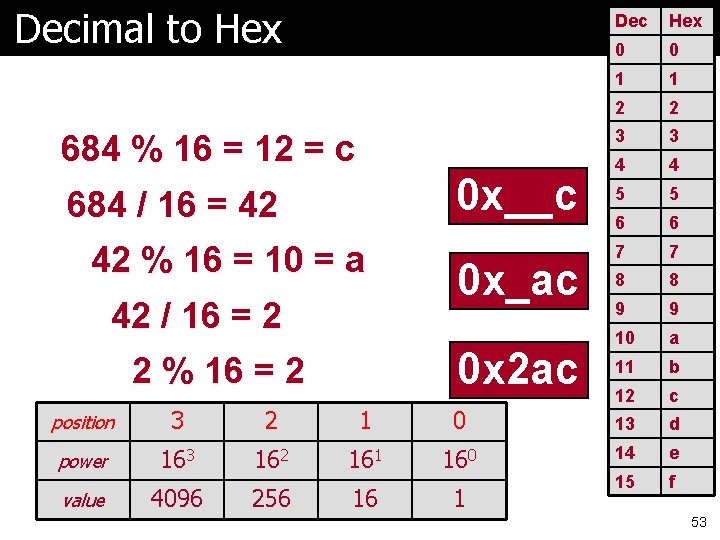

Decimal to Hex 684 % 16 = 12 = c 0 x__c 684 / 16 = 42 42 % 16 = 10 = a 42 / 16 = 2 0 x_ac 0 x 2 ac 2 % 16 = 2 Dec Hex 0 0 1 1 2 2 3 3 4 4 5 5 6 6 7 7 8 8 9 9 10 a 11 b 12 c position 3 2 1 0 13 d power 163 162 161 160 14 e 4096 256 16 1 15 f value 53

Octal ã Octal is base 8 ã Similar to hexadecimal l Conversions ã Less convenient for use with 8 -bit bytes 54

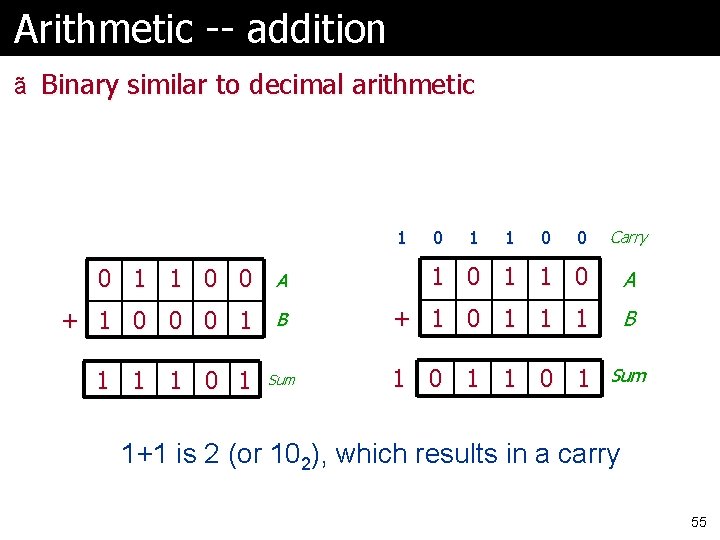

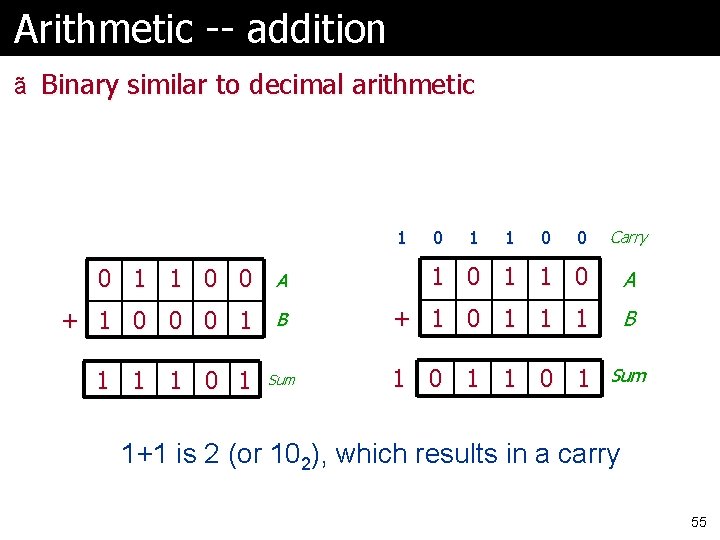

Arithmetic -- addition ã Binary similar to decimal arithmetic 1 No carries 0 1 1 0 0 Carry 0 1 1 0 0 A 1 0 1 1 0 A + 1 0 0 0 1 B + 1 0 1 1 1 B Sum 1 0 1 Sum 1 1 1 0 1 1+1 is 2 (or 102), which results in a carry 55

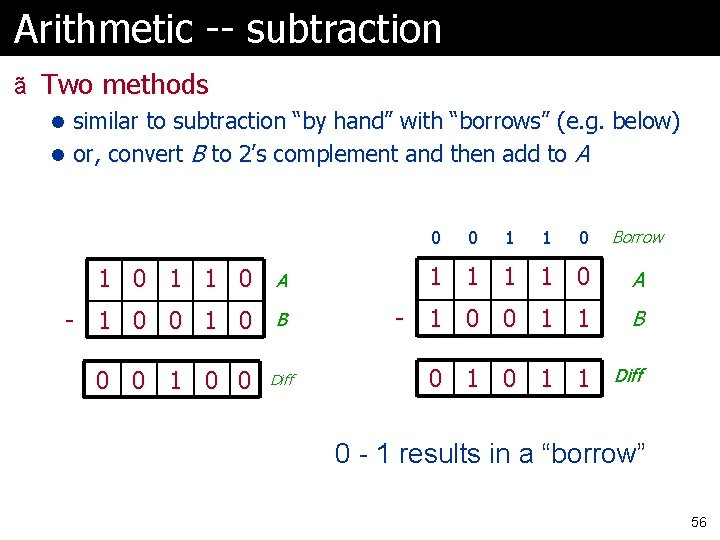

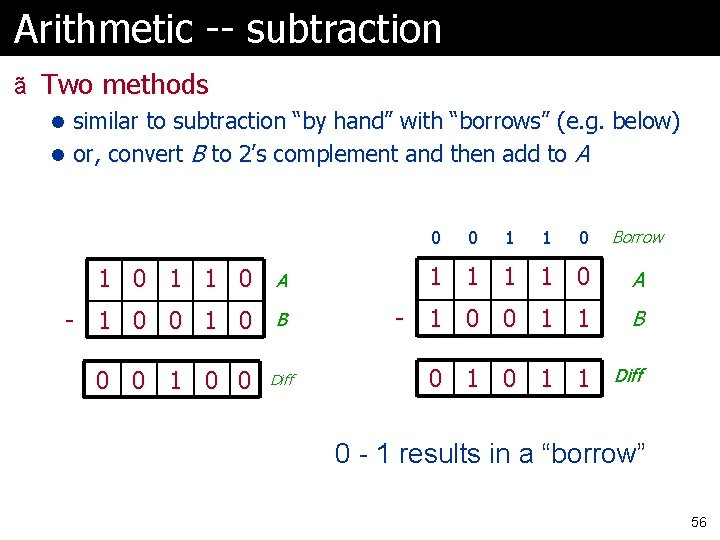

Arithmetic -- subtraction ã Two methods l similar to subtraction “by hand” with “borrows” (e. g. below) l or, convert B to 2’s complement and then add to A 0 No carries 1 0 1 1 0 A - 1 0 0 1 0 B 0 0 1 0 0 Diff - 0 1 1 0 Borrow 1 1 0 A 1 0 0 1 1 B 0 1 1 Diff 0 - 1 results in a “borrow” 56

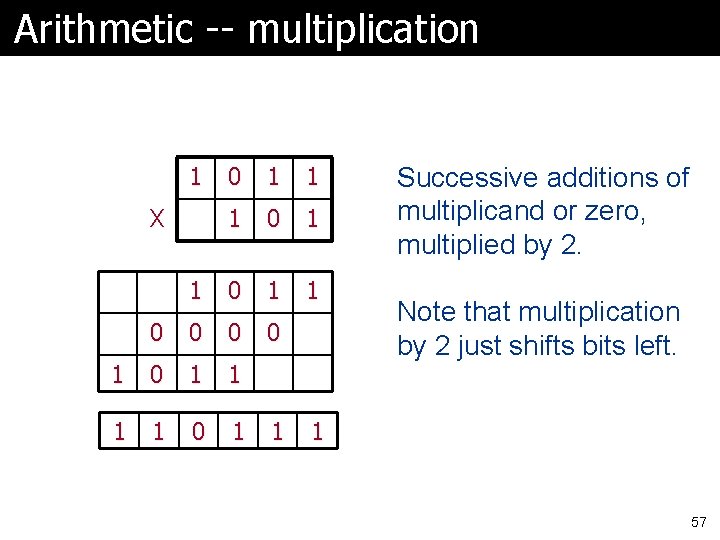

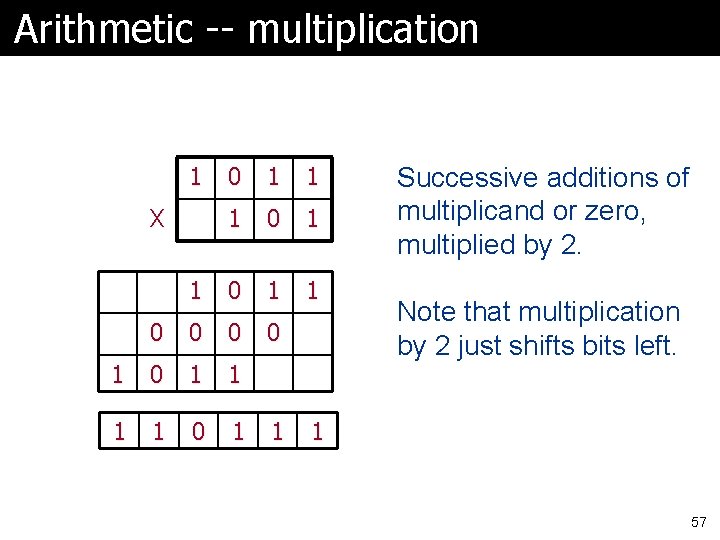

Arithmetic -- multiplication 1 0 1 1 0 0 1 0 1 X 1 Successive additions of multiplicand or zero, multiplied by 2. Note that multiplication by 2 just shifts bits left. 1 57