COMP 541 Combinational Logic I Montek Singh Jan

COMP 541 Combinational Logic - I Montek Singh Jan 14, 2010 1

Today ã Basics of digital logic (review) l Basic functions l Boolean algebra l Gates to implement Boolean functions 2

Binary Logic ã Binary variables l Can be 0 or 1 (T or F, low or high) l Variables named with single letters in examples l Really use words when designing circuits 3

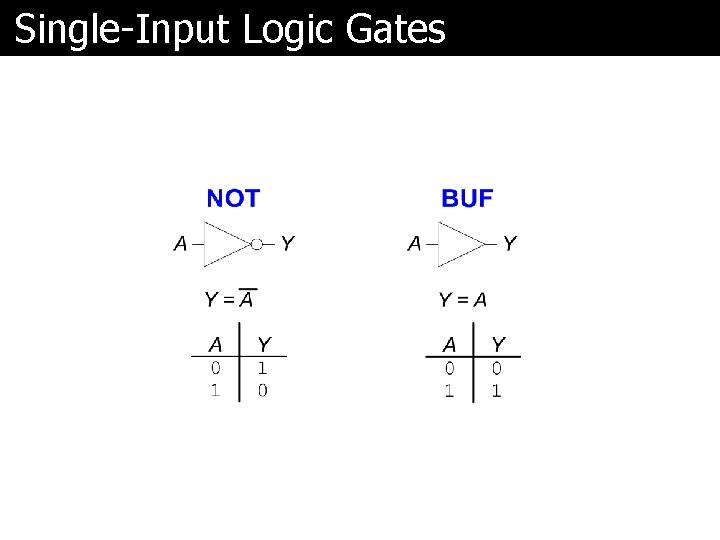

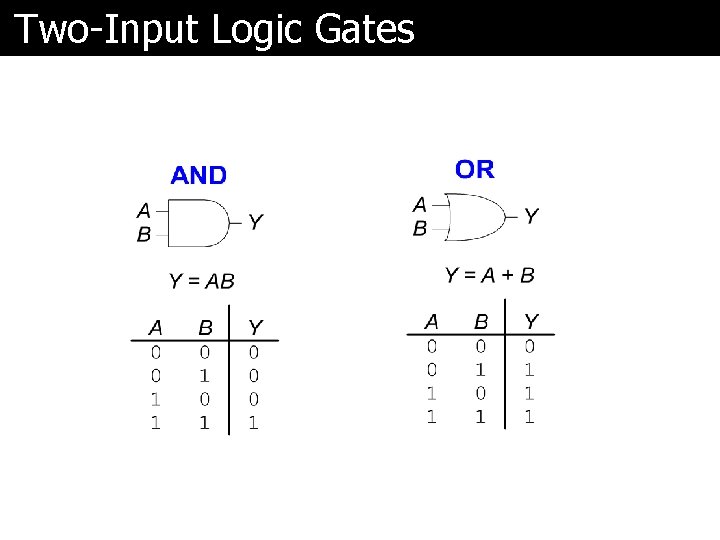

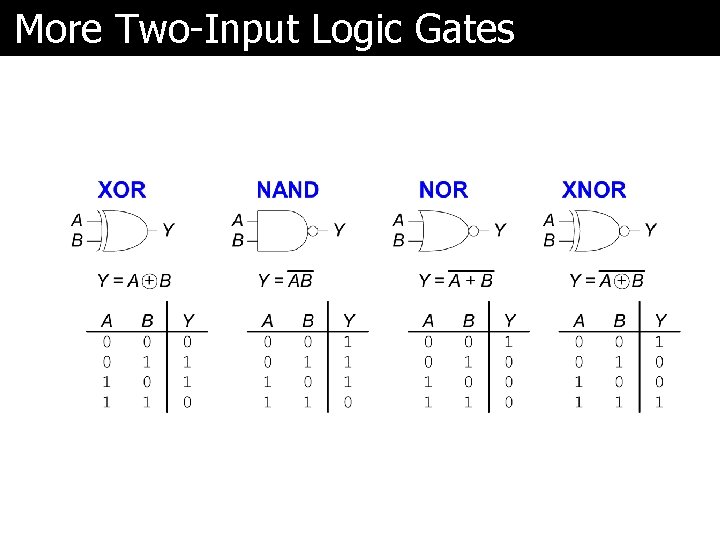

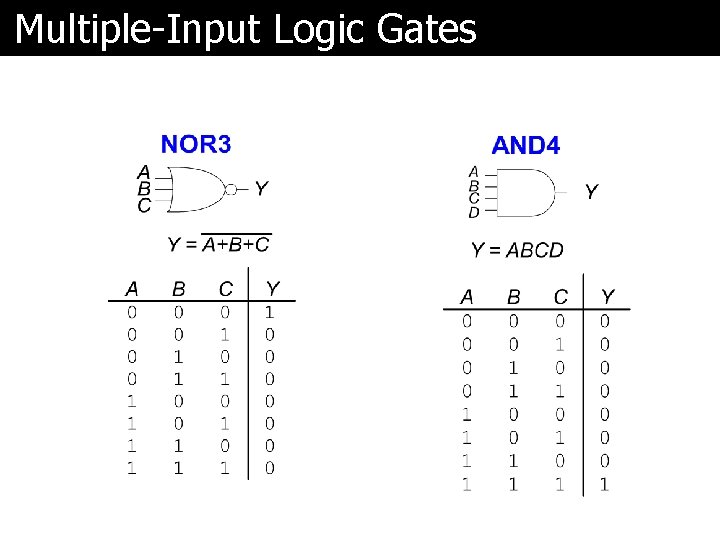

Logic Gates ã Perform logic functions: l inversion (NOT), AND, OR, NAND, NOR, etc. ã Single-input: l NOT gate, buffer ã Two-input: l AND, OR, XOR, NAND, NOR, XNOR ã Multiple-input

Single-Input Logic Gates

Two-Input Logic Gates

More Two-Input Logic Gates

Multiple-Input Logic Gates

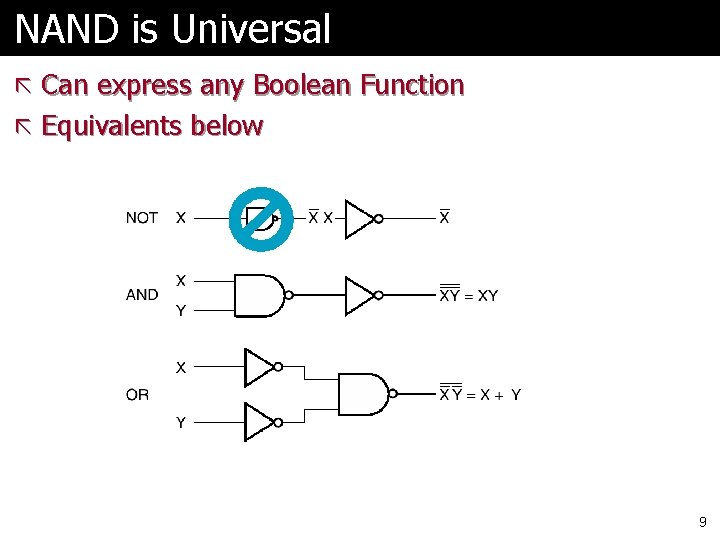

NAND is Universal ã Can express any Boolean Function ã Equivalents below 9

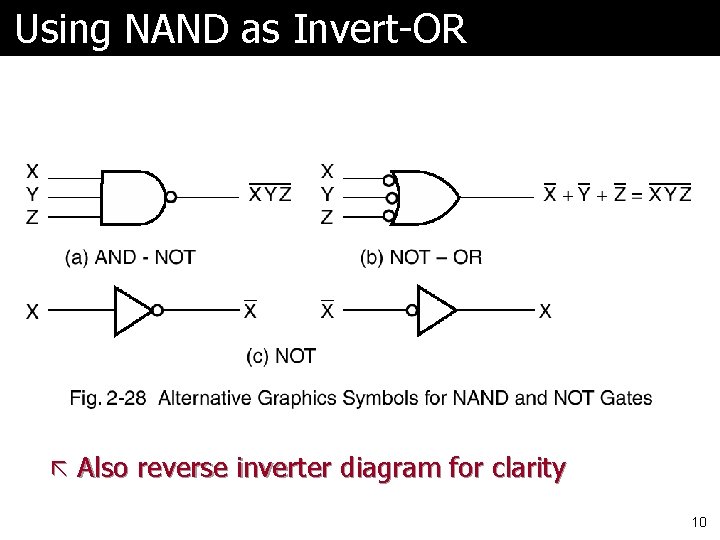

Using NAND as Invert-OR ã Also reverse inverter diagram for clarity 10

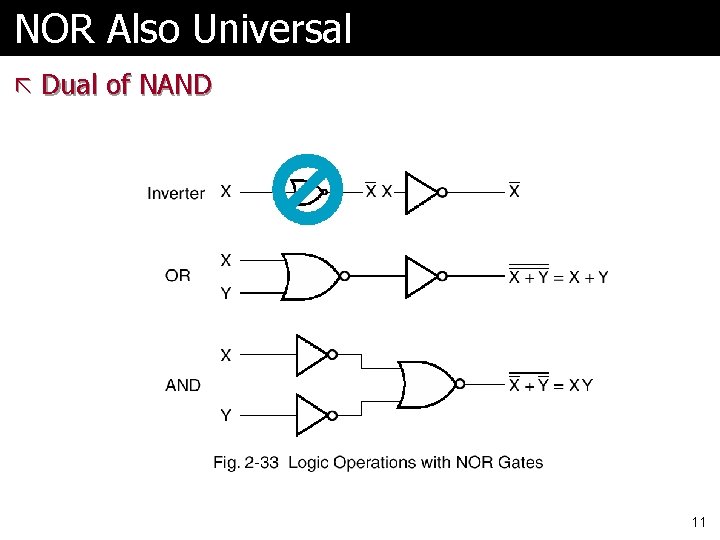

NOR Also Universal ã Dual of NAND 11

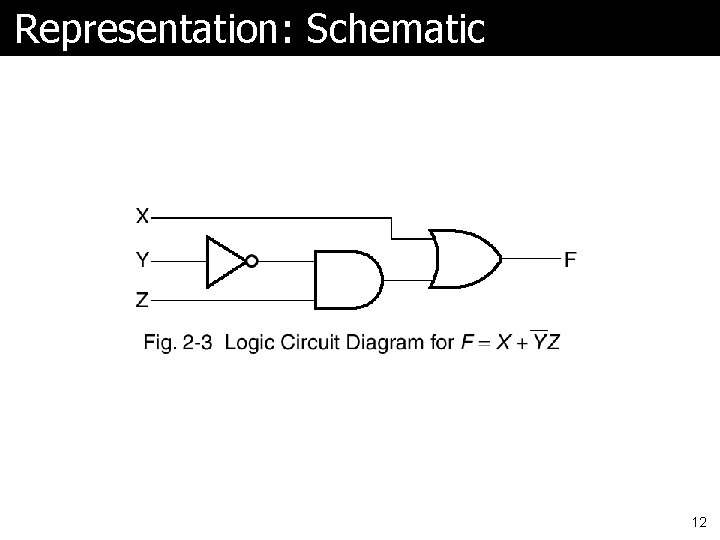

Representation: Schematic 12

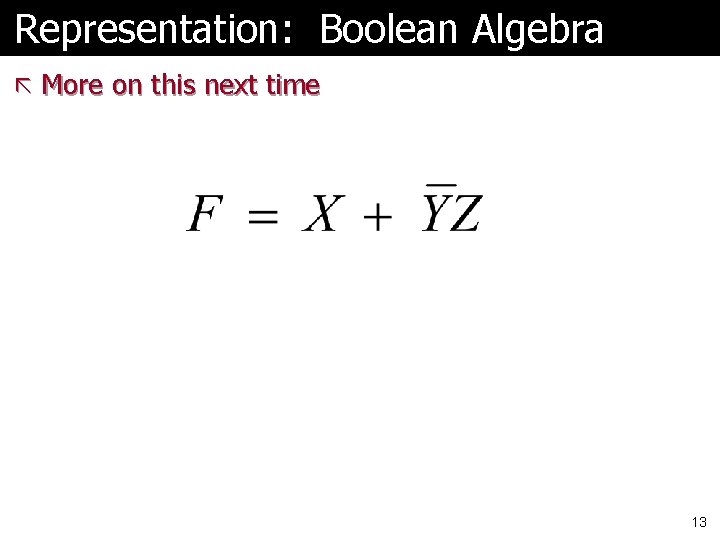

Representation: Boolean Algebra ã More on this next time 13

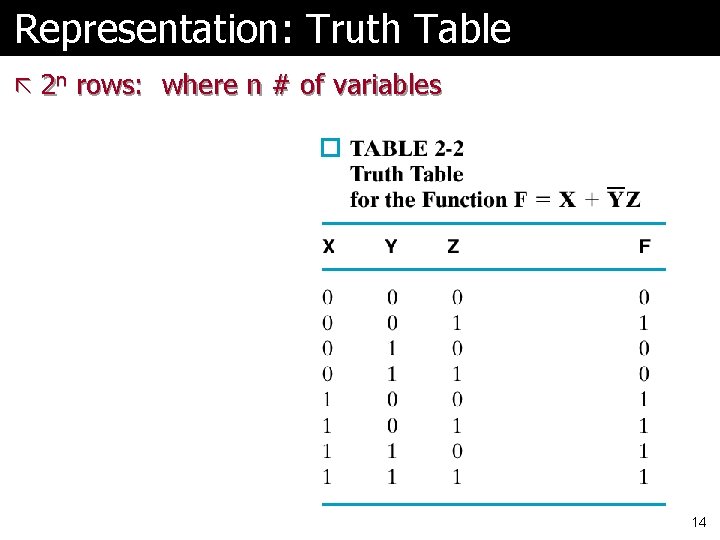

Representation: Truth Table ã 2 n rows: where n # of variables 14

Schematic Diagrams ã Can you design a Pentium or a graphics chip that way? l Well, yes, but diagrams are overly complex and hard to enter ã These days people represent the same thing with text (code) 15

Hardware Description Languages ã Main ones are Verilog and VHDL l Others: Abel, System. C, Handel ã Origins as testing languages l To generate sets of input values ã Levels of use from very detailed to more abstract descriptions of hdw l Think about C++ from assembly level description to very abstract HLL 16

Design w/ HDL ã Two leading HDLs: l Verilog Ø developed in 1984 by Gateway Design Automation Ø became an IEEE standard (1364) in 1995 l VHDL Ø Developed in 1981 by the Department of Defense Ø Became an IEEE standard (1076) in 1987 ã Most (all? ) commercial designs built using HDLs ã We’ll use Verilog

Uses of HDL ã Simulation l Defines input values are applied to the circuit l Outputs checked for correctness l Millions of dollars saved by debugging in simulation instead of hardware ã Synthesis l Transforms HDL code into a netlist describing the hardware (i. e. , a list of gates and the wires connecting them) IMPORTANT: l When describing circuits using an HDL, it’s critical to think of the hardware the code should produce.

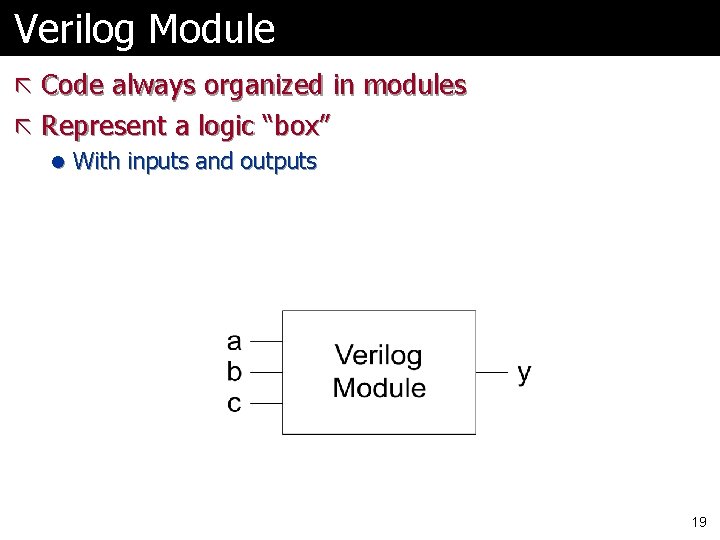

Verilog Module ã Code always organized in modules ã Represent a logic “box” l With inputs and outputs 19

Example module example(input a, b, c, output y); *** HDL CODE HERE *** endmodule 20

Levels of Verilog Several different levels (or “views”) l Structural l Dataflow l Conditional l Behavioral Look at first three today 21

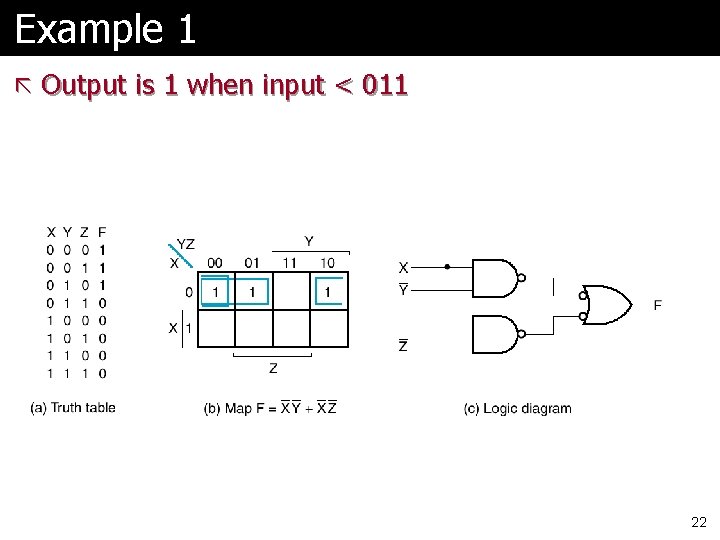

Example 1 ã Output is 1 when input < 011 22

Structural Verilog ã Explicit description of gates and connections ã Textual form of schematic ã Specifying netlist 23

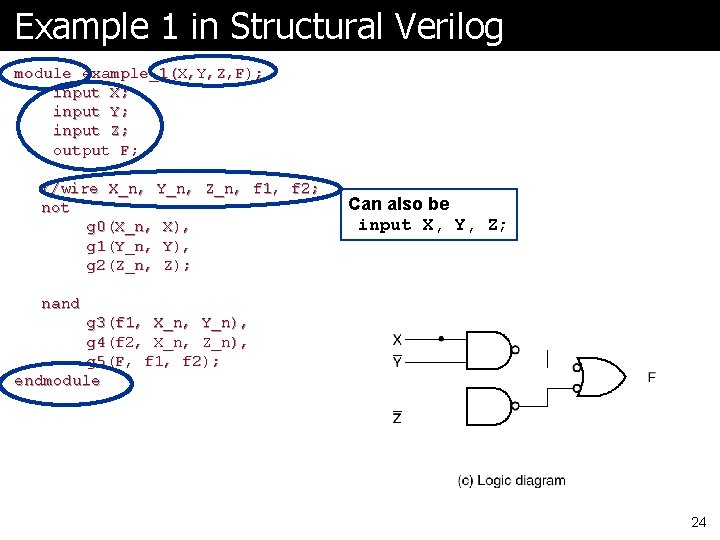

Example 1 in Structural Verilog module example_1(X, Y, Z, F); input X; input Y; input Z; output F; //wire X_n, Y_n, Z_n, f 1, f 2; not g 0(X_n, X), g 1(Y_n, Y), g 2(Z_n, Z); Can also be input X, Y, Z; nand g 3(f 1, X_n, Y_n), g 4(f 2, X_n, Z_n), g 5(F, f 1, f 2); endmodule 24

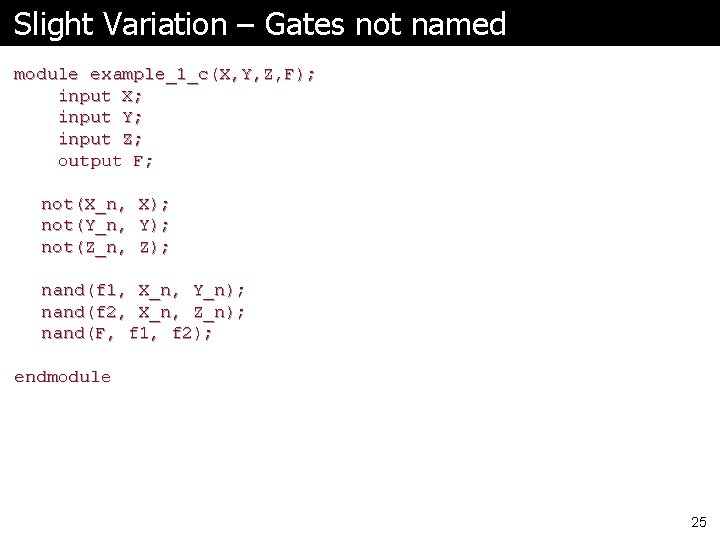

Slight Variation – Gates not named module example_1_c(X, Y, Z, F); input X; input Y; input Z; output F; not(X_n, X); not(Y_n, Y); not(Z_n, Z); nand(f 1, X_n, Y_n); nand(f 2, X_n, Z_n); nand(F, f 1, f 2); endmodule 25

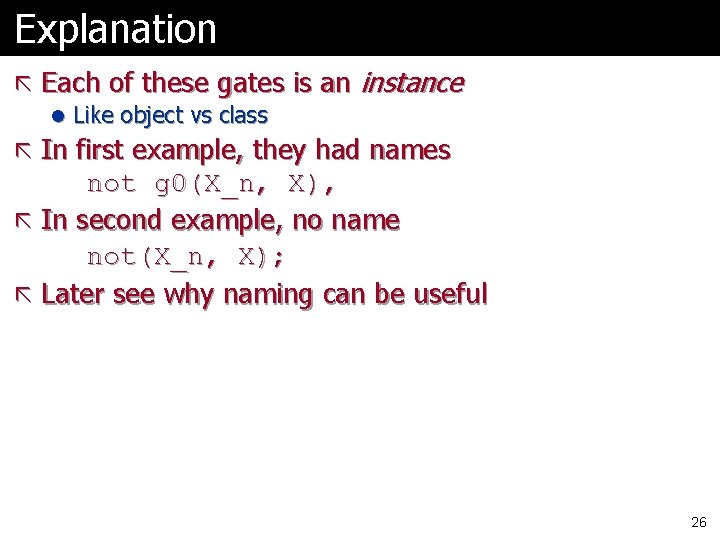

Explanation ã Each of these gates is an instance l Like object vs class ã In first example, they had names not g 0(X_n, X), ã In second example, no name not(X_n, X); ã Later see why naming can be useful 26

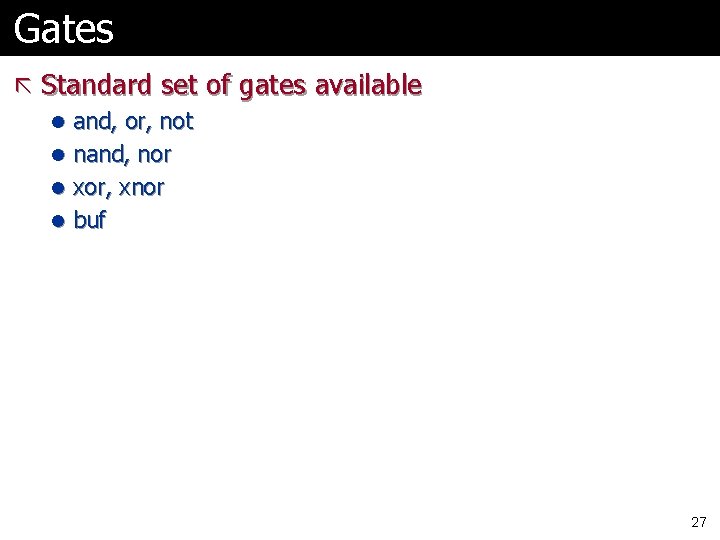

Gates ã Standard set of gates available l and, or, not l nand, nor l xor, xnor l buf 27

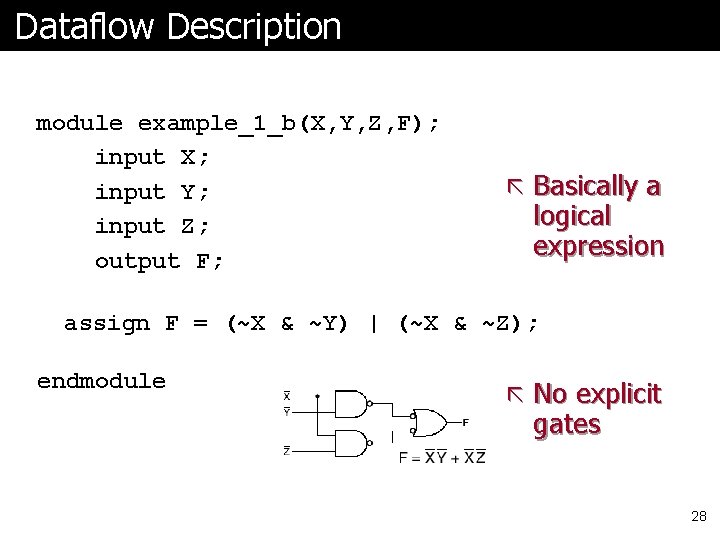

Dataflow Description module example_1_b(X, Y, Z, F); input X; input Y; input Z; output F; ã Basically a logical expression assign F = (~X & ~Y) | (~X & ~Z); endmodule ã No explicit gates 28

![Conditional Description module example_1_c(input [2: 0] A, output F); Notice alternate specification assign F Conditional Description module example_1_c(input [2: 0] A, output F); Notice alternate specification assign F](http://slidetodoc.com/presentation_image_h/277bfaa0d162c3ac373ce67b90796e21/image-29.jpg)

Conditional Description module example_1_c(input [2: 0] A, output F); Notice alternate specification assign F = (A > 3’b 011) ? 0 : 1; endmodule 29

Abstraction ã Using the digital abstraction we’ve been thinking of the inputs and outputs as l True or False l 1 or 0 ã What are they really? 30

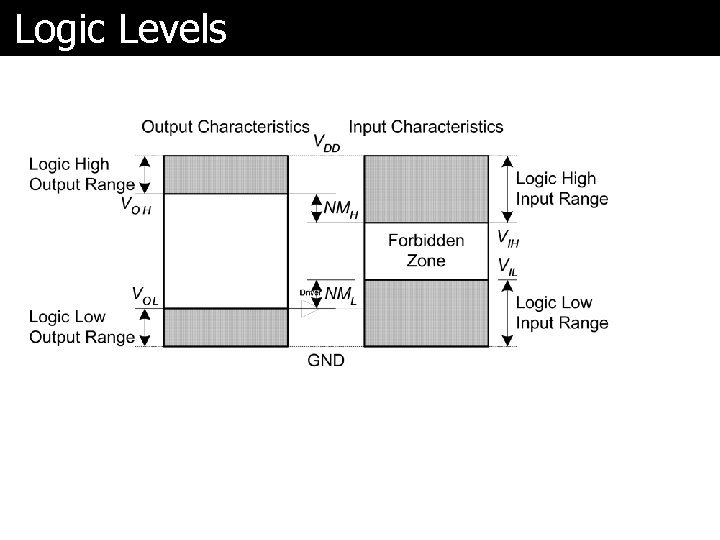

Logic Levels ã Define discrete voltages to represent 1 and 0 ã For example, we could define: l 0 to be ground or 0 volts l 1 to be VDD or 5 volts ã What about 4. 99 volts? Is that a 0 or a 1? ã What about 3. 2 volts?

Logic Levels ã Define a range of voltages to represent 1 and 0 ã Define different ranges for outputs and inputs to allow for noise in the system ã What is noise?

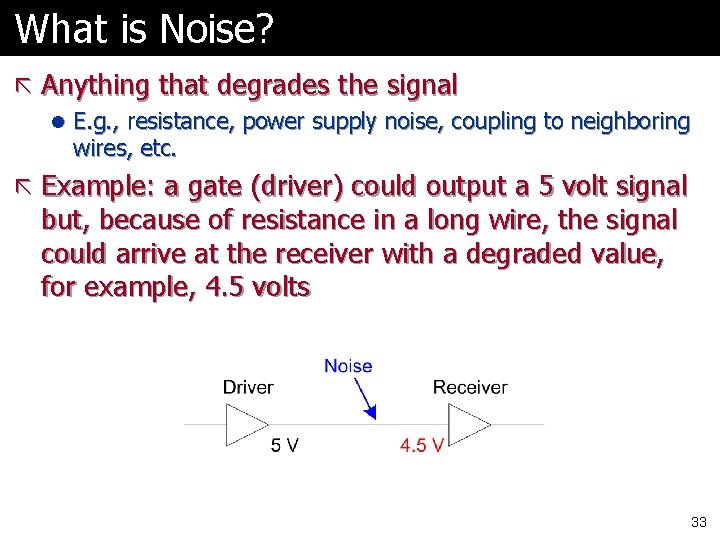

What is Noise? ã Anything that degrades the signal l E. g. , resistance, power supply noise, coupling to neighboring wires, etc. ã Example: a gate (driver) could output a 5 volt signal but, because of resistance in a long wire, the signal could arrive at the receiver with a degraded value, for example, 4. 5 volts 33

The Static Discipline ã Given logically valid inputs, every circuit element must produce logically valid outputs ã Discipline ourselves to use limited ranges of voltages to represent discrete values

Logic Levels

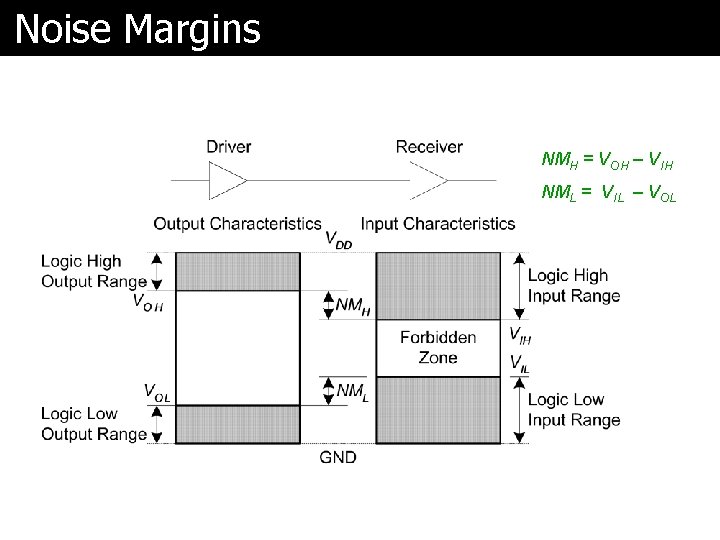

Noise Margins NMH = VOH – VIH NML = VIL – VOL

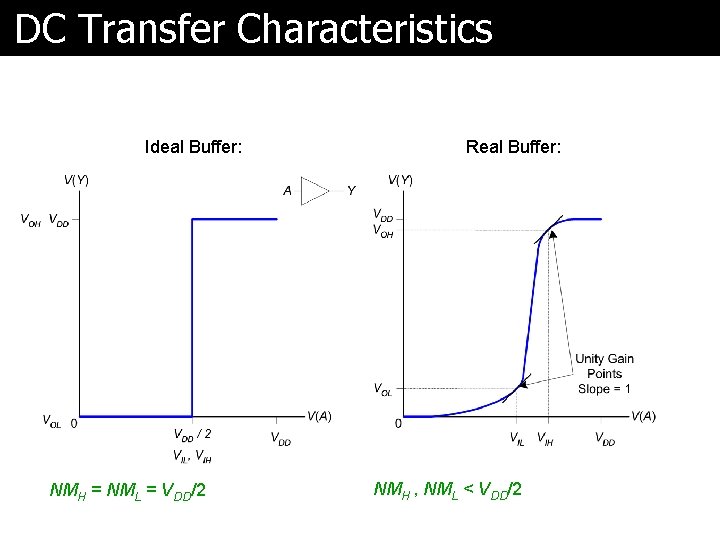

DC Transfer Characteristics Ideal Buffer: NMH = NML = VDD/2 Real Buffer: NMH , NML < VDD/2

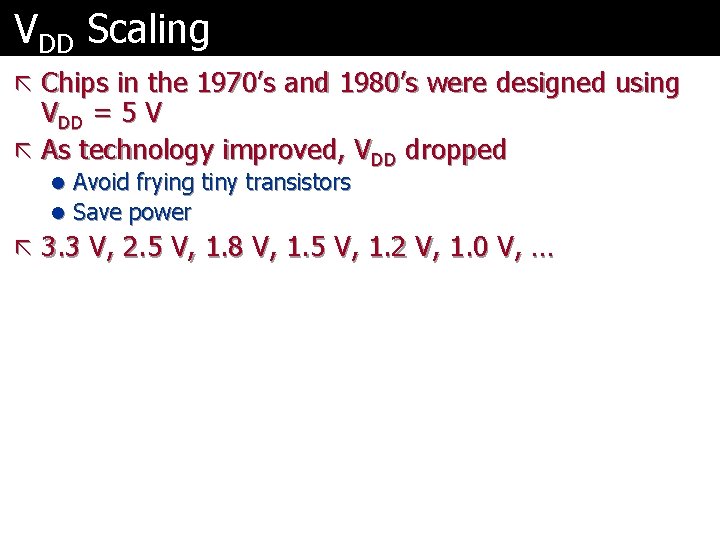

VDD Scaling ã Chips in the 1970’s and 1980’s were designed using VDD = 5 V ã As technology improved, VDD dropped l Avoid frying tiny transistors l Save power ã 3. 3 V, 2. 5 V, 1. 8 V, 1. 5 V, 1. 2 V, 1. 0 V, …

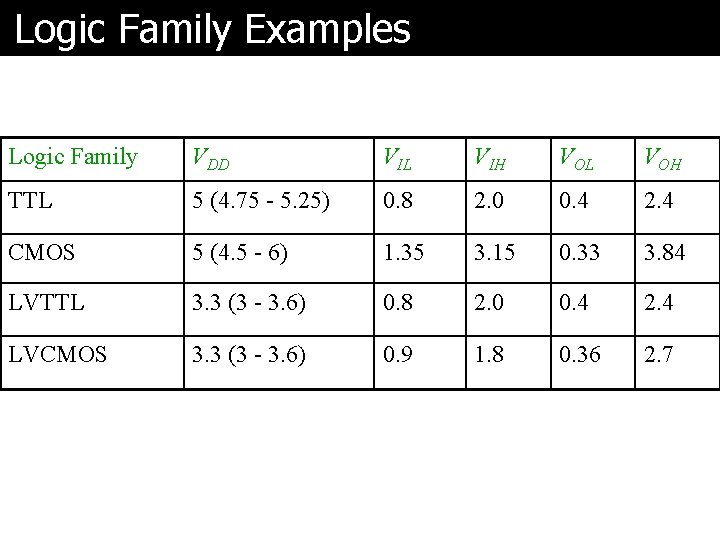

Logic Family Examples Logic Family VDD VIL VIH VOL VOH TTL 5 (4. 75 - 5. 25) 0. 8 2. 0 0. 4 2. 4 CMOS 5 (4. 5 - 6) 1. 35 3. 15 0. 33 3. 84 LVTTL 3. 3 (3 - 3. 6) 0. 8 2. 0 0. 4 2. 4 LVCMOS 3. 3 (3 - 3. 6) 0. 9 1. 8 0. 36 2. 7

Reading ã Textbook Ch. 2. 1 – 2. 6 40

- Slides: 40