Important Components Blocks and Methodologies To remember 1

Important Components, Blocks and Methodologies

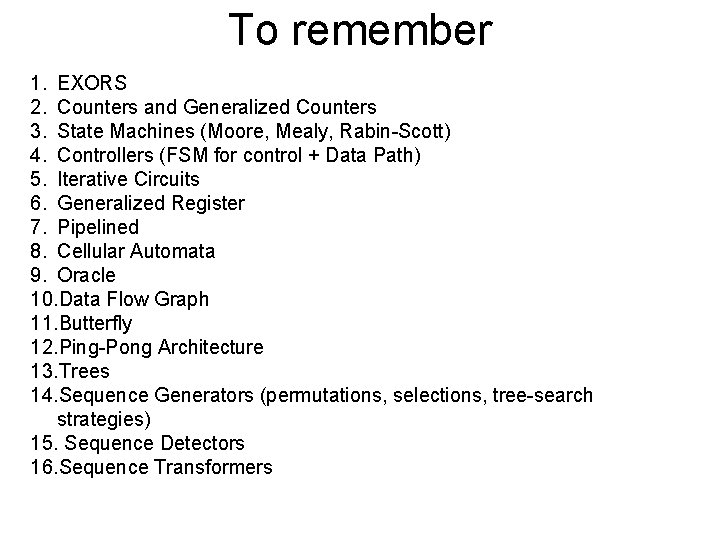

To remember 1. EXORS 2. Counters and Generalized Counters 3. State Machines (Moore, Mealy, Rabin-Scott) 4. Controllers (FSM for control + Data Path) 5. Iterative Circuits 6. Generalized Register 7. Pipelined 8. Cellular Automata 9. Oracle 10. Data Flow Graph 11. Butterfly 12. Ping-Pong Architecture 13. Trees 14. Sequence Generators (permutations, selections, tree-search strategies) 15. Sequence Detectors 16. Sequence Transformers

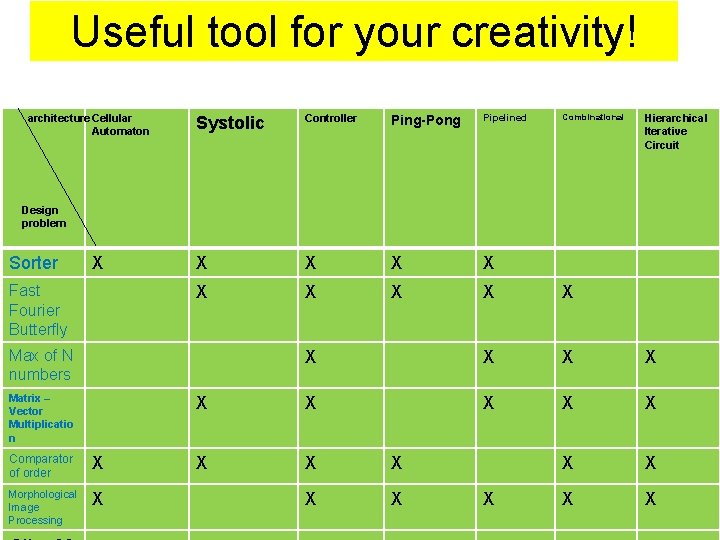

Useful tool for your creativity! architecture Cellular Automaton Combinational Systolic Controller Ping-Pong Pipelined X X X X X X X Hierarchical Iterative Circuit Design problem Sorter X Fast Fourier Butterfly Max of N numbers Matrix – Vector Multiplicatio n Comparator of order X Morphological Image Processing X X

XORs and XNORs

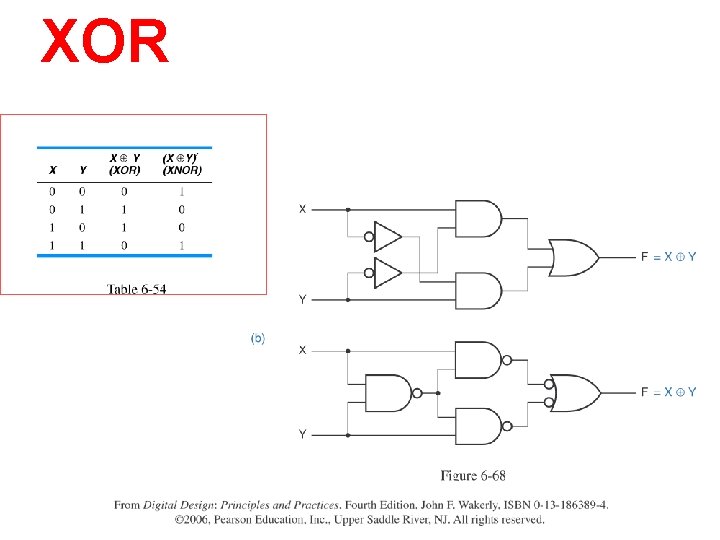

XOR

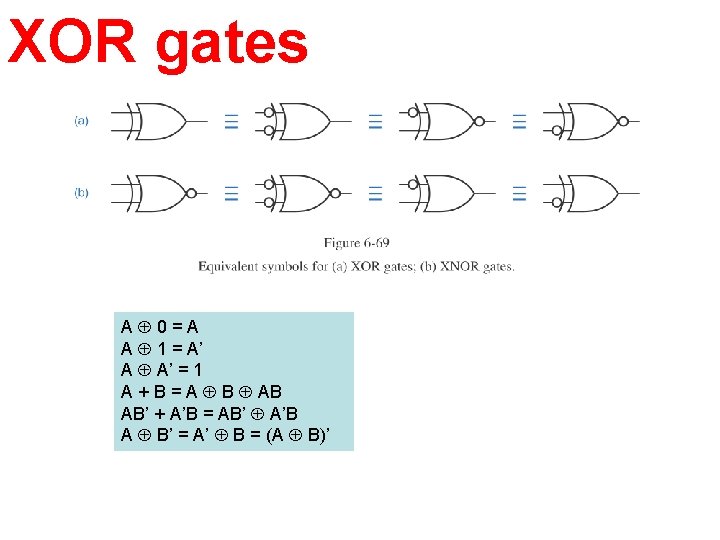

XOR gates A 0=A A 1 = A’ A A’ = 1 A + B = A B AB AB’ + A’B = AB’ A’B A B’ = A’ B = (A B)’

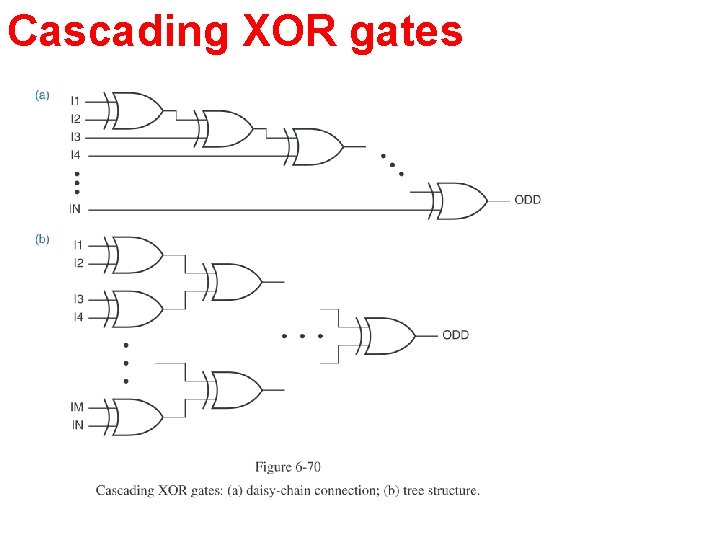

Cascading XOR gates

Parity Generation

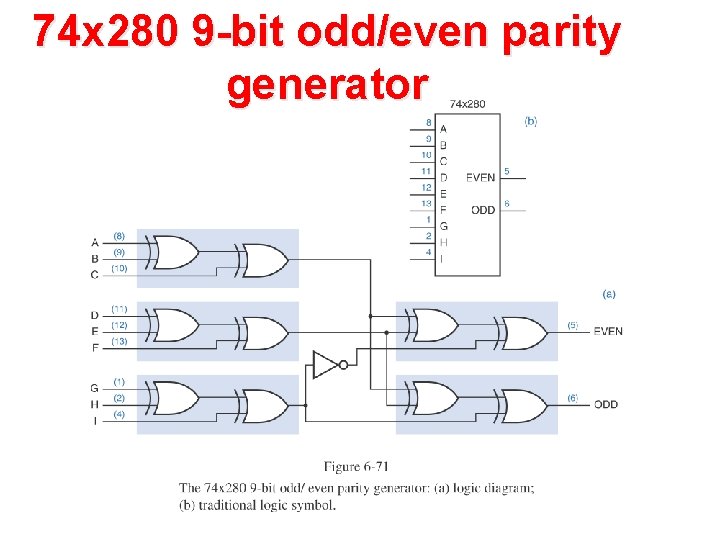

74 x 280 9 -bit odd/even parity generator

Tree and Iterative circuits

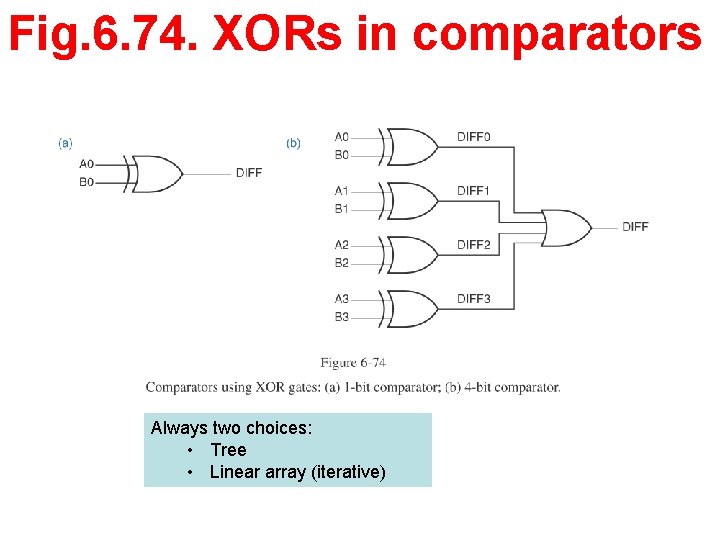

Fig. 6. 74. XORs in comparators Always two choices: • Tree • Linear array (iterative)

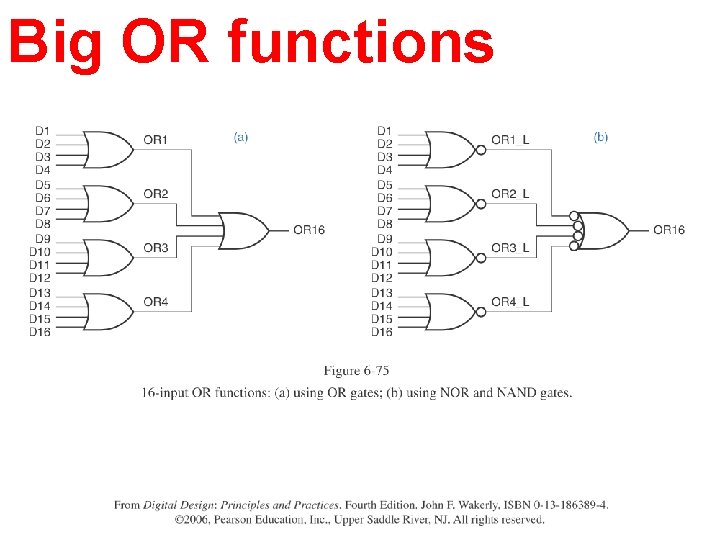

Big OR functions

Sequence Detectors

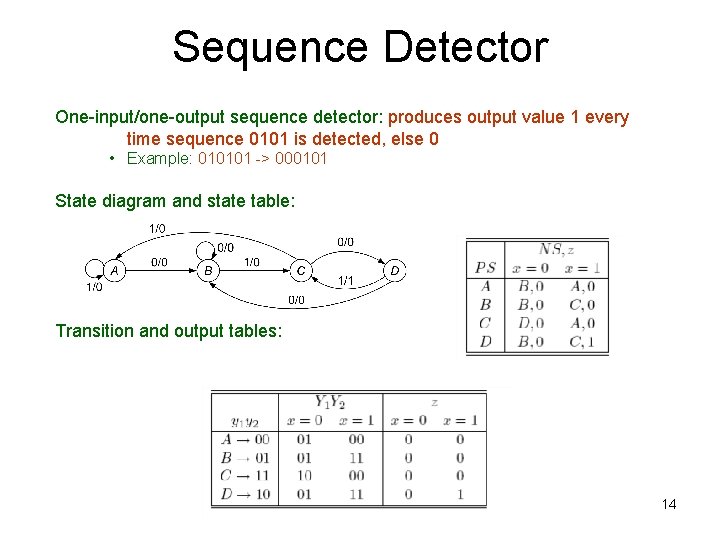

Sequence Detector One-input/one-output sequence detector: produces output value 1 every time sequence 0101 is detected, else 0 • Example: 010101 -> 000101 State diagram and state table: Transition and output tables: 14

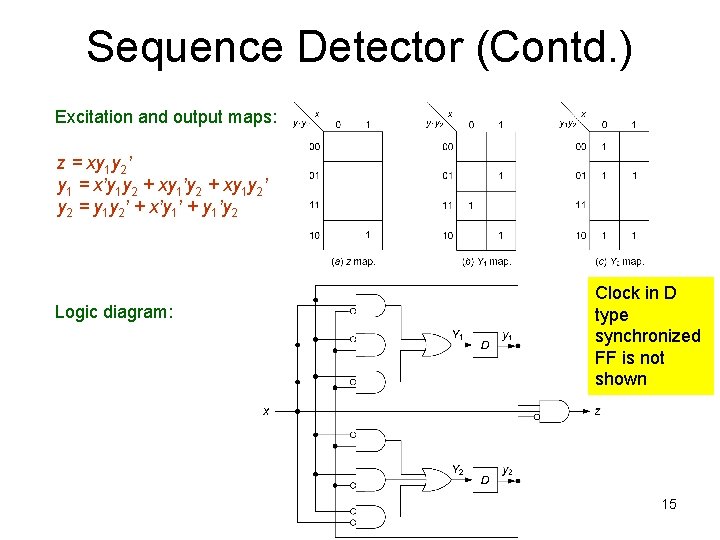

Sequence Detector (Contd. ) Excitation and output maps: z = xy 1 y 2’ y 1 = x’y 1 y 2 + xy 1’y 2 + xy 1 y 2’ y 2 = y 1 y 2’ + x’y 1’ + y 1’y 2 Logic diagram: Clock in D type synchronized FF is not shown 15

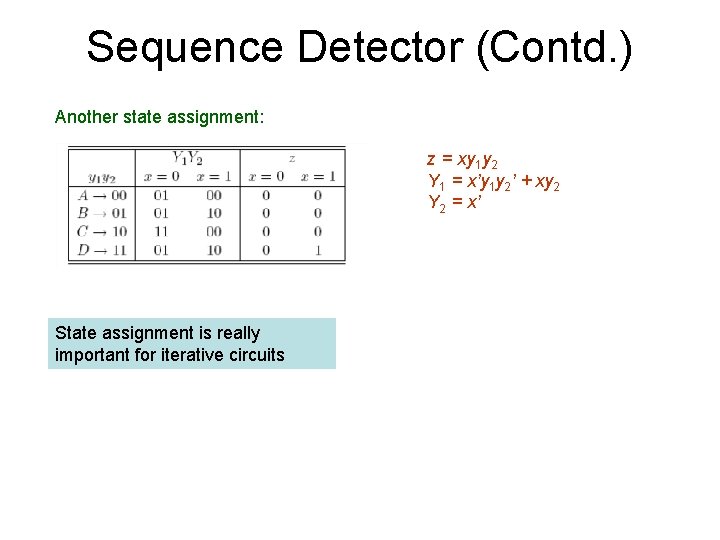

Sequence Detector (Contd. ) Another state assignment: z = xy 1 y 2 Y 1 = x’y 1 y 2’ + xy 2 Y 2 = x’ State assignment is really important for iterative circuits

Big Counters

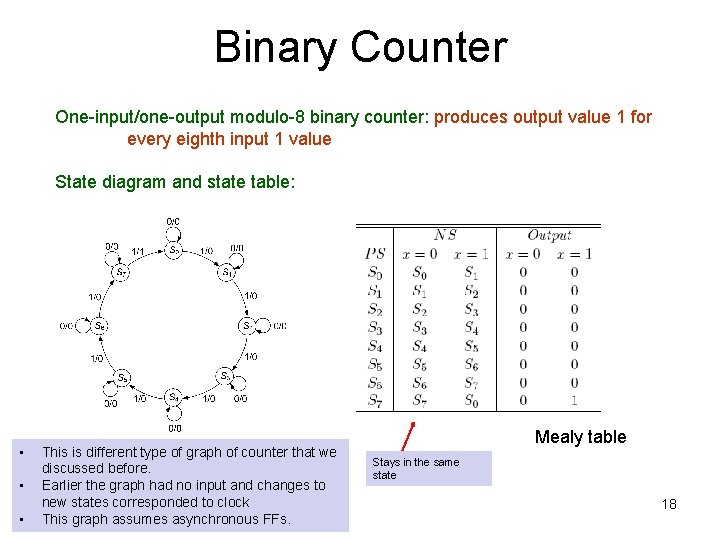

Binary Counter One-input/one-output modulo-8 binary counter: produces output value 1 for every eighth input 1 value State diagram and state table: • • • This is different type of graph of counter that we discussed before. Earlier the graph had no input and changes to new states corresponded to clock This graph assumes asynchronous FFs. Mealy table Stays in the same state 18

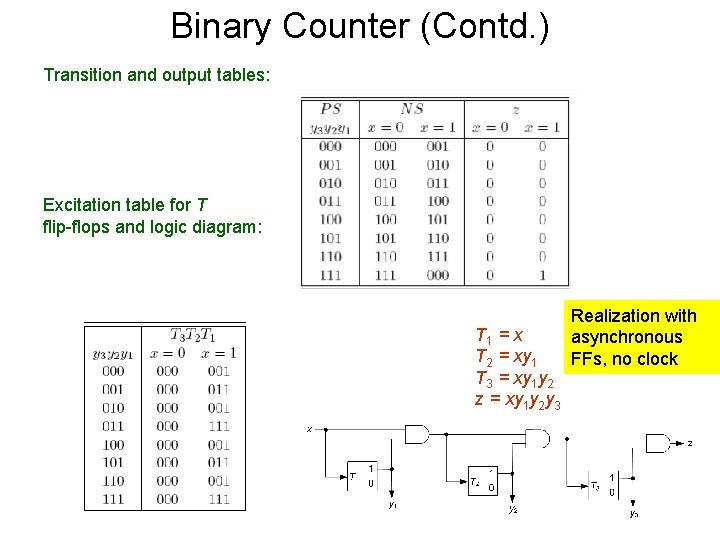

Binary Counter (Contd. ) Transition and output tables: Excitation table for T flip-flops and logic diagram: T 1 = x T 2 = xy 1 T 3 = xy 1 y 2 z = xy 1 y 2 y 3 Realization with asynchronous FFs, no clock

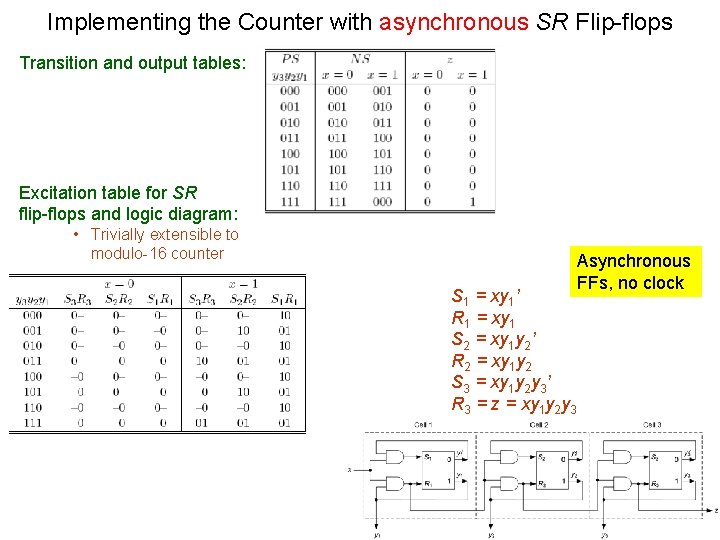

Implementing the Counter with asynchronous SR Flip-flops Transition and output tables: Excitation table for SR flip-flops and logic diagram: • Trivially extensible to modulo-16 counter S 1 = xy 1’ R 1 = xy 1 S 2 = xy 1 y 2’ R 2 = xy 1 y 2 S 3 = xy 1 y 2 y 3’ R 3 = z = xy 1 y 2 y 3 Asynchronous FFs, no clock

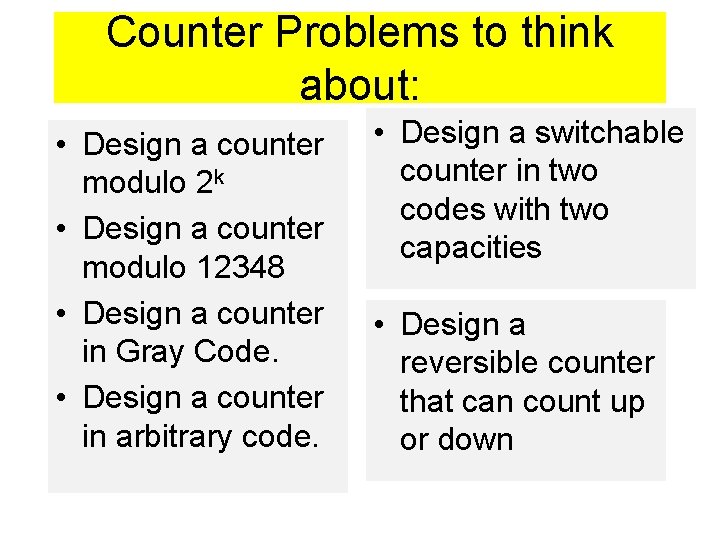

Counter Problems to think about: • Design a counter modulo 2 k • Design a counter modulo 12348 • Design a counter in Gray Code. • Design a counter in arbitrary code. • Design a switchable counter in two codes with two capacities • Design a reversible counter that can count up or down

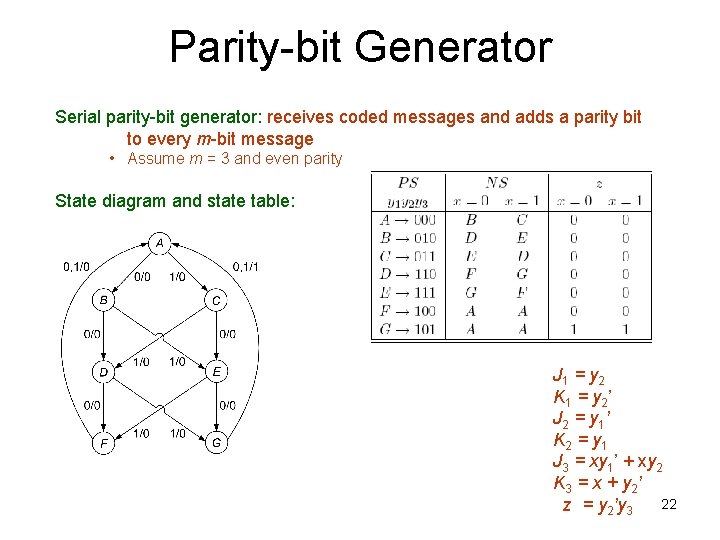

Parity-bit Generator Serial parity-bit generator: receives coded messages and adds a parity bit to every m-bit message • Assume m = 3 and even parity State diagram and state table: J 1 = y 2 K 1 = y 2’ J 2 = y 1’ K 2 = y 1 J 3 = xy 1’ + xy 2 K 3 = x + y 2’ 22 z = y 2’y 3

Controllers = (FSM+Data. Path)

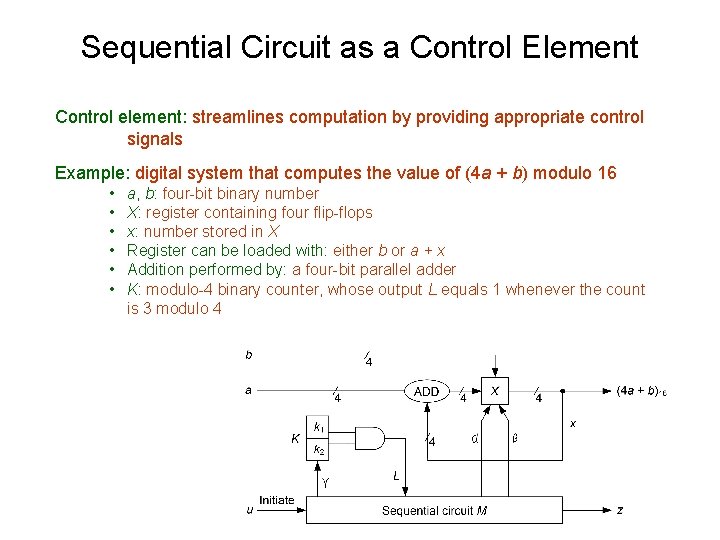

Sequential Circuit as a Control Element Control element: streamlines computation by providing appropriate control signals Example: digital system that computes the value of (4 a + b) modulo 16 • • • a, b: four-bit binary number X: register containing four flip-flops x: number stored in X Register can be loaded with: either b or a + x Addition performed by: a four-bit parallel adder K: modulo-4 binary counter, whose output L equals 1 whenever the count is 3 modulo 4

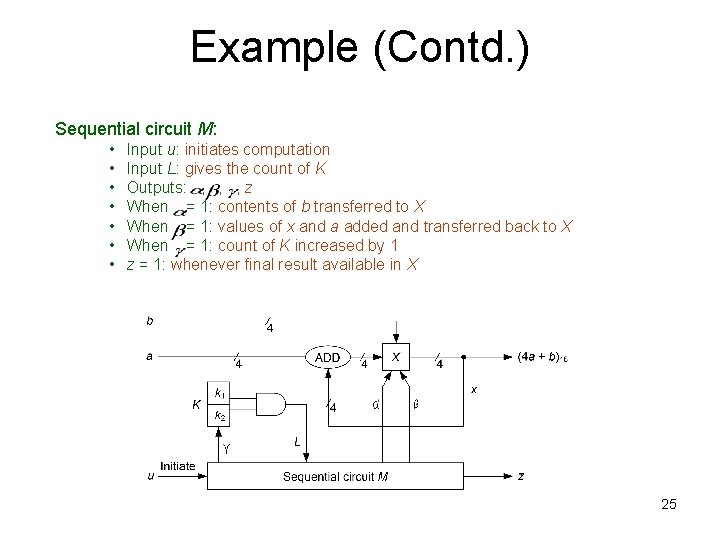

Example (Contd. ) Sequential circuit M: • • Input u: initiates computation Input L: gives the count of K Outputs: , , , z When = 1: contents of b transferred to X When = 1: values of x and a added and transferred back to X When = 1: count of K increased by 1 z = 1: whenever final result available in X 25

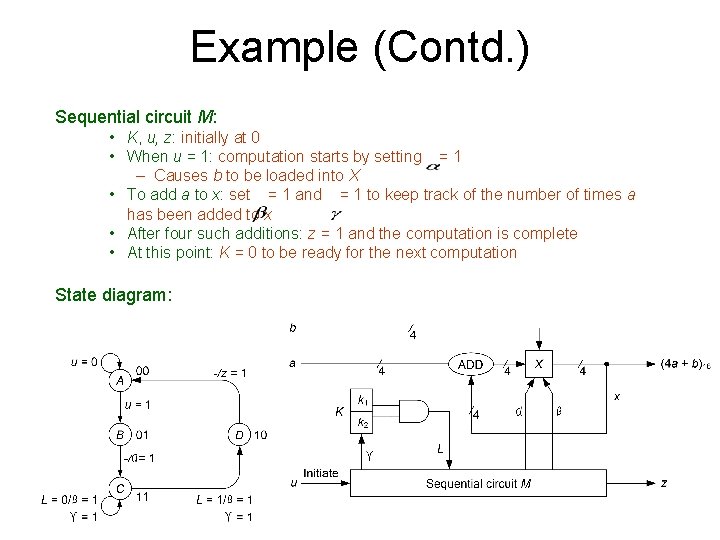

Example (Contd. ) Sequential circuit M: • K, u, z: initially at 0 • When u = 1: computation starts by setting = 1 – Causes b to be loaded into X • To add a to x: set = 1 and = 1 to keep track of the number of times a has been added to x • After four such additions: z = 1 and the computation is complete • At this point: K = 0 to be ready for the next computation State diagram:

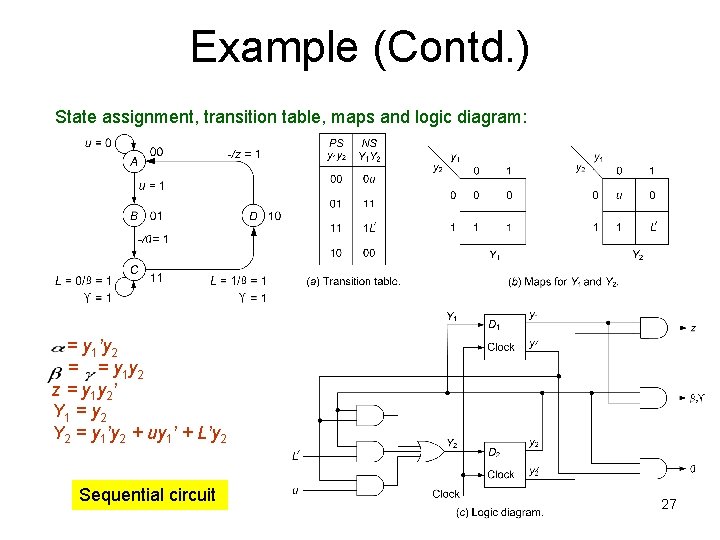

Example (Contd. ) State assignment, transition table, maps and logic diagram: = y 1’y 2 = = y 1 y 2 z = y 1 y 2’ Y 1 = y 2 Y 2 = y 1’y 2 + uy 1’ + L’y 2 Sequential circuit 27

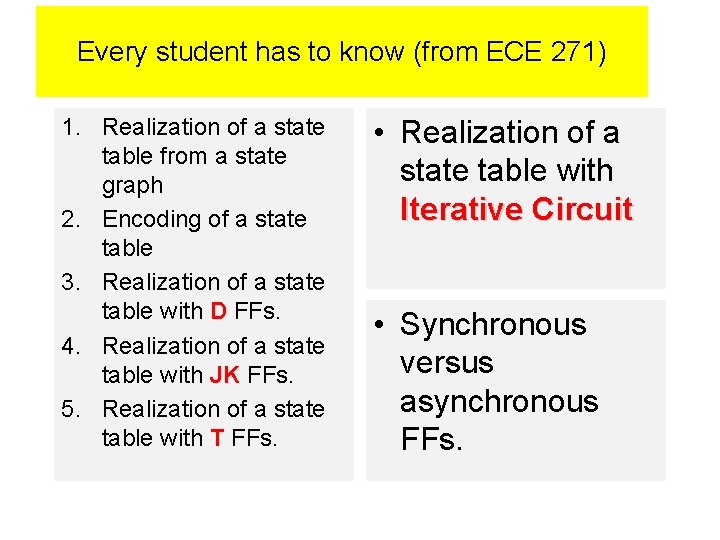

Every student has to know (from ECE 271) 1. Realization of a state table from a state graph 2. Encoding of a state table 3. Realization of a state table with D FFs. 4. Realization of a state table with JK FFs. 5. Realization of a state table with T FFs. • Realization of a state table with Iterative Circuit • Synchronous versus asynchronous FFs.

Arithmetic Circuits 29

Topics • Adder circuits • How to subtract – Why complemented representation works out so well • Overflow 30

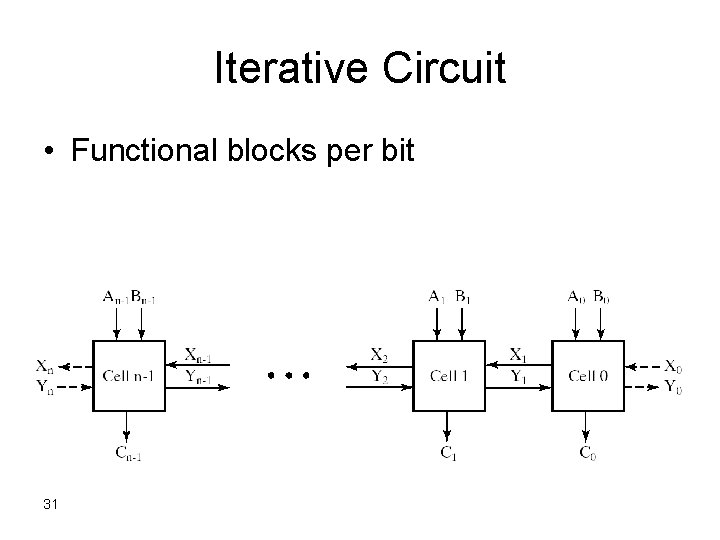

Iterative Circuit • Functional blocks per bit 31

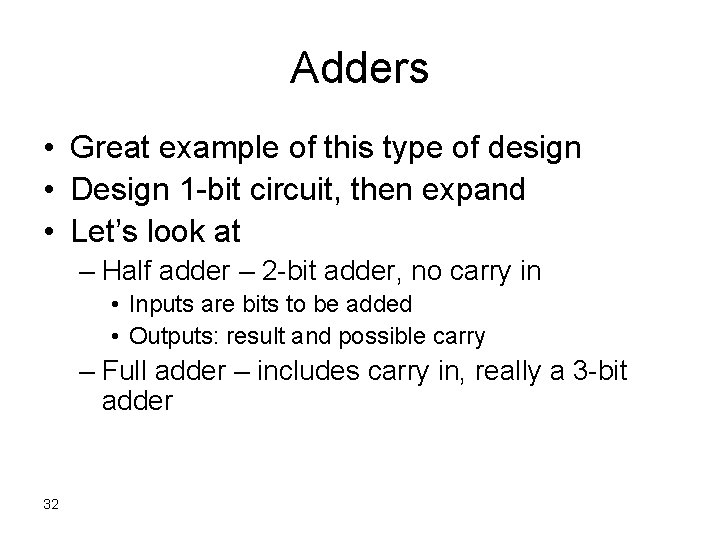

Adders • Great example of this type of design • Design 1 -bit circuit, then expand • Let’s look at – Half adder – 2 -bit adder, no carry in • Inputs are bits to be added • Outputs: result and possible carry – Full adder – includes carry in, really a 3 -bit adder 32

Sequential Parity Generators

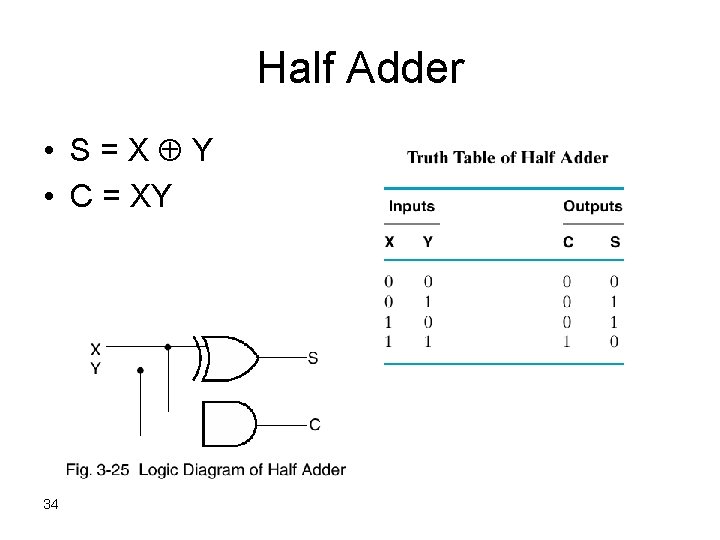

Half Adder • S=X Y • C = XY 34

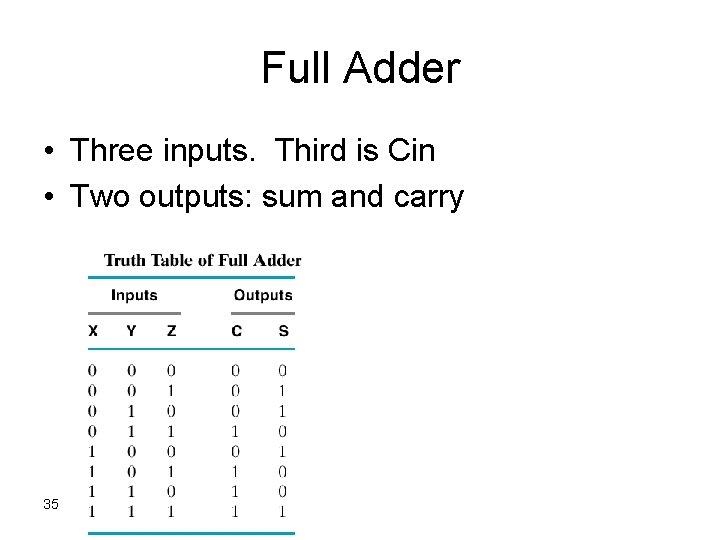

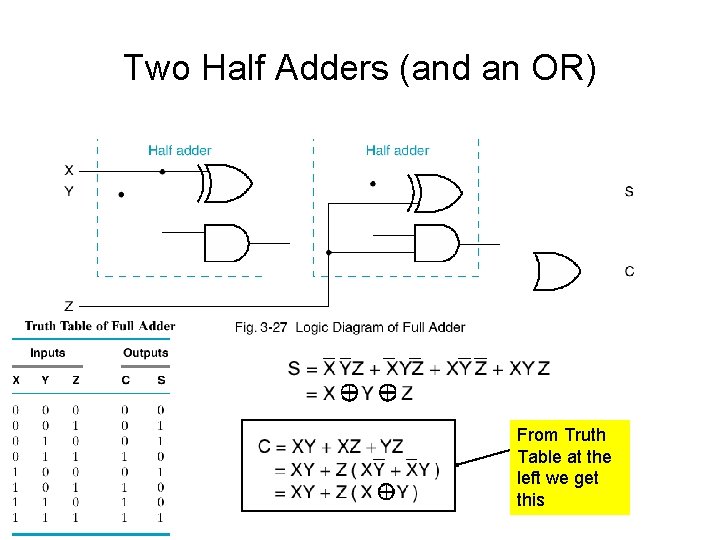

Full Adder • Three inputs. Third is Cin • Two outputs: sum and carry 35

Two Half Adders (and an OR) 36 From Truth Table at the left we get this

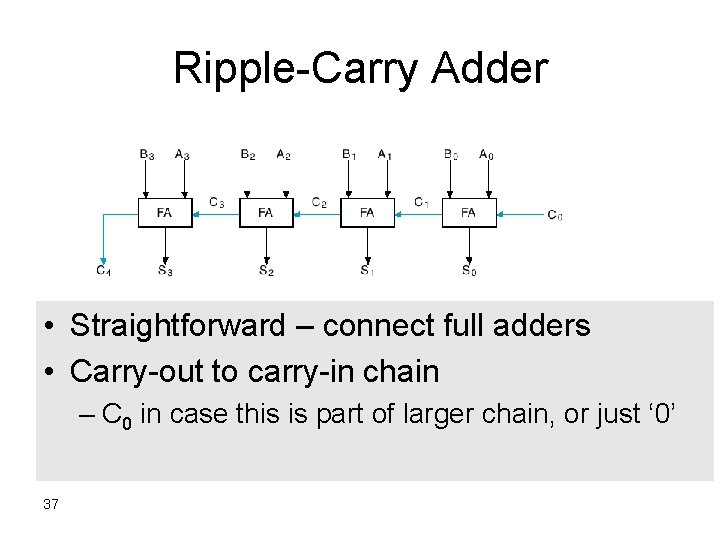

Ripple-Carry Adder • Straightforward – connect full adders • Carry-out to carry-in chain – C 0 in case this is part of larger chain, or just ‘ 0’ 37

Iterative Circuits

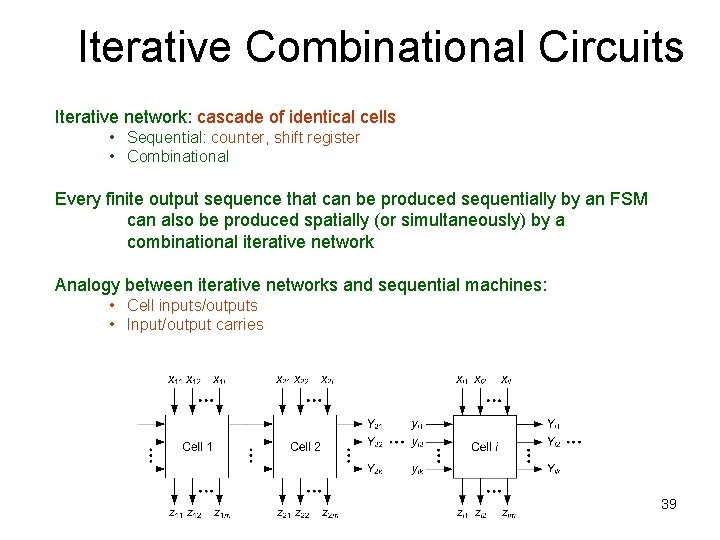

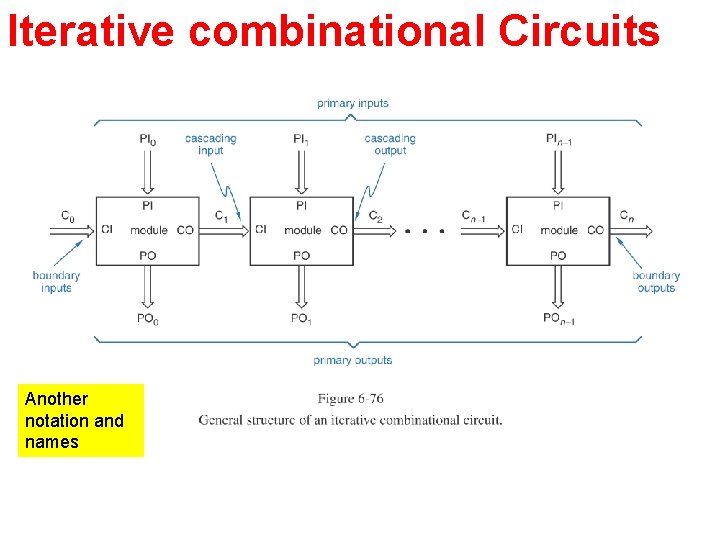

Iterative Combinational Circuits Iterative network: cascade of identical cells • Sequential: counter, shift register • Combinational Every finite output sequence that can be produced sequentially by an FSM can also be produced spatially (or simultaneously) by a combinational iterative network Analogy between iterative networks and sequential machines: • Cell inputs/outputs • Input/output carries 39

Iterative combinational Circuits Another notation and names

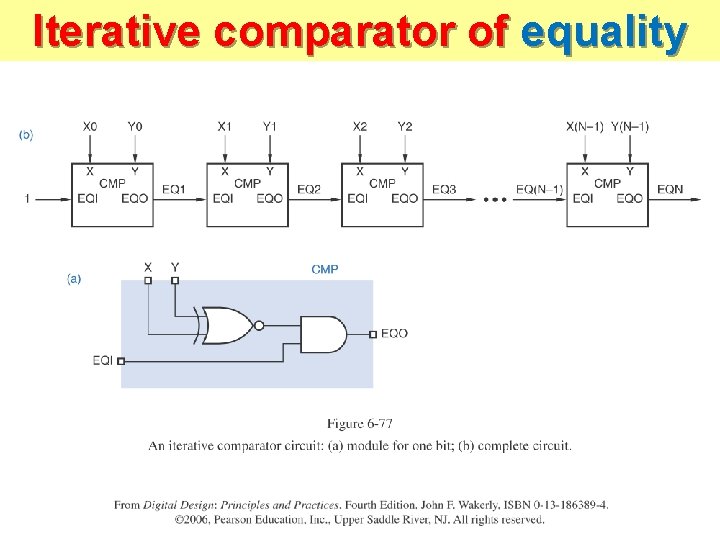

Iterative Comparators

Iterative comparator of equality

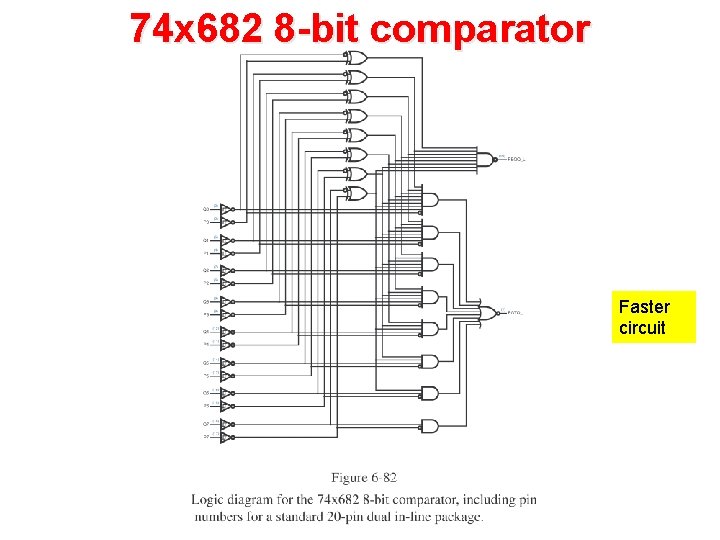

74 x 682 8 -bit comparator Faster circuit

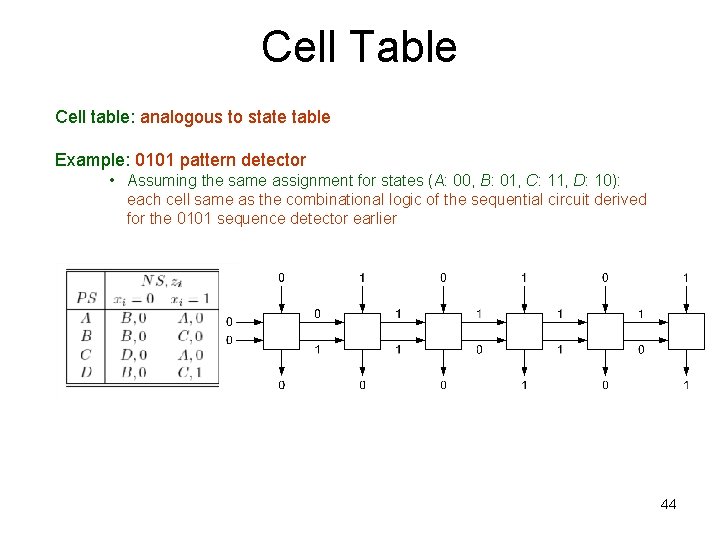

Cell Table Cell table: analogous to state table Example: 0101 pattern detector • Assuming the same assignment for states (A: 00, B: 01, C: 11, D: 10): each cell same as the combinational logic of the sequential circuit derived for the 0101 sequence detector earlier 44

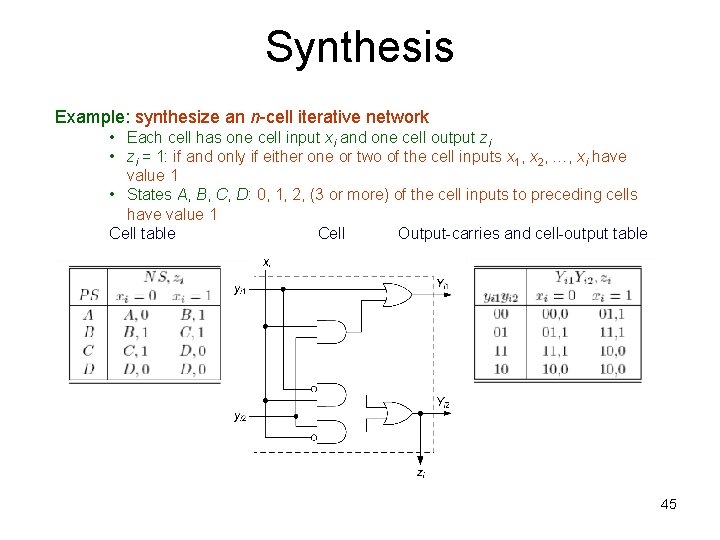

Synthesis Example: synthesize an n-cell iterative network • Each cell has one cell input xi and one cell output zi • zi = 1: if and only if either one or two of the cell inputs x 1, x 2, …, xi have value 1 • States A, B, C, D: 0, 1, 2, (3 or more) of the cell inputs to preceding cells have value 1 Cell table Cell Output-carries and cell-output table 45

Iterative comparator of orders and equality 1. 2. 3. 4. Calculated last week Starts from graph Next table from graph Realize circuit combining identical blocks 5. Last block different 6. Transition from combinational to sequential circuit 7. Main tradeoff of digital design – parallel versus serial

General Iterative Circuits

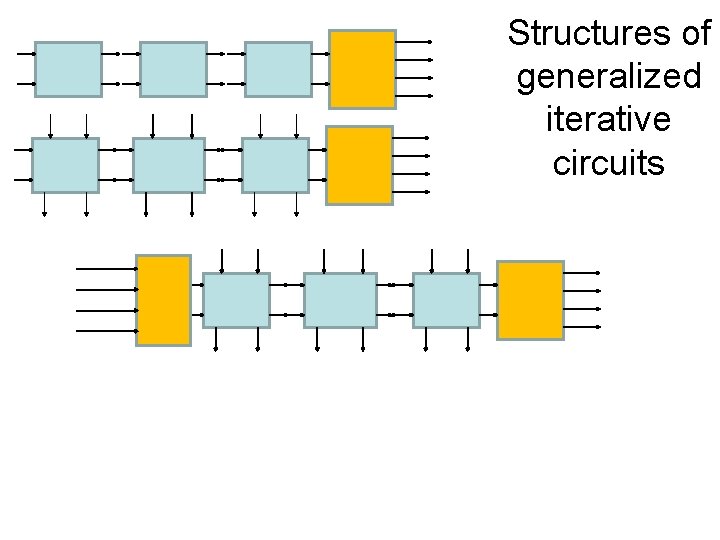

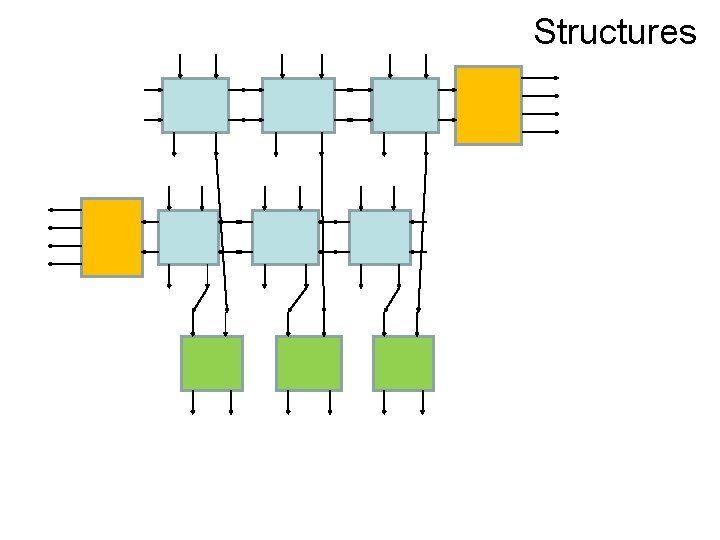

Structures of generalized iterative circuits

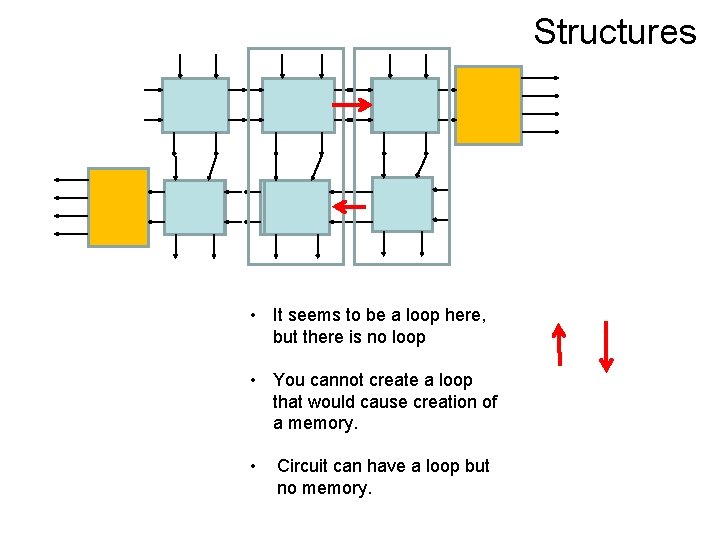

Structures

Structures • It seems to be a loop here, but there is no loop • You cannot create a loop that would cause creation of a memory. • Circuit can have a loop but no memory.

• Students that do not understand iterative circuits will be severely penalized!

Slides from • Wakerly • Montek Singh

- Slides: 52