COE 405 Introduction to Logic Design with Verilog

![Definition of a Module: Verilog-2005 n Module & Port Declaration: module [module-name] #(parameter declarations) Definition of a Module: Verilog-2005 n Module & Port Declaration: module [module-name] #(parameter declarations)](https://slidetodoc.com/presentation_image_h/aa152de2e73cb0c7e7faaa10fd3f3809/image-9.jpg)

![Module Instantiation module Add_rca_4 (output c_out, output [3: 0] sum, input [3: 0] a, Module Instantiation module Add_rca_4 (output c_out, output [3: 0] sum, input [3: 0] a,](https://slidetodoc.com/presentation_image_h/aa152de2e73cb0c7e7faaa10fd3f3809/image-24.jpg)

![Module Instantiation module Add_rca_16 (output c_out, output [15: 0] sum, input [15: 0] a, Module Instantiation module Add_rca_16 (output c_out, output [15: 0] sum, input [15: 0] a,](https://slidetodoc.com/presentation_image_h/aa152de2e73cb0c7e7faaa10fd3f3809/image-25.jpg)

- Slides: 43

COE 405 Introduction to Logic Design with Verilog Dr. Aiman H. El-Maleh Computer Engineering Department King Fahd University of Petroleum & Minerals

Outline n Introduction n Definition of a module n Gate-level modeling n Verilog primitives n Verilog Syntax n Verilog Data Types n Module instantiation n Organization of a Testbench for Verifying a Unit Under Test (UUT) n Propagation, inertial and transport delay n Truth Table Models of Combinational and Sequential Logic with Verilog 1 -2

Introduction n Verilog is one of the hardware description languages (HDL) available in the industry for hardware designing. n Verilog is a standard HDL (IEEE 1364 -1995, 2001, 2005) n It allows designers to design at Behavior Level, Register Transfer Level (RTL), Gate level and at switch level. n Parallel not serial (Not like C language). n Verilog can describe everything from single gate to full computer system. 1 -3

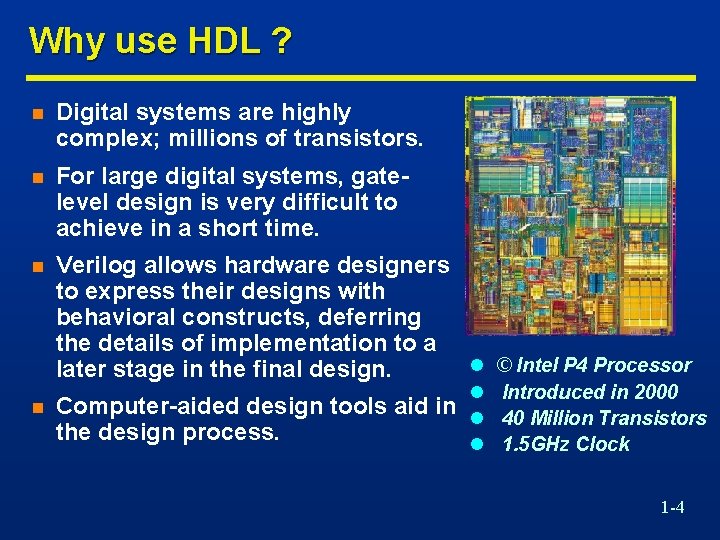

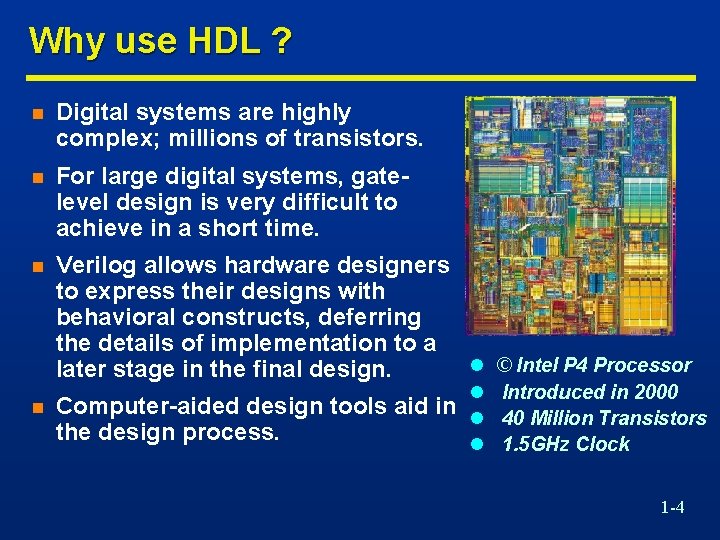

Why use HDL ? n Digital systems are highly complex; millions of transistors. n For large digital systems, gatelevel design is very difficult to achieve in a short time. n Verilog allows hardware designers to express their designs with behavioral constructs, deferring the details of implementation to a l © Intel P 4 Processor later stage in the final design. l Introduced in 2000 n Computer-aided design tools aid in l 40 Million Transistors the design process. l 1. 5 GHz Clock 1 -4

A Verilog Model n A digital system can be described at several levels of details (more details means more design entry time!): • Gate-level Net-list similar to schematic or bread boarding • Register-transfer-level (RTL): Describing logic between • n registers using simple assignment statement (two types of assignments; continuous and procedural) logic synthesis tools convert it to gate-level netlist (gates and FFs) Behavioral description: programming-like structures (if-thenelse, case, loops …etc) to describe what the circuit does (i. e. behavior) rather than how requires a high-level synthesis tool to synthesize an RTL implementation (DP & CU) which can then be synthesized into gate-level netlist. A digital system is described as a set of modules Basic building block encapsulation 1 -5

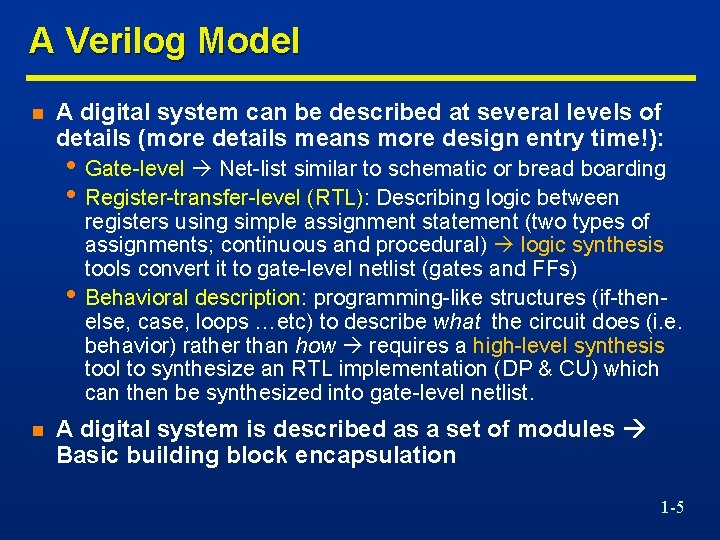

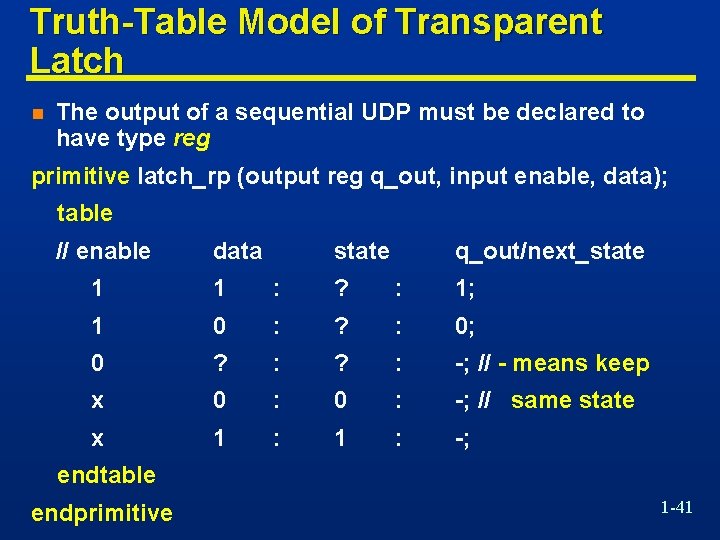

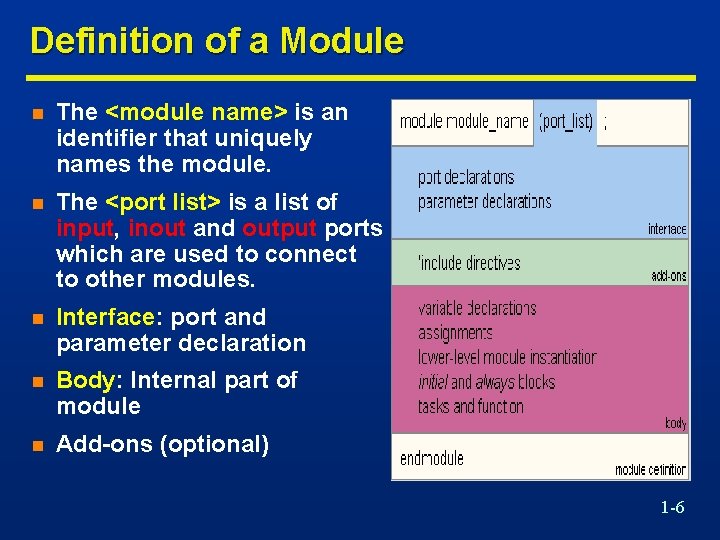

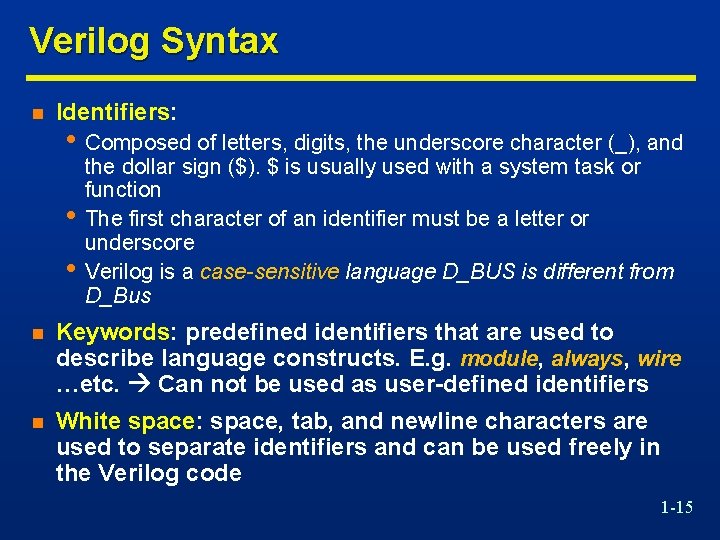

Definition of a Module n The <module name> is an identifier that uniquely names the module. n The <port list> is a list of input, inout and output ports which are used to connect to other modules. n Interface: port and parameter declaration n Body: Internal part of module n Add-ons (optional) 1 -6

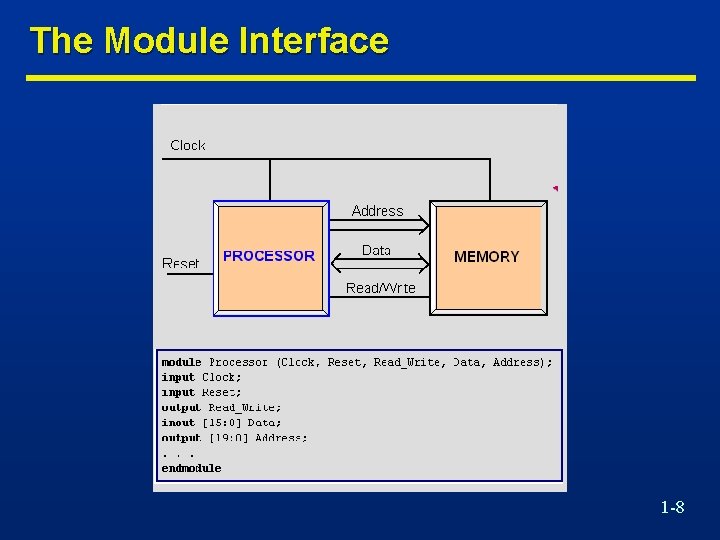

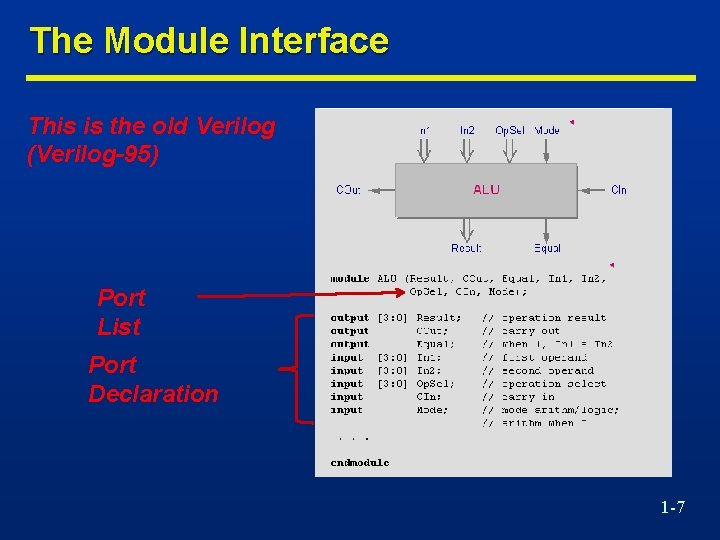

The Module Interface This is the old Verilog (Verilog-95) Port List Port Declaration 1 -7

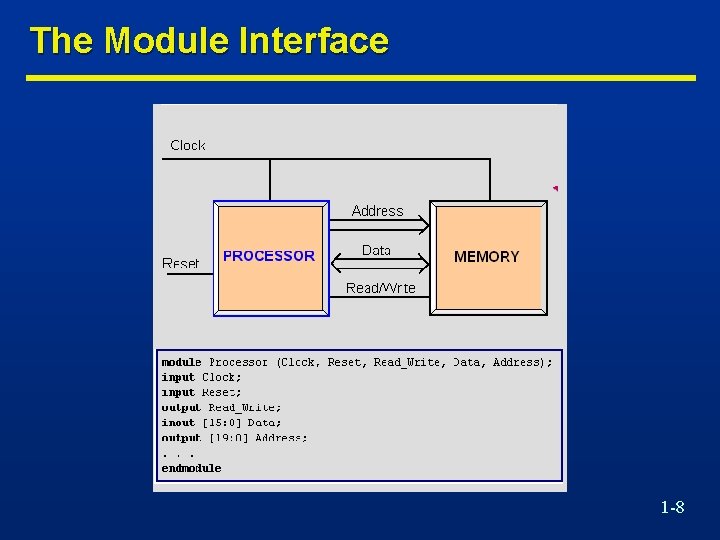

The Module Interface 1 -8

![Definition of a Module Verilog2005 n Module Port Declaration module modulename parameter declarations Definition of a Module: Verilog-2005 n Module & Port Declaration: module [module-name] #(parameter declarations)](https://slidetodoc.com/presentation_image_h/aa152de2e73cb0c7e7faaa10fd3f3809/image-9.jpg)

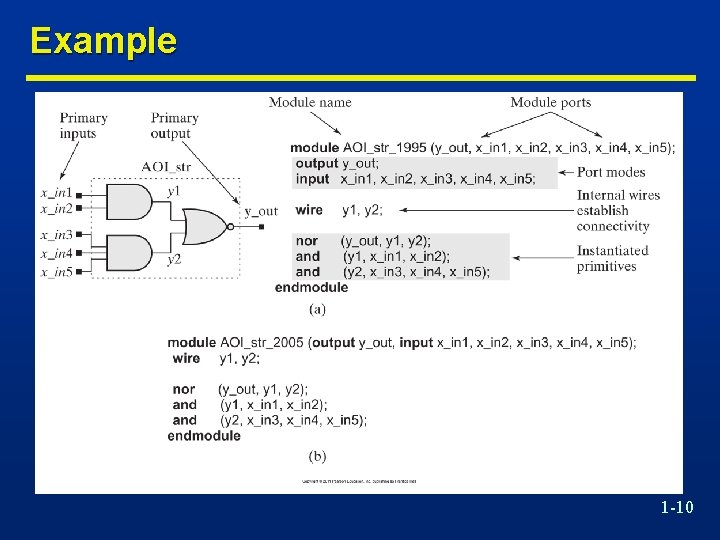

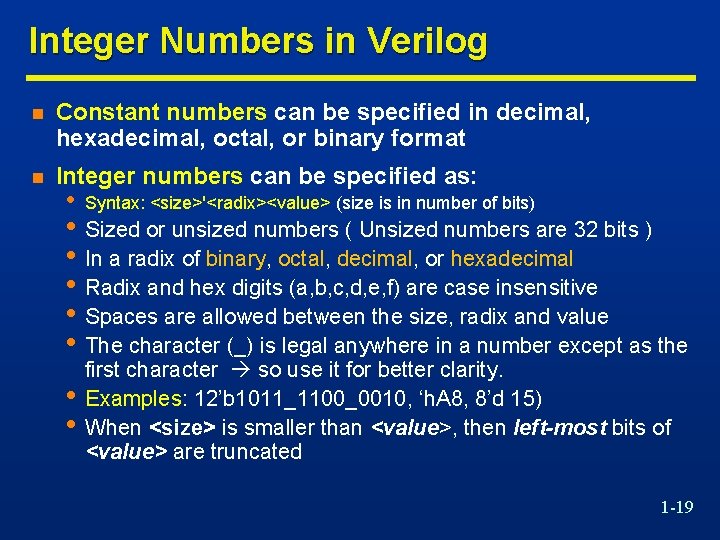

Definition of a Module: Verilog-2005 n Module & Port Declaration: module [module-name] #(parameter declarations) ( [mode] [ data-type] [port-names] , . . . [mode] [ data-type] [port-names] ); Mode: input, output or inout Data-Type: wire, reg or integer (scalar or array) 1 -9

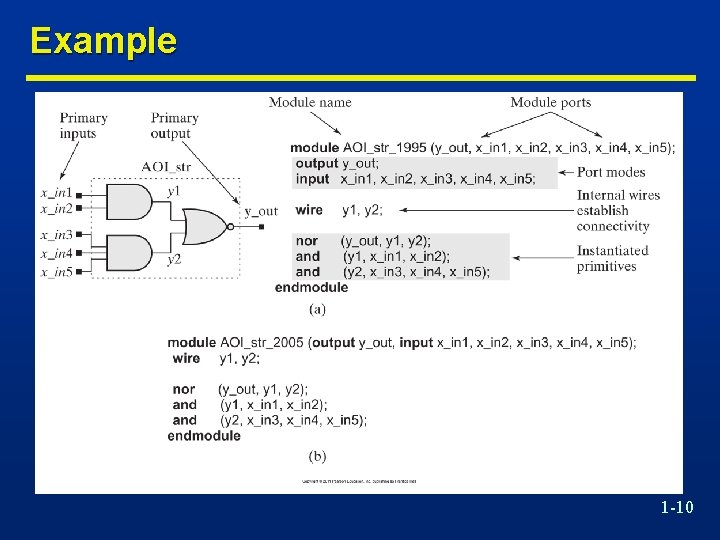

Example 1 -10

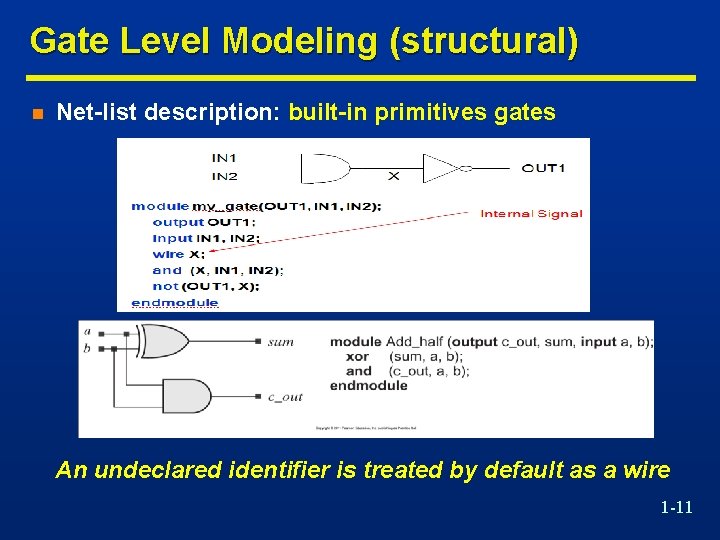

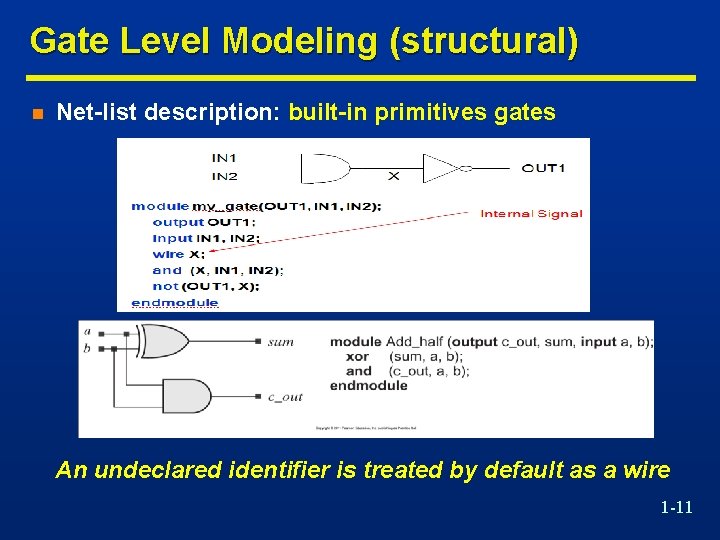

Gate Level Modeling (structural) n Net-list description: built-in primitives gates An undeclared identifier is treated by default as a wire 1 -11

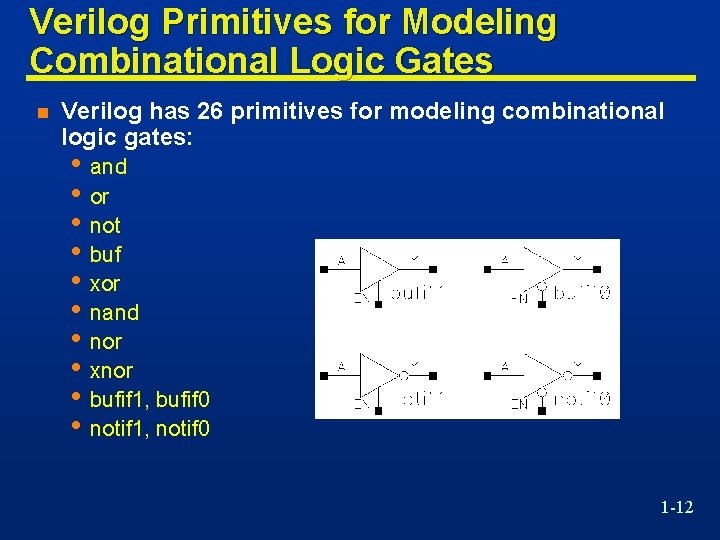

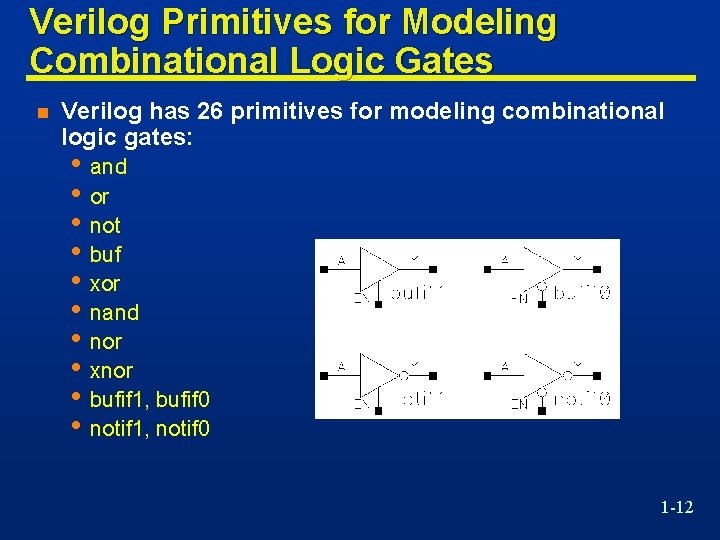

Verilog Primitives for Modeling Combinational Logic Gates n Verilog has 26 primitives for modeling combinational logic gates: • and • or • not • buf • xor • nand • nor • xnor • bufif 1, bufif 0 • notif 1, notif 0 1 -12

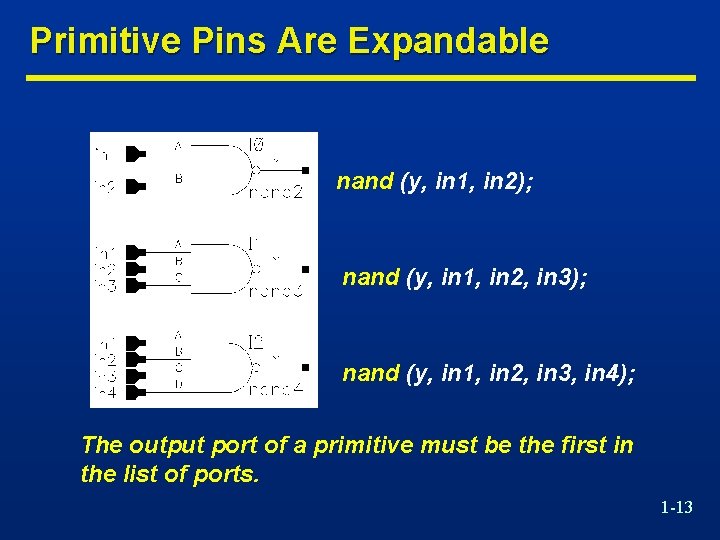

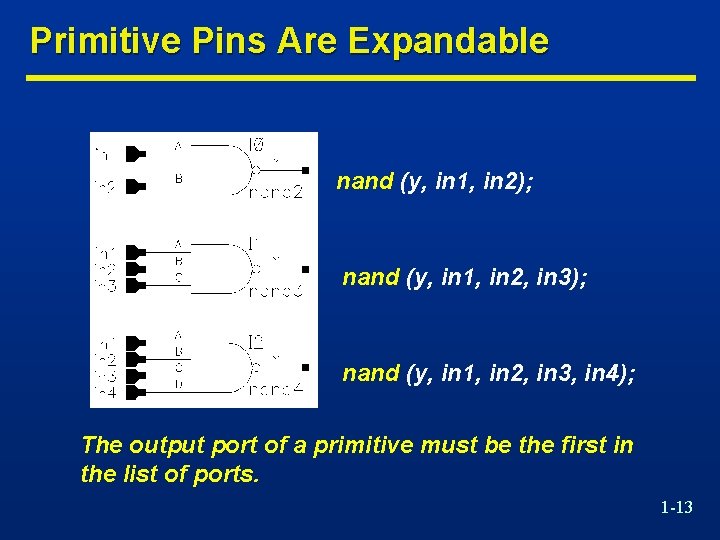

Primitive Pins Are Expandable nand (y, in 1, in 2); nand (y, in 1, in 2, in 3, in 4); The output port of a primitive must be the first in the list of ports. 1 -13

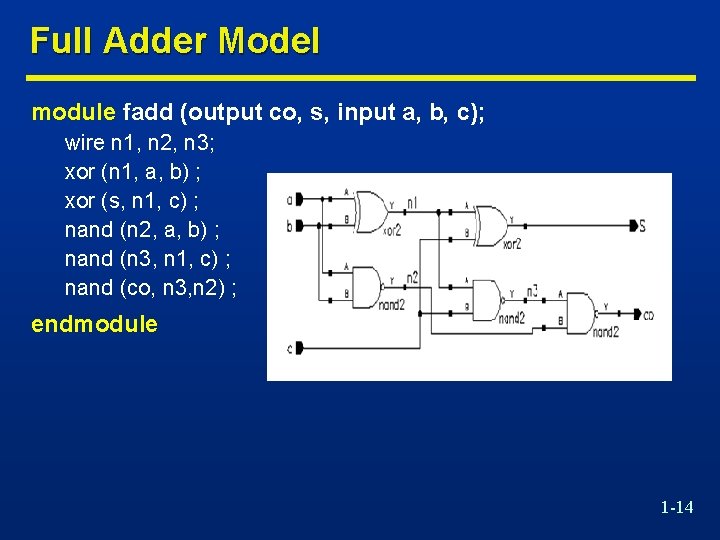

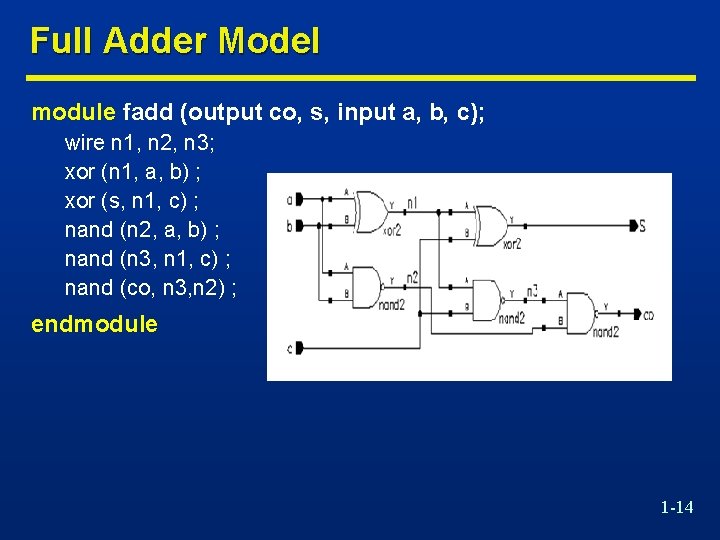

Full Adder Model module fadd (output co, s, input a, b, c); wire n 1, n 2, n 3; xor (n 1, a, b) ; xor (s, n 1, c) ; nand (n 2, a, b) ; nand (n 3, n 1, c) ; nand (co, n 3, n 2) ; endmodule 1 -14

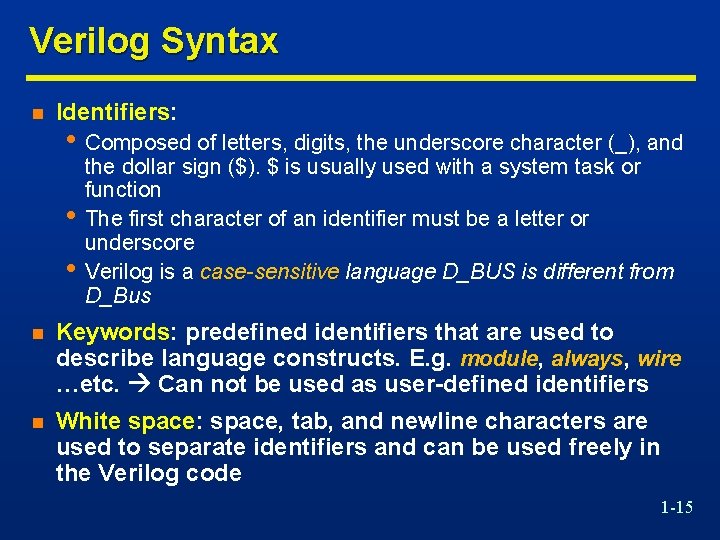

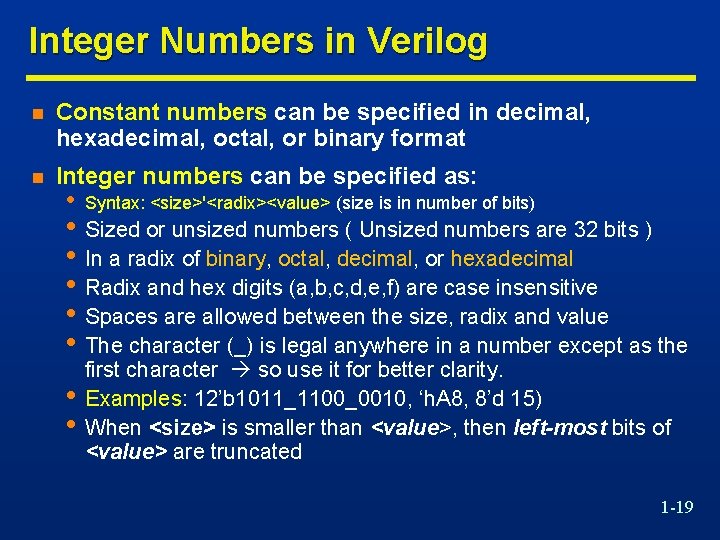

Verilog Syntax n Identifiers: • Composed of letters, digits, the underscore character (_), and • • the dollar sign ($). $ is usually used with a system task or function The first character of an identifier must be a letter or underscore Verilog is a case-sensitive language D_BUS is different from D_Bus n Keywords: predefined identifiers that are used to describe language constructs. E. g. module, always, wire …etc. Can not be used as user-defined identifiers n White space: space, tab, and newline characters are used to separate identifiers and can be used freely in the Verilog code 1 -15

Verilog Syntax n Comments: two forms; one-line comment starts with // and multiple-line comment is encapsulated between /* and */ // This is a comment /* This i s comment line 1. This i s comment line 2. This i s comment line 3. * / 1 -16

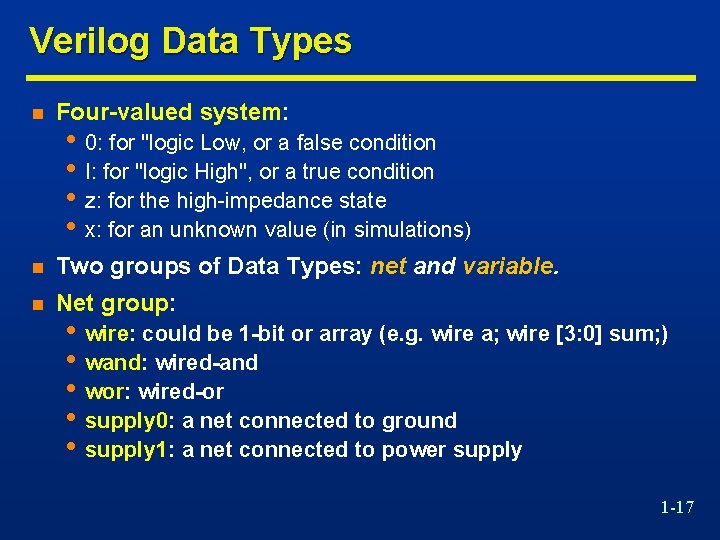

Verilog Data Types n Four-valued system: n Two groups of Data Types: net and variable. n Net group: • 0: for "logic Low, or a false condition • I: for "logic High", or a true condition • z: for the high-impedance state • x: for an unknown value (in simulations) • wire: could be 1 -bit or array (e. g. wire a; wire [3: 0] sum; ) • wand: wired-and • wor: wired-or • supply 0: a net connected to ground • supply 1: a net connected to power supply 1 -17

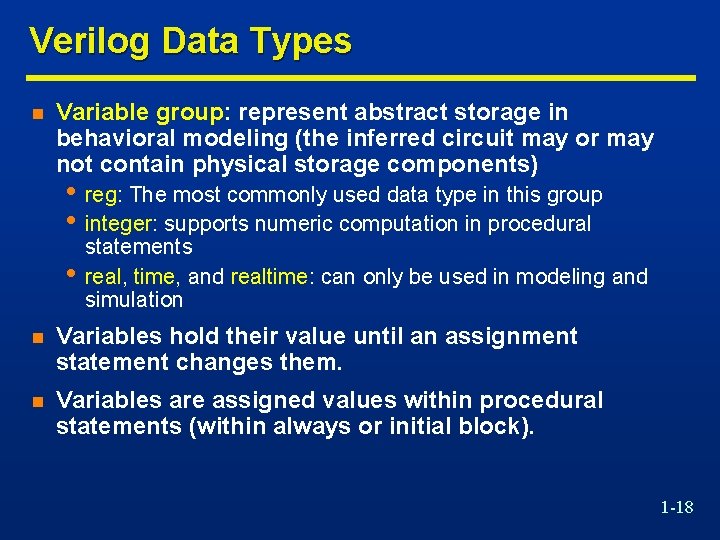

Verilog Data Types n Variable group: represent abstract storage in behavioral modeling (the inferred circuit may or may not contain physical storage components) • reg: The most commonly used data type in this group • integer: supports numeric computation in procedural • statements real, time, and realtime: can only be used in modeling and simulation n Variables hold their value until an assignment statement changes them. n Variables are assigned values within procedural statements (within always or initial block). 1 -18

Integer Numbers in Verilog n Constant numbers can be specified in decimal, hexadecimal, octal, or binary format n Integer numbers can be specified as: • Syntax: <size>'<radix><value> (size is in number of bits) • • first character so use it for better clarity. Examples: 12’b 1011_1100_0010, ‘h. A 8, 8’d 15) When <size> is smaller than <value>, then left-most bits of <value> are truncated • Sized or unsized numbers ( Unsized numbers are 32 bits ) • In a radix of binary, octal, decimal, or hexadecimal • Radix and hex digits (a, b, c, d, e, f) are case insensitive • Spaces are allowed between the size, radix and value • The character (_) is legal anywhere in a number except as the 1 -19

Constants n A constant is declared with keyword parameter, which declares and assigns value to the constant. n Constant expressions maybe used in value declaration. n A value of a constant may not change during simulation. n Examples: • parameter high_index = 31; • parameter width = 32, depth = 1024; • parameter byte_size = 8, byte_max = byte_size-1; • parameter initial_state = 8’b 1001_0110; 1 -20

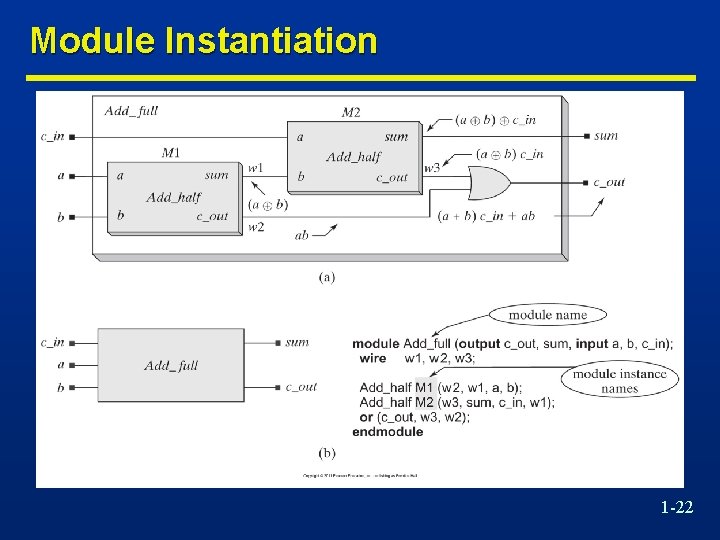

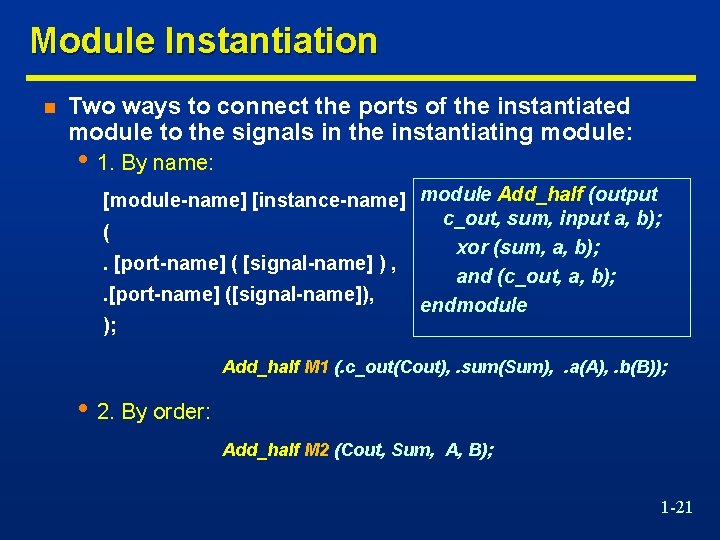

Module Instantiation n Two ways to connect the ports of the instantiated module to the signals in the instantiating module: • 1. By name: [module-name] [instance-name] module Add_half (output c_out, sum, input a, b); ( xor (sum, a, b); . [port-name] ( [signal-name] ) , and (c_out, a, b); . [port-name] ([signal-name]), endmodule ); Add_half M 1 (. c_out(Cout), . sum(Sum), . a(A), . b(B)); • 2. By order: Add_half M 2 (Cout, Sum, A, B); 1 -21

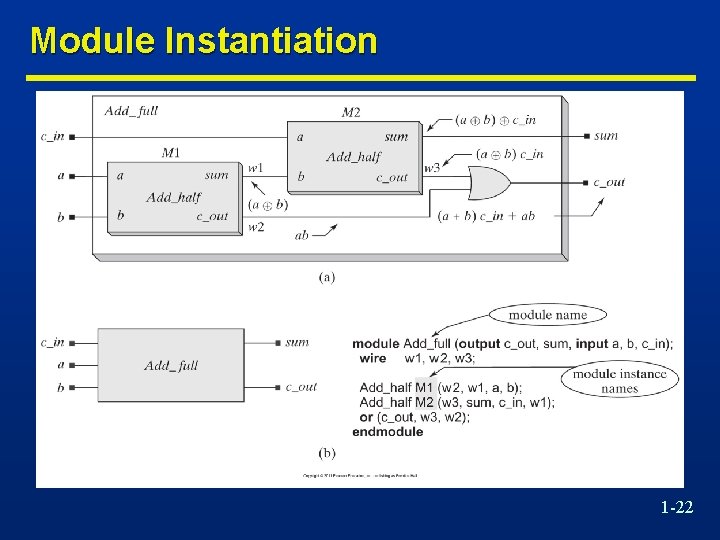

Module Instantiation 1 -22

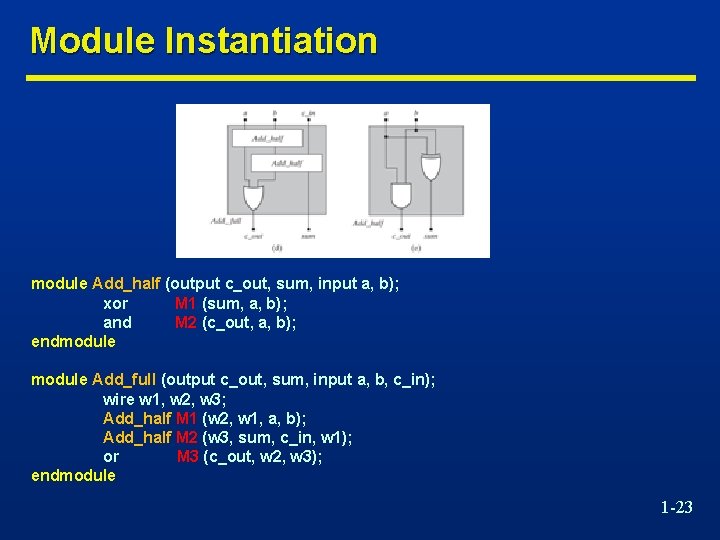

Module Instantiation module Add_half (output c_out, sum, input a, b); xor M 1 (sum, a, b); and M 2 (c_out, a, b); endmodule Add_full (output c_out, sum, input a, b, c_in); wire w 1, w 2, w 3; Add_half M 1 (w 2, w 1, a, b); Add_half M 2 (w 3, sum, c_in, w 1); or M 3 (c_out, w 2, w 3); endmodule 1 -23

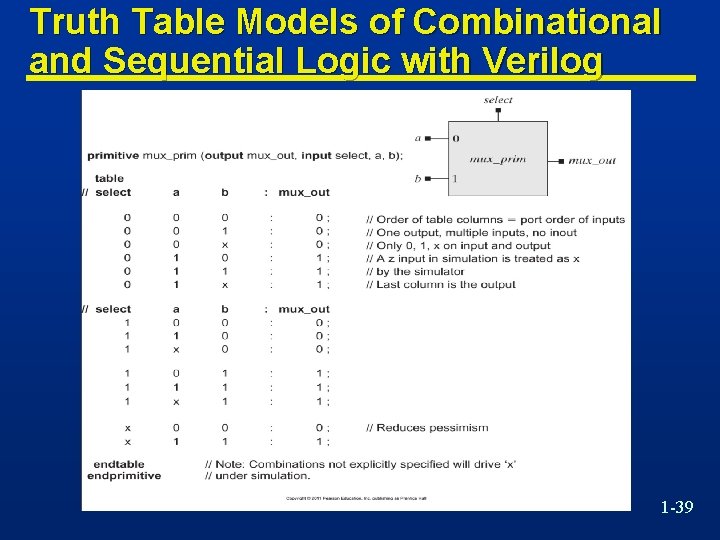

![Module Instantiation module Addrca4 output cout output 3 0 sum input 3 0 a Module Instantiation module Add_rca_4 (output c_out, output [3: 0] sum, input [3: 0] a,](https://slidetodoc.com/presentation_image_h/aa152de2e73cb0c7e7faaa10fd3f3809/image-24.jpg)

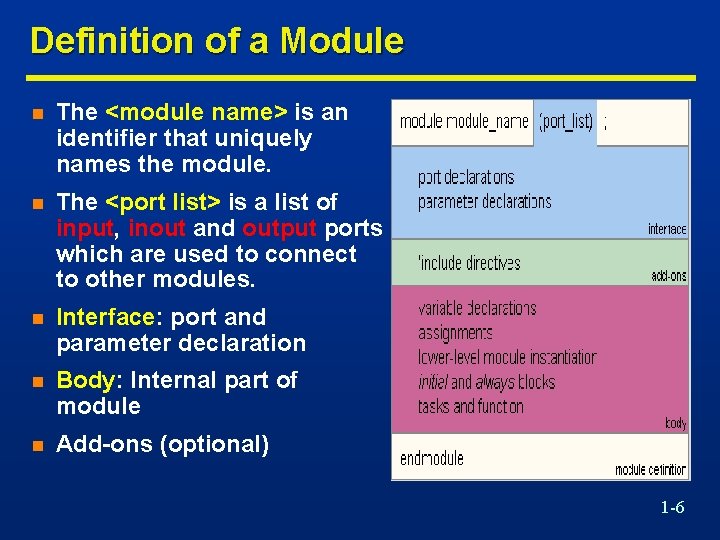

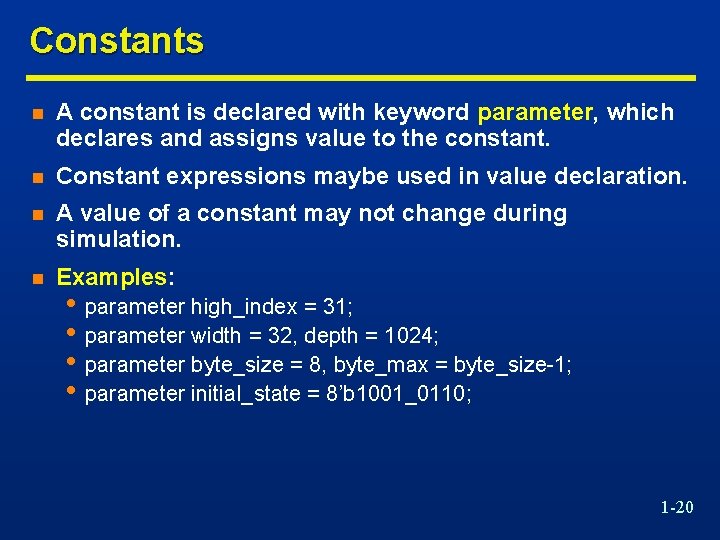

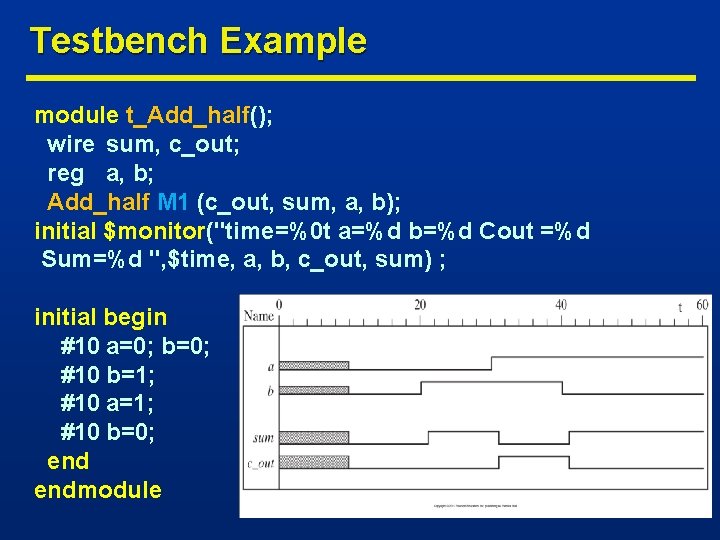

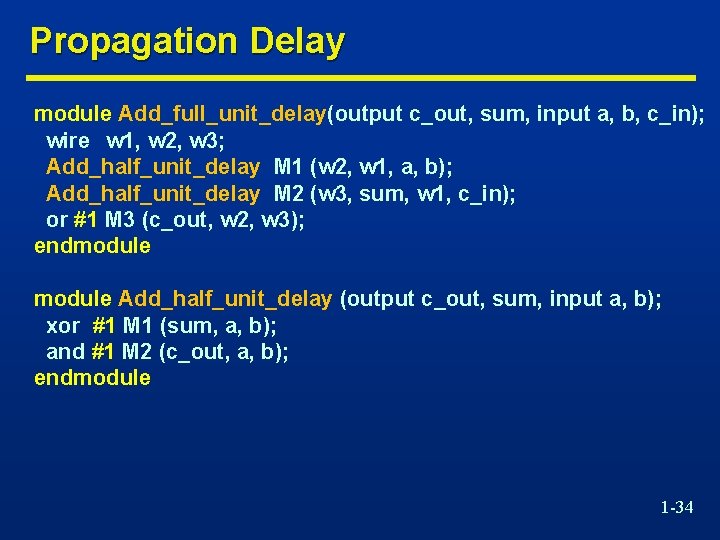

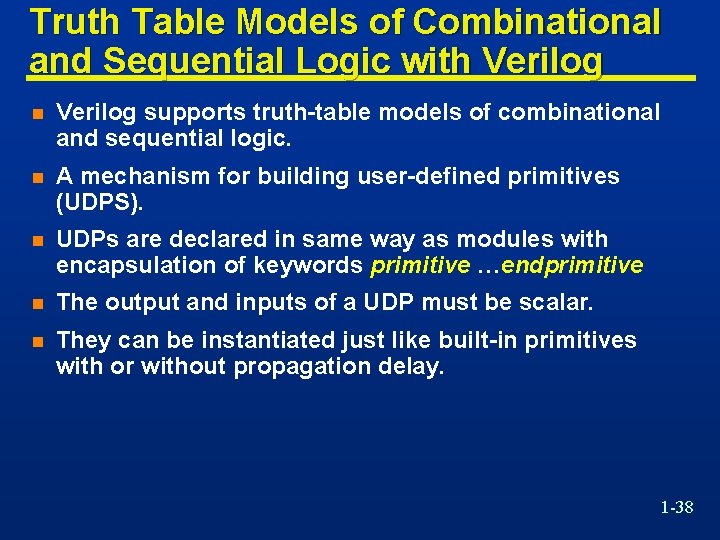

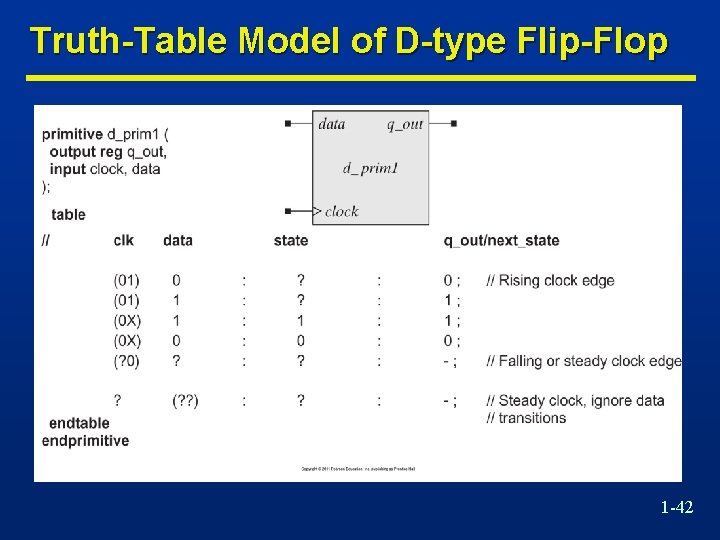

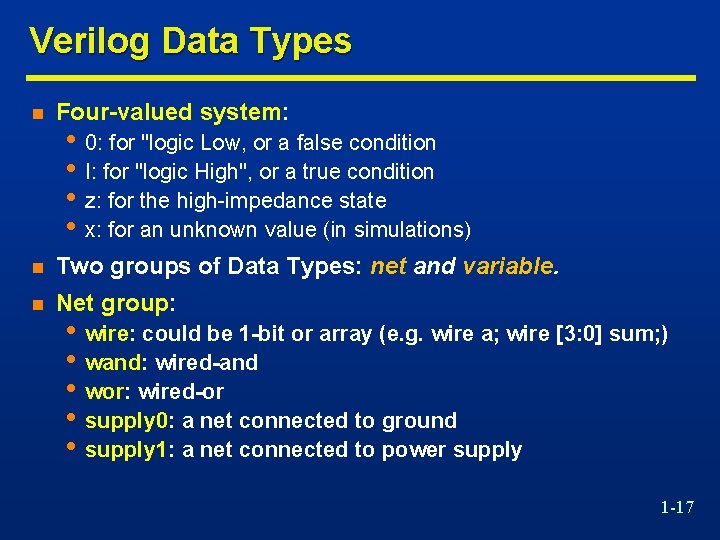

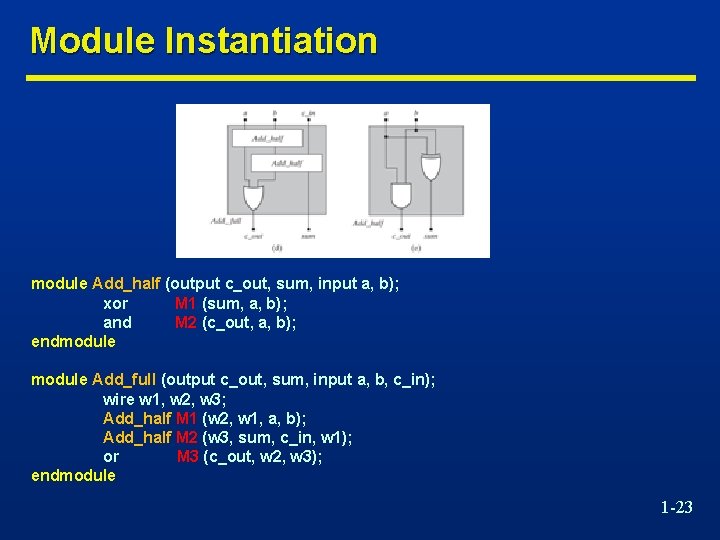

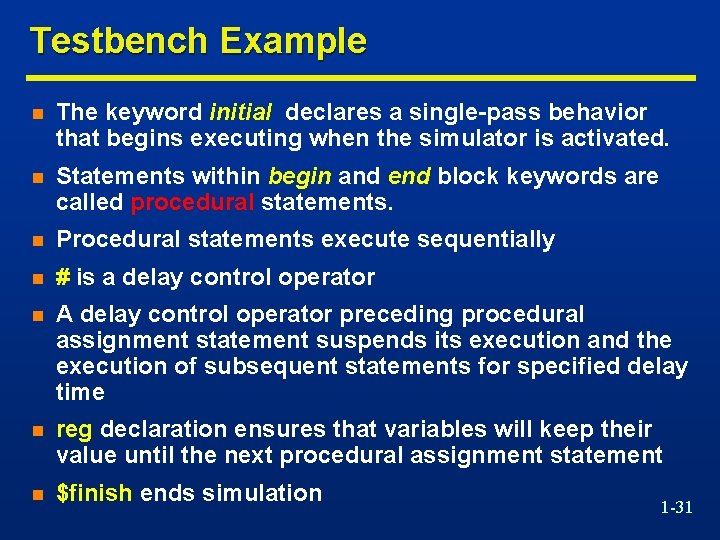

Module Instantiation module Add_rca_4 (output c_out, output [3: 0] sum, input [3: 0] a, b, input c_in); wire c_in 2, cin 3, c_in 3; Add_full M 1 (c_in 2, sum[0], a[0], b[0], c_in); Add_full M 2 (c_in 3, sum[1], a[1], b[1], c_in 2); Add_full M 3 (c_in 4, sum[2], a[2], b[2], c_in 3); Add_full M 4 (c_out, sum[3], a[3], b[3], c_in 4); endmodule 1 -24

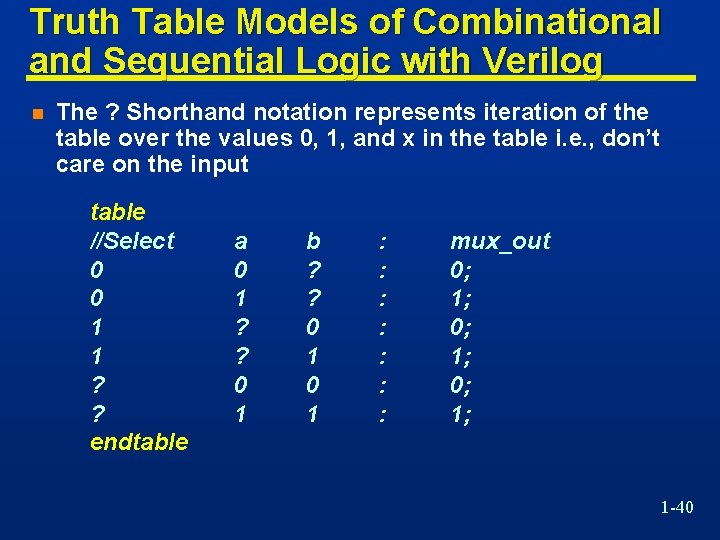

![Module Instantiation module Addrca16 output cout output 15 0 sum input 15 0 a Module Instantiation module Add_rca_16 (output c_out, output [15: 0] sum, input [15: 0] a,](https://slidetodoc.com/presentation_image_h/aa152de2e73cb0c7e7faaa10fd3f3809/image-25.jpg)

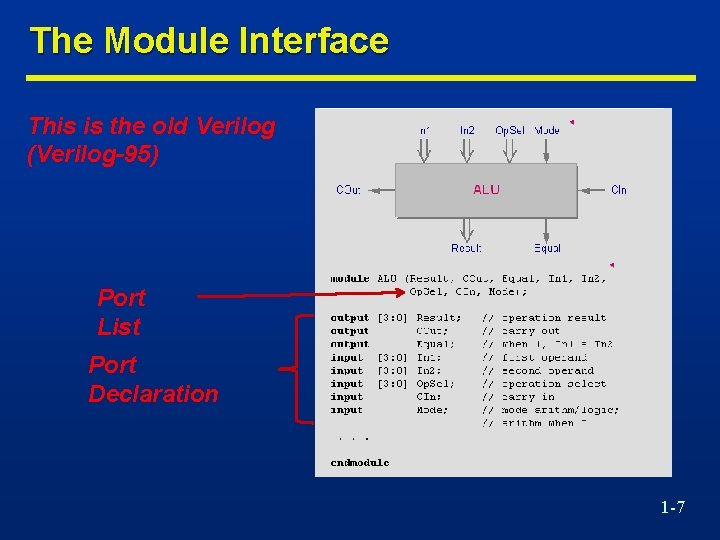

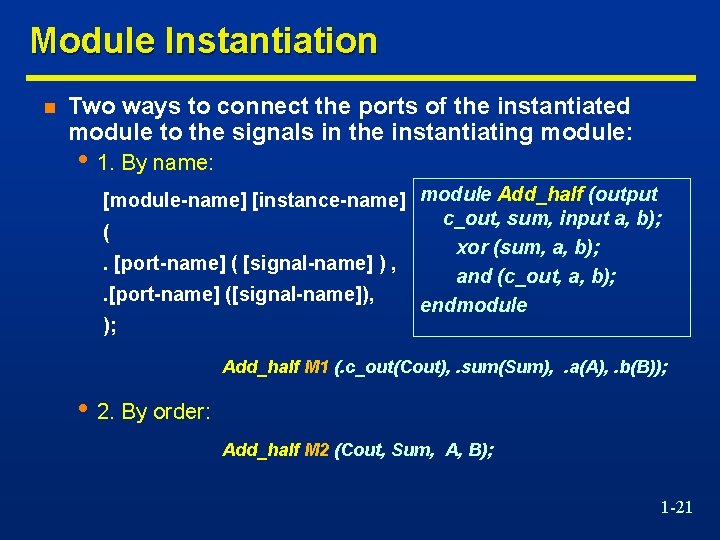

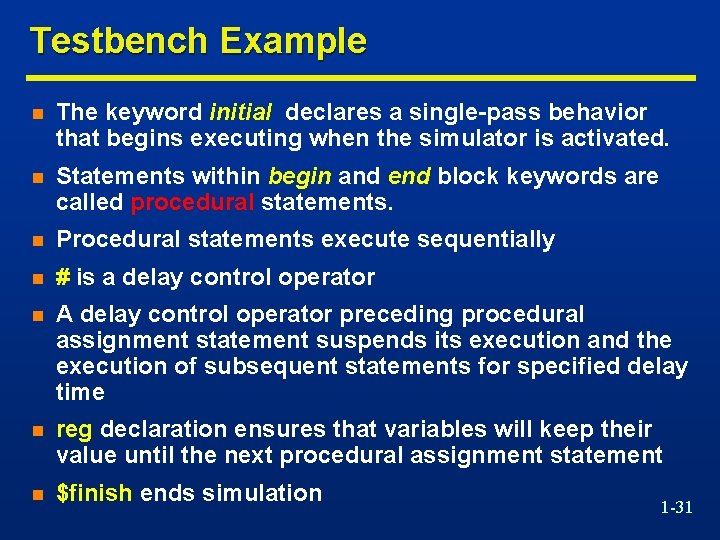

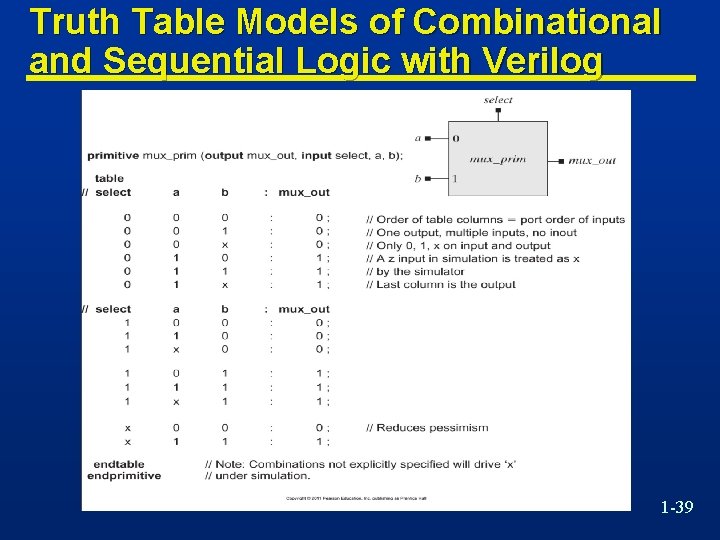

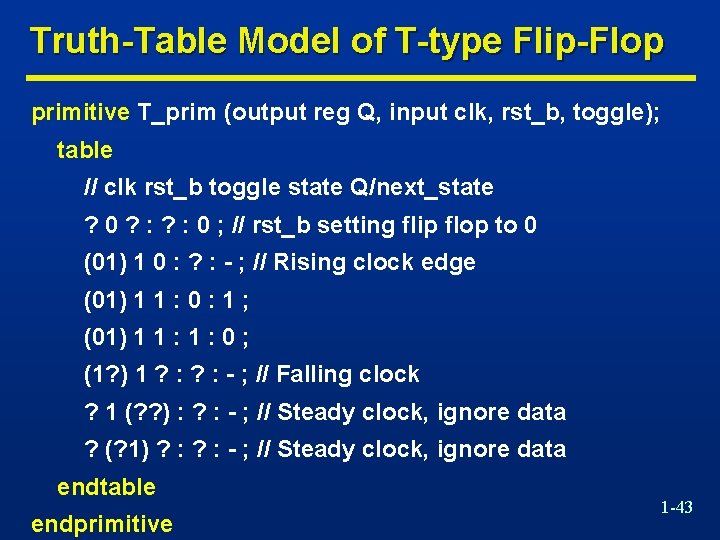

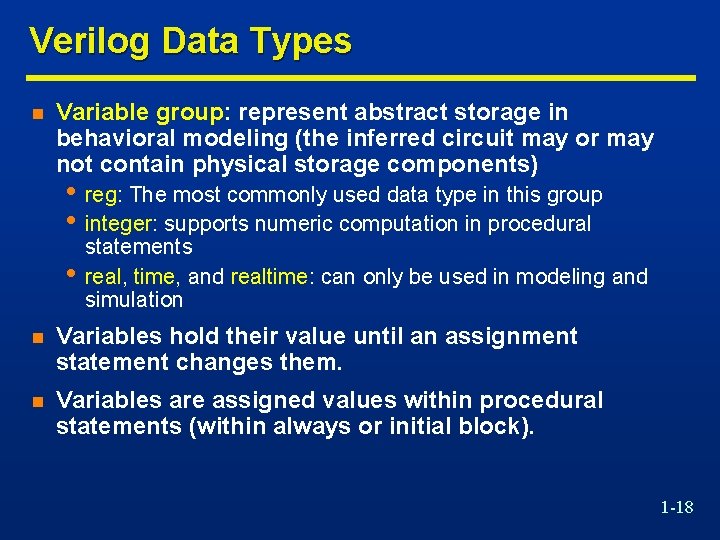

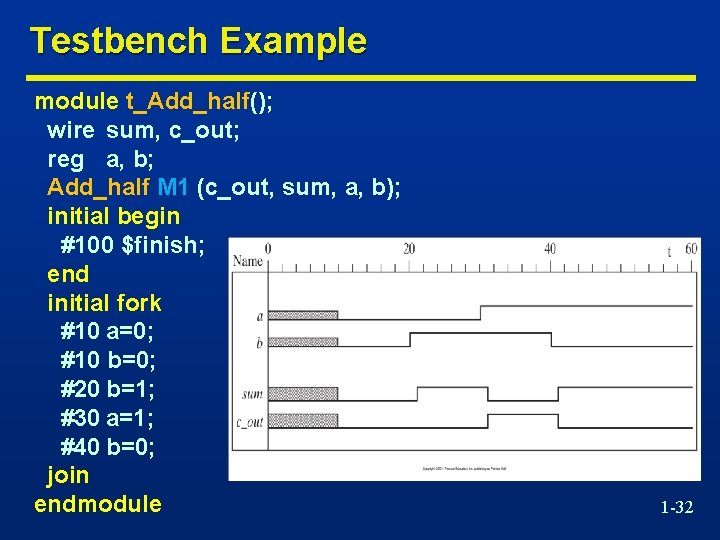

Module Instantiation module Add_rca_16 (output c_out, output [15: 0] sum, input [15: 0] a, b, input c_in); wire c_in 4, c_in 8, c_in 12; Add_rca_4 M 1 (c_in 4, sum[3: 0], a[3: 0], b[3: 0], c_in); Add_rca_4 M 2 (c_in 8, sum[7: 4], a[7: 4], b[7: 4], c_in 4); Add_rca_4 M 3 (c_in 12, sum[11: 8], a[11: 8], b[11: 8], c_in 8); Add_rca_4 M 4 (c_out, sum[15: 12], a[15: 12], b[15: 12], c_in 12); endmodule 1 -25

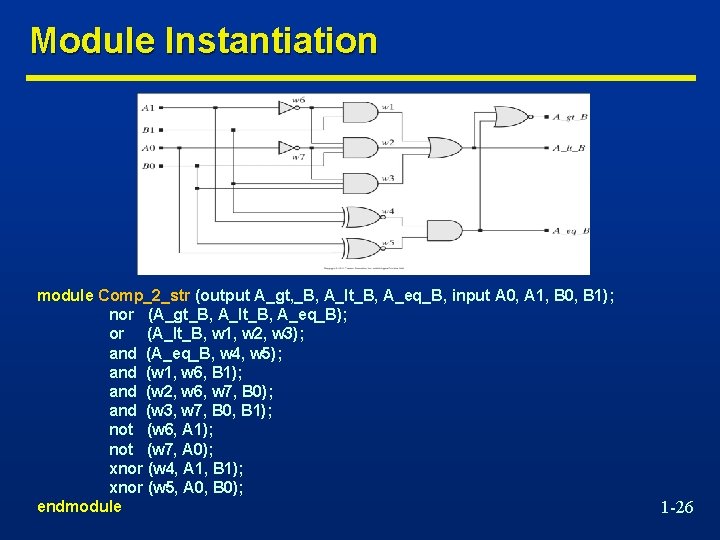

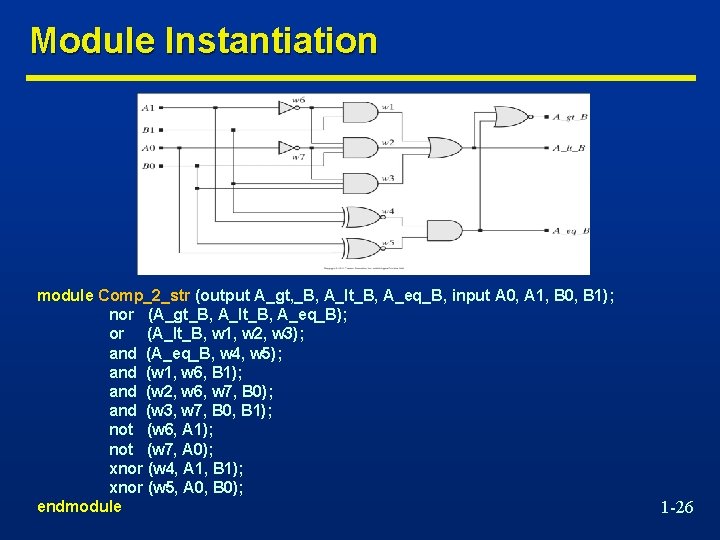

Module Instantiation module Comp_2_str (output A_gt, _B, A_lt_B, A_eq_B, input A 0, A 1, B 0, B 1); nor (A_gt_B, A_lt_B, A_eq_B); or (A_lt_B, w 1, w 2, w 3); and (A_eq_B, w 4, w 5); and (w 1, w 6, B 1); and (w 2, w 6, w 7, B 0); and (w 3, w 7, B 0, B 1); not (w 6, A 1); not (w 7, A 0); xnor (w 4, A 1, B 1); xnor (w 5, A 0, B 0); endmodule 1 -26

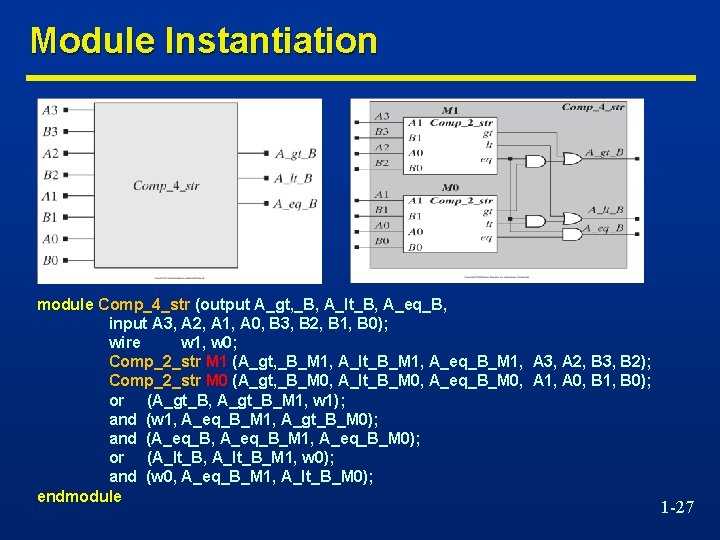

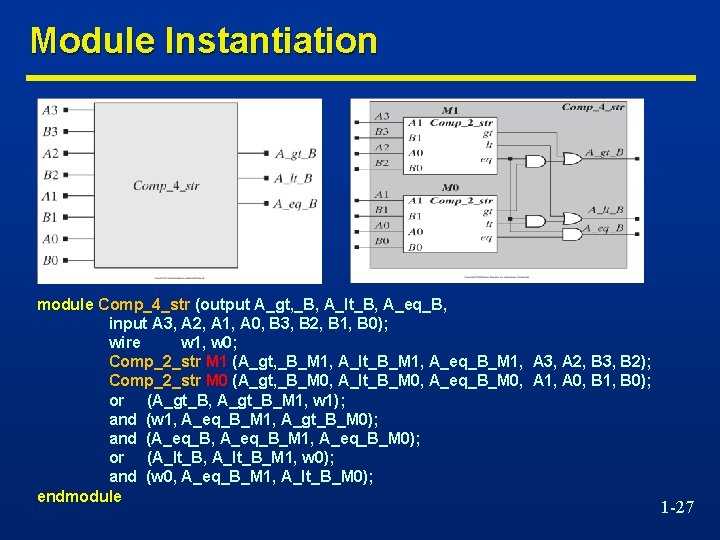

Module Instantiation module Comp_4_str (output A_gt, _B, A_lt_B, A_eq_B, input A 3, A 2, A 1, A 0, B 3, B 2, B 1, B 0); wire w 1, w 0; Comp_2_str M 1 (A_gt, _B_M 1, A_lt_B_M 1, A_eq_B_M 1, A 3, A 2, B 3, B 2); Comp_2_str M 0 (A_gt, _B_M 0, A_lt_B_M 0, A_eq_B_M 0, A 1, A 0, B 1, B 0); or (A_gt_B, A_gt_B_M 1, w 1); and (w 1, A_eq_B_M 1, A_gt_B_M 0); and (A_eq_B, A_eq_B_M 1, A_eq_B_M 0); or (A_lt_B, A_lt_B_M 1, w 0); and (w 0, A_eq_B_M 1, A_lt_B_M 0); endmodule 1 -27

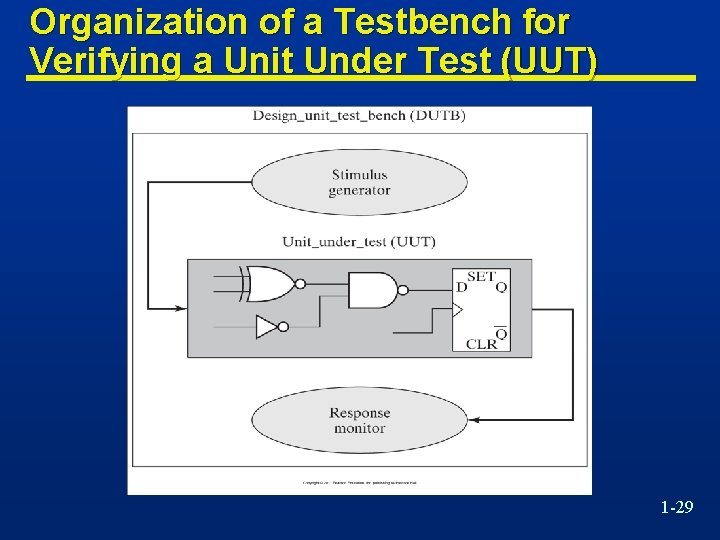

Test Methodology n Modeling begins with a complex functional unit and partitions it in a top-down fashion to enable design of simpler units. n Systematic verification begins with simpler units and moving to more complex units in design hierarchy. n To verify functionality of a digital circuit build a test bench that applies stimulus patterns to the circuit and collect responses. n Responses can be displayed or compared to a correct response. n Test bench is a separate Verilog module. 1 -28

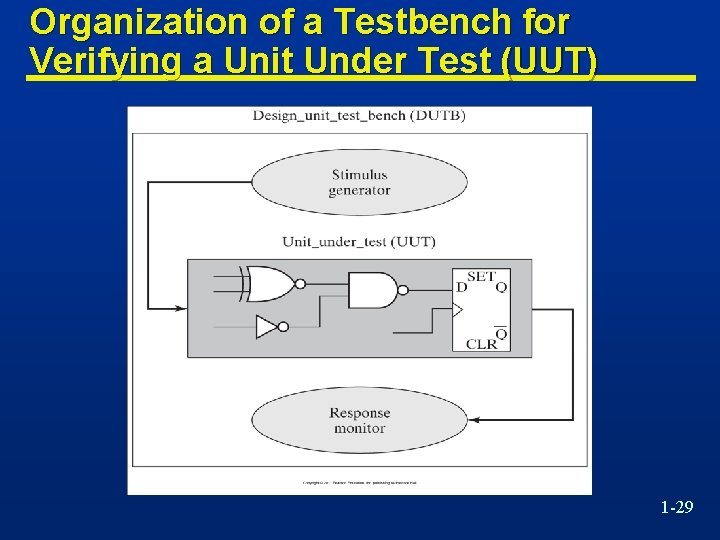

Organization of a Testbench for Verifying a Unit Under Test (UUT) 1 -29

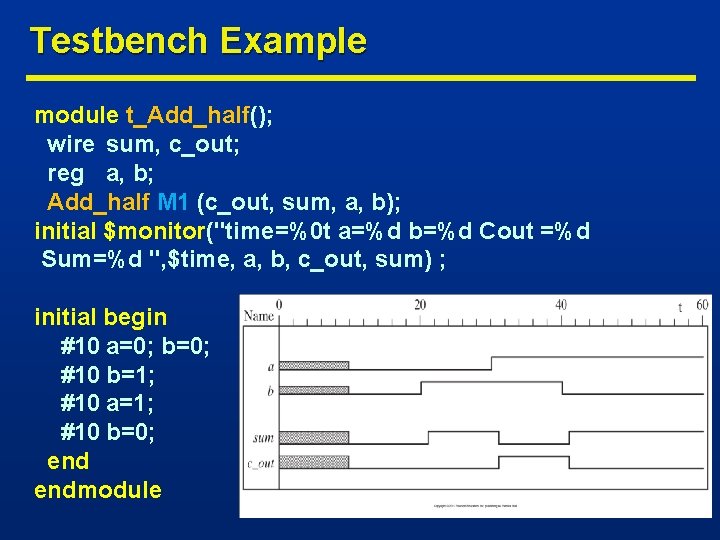

Testbench Example module t_Add_half(); wire sum, c_out; reg a, b; Add_half M 1 (c_out, sum, a, b); initial $monitor("time=%0 t a=%d b=%d Cout =%d Sum=%d ", $time, a, b, c_out, sum) ; initial begin #10 a=0; b=0; #10 b=1; #10 a=1; #10 b=0; endmodule 1 -30

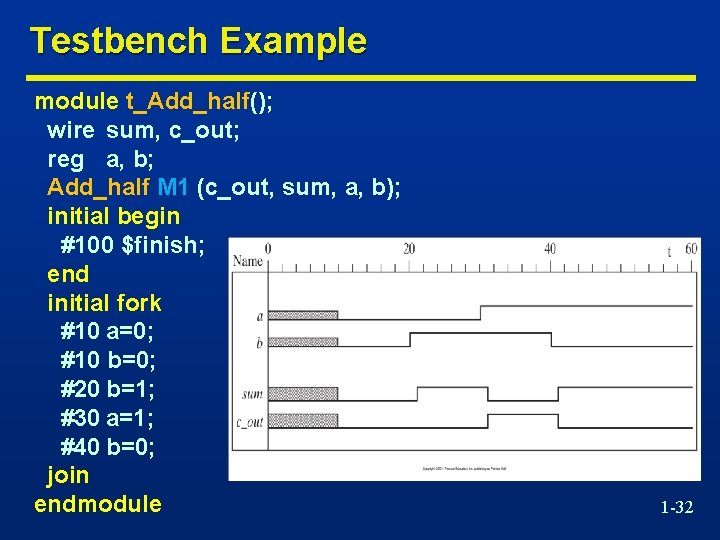

Testbench Example n The keyword initial declares a single-pass behavior that begins executing when the simulator is activated. n Statements within begin and end block keywords are called procedural statements. n Procedural statements execute sequentially n # is a delay control operator n A delay control operator preceding procedural assignment statement suspends its execution and the execution of subsequent statements for specified delay time n reg declaration ensures that variables will keep their value until the next procedural assignment statement n $finish ends simulation 1 -31

Testbench Example module t_Add_half(); wire sum, c_out; reg a, b; Add_half M 1 (c_out, sum, a, b); initial begin #100 $finish; end initial fork #10 a=0; #10 b=0; #20 b=1; #30 a=1; #40 b=0; join endmodule 1 -32

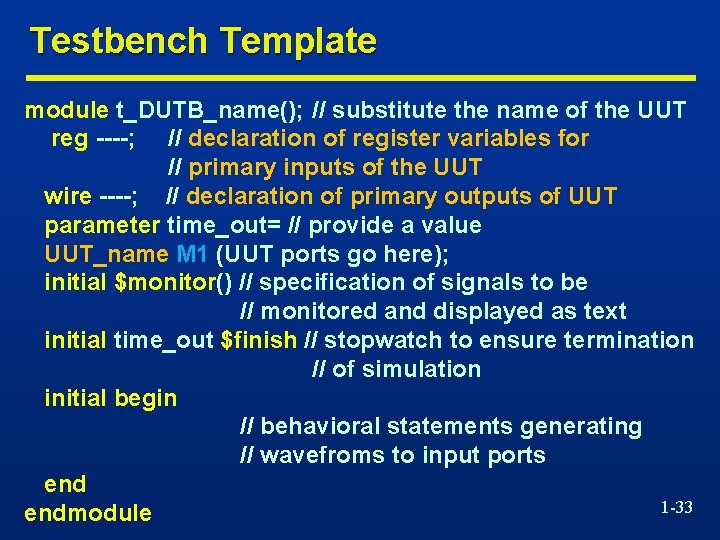

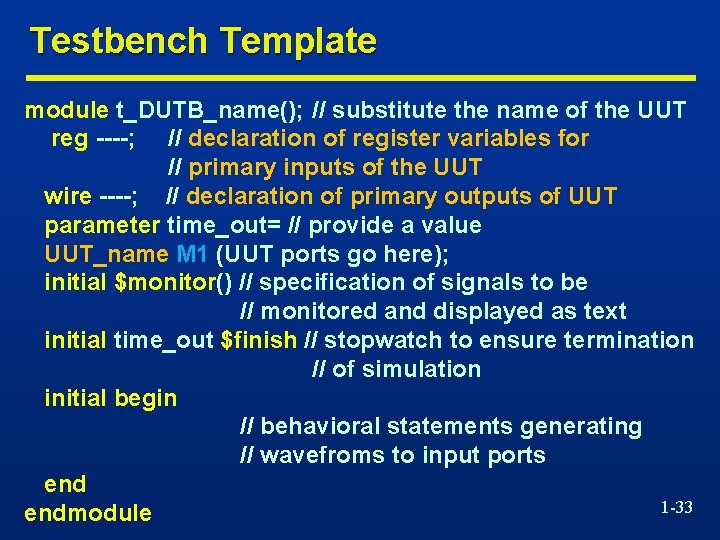

Testbench Template module t_DUTB_name(); // substitute the name of the UUT reg ----; // declaration of register variables for // primary inputs of the UUT wire ----; // declaration of primary outputs of UUT parameter time_out= // provide a value UUT_name M 1 (UUT ports go here); initial $monitor() // specification of signals to be // monitored and displayed as text initial time_out $finish // stopwatch to ensure termination // of simulation initial begin // behavioral statements generating // wavefroms to input ports end 1 -33 endmodule

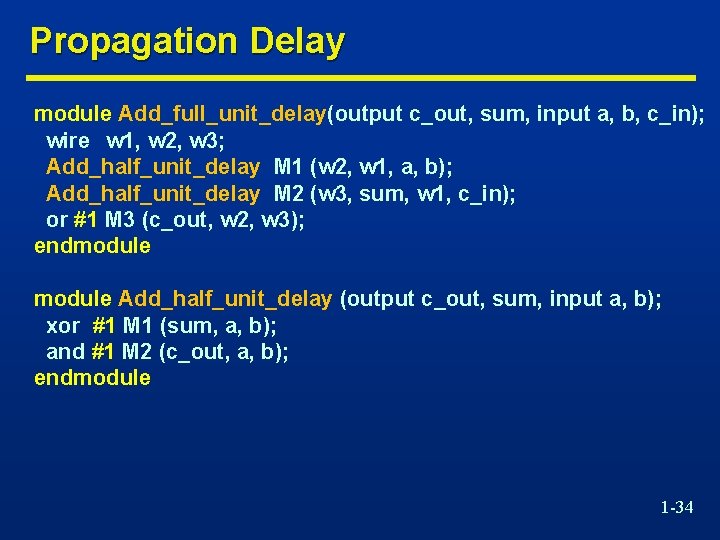

Propagation Delay module Add_full_unit_delay(output c_out, sum, input a, b, c_in); wire w 1, w 2, w 3; Add_half_unit_delay M 1 (w 2, w 1, a, b); Add_half_unit_delay M 2 (w 3, sum, w 1, c_in); or #1 M 3 (c_out, w 2, w 3); endmodule Add_half_unit_delay (output c_out, sum, input a, b); xor #1 M 1 (sum, a, b); and #1 M 2 (c_out, a, b); endmodule 1 -34

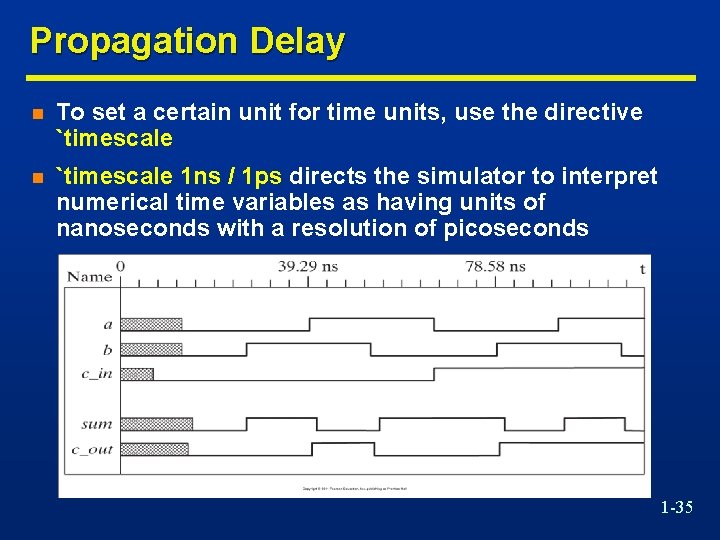

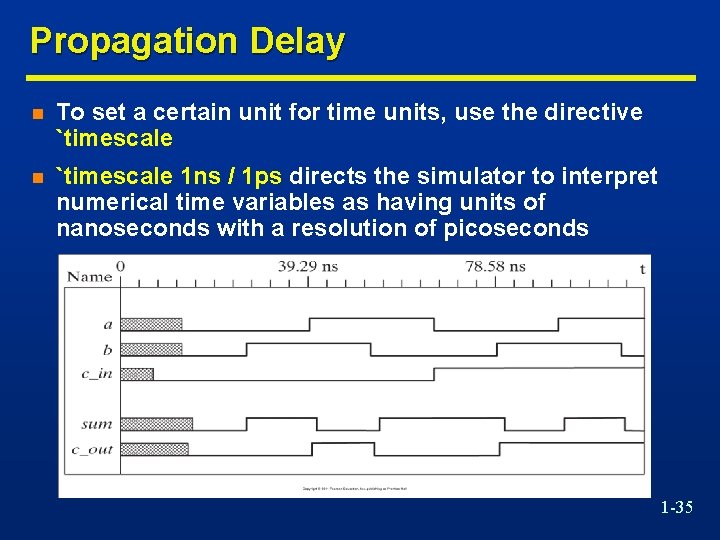

Propagation Delay n To set a certain unit for time units, use the directive `timescale n `timescale 1 ns / 1 ps directs the simulator to interpret numerical time variables as having units of nanoseconds with a resolution of picoseconds 1 -35

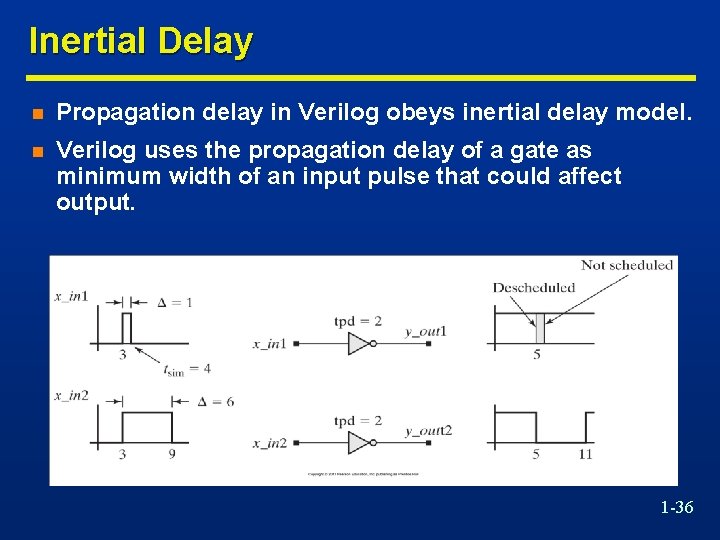

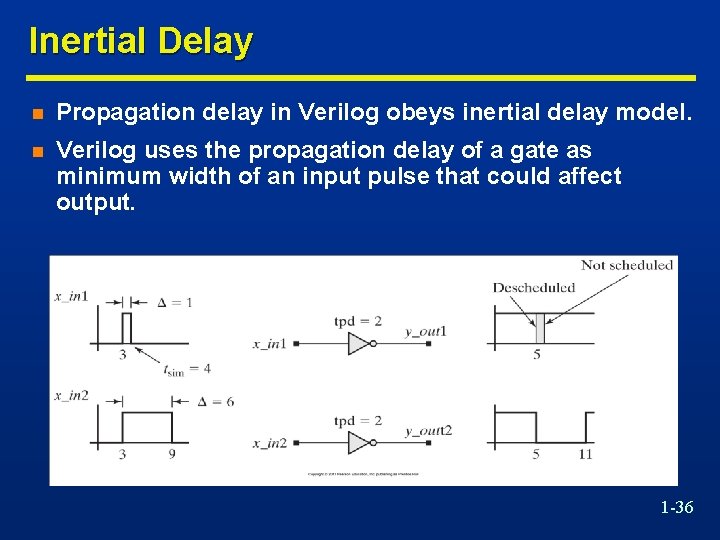

Inertial Delay n Propagation delay in Verilog obeys inertial delay model. n Verilog uses the propagation delay of a gate as minimum width of an input pulse that could affect output. 1 -36

Transport Delay n Propagation delay across a wire is modeled as transport delay i. e. narrow pulses are not suppressed n Example • wire #2 A_long_wire declares that A_long_wire has a transport delay of two time steps. 1 -37

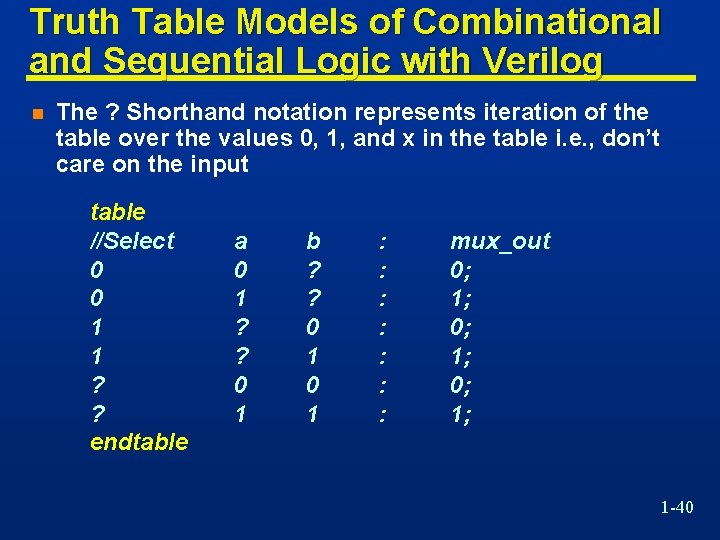

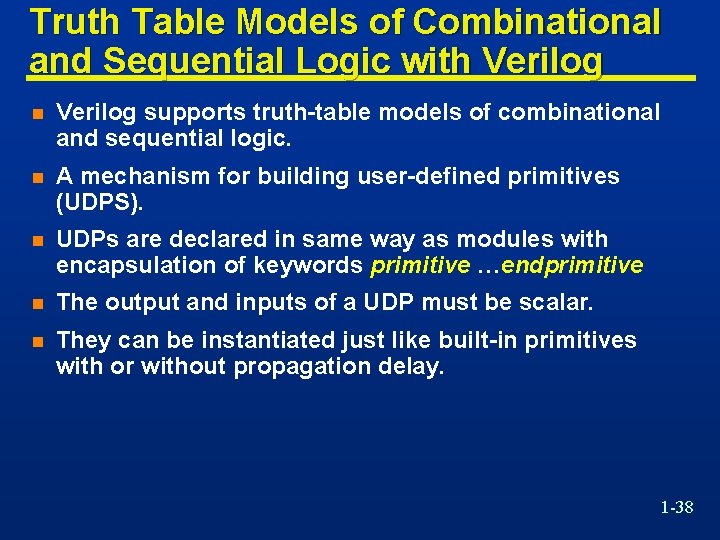

Truth Table Models of Combinational and Sequential Logic with Verilog n Verilog supports truth-table models of combinational and sequential logic. n A mechanism for building user-defined primitives (UDPS). n UDPs are declared in same way as modules with encapsulation of keywords primitive …endprimitive n The output and inputs of a UDP must be scalar. n They can be instantiated just like built-in primitives with or without propagation delay. 1 -38

Truth Table Models of Combinational and Sequential Logic with Verilog 1 -39

Truth Table Models of Combinational and Sequential Logic with Verilog n The ? Shorthand notation represents iteration of the table over the values 0, 1, and x in the table i. e. , don’t care on the input table //Select 0 0 1 1 ? ? endtable a 0 1 ? ? 0 1 b ? ? 0 1 : : : : mux_out 0; 1; 1 -40

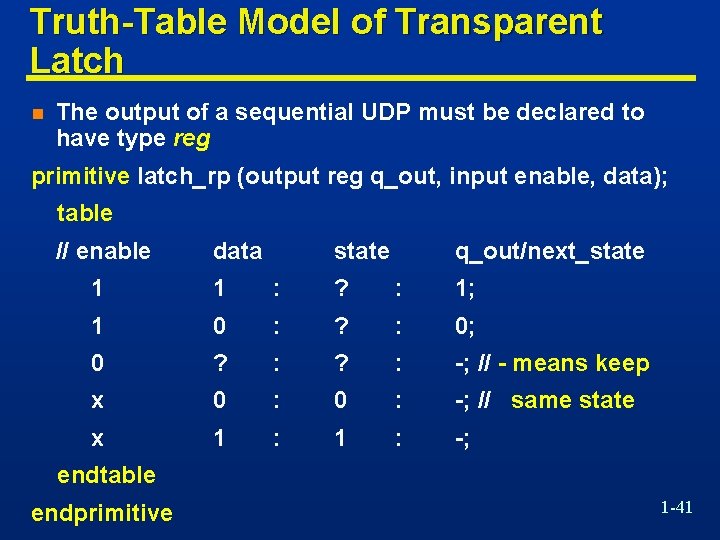

Truth-Table Model of Transparent Latch n The output of a sequential UDP must be declared to have type reg primitive latch_rp (output reg q_out, input enable, data); table // enable data state q_out/next_state 1 1 : ? : 1; 1 0 : ? : 0; 0 ? : -; // - means keep x 0 : -; // same state x 1 : -; endtable endprimitive 1 -41

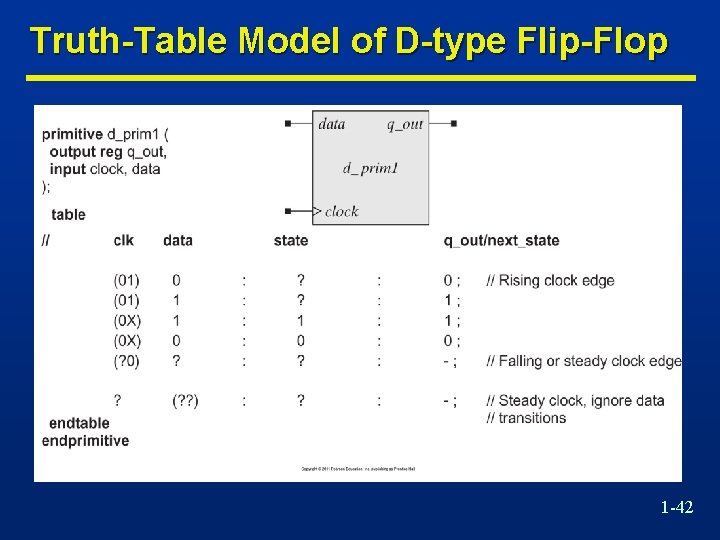

Truth-Table Model of D-type Flip-Flop 1 -42

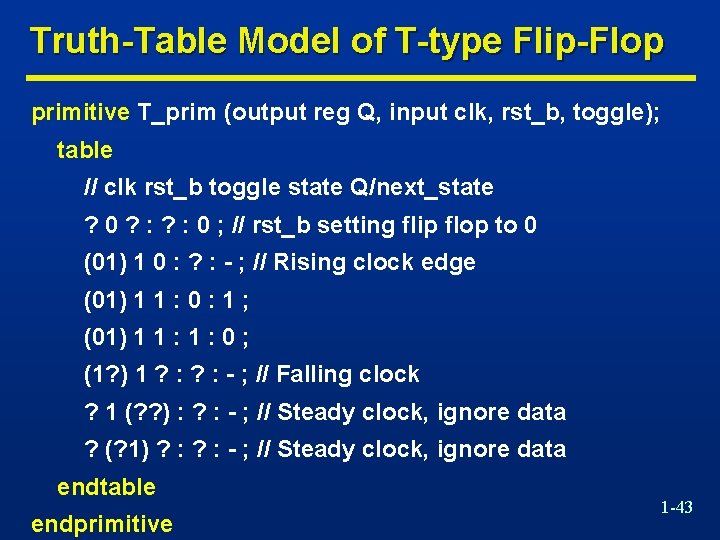

Truth-Table Model of T-type Flip-Flop primitive T_prim (output reg Q, input clk, rst_b, toggle); table // clk rst_b toggle state Q/next_state ? 0 ? : 0 ; // rst_b setting flip flop to 0 (01) 1 0 : ? : - ; // Rising clock edge (01) 1 1 : 0 : 1 ; (01) 1 1 : 0 ; (1? ) 1 ? : - ; // Falling clock ? 1 (? ? ) : ? : - ; // Steady clock, ignore data ? (? 1) ? : - ; // Steady clock, ignore data endtable endprimitive 1 -43