Sequential Circuits Chapter 6 Henry Hexmoor SIUC Henry

- Slides: 88

Sequential Circuits Chapter 6 Henry Hexmoor-- SIUC Henry Hexmoor 1

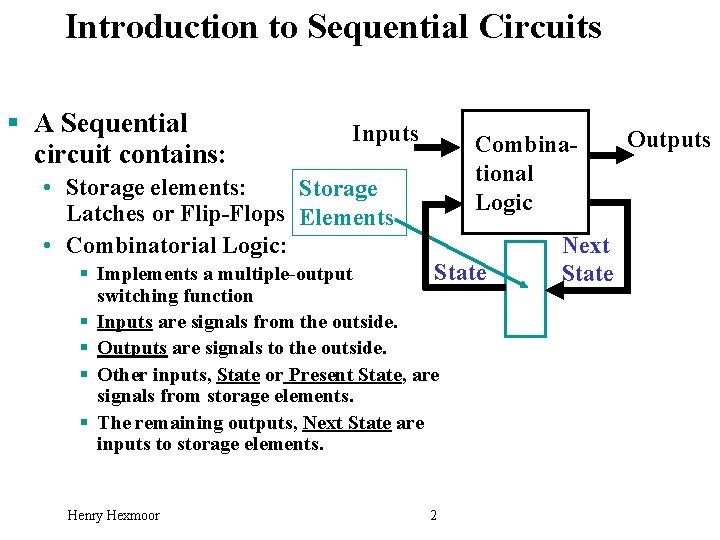

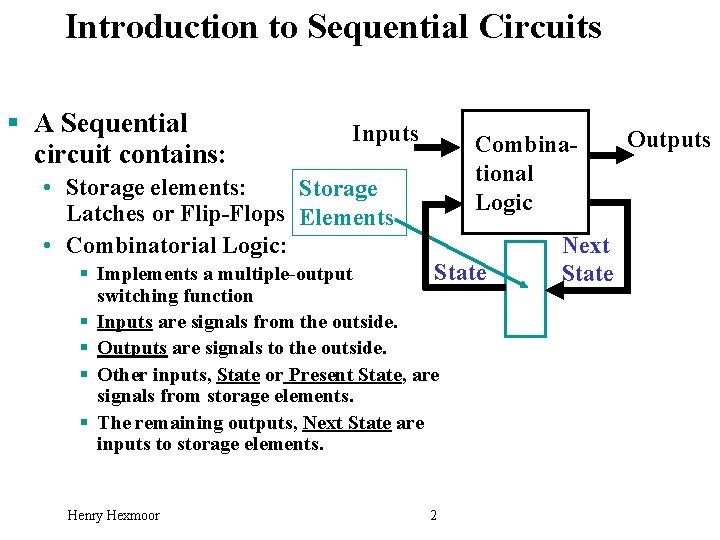

Introduction to Sequential Circuits § A Sequential Inputs Combinacircuit contains: tional Logic • Storage elements: Storage Latches or Flip-Flops Elements • Combinatorial Logic: § Implements a multiple-output State switching function § Inputs are signals from the outside. § Outputs are signals to the outside. § Other inputs, State or Present State, are signals from storage elements. § The remaining outputs, Next State are inputs to storage elements. Henry Hexmoor 2 Next State Outputs

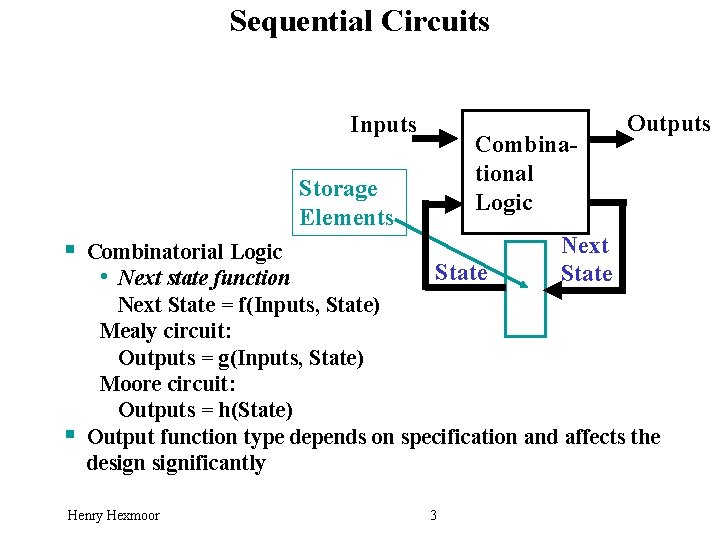

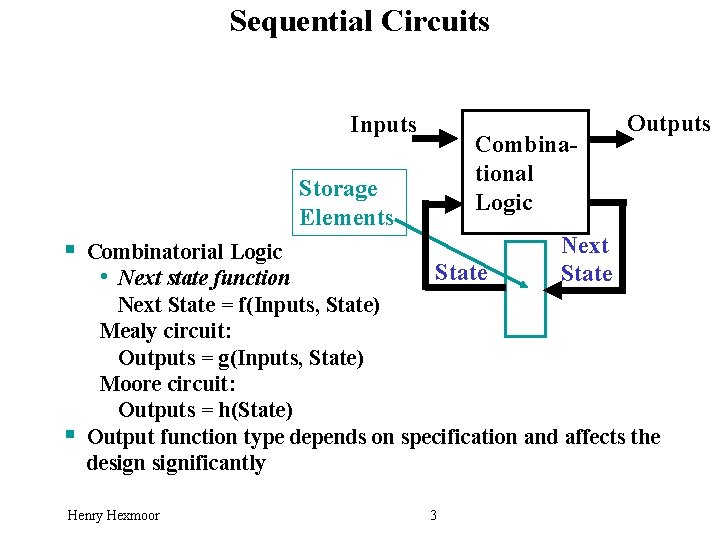

Sequential Circuits Inputs Combinational Logic Storage Elements § Combinatorial Logic • Next state function State Outputs Next State = f(Inputs, State) Mealy circuit: Outputs = g(Inputs, State) Moore circuit: Outputs = h(State) § Output function type depends on specification and affects the designificantly Henry Hexmoor 3

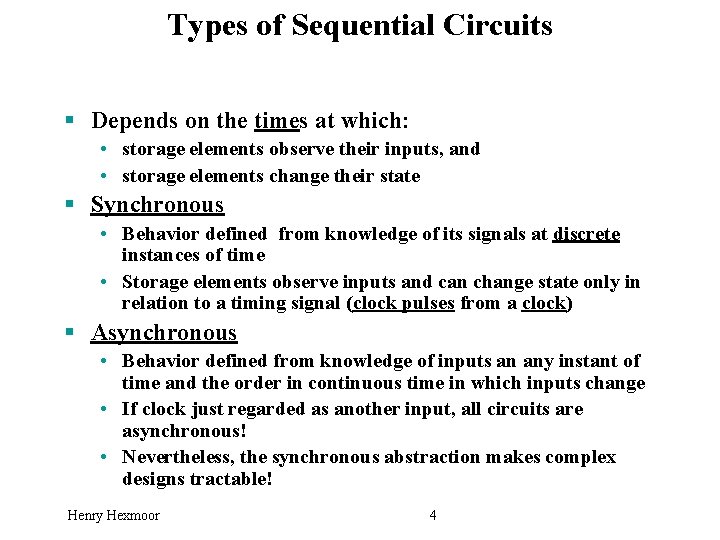

Types of Sequential Circuits § Depends on the times at which: • storage elements observe their inputs, and • storage elements change their state § Synchronous • Behavior defined from knowledge of its signals at discrete instances of time • Storage elements observe inputs and can change state only in relation to a timing signal (clock pulses from a clock) § Asynchronous • Behavior defined from knowledge of inputs an any instant of time and the order in continuous time in which inputs change • If clock just regarded as another input, all circuits are asynchronous! • Nevertheless, the synchronous abstraction makes complex designs tractable! Henry Hexmoor 4

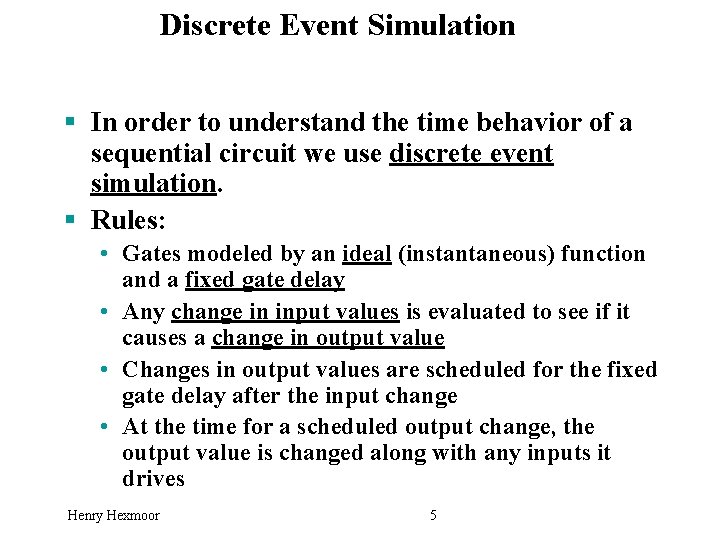

Discrete Event Simulation § In order to understand the time behavior of a sequential circuit we use discrete event simulation. § Rules: • Gates modeled by an ideal (instantaneous) function and a fixed gate delay • Any change in input values is evaluated to see if it causes a change in output value • Changes in output values are scheduled for the fixed gate delay after the input change • At the time for a scheduled output change, the output value is changed along with any inputs it drives Henry Hexmoor 5

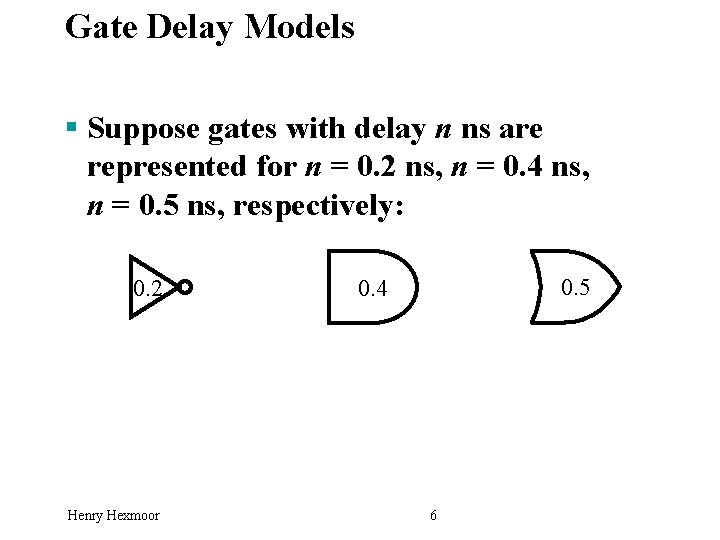

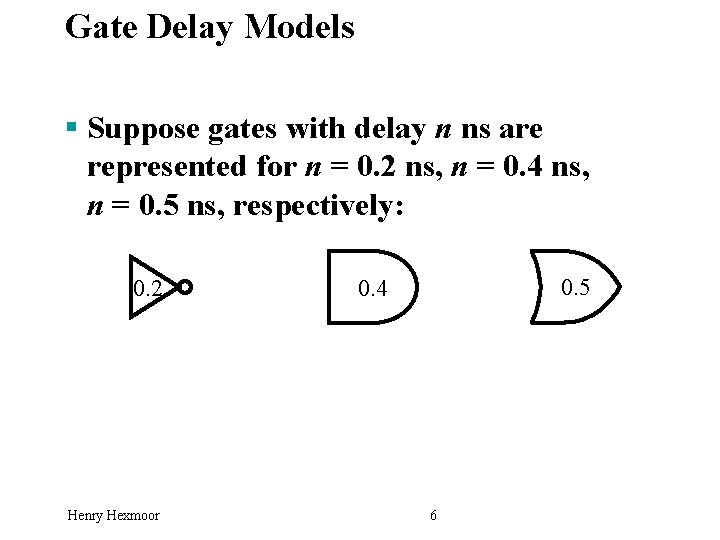

Gate Delay Models § Suppose gates with delay n ns are represented for n = 0. 2 ns, n = 0. 4 ns, n = 0. 5 ns, respectively: 0. 2 Henry Hexmoor 0. 5 0. 4 6

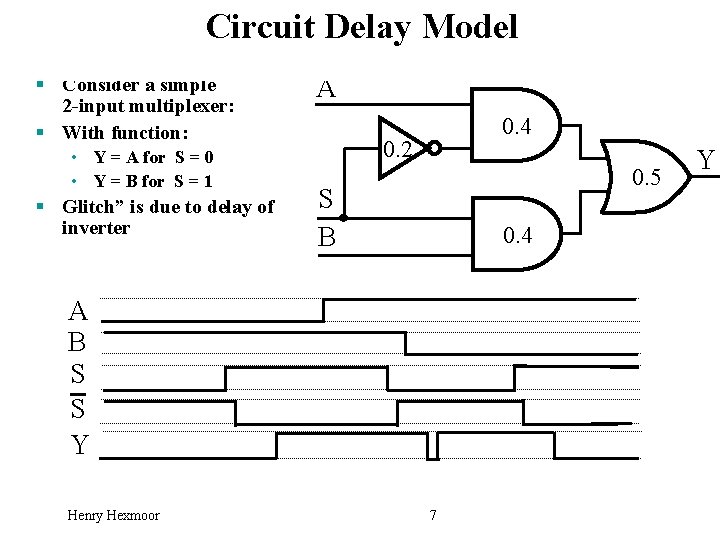

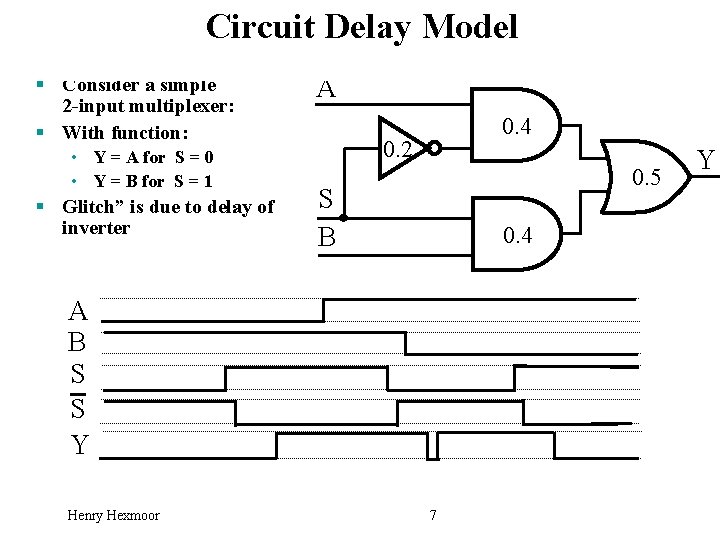

Circuit Delay Model § Consider a simple A 2 -input multiplexer: 0. 4 § With function: • Y = A for S = 0 • Y = B for S = 1 § Glitch” is due to delay of inverter 0. 2 0. 5 S B 0. 4 A B S S Y Henry Hexmoor 7 Y

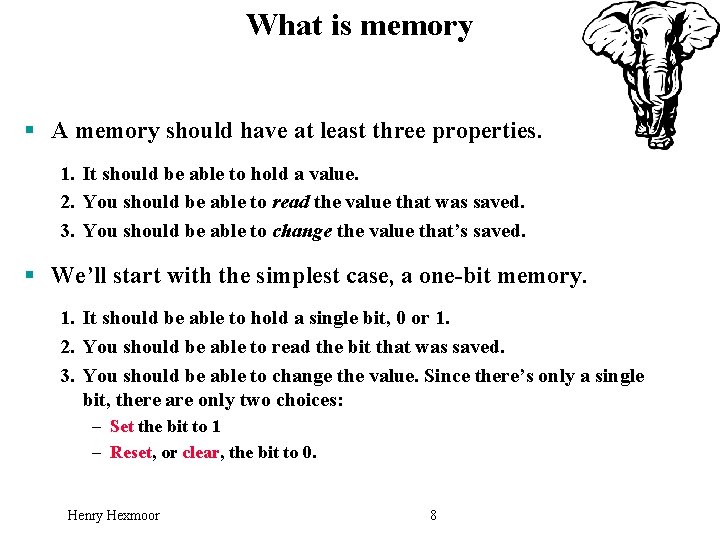

What is memory § A memory should have at least three properties. 1. It should be able to hold a value. 2. You should be able to read the value that was saved. 3. You should be able to change the value that’s saved. § We’ll start with the simplest case, a one-bit memory. 1. It should be able to hold a single bit, 0 or 1. 2. You should be able to read the bit that was saved. 3. You should be able to change the value. Since there’s only a single bit, there are only two choices: – Set the bit to 1 – Reset, or clear, the bit to 0. Henry Hexmoor 8

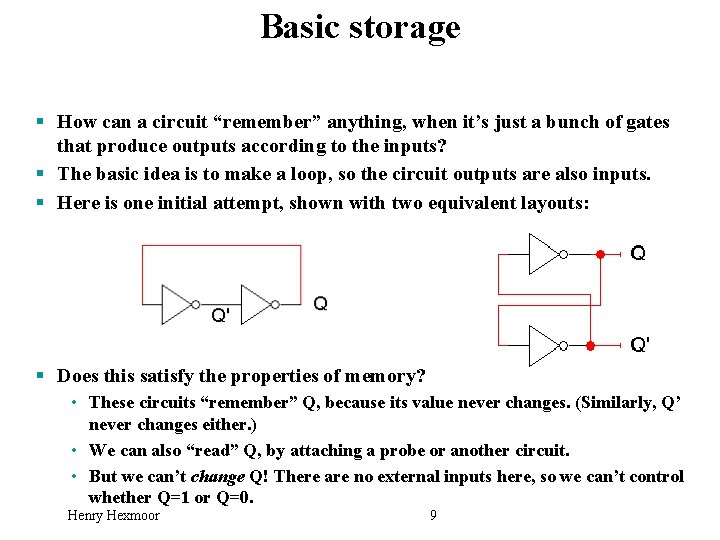

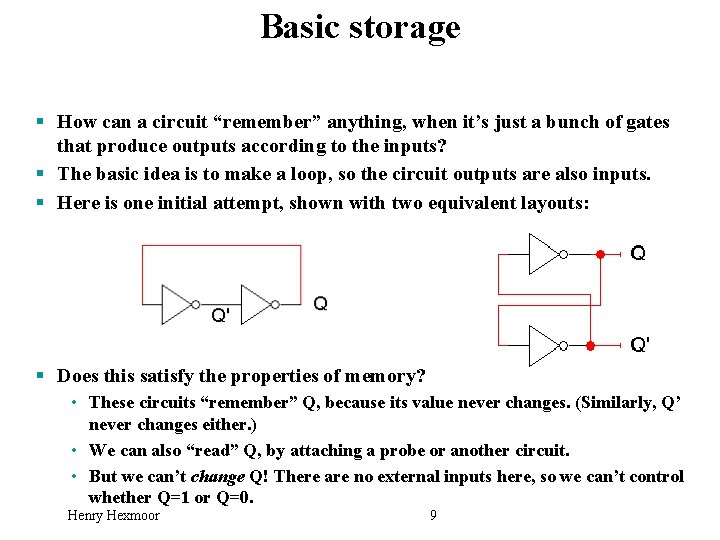

Basic storage § How can a circuit “remember” anything, when it’s just a bunch of gates that produce outputs according to the inputs? § The basic idea is to make a loop, so the circuit outputs are also inputs. § Here is one initial attempt, shown with two equivalent layouts: § Does this satisfy the properties of memory? • These circuits “remember” Q, because its value never changes. (Similarly, Q’ never changes either. ) • We can also “read” Q, by attaching a probe or another circuit. • But we can’t change Q! There are no external inputs here, so we can’t control whether Q=1 or Q=0. Henry Hexmoor 9

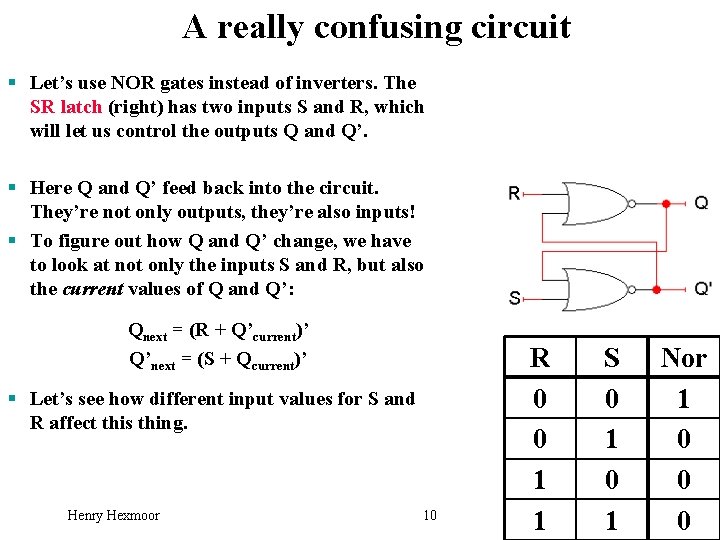

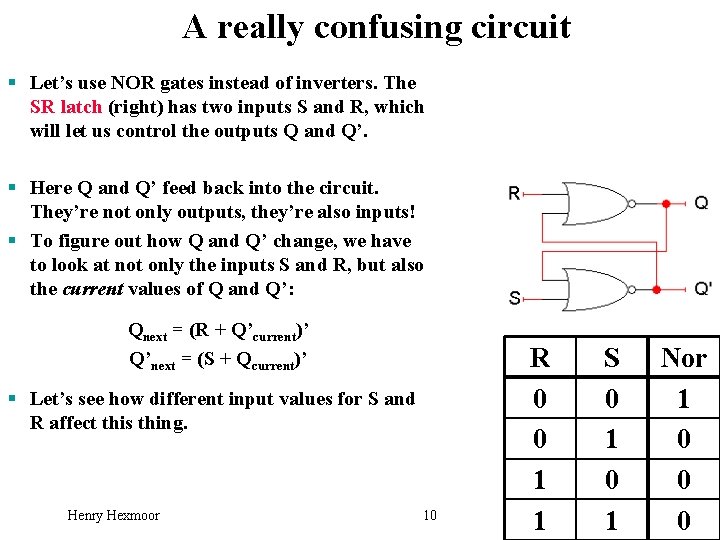

A really confusing circuit § Let’s use NOR gates instead of inverters. The SR latch (right) has two inputs S and R, which will let us control the outputs Q and Q’. § Here Q and Q’ feed back into the circuit. They’re not only outputs, they’re also inputs! § To figure out how Q and Q’ change, we have to look at not only the inputs S and R, but also the current values of Q and Q’: Qnext = (R + Q’current)’ Q’next = (S + Qcurrent)’ § Let’s see how different input values for S and R affect this thing. Henry Hexmoor 10 R 0 0 1 1 S 0 1 Nor 1 0 0 0

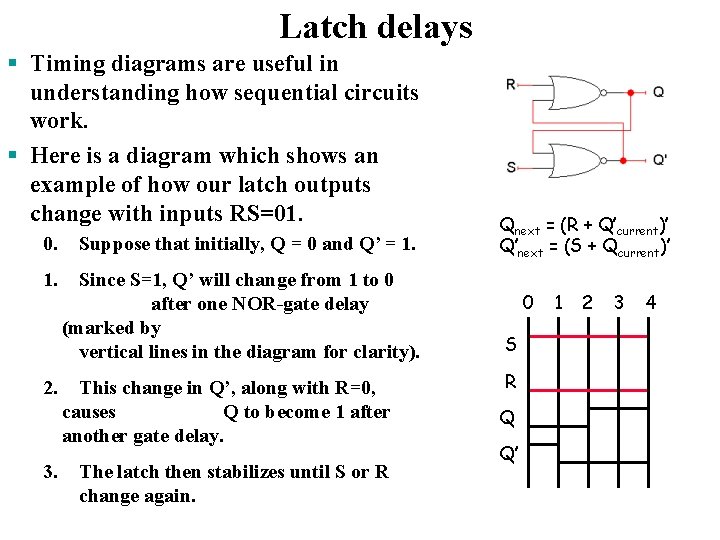

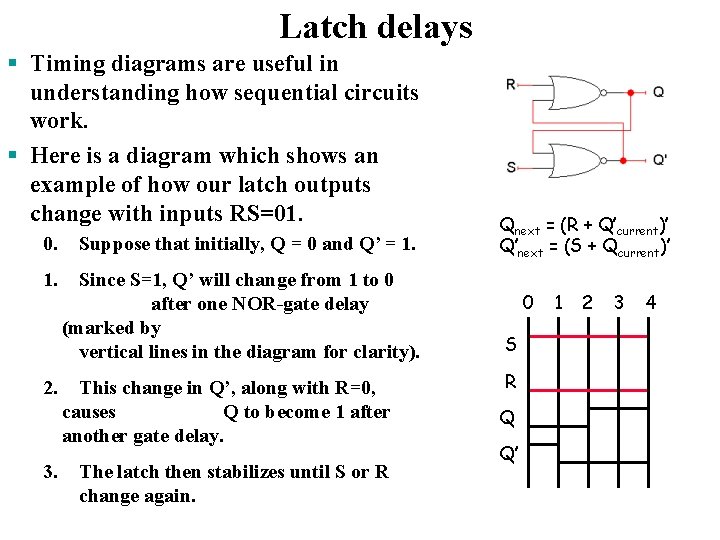

Latch delays § Timing diagrams are useful in understanding how sequential circuits work. § Here is a diagram which shows an example of how our latch outputs change with inputs RS=01. 0. Suppose that initially, Q = 0 and Q’ = 1. Since S=1, Q’ will change from 1 to 0 after one NOR-gate delay (marked by vertical lines in the diagram for clarity). 2. 3. 0 S R This change in Q’, along with R=0, causes Q to become 1 after another gate delay. Q Q’ The latch then stabilizes until S or R change again. Henry Hexmoor Qnext = (R + Q’current)’ Q’next = (S + Qcurrent)’ 11 1 2 3 4

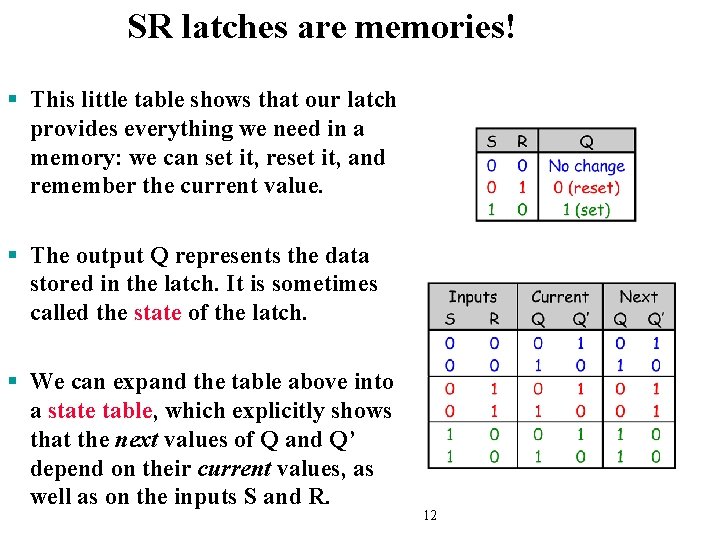

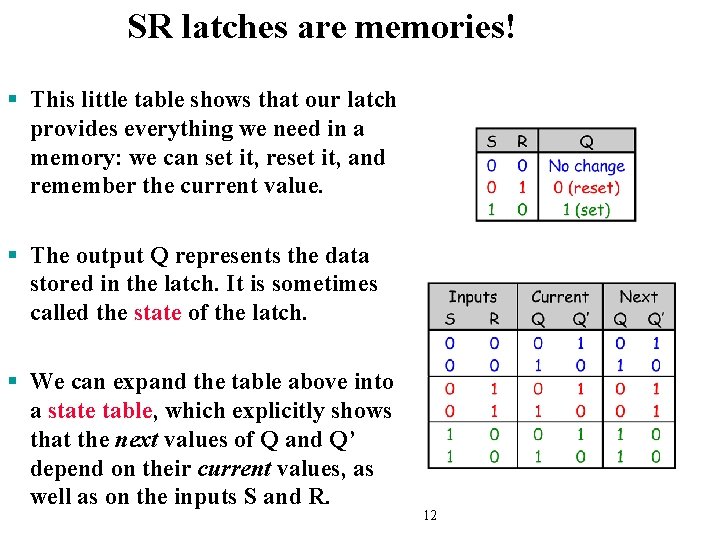

SR latches are memories! § This little table shows that our latch provides everything we need in a memory: we can set it, reset it, and remember the current value. § The output Q represents the data stored in the latch. It is sometimes called the state of the latch. § We can expand the table above into a state table, which explicitly shows that the next values of Q and Q’ depend on their current values, as well as on the inputs S and R. Henry Hexmoor 12

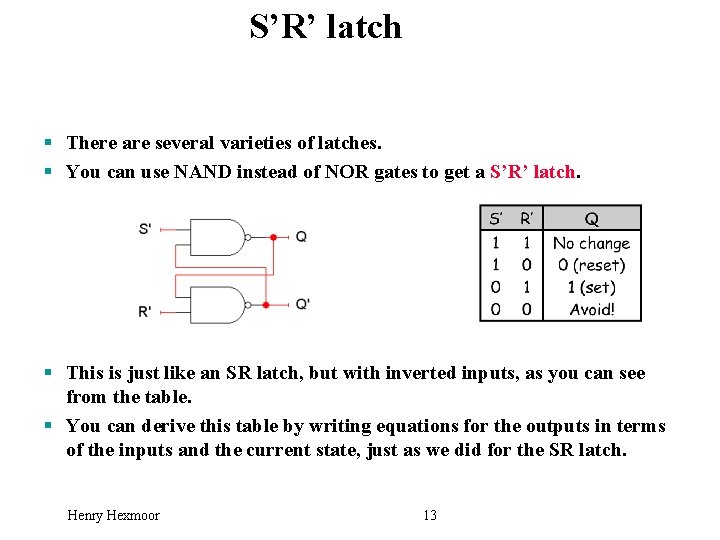

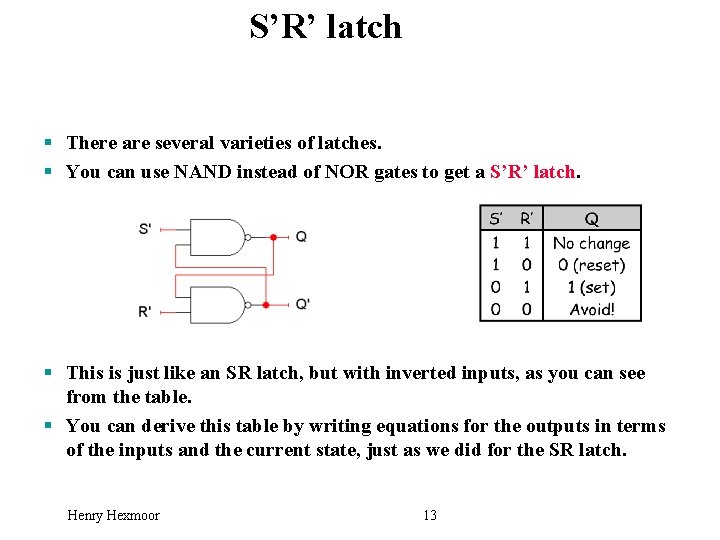

S’R’ latch § There are several varieties of latches. § You can use NAND instead of NOR gates to get a S’R’ latch. § This is just like an SR latch, but with inverted inputs, as you can see from the table. § You can derive this table by writing equations for the outputs in terms of the inputs and the current state, just as we did for the SR latch. Henry Hexmoor 13

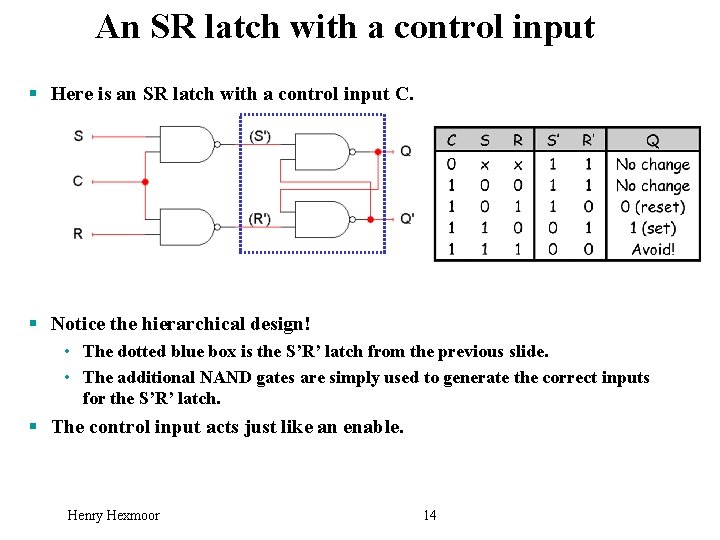

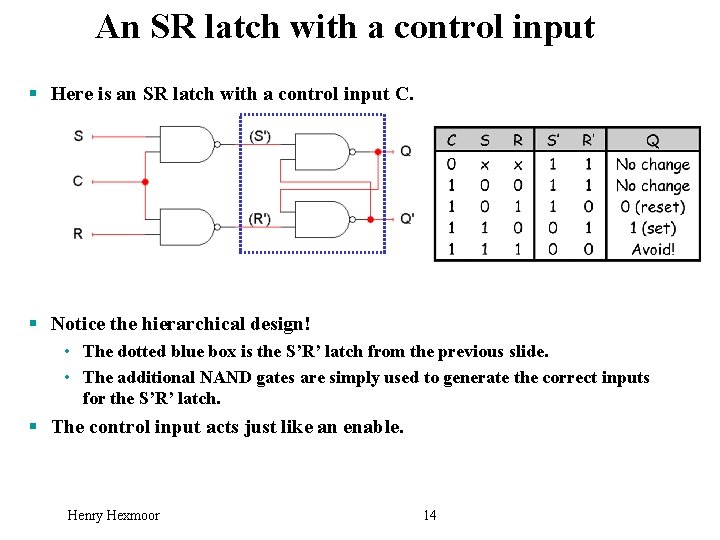

An SR latch with a control input § Here is an SR latch with a control input C. § Notice the hierarchical design! • The dotted blue box is the S’R’ latch from the previous slide. • The additional NAND gates are simply used to generate the correct inputs for the S’R’ latch. § The control input acts just like an enable. Henry Hexmoor 14

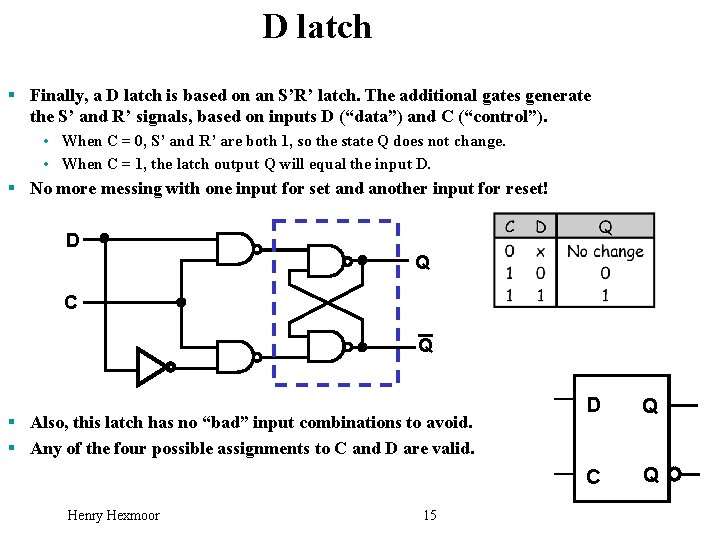

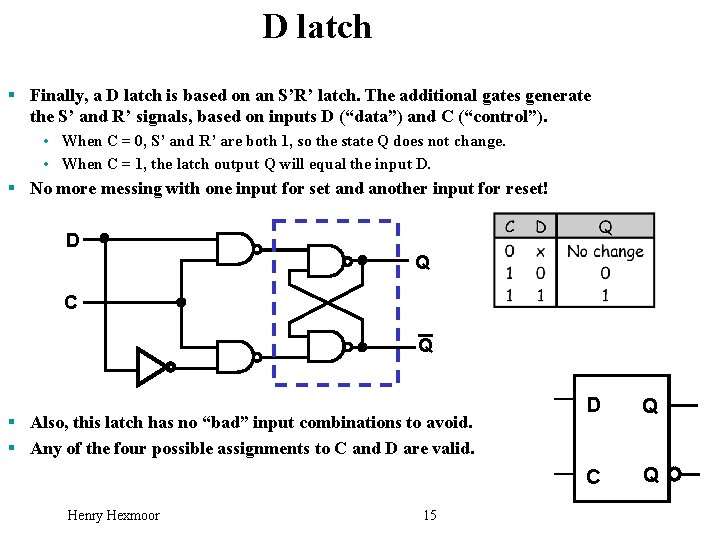

D latch § Finally, a D latch is based on an S’R’ latch. The additional gates generate the S’ and R’ signals, based on inputs D (“data”) and C (“control”). • When C = 0, S’ and R’ are both 1, so the state Q does not change. • When C = 1, the latch output Q will equal the input D. § No more messing with one input for set and another input for reset! D Q C Q § Also, this latch has no “bad” input combinations to avoid. § Any of the four possible assignments to C and D are valid. Henry Hexmoor 15 D Q C Q

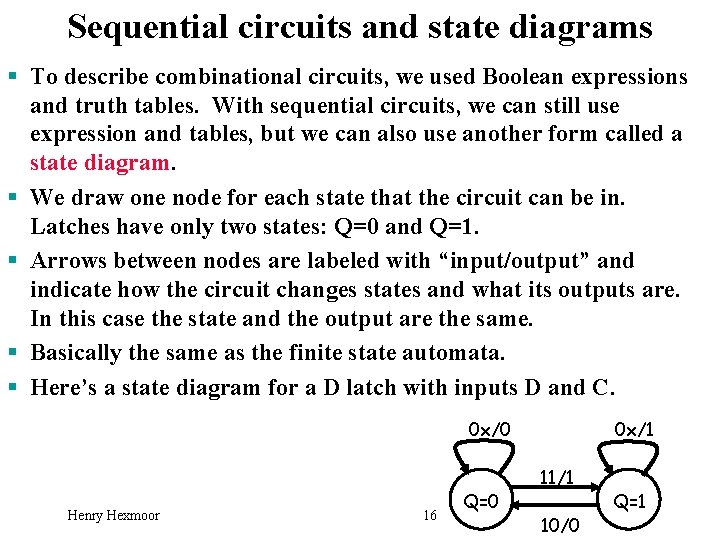

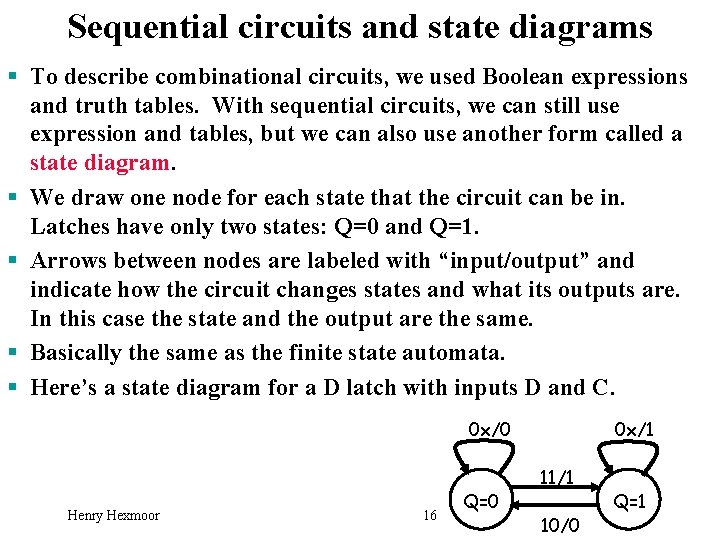

Sequential circuits and state diagrams § To describe combinational circuits, we used Boolean expressions and truth tables. With sequential circuits, we can still use expression and tables, but we can also use another form called a state diagram. § We draw one node for each state that the circuit can be in. Latches have only two states: Q=0 and Q=1. § Arrows between nodes are labeled with “input/output” and indicate how the circuit changes states and what its outputs are. In this case the state and the output are the same. § Basically the same as the finite state automata. § Here’s a state diagram for a D latch with inputs D and C. 0 x/0 Henry Hexmoor 16 Q=0 0 x/1 11/1 10/0 Q=1

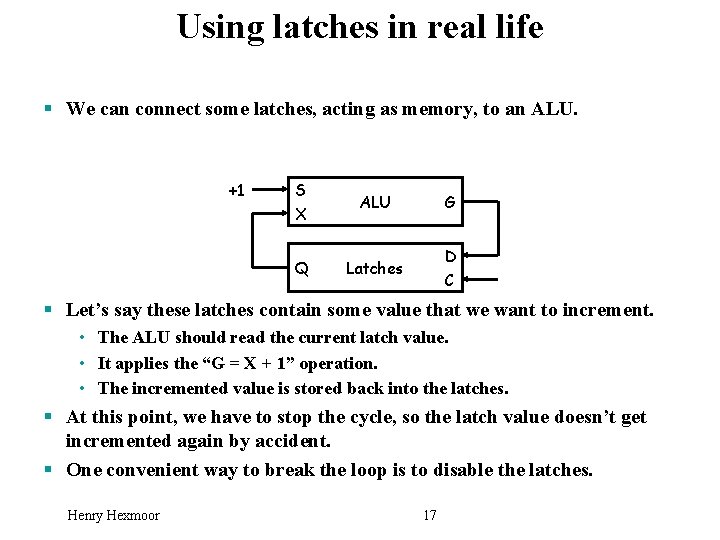

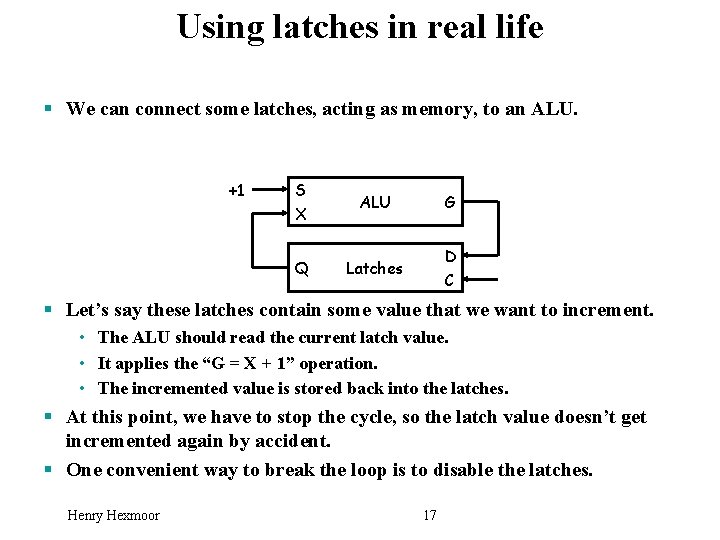

Using latches in real life § We can connect some latches, acting as memory, to an ALU. +1 S X Q ALU G D Latches C § Let’s say these latches contain some value that we want to increment. • The ALU should read the current latch value. • It applies the “G = X + 1” operation. • The incremented value is stored back into the latches. § At this point, we have to stop the cycle, so the latch value doesn’t get incremented again by accident. § One convenient way to break the loop is to disable the latches. Henry Hexmoor 17

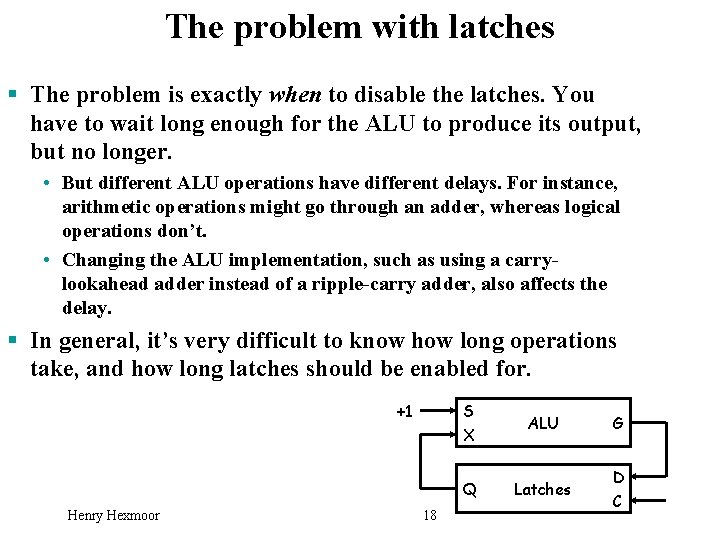

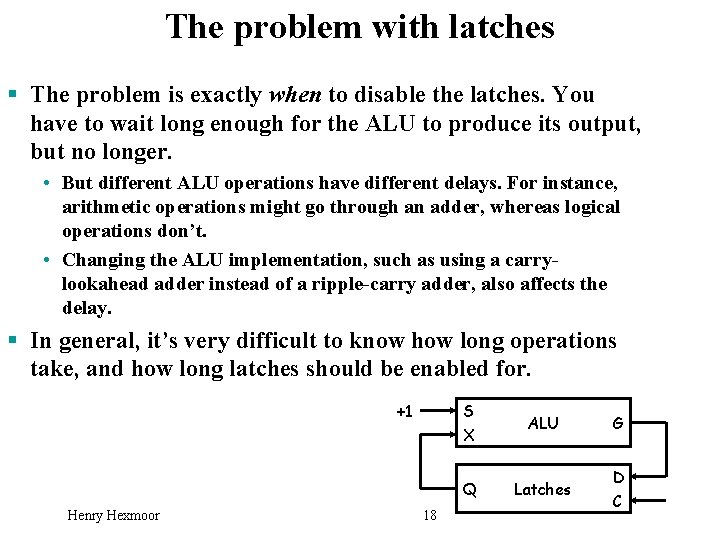

The problem with latches § The problem is exactly when to disable the latches. You have to wait long enough for the ALU to produce its output, but no longer. • But different ALU operations have different delays. For instance, arithmetic operations might go through an adder, whereas logical operations don’t. • Changing the ALU implementation, such as using a carrylookahead adder instead of a ripple-carry adder, also affects the delay. § In general, it’s very difficult to know how long operations take, and how long latches should be enabled for. +1 Henry Hexmoor 18 S X ALU G Q Latches D C

Memory Summary § A sequential circuit has memory. It may respond differently to the same inputs, depending on its current state. § Memories can be created by making circuits with feedback. • Latches are the simplest memory units, storing individual bits. • It’s difficult to control the timing of latches in a larger circuit. § Next, we’ll improve upon latches with flip-flops, which change state only at well-defined times. We will then use flip-flops to build all sequential circuits. Henry Hexmoor 19

Flip-Flops § Latches introduce new problems: • We need to know when to enable a latch. • We also need to quickly disable a latch. • In other words, it’s difficult to control the timing of latches in a large circuit. § We solve these problems with two new elements: clocks and flip-flops • Clocks tell us when to write to our memory. • Flip-flops allow us to quickly write the memory at clearly defined times. • Used together, we can create circuits without worrying about the memory timing. Henry Hexmoor 20

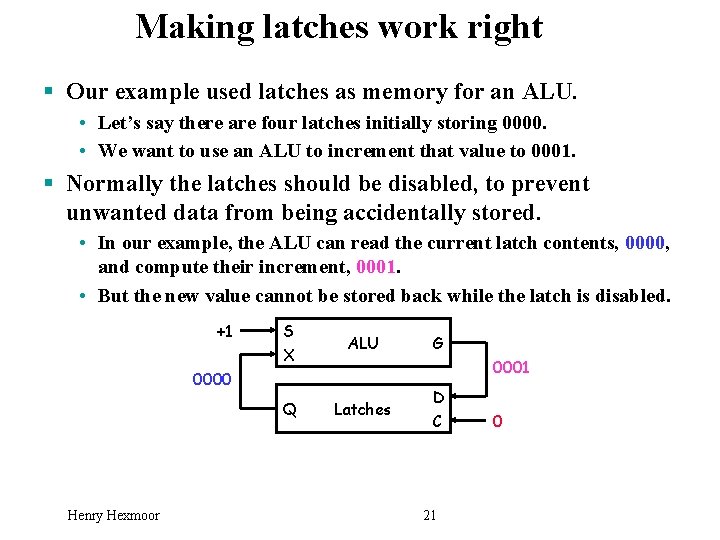

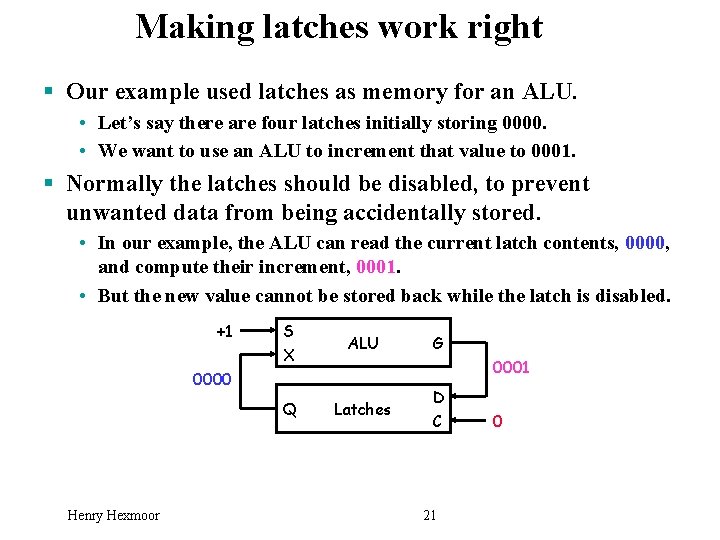

Making latches work right § Our example used latches as memory for an ALU. • Let’s say there are four latches initially storing 0000. • We want to use an ALU to increment that value to 0001. § Normally the latches should be disabled, to prevent unwanted data from being accidentally stored. • In our example, the ALU can read the current latch contents, 0000, and compute their increment, 0001. • But the new value cannot be stored back while the latch is disabled. +1 S X ALU Q Latches 0001 0000 Henry Hexmoor G D C 21 0

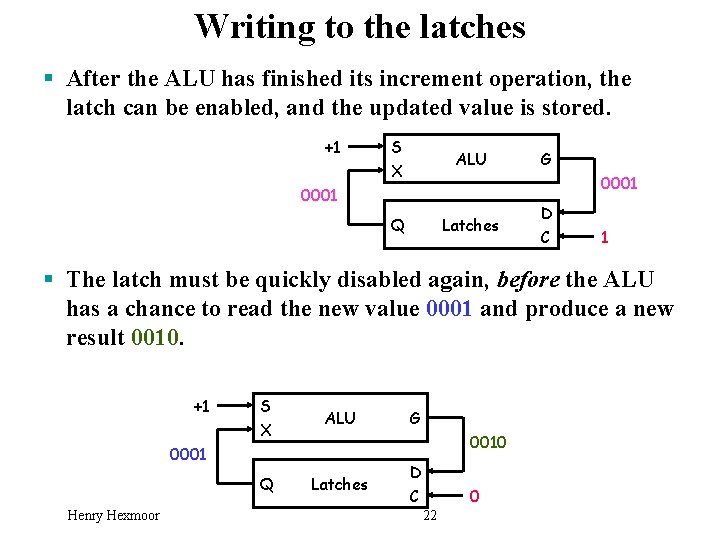

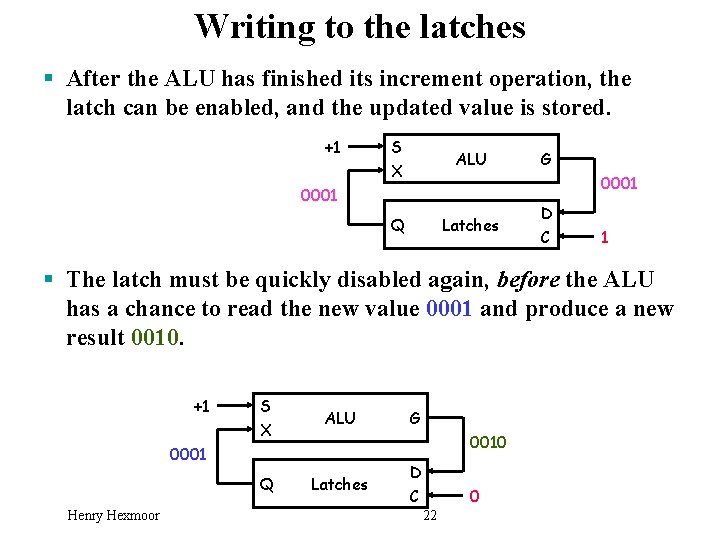

Writing to the latches § After the ALU has finished its increment operation, the latch can be enabled, and the updated value is stored. +1 S ALU X G 0001 Q Latches D C 1 § The latch must be quickly disabled again, before the ALU has a chance to read the new value 0001 and produce a new result 0010. +1 S X ALU Q Latches 0010 0001 Henry Hexmoor G D C 0 22

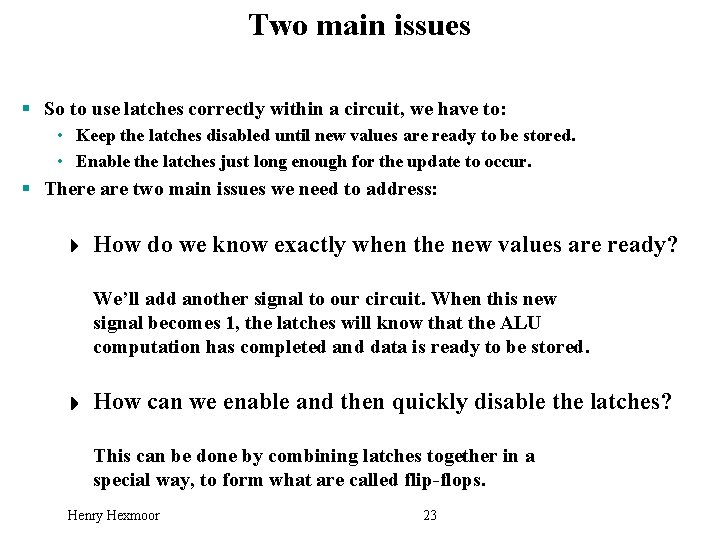

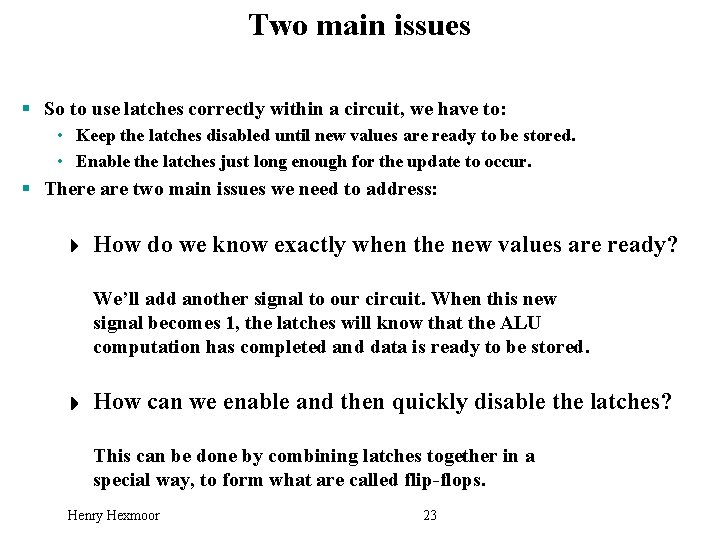

Two main issues § So to use latches correctly within a circuit, we have to: • Keep the latches disabled until new values are ready to be stored. • Enable the latches just long enough for the update to occur. § There are two main issues we need to address: How do we know exactly when the new values are ready? We’ll add another signal to our circuit. When this new signal becomes 1, the latches will know that the ALU computation has completed and data is ready to be stored. How can we enable and then quickly disable the latches? This can be done by combining latches together in a special way, to form what are called flip-flops. Henry Hexmoor 23

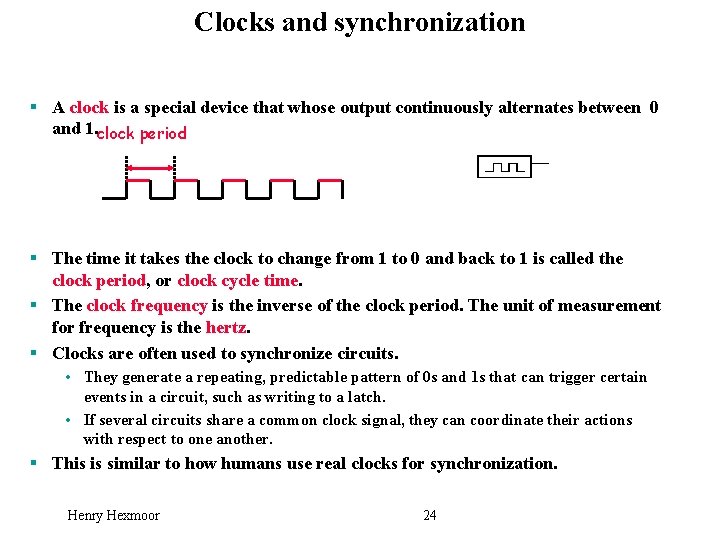

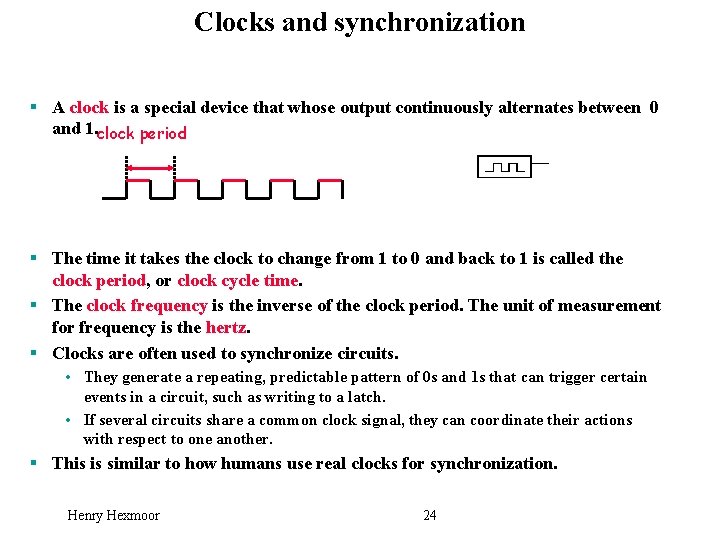

Clocks and synchronization § A clock is a special device that whose output continuously alternates between 0 and 1. clock period § The time it takes the clock to change from 1 to 0 and back to 1 is called the clock period, or clock cycle time. § The clock frequency is the inverse of the clock period. The unit of measurement for frequency is the hertz. § Clocks are often used to synchronize circuits. • They generate a repeating, predictable pattern of 0 s and 1 s that can trigger certain events in a circuit, such as writing to a latch. • If several circuits share a common clock signal, they can coordinate their actions with respect to one another. § This is similar to how humans use real clocks for synchronization. Henry Hexmoor 24

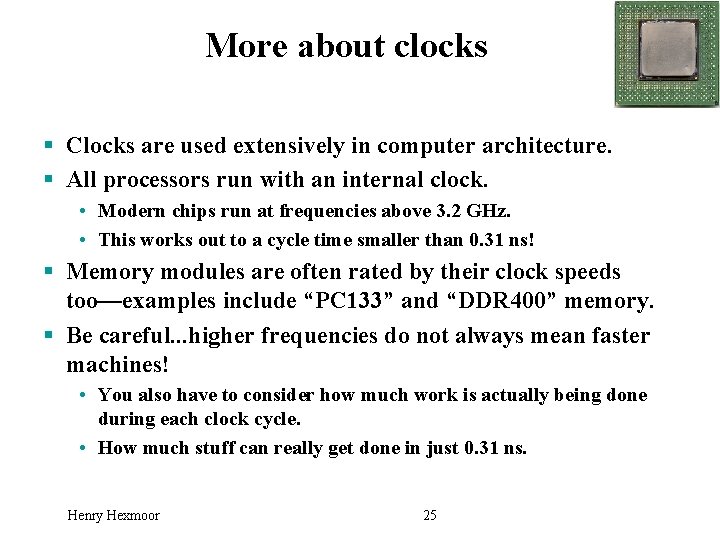

More about clocks § Clocks are used extensively in computer architecture. § All processors run with an internal clock. • Modern chips run at frequencies above 3. 2 GHz. • This works out to a cycle time smaller than 0. 31 ns! § Memory modules are often rated by their clock speeds too—examples include “PC 133” and “DDR 400” memory. § Be careful. . . higher frequencies do not always mean faster machines! • You also have to consider how much work is actually being done during each clock cycle. • How much stuff can really get done in just 0. 31 ns. Henry Hexmoor 25

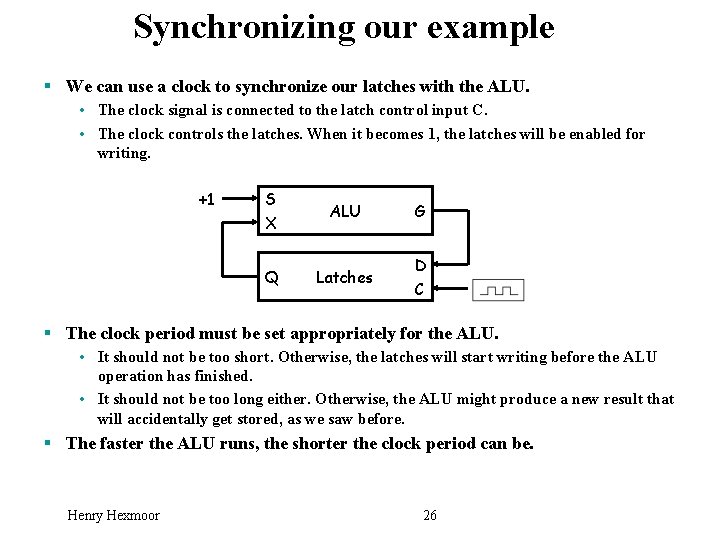

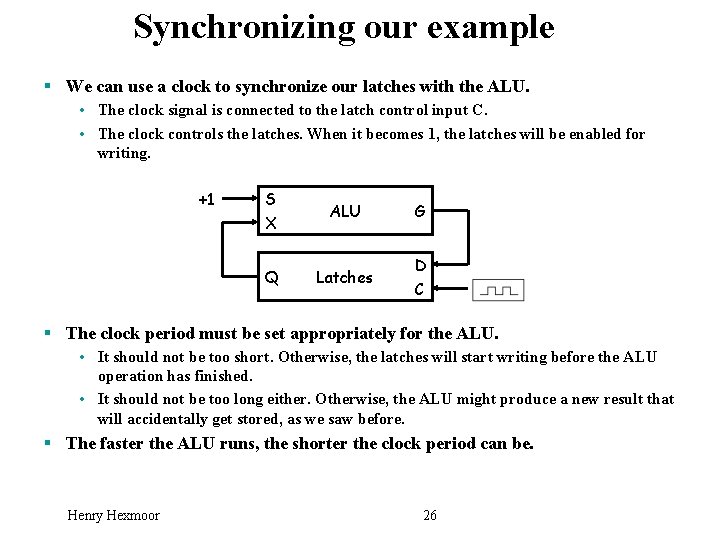

Synchronizing our example § We can use a clock to synchronize our latches with the ALU. • The clock signal is connected to the latch control input C. • The clock controls the latches. When it becomes 1, the latches will be enabled for writing. +1 S X Q ALU Latches G D C § The clock period must be set appropriately for the ALU. • It should not be too short. Otherwise, the latches will start writing before the ALU operation has finished. • It should not be too long either. Otherwise, the ALU might produce a new result that will accidentally get stored, as we saw before. § The faster the ALU runs, the shorter the clock period can be. Henry Hexmoor 26

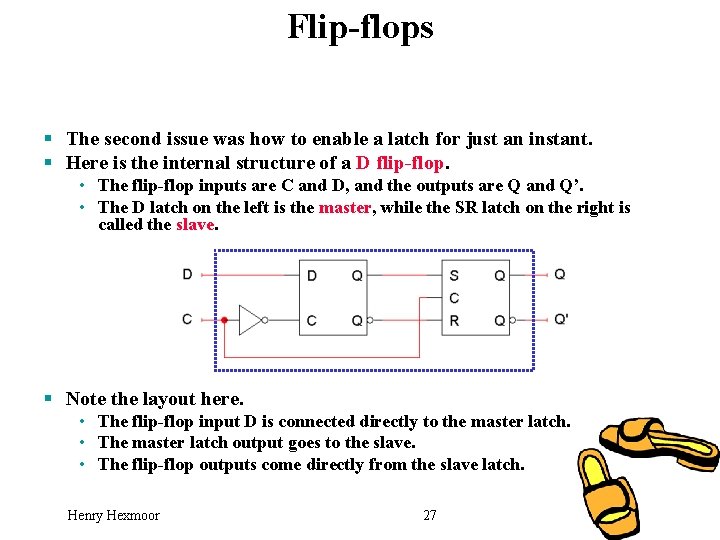

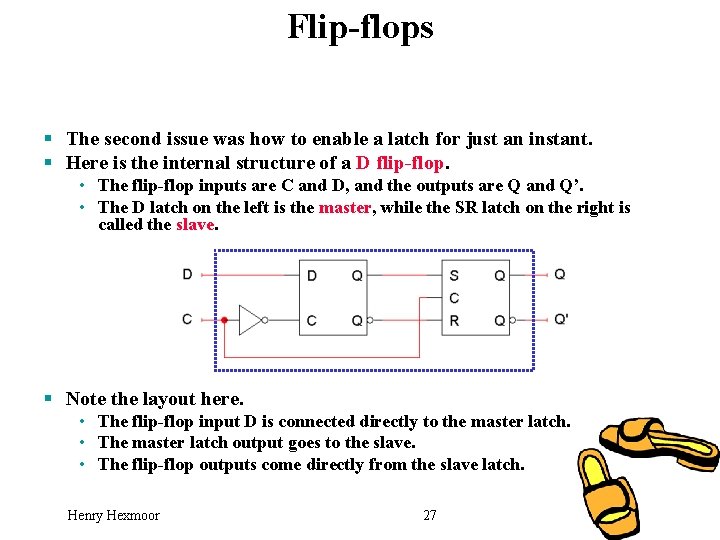

Flip-flops § The second issue was how to enable a latch for just an instant. § Here is the internal structure of a D flip-flop. • The flip-flop inputs are C and D, and the outputs are Q and Q’. • The D latch on the left is the master, while the SR latch on the right is called the slave. § Note the layout here. • The flip-flop input D is connected directly to the master latch. • The master latch output goes to the slave. • The flip-flop outputs come directly from the slave latch. Henry Hexmoor 27

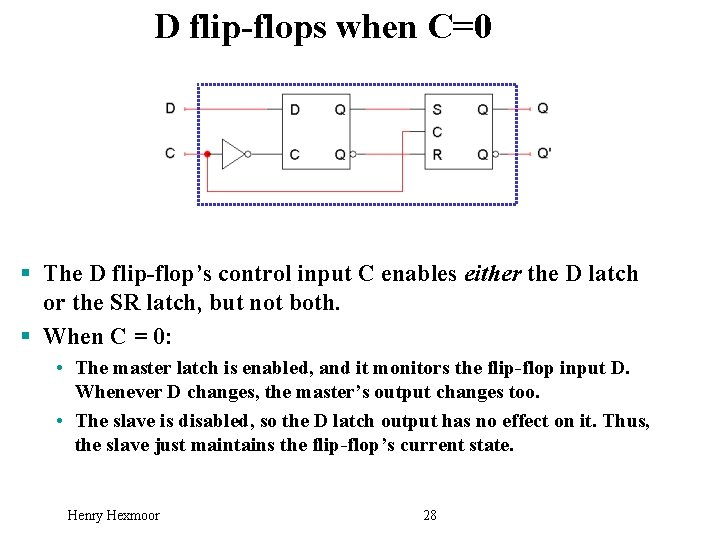

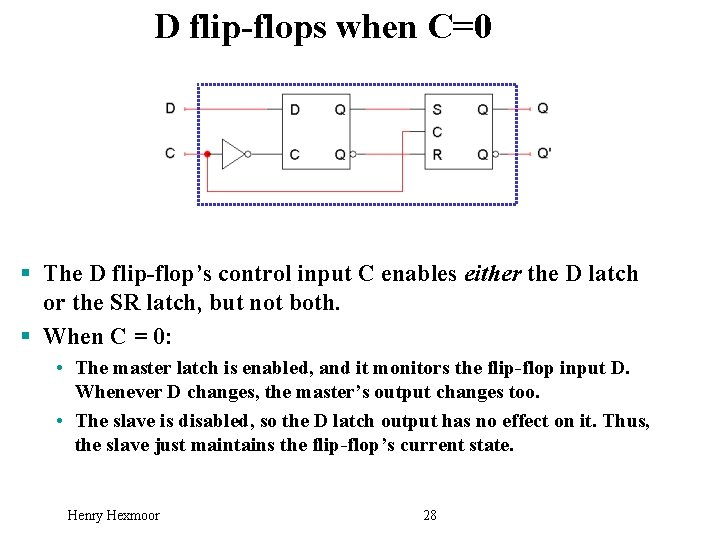

D flip-flops when C=0 § The D flip-flop’s control input C enables either the D latch or the SR latch, but not both. § When C = 0: • The master latch is enabled, and it monitors the flip-flop input D. Whenever D changes, the master’s output changes too. • The slave is disabled, so the D latch output has no effect on it. Thus, the slave just maintains the flip-flop’s current state. Henry Hexmoor 28

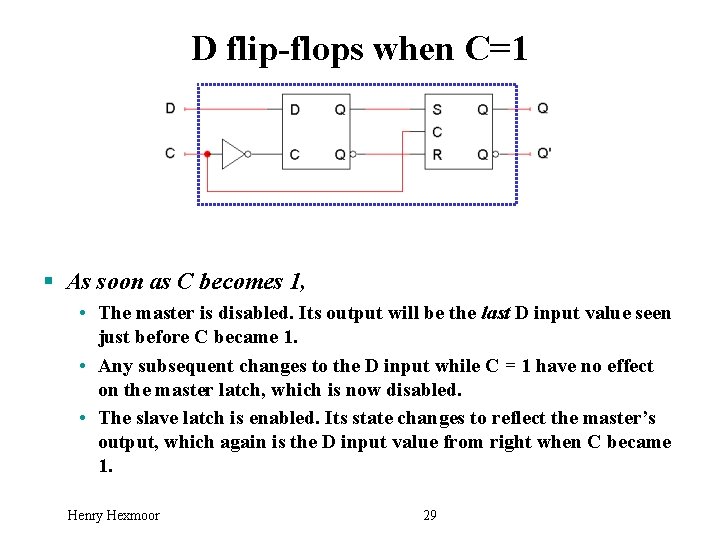

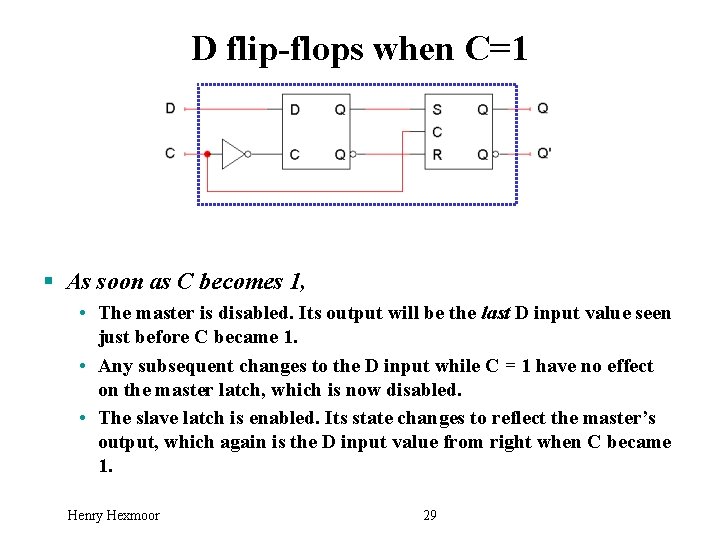

D flip-flops when C=1 § As soon as C becomes 1, • The master is disabled. Its output will be the last D input value seen just before C became 1. • Any subsequent changes to the D input while C = 1 have no effect on the master latch, which is now disabled. • The slave latch is enabled. Its state changes to reflect the master’s output, which again is the D input value from right when C became 1. Henry Hexmoor 29

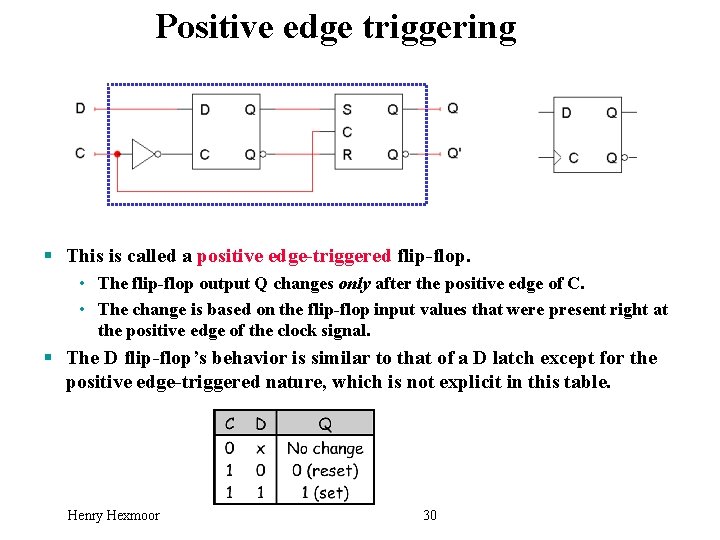

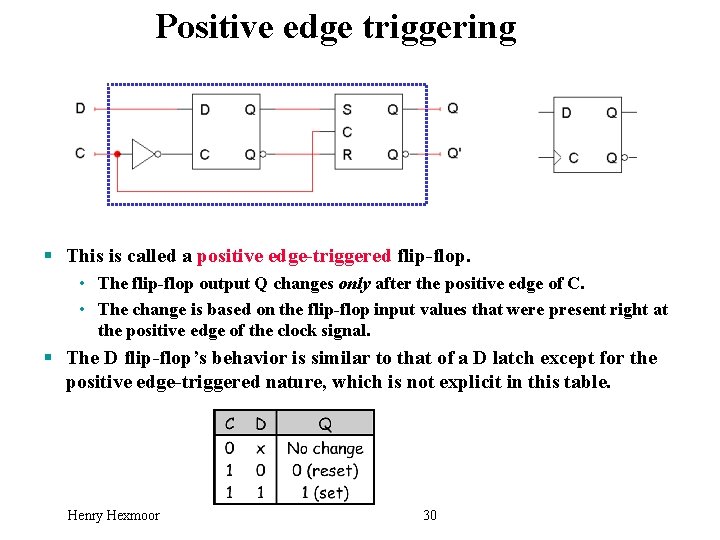

Positive edge triggering § This is called a positive edge-triggered flip-flop. • The flip-flop output Q changes only after the positive edge of C. • The change is based on the flip-flop input values that were present right at the positive edge of the clock signal. § The D flip-flop’s behavior is similar to that of a D latch except for the positive edge-triggered nature, which is not explicit in this table. Henry Hexmoor 30

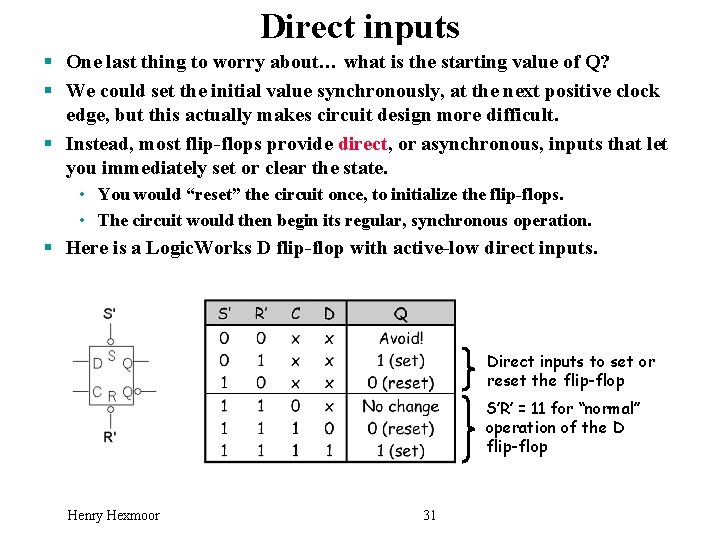

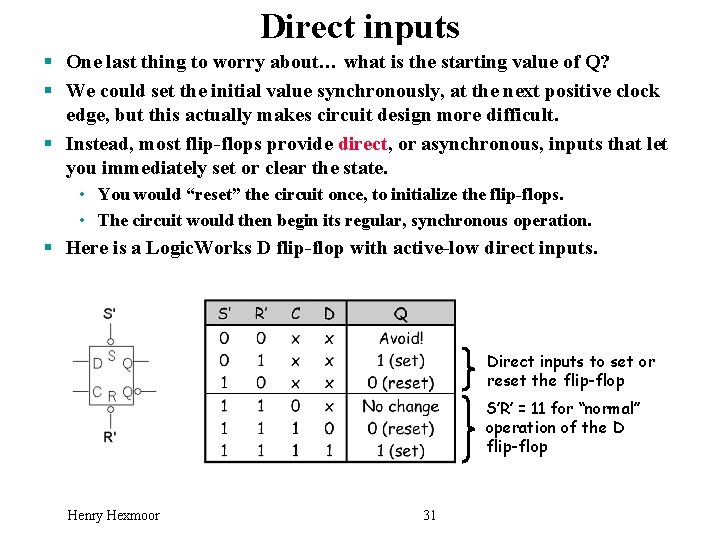

Direct inputs § One last thing to worry about… what is the starting value of Q? § We could set the initial value synchronously, at the next positive clock edge, but this actually makes circuit design more difficult. § Instead, most flip-flops provide direct, or asynchronous, inputs that let you immediately set or clear the state. • You would “reset” the circuit once, to initialize the flip-flops. • The circuit would then begin its regular, synchronous operation. § Here is a Logic. Works D flip-flop with active-low direct inputs. Direct inputs to set or reset the flip-flop S’R’ = 11 for “normal” operation of the D flip-flop Henry Hexmoor 31

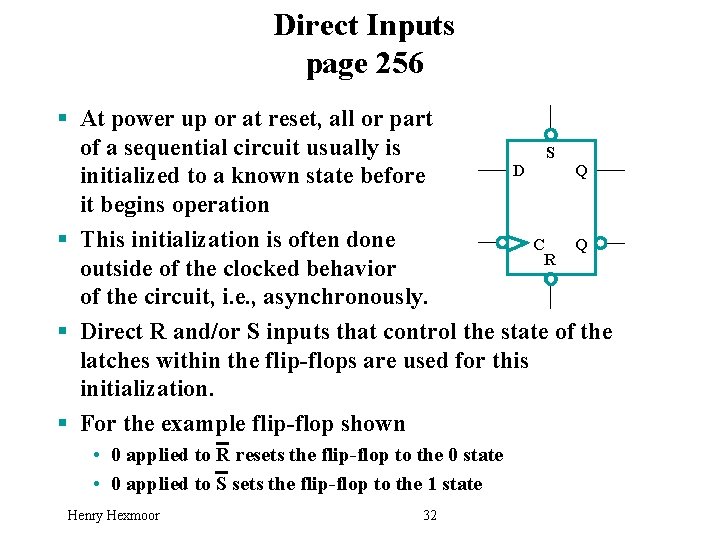

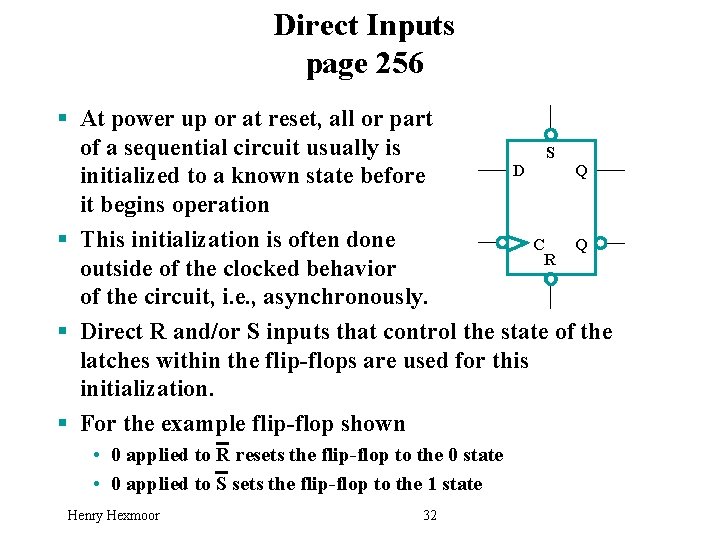

Direct Inputs page 256 § At power up or at reset, all or part of a sequential circuit usually is S D Q initialized to a known state before it begins operation § This initialization is often done C Q R outside of the clocked behavior of the circuit, i. e. , asynchronously. § Direct R and/or S inputs that control the state of the latches within the flip-flops are used for this initialization. § For the example flip-flop shown • 0 applied to R resets the flip-flop to the 0 state • 0 applied to S sets the flip-flop to the 1 state Henry Hexmoor 32

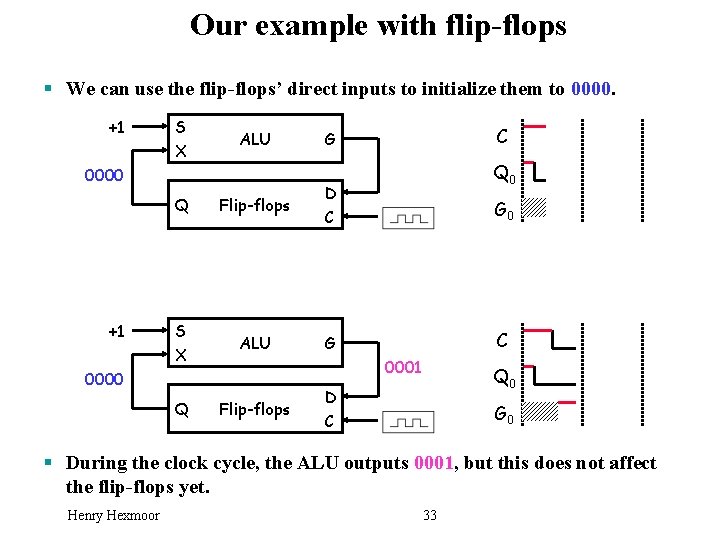

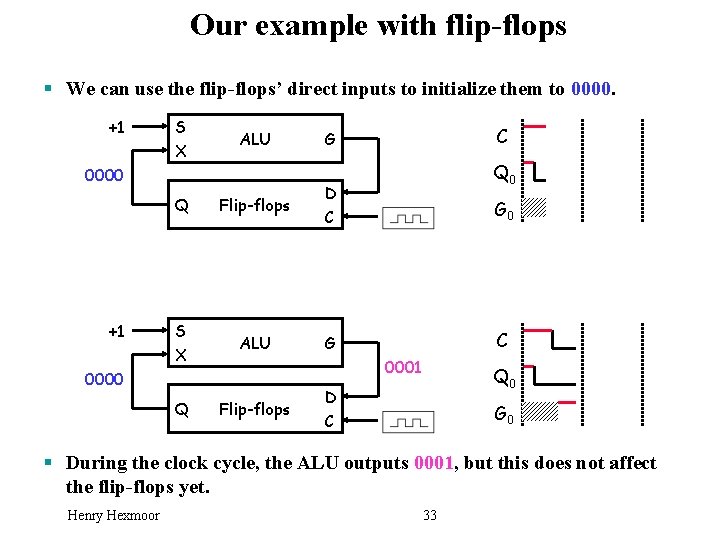

Our example with flip-flops § We can use the flip-flops’ direct inputs to initialize them to 0000. +1 S X ALU 0000 +1 Q Flip-flops S X ALU Q Flip-flops C G Q 0 D C G 0 G C 0001 0000 Q 0 D G 0 C § During the clock cycle, the ALU outputs 0001, but this does not affect the flip-flops yet. Henry Hexmoor 33

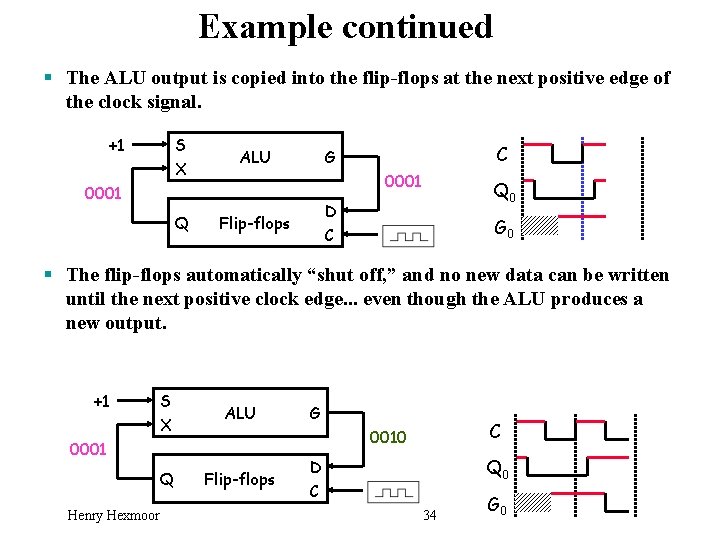

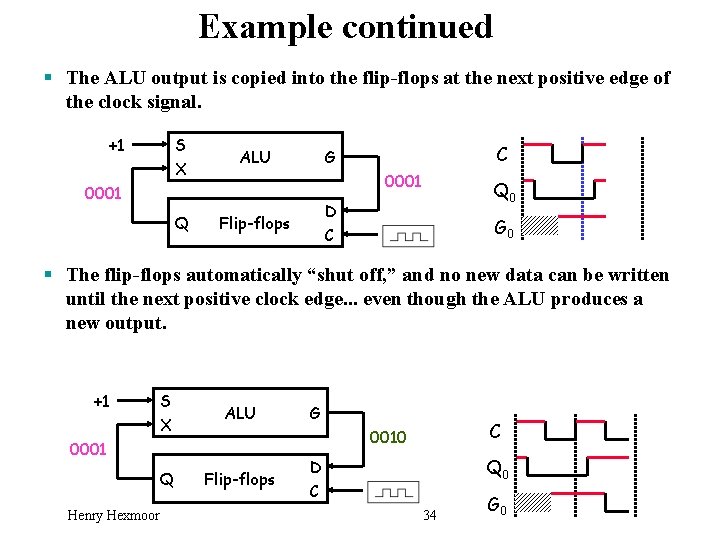

Example continued § The ALU output is copied into the flip-flops at the next positive edge of the clock signal. +1 S X ALU 0001 Q C G Q 0 D Flip-flops G 0 C § The flip-flops automatically “shut off, ” and no new data can be written until the next positive clock edge. . . even though the ALU produces a new output. +1 S X ALU Q Flip-flops C 0010 0001 Henry Hexmoor G Q 0 D C 34 G 0

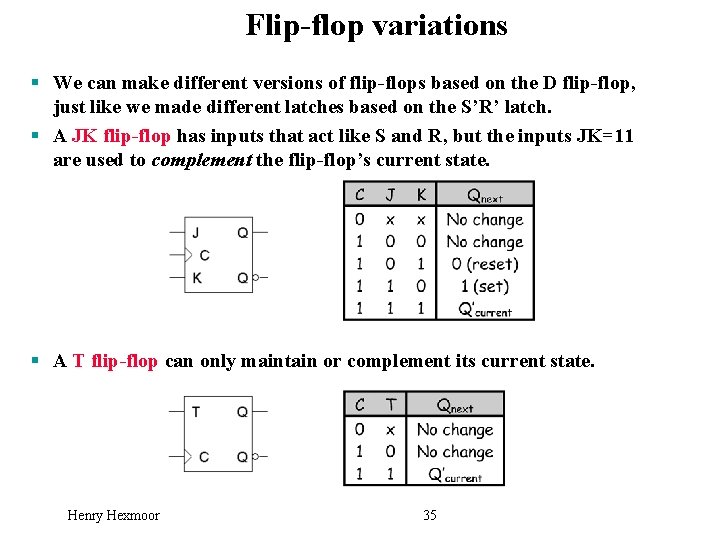

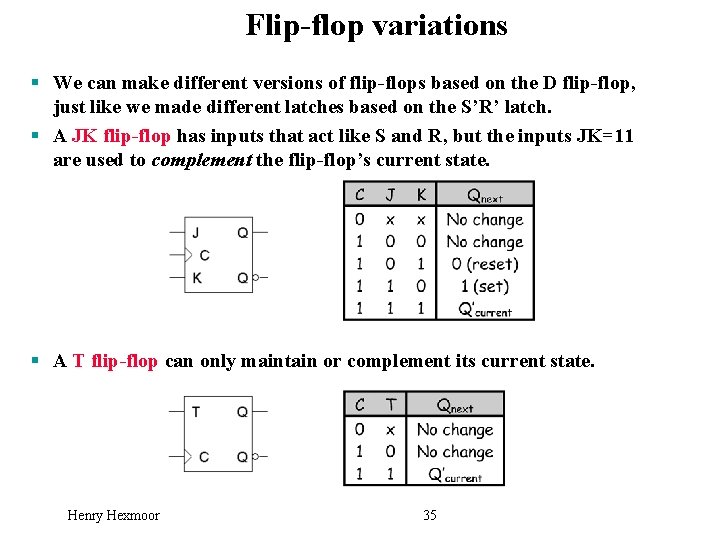

Flip-flop variations § We can make different versions of flip-flops based on the D flip-flop, just like we made different latches based on the S’R’ latch. § A JK flip-flop has inputs that act like S and R, but the inputs JK=11 are used to complement the flip-flop’s current state. § A T flip-flop can only maintain or complement its current state. Henry Hexmoor 35

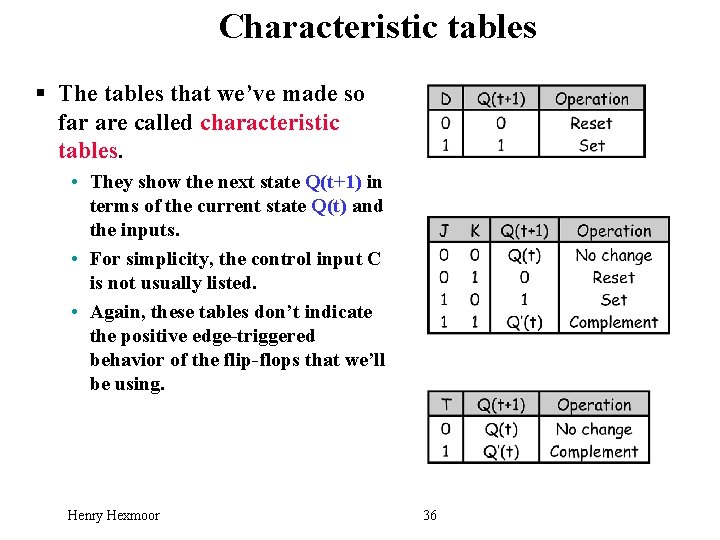

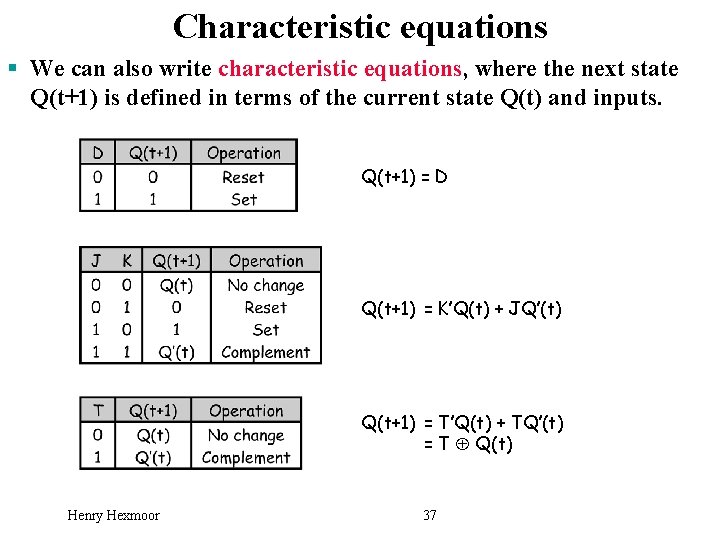

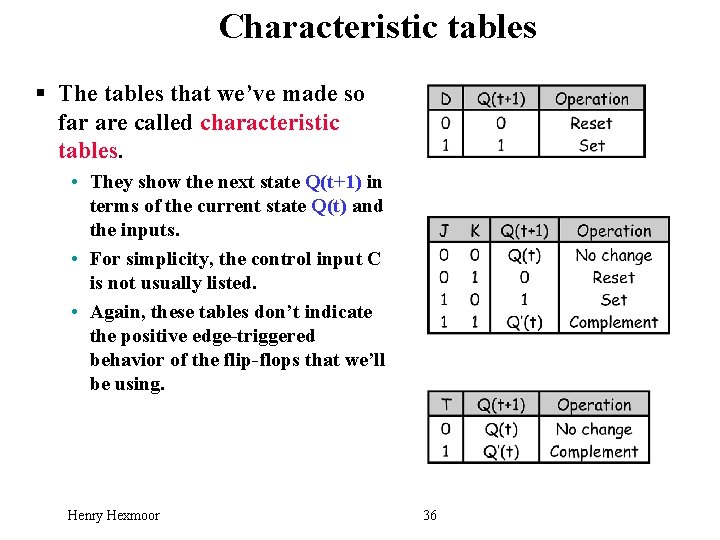

Characteristic tables § The tables that we’ve made so far are called characteristic tables. • They show the next state Q(t+1) in terms of the current state Q(t) and the inputs. • For simplicity, the control input C is not usually listed. • Again, these tables don’t indicate the positive edge-triggered behavior of the flip-flops that we’ll be using. Henry Hexmoor 36

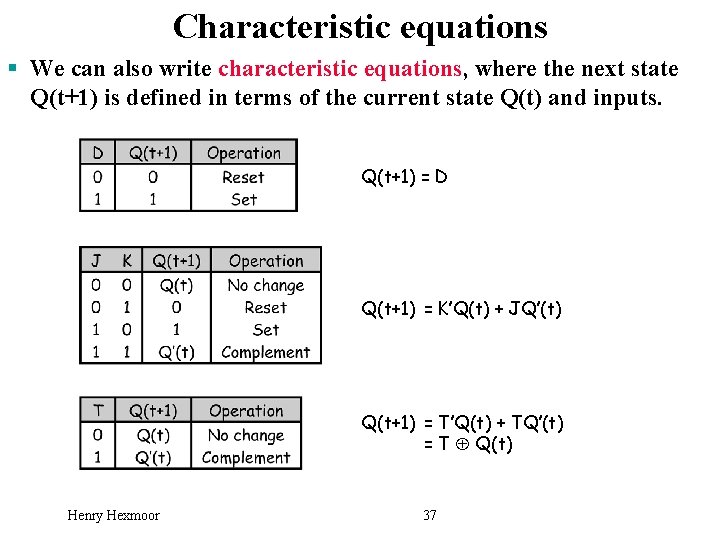

Characteristic equations § We can also write characteristic equations, where the next state Q(t+1) is defined in terms of the current state Q(t) and inputs. Q(t+1) = D Q(t+1) = K’Q(t) + JQ’(t) Q(t+1) = T’Q(t) + TQ’(t) = T Q(t) Henry Hexmoor 37

Flip Flop Summary § To use memory in a larger circuit, we need to: • Keep the latches disabled until new values are ready to be stored. • Enable the latches just long enough for the update to occur. § A clock signal is used to synchronize circuits. The cycle time reflects how long combinational operations take. § Flip-flops further restrict the memory writing interval, to just the positive edge of the clock signal. • This ensures that memory is updated only once per clock cycle. • There are several different kinds of flip-flops, but they all serve the same basic purpose of storing bits. Henry Hexmoor 38

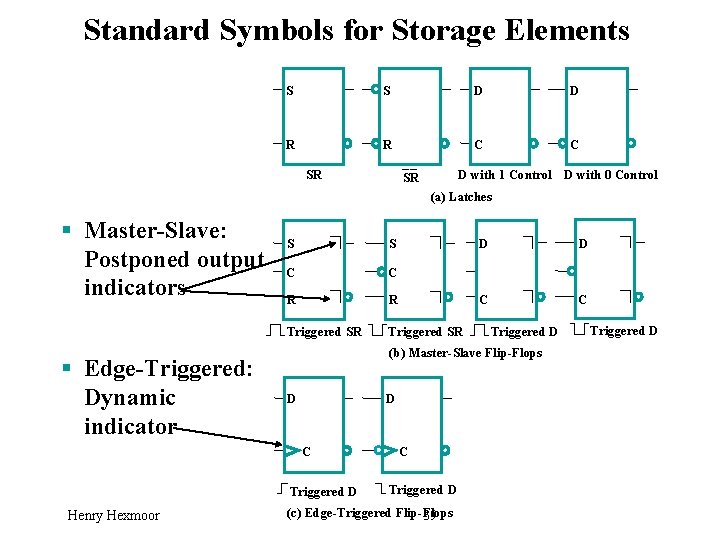

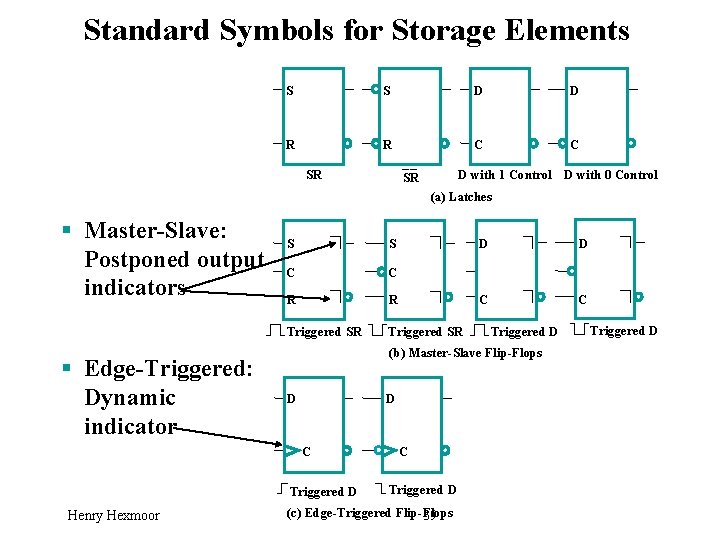

Standard Symbols for Storage Elements S S D D R R C C SR D with 1 Control D with 0 Control SR (a) Latches § Master-Slave: Postponed output indicators § Edge-Triggered: Dynamic indicator S S C C R R Triggered SR D C C Triggered D (b) Master-Slave Flip-Flops D D C Triggered D Henry Hexmoor D C Triggered D (c) Edge-Triggered Flip-Flops 39 Triggered D

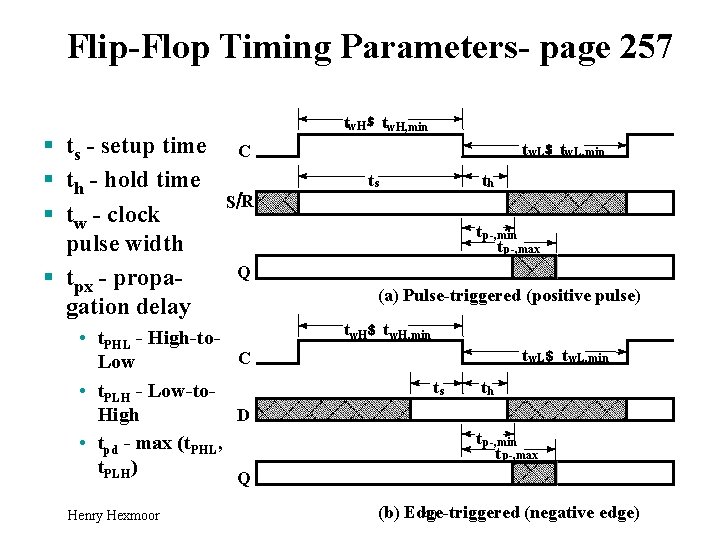

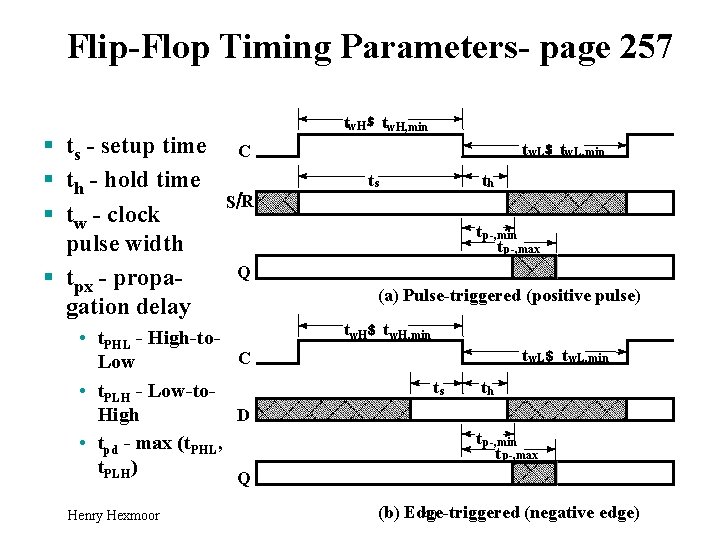

Flip-Flop Timing Parameters- page 257 § ts - setup time § th - hold time § tw - clock pulse width § tpx - propagation delay tw. H $ tw. H, min tw. L$ tw. L, min C ts th S/R tp-, min t p-, max Q (a) Pulse-triggered (positive pulse) • t. PHL - High-to. C Low • t. PLH - Low-to. High D • tpd - max (t. PHL, t. PLH) tw. H$ t w. H, min tw. L $ tw. L, min ts th t p-, min t p-, max Q Henry Hexmoor (b) Edge-triggered (negative edge) 40

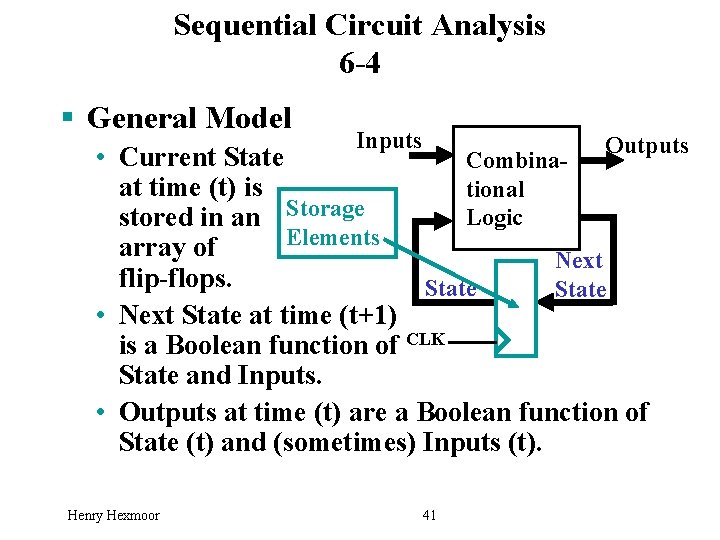

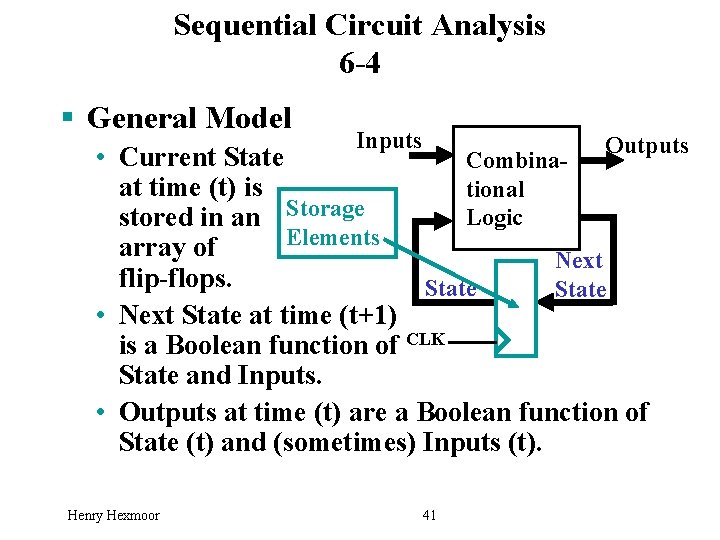

Sequential Circuit Analysis 6 -4 § General Model Inputs Outputs • Current State Combinaat time (t) is tional Storage Logic stored in an Elements array of Next flip-flops. State • Next State at time (t+1) CLK is a Boolean function of State and Inputs. • Outputs at time (t) are a Boolean function of State (t) and (sometimes) Inputs (t). Henry Hexmoor 41

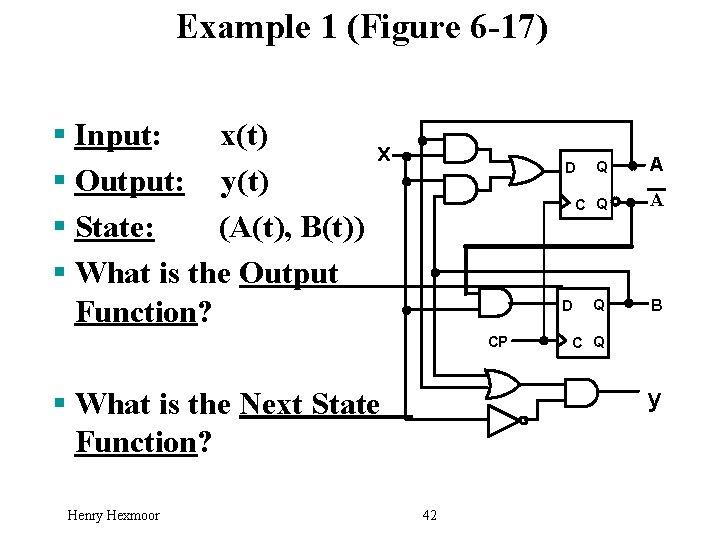

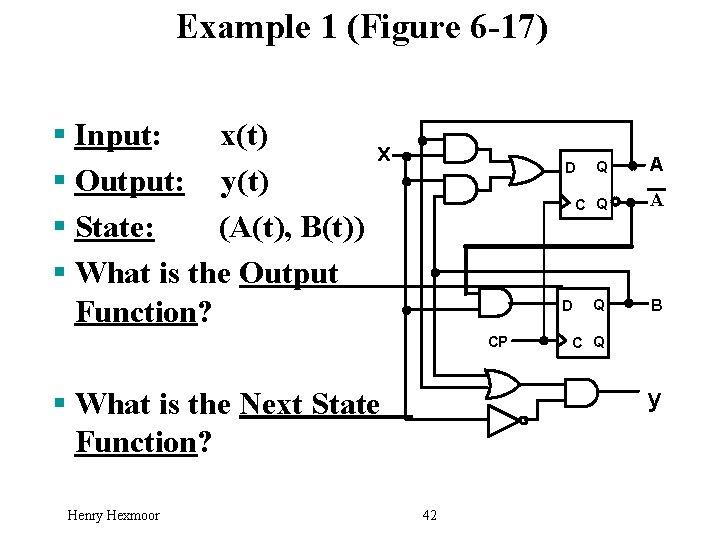

Example 1 (Figure 6 -17) § Input: x(t) x D Q § Output: y(t) C Q § State: (A(t), B(t)) § What is the Output D Q Function? CP 42 A B C Q § What is the Next State Function? Henry Hexmoor A y

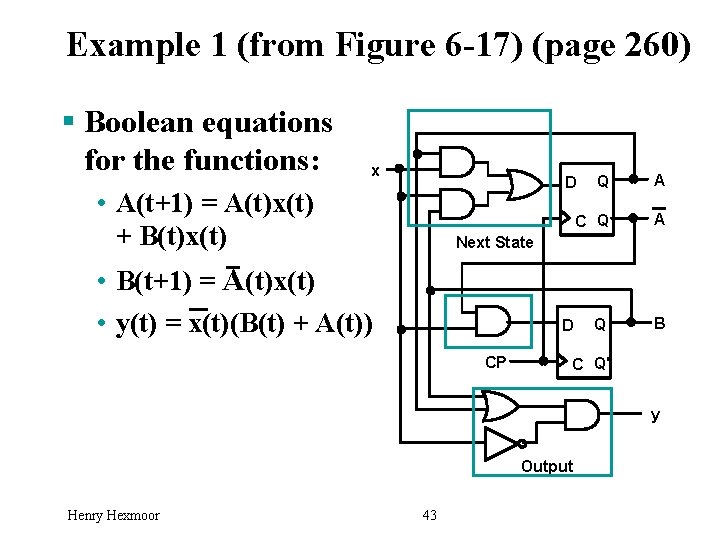

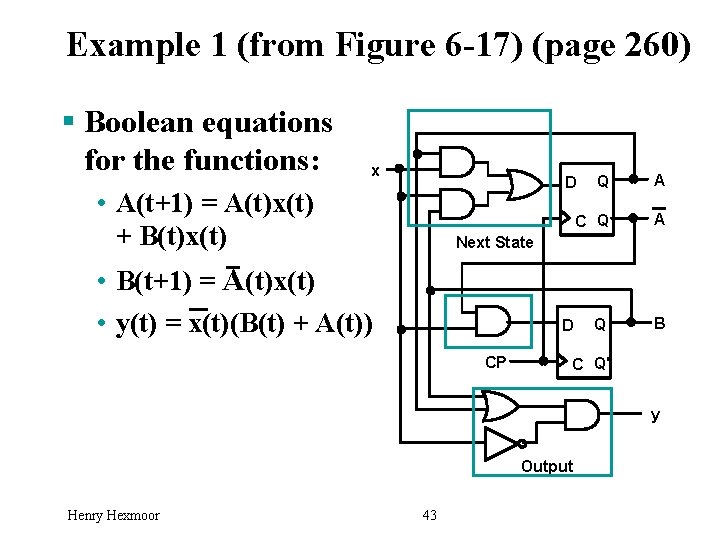

Example 1 (from Figure 6 -17) (page 260) § Boolean equations for the functions: x A D Q • A(t+1) = A(t)x(t) A C Q + B(t)x(t) Next State • B(t+1) = A(t)x(t) • y(t) = x(t)(B(t) + A(t)) CP B C Q' y Output Henry Hexmoor 43

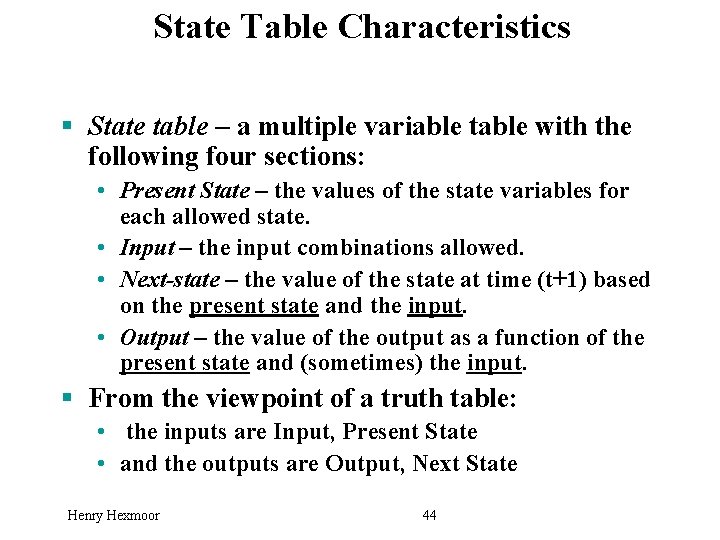

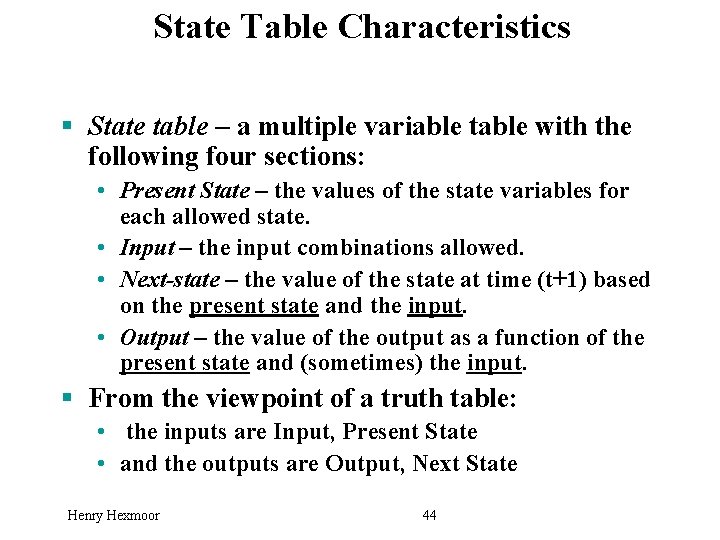

State Table Characteristics § State table – a multiple variable table with the following four sections: • Present State – the values of the state variables for each allowed state. • Input – the input combinations allowed. • Next-state – the value of the state at time (t+1) based on the present state and the input. • Output – the value of the output as a function of the present state and (sometimes) the input. § From the viewpoint of a truth table: • the inputs are Input, Present State • and the outputs are Output, Next State Henry Hexmoor 44

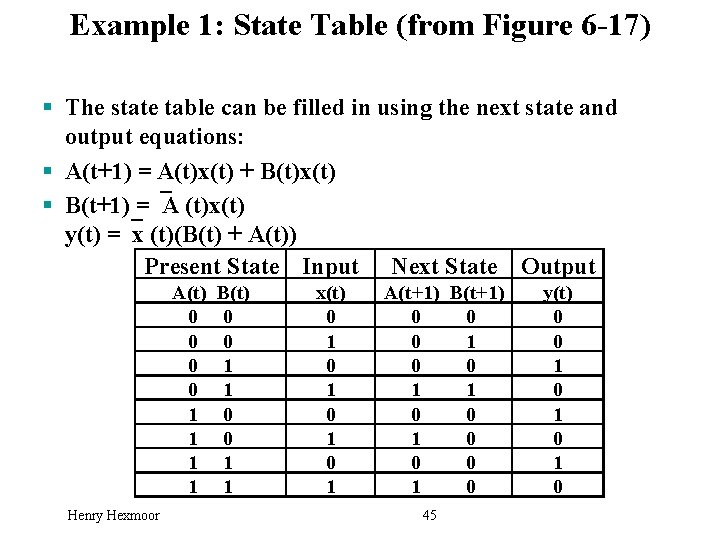

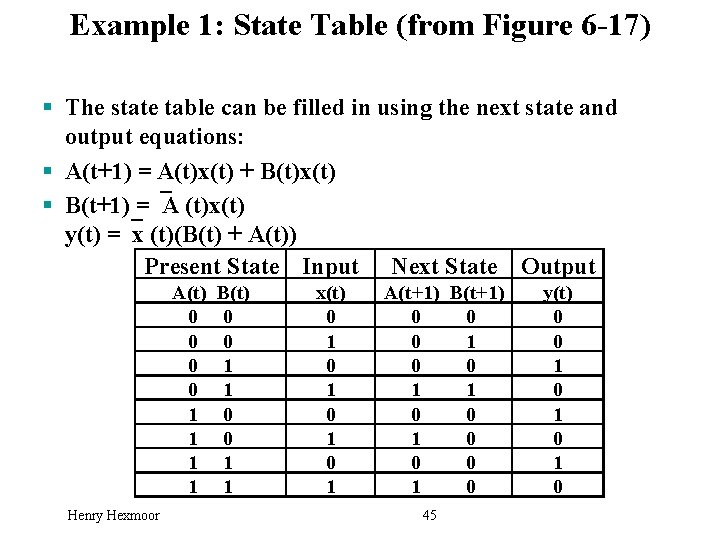

Example 1: State Table (from Figure 6 -17) § The state table can be filled in using the next state and output equations: § A(t+1) = A(t)x(t) + B(t)x(t) § B(t+1) = A (t)x(t) y(t) = x (t)(B(t) + A(t)) Present State Input Next State Output A(t) B(t) 0 0 0 1 0 1 1 1 1 Henry Hexmoor x(t) 0 1 0 1 A(t+1) B(t+1) 0 0 0 1 0 0 1 0 45 y(t) 0 0 1 0 1 0

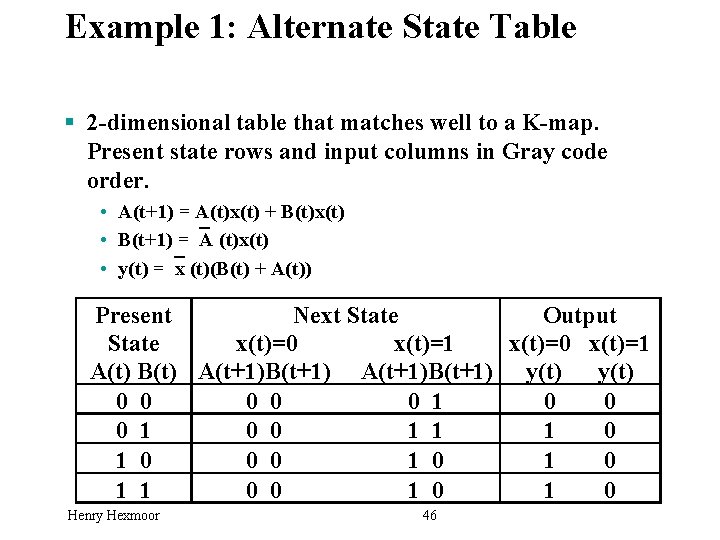

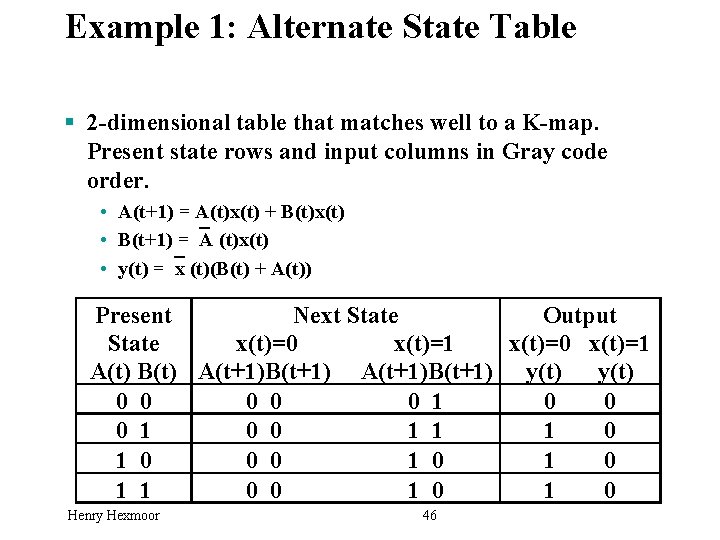

Example 1: Alternate State Table § 2 -dimensional table that matches well to a K-map. Present state rows and input columns in Gray code order. • A(t+1) = A(t)x(t) + B(t)x(t) • B(t+1) = A (t)x(t) • y(t) = x (t)(B(t) + A(t)) Present Next State Output State x(t)=0 x(t)=1 x(t)=0 x(t)=1 A(t) B(t) A(t+1)B(t+1) y(t) 0 0 0 1 0 0 0 1 0 0 1 1 1 0 1 0 0 0 1 0 1 1 0 0 1 0 1 0 Henry Hexmoor 46

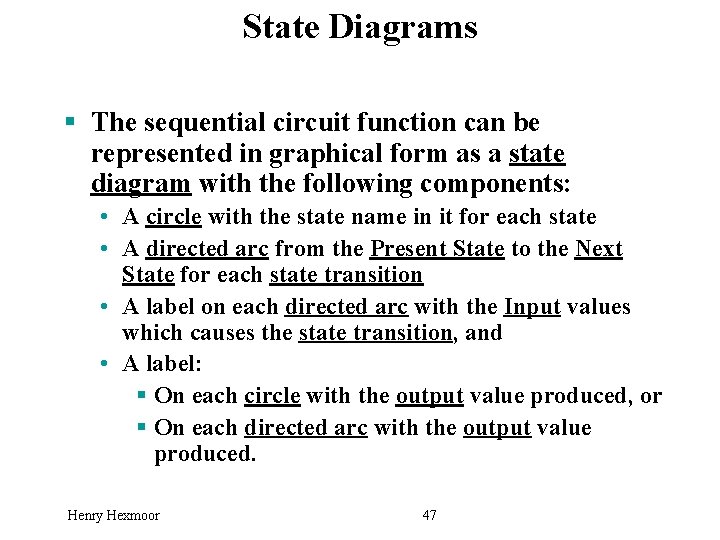

State Diagrams § The sequential circuit function can be represented in graphical form as a state diagram with the following components: • A circle with the state name in it for each state • A directed arc from the Present State to the Next State for each state transition • A label on each directed arc with the Input values which causes the state transition, and • A label: § On each circle with the output value produced, or § On each directed arc with the output value produced. Henry Hexmoor 47

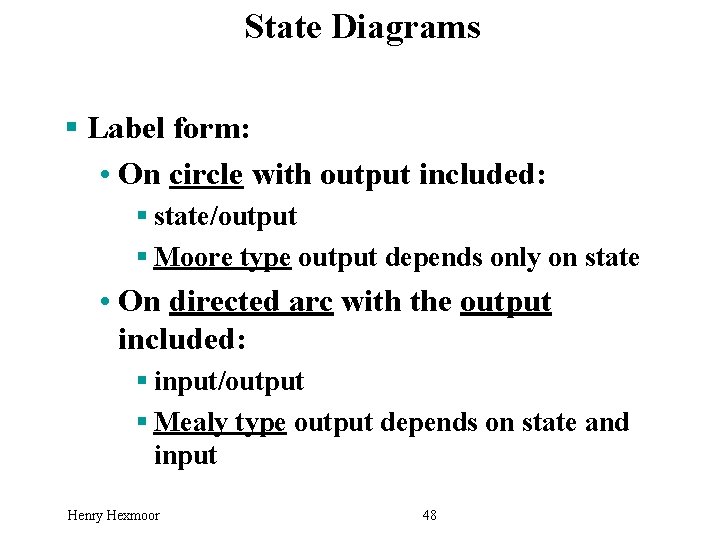

State Diagrams § Label form: • On circle with output included: § state/output § Moore type output depends only on state • On directed arc with the output included: § input/output § Mealy type output depends on state and input Henry Hexmoor 48

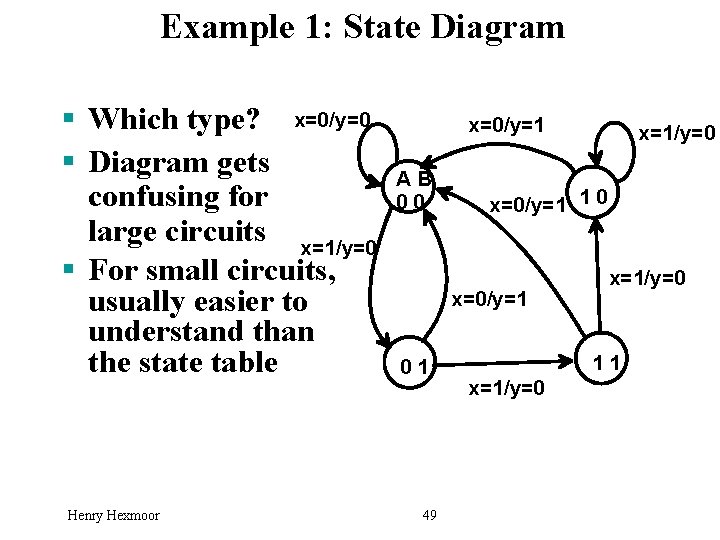

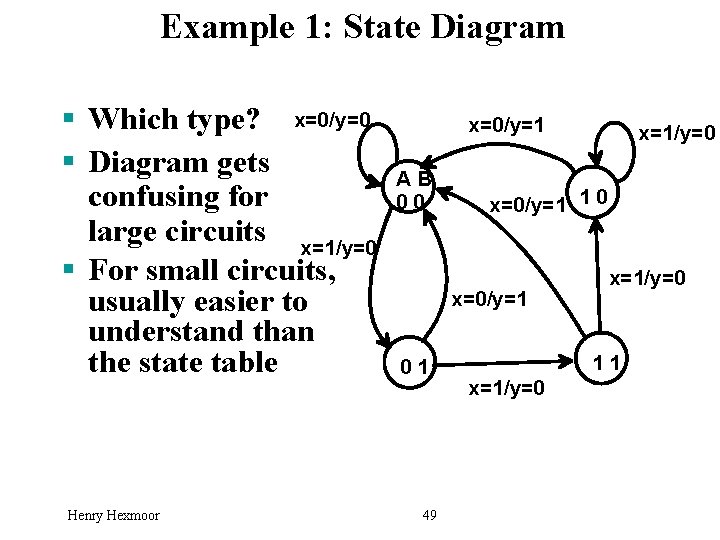

Example 1: State Diagram § Which type? x=0/y=0 § Diagram gets confusing for large circuits x=1/y=0 § For small circuits, usually easier to understand than the state table Henry Hexmoor x=0/y=1 AB 00 x=0/y=1 1 0 x=0/y=1 01 49 x=1/y=0 11 x=1/y=0

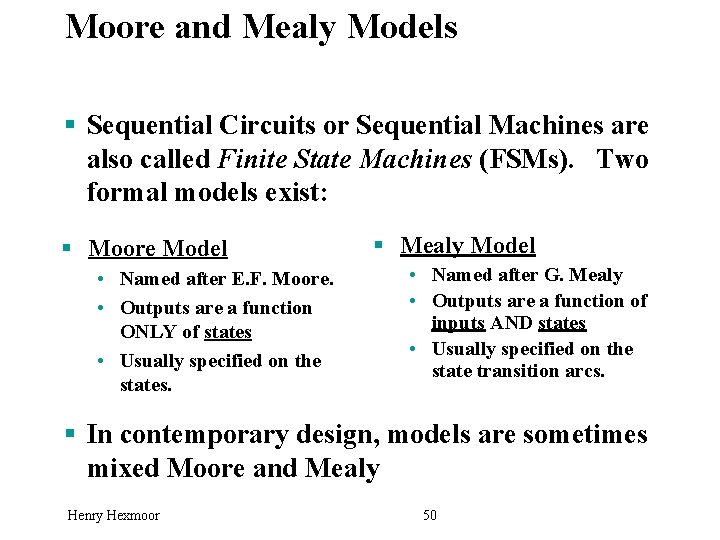

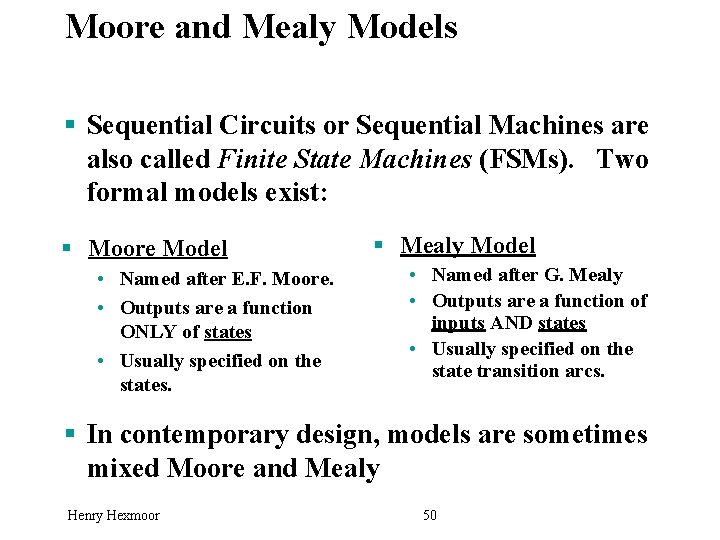

Moore and Mealy Models § Sequential Circuits or Sequential Machines are also called Finite State Machines (FSMs). Two formal models exist: § Moore Model • Named after E. F. Moore. • Outputs are a function ONLY of states • Usually specified on the states. § Mealy Model • Named after G. Mealy • Outputs are a function of inputs AND states • Usually specified on the state transition arcs. § In contemporary design, models are sometimes mixed Moore and Mealy Henry Hexmoor 50

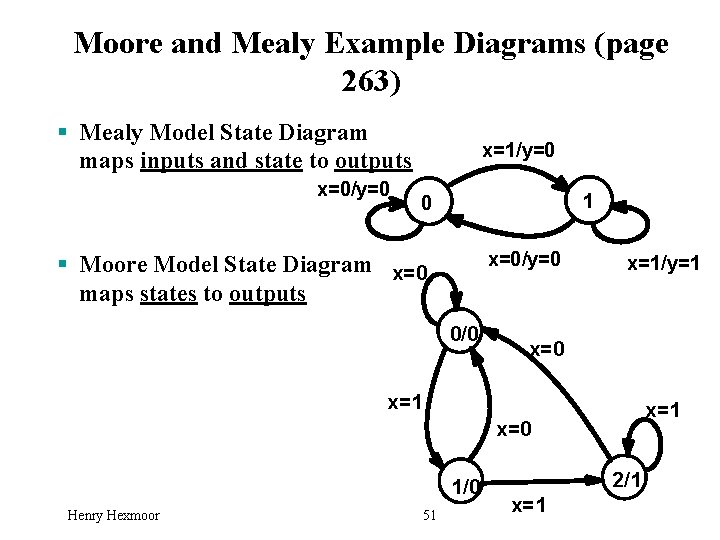

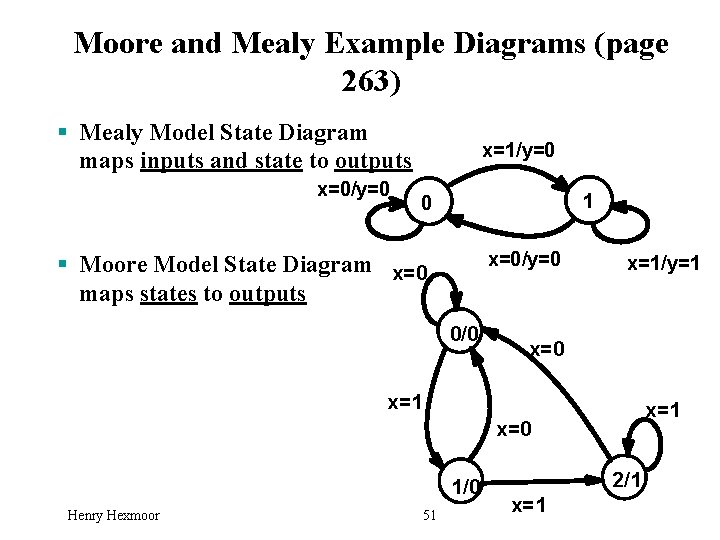

Moore and Mealy Example Diagrams (page 263) § Mealy Model State Diagram maps inputs and state to outputs x=0/y=0 x=1/y=0 1 0 x=0/y=0 x=1/y=1 § Moore Model State Diagram x=0 maps states to outputs 0/0 x=1 x=0 1/0 Henry Hexmoor 51 2/1 x=1

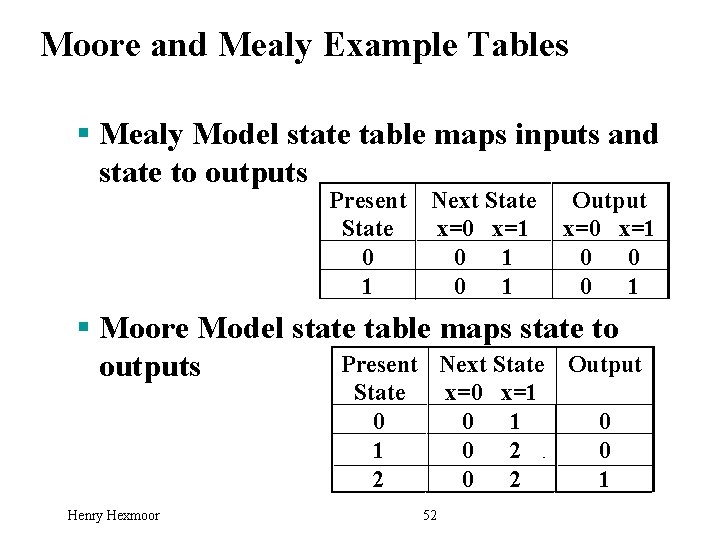

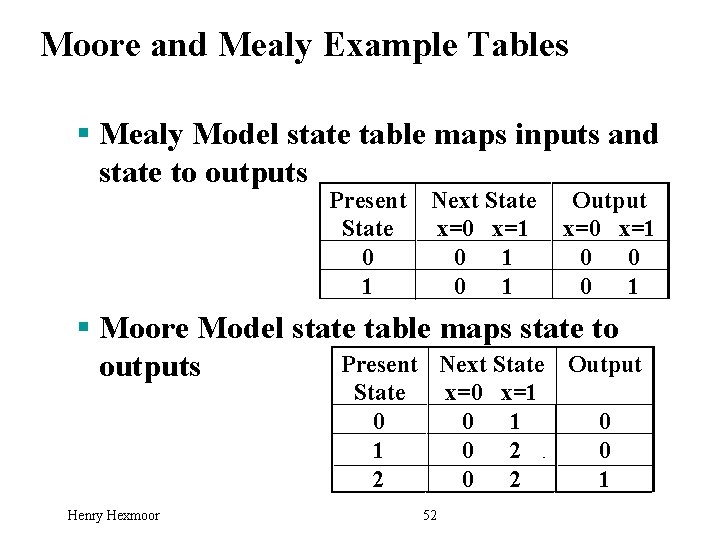

Moore and Mealy Example Tables § Mealy Model state table maps inputs and state to outputs Present Next State Output State x=0 x=1 0 0 1 0 1 § Moore Model state table maps state to Present Next State Output outputs State 0 1 2 x=0 x=1 0 2 0 2 Henry Hexmoor 52 0 0 1

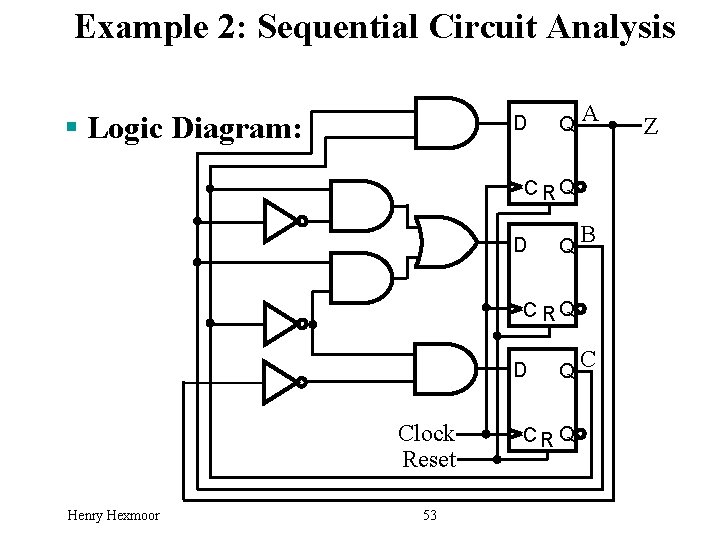

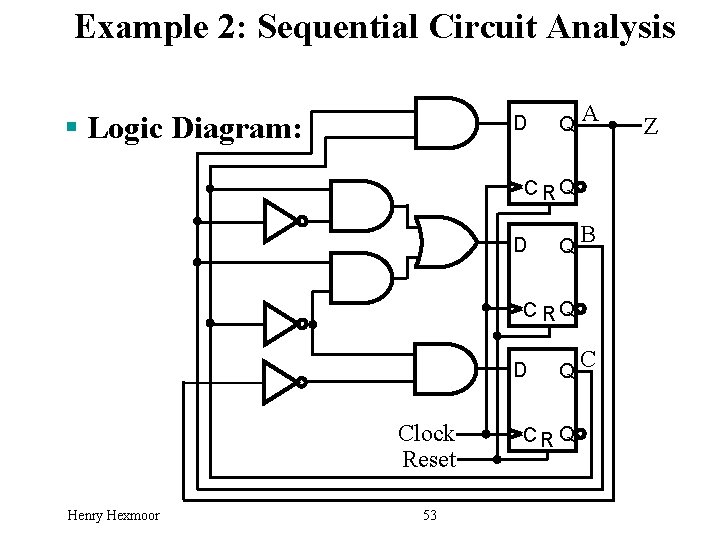

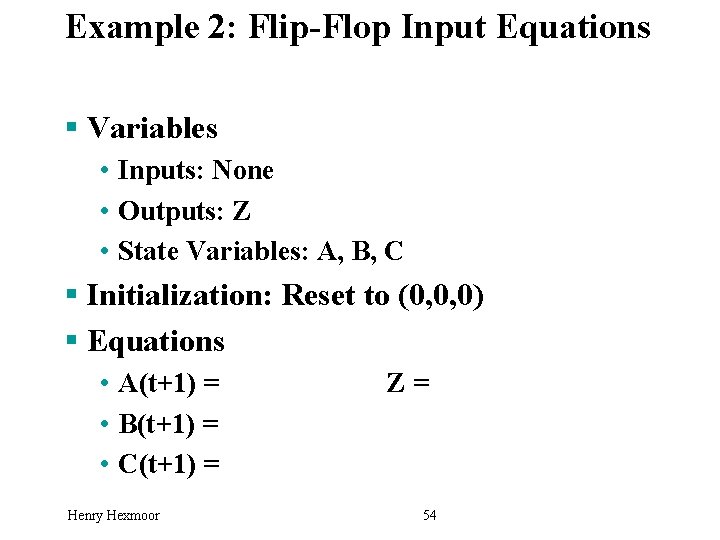

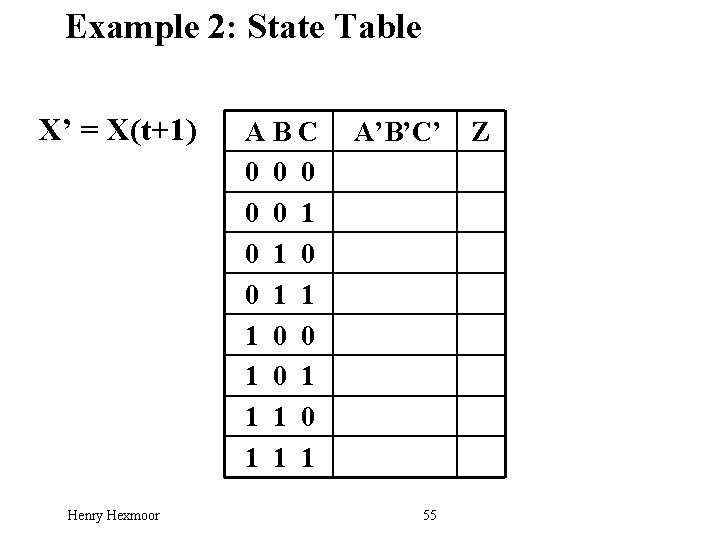

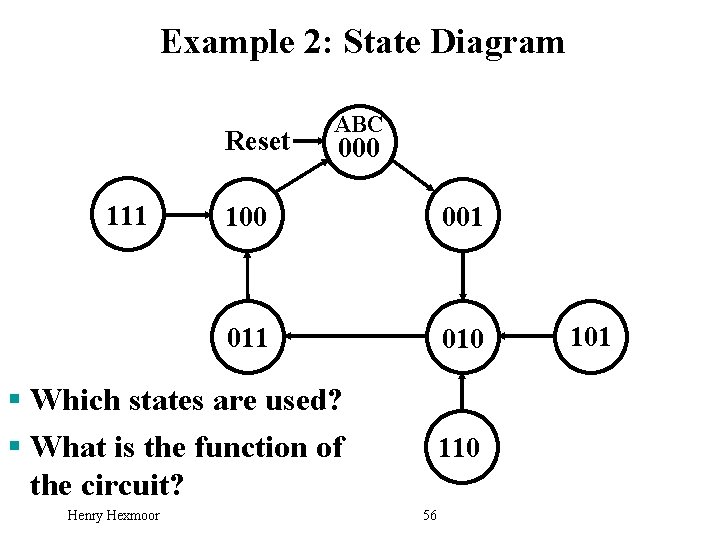

Example 2: Sequential Circuit Analysis § Logic Diagram: D Q A C RQ D Q B C RQ D Clock Reset Henry Hexmoor 53 Q CR Q C Z

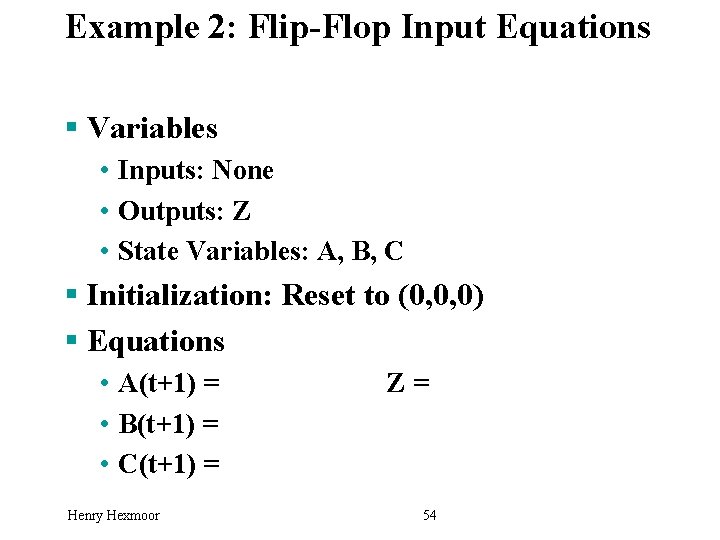

Example 2: Flip-Flop Input Equations § Variables • Inputs: None • Outputs: Z • State Variables: A, B, C § Initialization: Reset to (0, 0, 0) § Equations • A(t+1) = Z = • B(t+1) = • C(t+1) = Henry Hexmoor 54

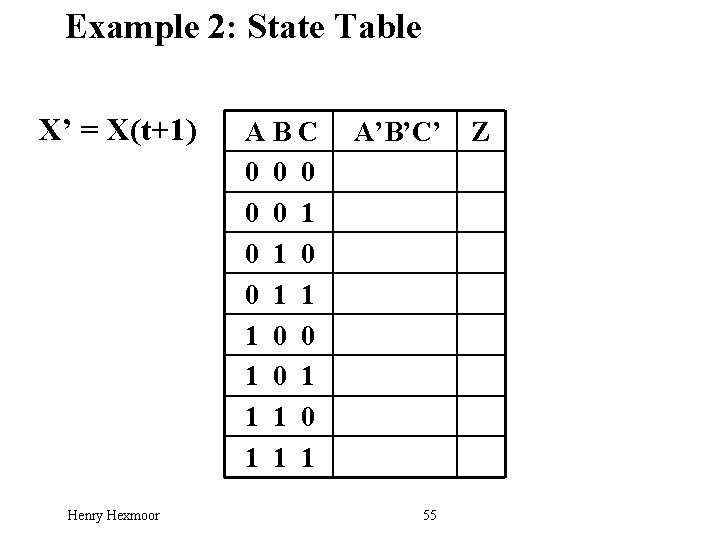

Example 2: State Table X’ = X(t+1) Henry Hexmoor A B C A’B’C’ Z 0 0 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 55

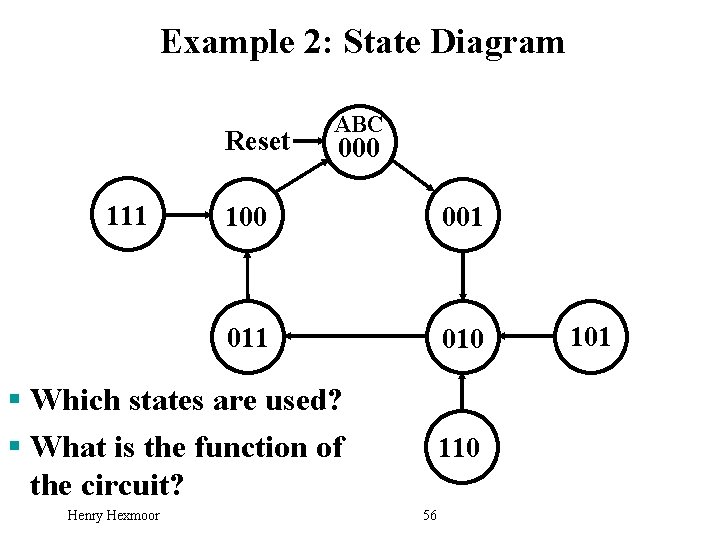

Example 2: State Diagram Reset 111 ABC 000 100 001 010 § Which states are used? § What is the function of the circuit? Henry Hexmoor 110 56 101

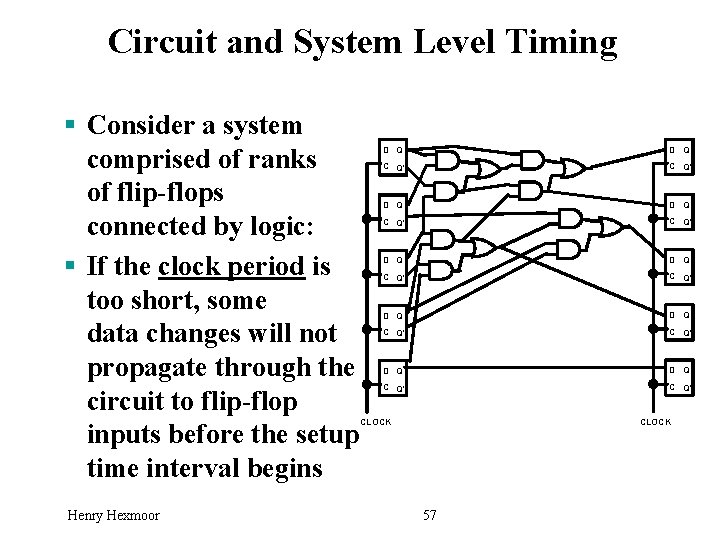

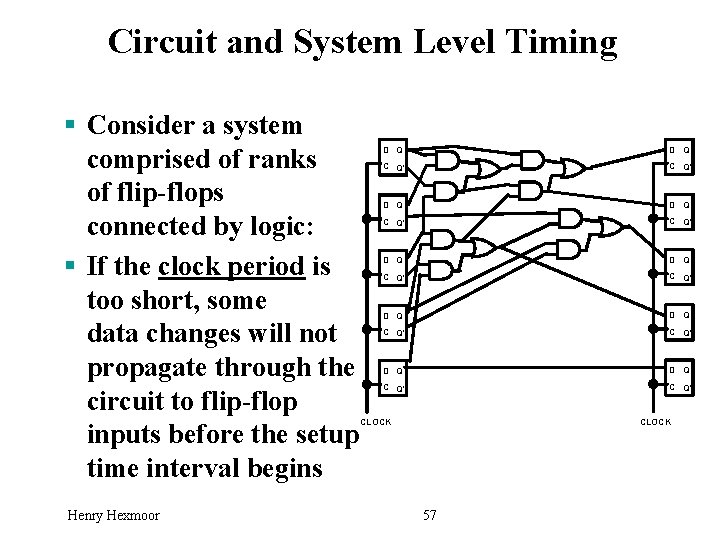

Circuit and System Level Timing § Consider a system comprised of ranks of flip-flops connected by logic: § If the clock period is too short, some data changes will not propagate through the circuit to flip-flop inputs before the setup time interval begins Henry Hexmoor D Q D Q C Q' C Q' D Q C Q' CLOCK 57

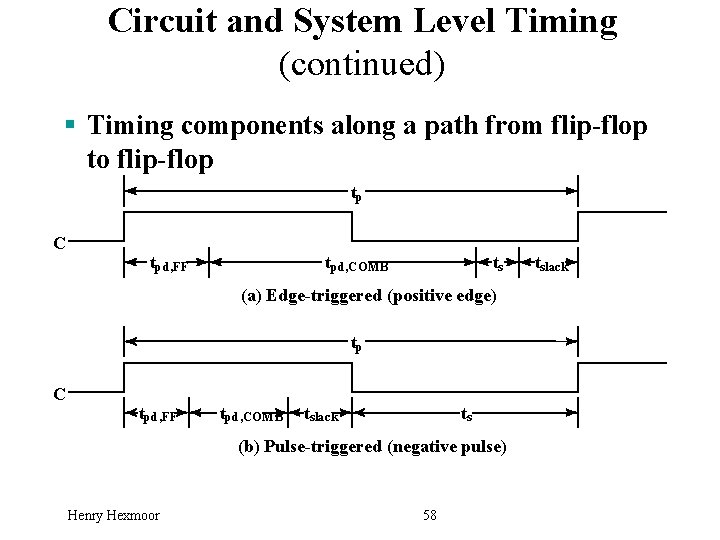

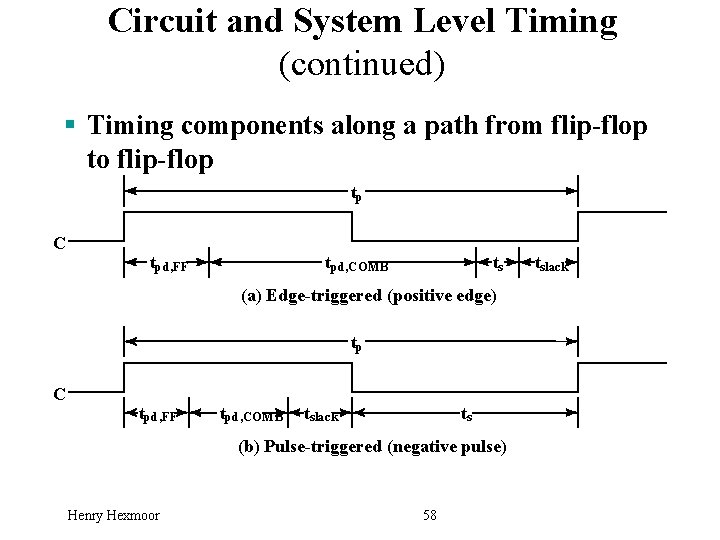

Circuit and System Level Timing (continued) § Timing components along a path from flip-flop to flip-flop tp C tpd, FF tpd, COMB ts (a) Edge-triggered (positive edge) tp C tpd, FF tpd, COMB tslack ts (b) Pulse-triggered (negative pulse) Henry Hexmoor 58 tslack

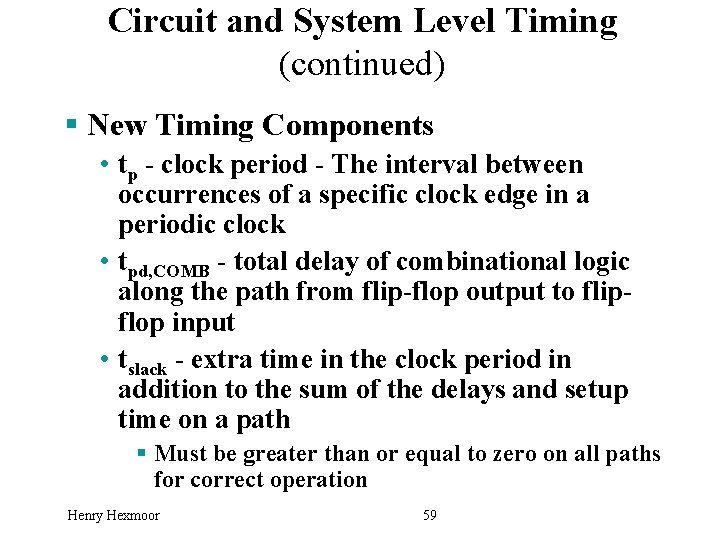

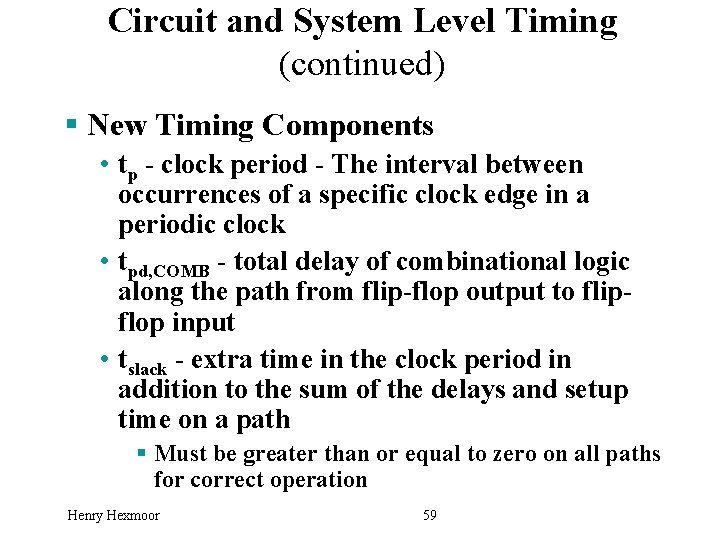

Circuit and System Level Timing (continued) § New Timing Components • tp - clock period - The interval between occurrences of a specific clock edge in a periodic clock • tpd, COMB - total delay of combinational logic along the path from flip-flop output to flipflop input • tslack - extra time in the clock period in addition to the sum of the delays and setup time on a path § Must be greater than or equal to zero on all paths for correct operation Henry Hexmoor 59

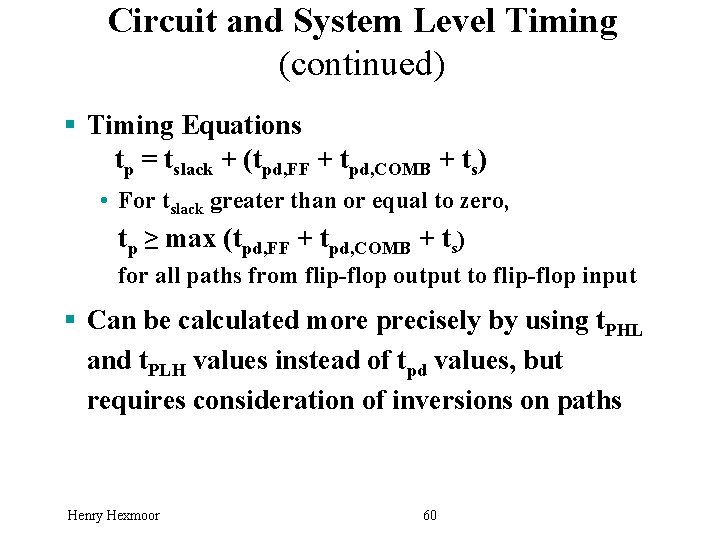

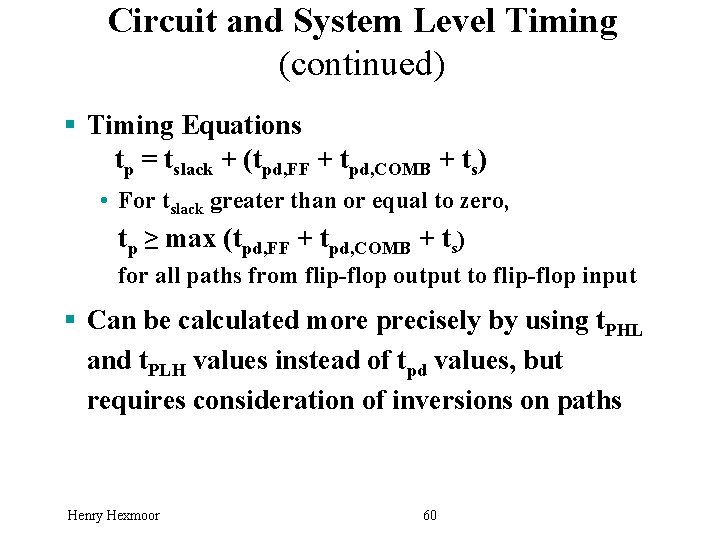

Circuit and System Level Timing (continued) § Timing Equations tp = tslack + (tpd, FF + tpd, COMB + ts) • For tslack greater than or equal to zero, tp ≥ max (tpd, FF + tpd, COMB + ts) for all paths from flip-flop output to flip-flop input § Can be calculated more precisely by using t. PHL and t. PLH values instead of tpd values, but requires consideration of inversions on paths Henry Hexmoor 60

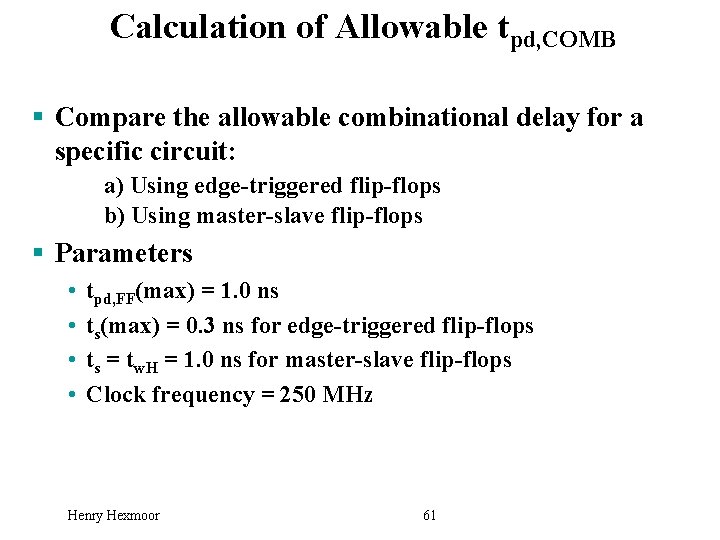

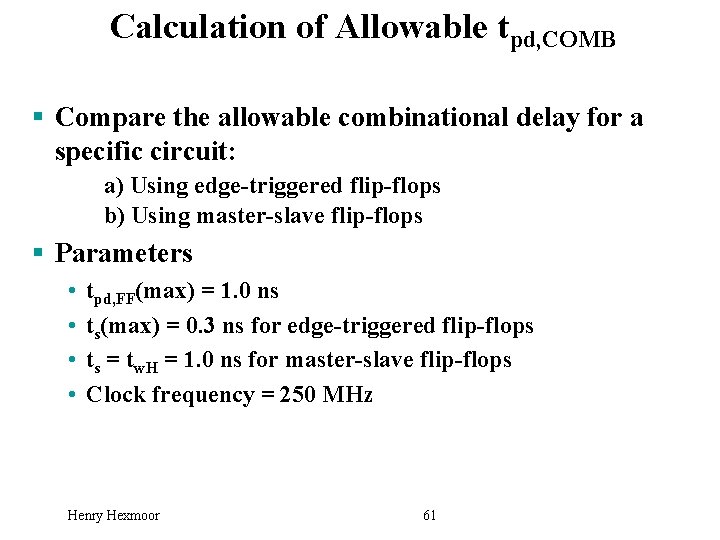

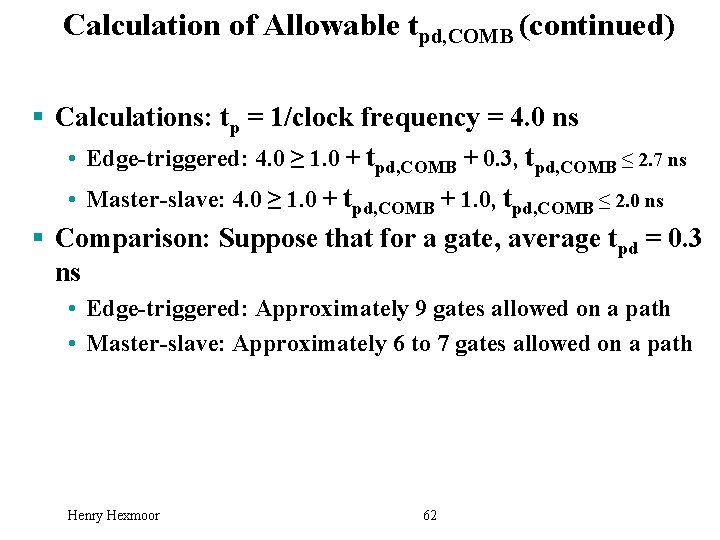

Calculation of Allowable tpd, COMB § Compare the allowable combinational delay for a specific circuit: a) Using edge-triggered flip-flops b) Using master-slave flip-flops § Parameters • • tpd, FF(max) = 1. 0 ns ts(max) = 0. 3 ns for edge-triggered flip-flops ts = tw. H = 1. 0 ns for master-slave flip-flops Clock frequency = 250 MHz Henry Hexmoor 61

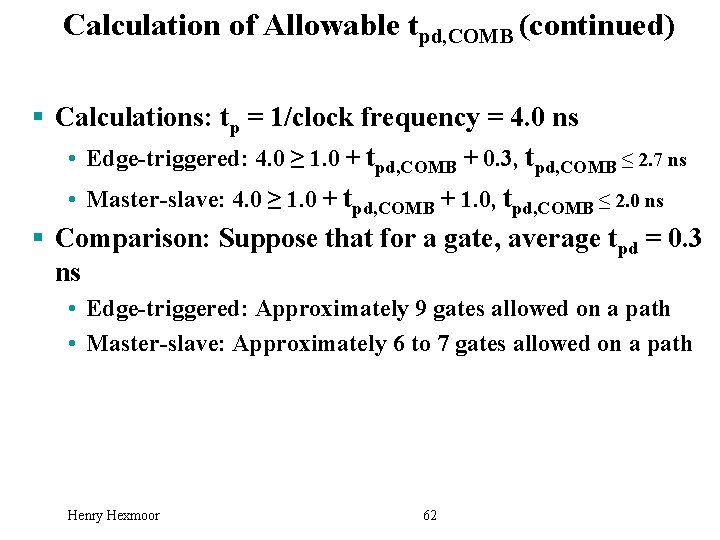

Calculation of Allowable tpd, COMB (continued) § Calculations: tp = 1/clock frequency = 4. 0 ns • Edge-triggered: 4. 0 ≥ 1. 0 + tpd, COMB + 0. 3, tpd, COMB ≤ 2. 7 ns • Master-slave: 4. 0 ≥ 1. 0 + tpd, COMB + 1. 0, tpd, COMB ≤ 2. 0 ns § Comparison: Suppose that for a gate, average tpd = 0. 3 ns • Edge-triggered: Approximately 9 gates allowed on a path • Master-slave: Approximately 6 to 7 gates allowed on a path Henry Hexmoor 62

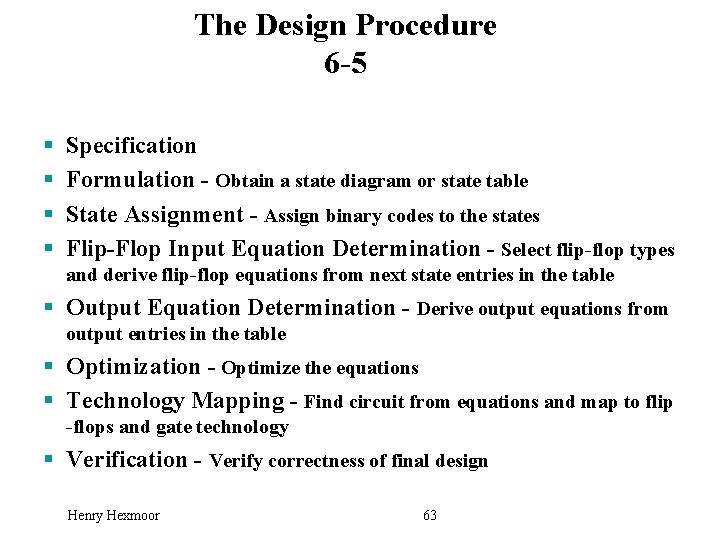

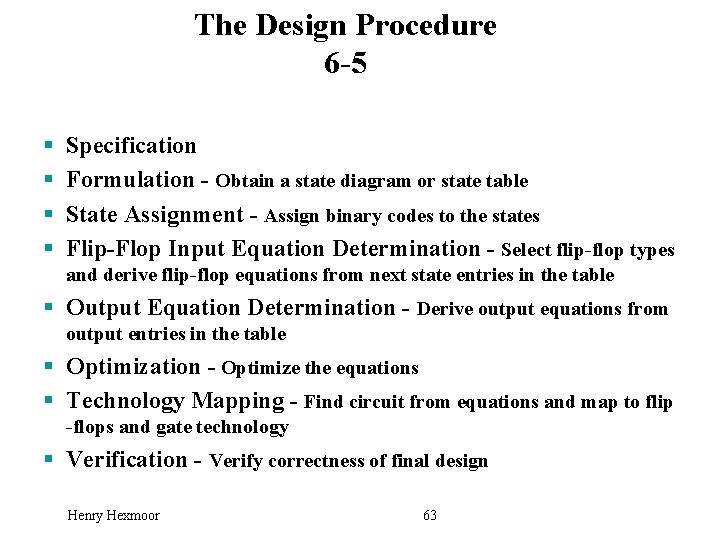

The Design Procedure 6 -5 § § Specification Formulation - Obtain a state diagram or state table State Assignment - Assign binary codes to the states Flip-Flop Input Equation Determination - Select flip-flop types and derive flip-flop equations from next state entries in the table § Output Equation Determination - Derive output equations from output entries in the table § Optimization - Optimize the equations § Technology Mapping - Find circuit from equations and map to flip -flops and gate technology § Verification - Verify correctness of final design Henry Hexmoor 63

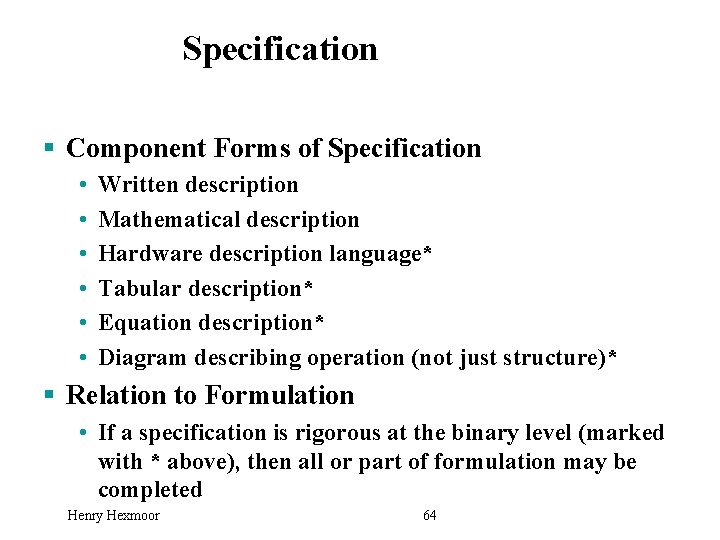

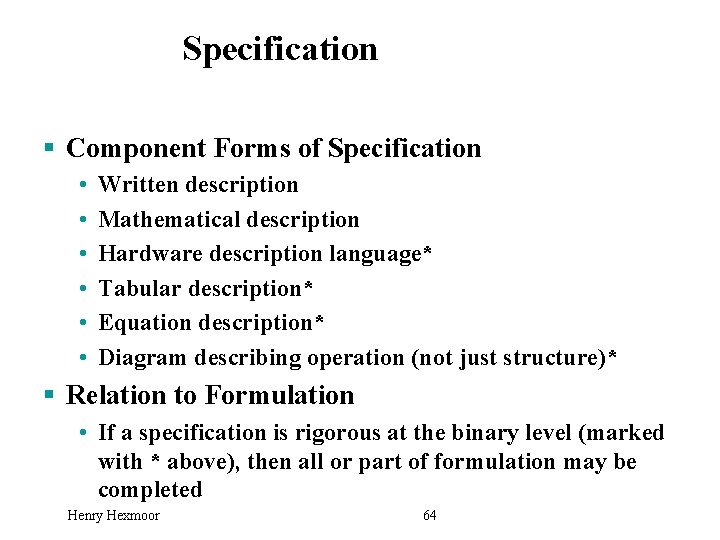

Specification § Component Forms of Specification • • • Written description Mathematical description Hardware description language* Tabular description* Equation description* Diagram describing operation (not just structure)* § Relation to Formulation • If a specification is rigorous at the binary level (marked with * above), then all or part of formulation may be completed Henry Hexmoor 64

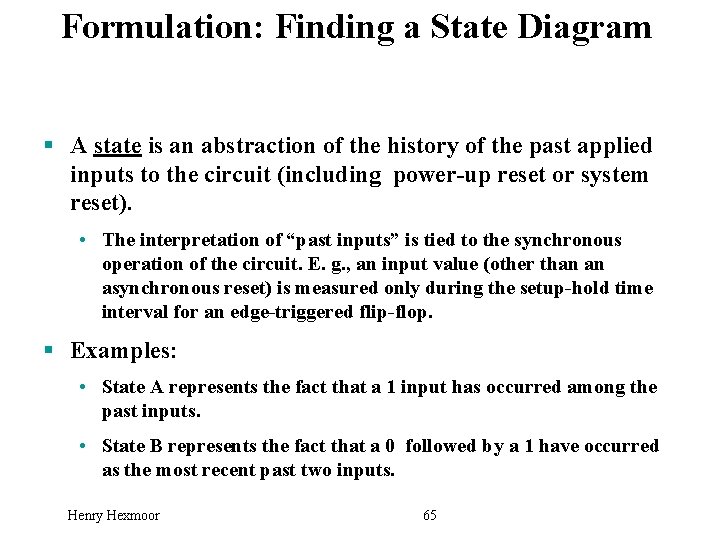

Formulation: Finding a State Diagram § A state is an abstraction of the history of the past applied inputs to the circuit (including power-up reset or system reset). • The interpretation of “past inputs” is tied to the synchronous operation of the circuit. E. g. , an input value (other than an asynchronous reset) is measured only during the setup-hold time interval for an edge-triggered flip-flop. § Examples: • State A represents the fact that a 1 input has occurred among the past inputs. • State B represents the fact that a 0 followed by a 1 have occurred as the most recent past two inputs. Henry Hexmoor 65

Formulation: Finding a State Diagram § In specifying a circuit, we use states to remember meaningful properties of past input sequences that are essential to predicting future output values. § A sequence recognizer is a sequential circuit that produces a distinct output value whenever a prescribed pattern of input symbols occur in sequence, i. e, recognizes an input sequence occurence. § We will develop a procedure specific to sequence recognizers to convert a problem statement into a state diagram. § Next, the state diagram, will be converted to a state table from which the circuit will be designed. Henry Hexmoor 66

Sequence Recognizer Procedure § To develop a sequence recognizer state diagram: • Begin in an initial state in which NONE of the initial portion of the sequence has occurred (typically “reset” state). • Add a state that recognizes that the first symbol has occurred. • Add states that recognize each successive symbol occurring. • The final state represents the input sequence (possibly less the final input value) occurence. • Add state transition arcs which specify what happens when a symbol not in the proper sequence has occurred. • Add other arcs on non-sequence inputs which transition to states that represent the input subsequence that has occurred. § The last step is required because the circuit must recognize the input sequence regardless of where it occurs within the overall sequence applied since “reset. ”. Henry Hexmoor 67

State Assignment § Each of the m states must be assigned a unique code § Minimum number of bits required is n such that n ≥ log 2 m where x is the smallest integer ≥ x § There are useful state assignments that use more than the minimum number of bits § There are 2 n - m unused states Henry Hexmoor 68

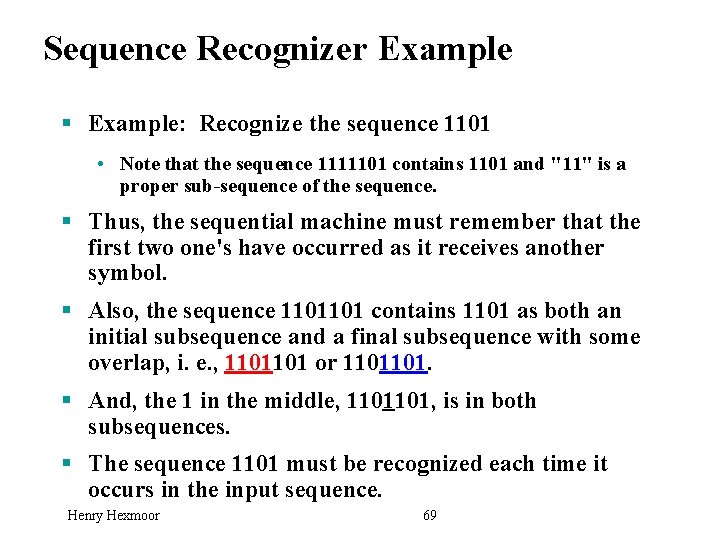

Sequence Recognizer Example § Example: Recognize the sequence 1101 • Note that the sequence 1111101 contains 1101 and "11" is a proper sub-sequence of the sequence. § Thus, the sequential machine must remember that the first two one's have occurred as it receives another symbol. § Also, the sequence 1101101 contains 1101 as both an initial subsequence and a final subsequence with some overlap, i. e. , 1101101 or 1101101. § And, the 1 in the middle, 1101101, is in both subsequences. § The sequence 1101 must be recognized each time it occurs in the input sequence. Henry Hexmoor 69

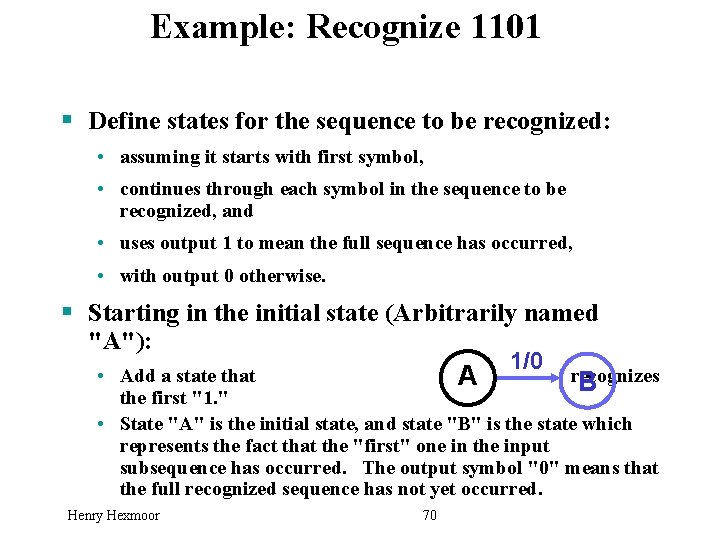

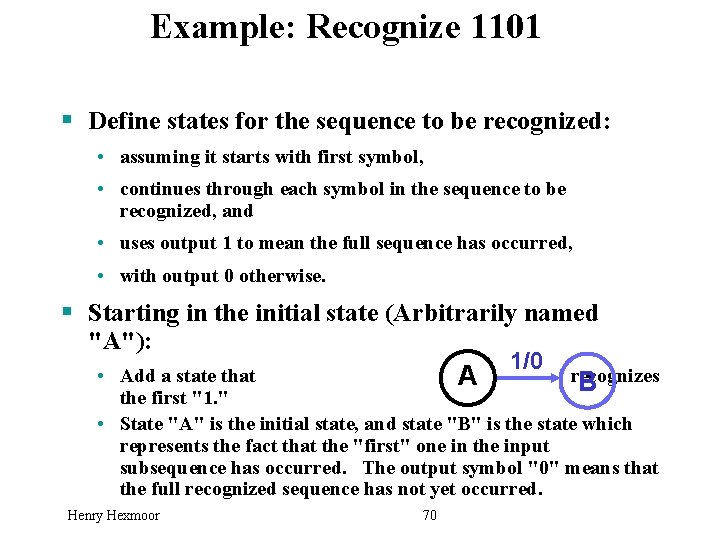

Example: Recognize 1101 § Define states for the sequence to be recognized: • assuming it starts with first symbol, • continues through each symbol in the sequence to be recognized, and • uses output 1 to mean the full sequence has occurred, • with output 0 otherwise. § Starting in the initial state (Arbitrarily named "A"): 1/0 • Add a state that recognizes A B the first "1. " • State "A" is the initial state, and state "B" is the state which represents the fact that the "first" one in the input subsequence has occurred. The output symbol "0" means that the full recognized sequence has not yet occurred. Henry Hexmoor 70

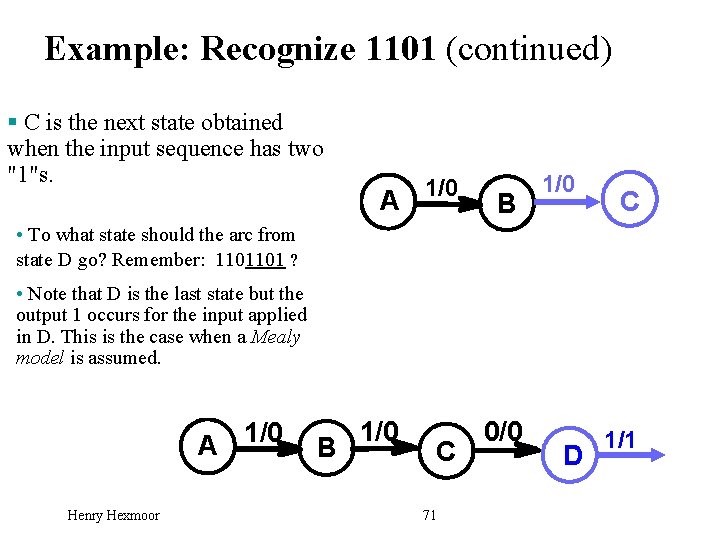

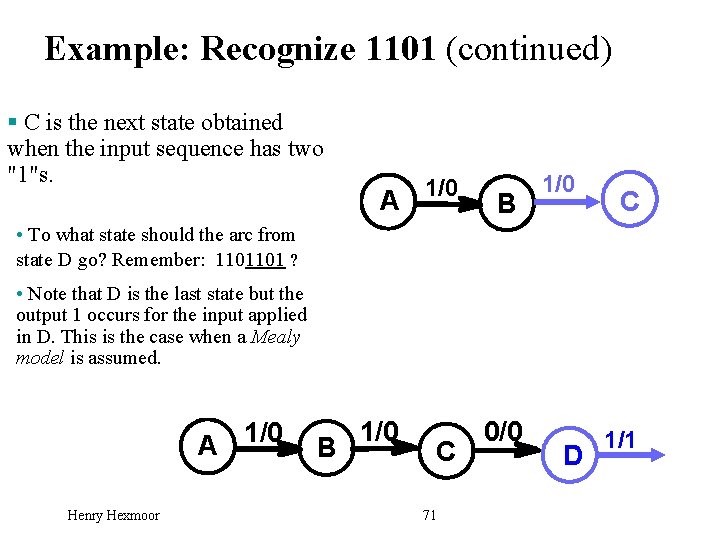

Example: Recognize 1101 (continued) § C is the next state obtained when the input sequence has two "1"s. A 1/0 B 1/0 C • To what state should the arc from state D go? Remember: 1101101 ? • Note that D is the last state but the output 1 occurs for the input applied in D. This is the case when a Mealy model is assumed. A 1/0 Henry Hexmoor B 1/0 C 71 0/0 D 1/1

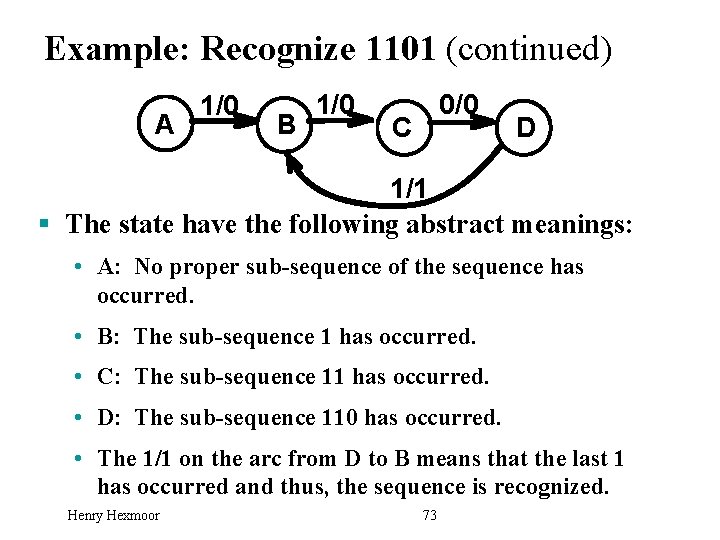

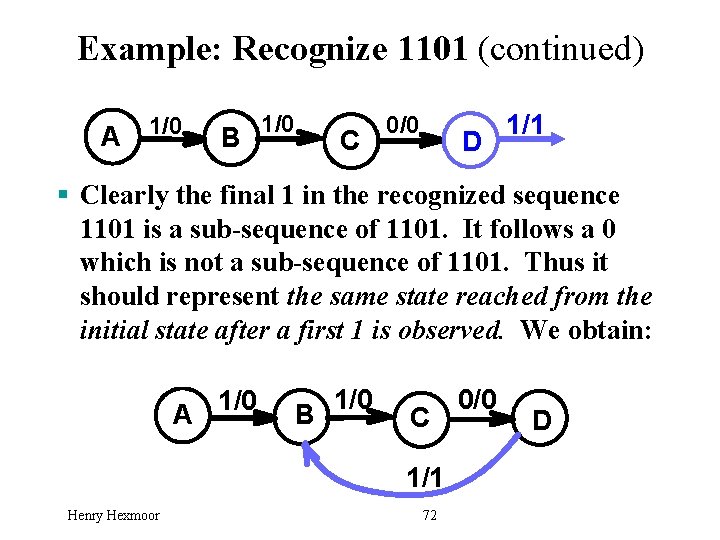

Example: Recognize 1101 (continued) A 1/0 B 1/0 C 0/0 D 1/1 § Clearly the final 1 in the recognized sequence 1101 is a sub-sequence of 1101. It follows a 0 which is not a sub-sequence of 1101. Thus it should represent the same state reached from the initial state after a first 1 is observed. We obtain: A 1/0 B 1/0 C 1/1 Henry Hexmoor 72 0/0 D

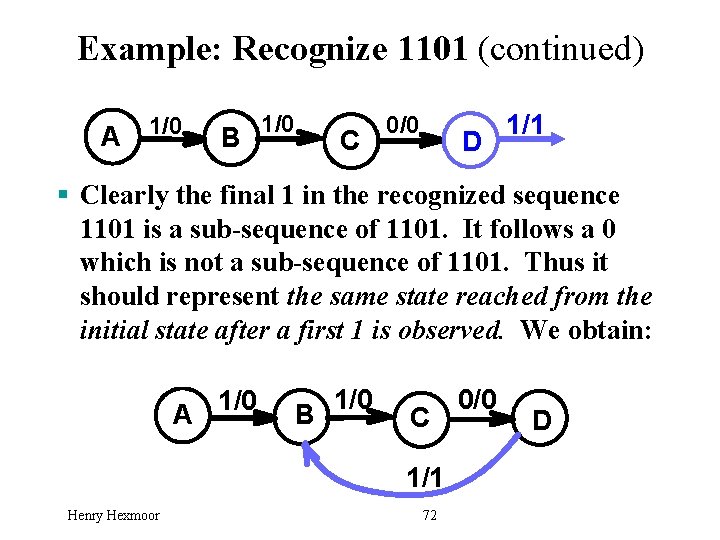

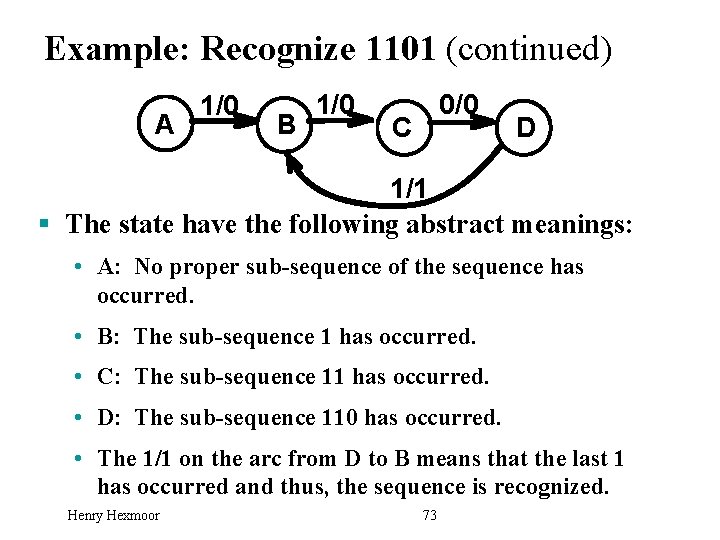

Example: Recognize 1101 (continued) A 1/0 B 1/0 0/0 C D 1/1 § The state have the following abstract meanings: • A: No proper sub-sequence of the sequence has occurred. • B: The sub-sequence 1 has occurred. • C: The sub-sequence 11 has occurred. • D: The sub-sequence 110 has occurred. • The 1/1 on the arc from D to B means that the last 1 has occurred and thus, the sequence is recognized. Henry Hexmoor 73

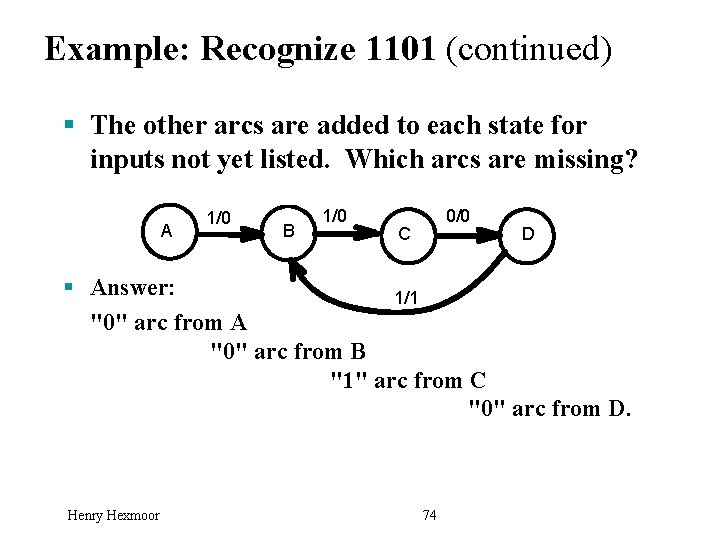

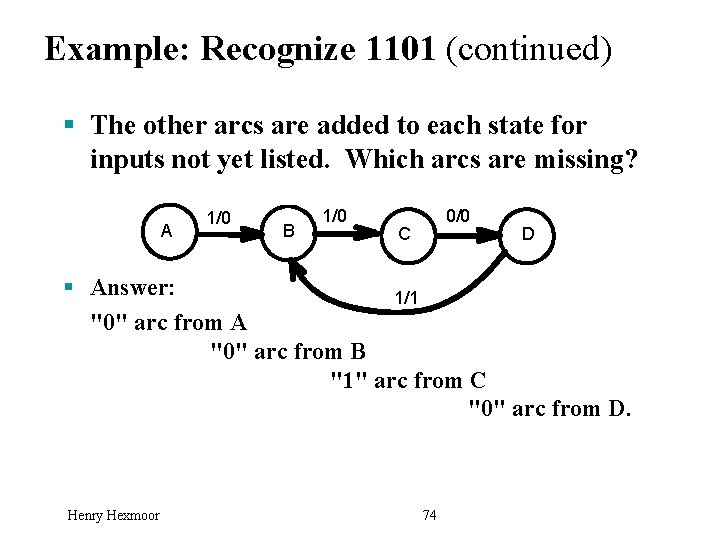

Example: Recognize 1101 (continued) § The other arcs are added to each state for inputs not yet listed. Which arcs are missing? A 1/0 B 1/0 0/0 C D § Answer: 1/1 "0" arc from A "0" arc from B "1" arc from C "0" arc from D. Henry Hexmoor 74

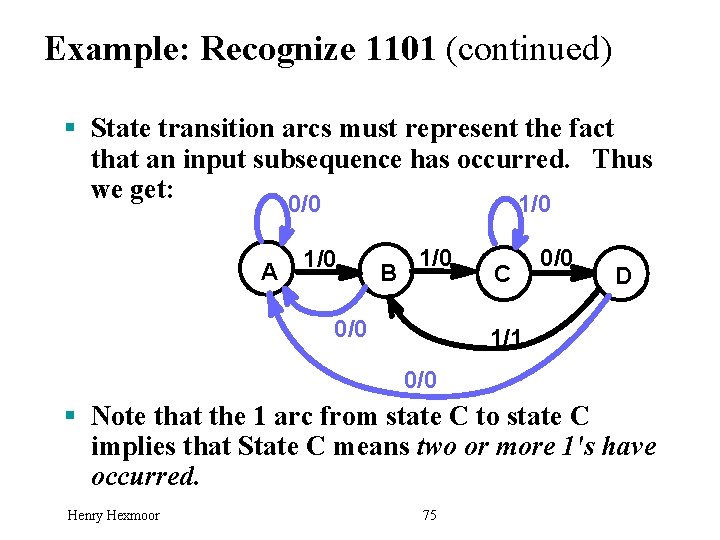

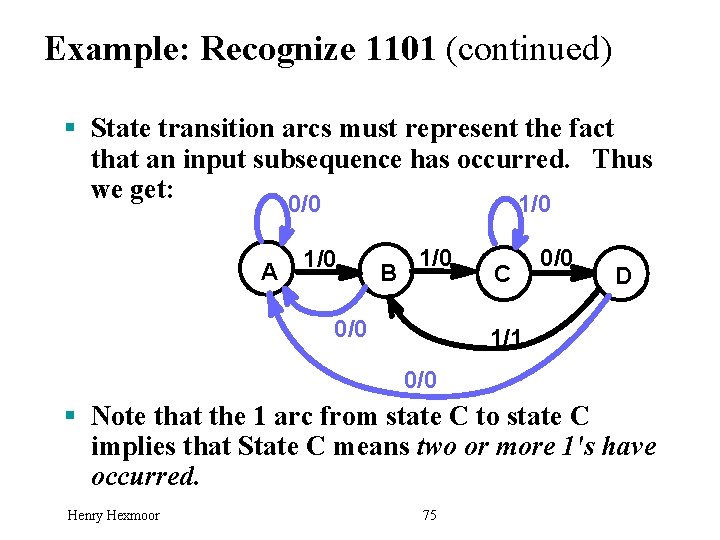

Example: Recognize 1101 (continued) § State transition arcs must represent the fact that an input subsequence has occurred. Thus we get: 0/0 1/0 A 1/0 B 1/0 0/0 C 0/0 D 1/1 0/0 § Note that the 1 arc from state C to state C implies that State C means two or more 1's have occurred. Henry Hexmoor 75

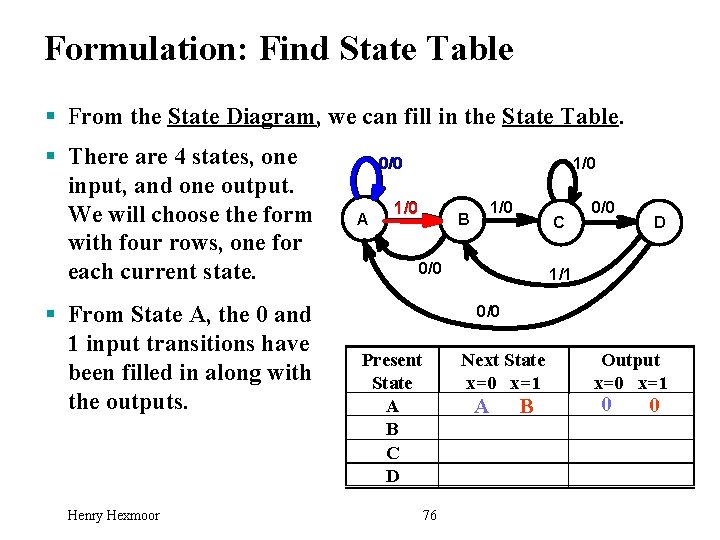

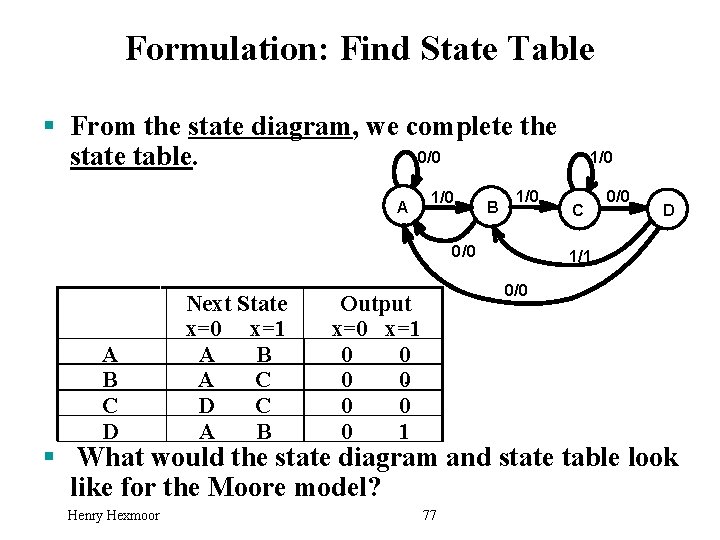

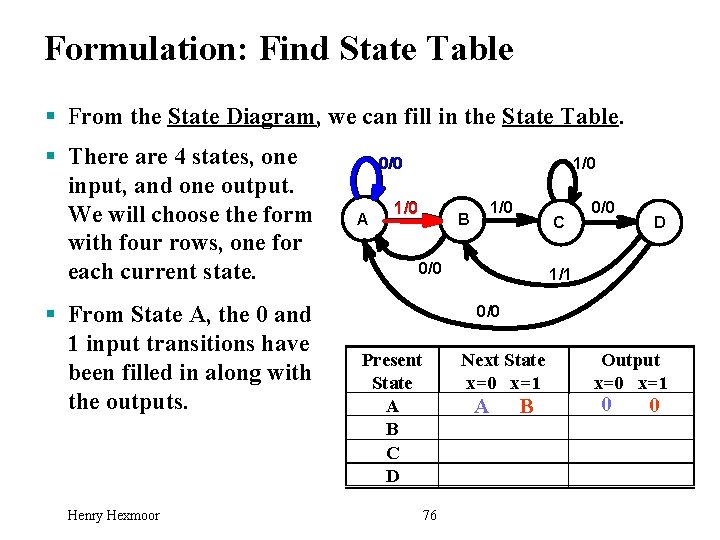

Formulation: Find State Table § From the State Diagram, we can fill in the State Table. § There are 4 states, one 0/0 1/0 input, and one output. 1/0 0/0 1/0 We will choose the form A B C D with four rows, one for 0/0 each current state. 1/1 0/0 § From State A, the 0 and 1 input transitions have Present Next State Output been filled in along with State x=0 x=1 the outputs. 0 0 A A B B C D Henry Hexmoor 76

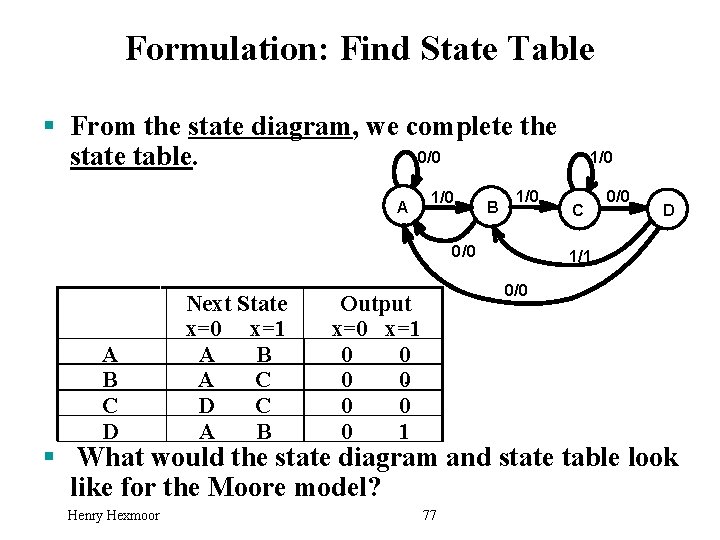

Formulation: Find State Table § From the state diagram, we complete the 0/0 state table. A 1/0 B 1/0 0/0 Present State A B C D Next State x=0 x=1 A B A C D C A B 1/0 C 0/0 D 1/1 0/0 Output x=0 x=1 0 0 0 1 § What would the state diagram and state table look like for the Moore model? Henry Hexmoor 77

Example: Moore Model for Sequence 1101 § For the Moore Model, outputs are associated with states. § We need to add a state "E" with output value 1 for the final 1 in the recognized input sequence. • This new state E, though similar to B, would generate an output of 1 and thus be different from B. § The Moore model for a sequence recognizer usually has more states than the Mealy model. Henry Hexmoor 78

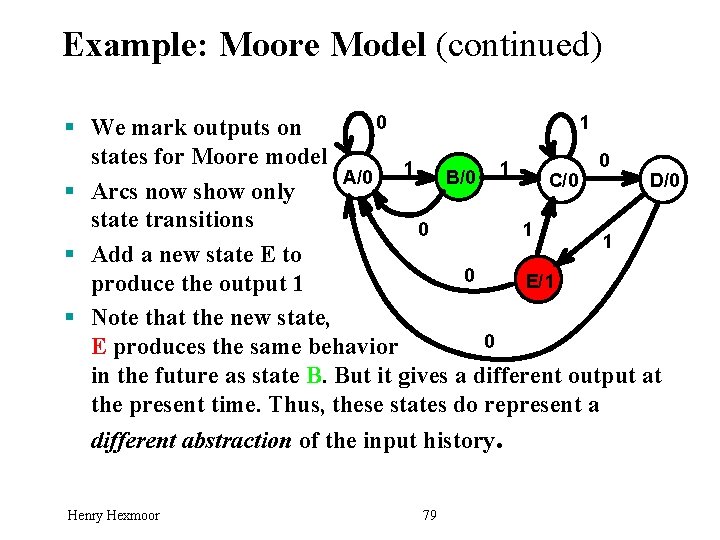

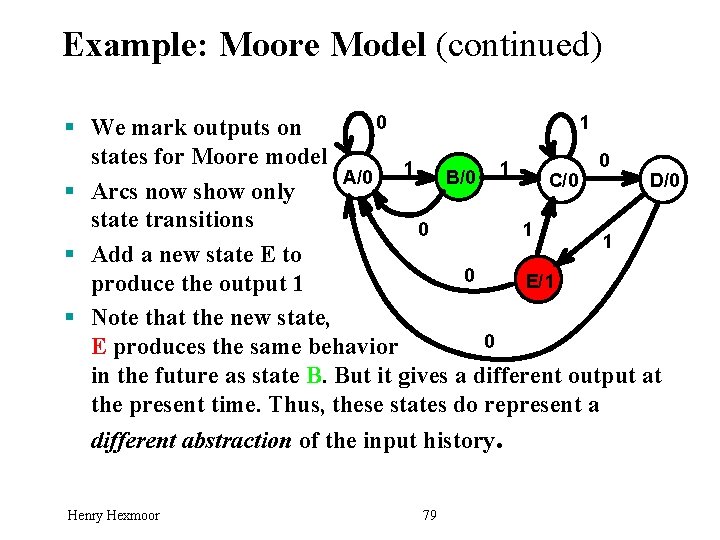

Example: Moore Model (continued) 0 1 § We mark outputs on states for Moore model 0 1 1 A/0 B/0 C/0 D/0 § Arcs now show only state transitions 0 1 1 § Add a new state E to 0 E/1 produce the output 1 § Note that the new state, 0 E produces the same behavior in the future as state B. But it gives a different output at the present time. Thus, these states do represent a different abstraction of the input history. Henry Hexmoor 79

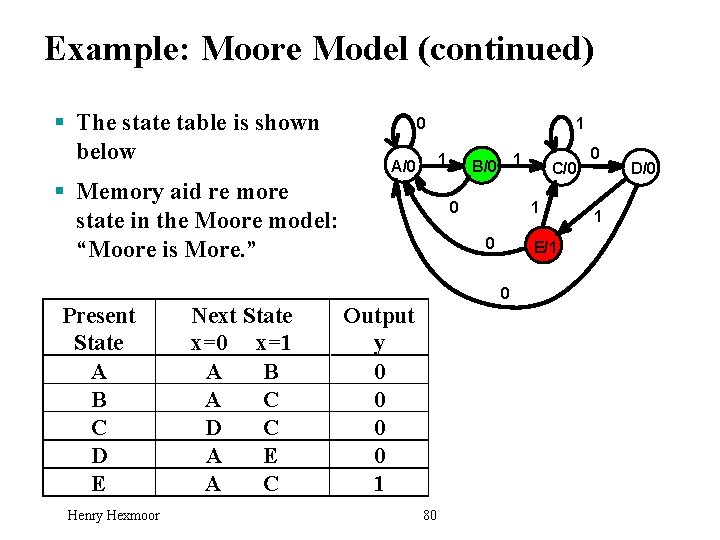

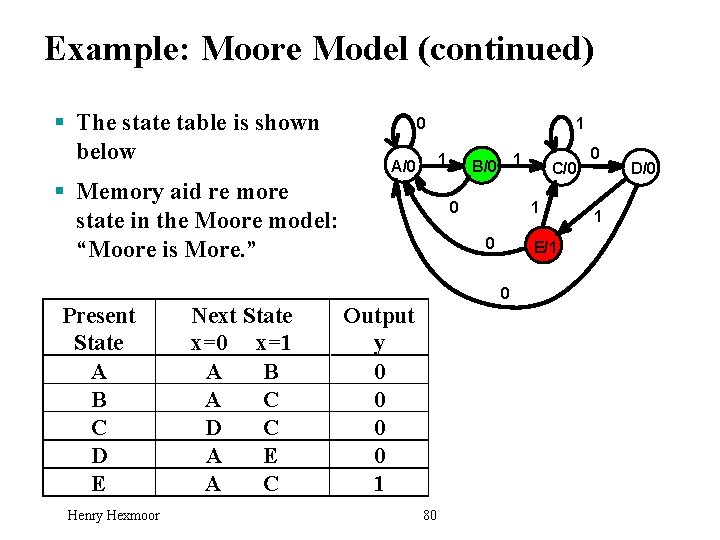

Example: Moore Model (continued) 0 1 § The state table is shown 0 below 1 1 A/0 B/0 C/0 § Memory aid re more 0 1 1 state in the Moore model: 0 E/1 “Moore is More. ” Present State A B C D E Henry Hexmoor Next State x=0 x=1 A B A C D C A E A C 0 Output y 0 0 1 80 D/0

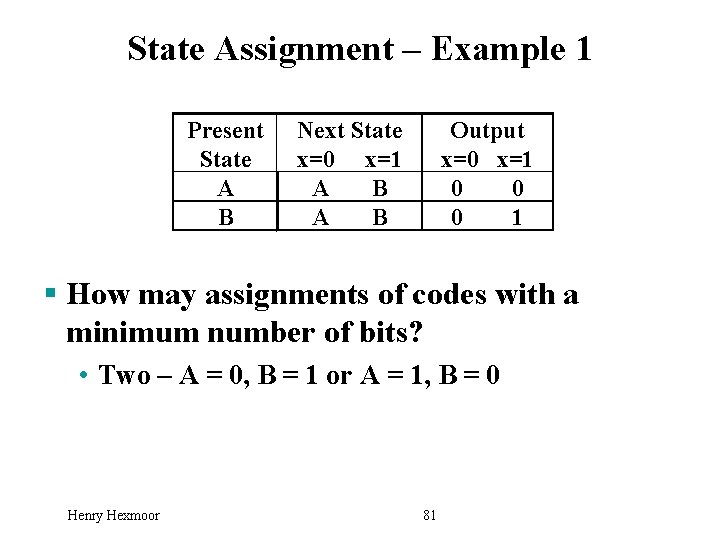

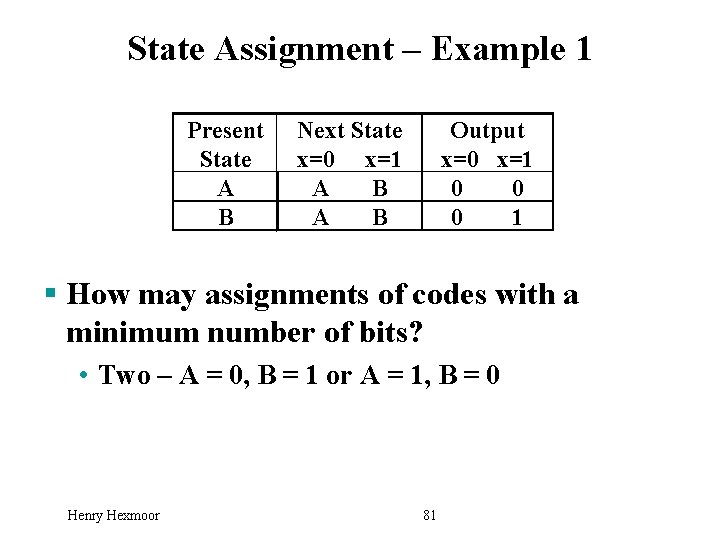

State Assignment – Example 1 Present State A B Next State x=0 x=1 A B Output x=0 x=1 0 0 0 1 § How may assignments of codes with a minimum number of bits? • Two – A = 0, B = 1 or A = 1, B = 0 Henry Hexmoor 81

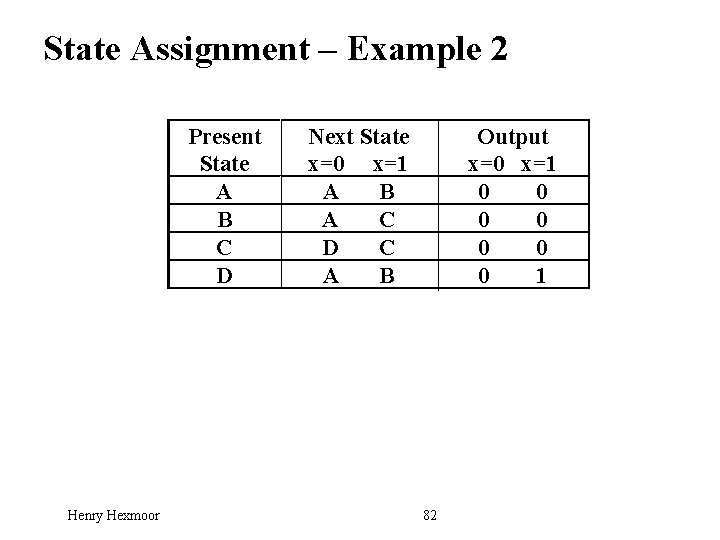

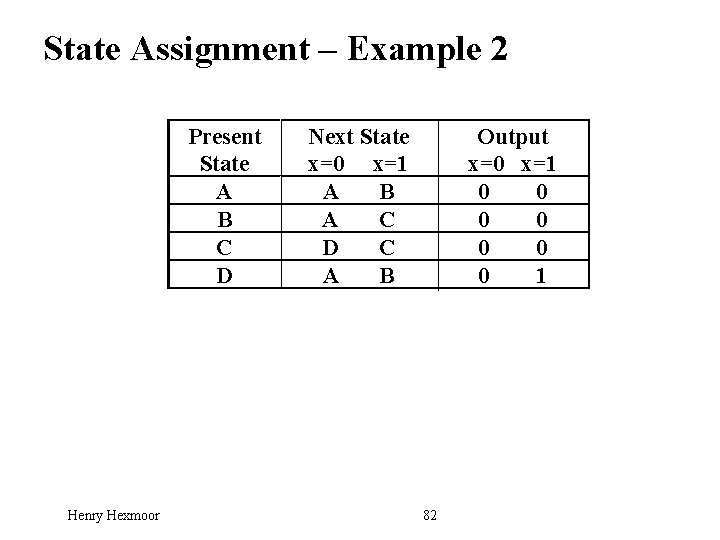

State Assignment – Example 2 Present State A B C D Next State x=0 x=1 A B A C D C A B Output x=0 x=1 0 0 0 1 Henry Hexmoor 82

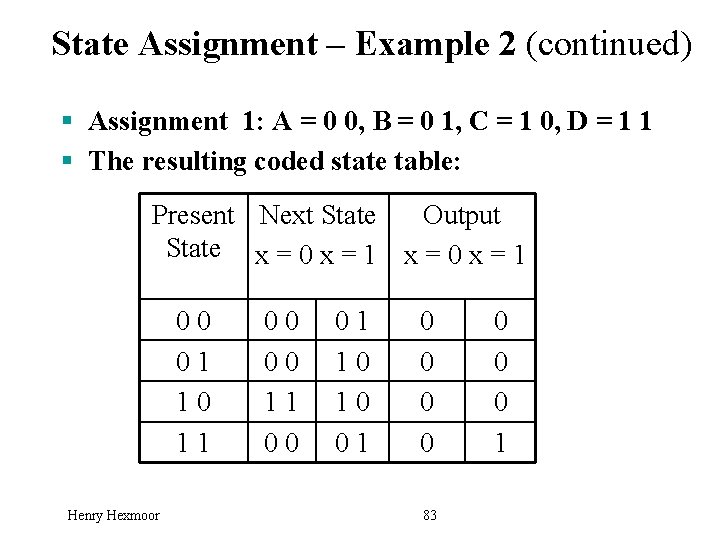

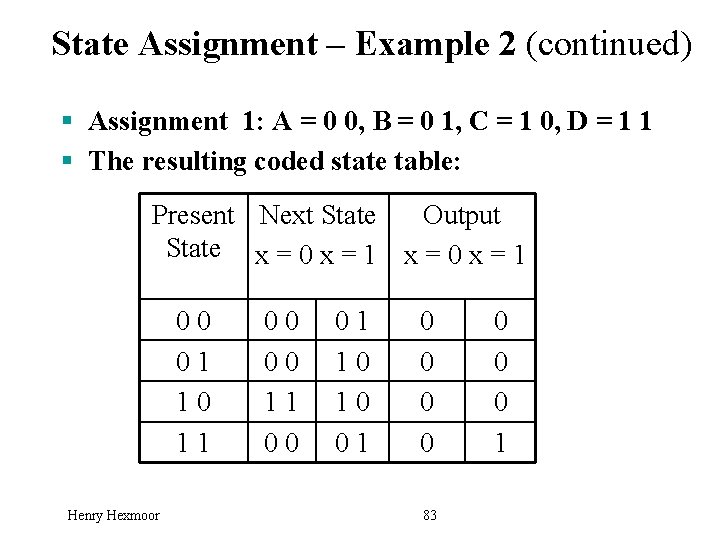

State Assignment – Example 2 (continued) § Assignment 1: A = 0 0, B = 0 1, C = 1 0, D = 1 1 § The resulting coded state table: Present Next State Output State x = 0 x = 1 00 01 10 11 Henry Hexmoor 00 00 11 00 01 10 10 01 0 0 83 0 0 0 1

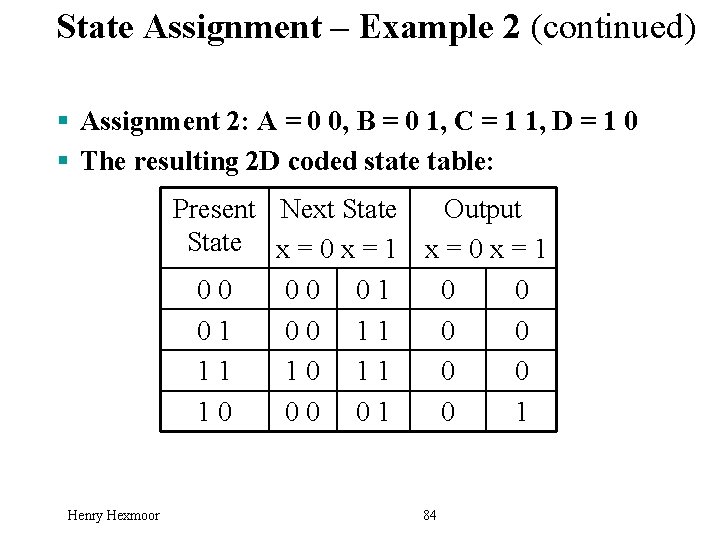

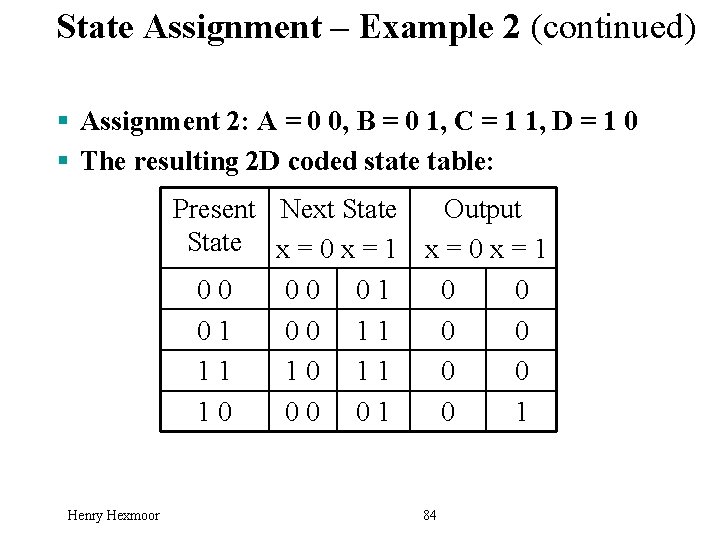

State Assignment – Example 2 (continued) § Assignment 2: A = 0 0, B = 0 1, C = 1 1, D = 1 0 § The resulting 2 D coded state table: Present Next State Output State x = 0 x = 1 00 00 01 00 11 0 0 11 10 11 0 0 10 00 01 0 1 Henry Hexmoor 84

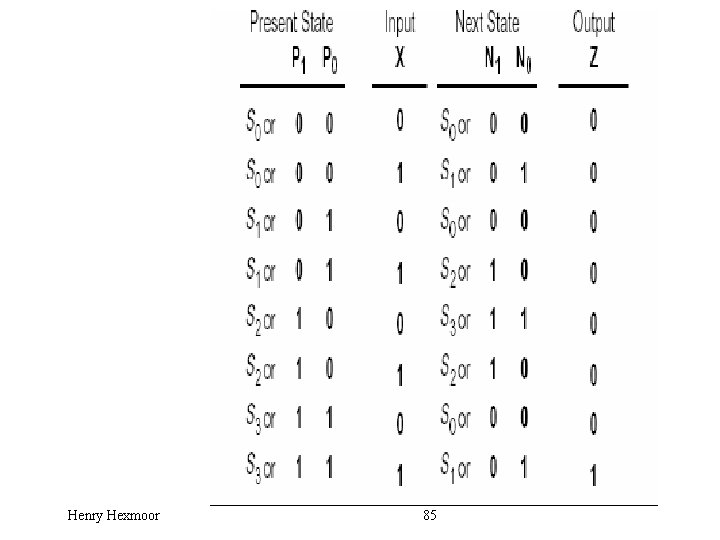

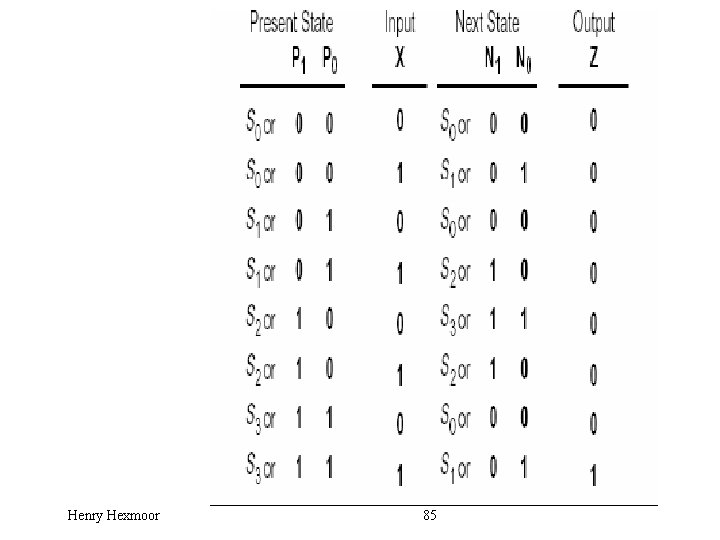

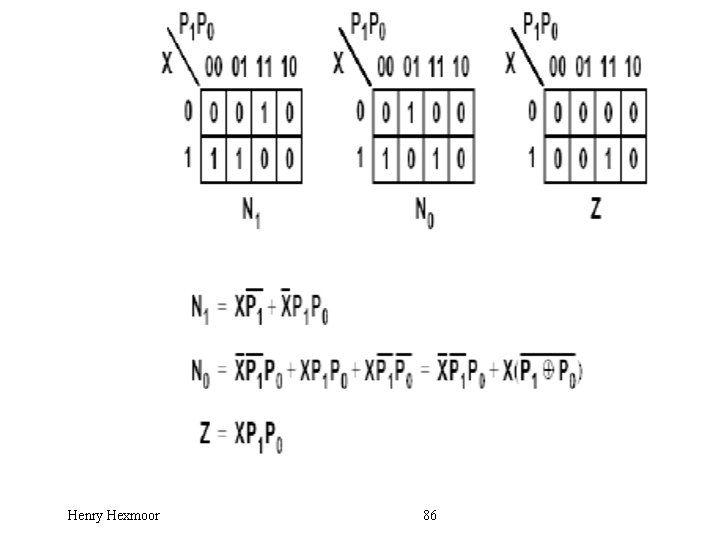

Henry Hexmoor 85

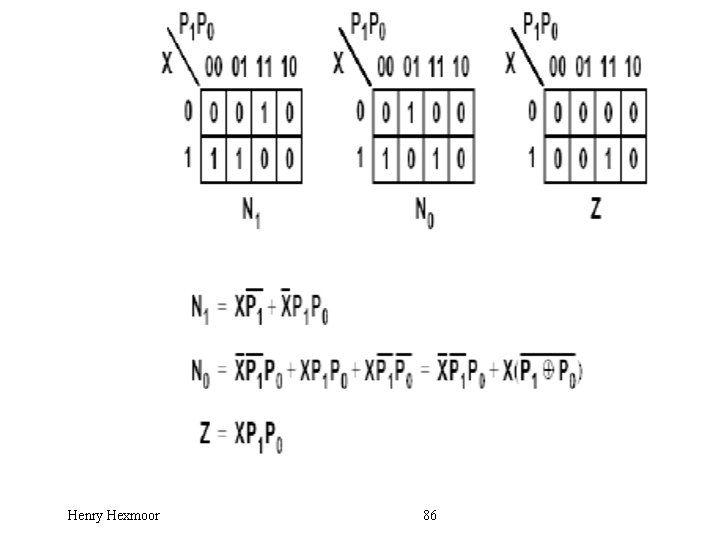

Henry Hexmoor 86

Henry Hexmoor 87

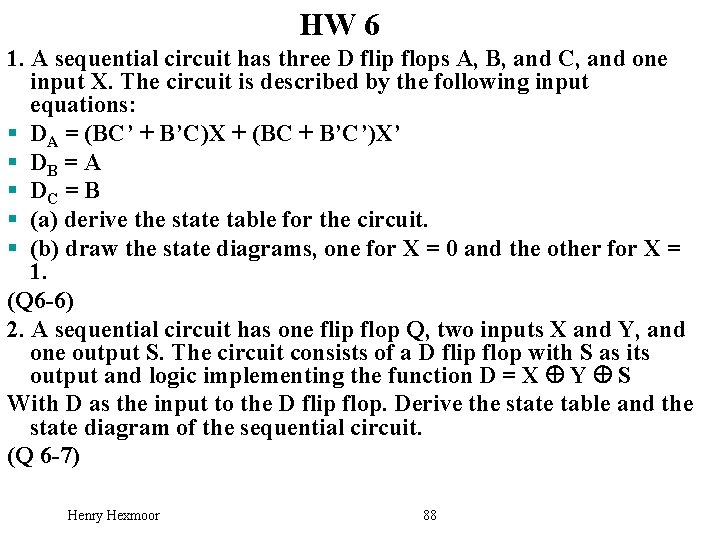

HW 6 1. A sequential circuit has three D flip flops A, B, and C, and one input X. The circuit is described by the following input equations: § DA = (BC’ + B’C)X + (BC + B’C’)X’ § DB = A § DC = B § (a) derive the state table for the circuit. § (b) draw the state diagrams, one for X = 0 and the other for X = 1. (Q 6 -6) 2. A sequential circuit has one flip flop Q, two inputs X and Y, and one output S. The circuit consists of a D flip flop with S as its output and logic implementing the function D = X Y S With D as the input to the D flip flop. Derive the state table and the state diagram of the sequential circuit. (Q 6 -7) Henry Hexmoor 88