Sequential Circuits Sequential Circuits Two primary differences between

Sequential Circuits

Sequential Circuits • Two primary differences between combinational circuits and sequential circuits – Sequential circuits are synchronous (use a clock) – Sequential circuits have memory (current state)

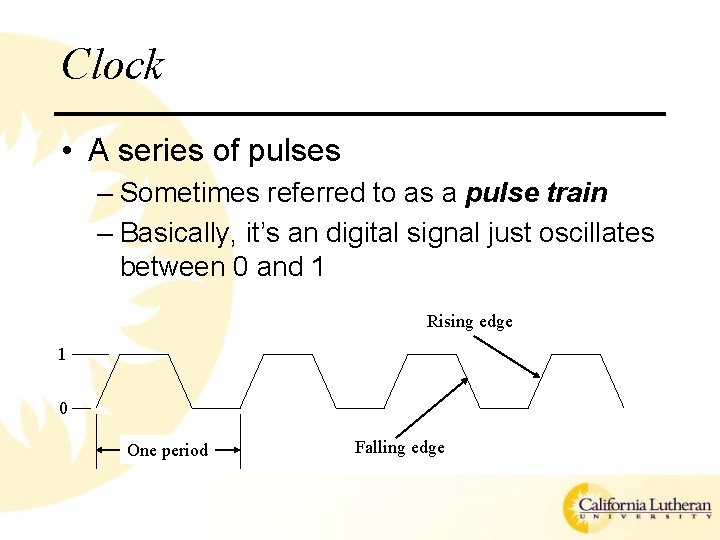

Clock • A series of pulses – Sometimes referred to as a pulse train – Basically, it’s an digital signal just oscillates between 0 and 1 Rising edge 1 0 One period Falling edge

Clock • Clock period is specified in units of time – Seconds, milliseconds, microseconds… • Clock frequency is specified in units of frequency – 1/period – pulses per timeunit – Hertz, Megahertz, Gigahertz…

Memory Devices • Flip flops – Four basic types • SR, D, JK, T – Each type stores 1 -bit (two states: 0/1) – Each maintains its current state until a clock pulse arrives • i. e. Ignores input lines until a clock pulse reaches the clock input

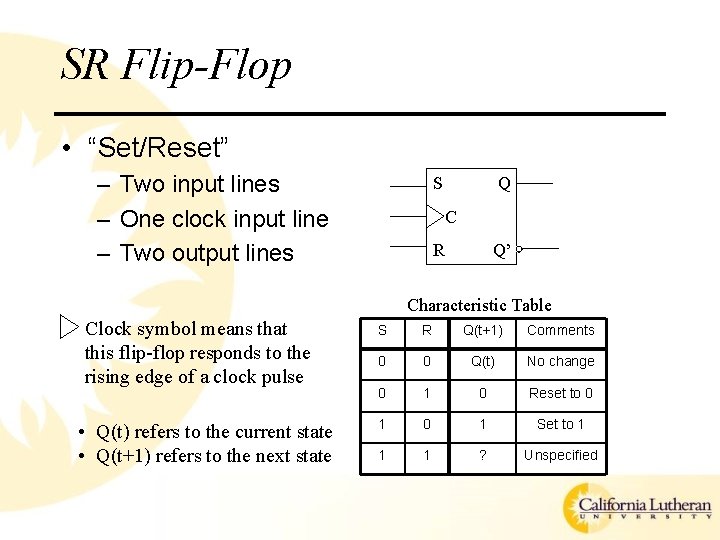

SR Flip-Flop • “Set/Reset” – Two input lines – One clock input line – Two output lines S Q C R Q’ Characteristic Table Clock symbol means that this flip-flop responds to the rising edge of a clock pulse • Q(t) refers to the current state • Q(t+1) refers to the next state S R Q(t+1) Comments 0 0 Q(t) No change 0 1 0 Reset to 0 1 Set to 1 1 1 ? Unspecified

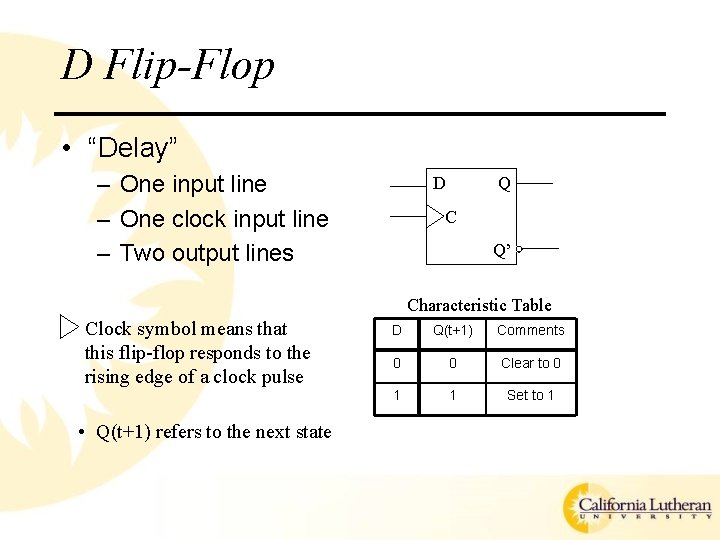

D Flip-Flop • “Delay” – One input line – One clock input line – Two output lines D Q C Q’ Characteristic Table Clock symbol means that this flip-flop responds to the rising edge of a clock pulse • Q(t+1) refers to the next state D Q(t+1) Comments 0 0 Clear to 0 1 1 Set to 1

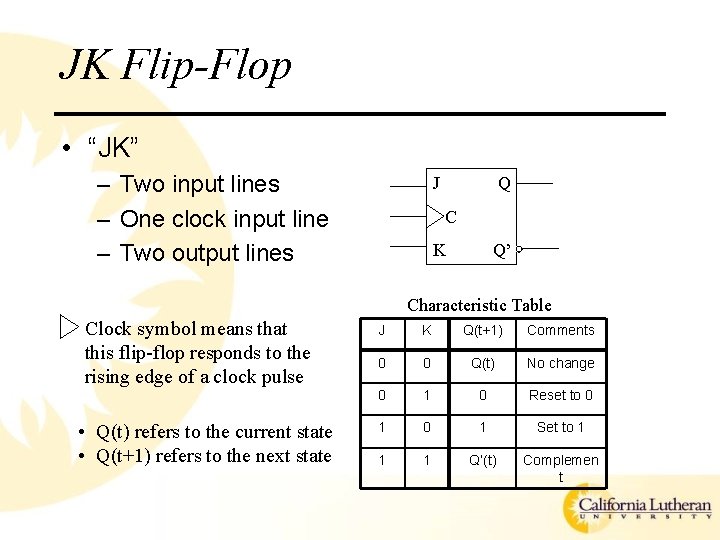

JK Flip-Flop • “JK” – Two input lines – One clock input line – Two output lines J Q C K Q’ Characteristic Table Clock symbol means that this flip-flop responds to the rising edge of a clock pulse • Q(t) refers to the current state • Q(t+1) refers to the next state J K Q(t+1) Comments 0 0 Q(t) No change 0 1 0 Reset to 0 1 Set to 1 1 1 Q’(t) Complemen t

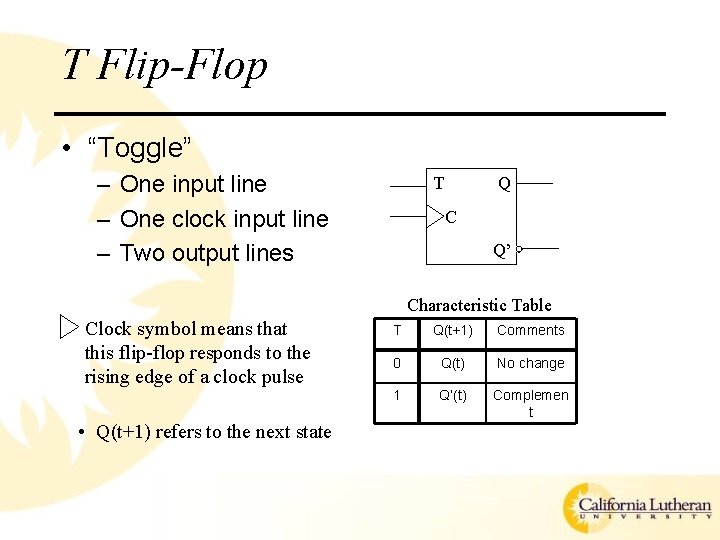

T Flip-Flop • “Toggle” – One input line – One clock input line – Two output lines T Q C Q’ Characteristic Table Clock symbol means that this flip-flop responds to the rising edge of a clock pulse • Q(t+1) refers to the next state T Q(t+1) Comments 0 Q(t) No change 1 Q’(t) Complemen t

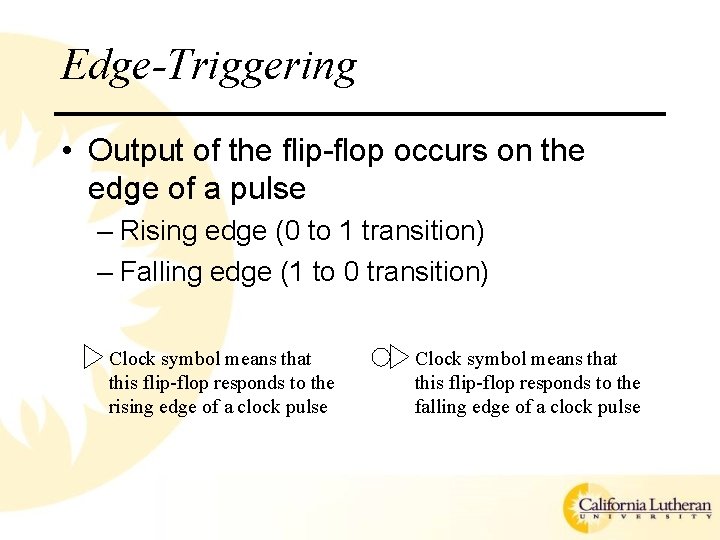

Edge-Triggering • Output of the flip-flop occurs on the edge of a pulse – Rising edge (0 to 1 transition) – Falling edge (1 to 0 transition) Clock symbol means that this flip-flop responds to the rising edge of a clock pulse Clock symbol means that this flip-flop responds to the falling edge of a clock pulse

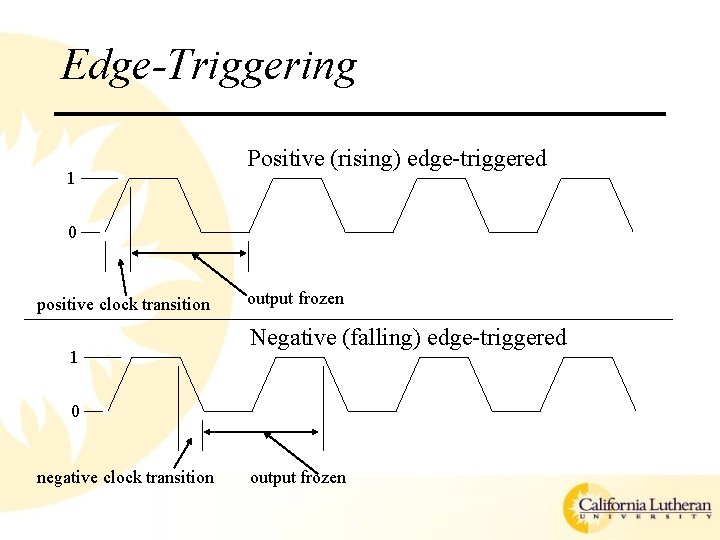

Edge-Triggering 1 Positive (rising) edge-triggered 0 positive clock transition 1 output frozen Negative (falling) edge-triggered 0 negative clock transition output frozen

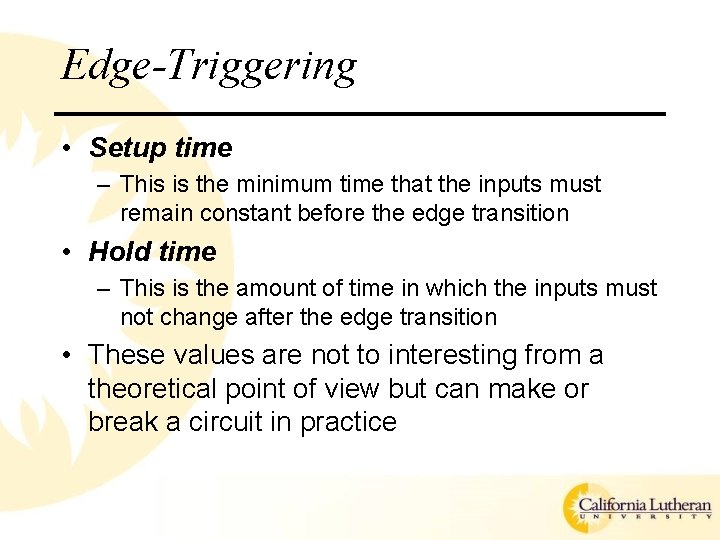

Edge-Triggering • Setup time – This is the minimum time that the inputs must remain constant before the edge transition • Hold time – This is the amount of time in which the inputs must not change after the edge transition • These values are not to interesting from a theoretical point of view but can make or break a circuit in practice

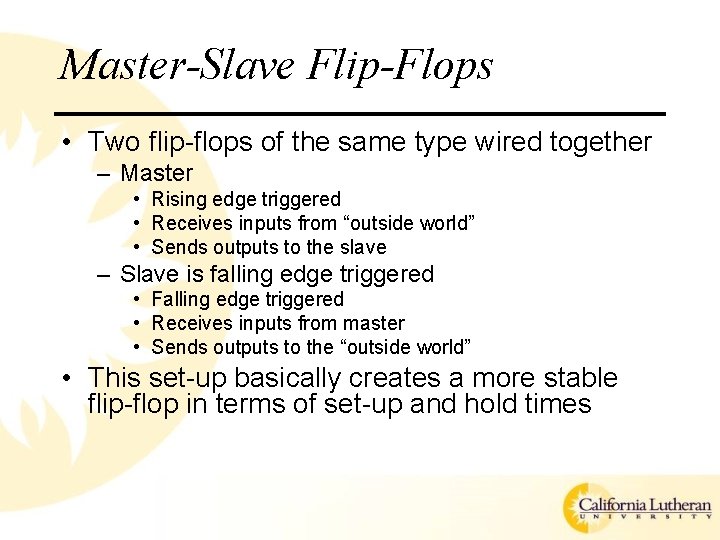

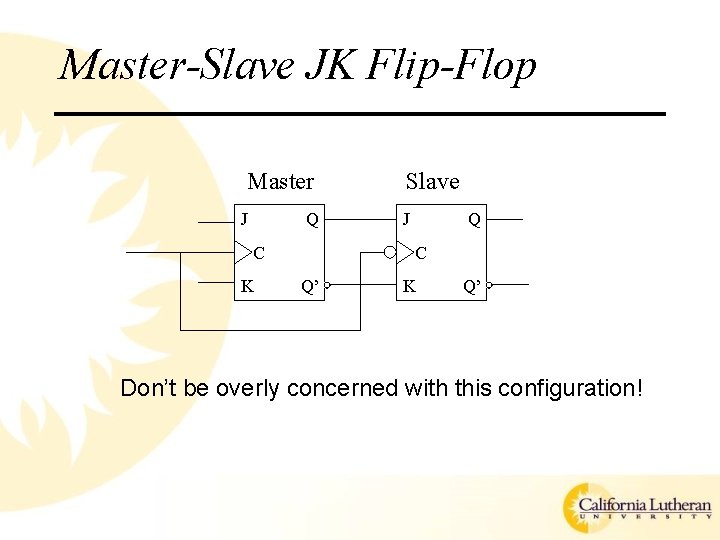

Master-Slave Flip-Flops • Two flip-flops of the same type wired together – Master • Rising edge triggered • Receives inputs from “outside world” • Sends outputs to the slave – Slave is falling edge triggered • Falling edge triggered • Receives inputs from master • Sends outputs to the “outside world” • This set-up basically creates a more stable flip-flop in terms of set-up and hold times

Master-Slave JK Flip-Flop Master J Q C K Slave J Q C Q’ K Q’ Don’t be overly concerned with this configuration!

Additional Inputs • May have… – Preset and Clear inputs which are used to set the flip flop to a predetermined state prior to starting the clock – Initialization

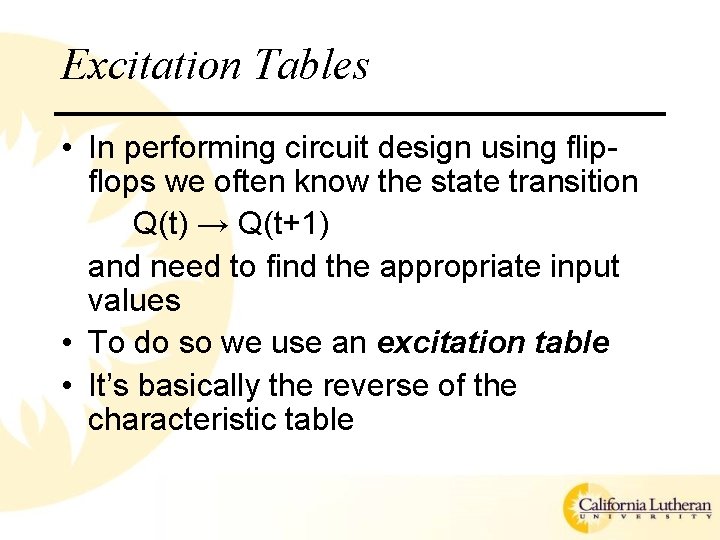

Excitation Tables • In performing circuit design using flipflops we often know the state transition Q(t) → Q(t+1) and need to find the appropriate input values • To do so we use an excitation table • It’s basically the reverse of the characteristic table

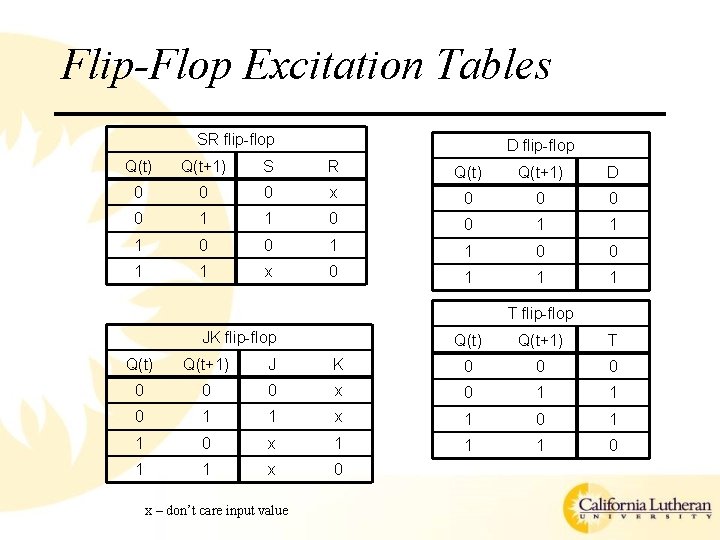

Flip-Flop Excitation Tables SR flip-flop D flip-flop Q(t) Q(t+1) S R Q(t) Q(t+1) D 0 0 0 x 0 0 1 1 0 0 1 1 x 0 1 1 1 T flip-flop JK flip-flop Q(t) Q(t+1) T Q(t) Q(t+1) J K 0 0 0 x 0 1 1 x 1 0 1 1 0 x 1 1 1 0 1 1 x 0 x – don’t care input value

Sequential Circuits • Combination of logic gates, flip-flops (memory elements), and a clock signal • The circuit can be described in two parts – The combinational part – The sequential part

The Combinational Part • Nothing more than what we’ve been doing so far – Describe outputs in terms of logic gates and flip-flop outputs

The Sequential Part • Flip-flop input equations – Describe the inputs to flip-flop elements in terms of logic gates and flip-flop elements

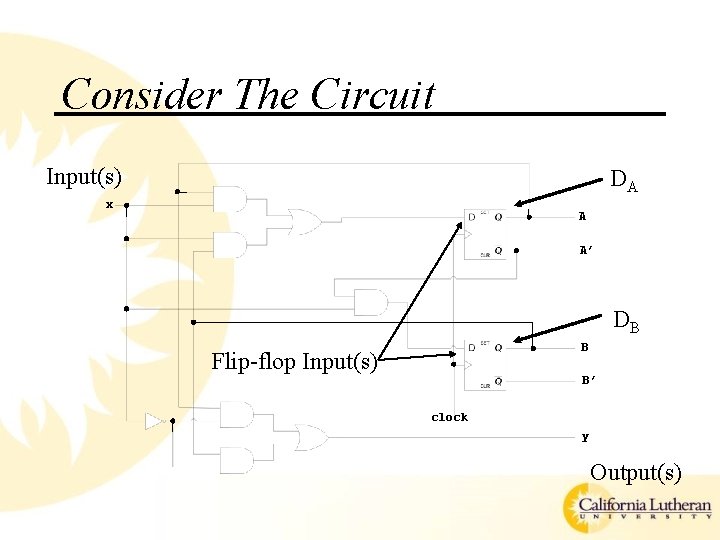

Consider The Circuit Input(s) DA x A A’ DB B Flip-flop Input(s) B’ clock y Output(s)

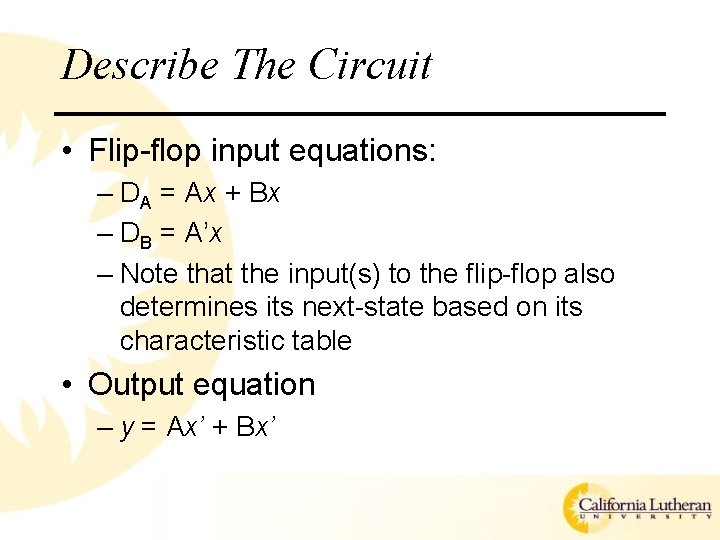

Describe The Circuit • Flip-flop input equations: – DA = Ax + Bx – DB = A’x – Note that the input(s) to the flip-flop also determines its next-state based on its characteristic table • Output equation – y = Ax’ + Bx’

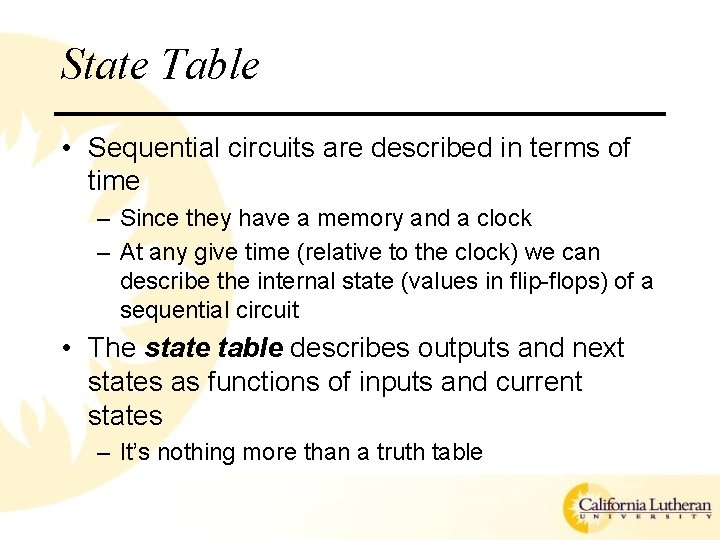

State Table • Sequential circuits are described in terms of time – Since they have a memory and a clock – At any give time (relative to the clock) we can describe the internal state (values in flip-flops) of a sequential circuit • The state table describes outputs and next states as functions of inputs and current states – It’s nothing more than a truth table

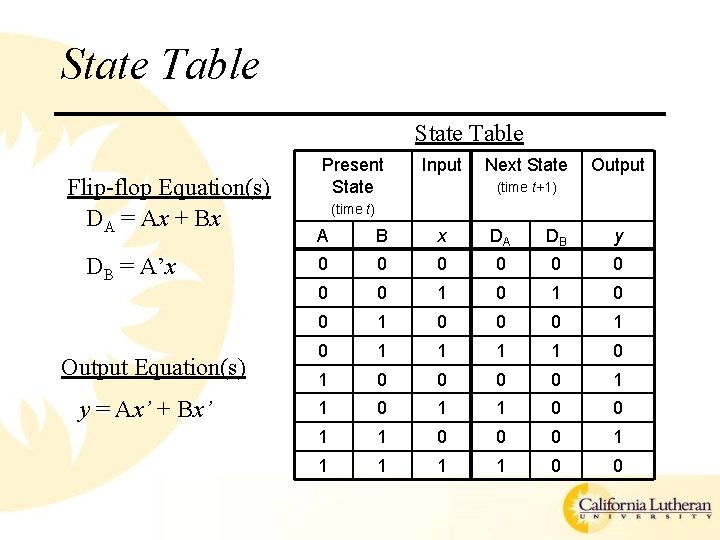

State Table Flip-flop Equation(s) DA = Ax + Bx DB = A’x Output Equation(s) y = Ax’ + Bx’ Present State Input Next State Output (time t+1) (time t) A B x DA DB y 0 0 0 0 1 0 0 0 1 1 1 1 0 0 0 0 1 1 0 0 0 1 1 1 0 0

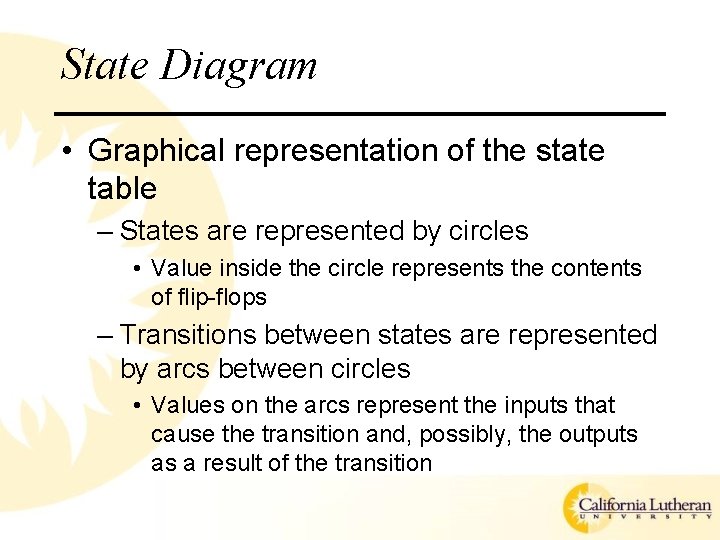

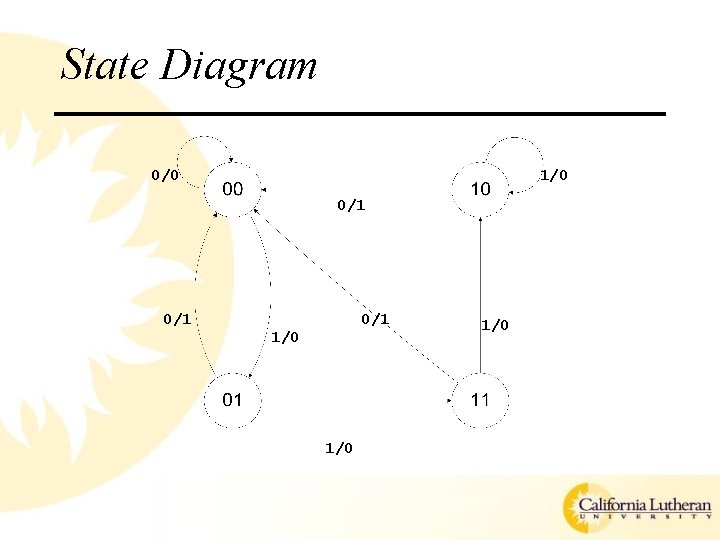

State Diagram • Graphical representation of the state table – States are represented by circles • Value inside the circle represents the contents of flip-flops – Transitions between states are represented by arcs between circles • Values on the arcs represent the inputs that cause the transition and, possibly, the outputs as a result of the transition

State Diagram 0/0 1/0 0/1 0/1 1/0 1/0

State Tables/Diagrams • Represent the same information • Are derivable from one another • They exist solely to support design and understanding of sequential circuit behavior • One form may be more suitable for a given task than the other

Designing a Circuit • The goal of circuit design is to convert a specification (a bunch of words) into a circuit – No different than software development! • Consider this example from the book – Design a circuit that counts modulo 4 every time it receives a 1 on the input line

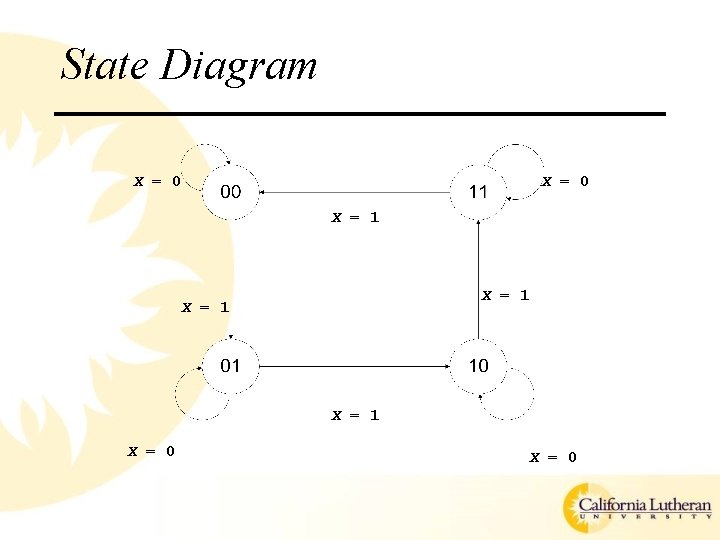

State Diagram X = 0 X = 1 X = 0

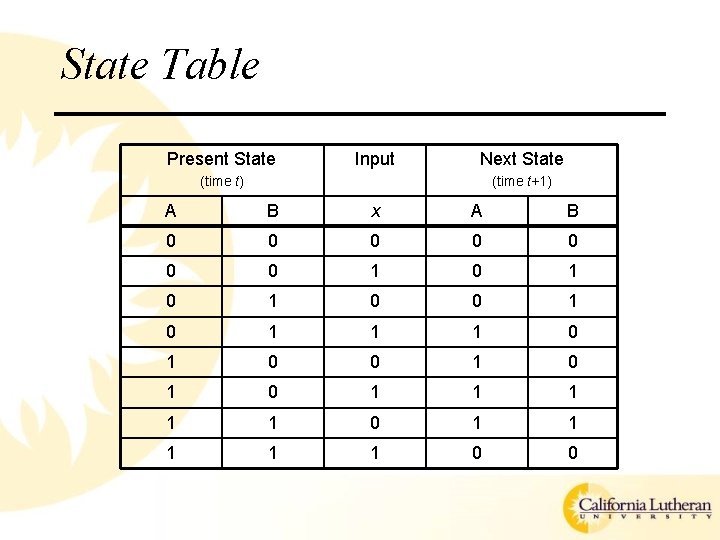

State Table Present State Input Next State (time t) (time t+1) A B x A B 0 0 0 0 1 0 1 0 1 1 1 0 0 1 0 1 1 1 1 1 0 0

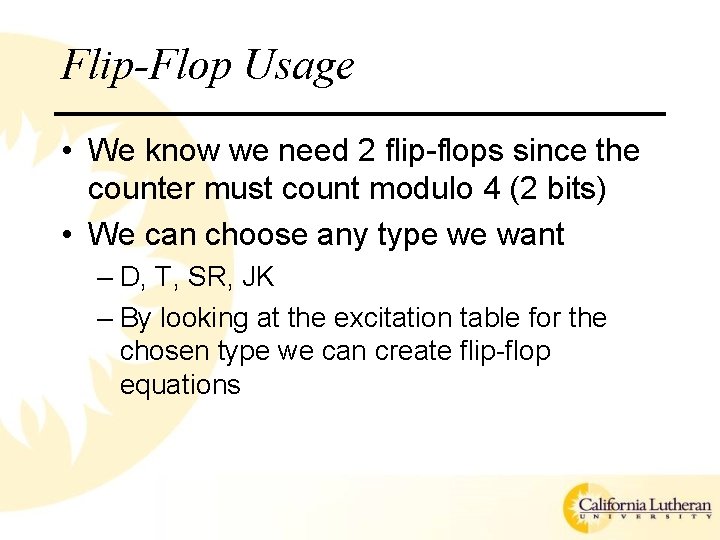

Flip-Flop Usage • We know we need 2 flip-flops since the counter must count modulo 4 (2 bits) • We can choose any type we want – D, T, SR, JK – By looking at the excitation table for the chosen type we can create flip-flop equations

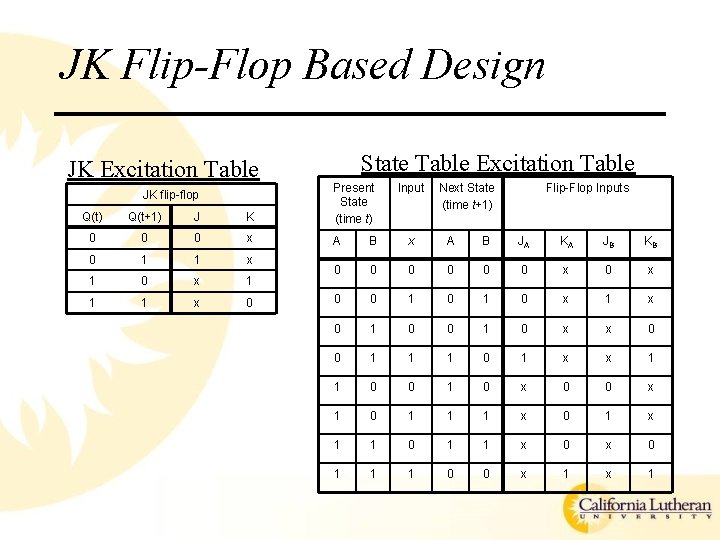

JK Flip-Flop Based Design JK Excitation Table State Table Excitation Table Q(t) Q(t+1) J K Present State (time t) 0 0 0 x A B JA KA JB KB 0 1 1 x 1 0 0 0 0 x 1 1 x 0 0 0 1 0 x 1 x 0 1 0 x x 0 0 1 1 1 0 1 x x 1 1 0 0 1 0 x 0 0 x 1 0 1 1 1 x 0 1 x 1 1 0 1 1 x 0 1 1 1 0 0 x 1 JK flip-flop Input Next State (time t+1) Flip-Flop Inputs

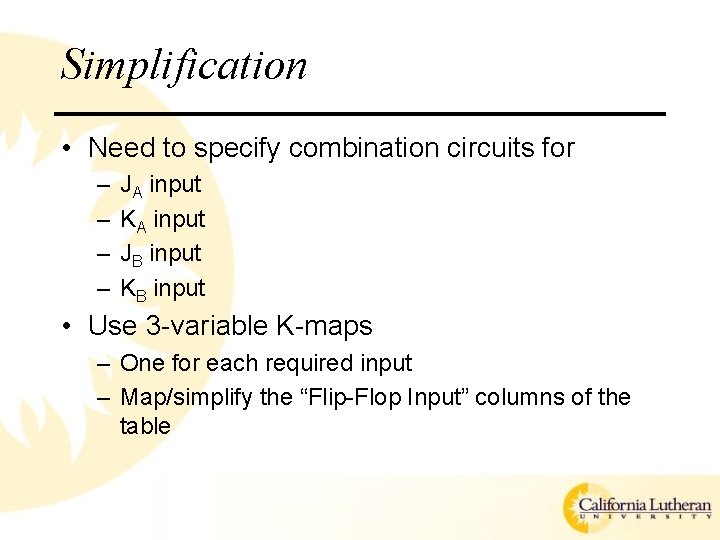

Simplification • Need to specify combination circuits for – – JA input KA input JB input KB input • Use 3 -variable K-maps – One for each required input – Map/simplify the “Flip-Flop Input” columns of the table

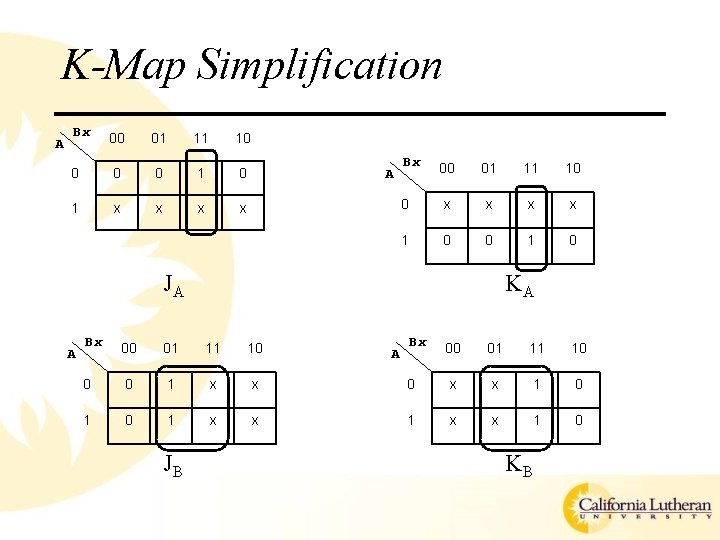

K-Map Simplification A Bx 00 01 11 10 0 1 0 1 x x A Bx 00 01 11 10 0 x x 1 0 0 1 0 JA A KA Bx 00 01 11 10 0 0 1 x x 1 0 1 x x JB A Bx 00 01 11 10 0 x x 1 0 1 x x 1 0 KB

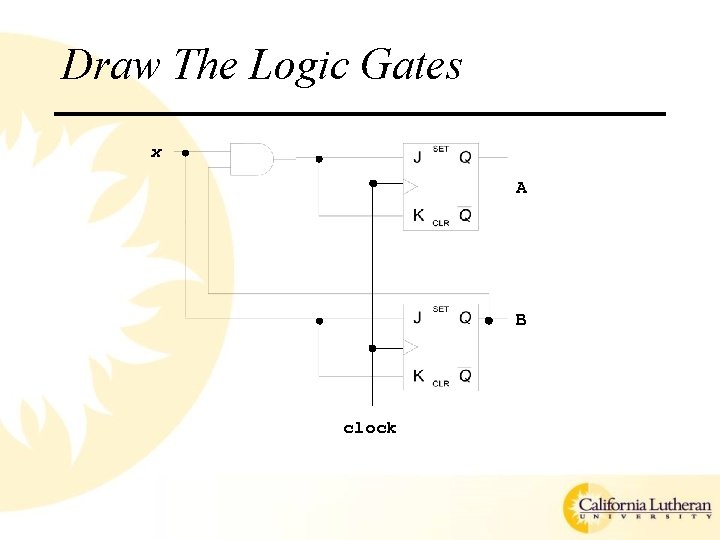

Draw The Logic Gates x A B clock

Homework • Pages 37 -38 – Problems • 1 -8, 1 -9, 1 -10, 1 -11, 1 -12, 1 -13, 1 -15, 1 -16 • Due next lecture

Exam #1 • Chapters 1 and 3 – Binary number representations – 2’s complement arithmetic – Boolean logic • Axioms • K-maps – Flip-flops • State tables, state diagrams – Circuit design • Closed book, closed notes – I’ll give you all you need

- Slides: 37