Chapter 5 Sequential Circuits Sequential Circuits Combinational Circuits

Chapter 5 Sequential Circuits

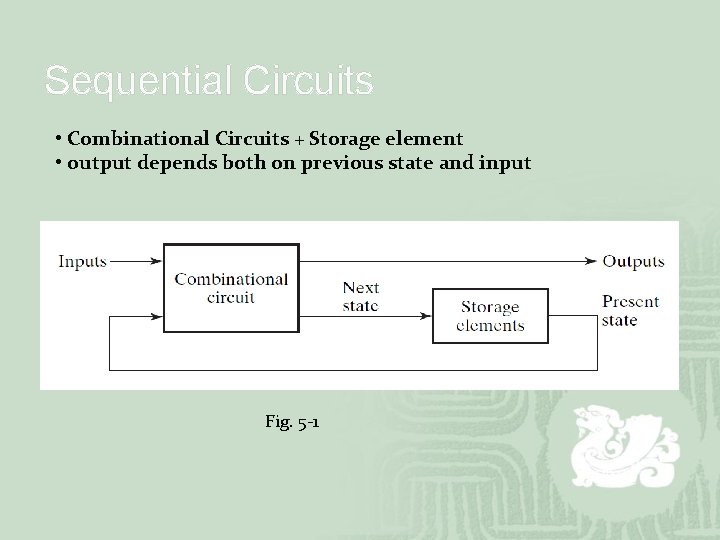

Sequential Circuits • Combinational Circuits + Storage element • output depends both on previous state and input Fig. 5 -1

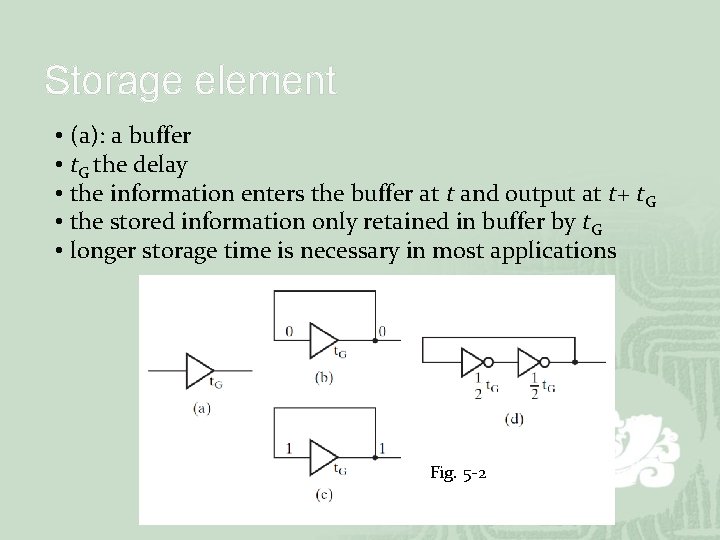

Storage element • (a): a buffer • t. G the delay • the information enters the buffer at t and output at t+ t. G • the stored information only retained in buffer by t. G • longer storage time is necessary in most applications Fig. 5 -2

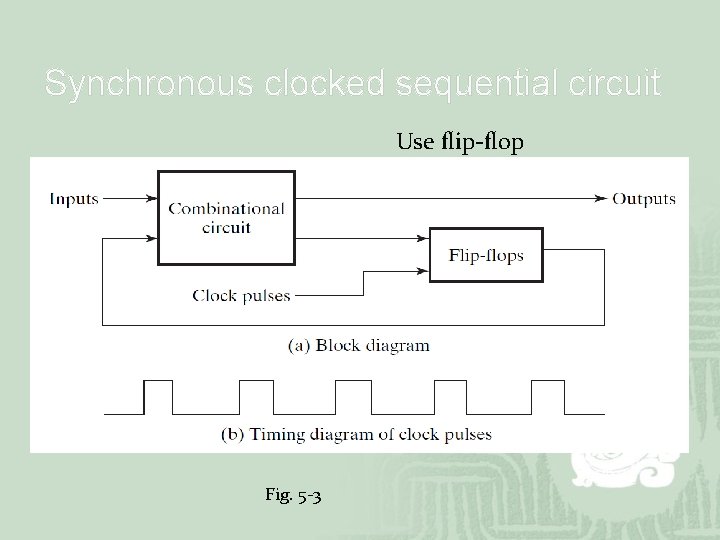

Synchronous clocked sequential circuit Use flip-flop Fig. 5 -3

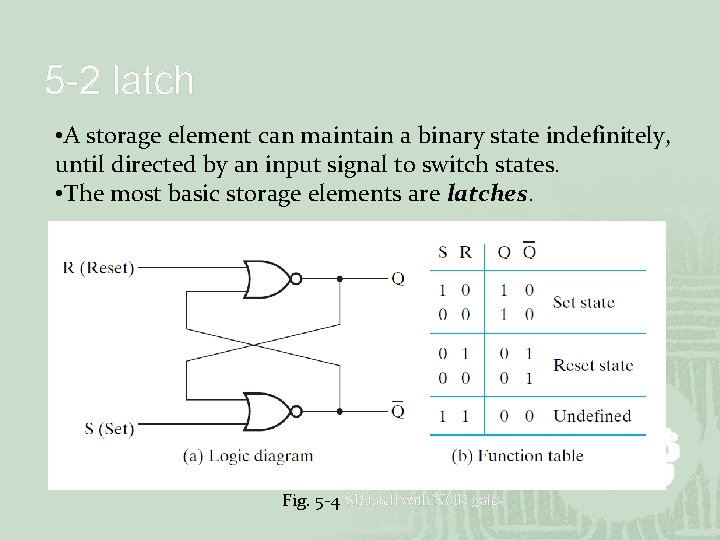

5 -2 latch • A storage element can maintain a binary state indefinitely, until directed by an input signal to switch states. • The most basic storage elements are latches. Fig. 5 -4 SR latch with NOR gates

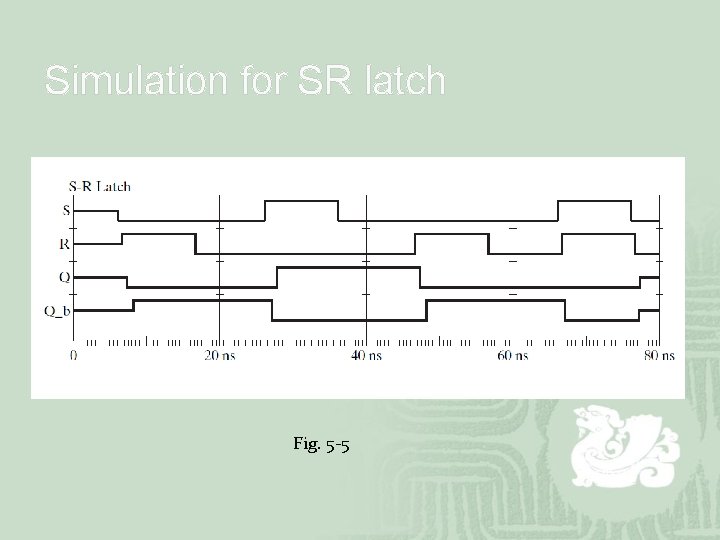

Simulation for SR latch Fig. 5 -5

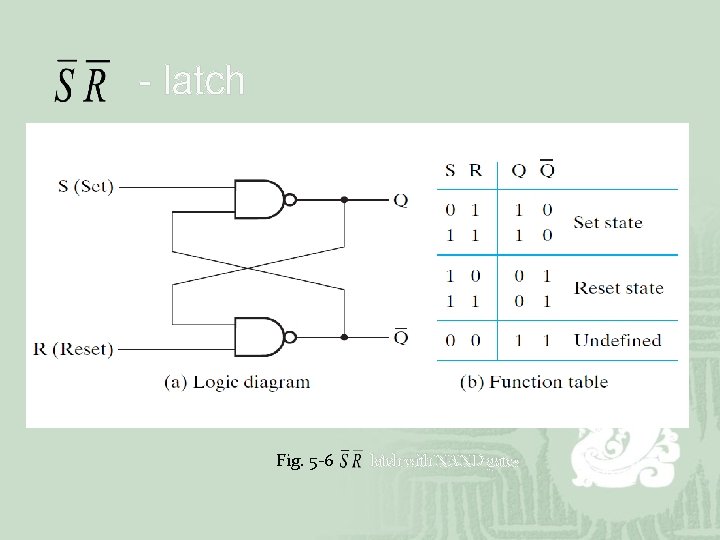

- latch Fig. 5 -6 latch with NAND gates

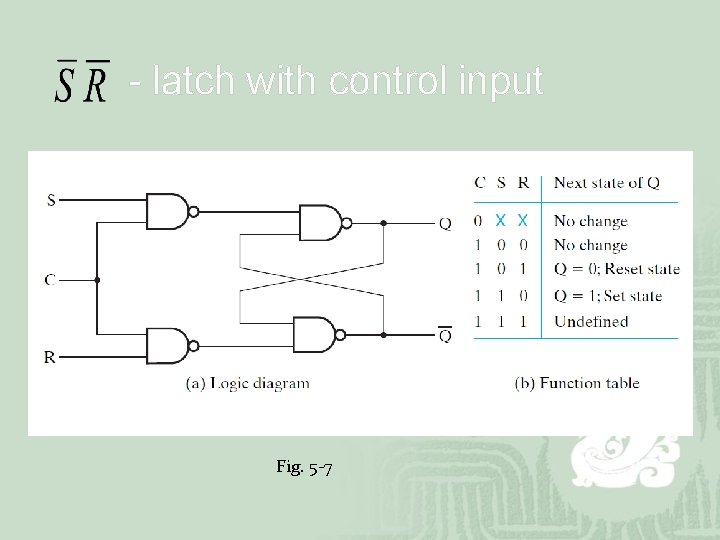

- latch with control input Fig. 5 -7

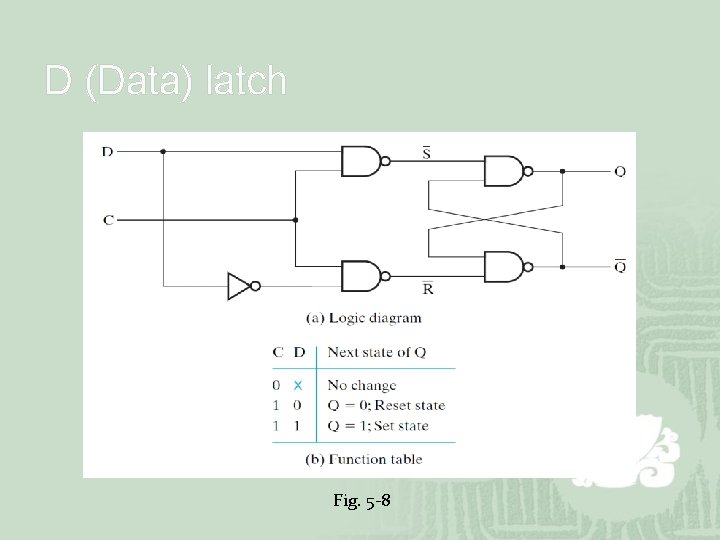

D (Data) latch Fig. 5 -8

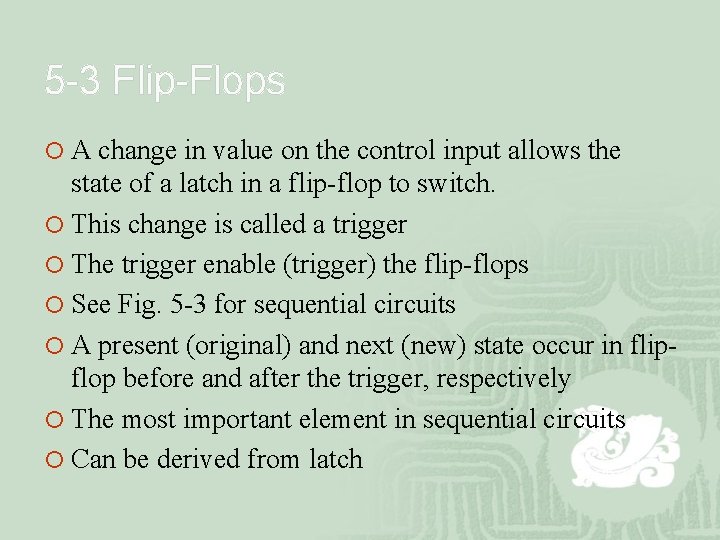

5 -3 Flip-Flops ¡ A change in value on the control input allows the state of a latch in a flip-flop to switch. ¡ This change is called a trigger ¡ The trigger enable (trigger) the flip-flops ¡ See Fig. 5 -3 for sequential circuits ¡ A present (original) and next (new) state occur in flipflop before and after the trigger, respectively ¡ The most important element in sequential circuits ¡ Can be derived from latch

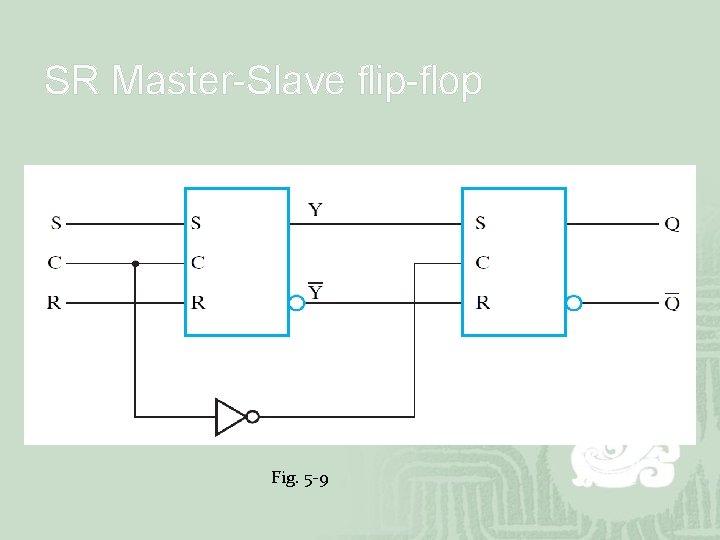

SR Master-Slave flip-flop Fig. 5 -9

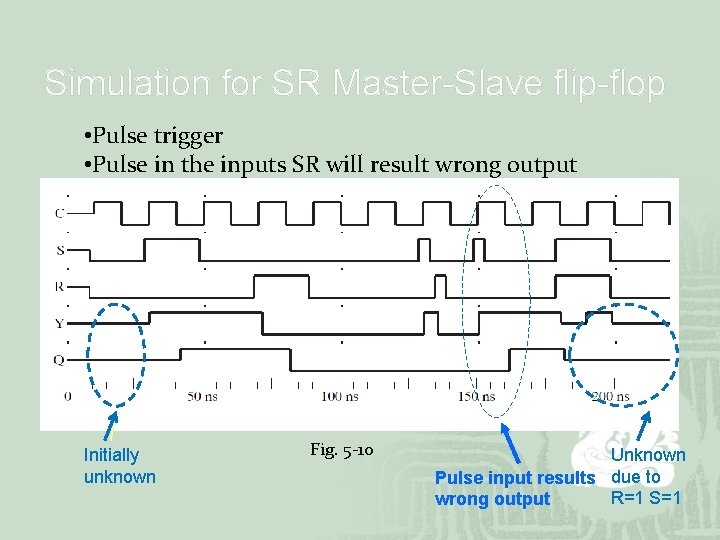

Simulation for SR Master-Slave flip-flop • Pulse trigger • Pulse in the inputs SR will result wrong output Initially unknown Fig. 5 -10 Unknown Pulse input results due to R=1 S=1 wrong output

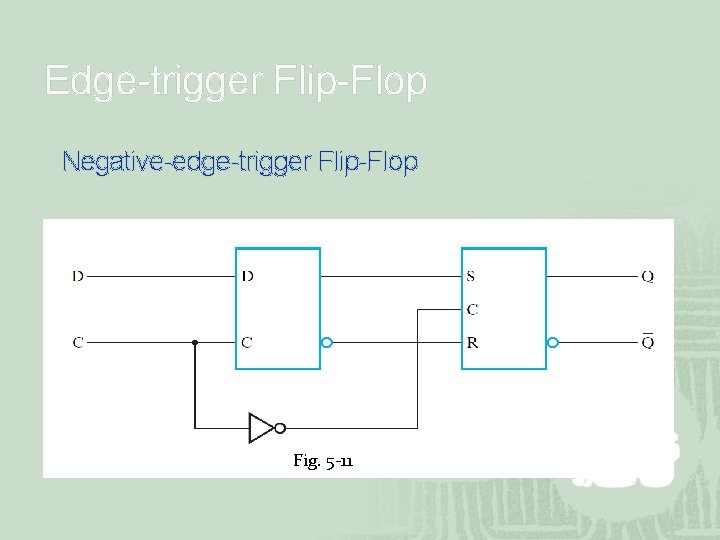

Edge-trigger Flip-Flop Negative-edge-trigger Flip-Flop Fig. 5 -11

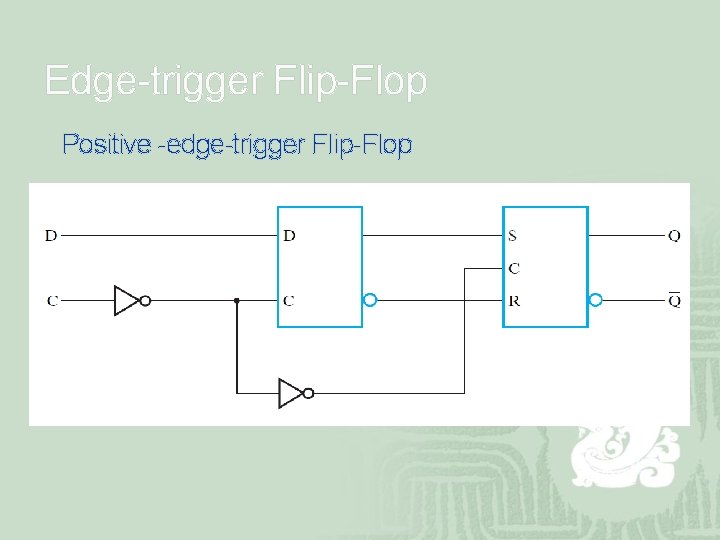

Edge-trigger Flip-Flop Positive -edge-trigger Flip-Flop

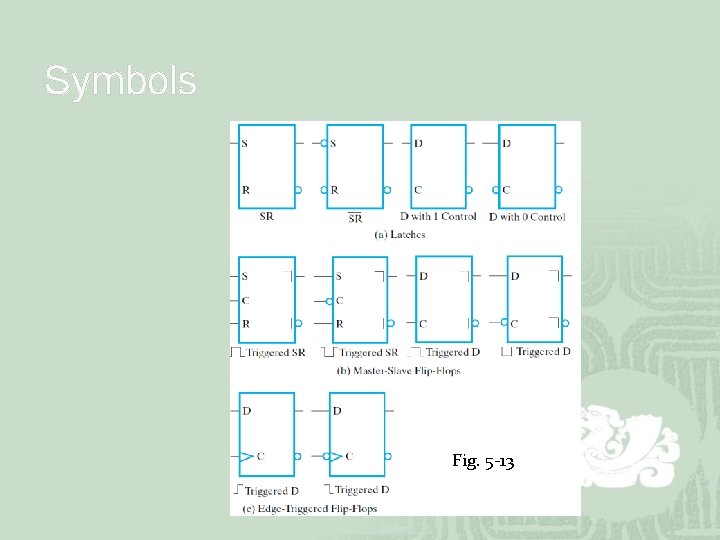

Symbols Fig. 5 -13

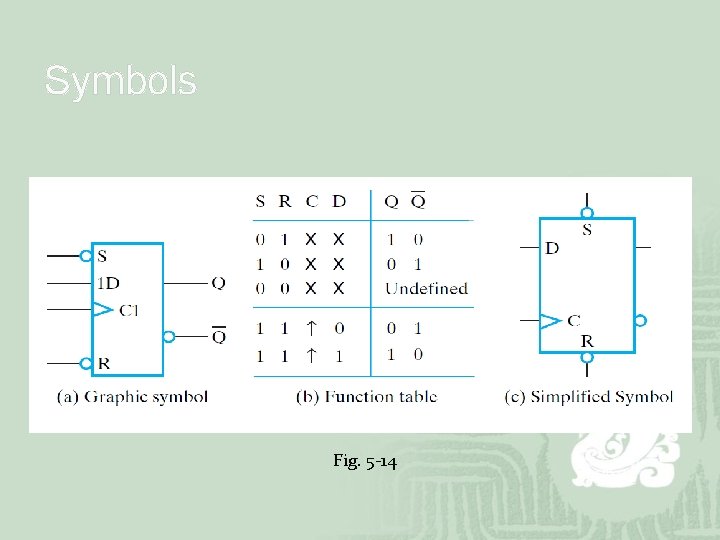

Symbols Fig. 5 -14

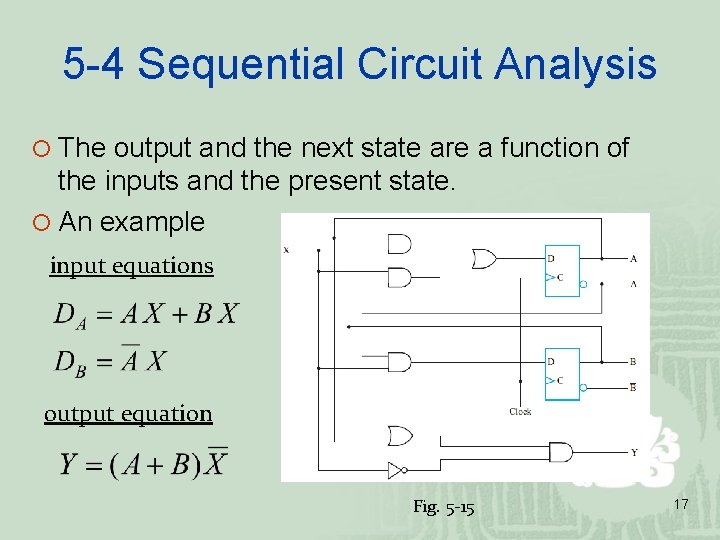

5 -4 Sequential Circuit Analysis ¡ The output and the next state are a function of the inputs and the present state. ¡ An example input equations output equation Fig. 5 -15 17

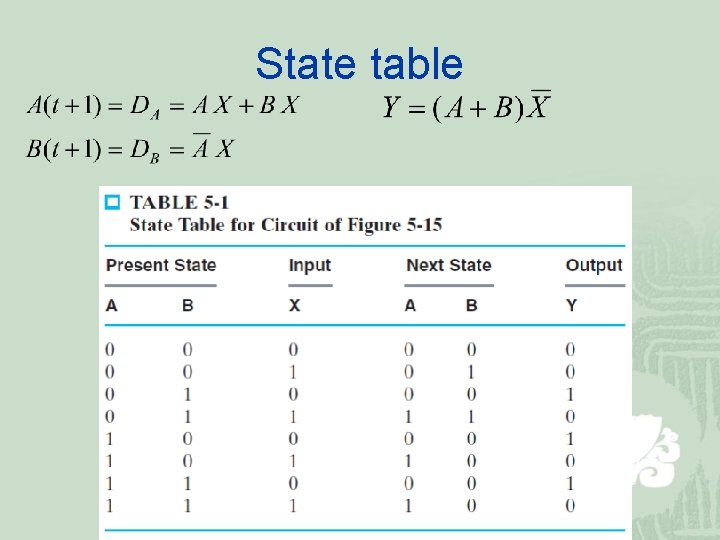

State table

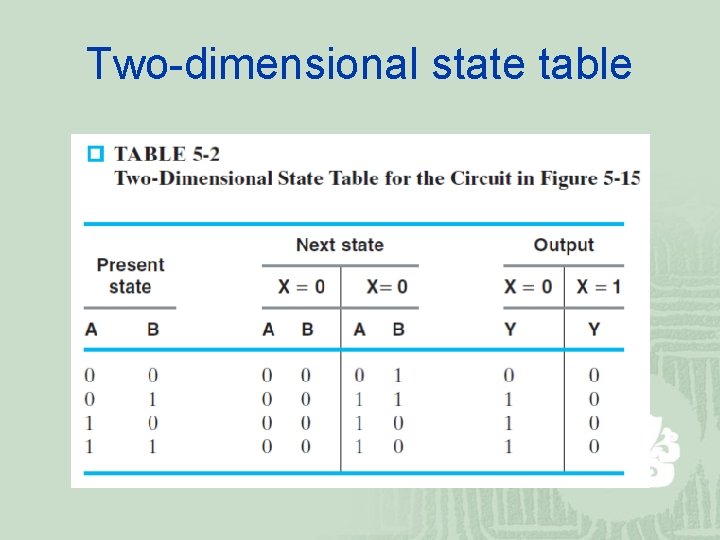

Two-dimensional state table

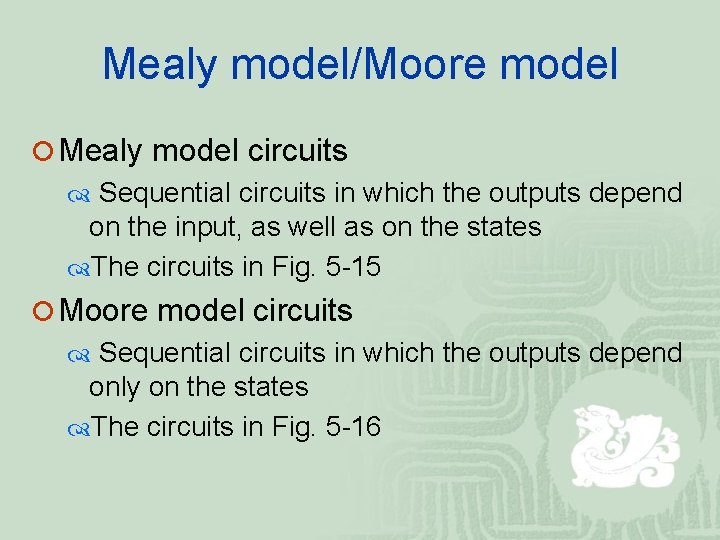

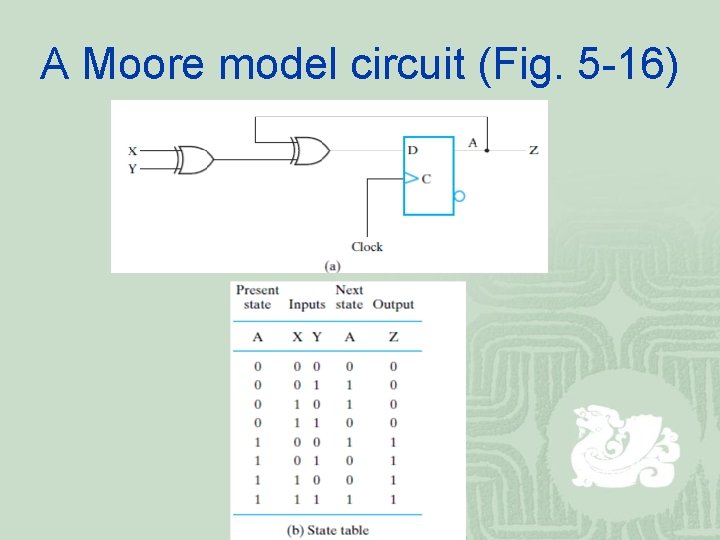

Mealy model/Moore model ¡ Mealy model circuits Sequential circuits in which the outputs depend on the input, as well as on the states The circuits in Fig. 5 -15 ¡ Moore model circuits Sequential circuits in which the outputs depend only on the states The circuits in Fig. 5 -16

A Moore model circuit (Fig. 5 -16)

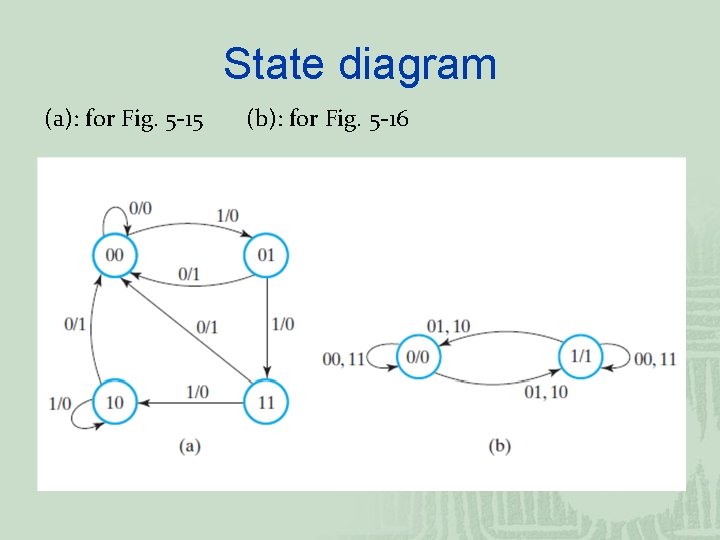

State diagram (a): for Fig. 5 -15 (b): for Fig. 5 -16

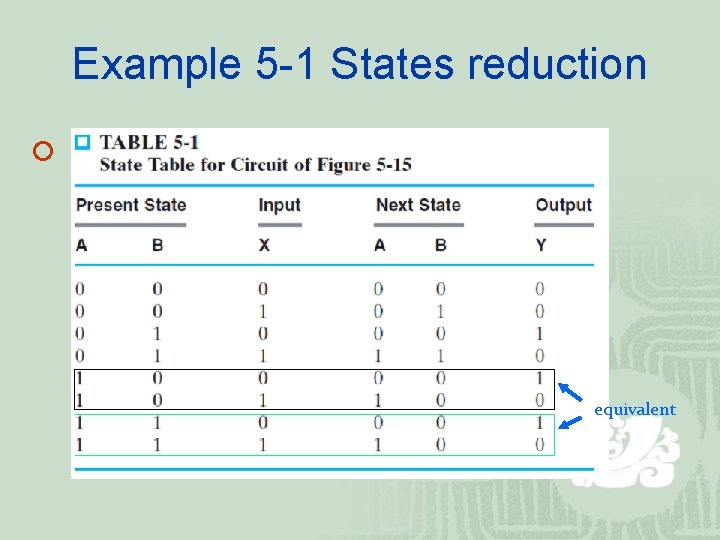

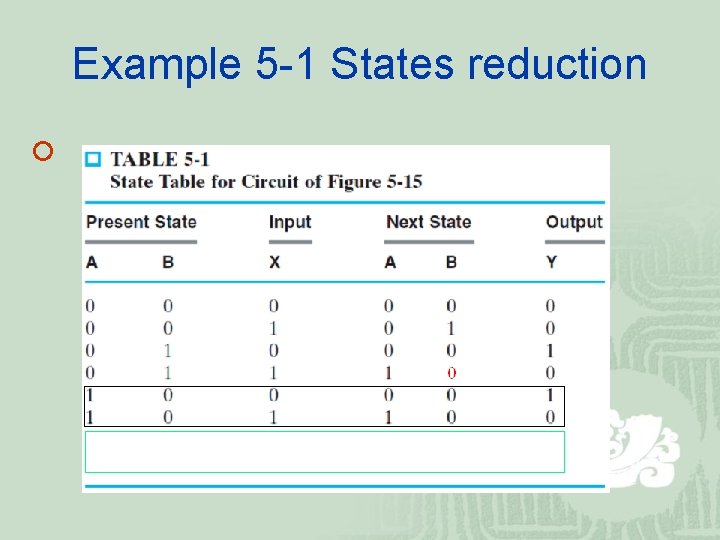

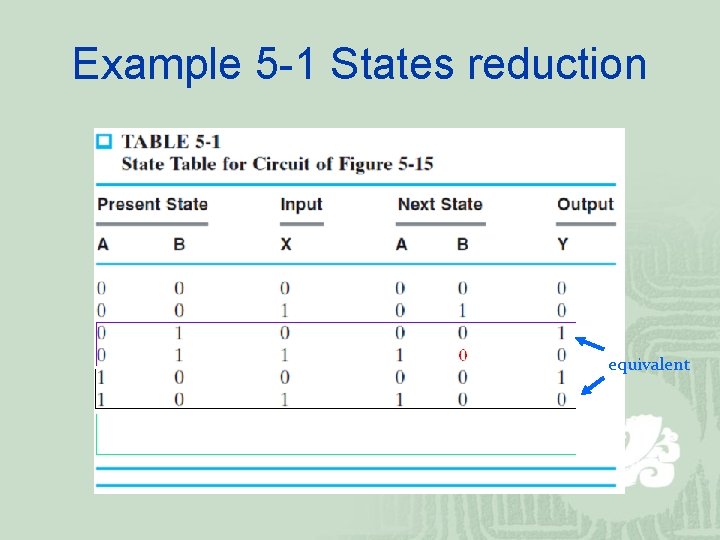

Example 5 -1 States reduction ¡ equivalent

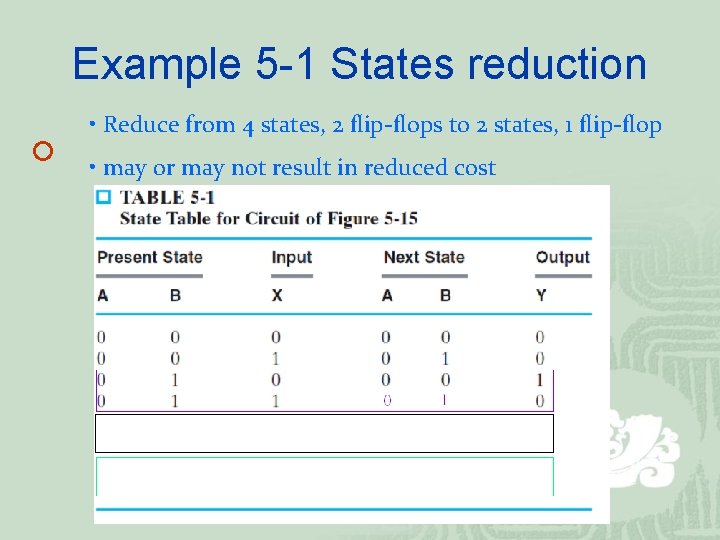

Example 5 -1 States reduction ¡

Example 5 -1 States reduction equivalent

Example 5 -1 States reduction ¡ • Reduce from 4 states, 2 flip-flops to 2 states, 1 flip-flop • may or may not result in reduced cost

Sequential Circuit Simulation ¡ A simulator for the input/output of a designed circuit ¡ Functional simulation ¡ Timing simulation

- Slides: 27